# MachXO sysIO Usage Guide

September 2010 Technical Note TN1091

# Introduction

The MachXO™ sysIO™ buffers provide the ability to easily interface with other devices using advanced system I/O standards. This technical note describes the sysIO standards available and how they can be implemented using Lattice design software.

# sysIO Buffer Overview

The MachXO sysIO interface contains multiple Programmable I/O Cell (PIC) blocks. Each PIC contains two Programmable I/Os (PIOs). Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C"). In the MachXO256, MachXO1200 and MachXO2280 devices, the PIOs are arranged in groups of six (PIOA, PIOB, PIOC, PIOD, PIOE, PIOF) on the top and bottom sides of the device and in groups of four (PIOA, PIOB, PIOC, PIOD) and two (PIOA, PIOB) on the left and right sides of the device. In the MachXO640 device, the PIOs are arranged in groups of six (PIOA, PIOB, PIOC, PIOD, PIOE, PIOF) on the top and bottom sides and in groups of four (PIOA, PIOB, PIOC, PIOD) on the left and right sides of the device.

The larger two devices, MachXO1200 and MachXO2280, support single-ended, differential receiver and differential output sysIO buffers. The two smaller devices, MachXO256 and MachXO640, support single-ended sysIO buffers. For more information on the architecture of the sysIO buffer please refer to the device data sheets.

# Supported sysIO Standards

The MachXO sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2, 1.5, 1.8, 2.5 and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down or bus-keeper latch) on I/O buffers. MachXO1200 and MachXO2280 devices also support differential standards like LVDS, RSDS, BLVDS and LVPECL. Table 8-1 lists the sysIO standards supported in the MachXO devices.

Table 8-1. sysIO Standards Supported

|                      | V <sub>CCIO</sub> (V) |      |       |

|----------------------|-----------------------|------|-------|

| Standard             | Min.                  | Тур. | Max.  |

| LVCMOS 3.3           | 3.135                 | 3.3  | 3.465 |

| LVCMOS 2.5           | 2.375                 | 2.5  | 2.625 |

| LVCMOS 1.8           | 1.71                  | 1.8  | 1.89  |

| LVCMOS 1.5           | 1.425                 | 1.5  | 1.575 |

| LVCMOS 1.2           | 1.14                  | 1.2  | 1.26  |

| LVTTL                | 3.135                 | 3.3  | 3.465 |

| PCI <sup>3</sup>     | 3.135                 | 3.3  | 3.465 |

| LVDS <sup>1, 2</sup> | 2.375                 | 2.5  | 2.625 |

| LVPECL1              | 3.135                 | 3.3  | 3.465 |

| BLVDS <sup>1</sup>   | 2.375                 | 2.5  | 2.625 |

| RSDS <sup>1</sup>    | 2.375                 | 2.5  | 2.625 |

$<sup>{\</sup>bf 1.}\ \ {\bf Inputs\ on\ chip.\ Outputs\ are\ implemented\ with\ the\ addition\ of\ external\ resistors.}$

<sup>2.</sup> MachXO1200 and MachXO2280 devices have dedicated LVDS buffers

<sup>3.</sup> Input on the top bank of the MachXO1200 and MachXO2280 only.

# sysIO Banking Scheme

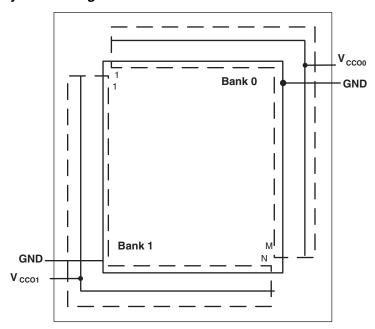

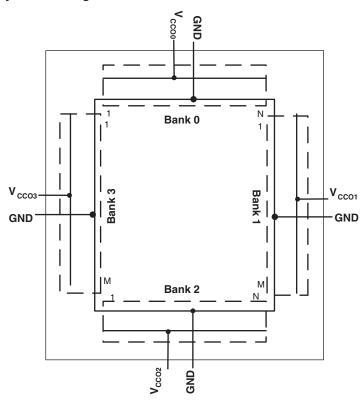

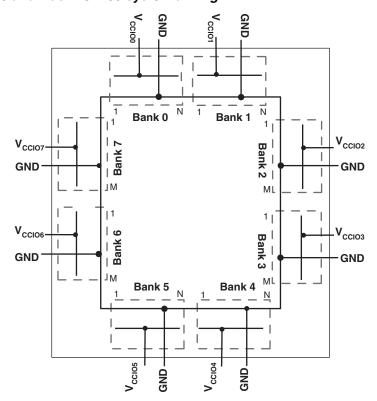

The MachXO family has a non-homogeneous I/O banking structure. The MachXO256 has two I/O banks, the MachXO640 has four I/O banks and the two largest devices, the MachXO1200 and the MachXO2280, have eight I/O banks. The figures below show the banking structures in each of the devices. Each sysIO bank has a  $V_{CCIO}$  supply voltage.

On the MachXO1200 and MachXO2280 devices, the top and bottom banks of the sysIO buffer pair consist of two single-ended output drivers, two single-ended and one differential input buffer. The sysIO buffers on the top side bank also supports PCI buffers. The left and right side sysIO buffer pairs, along with the two single-ended output and input drivers, a differential input and a differential driver on half the I/I/Os of the bank. On the MachXO640 and MachXO256 devices, all the banks of the sysIO buffer pair consists of two single-ended output drivers (with complementary outputs) and two single-ended and input buffers. All the banks will also support differential output buffers using external resistors. The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Figures 1, 2 and 3 show the banking schemes for the MachXO640, MachXO256 and MachXO1200/MachXO2280 devices respectively.

Figure 8-1. MachXO256 sysIO Banking

Figure 8-2. MachXO640 sysIO Banking

Figure 8-3. MachXO1200 and MachXO2280 sysIO Banking

# V<sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)

Each bank has a separate  $V_{CCIO}$  supply that powers the single-ended output drivers and the ratioed input buffers such as LVTTL, LVCMOS and PCI. LVTTL, LVCMOS3.3, LVCMOS2.5 and LVCMOS1.2 also have fixed threshold options allowing them to be placed in any bank and is independent of bank  $V_{CCIO}$ . The  $V_{CCIO}$  voltage applied to the bank determines the ratioed input standards that can be supported in that bank. It is also used to power the differential output drivers.

The  $V_{\rm CCIO}$  of one of the banks is also used to power the JTAG pins (Bank1 for MachXO256, Bank2 for MachXO640 and Bank5 for MachXO1200 and MachXO2280 devices). Therefore, the threshold of the JTAG pins is determined by the  $V_{\rm CCIO}$  of the JTAG bank.

# $V_{CCAUX}$ (3.3V)

In addition to the bank  $V_{CCIO}$  supplies, devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  auxiliary supply that powers the differential and referenced input buffers.  $V_{CCAUX}$  is required because  $V_{CC}$  does not have enough headroom to satisfy the common-mode range requirements of these drivers and input buffers.

# Mixed Voltage Support in a Bank

The MachXO sysIO buffer is connected to three parallel ratioed input buffers. These three parallel buffers are connected to  $V_{CCIO}$ ,  $V_{CCAUX}$  and to  $V_{CC}$ , giving support for thresholds that track with  $V_{CCIO}$ , as well as fixed thresholds for 3.3V ( $V_{CCAUX}$ ) and 1.2V ( $V_{CC}$ ) inputs. This allows the input threshold for ratioed buffers to be assigned on a pin-by-pin basis, rather than being tracked with  $V_{CCIO}$ . This option is available for all 1.2V, 2.5V and 3.3V ratioed inputs and is independent of the bank  $V_{CCIO}$  voltage. For example, if the bank  $V_{CCIO}$  is 1.8V, it is possible to have 1.2V and 3.3V ratioed input buffers with fixed thresholds, as well as 2.5V ratioed inputs with tracking thresholds.

Prior to device configuration, the ratioed input thresholds always track the bank  $V_{CCIO}$ . This option only takes effect after configuration. Output standards within a bank are always set by  $V_{CCIO}$ . Table 8-2 shows the sysIO standards that the user can mix in the same bank.

Table 8-2. Mixed Voltage Support

| Input sysIO Standards |      |      |      | Outpu | t sysIO Sta | ndards |      |      |      |      |

|-----------------------|------|------|------|-------|-------------|--------|------|------|------|------|

| V <sub>CCIO</sub>     | 1.2V | 1.5V | 1.8V | 2.5V  | 3.3V        | 1.2V   | 1.5V | 1.8V | 2.5V | 3.3V |

| 1.2V                  | Yes  |      |      | Yes   | Yes         | Yes    |      |      |      |      |

| 1.5V                  | Yes  | Yes  |      | Yes   | Yes         |        | Yes  |      |      |      |

| 1.8V                  | Yes  |      | Yes  | Yes   | Yes         |        |      | Yes  |      |      |

| 2.5V                  | Yes  |      |      | Yes   | Yes         |        |      |      | Yes  |      |

| 3.3V                  | Yes  |      |      | Yes   | Yes         |        |      |      |      | Yes  |

# sysIO Standards Supported in Each Bank

Table 8-3. I/O Standards Supported by Various Banks in the MachXO640 and MachXO256

| Description                   | Bank 0                                                                                                                           | Bank1                                                                                                                            | Bank2                                                                                                                            | Bank3                                                                            |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| I/O Buffer Type               | Single-ended                                                                                                                     | Single-ended                                                                                                                     | Single-ended                                                                                                                     | Single-ended                                                                     |

| Output Standards<br>Supported | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25E¹ LVPECL¹ BLVDS¹ RSDS¹ |

| Inputs                        | All Single-ended                                                                                                                 | All Single-ended                                                                                                                 | All Single-ended                                                                                                                 | All Single-ended                                                                 |

| Clock Inputs                  | All Single-ended                                                                                                                 | All Single-ended                                                                                                                 | All Single-ended                                                                                                                 | All Single-ended                                                                 |

<sup>1.</sup> These differential standards are implemented by using complementary LVCMOS driver with external resistor pack.

Table 8-4. I/O Standards Supported by I/O Pins on Each Side of the MachXO1200 and MachXO2280

| Description                   | Тор                                                                                                                                     | Right                                                                                                                                                | Bottom                                                                                                                           | Left                                                                                                                                                 |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Buffer Type               | Single-ended                                                                                                                            | Single-ended and Differential                                                                                                                        | Single-ended                                                                                                                     | Single-ended and Differential                                                                                                                        |

| Output Standards<br>Supported | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12  PCI33 LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25 <sup>2</sup> LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> | LVTTL LVCMOS33 LVCMOS25 LVCMOS18 LVCMOS15 LVCMOS12 LVDS25 <sup>2</sup> LVDS25E <sup>1</sup> LVPECL <sup>1</sup> BLVDS <sup>1</sup> RSDS <sup>1</sup> |

| Inputs                        | All Single-ended,<br>Differential                                                                                                       | All Single-ended,<br>Differential                                                                                                                    | All Single-ended,<br>Differential                                                                                                | All Single-ended,<br>Differential                                                                                                                    |

| Clock Inputs                  | All Single-ended,<br>Differential (PLL input)                                                                                           | All Single-ended,<br>Differential (PLL input)                                                                                                        | All Single-ended,<br>Differential (PLL input)                                                                                    | All Single-ended,<br>Differential (PLL input)                                                                                                        |

| PCI Support                   | PCI33 with Clamp                                                                                                                        |                                                                                                                                                      |                                                                                                                                  |                                                                                                                                                      |

| LVDS Output Buffers           |                                                                                                                                         | LVDS (3.5mA) Buffers                                                                                                                                 |                                                                                                                                  | LVDS (3.5mA) Buffers                                                                                                                                 |

<sup>1.</sup> These differential standards are implemented by using complementary LVCMOS driver with external resistor pack.

# **LVCMOS Buffer Configurations**

All LVCMOS buffer have programmable pull, programmable drive and programmable slew configurations that can be set in the software.

# Programmable PULLUP/PULLDOWN/BUSKEEPER

When configured as LVCMOS or LVTTL, each sysIO buffer has a weak pull-up, a weak pull-down resistor and a weak buskeeper (bus hold latch) available. Each I/O can independently be configured to have one of these features or none of them.

<sup>2.</sup> MachXO256 only has 2 banks, Banks 0 and Bank 1.

<sup>2.</sup> These are supported on half the I/Os of the bank.

# **Programmable Drive**

All LVCMOS and LVTTL single-ended drivers have programmable drive strength. This option can be set for each I/O independently. The table below lists the programmable drive strengths available for each I/O standard. The actual value will vary with the I/O voltage. The user must consider the maximum allowable current per bank and the package thermal limit current when selecting the drive strength.

Table 8-5. Programmable Drive Strength

| Single-ended I/O Standard | Programmable Drive (mA) |

|---------------------------|-------------------------|

| LVCMOS12                  | 2, 6                    |

| LVCMOS15                  | 4, 8                    |

| LVCMOS18                  | 4, 8, 12, 14            |

| LVCMOS25                  | 4, 8, 12, 14            |

| LVCMOS33                  | 4, 8, 12, 14            |

| LVTTL                     | 4, 8, 12, 16            |

# **Programmable Slew Rate**

Each LVCMOS or LVTTL output buffer pin also has a programmable output slew rate control that can be configured for either low noise or high-speed performance. Each I/O pin also has an individual slew rate control. This allows a designer to specify slew rate control on a pin-by-pin basis. This slew rate control affects both the rising edge and the falling edges.

# **Open-Drain Control**

Each LVCMOS and LVTTL output buffer can be configured to function as an open-drain output. The user can implement an open-drain output by turning on the OPENDRAIN attribute in the software.

### **Programmable PCICLAMP**

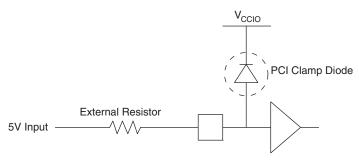

Each sysIO buffer on the top bank of the MachXO1200 and MachXO2280 devices can be configured to support PCI33. The buffers also have a PCI clamp diode that will be turned on when the sysIO buffer is configured as PCI33.

The PCI clamp is mainly used when implementing a 3.3V PCI interface. The PCI Specification revision 2.2 requires the use of clamping diodes for 3.3V operation. For more information on the PCI interface, please refer to the PCI specification, revision 2.2.

The PCI clamp can also be optionally turned on for LVCMOS and LVTTL sysIO buffers on the top bank of the MachXO1200 and MachXO2280 devices. In this case, the PCI clamp is used to implement a 5V input interface.

# 5V Input Interface Using the PCI Clamp Diode

All the I/Os on the top side of the MachXO1200 and MachXO2280 devices (Banks 0 and 1) have a clamp diode that is used to clamp the voltage at the input to  $V_{CCIO}$ . This clamp diode can be used along with an external resistor to make an input 5V tolerant.

Figure 8-4. 5V Input Interface Example

The value of this external resistor will depend on the PCI clamp diode characteristics. The voltage vs. current data across this diode can be found in the device IBIS model.

In order to interface to 5V input, it is recommended that the  $V_{CCIO}$  is set between 2.5V to 3.3V.

Below is an example of how to calculate the value of this external resistor when  $V_{CCIO}$  is 2.75V.

- Maximum voltage at input pin, V<sub>INMAX</sub> = 3.75V (see the <u>MachXO Family Data Sheet</u> for more details)

- Bank V<sub>CCIO</sub> = 2.75V

- Maximum voltage drop across clamp diode, V<sub>D</sub> = V<sub>INMAX</sub> V<sub>CCIO</sub> = 3.75 2.75 = 1V

- The current across the clamp diode at  $V_D$  can be found in the power clamp data of the IBIS file. Below is the power clamp portion of the IBIS file, for a LVCMOS3.3 input model with PCI Clamp turned on. When  $V_D$  is 1V, the clamp diode current is  $I_D = 382\mu A$ .

Table 8-6. Power Clamp Data from a Typical IBIS Model<sup>1</sup>

| Voltage | I (max.) | Units |

|---------|----------|-------|

| -1.40   | 408      | μΑ    |

| -1.30   | 402      | μΑ    |

| -1.20   | 395      | μΑ    |

| -1.10   | 389      | μΑ    |

| -1.00   | 382      | μΑ    |

| -0.90   | 380      | μΑ    |

| -0.80   | 380      | μΑ    |

| -0.70   | 380      | μΑ    |

| -0.60   | 380      | μΑ    |

| -0.50   | 380      | μΑ    |

| -0.40   | 353      | μΑ    |

| -0.30   | 51       | μΑ    |

| -0.20   | 3.8      | μΑ    |

| -0.10   | 0.23     | μΑ    |

| 0.00    | 0.15     | μΑ    |

Always consult the latest IBIS data available from Lattice. IBIS model information is available by device family on the <u>Lattice web site</u>.

Assume the maximum output voltage of the driving device is V<sub>EXT</sub> = 5.25V. The value of the external resistor can then be calculated as follows:

$$R_{EXT} = (V_{EXT} - V_{INMAX})/I_D = (5.25V - 3.75V)/382\mu A = 3.93 \text{ K ohm}$$

If the  $V_{CCIO}$  of the bank is increased, it will also increase the value of the external resistor required. Keep in mind that changing the Bank  $V_{CCIO}$  will change the value of the input threshold voltage.

# **Software sysIO Attributes**

sysIO attributes can be specified in the HDL, using the Preference Editor GUI in ispLEVER<sup>®</sup>, the Spreadsheet View in Lattice Diamond<sup>™</sup> design software, or in the ASCII Preference file (.perf) directly. Appendices A, B and C list examples of how these can be assigned using each of the methods mentioned above. This section describes in detail each of these attributes.

# **IO\_TYPE**

This is used to set the sysIO standard for an I/O. The  $V_{CCIO}$  required to set these I/O standards are embedded in the attribute names itself. There is no separate attribute to set the  $V_{CCIO}$  requirements. Table 6 and 7 list the available I/O types.

Table 8-7. IO\_TYPE Attribute Values for MachXO640 and MachXO256 Devices

| sysIO Signaling Standard | IO_TYPE               |

|--------------------------|-----------------------|

| DEFAULT                  | LVCMOS25              |

| RSDS                     | RSDS                  |

| Emulated LVDS 2.5V       | LVDS25E <sup>1</sup>  |

| Bus LVDS 2.5V            | BLVDS25 <sup>1</sup>  |

| LVPECL 3.3V              | LVPECL33 <sup>1</sup> |

| LVTTL                    | LVTTL33               |

| 3.3V LVCMOS              | LVCMOS33              |

| 2.5V LVCMOS              | LVCMOS25              |

| 1.8V LVCMOS              | LVCMOS18              |

| 1.5V LVCMOS              | LVCMOS15              |

| 1.2V LVCMOS              | LVCMOS12              |

These differential standards are implemented by using complementary LVCMOS driver with external resistor pack.

Table 8-8. IO\_TYPE Attribute Values for MachXO1200 and MachXO2280 Devices

| sysIO Signaling Standard | IO_TYPE               |

|--------------------------|-----------------------|

| DEFAULT                  | LVCMOS25              |

| LVDS 2.5V                | LVDS25 <sup>2</sup>   |

| RSDS                     | RSDS                  |

| Emulated LVDS 2.5V       | LVDS25E <sup>1</sup>  |

| Bus LVDS 2.5V            | BLVDS25 <sup>1</sup>  |

| LVPECL 3.3V              | LVPECL33 <sup>1</sup> |

| LVTTL                    | LVTTL33               |

| 3.3V LVCMOS              | LVCMOS33              |

| 2.5V LVCMOS              | LVCMOS25              |

| 1.8V LVCMOS              | LVCMOS18              |

| 1.5V LVCMOS              | LVCMOS15              |

| 1.2V LVCMOS              | LVCMOS12              |

| 3.3V PCI                 | PCI33 <sup>3</sup>    |

These differential standards are implemented by using a complementary LVCMOS driver with external resistor pack.

<sup>2.</sup> Available on 50% of the I/Os on the right and left side banks.

<sup>3.</sup> Available on the top side bank.

#### **OPENDRAIN**

LVCMOS and LVTTL I/O standards can be set to open-drain configuration by using the OPENDRAIN attribute.

Values: ON, OFF

Default: OFF

#### DRIVE

The Drive Strength attribute is available for LVTTL and LVCMOS output standards. These can be set or each I/O pin individually. The programmable drive available on a pad will depend on the  $V_{\rm CCIO}$ . Table 8-9 shows the drive strength available for different I/O standards and the defaults for each of them.

Table 8-9. Programmable Drive Strength Values at Various V<sub>CCIO</sub> Voltages

| Output Standard | Drive (mA)   | Default (mA) |

|-----------------|--------------|--------------|

| LVTTL           | 4, 8, 12, 16 | 8            |

| LVCMOS33        | 4, 8, 12, 14 | 8            |

| LVCMOS25        | 4, 8, 12, 14 | 12           |

| LVCMOS18        | 4, 8, 12, 14 | 8            |

| LVCMOS15        | 4, 8         | 8            |

| LVCMOS12        | 2, 6         | 6            |

#### **PULLMODE**

The PULLMODE attribute is available for all the LVTLL and LVCMOS inputs and outputs. This attribute can be enabled for each I/O independently.

Values: UP, DOWN, NONE, KEEPER

Default: UP

Table 8-10. PULLMODE Values

| PULL Options      | PULLMODE Value |

|-------------------|----------------|

| Pull up (Default) | UP             |

| Pull Down         | DOWN           |

| Bus Keeper        | KEEPER         |

| Pull Off          | NONE           |

#### **PCICLAMP**

PCI33 inputs and outputs are available on the top bank of the MachXO1200 and MachXO2280 devices. When an I/O is configured as a PCI33 standard, the PCICLAMP is enabled for that buffer. The PCICLAMP is also available for all LVCMOS33 and LVTTL inputs. This is used to implement a 5V input interface.

Values: ON, OFF

Default: ON (for PCI33 input and output)

OFF (for LVCMOS33 and LVTTL inputs)

#### **SLEWRATE**

The SLEWRATE attribute is available for all LVTTL and LVCMOS output drivers. Each I/O pin has an individual slew rate control. This allows designers to specify the slew rate control on pin-by-pin basis.

Values: FAST, SLOW

Default: FAST

#### LOC

This attribute can be used to make pin assignments to the I/O ports in the design. This attributes is only used when the pin assignments are made in HDL source. Users can also assign pins directly using the Preference Editor GUI in ispLEVER or the Spreadsheet View in Diamond. The appendices of this document explain this in greater detail.

# **Design Considerations and Usage**

This section discusses some rules and considerations for designing with the MachXO sysIO buffer.

# **Banking Rules**

- If the V<sub>CCIO</sub> for any bank is set to 3.3V, it is recommended that it be connected to the same power supply as V<sub>CCAUX</sub>, thus minimizing leakage.

- If V<sub>CCIO</sub> for any bank is set to 1.2V, it is recommended that it be connected to the same power supply as V<sub>CC</sub>, thus minimizing leakage.

- PCI I/O standards with PCI clamps are only available on the top bank (Banks 0 and 1) on the MachXO1200 and MachXO2280 devices.

- PCI I/O standards with PCI clamps are not available on the MachXO640 and MachXO256 devices.

- Only 50% of the I/Os on the left and right banks of the MachXO1200 and MachXO2280 devices support a True LVDS driver. True LVDS receivers are available on all banks for the MachXO1200 and MachXO2280 devices.

- All banks support emulated differential outputs using an external resistor pack and complementary LVCMOS driver.

#### **Zero Hold Time**

The user can achieve a zero hold time for his or her inputs by specifying a zero hold time preference in the software. The software will add additional delays to the input path in order to achieve this zero hold time.

## **Fast Output Path**

The MachXO devices have a dedicated fast output I/O connection from the adjacent PFUs to the I/O buffers within the PIO. This connection provides faster output delays for faster clock-to-output propagation delays and pin-to-pin propagation delays. The software will automatically use this fast output path to achieve faster  $t_{CO}$  and  $t_{PD}$  requirements. You can fulfill the  $t_{CO}$  and  $t_{PD}$  requirement by assigning these preferences in the Preference Editor in the software.

### **Dedicated Pins**

#### Global Set Rest (GSR)

The GSR in the MachXO devices is an asynchronous Global Set Reset. This signal is can be programmed to come from either the PFU logic or from the dedicated GSR input pad. When the software does not see any logic associated with the GSR, then it will automatically use the dedicated GSR input path. This provides faster timing. When the reset used is a logic reset, the polarity is programmable. When the dedicated GSR input from the GSR pad is used, the polarity has to be active low.

#### Tristate All (TSALLPAD)

All MachXO devices have a dedicated TSALLPAD pin that is used to enable or disable the tristate control to all the output buffers. By default, the pin will function as an I/O unless programmed to be a TSALLPAD. This signal also has programmable global polarity control. By default, the polarity is active high. This global tristate control signal can also be generated using user logic.

When the TSALLPAD is enabled, the software will implement the tristate control using the TSALL software primitive. The polarity control of the TSALLPAD will control the polarity of TSALL.

When TSALLPAD is not used in the design, but is required for test purposes, the TSALL primitive can be instantiated in the HDL and the TSALLPAD is connected to the input of this primitive.

# **Differential I/O Implementation**

MachXO devices support a variety of differential standards, as detailed in the following sections.

#### LVDS (MachXO1200 and MachXO2280)

True LVDS (LVDS25) drivers are available on 50% of the I/Os on the left and right sides of the MachXO1200 and MachXO2280 devices. LVDS input support is available on all sides of the MachXO1200 and MachXO2280 devices.

#### **LVDSE**

The single-ended sysIO buffer pairs in all the MachXO devices support LVDS output drivers using complementary LVCMOS drivers with external resistors (LVDS25E) on all four sides of the device.

The MachXO1200 and MachXO2280 devices also support LVDSE inputs on all four sides of the device.

Please refer to the MachXO Family Data Sheet for a detailed explanation of these LVDS implementations.

#### **BLVDS**

All single-ended sysIO buffer pairs in all the MachXO devices support Bus-LVDS output driver using complementary LVCMOS drivers with external resistors on all the four sides of the device.

The MachXO1200 and MachXO2280 devices also support BLVDS inputs on all four sides of the device.

Please refer to the MachXO Family Data Sheet for a detailed explanation of BLVDS implementation.

#### **RSDS**

All single-ended sysIO buffer pairs in all the MachXO devices support RSDS output driver using complementary LVCMOS drivers with external resistors.

The MachXO1200 and MachXO2280 devices also support RSDS inputs on all four sides of the device.

Please refer to the MachXO Family Data Sheet for a detailed explanation of RSDS implementation.

#### **LVPECL**

All single-ended sysIO buffers pairs in all the MachXO devices support LVPECL output driver using complementary LVCMOS drivers with external resistors.

The MachXO1200 and MachXO2280 devices also support LVPECL inputs on all four sides of the device.

Please refer to the MachXO Family Data Sheet for a detailed explanation of LVPECL implementation.

# **Technical Support Assistance**

Hotline: 1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail: techsupport@latticesemi.com

Internet: www.latticesemi.com

# **Revision History**

| Date           | Version | Change Summary                                                                                                                             |

|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| _              | _       | Previous Lattice releases.                                                                                                                 |

| July 2007      | 01.4    | Correction in VCCIO (1.2V/1.5V/1.8V/2.5V3.3V) text section. VCCIO of Bank2 is used to power the JTAG pin for MachXO640, rather than Bank3. |

| September 2010 | 01.5    | Updated for Lattice Diamond design software support.                                                                                       |

|                |         | Updated IBIS information.                                                                                                                  |

# Appendix A. HDL Attributes for Synplify® and Precision® RTL Synthesis

Using these HDL attributes, you can assign the sysIO attributes directly in your source. You will need to use the attribute definition and syntax for the synthesis vendor you are planning to you to use. Below are a list of all the sysIO attributes syntax and examples for Precision RTL Synthesis and Synplify. This section only lists the sysIO buffer attributes for these devices. Refer to the Precision RTL Synthesis and Synplify user manuals for a complete list of synthesis attributes. These manuals are available through the ispLEVER or Diamond software Help.

# VHDL Synplify/Precision RTL Synthesis

This section lists syntax and examples for all the sysIO attributes in VHDL when using Precision RTL Synthesis and Synplify synthesis tools.

# **Syntax**

Table 8-11. VHDL Attribute Syntax for Precision RTL Synthesis and Synplify

| Attribute | Syntax                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------|

| IO_TYPE   | attribute IO_TYPE: string; attribute IO_TYPE of <i>Pinname</i> : signal is " <i>IO_TYPE Value</i> ";       |

| OPENDRAIN | attribute OPENDRAIN: string; attribute OPENDRAIN of <i>Pinname</i> : signal is " <i>OpenDrain Value</i> "; |

| DRIVE     | attribute DRIVE: string; attribute DRIVE of <i>Pinname</i> : signal is " <i>Drive Value</i> ";             |

| PULLMODE  | attribute PULLMODE: string; attribute PULLMODE of <i>Pinname</i> : signal is " <i>Pullmode Value</i> ";    |

| PCICLAMP  | attribute PCICLAMP: string; attribute PCICLAMP of <i>Pinname</i> : signal is " <i>PCIClamp Value</i> ";    |

| SLEWRATE  | attribute PULLMODE: string; attribute PULLMODE of <i>Pinname</i> : signal is " <i>Slewrate Value</i> ";    |

| LOC       | attribute LOC: string; attribute LOC of <i>Pinname</i> : signal is " <i>pin_locations</i> ";               |

#### **Examples**

#### **IO TYPE**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE IO\_TYPE: string;

--\*\*\*IO\_TYPE assignment for I/O Pin\*\*\*

ATTRIBUTE IO\_TYPE OF portA: SIGNAL IS "PCI33";

ATTRIBUTE IO\_TYPE OF portB: SIGNAL IS "LVCMOS33";

ATTRIBUTE IO\_TYPE OF portC: SIGNAL IS "LVDS25";

#### **OPENDRAIN**

--\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE OPENDRAIN: string;

--\*\*\*OPENDRAIN assignment for I/O Pin\*\*\*

ATTRIBUTE OPENDRAIN OF portB: SIGNAL IS "ON";

#### **DRIVE**

#### --\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE DRIVE: string;

# --\*\*\*DRIVE assignment for I/O Pin\*\*\*

ATTRIBUTE DRIVE OF portB: SIGNAL IS "16";

#### **PULLMODE**

#### --\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE PULLMODE: string;

# --\*\*\*PULLMODE assignment for I/O Pin\*\*\*

ATTRIBUTE PULLMODE OF portA: SIGNAL IS "DOWN"; ATTRIBUTE PULLMODE OF portB: SIGNAL IS "UP";

#### **PCICLAMP**

#### --\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE PCICLAMP: string;

#### --\*\*\*PCICLAMP assignment for I/O Pin\*\*\*

ATTRIBUTE PCICLAMP OF portA: SIGNAL IS "ON";

#### **SLEWRATE**

#### --\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE SLEWRATE: string;

## --\*\*\* SLEWRATE assignment for I/O Pin\*\*\*

ATTRIBUTE SLEWRATE OF portB: SIGNAL IS "FAST";

#### LOC

#### --\*\*\*Attribute Declaration\*\*\*

ATTRIBUTE LOC: string;

# --\*\*\* LOC assignment for I/O Pin\*\*\*

ATTRIBUTE LOC OF input\_vector: SIGNAL IS "E3,B3,C3";

# **Verilog Synpilfy**

This section lists syntax and examples for all the sysIO attributes in Verilog using the Synplify synthesis tool.

## **Syntax**

Table 8-12. Verilog Synplify Attribute Syntax

| Attribute | Syntax                                                       |

|-----------|--------------------------------------------------------------|

| IO_TYPE   | PinType PinName /* synthesis IO_TYPE="IO_Type Value"*/;      |

| OPENDRAIN | PinType PinName /* synthesis OPENDRAIN ="OpenDrain Value"*/; |

| DRIVE     | PinType PinName /* synthesis DRIVE="Drive Value"*/;          |

| PULLMODE  | PinType PinName /* synthesis PULLMODE="Pullmode Value"*/;    |

| PCICLAMP  | PinType PinName /* synthesis PCICLAMP ="PCIClamp Value"*/;   |

| SLEWRATE  | PinType PinName /* synthesis SLEWRATE="Slewrate Value"*/;    |

| LOC       | PinType PinName /* synthesis LOC="pin_locations "*/;         |

# **Examples**

# //IO\_TYPE, PULLMODE, SLEWRATE and DRIVE assignment

output portB /\*synthesis IO\_TYPE="LVCMOS33" PULLMODE ="UP" SLEWRATE ="FAST" DRIVE ="14"\*/; output portC /\*synthesis IO\_TYPE="LVDS25" \*/;

#### //OPENDRAIN

output portA /\*synthesis OPENDRAIN ="ON"\*/;

#### //PCICLAMP

output portA /\*synthesis IO\_TYPE="PCI33" PCICLAMP ="PCICLAMP"\*/;

#### //I/O pin location

input [3:0] DATA0 /\* synthesis loc="E3,B1,F3"\*/;

# //Register pin location

reg data\_in\_ch1\_buf\_reg3 /\* synthesis loc="R40C47" \*/;

#### //Vectored internal bus

reg [3:0] data\_in\_ch1\_reg /\*synthesis loc ="R40C47,R40C46,R40C45,R40C44" \*/;

# **Verilog Precision RTL Synthesis**

This section lists syntax and examples for all the sysIO attributes in Verilog using the Precision RTL Synthesis synthesis tool.

#### **Syntax**

Table 8-13. Verilog Precision RTL Synthesis Attribute Syntax

| Attribute | Syntax                                                |

|-----------|-------------------------------------------------------|

| IO_TYPE   | // pragma attribute PinName IO_TYPE IO_TYPE Value     |

| OPENDRAIN | // pragma attribute PinName OPENDRAIN OpenDrain Value |

| DRIVE     | // pragma attribute PinName DRIVE Drive Value         |

| PULLMODE  | // pragma attribute PinName PULLMODE Pullmode Value   |

| PCICLAMP  | // pragma attribute PinName PCICLAMP PCIClamp Value   |

| SLEWRATE  | // pragma attribute PinName SLEWRATE Slewrate Value   |

| LOC       | // pragma attribute PinName LOC pin_location          |

#### Example

### //\*\*\*\*IO\_TYPE \*\*\*

// pragma attribute portA IO\_TYPE PCI33

// pragma attribute portB IO\_TYPE LVCMOS33

// pragma attribute portC IO\_TYPE SSTL25\_II

# //\*\*\* Opendrain \*\*\*

// pragma attribute portB OPENDRAIN ON

// pragma attribute portD OPENDRAIN OFF

# //\*\*\* Drive \*\*\*

// pragma attribute portB DRIVE 20

// pragma attribute portD DRIVE 8

## //\*\*\* Pullmode\*\*\*

// pragma attribute portB PULLMODE UP

#### //\*\*\* PCIClamp\*\*\*

// pragma attribute portB PCICLAMP ON

#### //\*\*\* Slewrate \*\*\*

// pragma attribute portB SLEWRATE FAST

// pragma attribute portD SLEWRATE SLOW

#### //\*\*\*LOC\*\*\*

// pragma attribute portB loc E3

# Appendix B. sysIO Attributes Using the ispLEVER Preference Editor or Diamond Spreadsheet View

You can assign the sysIO buffer attributes using the Pre-map Preference Editor GUI available in the ispLEVER or the Spreadsheet View GUI in Diamond. The Pin Attribute sheet in ispLEVER and Port Assignments sheet in Diamond list all the ports in your design and all the available sysIO attributes as preferences. When you click on each of these cells you get a list of all the valid I/O preferences for that port. Each column takes precedence over the next. Therefore, when you choose a particular IO\_TYPE, the DRIVE, PULLMODE and SLEWRATE columns will only list the valid combinations for that IO\_TYPE. The user can lock the pin locations using the pin location column of the Pin Attribute sheet. Right-click on a cell to list all the available pin locations. The Preference Editor and the Spreadsheet View will also do a DRC check to search for any incorrect pin assignments.

You can enter the DIN/ DOUT preferences using the Cell Attributes sheet of the Preference Editor. All the preferences assigned using the Preference Editor and the Spreadsheet View are written into the preference file (.prf).

Figure 8-5 shows the Pin Attribute sheet and the Cell Attribute sheet view of the Preference Editor. For further information on how to use the Preference Editor, please refer to the ispLEVER Help documentation. You can get to this in the Help menu option of the software.

≊ C:\Software\ispLever 5.0 Beta\evaluation\mojo\legalcomb\vhdl\prep\_9.prf\* \_|\_|× □··· prep\_9 □··· Input Ports PCIClamp SCHMITT\_TRIGGER OPENDRAIN Signal/Group Nam Bank IO Type Drive Slewrate Pullmode Output Load A 1 Output Port LVCMOS15 8 SLOW LIP OFF ah(7:0) 2 Output Port N/A LVCMOS15 8 UP N/A OFF SLOW q(5) N/A LVCMOS15 8 SLOW UP 3 Output Port q(7)as ck 4 Output Port q(3) N/A LVCMOS15 8 SLOW UP N/A OFF N/Δ LVCMOS15 8 SLOW UP N/A OFF 5 Output Port -- Output Ports LVDS25E 6 Output Port be Ν/A N/A NJA N/A LVCMOS15 SLOW UP N/A OFF 7 Output Port q(2) 8 Output Port q(1) N/A LVCMOS15 8 SLOW LIP N/A OFF 9 Output Port N/Δ LVCMOS15 8 SLOW UP M/A OFF q(4) Cells

N/A LVCMOS33 N/A 10 Input Port al(2) 11 Input Port al(3) N/A LVCMOS33 N/A N/A 12 Input Port al(1) Ν/A LVCMOS33 N/A NIA 13 Input Port N/A LVCMOS33 N/A NJA al(0) N/A LVCMOS25 N/A ON NJA 14 Input Port ah(1) 15 Input Port ah(5) N/A LVCMOS25 N/A N/A N/A LVCMOS33 N/A N/A 16 Input Port al(7) OFF 17 Input Port LVCMOS12 KEEPER N/A NJA Group Name Type ās N/A LVCMOS33 N/A 18 Input Port al(6) NJA 19 Input Port N/A LVCMOS25 N/A N/A 20 Input Port N/A LVCMOS25 N/A NJA ah(7) N/A LVCMOS18 N/A ΝJΑ 21 Input Port ah(6) N/A LVCMOS25 N/A NJA 22 Input Port ah(2) Þ ▶ Pin Attributes (Global ), Block ), Period/Frequency ), In/Out Clock ), Multicycle/Maxdelay /

Figure 8-5. Pin Attributes Tab

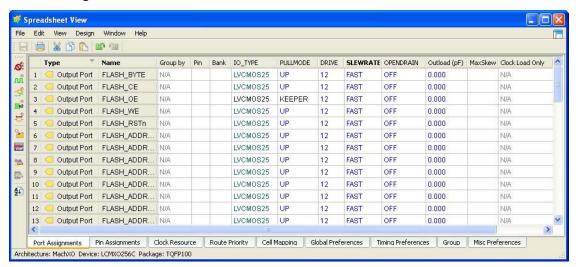

Figure 8-6 shows the Port Assignment sheet in the Diamond Spreadsheet View. For further information on how to use the Spreadsheet View, please refer to the Reference Guide available in Diamond.

#### Figure 8-6. Port Assignment Tab

# Appendix C. sysIO Attributes Using Preference File (ASCII File)

You can also enter the sysIO Attributes directly in the preference (.prf) file as sysIO buffer preferences. The PRF file is an ASCII file containing two separate sections: a schematic section for those preferences created by the Mapper or Translator, and a user section for preferences entered by the user. You can write user preferences directly into this file. The synthesis attributes appear between schematic start and schematic end of the file. You can enter the sysIO buffer preferences after the schematic end line using the preference file syntax. Below are a list of sysIO buffer preference syntax and examples.

#### **IOBUF**

This preference is used to assign the attribute IO\_TYPE, OPENDRAIN, DRIVE, PULLMODE, PCICLAMP and SLEWRATE.

#### **Syntax**

IOBUF [ALLPORTS | PORT <port name> | GROUP <group name>] (keyword=<value>)+;

where:

<port\_name> = These are not the actual top-level port names, but should be the signal name attached to the port.

PIOs in the physical design (.ncd) file are named using this convention. Any multiple listings or wildcarding should be done using GROUPs

Keyword = IO\_TYPE, OPENDRAIN, DRIVE, PULLMODE, PCICLAMP, SLEWRATE

#### Example

IOBUF PORT "port1" IO\_TYPE=LVTTL33 OPENDRAIN=ON DRIVE=8 PULLMODE=UP

PCICLAMP = OFF SLEWRATE=FAST;

DEFINE GROUP "bank1" "in\*" "out\_[0-31]";

IOBUF GROUP "bank1" IO\_TYPE=LVCMOS33;

#### LOCATE

When this preference is applied to a specified component, it places the component at a specified site and locks the component to the site. If applied to a specified macro instance it places the macro's reference component at a specified site, places all of the macro's pre-placed components (that is, all components that were placed in the macro's library file) in sites relative to the reference component, and locks all of these placed components at their sites. This can also be applied to a specified PGROUP.

#### **Syntax**

LOCATE [COMP < comp name > | MACRO < macro name > ] SITE < site name >;

LOCATE PGROUP cpgroup\_name [SITE <site\_name</pre>; | REGION <region\_name</pre>;

LOCATE PGROUP <pgroup\_name> RANGE <site\_1> [<site\_2> | <count>] [<direction>] | RANGE <chip\_side> [<direction>];

LOCATE BUS < bus name> ROW|COL < number>;

<bus name> := string

<number> := integer

Note: If the comp\_name, macro\_name, or site\_name begins with anything other than an alpha character (for example, "11C7"), you must enclose the name in quotes. Wildcard expressions are allowed in <comp\_name>.

# **Lattice Semiconductor**

## Example

This command places the port Clk0 on the site A4:

LOCATE COMP "Clk0" SITE "A4";

This command places the component PFU1 on the site named R1C7:

LOCATE COMP "PFU1" SITE "R1C7";

This command places bus1 on ROW 3 and bus2 on COL4

LOCATE BUS "bus1" ROW 3;

LOCATE BUS "bus2" COL 4;