## 1553 Encoder/Decoder

April 2005 Reference Design RD1021

### Introduction

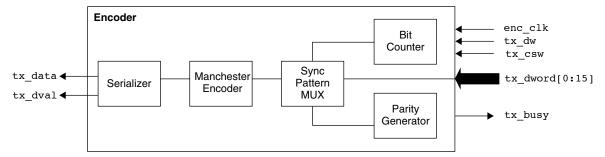

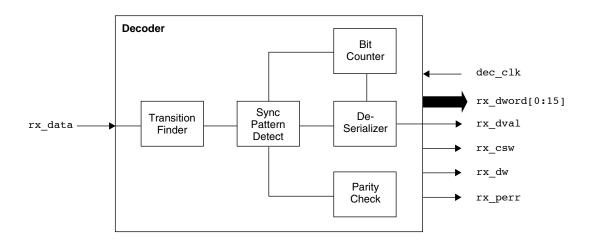

The MIL-STD-1553 is a low-speed serial bus used in avionics systems. This reference design implements Manchester II encoding and decoding required by the 1553 along with synchronization pattern insertion and identification, data serialization and de-serialization and parity checking and insertion functions.

#### **Features**

- MIL-STD-1553 Compatible

- 1 Mbps Data Rate

- · Sync Pattern Identification and Insertion

- · Manchester II Encoding/Decoding

- · Parity Checking and Insertion

- · Serialization and De-serialization

## **Functional Description**

The following figure shows a block diagram of the different functions implemented in this 1553 Encoder/Decoder along with the input/output signals.

Figure 1. 1553 Encoder/Decoder Block Diagram

### **Encoder Operation**

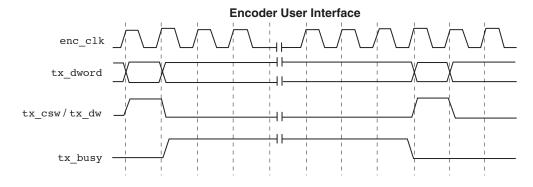

The encoder requires a single clock with a frequency (2 MHz) of twice the desired data rate (1 Mbps) for  $enc_clk$ . The encoder cycle begins with either  $tx_csw$  or  $tx_dw$  pulse along with the command-status or data word to be transmitted. Then the encoder asserts  $tx_busy$  until it transmits this word serially through all the encoder functions and then de-asserts tx busy to accept the next word.

### **Decoder Operation**

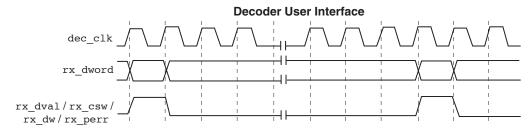

The decoder requires a single clock with a frequency (8 MHz) of 8 times the desired data rate (1 Mbps) for dec\_clk. The decoder is free running and continuously hunting for the synchronization pattern on the serial input. When a valid synchronization pattern is detected, it identifies the boundary of the word and determines it as either a command-status word or a data word. Then the serial bits are passed through shift registers, and a parallel word is presented to the user interface along with the type of word and when it is valid. Also, the word is checked for parity errors.

# **Pin Descriptions**

| Port Name      | Active State | I/O | Signal Description                                     |  |

|----------------|--------------|-----|--------------------------------------------------------|--|

| Decoder        |              |     |                                                        |  |

| dec_clk        | _            | In  | Decoder clock of 8 MHz                                 |  |

| rst_n          | Low          | In  | Asynchronous reset                                     |  |

| rx_data        | _            | In  | Serial data Input                                      |  |

| rx_dword[0:15] | _            | Out | Received output data word to user                      |  |

| rx_dval        | High         | Out | Data valid indication for rx_dword                     |  |

| rx_csw         | High         | Out | Indicates rx_dword has command or status word          |  |

| rx_dw          | High         | Out | Indicates rx_dword has data word                       |  |

| rx_perr        | High         | Out | Indicates parity error in rx_dword                     |  |

| Encoder        |              |     |                                                        |  |

| enc_clk        | _            | In  | Encoder clock of 2 MHz                                 |  |

| rst_n          | Low          | In  | Asynchronous reset                                     |  |

| tx_dword[0:15] | _            | In  | Data word from user for transmission                   |  |

| tx_csw         | High         | In  | Indicates tx_dword has command or status word          |  |

| tx_dw          | High         | In  | Indicates tx_dword has data word                       |  |

| tx_data        | _            | Out | Serial data output                                     |  |

| tx_dval        | High         | Out | Data valid indication for tx_data                      |  |

| tx_busy        | High         | Out | Indicates Encoder is not ready to accept the next word |  |

## **Timing Diagrams**

## **Implementation Results**

The design software used for this implementation is Lattice ispLEVER<sup>®</sup> version 4.2 and the Synplicity Synplify synthesis tool. The device utilization and performance summary for LatticeEC<sup>™</sup> and LatticeXP<sup>™</sup> devices (-4 speed grade) is shown below.

| Device    | Size      | Reported Frequency |  |  |  |

|-----------|-----------|--------------------|--|--|--|

| Decoder   |           | •                  |  |  |  |

| LFEC20E-4 | 53 SLICEs | 8 MHz              |  |  |  |

| LFXP10E-4 | 53 SLICEs | 8 MHz              |  |  |  |

| Encoder   |           |                    |  |  |  |

| LFEC20E-4 | 39 SLICEs | 2 MHz              |  |  |  |

| LFXP10E-4 | 33 SLICEs | 2 MHz              |  |  |  |

### **File List**

The files provided in this LatticeEC reference design package are:

#### **Lattice Semiconductor**

The files provided in this LatticeXP reference design package are:

1./1553\_enc\_dec/docs/1553\_enc\_dec.doc 2./1553\_enc\_dec/docs/readme.txt 3./1553\_enc\_dec/source/decoder\_1553.v 4./1553\_enc\_dec/source/encoder\_1553.v 5./1553\_enc\_dec/par/xp/decoder\_1553.prf 6./1553\_enc\_dec/par/xp/encoder\_1553.prf

7./1553\_enc\_dec/par/xp/encoder\_1553.syn 8./1553\_enc\_dec/par/xp/encoder\_1553.syn

9. /1553\_enc\_dec/simulation/xp/scripts/runsim\_1553.do 10. /1553\_enc\_dec/synthesis/xp/synplify/decoder\_1553.prj 11. /1553\_enc\_dec/synthesis/xp/synplify/encoder\_1553.prj 12. /1553\_enc\_dec/synthesis/xp/synplify/decoder\_1553.sdc 13. /1553\_enc\_dec/synthesis/xp/synplify/encoder\_1553.sdc

14. /1553\_enc\_dec/testbench/test\_1553.v

# **Technical Support Assistance**

Hotline: 1-800-LATTICE (North America)

+1-408-826-6002 (Outside North America)

e-mail: techsupport@latticesemi.com

Internet: www.latticesemi.com

Design document Read me file

Decoder source verilog file Encoder source verilog file

Decoder Constraint file for place and route Encoder Constraint file for place and route Decoder Project file for place and route Encoder Project file for place and route

Scripts for RTL simulation

Decoder Project file for synthesis using Synplify Encoder Project file for synthesis using Synplify Decoder Constraint file for synthesis using Synplify Encoder Constraint file for synthesis using Synplify

Testbench for simulation