# **Avant Versa Board – Customizable HSB Sensor Interfaces**

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                                                      | 3  |

|-------------------------------------------------------------------------------|----|

| Abbreviations in This Document                                                | 8  |

| 1. Introduction                                                               | 9  |

| 1.1. Quick Facts                                                              | 10 |

| 1.1.1. Quick Start Guide                                                      | 10 |

| 1.2. Features                                                                 | 11 |

| 1.3. Naming Conventions                                                       | 11 |

| 1.3.1. Nomenclature                                                           | 11 |

| 1.3.2. Signal Names                                                           | 11 |

| 2. Directory Structure and Files                                              | 12 |

| 3. Functional Description                                                     | 13 |

| 3.1. Customizable MIPI CSI-2 Sensor Interface                                 | 13 |

| 3.1.1. MIPI CSI-2 RX DPHY IP                                                  | 14 |

| 3.1.2. MIPI CSI-2 to AXIS Payload Converter                                   |    |

| 3.2. Hololink IP                                                              | 15 |

| 3.2.1. Overview                                                               | 15 |

| 3.3. Ethernet 10G/25G Support in Avant-X Device                               | 16 |

| 3.3.1. Ethernet 10G Support with 10GBase-T SFP+ Transceiver                   | 16 |

| 3.3.2. Ethernet 25G Support with 25GBase-SR SFP28 Transceiver                 | 17 |

| 3.4. Clocking and Reset Scheme                                                | 17 |

| 4. Customizing the Reference Design                                           | 19 |

| 4.1. Steps for Customizing Reference Design                                   | 19 |

| 4.1.1. IP Generation                                                          |    |

| 4.1.2. HDL Parameter and Define Switch Configuration                          | 22 |

| 4.1.3. Platform Design Constraint Configuration                               |    |

| 4.1.4. Driver Configuration/patches                                           |    |

| 4.1.5. Verifying Reference Design Configuration                               |    |

| 4.2. Customizing Reference Design to Fit into Avant-X Versa Evaluation Board  |    |

| 5. Compiling Reference Design                                                 |    |

| 5.1. Configuring the Reference Design Parameters                              |    |

| 5.2. Assigning a Revision for each Bitstream                                  |    |

| 5.3. Configuring the Lattice Radiant Software to Compile the Reference Design |    |

| 5.4. Generating the Bitstream File                                            |    |

| 6. Implementing the Reference Design on the Avant-X Versa Board               |    |

| 6.1. Requirements                                                             |    |

| 6.1.1. Hardware                                                               |    |

| 6.1.2. Software                                                               |    |

| 6.2. Jetson AGX ORIN Host Setup                                               |    |

| 6.2.1. Setting Up the Jetson AGX ORIN Developer Kit                           |    |

| 6.2.2. Configure the AGX Orin Developer Host Kit                              |    |

| 6.2.3. Building the Holoscan Sensor Bridge Demo Container                     |    |

| 6.2.4. Applying Patch to Support the IMX258 Camera Module                     |    |

| 6.3. Testing the System                                                       |    |

| 6.3.1. Programming the Bit File                                               |    |

| 6.3.2. Camera Video Streaming Test                                            |    |

| 7. Resource Utilization                                                       |    |

| 7.1. Resource Utilization with Ethernet 10G                                   |    |

| 7.2. Resource Utilization with Ethernet 25G                                   |    |

| 8. Debug Methodology                                                          |    |

| 8.1. Powering Up the Evaluation Board                                         |    |

| 8.1.1. Troubleshooting Common Issues                                          |    |

| 8.2. Verifying the Ethernet Connection                                        |    |

| o.e                                                                           |    |

| 8.2.1. Troubleshooting Connection Issues                   | 51 |

|------------------------------------------------------------|----|

| 8.3. Running the Streaming Script (linux_imx258_player.py) | 52 |

| 8.3.1. Preparing the Streaming Script                      |    |

| 8.3.2. Monitoring the Output of the Streaming Script       |    |

| 8.3.3. Troubleshooting Common Errors                       |    |

| Appendix A. Known Issue                                    |    |

| References                                                 |    |

| Technical Support Assistance                               |    |

| Revision History                                           |    |

# **Figures**

| Figure 1.1. Overview of Customizable HSB Sensor Interface RD with NVIDIA ecosystem |    |

|------------------------------------------------------------------------------------|----|

| Figure 2.1. Directory Structure                                                    |    |

| Figure 3.1. Overview of Reference Design Block Diagram                             | 13 |

| Figure 3.2. Overview block diagram of MIPI CSI-2 interface                         |    |

| Figure 3.3. Holoscan Sensor Bridge IP in FPGA                                      |    |

| Figure 3.4. Reset and Clock Domain Block Diagram for Ethernet 10G                  | 17 |

| Figure 3.5. Reset and Clock Domain Block Diagram for Ethernet 25G                  | 18 |

| Figure 4.1. Steps Flow to Customize and Verify the Reference Design                | 19 |

| Figure 4.2. MIPI CSI-2 RX DPHY IP Generation Module                                | 20 |

| Figure 4.3. Ethernet 10Gb (MAC + PHY) IP Generation                                | 21 |

| Figure 4.4. Ethernet 25Gb (MAC + PHY) IP Generation                                | 21 |

| Figure 4.5. Define Switch Setting in HOLOLINK_def.svh File                         | 22 |

| Figure 4.6. LDC File Setting for Ethernet Ports and Pin Allocation                 | 23 |

| Figure 4.7. PDC File Setting for 10G or 25G                                        | 23 |

| Figure 4.8. Screenshot of Lattice Radiant Software Hierarchy File List             | 25 |

| Figure 4.9. Avant-X Versa Evaluation Board Block Diagram                           | 26 |

| Figure 4.10. Required HDL Parameter and DEFINE Switch Configuration                | 27 |

| Figure 4.11. Required LDC Configuration                                            | 27 |

| Figure 4.12. Required PDC Configuration                                            | 28 |

| Figure 4.13. Lattice Radiant Software Hierarchy File                               | 28 |

| Figure 5.1. Revision ID assignment in hsb_1chip_avtx_top.sv                        | 29 |

| Figure 5.2. Revision ID Date Code Representation                                   | 30 |

| Figure 5.3. Lattice Radiant Software                                               | 30 |

| Figure 5.4. Open Project File                                                      | 30 |

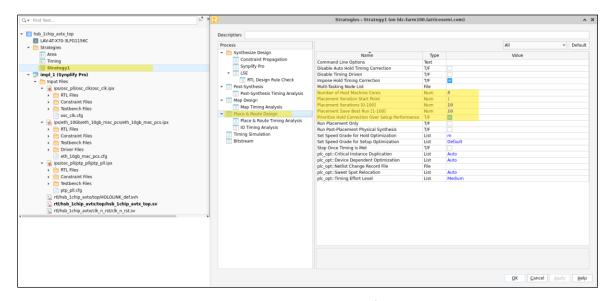

| Figure 5.5. Synthesis Design's Strategy                                            | 31 |

| Figure 5.6. Place and Route Design's Strategy                                      | 31 |

| Figure 5.7. Generate and Export Bitstream File                                     | 32 |

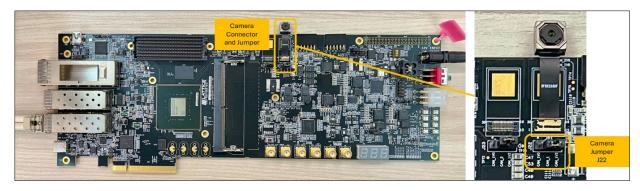

| Figure 6.1. Avant-X Versa Board Camera Connector and Jumper                        | 33 |

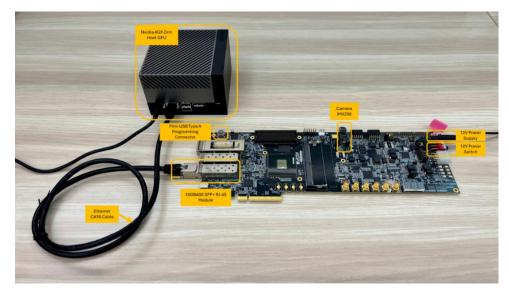

| Figure 6.2. Hardware Setup to support 10G Ethernet                                 | 34 |

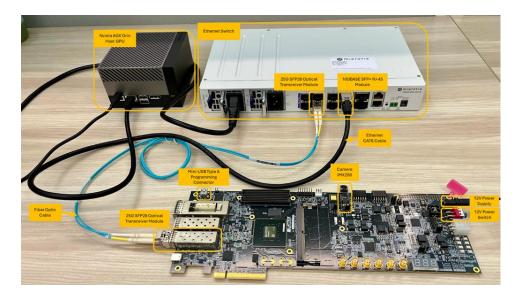

| Figure 6.3. Hardware Setup to support 25G Ethernet                                 | 34 |

| Figure 6.4. Ubuntu Host PC and Jetson AGX Orin Developer Kit Setup                 | 35 |

| Figure 6.5. Recovery and Reset Button                                              | 35 |

| Figure 6.6. Jetson AGX Orin [64GB developer kit version]                           | 36 |

| Figure 6.7. JetPack 6.2.1 (Rev.1)                                                  | 36 |

| Figure 6.8. Terms and Conditions – License Agreement                               | 37 |

| Figure 6.9. Download Operation and OS Image Creation                               | 37 |

| Figure 6.10. SDK Manager                                                           | 38 |

| Figure 6.11. Summary Finalization                                                  | 38 |

| Figure 6.12. MAXN Power Mode                                                       | 40 |

| Figure 6.13. Hardware Setup for Bit File Programming                               | 43 |

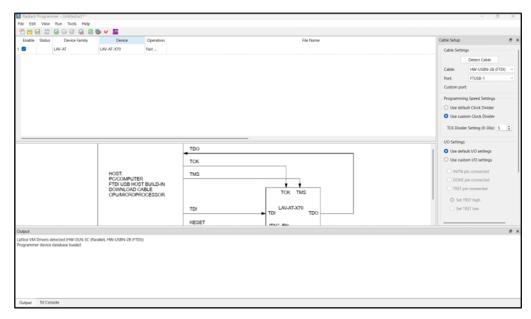

| Figure 6.14. Radiant Programmer Window                                             | 43 |

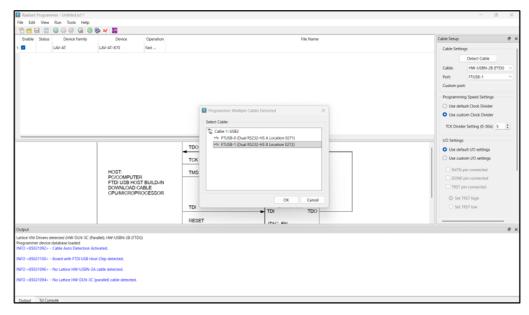

| Figure 6.15. Select Cable Settings                                                 | 44 |

| Figure 6.16. Load Bitstream File                                                   | 44 |

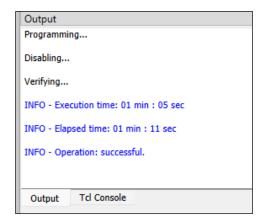

| Figure 6.17. Program Device Toolbar Icon                                           | 45 |

| Figure 6.18. Message on Successful Programming                                     |    |

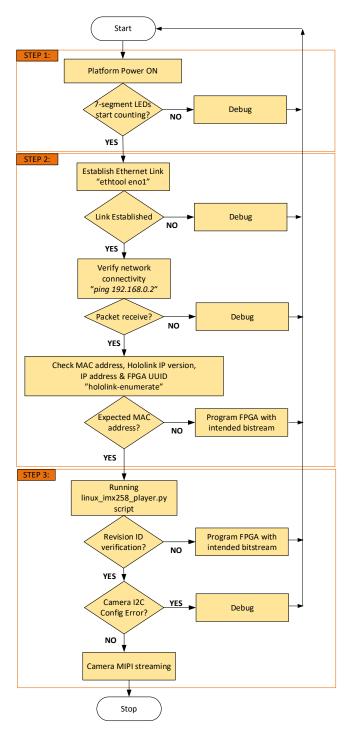

| Figure 8.1. Debug Methodology Flow Chart For Reference Design                      | 48 |

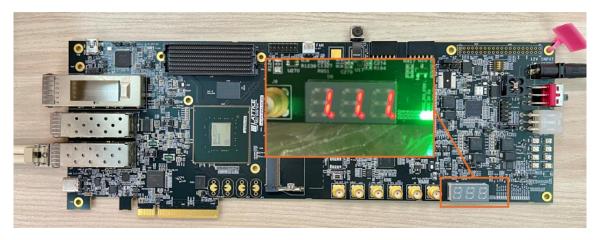

| Figure 8.2. Position of the 7-segment LEDs on Avant-X Versa Evaluation Board       | 49 |

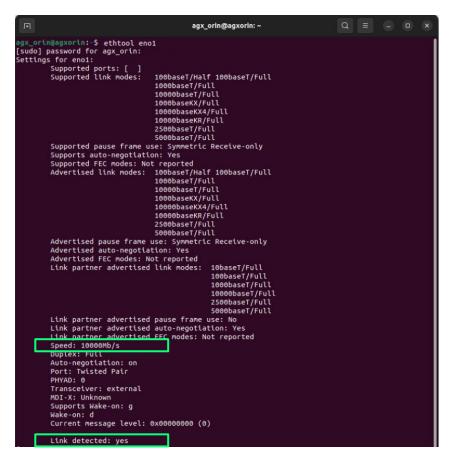

| Figure 8.3. Ethernet Link Establishment Status                                     |    |

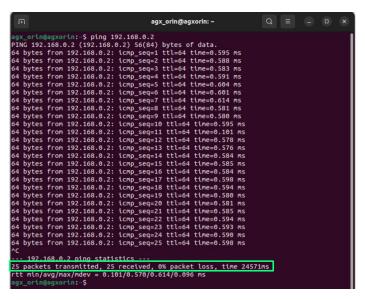

| Figure 8.4. Data Packet Received by Host                                           | 51 |

| Figure 8.5. Sample Output                                                          | 51 |

| Figure 8.6. LAN Light Indication on Host                                           | 52 |

| Figure 8.7. Revision ID Version                                                    | 52 |

Figure 8.8. Camera I2C configuration fail log ......53

## **Tables**

| Table 1.1. Summary of the Reference Design                                                        | 10 |

|---------------------------------------------------------------------------------------------------|----|

| Table 2.1. Folder Structure Description                                                           |    |

| Table 3.1. Clock Domain Distribution for Reference design with Ethernet 10G                       | 18 |

| Table 3.2. Clock Domain Distribution for Reference design with Ethernet 25G                       | 18 |

| Table 3.3. Reset Distribution applicable for both Ethernet 10G and 25G                            | 18 |

| Table 4.1. Reference design's MIPI CSI-2 RX DPHY IP configuration options                         | 19 |

| Table 4.2. PDC Pin Assignment for 2-Dimension Array for MIPI Data Lane                            | 24 |

| Table 4.3. Configuration required for reference design to fit into Avant-X Versa Evaluation Board | 26 |

| Table 5.1. Revision ID's Board ID and FW ID Representation                                        | 29 |

| Table 7.1. Logic Consumption for each instance Available in the Reference Design                  | 46 |

| Table 7.2. Comparison between Reference Design Utilization and LAV-AT-X70 Resources Available     | 46 |

| Table 7.3. Logic Consumption for each Instance Available in the Reference Design                  | 47 |

| Table 7.4. Comparison between Reference Design Utilization and Avant LAV-AT-X70 Resources         |    |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviations | Definition                          |

|---------------|-------------------------------------|

| APB           | Advanced Peripheral Bus             |

| AXI           | Advanced eXtensible Interface       |

| ВООТР         | Bootstrap Protocol                  |

| CDC           | Clock Domain Crossing               |

| CRC           | Cyclic Redundancy Check             |

| DPHY          | Digital Physical Layer              |

| EBR           | Embedded Block RAM                  |

| ECB           | Ethernet Control Bus                |

| FPGA          | Field-Programmable Gate Array       |

| FW            | Firmware                            |

| GUI           | Graphical User Interface            |

| HDL           | Hardware Description Language       |

| HIF           | Host Interface                      |

| HSB           | Holoscan Sensor Bridge              |

| I2C           | Inter-Integrated Circuit            |

| ICMP          | Internet Control Message Protocol   |

| IP            | Intellectual Property (Core)        |

| MAC           | Media Access Control                |

| MIPI          | Mobile Industry Processor Interface |

| MPCS          | Multi-Protocol Communication Stack  |

| NGC           | NVIDIA GPU Cloud                    |

| PCB           | Printed Circuit Board               |

| PCS           | Physical Coding Sublayer            |

| PDC           | Platform Design Constraint          |

| PFU           | Programmable Function Unit          |

| PLL           | Phase-Locked Loop                   |

| PTP           | Precision Time Protocol             |

| SDK           | Software Development Kit            |

| SERDES        | Serializer/Deserializer             |

| SFP           | Small Form-factor Pluggable         |

| SPI           | Serial Peripheral Interface         |

| STA           | Static Timing Analysis              |

| UDP           | User Datagram Protocol              |

| YAML          | YAML Ain't Markup Language          |

## 1. Introduction

This user guide describes the reference design for customizable HSB sensor interfaces, implemented using the Lattice Semiconductor Avant<sup>TM</sup>-X Versa Evaluation Board. The customizable interfaces in this reference design are divided into two categories.

Note: Only a single Ethernet port is used for the Avant-X Versa Evaluation board for current support.

#### Sensor Interface

This reference design targets a MIPI CSI-2 camera sensor. The sensor interface is designed to be flexible and scalable, allowing you to integrate multiple camera sensors based on your requirements. The system supports various configurations to meet diverse imaging needs.

#### Host Interface

The host interface focuses on Ethernet connectivity and supports multiple link speeds to accommodate varying data throughput requirements. This enables seamless communication between the sensor bridge and host systems.

In this reference design, the primary objective is to establish a robust and reliable bridge between the HSB interface and the NVDIA host. Image tuning is not included and involves defining image quality parameters, configuring processing pipelines, and optimizing the Image Signal Processing (ISP). These tasks are highly specific to the camera sensor and require dedicated resources to achieve optimal results.

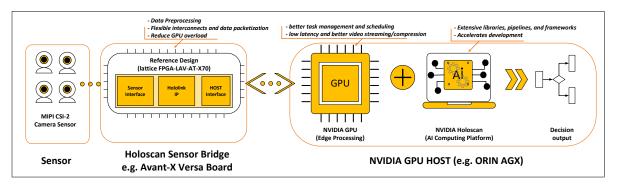

The reference design leverages NVIDIA's Holoscan Sensor Bridge solution and integrates smoothly within the broader NVIDIA ecosystem, enabling high-performance sensor data processing and transmission. An overview of the key components of the NVIDIA Holoscan Sensor Bridge solution and ecosystem is as follows:

#### 1. Sensors

Targets the MIPI CSI-2 camera sensor.

- 2. Holoscan Sensor Bridge (Lattice Avant-X Versa Evaluation Board)

- Lattice Avant-X Versa Evaluation Board functions as the Holoscan Sensor Bridge solution.

- Performs sensor data pre-processing to reduce computational load on the host system.

- The reference design is implemented in the Lattice FPGA targeting LAV-AT-X70 speed grade 3 device.

The key components of the reference design include:

- Sensor Interface

- Supports MIPI CSI-2 camera sensors.

- Highly configurable to accommodate various camera sensors with different MIPI lanes and lane rates.

- Hololink IP

- Acts as a bridge between the sensor interface and the host system.

- Handles data encapsulation, synchronization, and buffering to ensure smooth transmission of highthroughput sensor data.

- Host Interface (Ethernet link)

- Provides a high-speed Ethernet link to the host, supporting 10G or 25G speeds.

- Enables low-latency, and high-bandwidth communication.

- 3. Host (NVIDIA Jetson AGX ORIN Platform)

- Runs the Holoscan SDK to process incoming data.

- Performs real-time AI inference, visualization, and decision-making.

- Streams processed data to the cloud or other edge devices.

Figure 1.1. Overview of Customizable HSB Sensor Interface RD with NVIDIA ecosystem

## 1.1. Quick Facts

Table 1.1. Summary of the Reference Design

| Canaval               | Target Devices             | Avant-X FPGA (LAV-AT-X70-3LFG1156C)                                  |  |

|-----------------------|----------------------------|----------------------------------------------------------------------|--|

| General               | Source code format         | Verilog and SystemVerilog                                            |  |

|                       | Functional simulation      | N/A                                                                  |  |

| Cincolatian           | Timing simulation          | N/A                                                                  |  |

| Simulation            | Testbench                  | N/A                                                                  |  |

|                       | Testbench format           | N/A                                                                  |  |

|                       | Software tool and version  | Lattice Radiant™ software, version 2025.1.0.39.0                     |  |

|                       |                            | CSI-2/DSI D-PHY Rx IP v2.0.0                                         |  |

|                       |                            | • OSC IP v2.1.0                                                      |  |

|                       | IP version (if applicable) | • PLL IP v2.6.1                                                      |  |

|                       | ir version (ii applicable) | • 10G Ethernet IP Core v3.3.1                                        |  |

| Software Requirements |                            | • 25G Ethernet MAC+PHY IP Core v2.2.1                                |  |

|                       |                            | Hololink IP v2507                                                    |  |

|                       | Host Software              | JetPack 6.2.1                                                        |  |

|                       |                            | NVIDIA Holoscan SDK 3.3.0                                            |  |

|                       |                            | NVIDIA Jetson Linux 36.4.4                                           |  |

|                       |                            | • HSB SDK 2.2.0                                                      |  |

|                       | Board                      | Avant-X Versa Evaluation Board                                       |  |

|                       |                            | IMX258 camera module                                                 |  |

|                       |                            | • Ethernet 10GBase-T (Cat 6 RJ-45) SFP+ module (10G Ethernet)        |  |

|                       |                            | Ethernet 25G (Fiber) SFP28 module (25G Ethernet)                     |  |

| Hardware Requirements |                            | • Ethernet Switch (used to downscale 25G to 10G for Jetson AGX Orin) |  |

|                       |                            | Display Monitor                                                      |  |

|                       | Host                       | NVIDIA Jetson AGX Orin Platform                                      |  |

|                       |                            | DisplayPort cable                                                    |  |

|                       | Cable                      | Ethernet Cat 6 cable                                                 |  |

|                       |                            |                                                                      |  |

#### 1.1.1. Quick Start Guide

Refer to Implementing the Reference Design on Avant-X Versa Board for instructions on setting up and streaming video from the IMX258 camera module to the NVIDIA Jetson AGX Orin developer kit over a 10G or 25G Ethernet connection.

#### 1.2. **Features**

Key features of the reference design include:

- Sensor Interface

- Supports one or more camera sensors.

- Designed to be customizable, allowing flexible configuration of the MIPI CSI-2 RX DPHY interface.

- Enables integration of various camera types.

- In testing, the Avant-X Versa Evaluation Board was used with a single MIPI CSI-2 camera.

- Hololink IP

- Acts as a bridge between the sensor interface and the host system.

- Implements Ethernet packetization and supports streaming DMA, control interfaces, and transport abstraction.

- Enables low-latency, high-throughput data transfer from sensors to compute platforms.

- Supports Precision Time Protocol (PTP) per IEEE 1588-2019 specification. PTP synchronizes the Hololink IP's internal time with the host time, enabling the host to act as the Time Transmitter and send PTP packets.

- Host Interface (Ethernet link)

- Supports Ethernet channels with a link speed of 10G or 25G.

- Uses UDP over Ethernet to stream sensor data directly to GPU memory.

- Enables real-time AI inference and visualization with minimal latency.

- In testing, the Avant-X Versa Evaluation Board was used with a single Ethernet port configured for either 10G or 25G.

#### 1.3. **Naming Conventions**

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.3.2. Signal Names

- \_n are active low (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

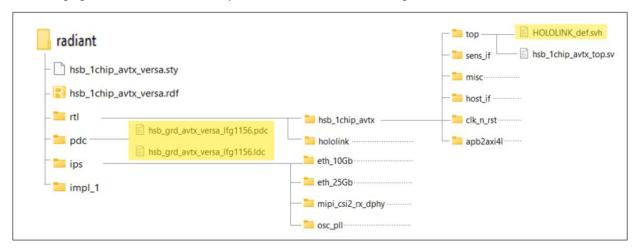

# 2. Directory Structure and Files

The following figure illustrates the directory structure of the reference design.

Figure 2.1. Directory Structure

**Table 2.1. Folder Structure Description**

| Folder/File              | Description                                                                                                                                                   |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| hsb_1chip_avtx_versa.rdf | This file is the Lattice Radiant software project file for the Avant-X reference design.                                                                      |  |

| hsb_1chip_avtx_versa.sty | This file is the strategy file used for the project. Custom settings were applied to improve place-and-route results.                                         |  |

| rtl/hsb_1chip_avtx       | This folder contains HDL code for the sensor interface, host interface, top level design and other components.                                                |  |

| rtl/hololink             | This folder contains the encrypted Hololink IP. The current version is 2507.                                                                                  |  |

| pdc                      | This folder contains the LDC and PDC files.                                                                                                                   |  |

| ips                      | This folder contains IP cores used in the reference design, such as the oscillator, PLLs, MIPI CSI-2 RX DPHY IP, Ethernet 10G IP and Ethernet 25G MAC+PHY IP. |  |

| imp_1                    | This folder contains reports and logs generated during FPGA bitstream compilation.                                                                            |  |

**Note:** The highlighted files in Figure 2.1 (HOLOLINK\_def.svh, hsd\_grd\_avtx\_versa\_lfg1156.ldc and hsb\_grd\_avtx\_versa\_lfg1156.pdc) are important. The user is required to modify these files to create the intended reference design.

## 3. Functional Description

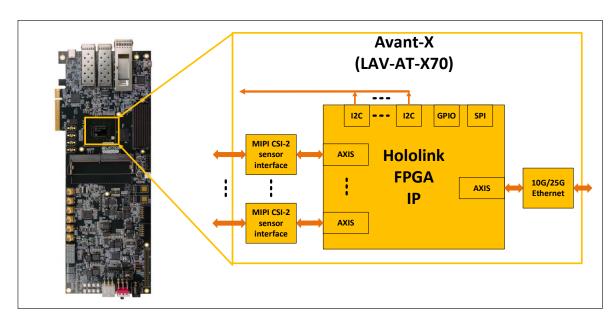

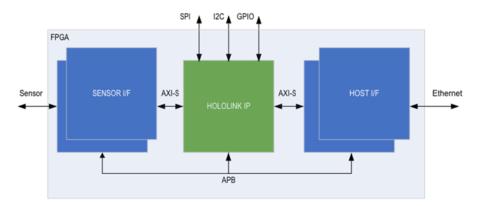

This section describes the architecture of the reference design. The system architecture includes several key subsystems working together seamlessly. The reference design includes three main components: the MIPI CSI-2 sensor interface, Hololink IP, and the Ethernet link as host interface. The reference design is implemented on the Avant-X Versa Evaluation Board. Figure 3.1 shows the overview of the reference design block diagram.

Figure 3.1. Overview of Reference Design Block Diagram

The MIPI CSI-2 sensor interface is highly customizable, supporting a variety of camera configurations based on user platform requirements. Its primary function is to receive raw image data from camera sensors and convert it into AXI-Stream (AXIS) payloads, which are then transmitted to the Hololink IP for further processing. This modularity ensures flexibility in adapting to different camera sensor types and resolutions.

The Hololink IP, provided by NVIDIA, serves as a critical bridge between the sensor interface and the host interface. It offers extensive configurability, including reconfigurable AXIS ports on both the sensor and host sides, and supports control peripherals such as I2C, GPIO, and SPI. This flexibility allows for seamless integration and communication between the sensor subsystem and the host processing platform.

The Ethernet block functions as the host interface. It supports both 10G and 25G link speeds with MAC+PHY IP cores. The Ethernet block connects to the Hololink IP via AXI-Stream ports and uses UDP over Ethernet to stream sensor data directly to GPU memory.

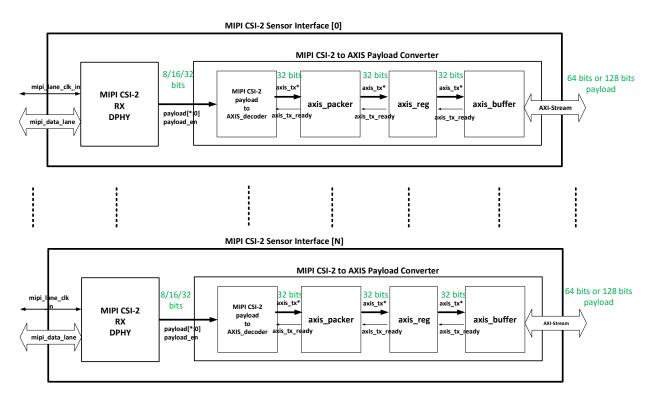

#### 3.1. Customizable MIPI CSI-2 Sensor Interface

The customizable MIPI CSI-2 camera sensor interface has two capabilities:

#### Scalability

Refers to the ability of the MIPI CSI-2 sensor interface to increase or decrease the number of the sensor interfaces based on user platform requirements.

#### Configurability

Refers to the ability to configure each camera sensor interface individually, such as setting different MIPI CSI-2 lane counts and lane rates.

Figure 3.2 shows the block diagram of MIPI CSI-2 interface. It consists of two main components: the MIPI CSI-2 RX DPHY IP and the MIPI CSI-2 to AXIS payload converter.

Figure 3.2. Overview block diagram of MIPI CSI-2 interface

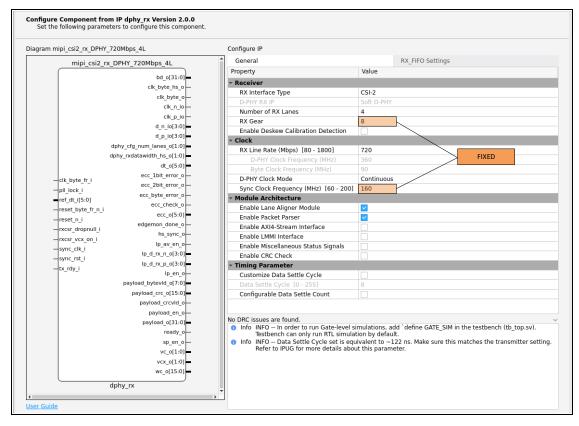

#### 3.1.1. MIPI CSI-2 RX DPHY IP

As the reference design targets the Avant-X device (package type), only the soft MIPI CSI-2/DSI RX DPHY IP is available. The soft MIPI CSI-2 RX DPHY IP is a configurable block. It receives MIPI CSI-2 data streams and converts them into parallel data formats such as 8-bit, 16-bit or 32-bit, based on the number of lanes configured during the IP generation. The IP provides flexibility to configure the MIPI CSI-2 lane rate as according to the camera sensor's requirement. Additionally, it generates an output byte clock based on the data type, which is passed to the AXIS blocks. When the sensor outputs a continuous D-PHY clock, it is recommended to disable RX\_FIFO in the settings and drive the clk\_byte\_fr\_i input clock directly using the clk\_byte\_hs\_o output clock. However, the soft MIPI CSI-2 RX DPHY IP has limitations compared to the hardened version, particularly in performance. These limitations may vary depending on the FPGA device family and package type used. For more detailed specifications and configuration guidelines, refer to the CSI-2/DSI D-PHY Receiver IP Core - User Guide (FPGA-IPUG-02081).

#### 3.1.2. MIPI CSI-2 to AXIS Payload Converter

The MIPI CSI-2 to AXIS Payload Converter module bridges the MIPI CSI-2 protocol and the AXI4-Stream (AXIS) interface. It extracts image data packets from the CSI-2 stream and reformats them into AXIS-compatible payloads for downstream processing.

This converter handles:

- Parsing of CSI-2 protocols elements (such as, long packets, short packets).

- Extracting payload from CSI-2 long packets.

- AXIS framing, including valid signals and handshake logic.

- Detecting errors in packet integrity and protocol compliance.

It enables seamless integration of camera sensor data into FPGA-based image processing pipelines using standard AXI4-Stream interfaces.

**Note:** Depending on the Hololink IP version, some features listed above may not be used. For example, in Hololink IP version 2507, parsing of CSI-2 protocols elements (such as, long packets, short packets) and detecting errors in packet integrity and protocol compliance are not supported.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

#### 3.1.2.1. MIPI CSI-2 Payload to AXIS Decoder Module

This module extracts image data packets from the CSI-2 stream and converts them into AXIS-compatible payloads. It supports CSI-2 stream output in parallel RAW10 formats of 8-bit, 16-bit, or 32-bit, as provided by the MIPI CSI-2 RX D-PHY IP. AXIS-compatible payloads are data packets formatted according to the AXI4-Stream (AXIS) protocol.

- 1. Structured data words: Payloads are aligned into fixed-width data words.

- TDATA[31:0]: Carries the payload of the MIPI CSI-2 RAW10

- 2. Control signals: Each payload includes AXIS control signals:

- TVALID: Indicates valid data.

- TREADY: Handshake signal from the receiver.

- TLAST: Marks the end of a frame or packet.

- TKEEP[3:0]: Specifies which bytes in the data word are valid.

- TUSER[1:0] Typically used for user-defined metadata.

- tuser[0] is asserted during cycles containing embedded data (MIPI Data Type = 0x12)

- tuser[1] is asserted on the final clock cycle of a long packet, indicating the line end signal.

#### 3.1.2.2. AXIS Packer Module

A key feature of this module is its handling of the TKEEP signal, which indicates the validity of individual bytes within each data word. The AXIS Packer filters out invalid TKEEP bits, ensuring that only valid image data is included in the output stream. This maintains data integrity and prevents downstream modules from processing corrupt or incomplete payloads.

#### 3.1.2.3. AXIS REG Module

The AXIS REG module acts as a simple register stage within the AXIS data path. Its primary function is to shift and hold one cycle of AXIS data, helping to manage timing, pipeline depth, and synchronization between modules.

#### 3.1.2.4. AXIS Buffer Module

The AXIS Buffer Module receives AXIS data from the AXIS REG module and passes it through a dual-clock FIFO (DC\_FIFO) to facilitate clock domain crossing (CDC). This ensures reliable data transfer between modules operating in different clock domains.

Key functions include:

- Data buffering: Temporarily stores AXIS data and control signals to manage timing differences.

- Clock domain crossing: Uses DC FIFO to safely transfer data between asynchronous clock domains.

- Flow control: Maintains AXIS protocol integrity using TVALID, TREADY, and TLAST signals across domains.

This module is essential in systems where the CSI-2 receiver and downstream AXIS processing blocks operate on separate clocks, ensuring smooth and error-free data streaming.

#### 3.2. Hololink IP

#### 3.2.1. Overview

A detail explanation on the Nvidia Hololink IP is provided in the NVIDIA documentation webpage, Holoscan Sensor Bridge v2.2.0 - NVIDIA Docs. You are encouraged to review the document for further understanding. This section provides only an overview of the IP.

The NVIDIA Holoscan Sensor Bridge FPGA IP works with the Holoscan software to provide a sensor-agnostic platform that transfers data from various sensors to an Ethernet-connected host.

The Holoscan Sensor Bridge FPGA IP, comprises three main components: the Sensor Interface IP, the Hololink IP, and the Host Interface IP. Figure 3.3 illustrates the block diagram of the Holoscan Sensor Bridge FPGA IP. The Sensor Interface and Host (Ethernet) Interface blocks are implemented using FPGA vendor-specific logic. In this reference design, Lattice Semiconductor is responsible for the integration and maintaining the IP for both the Sensor Interface and Host Interface components.

Figure 3.3. Holoscan Sensor Bridge IP in FPGA

The Holoscan Sensor Bridge FPGA IP streamlines FPGA development, offering scalability and configurability to support a wide range of sensor-to-host applications.

Key functions of the Holoscan Sensor Bridge IP include:

- Encapsulation of sensor data: Converts AXI-Stream sensor data into Ethernet UDP AXI-Stream format for host-side processing.

- Network protocol support: Implements BOOTP, ICMP, and NVIDIA-defined Ethernet Control Bus (ECB) protocols.

- Event and control packet transmission: Sends enumeration and control event packets based on predefined conditions.

- Peripheral interface control: Manages SPI, I2C, and GPIO interfaces to configure sensors and other onboard components.

## 3.3. Ethernet 10G/25G Support in Avant-X Device

The Avant-X device supports high-speed Ethernet connectivity via integrated IP cores and external transceiver modules. This section outlines the supported configurations for both 10G and 25G Ethernet, including key components, integration details, and functional descriptions.

#### 3.3.1. Ethernet 10G Support with 10GBase-T SFP+ Transceiver

The Avant-X device supports 10G Ethernet using SFP+ transceivers, enabling high-speed data communication for bandwidth-intensive applications. The solution combines multiple IP cores and hardware components.

**Key Components:**

#### MAC IP Core

Manages Ethernet frame-level operations, including encapsulation, CRC generation, and flow control. Interfaces with system logic via AXI or Avalon, depending on the FPGA architecture.

#### • PCS IP Core (Physical Coding Sublayer)

Handles low-level physical-layer functions and interfaces directly with the SFP+ module.

#### Features:

- Encoding and Decoding: Supports 8b/10b or 64b/66b schemes.

- Scrambling and Descrambling: Maintains signal integrity.

- Clock Data Recovery (CDR): Aligns incoming data with system clock.

- Link synchronization: Establishes and maintains stable link.

- Error handling: Includes optional Forward Error Correction (FEC) for enhanced reliability.

#### • SFP+ Transceiver Module

A compact, hot-swappable module used for 10G connections.

#### Features:

- Hot-swappable: Enables module replacement without shutting down the system.

- Media support: Compatible with copper and fiber (such as SR for short range, LR for long range).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-RD-02329-1.0

- Diagnostics: supports real-time monitoring of temperature, power, and signal quality.

- Transmission range: Varies from a few meters (copper) to tens of kilometers (fiber).

The MAC and PCS IP cores work together to prepare and transmit Ethernet frames through the SFP+ module. This setup ensures high-speed, low-latency communication for advanced networking applications.

#### 3.3.2. Ethernet 25G Support with 25GBase-SR SFP28 Transceiver

The Avant-X device supports 25G Ethernet using 25GBASE-SR SFP28 transceivers. This setup uses the Lattice 25G Ethernet MAC+PHY IP core, providing high-speed 25Gbps connectivity. The integrated MAC and PHY communicate through a 25-Gigabit Media-Independent Interface (25GMII), enabling seamless data transmission and reception between the host system and Ethernet networks in 25GBASE-R applications.

#### **Key Components**

#### MAC IP Core

Manages Ethernet frame processing, enforces media-access rules, supports flow control (pause frames, PFC), CRC/FCS checks, and collects statistics. Operates on a 128-bit data path at 195.3125 MHz with AXI4-Stream TX/RX interfaces.

#### • PHY IP Core

Handles PCS (64b/66b encoding) and PMA for the serial interface, with lane merging, loopback modes, and AXI4-Lite management.

#### • 25GBase-SR SFP28 Transceiver Module

A compact, hot-swappable module used for 25GbE connections.

#### Features:

- Hot-swappable: Enables module replacement without shutting down the system.

- Media support: Compatible with fiber (such as SR for short range, LR for long range).

- Diagnostics: Supports real-time monitoring of temperature, power, and signal quality.

The 25G Ethernet MAC+PHY IP core integrates with the SFP28 module to process and transmit Ethernet frames, providing high-speed, low-latency 25Gbps communication for advanced networking applications.

## 3.4. Clocking and Reset Scheme

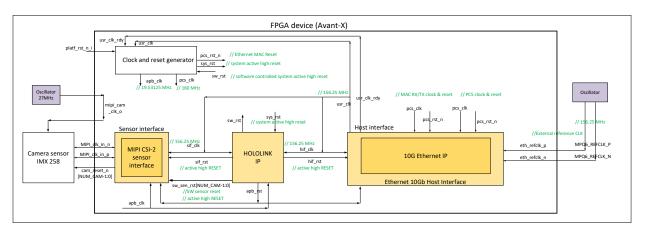

Figure 3.4. Reset and Clock Domain Block Diagram for Ethernet 10G

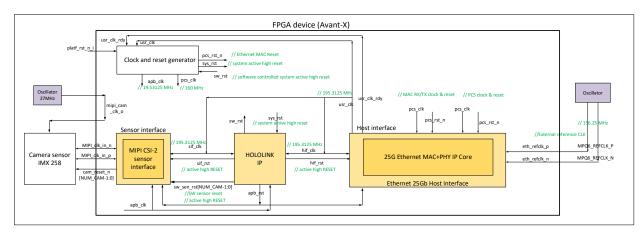

Figure 3.5. Reset and Clock Domain Block Diagram for Ethernet 25G

The following table lists the clock frequencies and their distribution.

Table 3.1. Clock Domain Distribution for Reference design with Ethernet 10G

| Clocks  | Frequency (MHz) | Description                                                                                                    |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------|

| usr_clk | 156.25          | Ethernet IP TX output clock used as a reference clock for the PLL to generate system clocks (such as apb_clk). |

| pcs_clk | 160             | PCS calibration clock.                                                                                         |

| hif_clk | 156.25          | Directly assigned from usr_clk and is used for host AXIS interface.                                            |

| sif_clk | 156.25          | Directly assigned from hif_clk and is used as the AXIS clock for the sensor interface.                         |

| apb_clk | 19.5313         | APB bus clock.                                                                                                 |

Table 3.2. Clock Domain Distribution for Reference design with Ethernet 25G

| Clocks  | Frequency (MHz) | Description                                                                                                    |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------|

| usr_clk | 195.3125        | Ethernet IP TX output clock used as a reference clock for the PLL to generate system clocks (such as apb_clk). |

| pcs_clk | 160             | PCS calibration clock.                                                                                         |

| hif_clk | 195.3125        | Directly assigned from usr_clk and is used for host AXIS interface.                                            |

| sif_clk | 195.3125        | Directly assigned from hif_clk and is used as the AXIS clock for sensor interface.                             |

| apb_clk | 19.5313         | APB bus clock.                                                                                                 |

Table 3.3. Reset Distribution applicable for both Ethernet 10G and 25G

| Clocks                  | Description                                                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sw_sen_rst[NUM_CAM-1:0] | Register-controlled sensor reset. The reset signal width increases based on the number of assigned cameras. Details are discussed in the Customizing the Reference Design section. |

| sw_sys_rst              | Register-controlled system reset. Used to reset system-level logic. Also triggers reset for hif_rst, apb_rst, and sif_rst.                                                         |

| apb_rst                 | Reset APB logic                                                                                                                                                                    |

| hif_rst                 | Reset Host logic                                                                                                                                                                   |

| sif_rst                 | Reset Sensor logic                                                                                                                                                                 |

## 4. Customizing the Reference Design

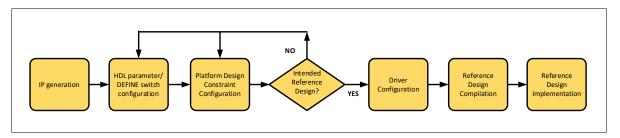

## 4.1. Steps for Customizing Reference Design

This section provides a detailed walkthrough of the steps required to configure the reference design and to verify the customized reference design. Figure 4.1 illustrates the steps involved to enable customization and support for various customer-specific configurations. Detailed explanation is provided in this section. However, details on reference design compilation and implementation are covered separately in Compiling the Reference Design section and Implementing the Reference Design on Avant-X Versa Board section.

Figure 4.1. Steps Flow to Customize and Verify the Reference Design

#### 4.1.1. IP Generation

#### 4.1.1.1. MIPI CSI-2 RX DPHY IP generation

Each MIPI CSI-2 camera sensor interface requires a corresponding MIPI CSI-2 RX DPHY IP block. This IP must be generated based on the specifications of the camera sensor being used. The key parameters to configure includes:

- Number of data lanes

- MIPI lane rate

- Gear Ratio

- MIPI synchronizer clock frequency

These parameters must be correctly set before generating the IP to ensure compatibility with the camera sensor. The gear ratio for the Avant-X family device is fixed at 8, and the MIPI synchronizer clock frequency in the reference design is set to 160 MHz. The reference design also provides preconfigured MIPI CSI-2 RX DPHY IPs for users to choose from. The table shows the available IP configuration option that the user can select. The IP is selected based on user settings, which will be explained in the HDL Parameter and Define Switch Configuration section.

Table 4.1. Reference design's MIPI CSI-2 RX DPHY IP configuration options

| MIPI Lane Rate (Mbps) | MIPI Lane Number | MIPI RX DPHY IP name              |

|-----------------------|------------------|-----------------------------------|

|                       | 1 lane           | mipi_csi2_rx_DPHY_720Mbps_1L.ipx  |

| 720                   | 2 lanes          | mipi_csi2_rx_DPHY_720Mbps_2L.ipx  |

|                       | 4 lanes          | mipi_csi2_rx_DPHY_720Mbps_4L.ipx  |

| 000                   | 2 lanes          | mipi_csi2_rx_DPHY_960Mbps_2L.ipx  |

| 960                   | 4 lanes          | mipi_csi2_rx_DPHY_960Mbps_4L.ipx  |

| 1440                  | 4 lanes          | mipi_csi2_rx_DPHY_1440Mbps_4L.ipx |

| 1500                  | 4 lanes          | mipi_csi2_rx_DPHY_1500Mbps_4L.ipx |

Figure 4.2. MIPI CSI-2 RX DPHY IP Generation Module

#### 4.1.1.2. Hololink IP

Hololink IP is owned by NVIDIA, and NVIDIA updates the latest Hololink IP source code on GitHub at the following link, GitHub - nvidia-holoscan/holoscan-sensor-bridge at 2.2.0-branch. The IP is encrypted. Currently, the reference design integrates the latest available Hololink IP, which is version 2507.

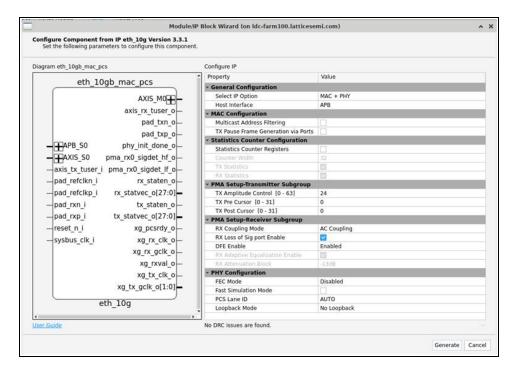

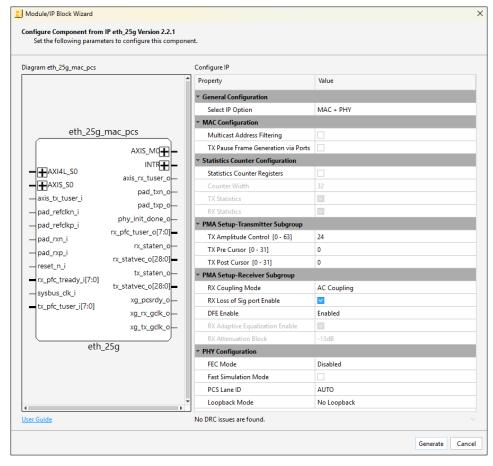

#### 4.1.1.3. Ethernet IP Generation

Specific Ethernet IPs are required to support 10G or 25G link speeds in the Avant-X FPGA device. To support Ethernet 10G link speed, the 10Gb Ethernet IP Core v3.3.1 is used. To support Ethernet 25G link speed, the 25Gb Ethernet MAC+PHY IP Core v2.2.1 is used. The 10G and 25G Ethernet Lane ID is set to AUTO for the Avant-X Versa Evaluation Board before generating the IP. Figure 4.3 shows the 10Gb Ethernet IP generation, while Figure 4.4 shows the Ethernet 25Gb MAC+PHY IP generation.

Figure 4.3. Ethernet 10Gb (MAC + PHY) IP Generation

Figure 4.4. Ethernet 25Gb (MAC + PHY) IP Generation

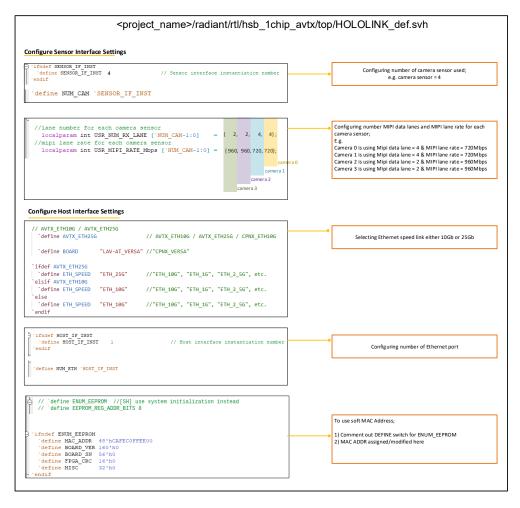

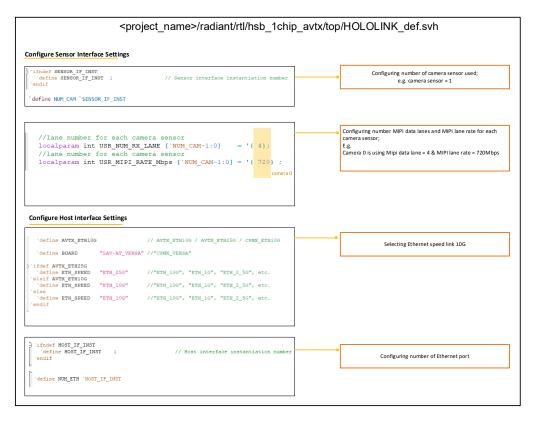

#### 4.1.2. HDL Parameter and Define Switch Configuration

Configure the HDL parameters and Define switches to reflect the desired hardware setup. These configurations modify the HDL design prior to compilation and affect the following aspects:

- Number of camera sensor interfaces

- Number of lanes per camera sensor

- Number of camera reset outputs

- I2C control peripherals for each camera sensor

- AXI-Stream ports connecting the sensor interface to the Hololink IP

- AXI-Stream ports connecting the Hololink IP to the host interface (Ethernet link)

- Ethernet link speed: 10G or 25G

- Number of Ethernet links used as host interface

- Ethernet MAC IP address

Configurations such as cameras reset outputs, I2C camera controls, and AXI-Stream ports for the sensor/host interface are automatically configured based on the number of camera sensors and assigned Ethernet 10G or 25G links. Figure 4.5 shows the DEFINE switches that need to be changed in HOLOLINK\_def.svh file. These settings must be carefully configured to ensure the HDL design reflects the intended hardware setup and supports the required camera sensor interfaces.

Figure 4.5. Define Switch Setting in HOLOLINK\_def.svh File

-RD-02329-1.0

**Note:** Figure 4.5 screenshot shows an example setting of four camera sensors. If more or less cameras are required for the intended reference design, the array size for USR\_NUM\_RX\_LANE[`NUM\_CAM-1:0] and USR\_MIPI\_RATE\_Mbps[`NUM\_CAM-1:0] will change. Therefore, the data assigned to it are trimmed or added based on the intended camera number usage.

#### 4.1.3. Platform Design Constraint Configuration

Once the HDL design configuration is finalized, platform design constraints in both the LDC and PDC files are updated. An LDC and PDC template files are provided with this reference design and are located at:

```

ct_name>/radiant/pdc/hsb_grd_avtx_versa_lfg1156.ldc

ct_name>/radiant/pdc/hsb_grd_avtx_versa_lfg1156.pdc

```

```

set ETH_NUM 1

2

4

ldc_set_location -site {MPQ6_REFCLKP} [get_ports eth_refclk_p]

ldc_set_location -site {MPQ6_REFCLKN} [get_ports eth_refclk_n]

\label{location} \mbox{ldc\_set\_location -site $\{MPQ6\_RX0N\} [get\_ports $\{eth\_rxd\_n[0]\}]$}

6

ldc set location -site {MPQ6 RX0P} [get ports {eth rxd p[0]}]

ldc_set_location -site {MPQ6_TX0N} [get_ports {eth_txd_n[0]}]

8

ldc_set_location -site {MPQ6_TX0P} [get_ports {eth_txd_p[0]}]

10

if {($ETH_NUM == 2) } {

ldc_set_location -site {MPQ6_RX1N} [get_ports {eth_rxd_n[1]}]

11

12

ldc_set_location -site {MPQ6_RX1P} [get_ports {eth_rxd_p[1]}]

13

ldc_set_location -site {MPQ6_TX1N} [get_ports {eth_txd_n[1]}]

14

ldc_set_location -site {MPQ6_TX1P} [get_ports {eth_txd_p[1]}]

15

16

```

Figure 4.6. LDC File Setting for Ethernet Ports and Pin Allocation

Figure 4.6 shows the LDC file settings for the Ethernet port configuration and pin allocation. Please note that the Avant-X Versa board supports a maximum of two SFP+ connectors.

Figure 4.7. PDC File Setting for 10G or 25G

Figure 4.7 shows the PDC file settings for the number of camera sensors, data lane, and lane rates used for each camera sensor, as well as the number of Ethernet ports and link speed, configurable to 10G or 25G. If fewer cameras are used, the lane numbers for undefined cameras will be ignored. For example, if the number of cameras is 1, the lane number values set for cameras 2, 3, and 4 will be ignored.

The steps to update the platform design constraints include:

- Pin assignment at the top level of the HDL design

- Defining timing constraints

Proper configuration of these constraints is essential to produce intended reference design. However, the PDC file template provided with the reference design allows users to choose 1, 2, or 4 camera sensors. If more camera sensors are required, users must manually add the desired settings.

#### 4.1.3.1. Pin Assignment for MIPI CSI-2 Camera Sensor Interface

In this section, the focus is solely on the MIPI CSI-2 camera sensor interface. The pins that need to be updated at the HDL top level are the camera MIPI clock lane, camera MIPI data lane, camera sensor reset, and camera I2C control. Special attention is required for the MIPI data lane assignment due to the use of two-dimensional array coding method at the HDL top-level design.

MIPI clock and data lanes are differential signals, and the pins assigned to them must be high-speed differential I/O types. For Avant-X FPGAs, the typical I/O type used for MIPI clock and data lanes is LVDS (Low Voltage Differential Signaling) I/O pairs. Special handling is required when setting pin assignments for MIPI data lanes, as the reference design's top level uses a two-dimensional array coding method. This affects how the assignments are defined and mapped in PDC file. Table 4.2 illustrates the correct pin assignment approach under these conditions in the PDC file.

Table 4.2. PDC Pin Assignment for 2-Dimension Array for MIPI Data Lane

| Camera   | System Verilog pin name | PDC mapped pin name |

|----------|-------------------------|---------------------|

| Camera 0 | mipi_cam_data_p[0][0]   | mipi_cam_data_p[0]  |

|          | mipi_cam_data_n[0][0]   | mipi_cam_data_n[0]  |

|          | mipi_cam_data_p[0][1]   | mipi_cam_data_p[1]  |

|          | mipi_cam_data_n[0][1]   | mipi_cam_data_n[1]  |

|          | mipi_cam_data_p[0][2]   | mipi_cam_data_p[2]  |

|          | mipi_cam_data_p[0][2]   | mipi_cam_data_n[2]  |

|          | mipi_cam_data_p[0][3]   | mipi_cam_data_p[3]  |

|          | mipi_cam_data_p[0][3]   | mipi_cam_data_n[3]  |

|          | mipi_cam_data_p[1][0]   | mipi_cam_data_p[4]  |

|          | mipi_cam_data_n[1][0]   | mipi_cam_data_n[4]  |

|          | mipi_cam_data_p[1][1]   | mipi_cam_data_p[5]  |

| Comoro 1 | mipi_cam_data_n[1][1]   | mipi_cam_data_n[5]  |

| Camera 1 | mipi_cam_data_p[1][2]   | mipi_cam_data_p[6]  |

|          | mipi_cam_data_p[1][2]   | mipi_cam_data_n[6]  |

|          | mipi_cam_data_p[1][3]   | mipi_cam_data_p[7]  |

|          | mipi_cam_data_p[1][3]   | mipi_cam_data_n[7]  |

|          | mipi_cam_data_p[2][0]   | mipi_cam_data_p[8]  |

|          | mipi_cam_data_n[2][0]   | mipi_cam_data_n[8]  |

|          | mipi_cam_data_p[2][1]   | mipi_cam_data_p[9]  |

| Camera 2 | mipi_cam_data_n[2][1]   | mipi_cam_data_n[9]  |

|          | mipi_cam_data_p[2][2]   | mipi_cam_data_p[10] |

|          | mipi_cam_data_p[2][2]   | mipi_cam_data_n[10] |

|          | mipi_cam_data_p[2][3]   | mipi_cam_data_p[11] |

|          | mipi_cam_data_p[2][3]   | mipi_cam_data_n[11] |

| Camera   | System Verilog pin name | PDC mapped pin name |  |

|----------|-------------------------|---------------------|--|

| Camera 3 | mipi_cam_data_p[3][0]   | mipi_cam_data_p[12] |  |

|          | mipi_cam_data_n[3][0]   | mipi_cam_data_n[12] |  |

|          | mipi_cam_data_p[3][1]   | mipi_cam_data_p[13] |  |

|          | mipi_cam_data_n[3][1]   | mipi_cam_data_n[13] |  |

|          | mipi_cam_data_p[3][2]   | mipi_cam_data_p[14] |  |

|          | mipi_cam_data_p[3][2]   | mipi_cam_data_n[14] |  |

|          | mipi_cam_data_p[3][3]   | mipi_cam_data_p[15] |  |

|          | mipi_cam_data_p[2][3]   | mipi_cam_data_n[15] |  |

#### 4.1.3.2. Timing constraint for MIPI CSI-2 Camera Sensor Interface

Using the PDC template from reference design, you can configure the timing constraint for the MIPI CSI-2 camera sensor interface by assigning the MIPI lane rate, as shown in Figure 4.7. In the PDC file, this value will be used to assign the timing constraint required for the MIPI clock input.

#### 4.1.4. Driver Configuration/patches

Driver configuration is modified based on the target reference design. For example, each camera sensor has its own I2C control signals, so the driver must be modified to correctly identify and communicate with the target sensor. This ensures successful initialization and operation of the camera.

Driver configuration support for IMX258 is specifically covered in the Applying Patch to Support the IMX258 Camera Module section. To enable the driver configuration support, follow the steps from the Configuring the AGX Orin Developer Host Kit section through the Applying Patch to Support the IMX258 Camera Module section.

## 4.1.5. Verifying Reference Design Configuration

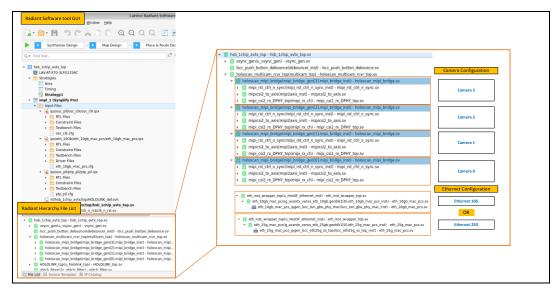

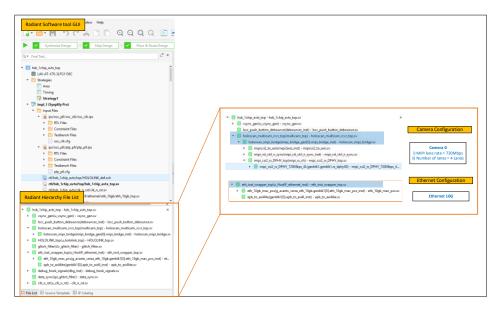

You are expected to verify whether the configured setting delivers the target reference design. There are two steps required for you to verify: first, check the Lattice Radiant software's hierarchy list to confirm the selected camera number and camera configuration. Secondly, you need to check the clock summary details in the timing analysis report to ensure the assigned timing constraint matches the target configuration. Figure 4.8 shows a screenshot of the reference design implemented on the Avant-X Versa Evaluation Board. If the verified design is not the target reference design, then you are required to review the HDL parameters, DEFINE switch configuration, and PDC configuration, following the configuration flow shown in Figure 4.1.

Figure 4.8. Screenshot of Lattice Radiant Software Hierarchy File List

#### 4.2. **Customizing Reference Design to Fit into Avant-X Versa Evaluation Board**

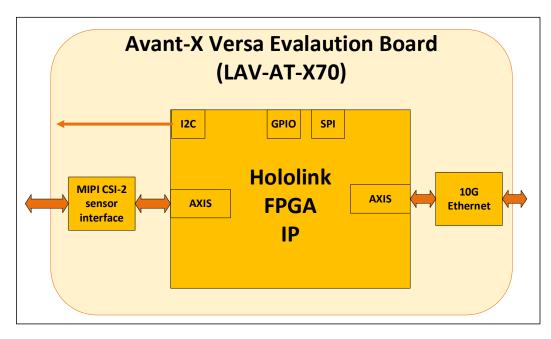

Figure 4.9 shows an overview of the configured Avant-X Versa Evaluation board block diagram.

Figure 4.9. Avant-X Versa Evaluation Board Block Diagram

Table 4.3 shows the configuration required for the reference design to fit onto the Avant-X Versa Evaluation Board.

Table 4.3. Configuration required for reference design to fit into Avant-X Versa Evaluation Board

|                         | Features                   | Configuration |

|-------------------------|----------------------------|---------------|

| Camera sensor interface | Number of camera sensors   | 1             |

|                         | Camera 0: MIPI lane number | 4             |

|                         | Camera 0: MIPI lane rate   | 720 Mbps      |

| Ethernet Link           | Number of Ethernet port    | 1             |

|                         | Ethernet link speed        | 10G           |

To customize the reference design, follow the steps below.

Note: This reference design is already integrated with a preset MIPI RX DPHY IP configuration, latest Hololink IP version 2507 and Ethernet IPs.

1. Configure HDL Parameter and DEFINE Switch.

The reference design need to be configured by changing the settings of the HDL parameter and DEFINE switch to meet the Avant-X Versa board requirement using this file.

project name>/radiant/rtl/hsb 1chip antx/top/HOLOLINK def.svh

26

Figure 4.10. Required HDL Parameter and DEFINE Switch Configuration

2. Review the PDC configuration file.

Figure 4.11 shows the screenshot of the required LDC configuration. Figure 4.12 shows a screenshot of the required PDC configuration.

```

cproject_name>/radiant/pdc/hsb_grd_avtx_versa_lfg1156.ldc

ct_name>/radiant/pdc/hsb_grd_avtx_versa_lfg1156.pdc

```

```

set ETH NUM 1

Number of Ethernet = 1

2

4

ldc_set_location -site {MPQ6_REFCLKP} [get_ports eth_refclk_p]

ldc_set_location -site {MPQ6_REFCLKN} [get_ports eth_refclk_n]

ldc_set_location -site {MPQ6_RX0N} [get_ports {eth_rxd_n[0]}]

\label{location} \mbox{ldc\_set\_location -site } \{\mbox{MPQ6\_RX0P}\} \ [\mbox{get\_ports } \{\mbox{eth\_rxd\_p[0]}\}]

8

ldc_set_location -site {MPQ6_TX0N} [get_ports {eth_txd_n[0]}]

ldc_set_location -site {MPQ6_TX0P} [get_ports {eth_txd_p[0]}]

10

if {($ETH_NUM == 2) } {

ldc_set_location -site {MPQ6_RX1N} [get_ports {eth_rxd_n[1]}]

11

12

ldc_set_location -site {MPQ6_RX1P} [get_ports {eth_rxd_p[1]}]

ldc_set_location -site {MPQ6_TX1N} [get_ports {eth_txd_n[1]}]

13

14

ldc_set_location -site {MPQ6_TX1P} [get_ports {eth_txd_p[1]}]

15

}

16

```

Figure 4.11. Required LDC Configuration

Figure 4.12. Required PDC Configuration

- Configure the driver: For details on how to configure the driver, refer to the Applying Patch to Support the IMX258

Camera Module section. To enable driver configuration support, follow the steps from the Configuring the AGX

Orin Developer Host Kit section through the Applying Patch to Support the IMX258 Camera Module section.

- 4. Verify the reference design configuration: Review the Lattice Radiant software hierarchy file list and the clock summary from the place-and-route timing report. Figure 4.13 shows the reference design in the Lattice Radiant software hierarchy file list. The reference design is now ready for compilation and implementation.

Figure 4.13. Lattice Radiant Software Hierarchy File

## 5. Compiling Reference Design

This section describes how to compile the reference design using Lattice Radiant software. For more details on the Lattice Radiant software, please refer to the Lattice Radiant Software User Guide.

## 5.1. Configuring the Reference Design Parameters

To configure the reference design parameters, refer to the details in the Customizing the Reference Design section.

## 5.2. Assigning a Revision for each Bitstream

To assign a revision ID for each bitstream modify the reference design HDL top-level file, *hsb\_1chip\_avtx\_top.sv* as shown in Figure 5.1.

```

module hsb_1chip_avtx_top

#(

'ifdef AVTX_ETH25G

parameter BUILD_REV = 48'h04_02_3364_0000

'elsif AVTX_ETH10G

parameter BUILD_REV = 48'h03_01_3364_0000

'else

parameter BUILD_REV = 48'h00_00_00000

'endif

)(

```

Figure 5.1. Revision ID assignment in hsb\_1chip\_avtx\_top.sv

Table 5.1 shows the board ID and firmware ID in hexadecimal format.

Table 5.1. Revision ID's Board ID and FW ID Representation

| Reference design with Avant-X Device | Reference Design with 10G<br>Ethernet | Reference Design with 25G<br>Ethernet | Remarks                                                                                     |

|--------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------|

| Board ID (in Hexadecimal)            | 03                                    | 04                                    | Board ID used for Avant-X<br>device with ethernet link<br>10G or 25G                        |

| FW ID (in Hexadecimal)               | 01                                    | 02                                    | FW ID used for FW upgrade that has code change (design integration, bug fix or new feature) |

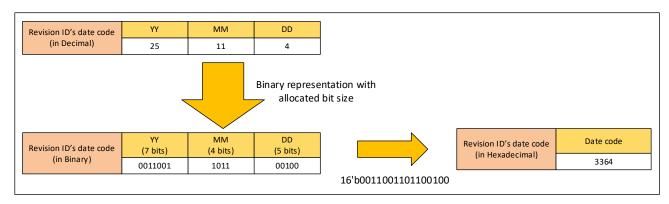

The date code refers to the date used to generate the release bitstream. The date code is represented differently, as shown in Figure 5.2. The example in the figure illustrates the conversion of the date 4<sup>th</sup> November 2025 from decimal to binary to hexadecimal formats.

Figure 5.2. Revision ID Date Code Representation

## 5.3. Configuring the Lattice Radiant Software to Compile the Reference Design

1. Launch the Lattice Radiant software, as shown in Figure 5.3. Note that the project is compiled using the Lattice Radiant software version 2025.1.0.39.0

Figure 5.3. Lattice Radiant Software

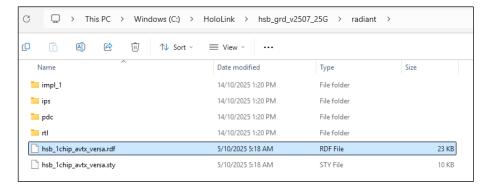

2. Click **File** > **Open Project**. From the project database, open the Lattice Radiant software project file (hsb\_1chip\_avtx\_versa.rdf), as shown in Figure 5.4.

Figure 5.4. Open Project File

3. Modify the Synplify Pro strategy details under Synthesis Design > Synplify Pro. Refer to Figure 5.5.

Figure 5.5. Synthesis Design's Strategy

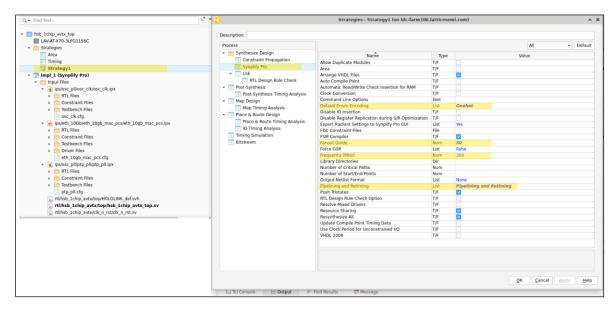

4. Modify the Place and Route design strategy details under Strategy1 > Place & Route Design. Refer to Figure 5.6. The seed run count has been increased to 10 for this reference design, allowing you to select the reference design with the best place-and-route result and the best STA report. Specify multiple seeds for placement and routing during implementation.

**Note:** This is controlled by the Placement Iteration setting under the Place and Route Design strategy in the Lattice Radiant software, which determines how many placement and routing iterations are performed. Each Iteration uses a different cost table, resulting in a unique placement strategy and generating a distinct Uniform Database (.udb) file. By exploring multiple placement options, you increase the likelihood of achieving better timing closure and overall design performance. Using multiple seeds is beneficial for complex designs as it provides alternative implementations that may meet timing more effectively.

Figure 5.6. Place and Route Design's Strategy

For further details on configuring Lattice Radiant Software, refer to the Lattice Radiant User Guide 2025.1.

## 5.4. Generating the Bitstream File

To create the FPGA bitstream file, click **Export Files** to generate the bit file. View the log message in the Export Reports folder for the generated bitstream.

Figure 5.7. Generate and Export Bitstream File

# 6. Implementing the Reference Design on the Avant-X Versa Board

## 6.1. Requirements

#### 6.1.1. Hardware

- NVIDIA Jetson AGX Orin Developer Kit

- Lattice Avant-X Versa Board

- IMX258 Camera Sensor Module contact Lattice Sales for more information

- Ethernet 10GBase-T (Cat 6 RJ-45) SFP+ Module (tested with 6COM 6C-SFP+-T Compatible 10GBASE-T SFP+ Copper RJ-45 30m Optical Transceiver Module)

- 25G SFP28 Optical Transceiver Module (tested with FS 25GBASE-SR SFP28 850nm 100m DOM Duplex LC/UPC MMF Optical Transceiver Module for FS Switches)

- CAT6 Ethernet cable (support 10G)

- Fiber Optic cable (support 25G)

- Type-C USB Cable

- DisplayPort Cable

- Monitor with DisplayPort support (for AGX Orin)

- Keyboard (for AGX Orin)

- Mouse (for AGX Orin)

- Mini USB Type-A cable for programming

- 12 V Power Supply

- Host Orin AGX power adapter

- Gigabit Ethernet Switch (tested with MikroTik CRS510-8XS-2XQ-IN)

The additional camera power jumper connector (J22) should be set to the 1.2 V option, as illustrated in Figure 6.1. This configuration is intended for the IMX258 camera, which supports switching between 1.0 V and 1.2 V, depending on the specific camera model connected.

Figure 6.1. Avant-X Versa Board Camera Connector and Jumper

Figure 6.2 shows the hardware setup for the Jetson AGX Orin host and the Lattice Avant-X Versa Board used in the 10G Ethernet Reference Design implementation.

Figure 6.2. Hardware Setup to support 10G Ethernet

Figure 6.3 shows the hardware setup for the Jetson AGX Orin host and the Lattice Avant-X Versa Board used in the 25G Ethernet Reference Design implementation.

Figure 6.3. Hardware Setup to support 25G Ethernet

Note: An additional Ethernet switch is required to reduce 25 Gb traffic to 10 Gb to match the Jetson AGX Orin maximum supported bandwidth of 10 Gb. A fiber-optic cable connects the 25 Gb output from the Avant-X Versa Board's SFP cage to the Ethernet switch, while a CAT6 Ethernet cable links the switch to the Jetson AGX Orin's Ethernet port.

Be aware that additional configuration may be necessary on the Ethernet switch to ensure compatibility with both 10 Gb and 25 Gb protocols, depending on the expected input speed. A MikroTik Gigabit Ethernet switch was used in this demonstration, as shown in Figure 6.3. Users may opt for any equivalent switch that supports 25 Gb connectivity.

### 6.1.2. Software

- Jetpack 6.2.1

- NVIDIA Jetson Linux 36.4.4

- NVIDIA Holoscan SDK 3.3.0

- Holoscan Sensor Bridge (HSB) SDK 2.2.0

#### 6.2. Jetson AGX ORIN Host Setup

#### 6.2.1. Setting Up the Jetson AGX ORIN Developer Kit

To set up the Jetson AGX Orin Developer Kit, follow the steps below. These steps are to be executed on the Ubuntu host PC terminal.

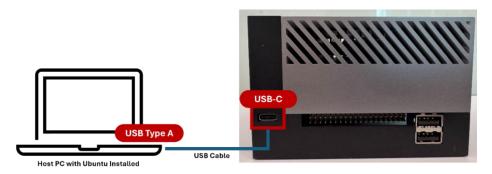

1. Set up an Ubuntu 22.04 host PC with at least 8 GB of RAM and an internet connection. Connect the Ubuntu host to the Jetson AGX Orin using a USB cable as shown in Figure 6.4.

Figure 6.4. Ubuntu Host PC and Jetson AGX Orin Developer Kit Setup

2. Download and install the NVIDIA SDK Manager:

```

wget https://developer.download.nvidia.com/compute/cuda/repos/ubuntu2204/x86_64/cuda-

keyring_1.1-1_all.deb

sudo dpkg -i cuda-keyring_1.1-1_all.deb

sudo apt-get update

sudo apt-get -y install sdkmanager

```

3. Place the AGX Orin into recovery mode by pressing and holding the recovery button as shown in Figure 6.5. While holding the recovery button, press the reset button and release it. Wait for about three seconds or more, then release the recovery button.

Figure 6.5. Recovery and Reset Button

- 4. Launch SDK Manager from the terminal, type: sdkmanager

- 5. Log in using your NVIDIA developer credentials if using the SDK Manager for the first time. Select the checkbox, **Stay logged in**, then click the **LOGIN** button.

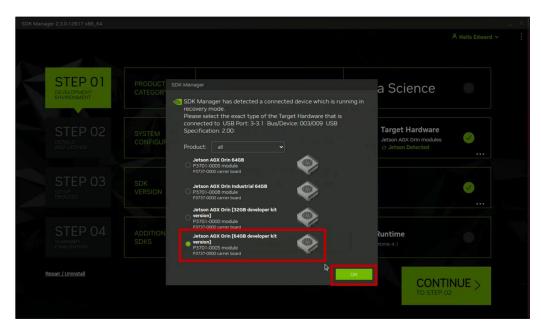

- 6. Select **Jetson AGX Orin [64 GB Developer Kit version]** as the target hardware after the SDK Manager window appears. Then click **OK.**

Figure 6.6. Jetson AGX Orin [64GB developer kit version]

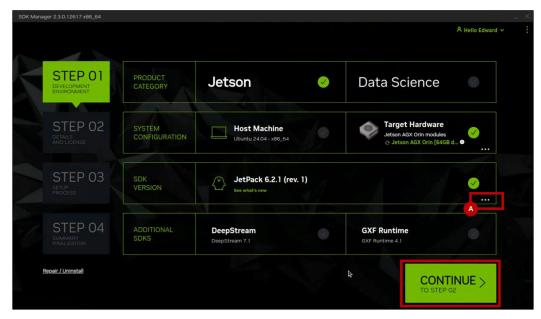

7. Click the ... icon at (A) as shown in Figure 6.7, and select JetPack 6.2.1 (Rev. 1). Then, click CONTINUE to proceed.

Figure 6.7. JetPack 6.2.1 (Rev.1)

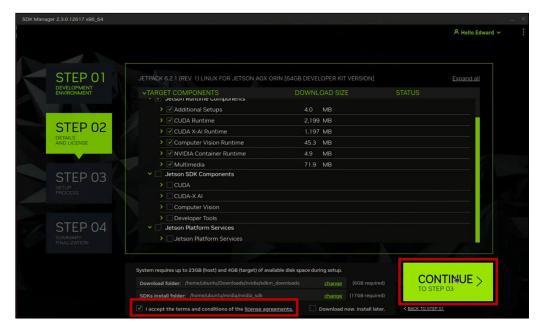

8. Leave all settings as default, and select I accept the terms and conditions of the license agreements. The, click **CONTINUE** to proceed with the installation process.

Figure 6.8. Terms and Conditions - License Agreement

9. In **STEP 03 – SETUP IN PROCESS**, as shown in Figure 6.9, wait for the download operation and OS image creation process to complete.

Figure 6.9. Download Operation and OS Image Creation

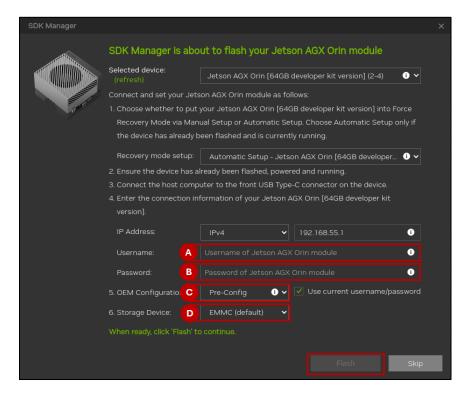

10. When prompted for the flash setup, enter the desired username to access the AGX Orin system, see letter (A) in Figure 6.10, along with the password at (B). Select Pre-Config from the dropdown at (C) and EMMC as the storage device at (D). Then, click Flash to proceed.

Figure 6.10. SDK Manager

11. Complete **STEP 04 – SUMMARY FINALIZATION** to finish the setup. Reset the Jetson AGX Orin system by pressing the reset button as shown in Figure 6.4. Then proceed to the next section to configure the Jetson AGX Orin itself.

Figure 6.11. Summary Finalization

#### 6.2.2. Configure the AGX Orin Developer Host Kit

The customizable HSB sensor interface reference design is supported by the Jetson AGX Orin system running at JetPack 6.2.1. The following steps are one-time setup procedures and should be executed directly on the AGX Orin terminal, outside the Holoscan Sensor Bridge (HSB) docker container. All commands assume the HSB is connected via eno1 (the Ethernet interface on the Jetson AGX Orin).

1. Install git-lfs (some data files in the HSB source repository use it).

```

sudo apt-get update

sudo apt-get install -y git-lfs

```

2. Grant the user permission to the docker subsystem.

```

sudo usermod -aG docker $USER

```

3. Reboot the AGX Orin to apply the changes.

sudo reboot

4. Increase the network receive buffer size to support Linux sockets.

```

echo 'net.core.rmem_max = 31326208' | sudo tee /etc/sysctl.d/52-hololink-

rmem_max.conf

sudo sysctl -p /etc/sysctl.d/52-hololink-rmem max.conf

```

5. Assign a static IP address (192.168.0.101) to the onboard network port.

```

EN0=eno1 sudo nmcli con add con-name hololink-$EN0 ifname $EN0 type ethernet ip4 192.168.0.101/24 sudo nmcli connection up hololink-$EN0

```

6. Power on the Avant-X Versa board and ensure it is properly connected. Then, ping to check connectivity . ping 192.168.0.101

7. Isolate a processor core from the Linux kernel when running Linux socket-based examples1.

To isolate that core, edit the /boot/extlinux/extlinux.conf file.

```

sudo nano /boot/extlinux/extlinux.conf

```

8. Add the setting isolcpus=2 to the end of the line that begins with **APPEND**.

Your file should resemble the following:

```

TIMEOUT 30

DEFAULT primary

MENU TITLE L4T boot options

LABEL primary

MENU LABEL primary kernel

LINUX /boot/Image

...

APPEND ${cbootargs} ...<other-settings>... isolcpus=2

```

9. Save and exit by pressing Ctrl+O, then Enter, followed by Ctrl+X.

The sensor bridge applications can run the network receiver process on a different core by setting the environment variable **HOLOLINK\_AFFINITY** to the desired core.

For example, to run on the first processor core, type:

HOLOLINK\_AFFINITY=0 python3 examples/linux\_imx258\_player.py

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

10. Run the **jetson\_clocks** tool at startup to set the core clocks to their maximum.

sudo systemctl enable jetson\_clocks.service

```

JETSON_CLOCKS_SERVICE=/etc/systemd/system/jetson_clocks.service

cat <<EOF | sudo tee $JETSON_CLOCKS_SERVICE >/dev/null

[Unit]

Description=Jetson Clocks Startup

After=nvpmodel.service

[Service]

Type=oneshot

ExecStart=/usr/bin/jetson_clocks

[Install]

WantedBy=multi-user.target

EOF

sudo chmod u+x $JETSON_CLOCKS_SERVICE

```

11. Set the Jetson AGX Orin power mode to **MAXN** for optimal performance. You can change this setting via the L4T power dropdown menu in the upper-right corner of the screen, as indicated by **(A)**. Click **(B)** to select the **MAXN** option.

Figure 6.12. MAXN Power Mode

12. Reboot Jetson AGX Orin to apply changes.

sudo reboot

13. Enable PTP for **\$EN0** to synchronize timestamps in received data with the host system time. Install the **linuxptp** tool, then create a systemd service file to run **phc2sys** at boot time, ensuring the clock in **\$EN0** is synchronized with the system clock.

```

sudo apt update && sudo apt install -y linuxptp

EN0=eno1

PHC2SYS_SERVICE=/etc/systemd/system/phc2sys-$EN0.service

cat <<EOF | sudo tee $PHC2SYS SERVICE >/dev/null

[Unit]

Description=Copy system time to $EN0

Requires=NetworkManager.service

After=NetworkManager.service

After=timemaster.service

[Service]

Type=simple

ExecStartPre=timeout 3m bash -c "until [ \"\$(nmcli -g GENERAL.STATE device show

$EN0)\" = \"100 (connected)\" ]; do sleep 1; done"

ExecStart=/usr/sbin/phc2sys -c $EN0 -s CLOCK REALTIME -0 0 -S 0.0001

[Install]

WantedBy=multi-user.target

EOF

```

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

14. Configure it for execution at startup, and start it now.

```

sudo chmod u+x $PHC2SYS_SERVICE

sudo systemctl enable phc2sys-$EN0.service

sudo systemctl start phc2sys-$EN0.service

```

15. Next, run ptp4l to send PTP SYNC messages to \$ENO.

```

cat <<EOF | sudo tee /etc/linuxptp/hsb-ptp.conf >/dev/null

# This configuration is appropriate for NVIDIA Holoscan sensor bridge

# applications, where PTP messages are sent over L2 and a 1/2 second interval.

[global]

logSyncInterval -1

logMinDelayReqInterval -1

network_transport L2

EOF

```

16. Create a systemd service to run ptp4l.

```

PTP4L_SERVICE=/etc/systemd/system/ptp4l-$EN0.service

cat <<EOF | sudo tee $PTP4L_SERVICE >/dev/null

[Unit]

Description=Send PTP SYNC messages to $EN0

After=phc2sys-$EN0.service

[Service]

Type=simple

ExecStart=/usr/sbin/ptp4l -i $EN0 -f /etc/linuxptp/hsb-ptp.conf

[Install]

WantedBy=multi-user.target

EOF

```

```

sudo chmod u+x $PTP4L_SERVICE

sudo systemctl enable ptp4l-$EN0.service

sudo systemctl start ptp4l-$EN0.service

```

- 17. Log in to NVIDIA GPU Cloud (NGC).

- Register for an NGC account at https://catalog.ngc.nvidia.com/

- Create an API key at https://ngc.nvidia.com/setup/api-key

- Use the API key to log in to nvcr.io

```

$ docker login nvcr.io

Username: $oauthtoken

Password: <Your token key to NGC>

WARNING! Your password will be stored unencrypted in

/home/<user>/.docker/config.json.

Configure a credential helper to remove this warning. See

https://docs.docker.com/engine/reference/commandline/login/#credentials-store

Login Succeeded

```

#### Note:

1. For high-bandwidth applications, such as 4K video acquisition, isolate the network receiver core to ensure optimal performance. Set processor affinity for the example program to the isolated core to improve performance and reduce latency. By default, the sensor bridge software runs the time-critical background network receiver process on core 3. Ensure core 3 is isolated from Linux scheduling so that no other processes run on it without explicit user assignment, thereby improving reliability and performance.

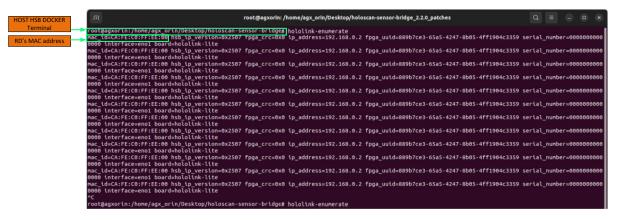

FPGA-RD-02329-1.0