# **5G Ethernet IP**

IP Version: v1.0.0

# **User Guide**

FPGA-IPUG-02313-1.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents                                |    |

|-----------------------------------------|----|

| Abbreviations in This Document          | 8  |

| 1. Introduction                         | 9  |

| 1.1. Overview of the IP                 | 9  |

| 1.2. Quick Facts                        | 9  |

| 1.3. IP Support Summary                 | 10 |

| 1.4. Features                           | 10 |

| 1.5. Licensing and Ordering Information | 10 |

| 1.5.1. Hardware Evaluation              | 11 |

| 1.6. Hardware Support                   | 11 |

| 1.7. Minimum Device Requirements        | 11 |

| 1.8. Naming Conventions                 | 11 |

| 1.8.1. Nomenclature                     | 11 |

| 1.8.2. Signal Names                     | 11 |

| 2. Functional Description               | 12 |

| 2.1. MAC + PHY                          |    |

| 2.1.1. IP Architecture Overview         |    |

| 2.1.2. Block Diagram                    |    |

| 2.1.3. Management Block                 |    |

| 2.2. MAC                                |    |

| 2.2.1. IP Architecture Overview         | 12 |

| 2.2.2. Block Diagram                    | 13 |

| 2.2.3. Ethernet Data Format             | 13 |

| 2.2.4. Receive MAC                      | 14 |

| 2.2.5. Transmit MAC                     | 14 |

| 2.2.6. Receive AXI4-Stream Interface    | 15 |

| 2.2.7. Transmit AXI4-Stream Interface   | 19 |

| 2.2.8. Data Unpacking                   |    |

| 2.2.9. MAC Management Block             | 23 |

| 2.3. PHY                                |    |

| 2.3.1. IP Architecture Overview         |    |

| 2.3.2. Block Diagram                    |    |

| 2.3.3. Lane Merging                     |    |

| 2.3.4. PHY Management Block             |    |

| 2.3.5. Loopback Modes                   |    |

| 2.4. Clocking                           |    |

| 2.4.1. Clocking Overview                |    |

| 2.5. Reset                              |    |

| 2.5.1. MAC Reset Sequence               |    |

| 2.5.2. PHY Reset Sequence               |    |

| 2.6. Latency                            |    |

| 3. IP Parameter Description             |    |

| 3.1. MAC + PHY                          |    |

| 3.2. MAC Only                           |    |

| 3.3. PHY Only                           |    |

| 4. Signal Description                   |    |

| 4.1. MAC + PHY Signals                  |    |

| 4.2. MAC Only Signals                   |    |

| 4.3. PHY Only Signals                   |    |

| 5. Register Description                 |    |

| 5.1. MAC + PHY Registers                |    |

| 5.2. MAC Registers                      | 45 |

| 5.2.1. Configuration Registers for MAC                 | 45 |

|--------------------------------------------------------|----|

| 5.2.2. Interrupt Registers                             | 49 |

| 5.2.3. Statistics Counters                             | 50 |

| 5.3. PHY Registers                                     | 55 |

| 5.3.1. Configuration Registers for PHY                 | 55 |

| 6. Example Design                                      | 56 |

| 6.1. Example Design Configuration                      | 56 |

| 6.2. Overview of Example Design and Features           | 56 |

| 6.3. Example Design Components                         | 57 |

| 6.3.1. Versa Example Design Components (Avant Devices) | 57 |

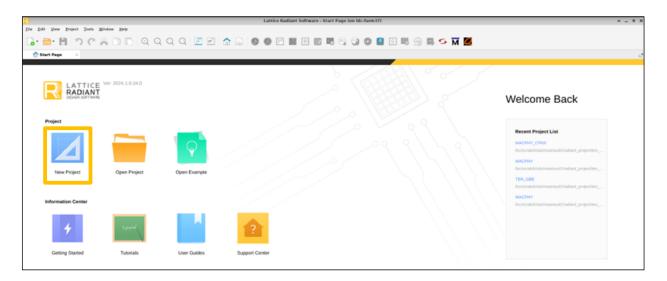

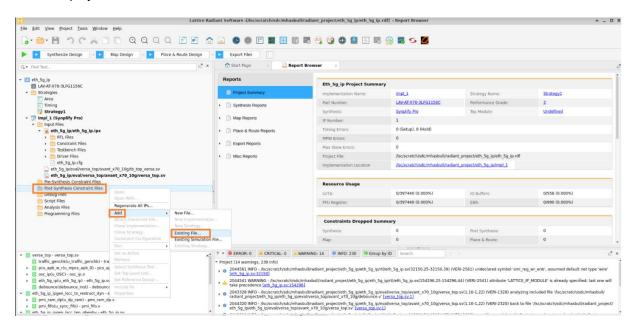

| 6.4. Generating Example Design                         | 58 |

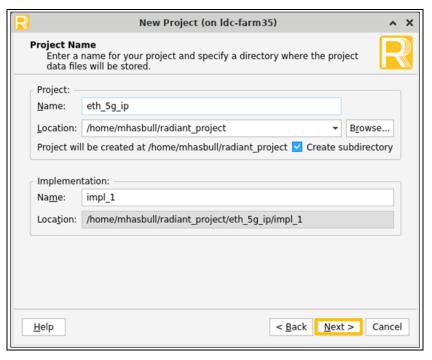

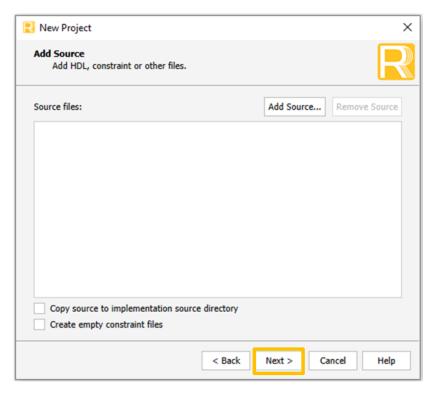

| 6.4.1. Create New Radiant Project                      | 58 |

| 6.4.2. IP Installation and Generation                  | 62 |

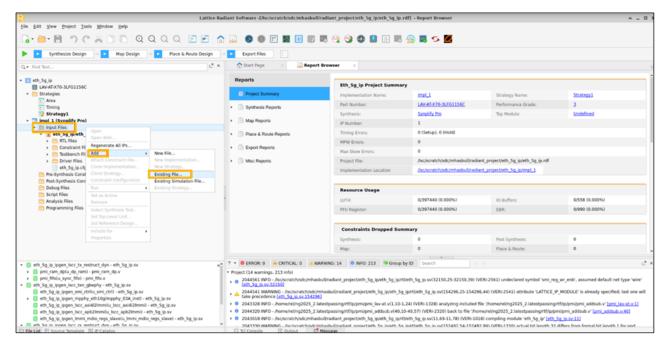

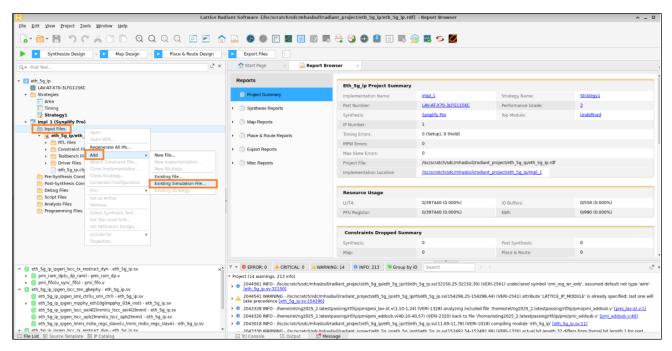

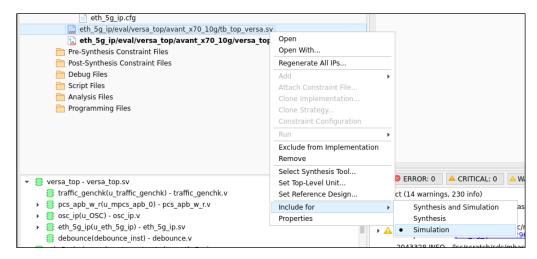

| 6.4.3. Importing Example Design Files to a Project     | 63 |

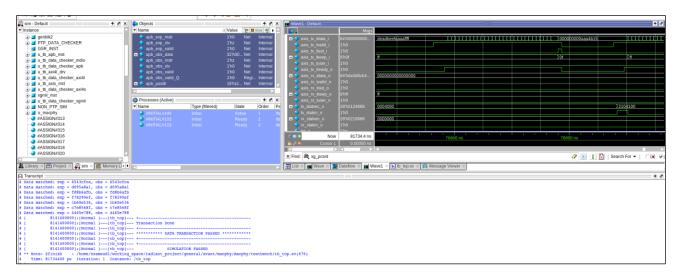

| 6.5. Example Design Simulation                         | 67 |

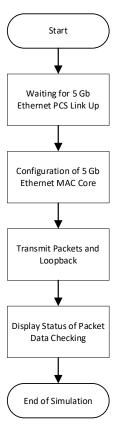

| 6.5.1. 5 Gb Ethernet MAC Example Design Testbench Flow | 67 |

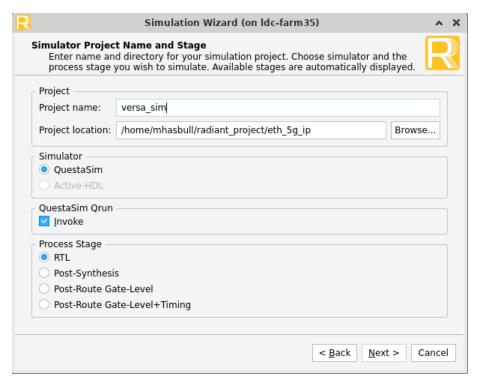

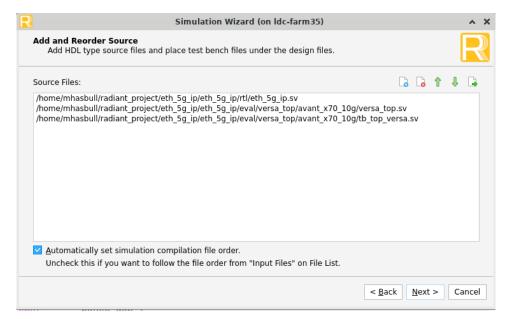

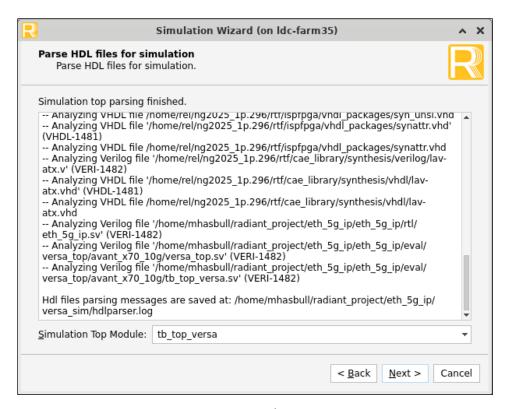

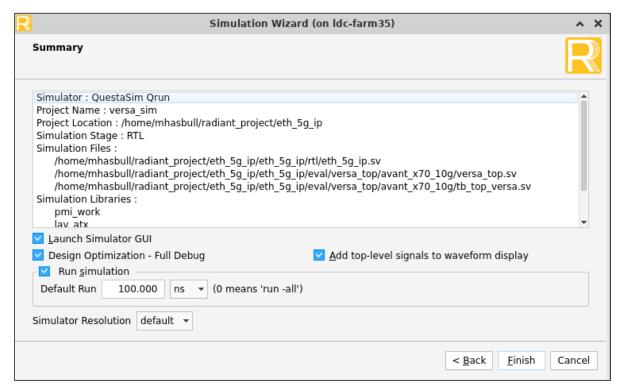

| 6.5.2. Create a Simulation Project                     | 67 |

| 6.6. Hardware Testing                                  | 73 |

| 7. Designing with the IP                               | 78 |

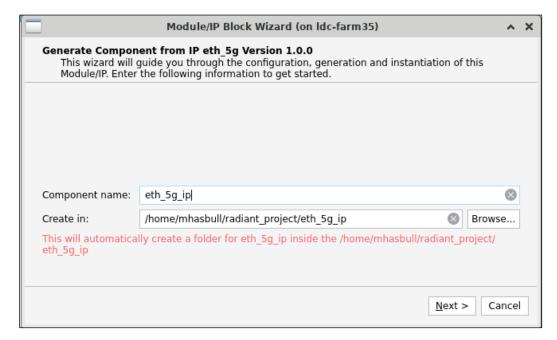

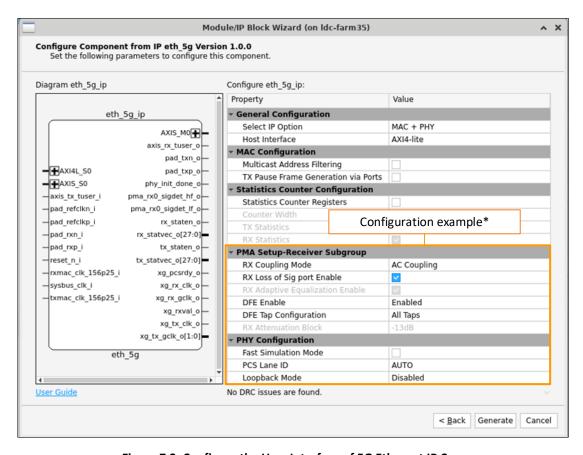

| 7.1. Generating and Instantiating the IP               | 78 |

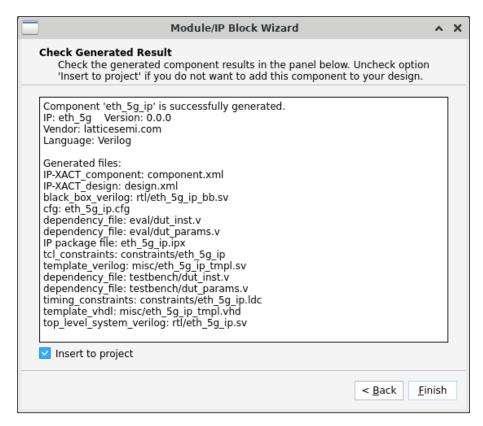

| 7.1.1. Generated Files and File Structure              | 81 |

| 7.2. Design Implementation                             | 81 |

| 7.3. Timing Constraints                                | 82 |

| 7.3.1. Create Clock Constraints for MAC-only Option    | 82 |

| 7.3.2. Create Clock Constraints for MAC + PHY Option   | 82 |

| 7.3.3. Create Clock Constraints for PHY-only Option    | 83 |

| 7.4. Specifying the Strategy                           | 83 |

| 7.5. Running Functional Simulation                     | 83 |

| 7.5.1. Simulation Results                              | 85 |

| Appendix A. Resource Utilization                       | 86 |

| References                                             | 87 |

| Technical Support Assistance                           | 88 |

| Revision History                                       | 89 |

# **Figures**

| Figure 1.1. 5GBASE-R Application                                                              | 9  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2.1. 5GbE MAC + PHY IP Core Block Diagram                                              | 12 |

| Figure 2.2. 5G Ethernet MAC IP Core Block Diagram                                             | 13 |

| Figure 2.3. Untagged Ethernet Frame Format                                                    |    |

| Figure 2.4. Tagged Ethernet Frame Format                                                      | 13 |

| Figure 2.5. AXI4-Stream RX Adapter Interface Diagram                                          | 15 |

| Figure 2.6. Normal Frame Reception                                                            |    |

| Figure 2.7. Back-to-back Frames Reception                                                     | 17 |

| Figure 2.8. Frame Reception with In-Band FCS Passing                                          | 18 |

| Figure 2.9. Reception with Custom Preamble                                                    | 19 |

| Figure 2.10. AXI4-Stream TX Adapter Interface Diagram                                         | 19 |

| Figure 2.11. Default Normal Frame Transmission                                                | 20 |

| Figure 2.12. Transmission with In-Band FCS Passing                                            | 21 |

| Figure 2.13. Transmission with Custom Preamble Passing                                        | 22 |

| Figure 2.14. Receive Physical Interface for 8/6-bit GMII or MII                               | 22 |

| Figure 2.15. Transmit Physical Interface for 8/16-bit GMII or MII                             | 23 |

| Figure 2.16. 5G Ethernet PHY IP Core Block Diagram                                            | 24 |

| Figure 2.17. Set the Lane ID Configuration of the 5G Ethernet PHY IP Core                     | 25 |

| Figure 2.18. Lane ID Numbering                                                                | 25 |

| Figure 2.19. Lane Merging Report File                                                         |    |

| Figure 2.20. Remapped Addresses for PCS Register Address through the AXI4-Lite Interface      |    |

| Figure 2.21. Far End Parallel Loopback                                                        |    |

| Figure 2.22. Near End Parallel Loopback                                                       |    |

| Figure 2.23. 5G Clock Network Diagram for Avant Devices                                       |    |

| Figure 2.24. Sequence to Configure RX MAC In-Band FCS Passing                                 |    |

| Figure 2.25. PHY Initialization Sequence                                                      |    |

| Figure 6.1 5 Gb Ethernet MAC IP Versa Example Design Block Diagram                            |    |

| Figure 6.2. Start Page of the Radiant Software                                                |    |

| Figure 6.3. Create a New Project                                                              |    |

| Figure 6.4. Add Source to Project                                                             |    |

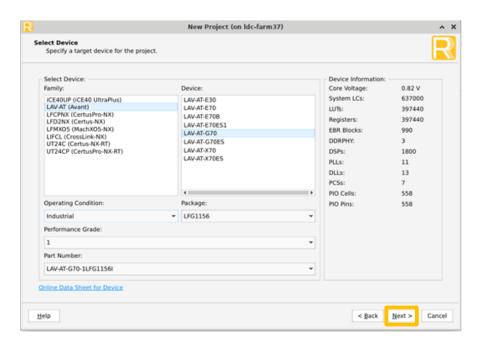

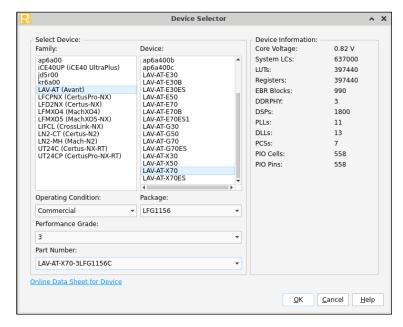

| Figure 6.5. Select an Avant Device for the Project                                            |    |

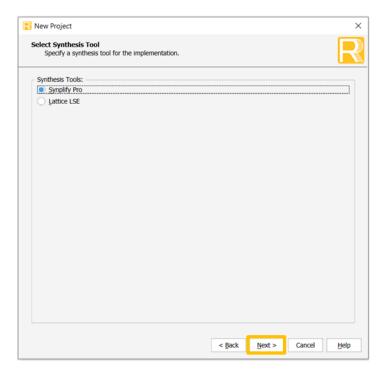

| Figure 6.6. Select a Synthesis Tool                                                           |    |

| Figure 6.7. Project Information                                                               |    |

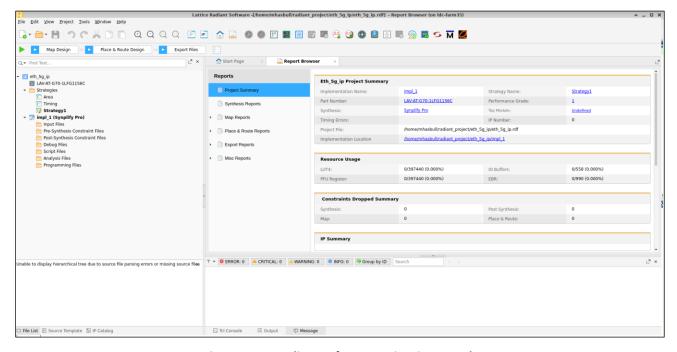

| Figure 6.8. A Radiant Software Project is Created                                             |    |

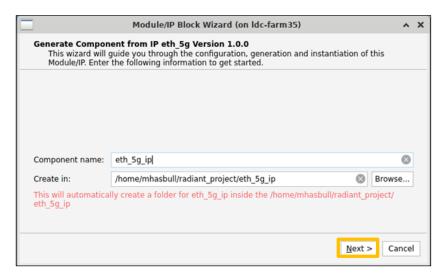

| Figure 6.9. Generate Component                                                                |    |

| Figure 6.10. Configure Component                                                              |    |

| Figure 6.11. Device Setup for Avant Devices                                                   |    |

| Figure 6.12. Add Related Files into the Radiant Software Project                              |    |

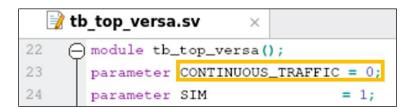

| Figure 6.13. CONTINUOUS_TRAFFIC Parameter for Continuous Mode in versa_top.sv File            |    |

| Figure 6.14. Add the tb_top_versa.sv File into the Radiant Software Project                   |    |

| Figure 6.15. CONTINUOUS_TRAFFIC Parameter for Continuous Mode in the tb_versa_top.sv File     |    |

| Figure 6.16. CONTINUOUS_TRAFFIC Parameter for Non-Continuous Mode in the tb_versa_top.sv File |    |

| Figure 6.17. Set the tb_top_versa.sv File to be Included for Simulation Only                  |    |

| Figure 6.18. Add the .pdc File into the Radiant Software Project                              |    |

| Figure 6.19. Timing Constraint File (versa.pdc Example from an Avant Device)                  |    |

| Figure 6.20. 5G Ethernet MAC Example Design Testbench Flowchart                               |    |

| Figure 6.21. Create a Simulation Project                                                      |    |

| Figure 6.22. Include Source Files                                                             |    |

| Figure 6.23. Set tb_top* as Top Module                                                        |    |

| Figure 6.24. Change the Time Setting for Default Run                                          |    |

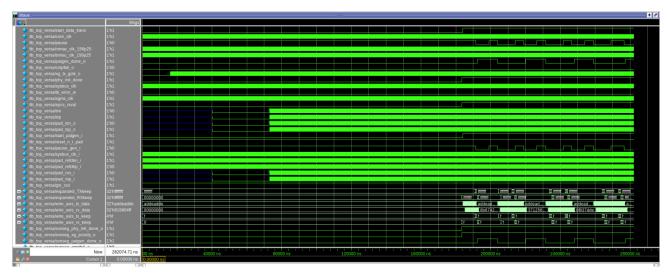

| Figure 6.25. Example Design Simulation Waveform for Continuous Mode                           |    |

| Figure 6.26. Example Design Simulation Output for Continuous Mode                             |    |

| O                                                                                             |    |

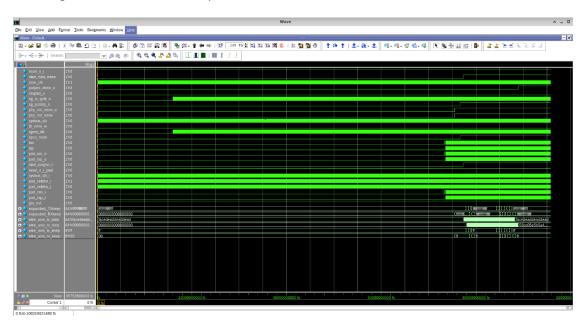

| Figure 6.27. Example Design Simulation Waveform for Non-Continuous Mode      | 71 |

|------------------------------------------------------------------------------|----|

| Figure 6.28. Example Design Simulation Output for Non-Continuous Mode        | 72 |

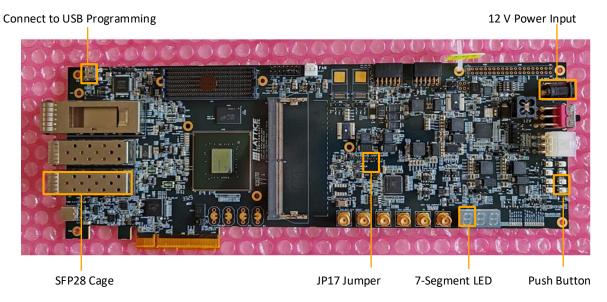

| Figure 6.29. Avant-X Versa Board Setup                                       | 73 |

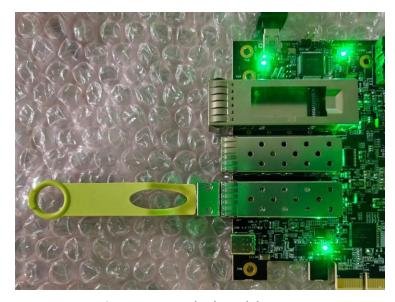

| Figure 6.30. Loopback Module Setup                                           | 73 |

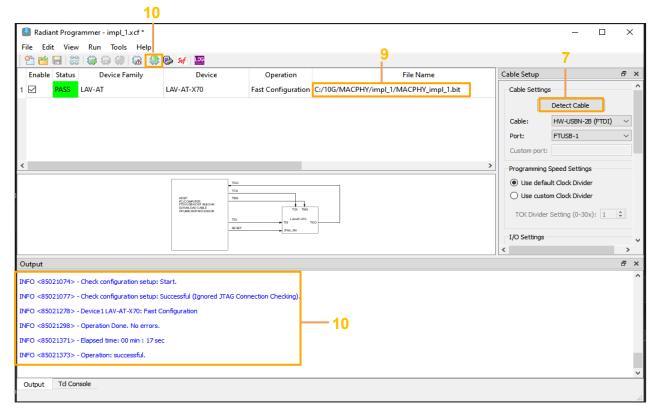

| Figure 6.31. Successful Design Compilation                                   | 74 |

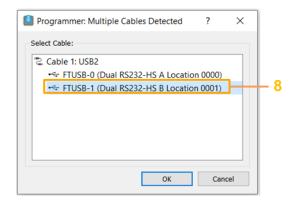

| Figure 6.32. Cable Selection for Avant-AT-X Device                           | 74 |

| Figure 6.33. Programmer GUI                                                  | 74 |

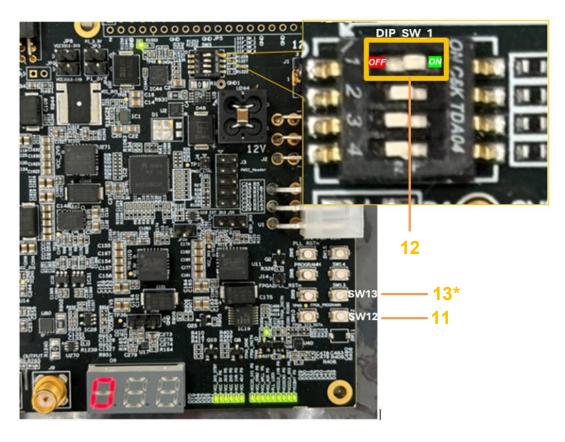

| Figure 6.34. Push Buttons on Avant-AT-X Device                               | 75 |

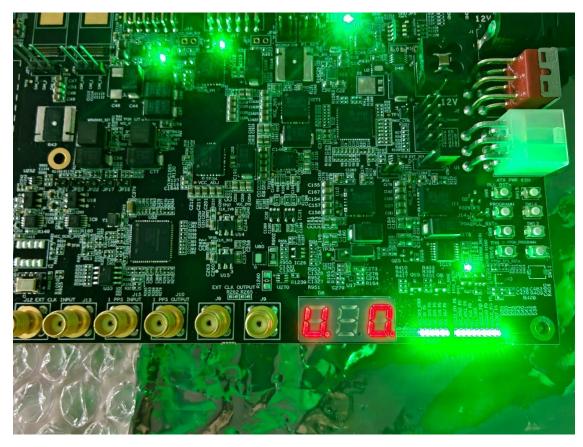

| Figure 6.35. Passing Scenario on Avant-AT-X Device                           |    |

| Figure 6.36. Failing Scenario on Avant-AT-X Device                           | 76 |

| Figure 6.37. LED 7-Segment                                                   | 77 |

| Figure 6.38. Parameters for Frame Size in the Top File                       |    |

| Figure 7.1. Module/IP Block Wizard                                           |    |

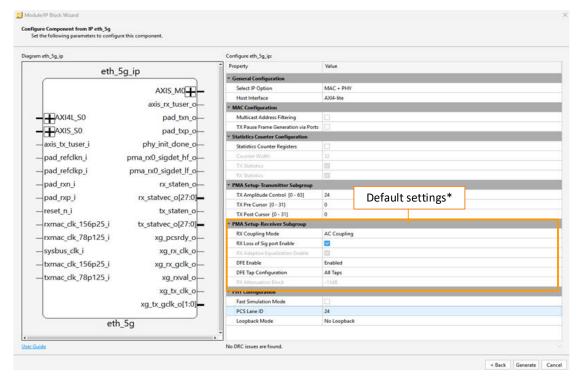

| Figure 7.2. Configure the User Interface of 5G Ethernet IP Core              | 79 |

| Figure 7.3. Check Generated Result                                           | 80 |

| Figure 7.4. Synthesize Design                                                | 80 |

| Figure 7.5. Timing Constraint File (.pdc) for the 5G MAC IP                  |    |

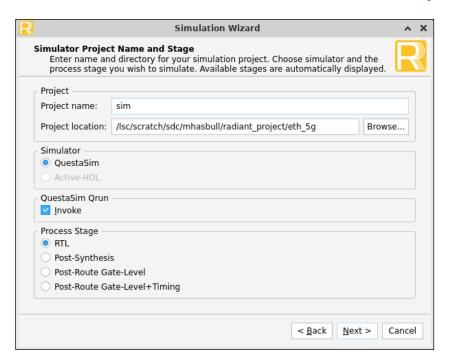

| Figure 7.6. Simulation Wizard                                                |    |

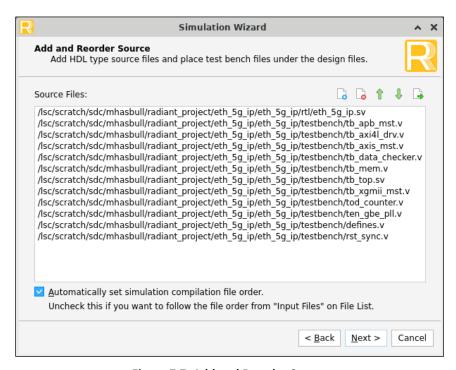

| Figure 7.7. Add and Reorder Source                                           |    |

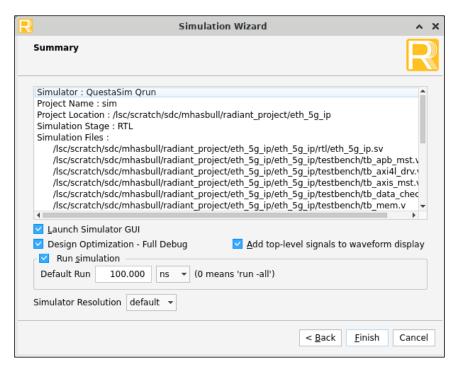

| Figure 7.8. Summary Window                                                   |    |

| Figure 7.9. Simulation Results                                               | 85 |

|                                                                              |    |

| Tables                                                                       |    |

| Table 1.1. Summary of the 5G Ethernet IP                                     |    |

| Table 1.2. 5G Ethernet IP Support Readiness                                  | 10 |

| Table 1.3. Minimum Device Requirements for 5G Ethernet IP Core               | 11 |

| Table 2.1. Shared Signal Mapping of 5G Ethernet IP to MPPHY for Lane Merging |    |

| Table 2.2. AXI4-Lite to PCS Address and Data Conversion                      |    |

| Table 2.3. MAC + PHY Attributes                                              |    |

| Table 3.1. MAC + PHY Attributes                                              |    |

| Table 3.2. MAC Only Attributes                                               |    |

| Table 3.3. PHY Only Attributes                                               |    |

| Table 4.1. Signal Description—MAC + PHY                                      |    |

| Table 4.2. Signal Description—MAC Only                                       |    |

| Table 4.3. Signal Description—PHY Only                                       |    |

| Table 5.1. Access Types for MAC Only                                         |    |

| Table 5.2. Configuration Registers for MAC                                   |    |

| Table 5.3. MODE Register                                                     |    |

| Table 5.4. TX_CTL Register                                                   |    |

| Table 5.5. RX_CTL Register                                                   |    |

| Table 5.6. MAX_PKT_LNGTH Register                                            |    |

| Table 5.7. IPG_VAL Register                                                  |    |

| Table 5.8. MAC_ADDR_0 Register                                               |    |

| Table 5.9. MAC_ADDR_1 Register                                               |    |

| Table 5.10. TX_RX_STS Register                                               |    |

| Table 5.11. VLAN_TAG Register                                                |    |

| Table 5.12. MC_TABLE_0 Register                                              |    |

| Table 5.13. MC_TABLE_1 Register                                              |    |

| Table 5.14. PAUSE_OPCODE Register                                            |    |

| Table 5.15. MAC_CTL Register                                                 |    |

| Table 5.16. PAUSE_TM Register                                                |    |

| Table 5.17. Summary of Interrupt Registers                                   | 49 |

| Table 5.18. INT_STATUS Register                                       | 50 |

|-----------------------------------------------------------------------|----|

| Table 5.19. INT_ENABLE Register                                       | 50 |

| Table 5.20. INT_SET Register                                          |    |

| Table 5.21. Summary of Statistics Counters                            |    |

| Table 5.22. Access Types for PHY                                      | 55 |

| Table 5.23. Register Address Map for PHY                              | 55 |

| Table 6.1. IP Configuration for the 5G Ethernet MAC IP Example Design | 56 |

| Table 6.2. AXI4-Lite Module Configuration Registers                   | 58 |

| Table 6.3. Description of Generated Files in the Eval Folder          | 63 |

| Table 6.4. Top-Level Files                                            | 64 |

| Table 6.5. LED 7-Segment Description for DIG 1                        | 77 |

| Table 6.6. LED 7-Segment Description for DIG 3                        | 77 |

| Table 7.1. Generated File List                                        | 81 |

| Table A.1. Resource Utilization for Avant Devices                     |    |

|                                                                       |    |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation      | Definition                             |  |  |

|-------------------|----------------------------------------|--|--|

| APB               | Advanced Peripheral Bus                |  |  |

| AXI4-Lite         | Advanced eXtensible Interface 4 Lite   |  |  |

| AXI4-Stream/AXI4S | Advanced eXtensible Interface 4 Stream |  |  |

| CRC               | Cyclic Redundancy Check                |  |  |

| DA                | Destination Address                    |  |  |

| DFE               | Decision Feedback Equalizer            |  |  |

| DIC               | Deficit Idle Count                     |  |  |

| EBR               | Embedded Block RAM                     |  |  |

| FCS               | Frame Check Sequence                   |  |  |

| FIFO              | First-In First-Out                     |  |  |

| GPLL              | Generic Phase-Locked Loop              |  |  |

| IFG               | Inter-Frame Gap                        |  |  |

| IPG               | Inter-Packet Gap                       |  |  |

| LINTR             | Lattice Interrupt Interface            |  |  |

| LUT               | Look-Up Table                          |  |  |

| L/T               | Length/Type                            |  |  |

| MAC               | Media Access Controller                |  |  |

| MDIO              | Management Data Input/Output           |  |  |

| MMD               | MDIO Manageable Device                 |  |  |

| MTU               | Maximum Transmission Unit              |  |  |

| PCS               | Physical Coding Sublayer               |  |  |

| PHY               | Physical Layer Device                  |  |  |

| PMA               | Physical Medium Attachment             |  |  |

| PTP               | Precision Time Protocol                |  |  |

| SA                | Source Address                         |  |  |

| SFD               | Start Frame Delimiter                  |  |  |

| SOF               | Start of Frame                         |  |  |

| ToD               | Time of Day                            |  |  |

| TSU               | Timestamp Unit                         |  |  |

| XGMII             | 10-Gigabit Media Independent Interface |  |  |

## 1. Introduction

## 1.1. Overview of the IP

The Lattice Semiconductor 5G Ethernet (GbE) IP core supports the ability to transmit and receive data between a host processor and an Ethernet network. The 5GbE IP core consists of the 10-Gigabit Media Independent Interface (XGMII), which connects media access controllers (MACs) and Physical Layer devices (PHYs). The main function of the 5GbE MAC is to ensure that the media access rules specified in the IEEE 802.3 standards are met while transmitting a frame of data over an Ethernet. On the receiver side, the Ethernet MAC extracts the different components of a frame and transfers them to higher applications through an AXI4-Stream interface. The PHY implements the physical coding sublayer (PCS) and physical medium attachment (PMA) functionality based on the IEEE 802.3 5GBASE-R specification.

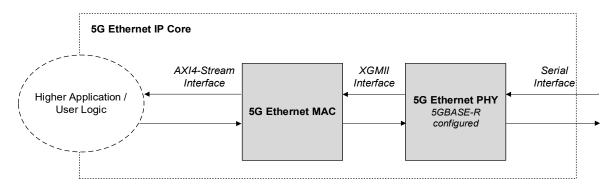

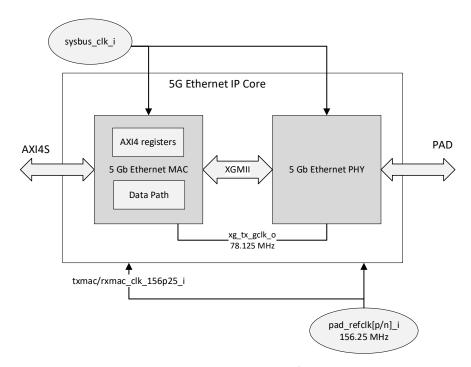

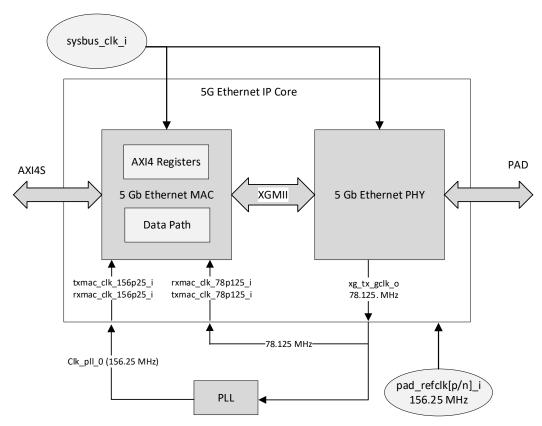

The following figure shows an example of a 5GBASE-R application. The 5GbE MAC is connected to the 5GbE PHY within the 5G Ethernet IP core through the XGMII interface. The clock source to the Ethernet MAC is from xg\_tx\_gclk\_o[0] (clock output from the Ethernet PHY).

Figure 1.1. 5GBASE-R Application

## 1.2. Quick Facts

The following table provides quick facts about the 5G Ethernet IP core.

Table 1.1. Summary of the 5G Ethernet IP

| Supported Devices                                                                  |                                                 | Avant™-AT-G and Avant-AT-X                                                         |  |

|------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------|--|

| ● MAC only ■ PHY only                                                              |                                                 | MAC only                                                                           |  |

|                                                                                    |                                                 | PHY only                                                                           |  |

|                                                                                    |                                                 | MAC + PHY                                                                          |  |

|                                                                                    | IP Changes <sup>1</sup>                         | Refer to the 5G Ethernet IP Release Notes (FPGA-RN-02102).                         |  |

| Resource Utilization Supported User Interface AXI4-Stream/APB/AXI4-Lite interface. |                                                 | AXI4-Stream/APB/AXI4-Lite interface.                                               |  |

| Resource Offization                                                                | Resources See Appendix A. Resource Utilization. |                                                                                    |  |

|                                                                                    | Lattice Implementation                          | n IP core v1.0.0—Lattice Radiant™ software 2025.2 or later.                        |  |

| Design Tool Support  Synthesis  Synopsys® Synplify Pro® software, O-2018.09LR-SP1. |                                                 | Synopsys® Synplify Pro® software, O-2018.09LR-SP1.                                 |  |

| besign roof support                                                                | Simulation                                      | For the list of supported simulators, see the Lattice Radiant Software User Guide. |  |

#### Note:

1. In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

## 1.3. IP Support Summary

The following table provides IP support information on the 5G Ethernet IP core.

#### Table 1.2. 5G Ethernet IP Support Readiness

| Device Family | Mode                          | Radiant Timing Model | Hardware Validated |

|---------------|-------------------------------|----------------------|--------------------|

| Avant-AT-G/X  | MAC only, PHY only, MAC + PHY | Preliminary          | Yes                |

### 1.4. Features

The 5G Ethernet IP core offers the following key features:

#### MAC

- Compliant to the IEEE 802.3-2022 standard

- Supports standard 5 Gbps Ethernet link layer data rate

- 32-bit AXI4-Stream interface on the client's transmit and receive interfaces operating at 156.25 MHz

- 64-bit XGMII interface operating at 78.125 MHz

- Supports deficit idle count (DIC)

- Supports VLAN and Jumbo frames of 9,600 bytes

- Custom preamble mode

- Independent TX and RX Maximum Transmission Unit (MTU) frame length

- Comprehensive statistics support

- Optional frame check sequence (FCS) generation on transmission

- Optional FCS stripping during reception

- Optional multicast address filtering

- Programmable Inter-Frame Gap

- Supports flow control using pause frames

- Automatic padding of short frames

- Inter-Frame Stretch Mode during transmission

- Supports full-duplex operation

- Advanced Peripheral Bus (APB) interface or AXI4-Lite interface for register accessProgrammable promiscuous (transparent) mode

## PHY

- Designed to the IEEE 802.3-2022 5GBASE-R specification

- 64b/66b encoding and decoding

- XGMII interface: 64-bit, 78.125 MHz

- Supports AXI4-Lite and management data input/output for PCS/

- TX phase compensation FIFO and RX clock compensation FIFO

# 1.5. Licensing and Ordering Information

The 5G Ethernet IP is available with Lattice Radiant Subscription Software. To purchase the Lattice Radiant Subscription license, contact sales or buy through our Online Store.

#### 1.5.1. Hardware Evaluation

The 5G Ethernet IP core supports Lattice's IP hardware evaluation capability when used with Avant-AT-G, and Avant-AT-X devices. The hardware evaluation capability enables you to create versions of the IP core that operate in hardware for a limited period (approximately four hours) without requiring the purchase of an IP license. It may also be used to evaluate the core in hardware in user-defined designs. The hardware evaluation capability may be enabled or disabled in the **Strategy** dialog box. It is enabled by default. To change this setting, go to **Project > Active Strategy > Synplify Pro Settings**.

## 1.6. Hardware Support

Refer to the Example Design section for more information on the boards used.

## 1.7. Minimum Device Requirements

The minimum device requirements for the 5G Ethernet IP core are as follows:

Table 1.3. Minimum Device Requirements for 5G Ethernet IP Core

| Devices      | Speed Grades     |

|--------------|------------------|

| Avant-AT-G/X | All speed grades |

## 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.8.2. Signal Names

Signal names that end with:

- \_n are active low signals (asserted when value is logic 0)

- \_*i* are input signals

- \_o are output signals

- \_io are bi-directional input/output signals

# 2. Functional Description

## 2.1. MAC + PHY

## 2.1.1. IP Architecture Overview

The 5G Ethernet IP core transmits and receives data between a host processor and an Ethernet network. With the MAC + PHY option selected, the IP consists of a MAC and a PHY that is connected through the XGMII internally.

This IP option is supported on Avant-AT-G and Avant-AT-X devices.

For Lane Merging details, refer to the Lane Merging section.

### 2.1.2. Block Diagram

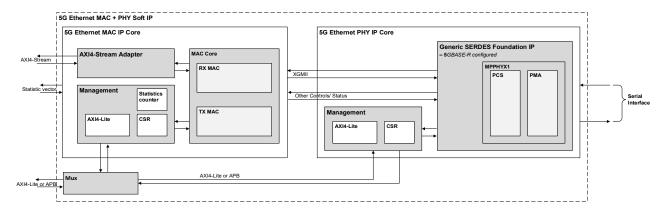

Figure 2.1. 5GbE MAC + PHY IP Core Block Diagram

## 2.1.3. Management Block

The Management block can be accessed through the AXI4-Lite or APB interface when the *MAC + PHY* option is selected. For more details about the management blocks in MAC and PHY respectively, refer to the MAC Management Block and PHY Management Block sections. For protocol timing details, refer to AMBA 4 AXI and ACE Protocol Specification issue H or AMBA 3 APB Protocol version 1.0 Specification.

#### 2.2. MAC

#### 2.2.1. IP Architecture Overview

The main function of the 5G Ethernet MAC IP is to ensure that the media access rules specified in the IEEE 802.3 standards are met while transmitting a frame of data over an Ethernet. On the receiver side, the Ethernet MAC extracts the different components of a frame and transfers them to higher applications through an AXI4-Stream interface.

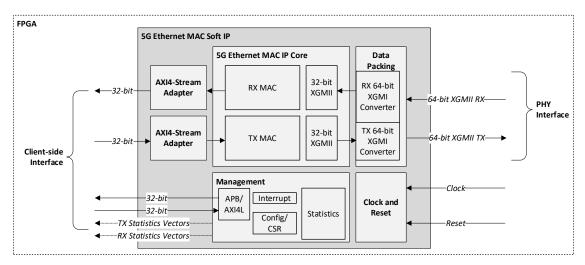

## 2.2.2. Block Diagram

Figure 2.2. 5G Ethernet MAC IP Core Block Diagram

#### 2.2.3. Ethernet Data Format

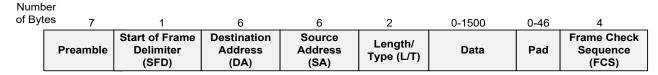

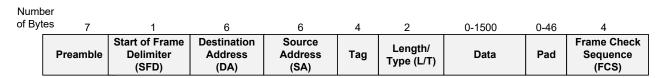

The following figure shows an untagged Ethernet frame format.

Figure 2.3. Untagged Ethernet Frame Format

The following figure shows a tagged Ethernet frame format.

Figure 2.4. Tagged Ethernet Frame Format

The MAC is responsible for constructing a valid frame from the data received from the client before transmitting it. On the receiver path, it receives frames from the network through XGMII interface and passes the parameters of the frame to the client through the AXI4-Stream interface.

The fields that are expected from the client-side interface can be one of the following:

- The frame contains the FCS along with the destination address (DA), source address (SA), length/type (L/T), and data. The TX MAC adds the preamble and start frame delimiter (SFD) before transmitting the frame. This mode can be set by enabling tx pass fcs bit in the TX CTL register. For timing details, see the In-Band FCS Passing section.

- The TX MAC calculates the number of bytes to be padded as well (if required) in addition to the FCS for the entire frame and adds the preamble and SFD before transmitting the frame. For timing details, see the Default Normal Frame section.

- When tx\_pass\_pream bit is set in the TX\_CTL register, the client supplies a custom data in the preamble and SFD field. The TX MAC preserves the preamble field and passed it directly to physical layer. This applies to both cases mentioned above. For timing details, see the Custom Preamble Passing section.

On the receiver path, the MAC can be programmed to transfer frame in one of the following cases:

- Transfer the frame after stripping off the FCS and any pad fields. This is the default settings of the RX MAC.

- Transfer the frame with the FCS field and any pad fields by setting the rx\_pass\_fc bit of RX\_CTL register.

- Transfer the frame in promiscuous mode by setting the prms bit of RX\_CTL register. This mode transfers all frames it receives to the client rather than passing only the frames that is specifically programmed to receive.

In all cases, the preamble and SFD bytes are always stripped off the frame before it is transferred on the AXI4-Stream interface unless the rx\_pass\_pream bit is set in the RX\_CTL register. When rx\_pass\_pream bit is set, the RX MAC does not check for the SFD.

#### 2.2.4. Receive MAC

The Receive MAC receives the incoming frames and transfers them to the client via the AXI4-Stream interface. In the process, it performs the following operations:

- Checks the frame for a valid start of frame (SOF) and SFD symbol. This checking is disabled when RX is configured to custom preamble mode.

- Determines whether the frame should be received by analyzing the DA.

- Determines the type of the frame by analyzing the length/type field.

- Checks for any errors in the frame by recalculating the CRC and comparing it with the expected value.

The RX MAC operation is determined by programming the MODE and RX CTL registers.

You can specify whether the FCS field should be transferred on to the AXI4-Stream interface by programming the rx\_pass\_fcs bit of RX\_CTL register. If the FCS field is to be stripped off the frame, any padding bytes within the frame are stripped off as well.

Once a valid SOF is detected, the DA field of the incoming frame is analyzed. If the DA field is a unicast address, it is compared with the programmed MAC address. Unless the prms bit of RX\_CTL register was set, the incoming frame is discarded if the DA field and the programmed MAC address (MAC\_ADDR\_{0,1} registers) do not match. If the frame had a multicast address and if receive\_all\_mc signal is not asserted, all such frames are dropped (except PAUSE frames). If the frame had a multicast address and if receive\_all\_mc signal is asserted, the multicast frames are subject to the following address filtering rules:

• For all frames with multicast address, the CRC of the destination address is computed and the mid-six bits of the least significant byte of the CRC is chosen as the address to a hash table. The 64-bit hash table is programmed in the MC\_TABLE\_{0,1} registers. The MAC implements an eight-row table with eight bits in each row. The lower three bits of the selected CRC are used to select one of these eight rows and the next three bits are used to select one of the bits in the selected table. The incoming multicast frame is accepted if the bit selected from the hash table is set to one. It is discarded if the bit selected is zero.

If the incoming frame had a broadcast address, it is accepted if either the prms or the receive\_bc bit of RX\_CTL register is set. A broadcast frame is discarded if none of these bits are set.

## 2.2.5. Transmit MAC

The Transmit MAC controls access to the physical medium. Its main functions are as follow:

- Data padding for short frames when FCS generation is enabled.

- Generation of a pause frame when the tx\_pausreq bit of MAC\_CTL register is asserted. The bit tx\_fc\_en of TX\_CTL register should be set to 1 to enable this feature.

- To stop frame transmission when a pause frame is received by the Receive MAC.

- Implement link fault signaling logic and transmit appropriate sequences based on the remote link status of the TX\_RX\_STS register.

The TX MAC operation is determined by programming the MODE and TX\_CTL registers.

By default, the Transmit MAC is configured to generate the FCS pattern for the frame to be transmitted. However, this can be prevented by setting tx\_pass\_fcs bit of the TX\_CTL register. This feature is useful if the frames being presented for transmission already contain the FCS field. When FCS field generation by the MAC is disabled, ensure that short frames are properly padded before the FCS is generated. If the MAC receives a frame to transmit that is shorter than 64 bytes when FCS generation is disabled, the frame is sent as is and a statistic vector for the condition is generated.

The DA, SA, L/T, and data fields are derived from higher applications through the AXI4-Stream interface and then encapsulated into an un-tagged Ethernet frame. The frame encapsulation consists of adding the preamble bits, the SFD bits, and the CRC check sum to the end of the frame. If transmit\_short bit of TX\_CTL register is not set, all short frames are padded.

The frame is not sent over the network until the network has been idle for a minimum of Inter-Packet Gap (IPG) of 12 bytes. The IPG is adjustable through the tx\_ipg field of the IPG\_VAL register. The Transmit MAC uses DIC to reach an average IPG of 8 bytes + (tx\_ipg x 4 bytes). With the default tx\_ipg value of 1, the Transmit MAC aims for an average IPG of 12 bytes. For more information on DIC, refer to the IEEE 802.3-2022 Section 46.

The TX MAC requires a continuous stream of data for the entire frame. There cannot be any bubbles of no data transfer within a frame. After the TX MAC is done transmitting a frame, it waits for more frames from the AXI4-Stream interface. During this time, it goes to an idle state that can be detected by reading the TX\_RX\_STS register. Because the MODE register can be written at any time, the TX MAC can be disabled while it is actively transmitting a frame. In such cases, the MAC completely transmits the current frame and then return to the idle state. The control registers should be programmed only after the MAC has returned to the IDLE state.

There are two different methods for transmitting a pause frame. In the first method, the application layer forms a pause frame and submits it for transmission via the AXI4-Stream interface. In the other method, the application layer signals the TX MAC directly to transmit a pause frame. This is accomplished by asserting tx\_pausreq bit of MAC\_CTL register. In this case, the TX MAC completes the transmission of the current packet and then transmit a pause frame with the pause time value supplied through the tx\_paustim bits of the PAUSE\_TMR register.

#### 2.2.6. Receive AXI4-Stream Interface

The receive client-side interface supports the AXI4-Stream interface.

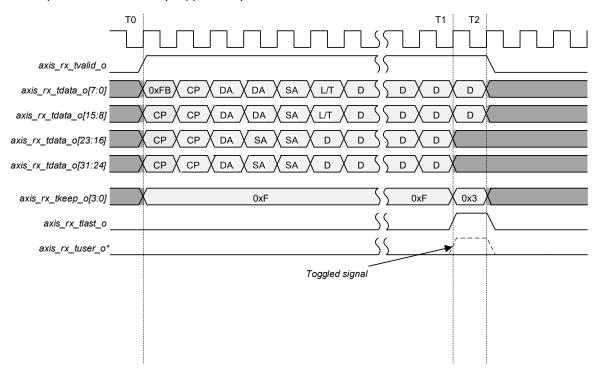

Figure 2.5. AXI4-Stream RX Adapter Interface Diagram

#### 2.2.6.1. Default Normal Frame

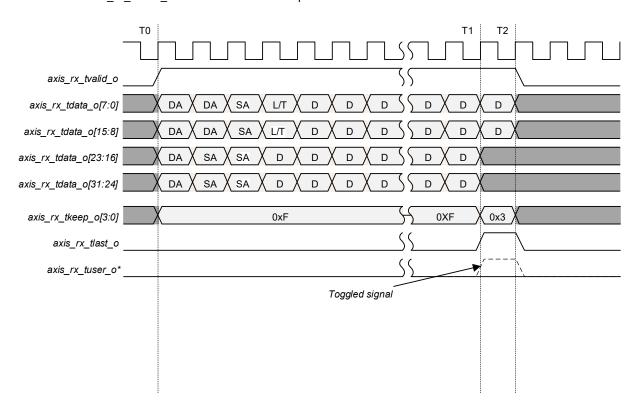

The following figure shows the timing diagram of a default normal frame at the Receive AXI4-Stream interface:

- T0: MAC asserts axis\_rx\_tvalid\_o to indicate start of frame. The valid packet includes from the DA field up to the end of the data field.

- T1: MAC asserts axis\_rx\_tlast\_o to indicate last packet transfer.

- T2: MAC deasserts axis\_rx\_tvalid\_o when there is no next packet transfer.

Figure 2.6. Normal Frame Reception

<sup>\*</sup> Note: Under normal circumstances, the axis\_rx\_tuser\_o signal must not be toggled when there is no error. However, if an error occurs and the axis\_rx\_tuser\_o signal is toggled, you must check on the status signal—rx\_statvec\_o signal.

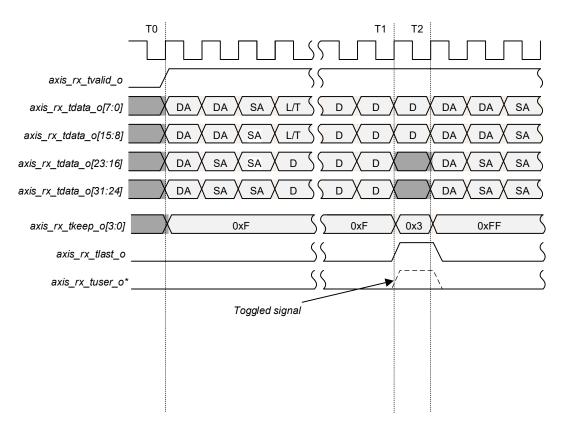

The following figure shows the timing diagram of a back-to-back frame at the Receive AXI4-Stream interface:

- T0: MAC asserts axis\_rx\_tvalid\_o to indicate start of frame. The valid packet starts from the DA field up to the end of the data field.

- T1: MAC asserts axis rx tlast o to indicate last packet transfer.

- T2: MAC still asserts the axis\_rx\_tvalid\_o to indicate another packet transfer.

Figure 2.7. Back-to-back Frames Reception

\* Note: Under normal circumstances, the axis\_rx\_tuser\_o signal must not be toggled when there is no error. However, if an error occurs and the axis\_rx\_tuser\_o signal is toggled, you must check on the status signal—rx\_statvec\_o signal.

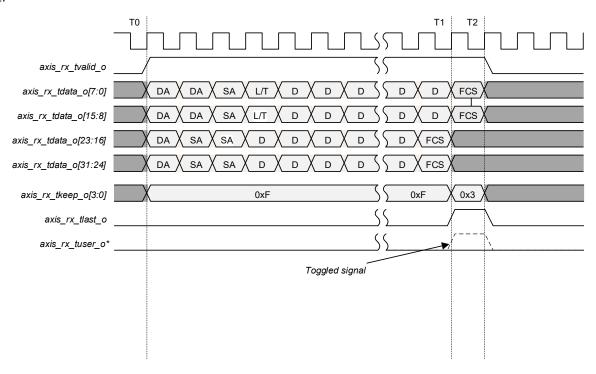

#### 2.2.6.2. In-Band FCS Passing

The following figure shows the timing diagram of a frame with in-band FCS. The FCS field is included inside the valid frame.

Figure 2.8. Frame Reception with In-Band FCS Passing

<sup>\*</sup> Note: Under normal circumstances, the axis\_rx\_tuser\_o signal must not be toggled when there is no error. However, if an error occurs and the axis\_rx\_tuser\_o signal is toggled, you must check on the status signal—rx\_statvec\_o signal.

#### 2.2.6.3. Custom Preamble Passing

The following figure shows the timing diagram of a frame with custom preamble mode enabled. A custom preamble (CP) field is included inside the valid frame.

**Note**: Custom preamble mode is only supported by XGMII interface.

Figure 2.9. Reception with Custom Preamble

#### 2.2.7. Transmit AXI4-Stream Interface

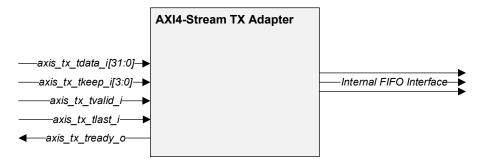

The transmit client-side interface supports the AXI4-Stream interface.

Figure 2.10. AXI4-Stream TX Adapter Interface Diagram

<sup>\*</sup> Note: Under normal circumstances, the axis\_rx\_tuser\_o signal must not be toggled when there is no error. However, if an error occurs and the axis\_rx\_tuser\_o signal is toggled, you must check on the status signal—rx\_statvec\_o signal.

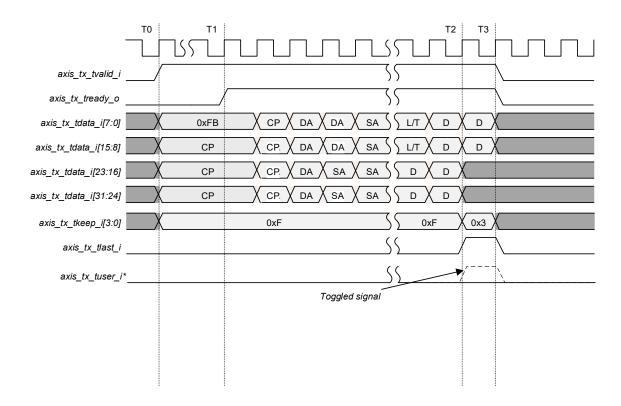

#### 2.2.7.1. Default Normal Frame

The following figure shows the timing diagram of a default normal frame at the Transmit AXI4-Stream interface:

- T0: Client asserts axis\_tx\_tvalid\_i to indicate the start of packet transfer. It must hold the data and axis\_tx\_tvalid\_i until axis\_tx\_tready\_o asserts.

- T1: Client continues to send data once it sees axis tx tready o asserted.

- T2: Client asserts axis\_tx\_tlast\_i to indicate last packet transfer.

- T3: Client deasserts axis\_tx\_tvalid\_i when there is no packet transfer. Transmit MAC also deasserts axis\_tx\_tready\_o once it sees the last packet transfer (axis\_tx\_tlast\_i = 1).

Figure 2.11. Default Normal Frame Transmission

\* Note: You can inject the error by asserting the axis\_tx\_tuser\_i signal during EOP. Otherwise, the axis\_tx\_tuser\_i signal must drive to low.

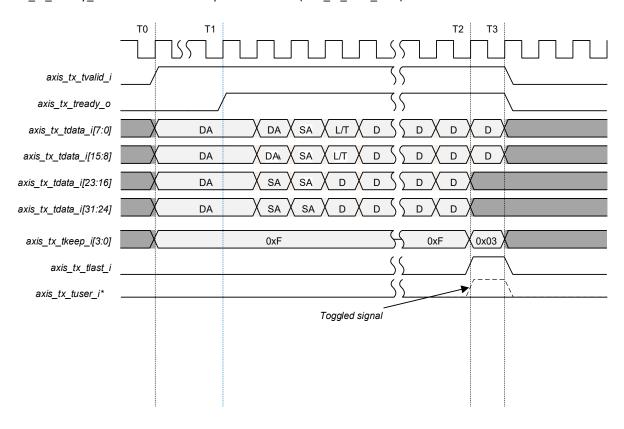

#### 2.2.7.2. In-Band FCS Passing

The following figure shows the timing diagram of a frame when In-Band FCS passing is enabled.

Figure 2.12. Transmission with In-Band FCS Passing

<sup>\*</sup> Note: You can inject the error by asserting the axis\_tx\_tuser\_i signal during EOP. Otherwise, the axis\_tx\_tuser\_i signal must drive to low.

#### 2.2.7.3. Custom Preamble Passing

The following figure shows the timing diagram of a frame when custom preamble passing is enabled. **Note**: Custom preamble mode is only supported by XGMII interface.

Figure 2.13. Transmission with Custom Preamble Passing

\* Note: You can inject the error by asserting the axis\_tx\_tuser\_i signal during EOP. Otherwise, the axis\_tx\_tuser\_i signal must drive to low.

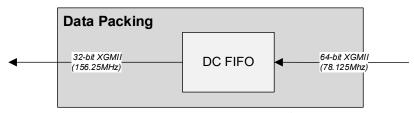

## 2.2.8. Data Unpacking

This module converts between 64-bit XGMII and 32-bit XGMII interfaces.

Figure 2.14. Receive Physical Interface for 8/6-bit GMII or MII

The receiver side takes the 64-bit XGMII from PHY and convert into 32-XGMII packets. The transformation process involves clock crossing from 64-bit XGMII at 78.125 MHz to 32-bit XGMII at 156.25 MHz by using a DC FIFO block.

Figure 2.15. Transmit Physical Interface for 8/16-bit GMII or MII

The Data Unpacking block converts the 32-bit XGMII data to 64-bit XGMII through the DC FIFO block. This module also include clock crossing from 156.25 MHz to 78.125 MHz handling.

## 2.2.9. MAC Management Block

The MAC Management block is accessed through the APB interface. This block is responsible for the following:

- Configuration of the core

- Access to interrupt block

- Access to statistics counter

The various events that occur during the reception of a frame are also logged into the statistics vector signals (rx\_statvec\_o) and the TX\_RX\_STS register. At the end of reception, the rx\_staten\_o signal is asserted to qualify the rx\_statvec\_o signal. A vector is not generated for all those frames that are discarded (no address match or frame length is less than 64 bytes) or ignored (you assert the ignore\_pkt of MAC\_CTL register). For every frame transmitted, a statistics vector signals (tx\_statvec\_o) is generated, including all the statistical information collected in the process of transmitting the frame. Data on tx\_statvec\_o is qualified by assertion of the tx\_staten\_o signal. These statistics can also be accessed in the statistics counter when the *Statistics Counter Register* attribute is enabled.

For the timing details of the AMBA 3 APB protocol, refer to the AMBA 3 APB Protocol version 1.0 Specification.

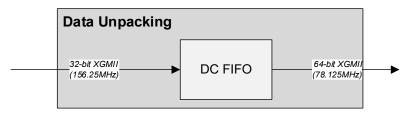

## 2.3. PHY

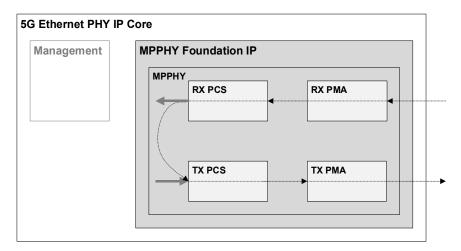

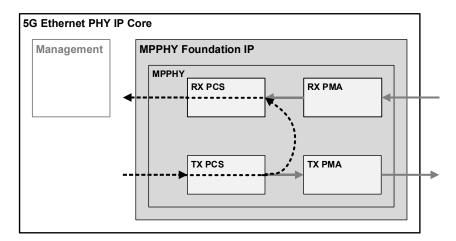

### 2.3.1. IP Architecture Overview

The 5G Ethernet PHY IP core provides the XGMII interface to the MAC and follows the IEEE 802.3 5GBASE-R standard. It supports 64 bits of data and 8 bits of control signals for both the transmit and receive paths.

This IP core instantiates the MPPHY foundation IP configured as 1-Lane 64b/66b PCS and a Management block that supports AXI4-Lite, or APB access to PCS registers. For more information on MPPHY foundation IP, refer to the Lattice Avant SERDES/PCS User Guide (FPGA-TN-02313).

The functional description in this section is only applicable for 5G Ethernet PHY IP core on Avant-AT-G and Avant-AT-X devices.

## 2.3.2. Block Diagram

The following figure shows the top-level block diagram of the 5G Ethernet PHY IP core.

Figure 2.16. 5G Ethernet PHY IP Core Block Diagram

## 2.3.3. Lane Merging

#### 2.3.3.1. Overview

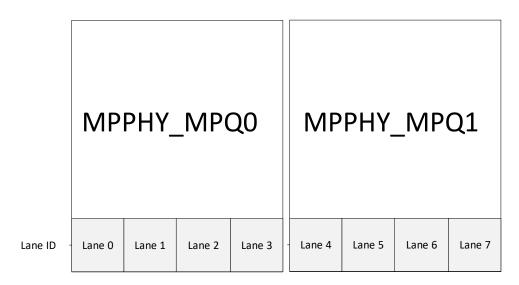

The Avant-AT-G/X silicon can have up to seven usable quads, depending on the package. Each MPPHY block is a quad made up of four lanes (X4). Therefore, a single device could theoretically contain up to 28 lanes across seven quads.

You can configure the quad to use each lane individually, enabling you to merge multiple MPPHY instances into a single physical quad. This maximizes the usage of silicon resources in your design.

**Note:** Lane merging is only supported by Avant devices. For more information, refer to the Lattice Avant-G/X MPPHY Module User Guide (FPGA-IPUG-02233).

#### 2.3.3.2. Usage

The 5G Ethernet PHY IP core instantiates the MPPHY foundation IP configured with a 1X1 link width, which occupies a single lane of a quad. By default, the Radiant software attempts to merge MPPHY instances to minimize the device power consumption.

If you want to override this behavior and select specific locations for the MPPHY instances, you can set the LANE ID configuration of the IP according to the number of quads you want to use.

To set the Lane ID, follow these steps:

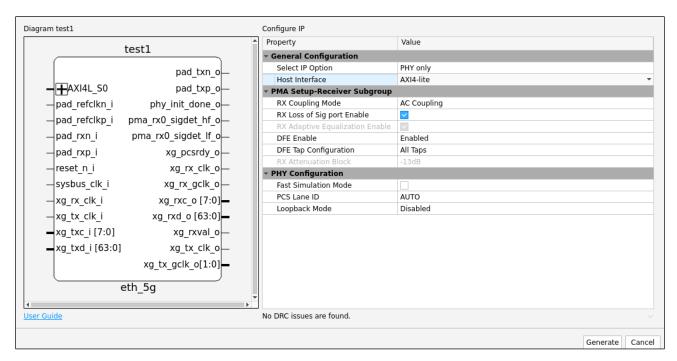

- 1. In the Select IP Option field, select PHY only or MAC + PHY.

- 2. In the PCS Lane ID field, set the lane ID configuration of the IP as shown in the figure below. By default the ID is set to **AUTO**. If the ID is not set to **AUTO**, in the case of a conflict between the Lane ID configuration and a top-level design port constraint, the top-level design port constraint takes precedence, which means the Lane ID setting is ignored and a warning message is shown.

Figure 2.17. Set the Lane ID Configuration of the 5G Ethernet PHY IP Core

The Lane ID value is global for the entire device, starting at 0 from Lane 0 of the left-most quad, then incrementing up to 27 for Lane 3 of the right-most quad for the largest package of LAV-AT-G/X70. An example of Lane ID numbering is shown in the figure below.

Figure 2.18. Lane ID Numbering

#### 2.3.3.3. Lane Merging Report

During lane merging, the Post-Synthesis process produces a report file named *mpphy\_lane\_assignment.mrf* in the project's active implementation folder that shows how the MPPHY design instances were merged into the device MPPHY quads. You can open the report file with any text editor.

Figure 2.19. Lane Merging Report File

#### 2.3.3.4. Restriction and Limitations

To merge instances into the same quad, instances must abide by the following restrictions:

- Shared reference clock connection.

- Shared LMMI clock and reset connections.

- Compatible PLL settings (this is protocol/data rate dependent, and will be configured by the IP Catalog tool)

- Compatible "per-quad" connections a limited number of ports exposed on the MPPHY IP physically have only a

single instance on the silicon. These must be connected to the same net if it is an input, or have a maximum of one

connected per-quad if it is an output.

The table below shows the signal mapping of the 10G Ethernet IP to MPPHY that must be shared for lane merging to work. All input must be driven by the same source.

For output clock, use only output clock from one instance of the quad to drive the logic. For output clocks from other IP instances that are merged into the same quad, do not use the clock to drive any logic. Refer to the table below.

| Table 2.1. Shared Signal Mapping of 5G Ethernet IP to MPPHY for Lane Merging |                                |           |  |  |

|------------------------------------------------------------------------------|--------------------------------|-----------|--|--|

| МРРНҮ                                                                        | 2.5G Ethernet IP               | Direction |  |  |

| lmmiclk_q0_i                                                                 | sysbus_clk_i                   | Input     |  |  |

| refclk_p_q0_i<br>refclk_n_q0_i                                               | pad_refclkp_i<br>pad_refclkn_i | Input     |  |  |

| Immireset_n_q0_i                                                             | reset_n_i                      | Input     |  |  |

| txoutgclk_pll0_q0_o                                                          | xg_tx_gclk_o[0]                | Output    |  |  |

| txoutgclk_pll1_q0_o                                                          | xg_tx_gclk_o[1]                | Output    |  |  |

Table 2.1. Shared Signal Mapping of 5G Ethernet IP to MPPHY for Lane Merging

If you select AUTO lane ID, your pin location assignment must be included in sdc or ldc instead of pdc.

If any of these restrictions are violated, the Radiant software will not automatically merge the MPPHY instances into a single quad. If user constraints or lane assignment forces incompatible MPPHY instances into the same quad, an error message is issued, and the Radiant software flow will not continue past the Post-Synthesis stage.

## 2.3.4. PHY Management Block

The PHY Management block is accessed through the AXI4-Lite, or APB interface. This block is responsible for register access to the PCS registers. While all the two interfaces (AXI4-Lite, or APB) are available for PCS Module Registers

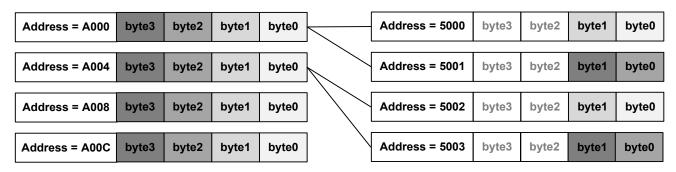

For PCS register access through AXI4-Lite, this soft IP requires the use of remapped addresses (0xA000 – 0xA0FC) as AXI4-Lite addresses must be DWORD-aligned (0xA000, 0xA004, 0xA008, 0xA00C, and so on). To get the corresponding AXI4-Lite addresses, you will need to left shift even-numbered PCS address once (or multiply by two) – the lower 2

bytes of the AXI4-Lite read/write data will be mapped to the even-numbered PCS register; while the upper 2 bytes of the AXI4-Lite read/write data will be mapped to the subsequent odd-numbered PCS register.

For details and illustrations on how the AXI4-Lite address remapping works, refer to Table 2.2 and Figure 2.20.

Note: The read/write data values used in the following illustrations are just examples and are not the suggested register values to be written. Because PCS registers are half-duplex, simultaneous write to/read from PCS registers through AXI4-Lite channels are not supported.

With APB interfaces, no address remapping is required. The actual PCS Module Registers addresses (0x5000 – 0x507F) are used.

Table 2.2. AXI4-Lite to PCS Address and Data Conversion

| axi4l_awaddr_i[31:0] / axi4l_araddr_i[31:0] | axi4l_wdata_i[31:0] /<br>axi4l_rdata_o[31:0] | PCS Register<br>Address (16-bit) | Access Types                  | PCS Register Values (16-bit)  |

|---------------------------------------------|----------------------------------------------|----------------------------------|-------------------------------|-------------------------------|

| 0×4000                                      | Ov222244EE                                   | 0x5000                           | RW                            | 0x4455 = axi4l_wdata_i[15:0]  |

| UXAUUU                                      | 0xA000 0x22334455                            |                                  | _                             | Not available                 |

| 0xA004 0xaabbccdd                           | O h b d d                                    | 0x5002                           | RW                            | 0xccdd = axi4l_wdata_i[15:0]  |

|                                             | 0x5003                                       | RW                               | 0xaabb = axi4l_wdata_i[31:16] |                               |

| 0,4000                                      | 0.11225577                                   | 0x5004                           | RW                            | 0x5577 = axi4l_wdata_i[15:0]  |

| 0xA008 0x11335577                           |                                              | 0x5005                           | RW                            | 0x1133 = axi4l_wdata_i[31:16] |

| 0.4050                                      | 0x507E                                       | RO                               | Read-only register            |                               |

| 0xA0FC 0x8899eeff                           |                                              | 0x507F                           | RW                            | 0x8899 = axi4l_wdata_i[31:16] |

Figure 2.20. Remapped Addresses for PCS Register Address through the AXI4-Lite Interface

#### 2.3.5. Loopback Modes

#### 2.3.5.1. Far End Parallel Loopback

The input signal is driven at the serial RX port (RX PMA input) and the output is observed at the serial TX port (TX PMA output). In this loopback, user logic is not involved.

Figure 2.21. Far End Parallel Loopback

#### 2.3.5.2. Near End Parallel Loopback

The input signal is driven at the parallel TX port (user logic side) and the output signal is observed at the parallel RX port (user logic side). In this loopback, PMA is not involved.

Figure 2.22. Near End Parallel Loopback

## 2.4. Clocking

## 2.4.1. Clocking Overview

The following figure shows the clock network of the 5G Ethernet IP core for Avant devices. The clock frequency requirements are described in the Signal Description section according to the configuration selected—MAC only, PHY only, or MAC+PHY. In the MAC + PHY configuration, the txmac\_clk\_i and rxmac\_clk\_i are connected internally to the output clock from the PHY block.

Figure 2.23. 5G Clock Network Diagram for Avant Devices

## **2.5.** Reset

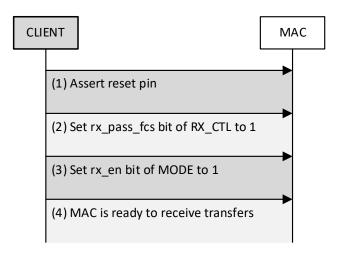

## 2.5.1. MAC Reset Sequence

#### 2.5.1.1. Reset

An asynchronous reset pin (active low) as system reset is used for resetting the 5G Ethernet IP core. Internal reset logic is implemented to guarantee synchronous deassertion all throughout the different clock domain among soft logic blocks. The minimum assertion of reset is five clock cycles of the slowest clock\*.

#### 2.5.1.2. Power Up Sequence

The following lists the sequence after power-up of the chip or system:

- 1. Assert reset pin for five clock cycles of the slowest clock\* of the system.

- 2. Wait for the 5G PHY to be in a ready state.

For more information on the sequence, see the PHY section.

- 3. Send settings through the AXI4-Lite interface to configure the system. For a list of MAC registers, refer to the Configuration Registers for MAC section.

- 4. The MAC is ready to receive transfers.

- \* Note: The fastest clock refers to the sysbus\_clk\_i with a frequency of 100 MHz.

The following figure shows a sample sequence when the RX MAC is configured to pass the FCS field to the client.

Figure 2.24. Sequence to Configure RX MAC In-Band FCS Passing

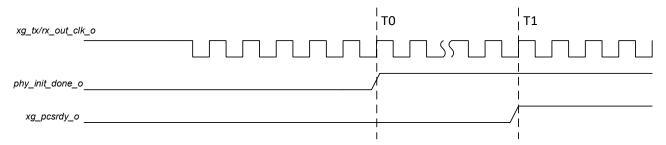

## 2.5.2. PHY Reset Sequence

## 2.5.2.1. Reset

An asynchronous reset pin (active low) as system reset is used for resetting the 5GbE PHY IP core. Internal reset logic is implemented to guarantee synchronous deassertion all throughout the different clock domain among soft logic blocks. The minimum assertion of reset is five clock cycles of the slowest clock\*.

#### 2.5.2.2. Sequence

The following lists the sequence after power-up of the chip or system:

- 1. Assert reset pin, reset\_n\_i, for five clock cycles of the slowest clock\* of the system.

- 2. Wait for phy\_init\_done\_o to assert. It is expected during this time (before T0), xg\_tx\_out\_clk\_o and xg\_tx\_out\_clk\_o are not toggling yet.

- 3. After T0, user drives continuous IDLE patterns until xg\_pcsrdy\_o asserts.

- 4. After T1, the PHY is ready to transmit data packets.

- \* Note: The fastest clock refers to the sysbus\_clk\_i with a frequency of 100 MHz.

The following figure shows the PHY initialization sequence.

Figure 2.25. PHY Initialization Sequence

## 2.6. Latency

The following table provides the measured latency information for 5G Ethernet IP.

Table 2.3. MAC + PHY Attributes

| Core      | Core Configuration | Latency (ns) | User Bus Width (bits) | Core Clock Frequency (MHz) |

|-----------|--------------------|--------------|-----------------------|----------------------------|

| MAC + PHY | 5G BASE-R TX       | 252          | 32                    | 156.25                     |

| MAC + PHY | 5G BASE-R RX       | 204          | 32                    | 156.25                     |

# 3. IP Parameter Description

The configurable attributes of the 5G Ethernet IP core are shown in the following tables. You can configure the IP core by setting the attributes accordingly in the IP Catalog's Module/IP wizard of the Lattice Radiant software.

## 3.1. MAC + PHY

The following table lists the 5G Ethernet IP core configurable attributes for the MAC + PHY option. The values set for attributes with corresponding registers serve as the maximum values and cannot be set higher during dynamic reconfiguration. Select IP Option—MAC + PHY option.

Table 3.1. MAC + PHY Attributes

| Attribute                           | Selectable Values                                             | Default   | Description                                                   | Dependency on<br>Other Attributes                      |

|-------------------------------------|---------------------------------------------------------------|-----------|---------------------------------------------------------------|--------------------------------------------------------|

| <b>General Configuration</b>        |                                                               |           |                                                               |                                                        |

| Select IP Option                    | <ul><li>MAC + PHY</li><li>PHY Only</li><li>MAC Only</li></ul> | MAC + PHY | IP option.                                                    | _                                                      |

| Host Interface                      | <ul><li>AXI4-Lite</li><li>APB</li></ul>                       | AXI4-Lite | Set the register interface.                                   | _                                                      |

| MAC Configuration                   |                                                               |           |                                                               |                                                        |

| Multicast Address Filtering         | <ul><li>Enabled</li><li>Disabled</li></ul>                    | Disabled  | Enables or disables address filtering for multicast frames.   | Enabled when Select IP Option == MAC Only or MAC + PHY |

| TX Pause Frame Generation via Ports | <ul><li>Enabled</li><li>Disabled</li></ul>                    | Disabled  | Enables or disables TX pause frame generation via ports.      | Enabled when Select IP Option == MAC Only or MAC + PHY |

| Statistics Counter Configurati      | on                                                            |           |                                                               |                                                        |

| Statistic Counter Registers         | <ul><li>Enabled</li><li>Disabled</li></ul>                    | Disabled  | Enables or disables statistics counter registers              | Enabled when Select IP Option == MAC Only or MAC + PHY |

| Counter Width                       | • 32<br>• 64                                                  | 32        | Statistics<br>counters register<br>size.                      | Enabled when Select IP Option == MAC Only or MAC + PHY |

| TX Statistics                       | <ul><li>Enabled</li><li>Disabled</li></ul>                    | Disabled  | TX statistics.                                                | Enabled when Select IP Option == MAC Only or MAC + PHY |

| RX Statistics                       | <ul><li>Enabled</li><li>Disabled</li></ul>                    | Disabled  | RX statistics.                                                | Enabled when Select IP Option == MAC Only or MAC + PHY |

| PMA Setup-Transmitter Subg          | roup (default values are rec                                  | ommended) |                                                               |                                                        |

| TX Amplitude Control [0-63]         | 0-63                                                          | 24        | Transmitter amplitude adjustment control.                     | Enabled when Select IP Option == PHY Only or MAC + PHY |

| TX Pre Cursor [0-31]                | 0-31                                                          | 0         | Transmitter pre-<br>emphasis level<br>adjustment<br>control.  | Enabled when Select IP Option == PHY Only or MAC + PHY |

| TX Post Cursor [0-31]               | 0-31                                                          | 0         | Transmitter post-<br>emphasis level<br>adjustment<br>control. | Enabled when Select IP Option == PHY Only or MAC + PHY |

| Attribute                                                    | Selectable Values                                                                                                      | Default     | Description                                                                                           | Dependency on<br>Other Attributes                                                                                       |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| PMA Setup-Receiver Subgroup (default values are recommended) |                                                                                                                        |             |                                                                                                       |                                                                                                                         |  |

| RX Coupling Mode                                             | <ul><li>AC Coupling</li><li>DC Coupling</li></ul>                                                                      | AC Coupling | PMA Coupling mode.                                                                                    | Enabled when Select IP Option == PHY Only or MAC + PHY                                                                  |  |

| RX Loss of Sig port Enable                                   | <ul><li>Enabled</li><li>Disabled</li></ul>                                                                             | Enabled     | RX Loss of Sig capability.                                                                            | Enabled when Select IP Option == PHY Only or MAC + PHY                                                                  |  |

| DFE Enable                                                   | <ul><li>Enabled</li><li>Disabled</li></ul>                                                                             | Enabled     | DFE capability.                                                                                       | Enabled when Select IP Option == PHY Only or MAC + PHY                                                                  |  |

| RX Adaptive Equalization<br>Enable                           | <ul><li>Enabled</li><li>Disabled</li></ul>                                                                             | Enabled     | RX adaptive EQ capability.                                                                            | Enabled when Select IP Option == PHY Only or MAC + PHY Selectable only when DFE Enable == Disabled                      |  |

| RX Attenuation Block                                         | <ul><li>-13dB</li><li>-2dB</li></ul>                                                                                   | -13dB       | RX Attenuation setting. Higher dB loss reflects higher capability of the RX to handle a lossy signal. | Enabled when Select IP Option == PHY Only or MAC + PHY Selectable only when RX Adaptive Equalization Enable == Disabled |  |

| PHY Configuration                                            |                                                                                                                        | l           |                                                                                                       | I                                                                                                                       |  |

| Fast Simulation Mode                                         | Enabled     Disabled                                                                                                   | Disabled    | Enables or disables the fast sim mode.                                                                | Enabled when Select IP Option == PHY Only or MAC + PHY                                                                  |  |

| PCS Lane ID                                                  | • AUTO<br>• 0-27                                                                                                       | AUTO        | Specifies the Lane ID.                                                                                | Enabled when Select IP Option == PHY Only or MAC + PHY                                                                  |  |

| Loopback Mode                                                | <ul> <li>Far End Parallel         Loopback</li> <li>Near End Parallel         Loopback</li> <li>No Loopback</li> </ul> | No Loopback | Enables the Far End Parallel Loopback or Near End Parallel Loopback or No Loopback.                   | Enabled when Select IP Option == PHY Only or MAC + PHY                                                                  |  |

# 3.2. MAC Only

The following table lists the 5Gb Ethernet IP core configurable attributes for the *MAC Only* option. The values set for attributes with corresponding registers serves as the maximum values and cannot set higher than these values during dynamic reconfiguration. Select IP Option—*MAC Only* option.

**Table 3.2. MAC Only Attributes**

| Attribute             | Selectable Values                                             | Default   | Description                 | Dependency on<br>Other Attributes |

|-----------------------|---------------------------------------------------------------|-----------|-----------------------------|-----------------------------------|

| General Configuration |                                                               |           |                             |                                   |

| Select IP Option      | <ul><li>MAC + PHY</li><li>PHY Only</li><li>MAC Only</li></ul> | MAC + PHY | IP option.                  | _                                 |

| Host Interface        | AXI4-Lite     APB                                             | AXI4-Lite | Set the register interface. | _                                 |

| Attribute                             | Selectable Values                          | Default  | Description                                                 | Dependency on<br>Other Attributes                      |

|---------------------------------------|--------------------------------------------|----------|-------------------------------------------------------------|--------------------------------------------------------|

| MAC Configuration                     |                                            |          |                                                             |                                                        |

| Multicast Address Filtering           | <ul><li>Enabled</li><li>Disabled</li></ul> | Disabled | Enables or disables address filtering for Multicast frames. | Enabled when Select IP Option == MAC Only or MAC + PHY |

| TX Pause Frame Generation via Ports   | <ul><li>Enabled</li><li>Disabled</li></ul> | Disabled | Enables or disables TX pause frame generation via ports.    | Enabled when Select IP Option == MAC Only or MAC + PHY |

| <b>Statistics Counter Configurati</b> | on                                         |          |                                                             |                                                        |

| Statistics Counter Registers          | <ul><li>Enabled</li><li>Disabled</li></ul> | Disabled | Enables or disables statistics counter registers.           | Enabled when Select IP Option == MAC Only or MAC + PHY |

| Counter Width                         | <ul><li>32</li><li>64</li></ul>            | 32       | Statistics<br>counters register<br>size.                    | Enabled when Select IP Option == MAC Only or MAC + PHY |

| TX Statistics                         | <ul><li>Enabled</li><li>Disabled</li></ul> | Disabled | TX statistics.                                              | Enabled when Select IP Option == MAC Only or MAC + PHY |

| RX Statistics                         | <ul><li>Enabled</li><li>Disabled</li></ul> | Disabled | RX statistics.                                              | Enabled when Select IP Option == MAC Only or MAC + PHY |

## 3.3. PHY Only

The following table lists the 5G Ethernet IP core configurable attributes for the *PHY Only* option in Avant devices. Select IP Option—*PHY Only* option.

**Table 3.3. PHY Only Attributes**

| Attribute                  | Selectable Values             | Default     | Description      | Dependency on Other<br>Attributes  |

|----------------------------|-------------------------------|-------------|------------------|------------------------------------|

| General Configuration      |                               |             |                  |                                    |

| Select IP Option           | • MAC + PHY                   | MAC + PHY   | IP option.       | _                                  |

|                            | <ul> <li>PHY Only</li> </ul>  |             |                  |                                    |

|                            | <ul> <li>MAC Only</li> </ul>  |             |                  |                                    |

| Host Interface             | <ul> <li>AXI4-Lite</li> </ul> | AXI4-Lite   | Set the register | _                                  |

|                            | • APB                         |             | interface.       |                                    |

| PMA Setup-Receiver Subgrou | up (default values are recon  | nmended)    |                  |                                    |

| RX Coupling Mode           | AC Coupling                   | AC Coupling | PMA Coupling     | Enabled when Select IP             |

|                            | DC Coupling                   |             | mode.            | Option == PHY Only or<br>MAC + PHY |

| RX Loss of Sig port Enable | • Enabled                     | Enabled     | RX Loss of Sig   | Enabled when Select IP             |

|                            | • Disabled                    |             | capability.      | Option == PHY Only or<br>MAC + PHY |

| DFE Enable                 | • Enabled                     | Enabled     | DFE capability.  | Enabled when Select IP             |

|                            | • Disabled                    |             |                  | Option == PHY Only or<br>MAC + PHY |

| RX Adaptive Equalization   | • Enabled                     | Enabled     | RX adaptive EQ   | Enabled when Select IP             |

| Enable                     | <ul> <li>Disabled</li> </ul>  |             | capability.      | Option == PHY Only or              |

|                            |                               |             |                  | MAC + PHY                          |

|                            |                               |             |                  | Selectable only when               |

|                            |                               |             |                  | DFE Enable ==                      |

| Attribute            | Selectable Values                                                                | Default     | Description                                                                                                            | Dependency on Other Attributes                                                                                          |

|----------------------|----------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                  |             |                                                                                                                        | Disabled                                                                                                                |

| RX Attenuation Block | • -13dB<br>• -2dB                                                                | -13dB       | RX Attenuation<br>setting. Higher dB<br>loss reflects<br>higher capability<br>of the RX to<br>handle a lossy<br>signal | Enabled when Select IP Option == PHY Only or MAC + PHY Selectable only when RX Adaptive Equalization Enable == Disabled |

| PHY Configuration    |                                                                                  |             | ·                                                                                                                      |                                                                                                                         |

| Fast Simulation Mode | <ul><li>Enabled</li><li>Disabled</li></ul>                                       | Disabled    | Enables or<br>disables the fast<br>sim mode                                                                            | Enabled when Select IP<br>Option == PHY Only or<br>MAC + PHY                                                            |

| PCS Lane ID          | For Avant-AT-G/X devices:  • AUTO • 0-27                                         | AUTO        | Specifies the Lane ID.                                                                                                 | Enabled when Select IP<br>Option == PHY Only or<br>MAC + PHY                                                            |

| Loopback Mode        | Far End Parallel     Loopback     Near End Parallel     Loopback     No Loopback | No Loopback | Enables the Far End Parallel Loopback or Near End Parallel Loopback or No Loopback.                                    | Enabled when Select IP<br>Option == PHY Only or<br>MAC + PHY                                                            |

# 4. Signal Description

This section describes the 5G Ethernet IP core ports.

# 4.1. MAC + PHY Signals

Table 4.1. Signal Description—MAC + PHY

| Port Name              | Clock Domain                          | 1/0 | Width | Description                                                                                                                                                                                                                                                   |  |  |

|------------------------|---------------------------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|