# Mailbox IP – Lattice Propel Builder 2025.2

IP Version: v1.0.0

# **User Guide**

FPGA-IPUG-02306-1.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| C  | ontents .  |                                             | 3  |

|----|------------|---------------------------------------------|----|

| Αl | bbreviati  | ons in This Document                        | 5  |

| 1. | Intro      | duction                                     | 6  |

|    | 1.1.       | Quick Facts                                 | 6  |

|    | 1.2.       | Features                                    | 6  |

|    | 1.3.       | Conventions                                 | 6  |

|    | 1.3.1.     | Nomenclature                                | 6  |

|    | 1.3.2.     | Signal Names                                | 6  |

|    | 1.4.       | Licensing and Ordering Information          | 6  |

| 2. | Funct      | ional Descriptions                          | 7  |

|    | 2.1.       | Overview                                    |    |

|    | 2.2.       | Modules Description                         | 8  |

|    | 2.2.1.     | Bus Interface                               | 8  |

|    | 2.2.2.     |                                             |    |

|    | 2.3.       | Signal Description                          | 9  |

|    | 2.3.1.     |                                             | _  |

|    | 2.3.2.     |                                             |    |

|    | 2.3.3.     |                                             |    |

|    | 2.3.4.     | ·                                           |    |

|    |            | Attribute Summary                           |    |

| 3. |            | ox IP Generation                            |    |

| 4. | Exam       | ple Design                                  |    |

|    | 4.1.       | Supported Configuration                     |    |

|    | 4.2.       | Overview of the Example Design and Features |    |

|    | 4.3.       | Generating the Example Design               |    |

|    | 4.4.       | Running the Example Design                  |    |

|    | 4.4.1.     | 0 - F                                       |    |

|    | 4.4.2.     |                                             |    |

|    | 4.4.3.     | 1 - 8                                       |    |

|    |            | A. Resource Utilization                     |    |

|    |            | S                                           |    |

| Te | echnical S | Support Assistance                          | 28 |

| Re | evision H  | istory                                      | 29 |

# **Figures**

| Figure 3.1. Entering Component Name                                                 |    |

|-------------------------------------------------------------------------------------|----|

|                                                                                     | 11 |

| Figure 3.2. Configuring Parameters                                                  | 11 |

| Figure 3.3. Verifying Results                                                       | 12 |

| Figure 3.4. Specifying Instance Name                                                | 12 |

| Figure 3.5. Generated Instance                                                      | 12 |

| Figure 4.1. RISC-V MC Multi-Processor Project with Mailbox IP Block Diagram         | 14 |

| Figure 4.2. Lattice Propel Builder – Create New SoC Design                          | 15 |

| Figure 4.3. Create Project – Design Information                                     | 15 |

| Figure 4.4. Select Template – RISC-V MC Multi-Processor Project                     |    |

| Figure 4.5. Select Target Device – Avant-E Evaluation (ES1)                         | 16 |

| Figure 4.6. Lattice Propel Builder – Generate SoC Design                            |    |

| Figure 4.7. Lattice Propel SDK – Select Workspace and Launch                        |    |

| Figure 4.8. Lattice Propel SDK – Create New C/C++ Project                           |    |

| Figure 4.9. Load System and BSP – Select cpu0_inst                                  | 19 |

| Figure 4.10. Lattice Propel SDK – Build All Projects                                |    |

| Figure 4.11. File Explorer – .mem Files for Each CPU Project                        |    |

| Figure 4.12. Lattice Propel Builder – Initialize System Memory with .mem Files      |    |

| Figure 4.13. Lattice Propel Builder – Regenerate Design After Memory Initialization |    |

| Figure 4.14. Launch Lattice Radiant – Compile Design                                |    |

| Figure 4.15. Launching Radiant Programmer                                           |    |

| Figure 4.16. Lattice Radiant Programmer – Device and Bitstream Configuration        |    |

| Figure 4.17. Cable Setup – Detecting Cable                                          | 24 |

| Figure 4.18. Select Cable – FTUSB-0 Option                                          |    |

| Figure 4.19. Output Console – Programming the FPGA Bitstream                        |    |

| Figure 4.20. UART Terminal – Expected Output Messages                               |    |

|                                                                                     |    |

| Tables                                                                              |    |

| Table 1.1. Mailbox IP Quick Facts                                                   | 6  |

| Table 2.1. Register Memory Map                                                      | 8  |

| Table 2.2. Clock and Reset Ports                                                    | 9  |

| Table 2.3. AXI-Lite Subordinate Ports                                               | 9  |

| Table 2.4. AHB-Lite Subordinate Ports                                               | 10 |

| Table 2.5. Interrupt Ports                                                          | 10 |

| Table 2.6. Configurable Attributes                                                  |    |

| Table 2.7. Attributes Description                                                   |    |

| Table 4.1. Mailbox IP Configuration Used in Example Design                          |    |

| Table 4.2. Load System and BSP – Select Remaining CPUs                              |    |

|                                                                                     |    |

| Table 4.3. Initialize System Memory with .mem Files                                 |    |

| Table 4.3. Initialize System Memory with .mem Files                                 |    |

5

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation             | Definition                                                  |  |  |

|--------------------------|-------------------------------------------------------------|--|--|

| AXI-Lite                 | Advanced eXtensible Interface – Lite                        |  |  |

| AHB-Lite                 | Advanced High-Performance Bus – Lite                        |  |  |

| APB                      | Advanced Peripheral Bus                                     |  |  |

| CPU                      | Central Processing Unit                                     |  |  |

| EBR                      | Embedded Block RAM                                          |  |  |

| FIFO                     | First In First Out                                          |  |  |

| FPGA                     | Field Programmable Gate Array                               |  |  |

| GPIO                     | General Purpose Input/Output                                |  |  |

| GUI                      | Graphic User Interface                                      |  |  |

| HDL                      | Hardware Description Language                               |  |  |

| IOPMP                    | I/O Physical Memory Protection                              |  |  |

| IP Intellectual Property |                                                             |  |  |

| IRQ Interrupt Request    |                                                             |  |  |

| LUT Look Up Table        |                                                             |  |  |

| MC                       | Micro-Controller (RISC-V for Micro-Controller applications) |  |  |

| PIC                      | Programmable Interrupt Controller                           |  |  |

| RAM                      | Random Access Memory                                        |  |  |

| RISC-V                   | Reduced Instruction Set Computer-V (Five)                   |  |  |

| SoC                      | System-on-Chip                                              |  |  |

| UART                     | Universal Asynchronous Receiver/Transmitter                 |  |  |

| W1C                      | Write One Clear                                             |  |  |

6

### 1. Introduction

The Lattice Semiconductor Mailbox IP is designed for a multi-processor environment that requires sharing data between each processor. The mailbox IP provides a bi-directional communication interface between two processors. The IP can be connected to the processor through AHB-Lite or AXI-Lite interfaces.

The Mailbox IP is implemented using Verilog HDL and it can be configured and generated using the Lattice Propel™ Builder software. The IP supports Certus™-N2, Lattice Avant™, MachXO5™-NX, CrossLinkU™-NX, CrossLink™-NX, CertusPro™-NX, and Certus-NX FPGA devices.

This document includes the description of a new example design that incorporates the Mailbox IP and can be generated using the RISC-V MC Multi-Processor Project template available in Lattice Propel 2025.2. Refer to the Example Design section for details.

### 1.1. Quick Facts

Table 1.1 presents a summary of the Mailbox IP.

Table 1.1. Mailbox IP Quick Facts

| IP Requirements        | Supported Devices         | Certus-N2, Lattice Avant, MachXO5-NX, CrossLinkU-NX, CrossLink-NX, CertusPro-NX, and Certus-NX |

|------------------------|---------------------------|------------------------------------------------------------------------------------------------|

| Resource               | Supported User Interfaces | AXI-Lite Interface and AHB-Lite Interface                                                      |

| Utilization            | Resources                 | See Table A.1 and Table A.2.                                                                   |

| Design To al           | Lattice Implementation    | IP v1.0.0 – Lattice Propel Builder 2025.2, Lattice Radiant™ Software 2025.2                    |

| Design Tool<br>Support | Simulation                | For a list of supported simulators, see the Lattice Radiant software user guide.               |

### 1.2. Features

The Mailbox IP has the following features:

- AXI-Lite interface and AHB-Lite interface

- Configurable depth of mailbox

- Configurable interrupt thresholds and maskable interrupts

#### 1.3. Conventions

### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.3.2. Signal Names

Signal Names that end with:

- \_n are active low.

- \_i are input signals.

- \_o are output signals.

- \_io are bi-directional input/output signals.

# 1.4. Licensing and Ordering Information

The Mailbox IP is provided at no additional cost with the Lattice Propel design environment. The IP can be fully evaluated in hardware without requiring an IP license string.

# 2. Functional Descriptions

### 2.1. Overview

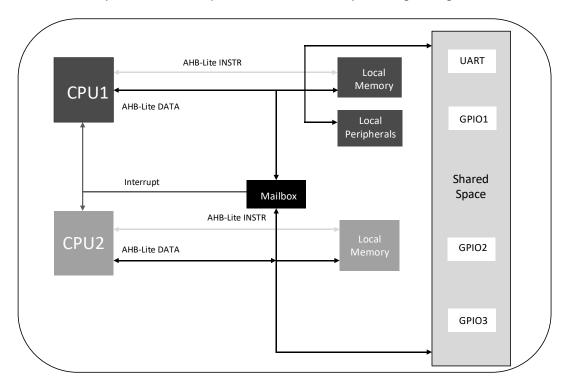

The Mailbox IP is used for multi-processor system-on-chips (SoCs) for bi-directional communication between two processors or two subsystems. Figure 2.1. Mailbox IP Diagram

shows a typical connection for the AHB-Lite system to share data between CPU1 and CPU2. You can configure the interrupt threshold and the Mailbox IP can notify the processors to start to receive data or stop sending data. The data flow is FIFO-based. You may select the FIFO implementation and FIFO depth through configurable attributes.

Figure 2.1. Mailbox IP Diagram

8

## 2.2. Modules Description

#### 2.2.1. Bus Interface

The Mailbox IP has two data bus interfaces to access internal memory-mapped registers. These interfaces need to be connected to different processors in a multi-processor system. Each interface can be configured as AXI-Lite or AHB-Lite.

### 2.2.2. Registers

- Read and Write Data Registers: Processors can send data to or receive data from these registers. The registers are FIFO-based, and the depth can be configured through attributes.

- Status Registers: Processors can access these registers to get the status of the IP.

- Interrupt Registers: Processors can handle the interrupt behaviors, such as interrupt thresholds, mask, and interrupts status through these registers.

**Table 2.1. Register Memory Map**

| Address | Register Name | Access     | Description                             | Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|---------------|------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00    | FIFO_WR       | Write-Only | Write Data address                      | [31:0] Write data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x08    | FIFO_RD       | Read-Only  | Read Data address                       | [31:0] Read data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x10    | Status        | Read-Only  | Status of Mailbox                       | <ul> <li>[31] Empty:</li> <li>0 = There is data in the Receive FIFO.</li> <li>1 = The Receive FIFO is empty.</li> <li>[30] Full:</li> <li>0 = The Send FIFO can receive more data.</li> <li>1 = The Send FIFO is full.</li> <li>[29]: Almost Full:</li> <li>0 = The Send FIFO level is greater than the WR_Thresholds.</li> <li>1 = The Send FIFO level is less or equal to the WR_Thresholds.</li> <li>[28]: Almost Empty:</li> <li>0 = The Receive FIFO level is less or equal to the RD_Thresholds.</li> <li>1 = The Receive FIFO level is greater than the RD_Thresholds.</li> </ul> |

| 0x14    | Error         | Read-Only  | Error Flags. A read clears the status.  | <ul><li>[31] Empty Error: Asserts when the processor tries to read the Empty FIFO. The read is ignored.</li><li>[30] Full Error: Assert when the processor tries to write the Full FIFO. The write is ignored.</li></ul>                                                                                                                                                                                                                                                                                                                                                                 |

| 0x18    | WR_Thresholds | Read-Write | Threshold to raise the write interrupt. | [31:0] Write Thresholds: Thresholds for the Send FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x1C    | RD_Thresholds | Read-Write | Threshold to raise the read interrupt   | [31:0] Read Thresholds: Thresholds for the Receive FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x20    | IRQ_STATUS    | Read-W1C   | Interrupt status                        | [31]: Write Threshold Interrupt: The Send FIFO level is greater than WR_Threshold. [30]: Read Threshold Interrupt: The Receive FIFO level is greater than or equal to RD_Threshold. [29]: Error Interrupt: The mailbox IP encounters a read or write error.                                                                                                                                                                                                                                                                                                                              |

| 0x24    | IRQ_ENABLE    | Read-Write | Enable each type of interrupts          | [31]: Write Threshold Interrupt Enable<br>[30]: Read Threshold Interrupt Enable<br>[29]: Error Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x28    | IRQ_PENDING   | Read-only  | Current pending interrupts.             | [31]: Write Threshold Interrupt Pending [30]: Read Threshold Interrupt Pending [29]: Error Interrupt Pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## 2.3. Signal Description

Table 2.2 to Table 2.5 list the ports of the soft IP in different categories.

### 2.3.1. Clock and Reset

**Table 2.2. Clock and Reset Ports**

| Name        | Direction | Width | Description                      |

|-------------|-----------|-------|----------------------------------|

| port0_clk   | In        | 1     | Mailbox port 0 system clock.     |

| port1_clk   | In        | 1     | Mailbox port 1 system clock.     |

| port0_rst_n | In        | 1     | Port 0 global reset, active low. |

| port1_rst_n | In        | 1     | Port 1 global reset, active low. |

### 2.3.2. AXI-Lite Interface

**Table 2.3. AXI-Lite Subordinate Ports**

| Name       | Direction | Width                                                             | Group                                     | Description               |

|------------|-----------|-------------------------------------------------------------------|-------------------------------------------|---------------------------|

| AWREADY_Sx | Out       | 1                                                                 |                                           | _                         |

| AWVALID_Sx | In        | 1                                                                 | AVIA Mandatam, Write Address Channel      | _                         |

| AWADDR_Sx  | In        | 32                                                                | AXI4 Mandatory Write Address Channel      | _                         |

| AWPROT_Sx  | In        | 3                                                                 |                                           | Not implemented.          |

| WREADY_Sx  | Out       | 1                                                                 |                                           | _                         |

| WVALID_Sx  | In        | 1                                                                 | AVIA NA and a to an all vite Bets Channel | _                         |

| WDATA_Sx   | In        | 32                                                                | AXI4 Mandatory Write Data Channel         | _                         |

| WSTRB_Sx   | In        | 4                                                                 |                                           | _                         |

| BVALID_Sx  | Out       | 1                                                                 |                                           | _                         |

|            |           |                                                                   | b'00: OKA'                                | b'00: OKAY <sup>1</sup>   |

| BRESP_Sx   | Out       | 2 AXI4 Mandatory Write Response Channel b'10: SLVERR <sup>1</sup> | b'10: SLVERR <sup>1</sup>                 |                           |

|            |           |                                                                   | b'11: DECERR <sup>1</sup> 1               | b'11: DECERR <sup>1</sup> |

| BREADY_Sx  | In        | 1                                                                 |                                           | _                         |

| ARVALID_Sx | In        | 1                                                                 |                                           | _                         |

| ARREADY_Sx | Out       | 1                                                                 |                                           | _                         |

| ARADDR_Sx  | In        | 32                                                                |                                           | _                         |

| RDATA_Sx   | Out       | 32                                                                | _                                         | _                         |

|            |           | AXI4 Mandatory Read Address Channel b'0                           | b'00: OKAY <sup>1</sup>                   |                           |

| RRESP_Sx   | Out       | 2                                                                 |                                           | b'10: SLVERR¹             |

| _          |           | b'1                                                               | b'11: DECERR <sup>1</sup>                 |                           |

| RVALID_Sx  | Out       | 1                                                                 |                                           | _                         |

| RREADY_Sx  | In        | 1                                                                 |                                           | _                         |

#### Note:

- 1. Refer to the AMBA AXI Protocol Specification for more detailed descriptions of these responses.

- 2. Sx represents the subordinate number from 0 to 7.

### 2.3.3. AHB-Lite Interface

**Table 2.4. AHB-Lite Subordinate Ports**

| Name              | Direction | Width | Description      |

|-------------------|-----------|-------|------------------|

| AHBL_Sx_HADDR     | In        | 32    | _                |

| AHBL_Sx_HWRITE    | In        | 1     | _                |

| AHBL_Sx_HSIZE     | In        | 3     | _                |

| AHBL_Sx_HPROT     | In        | 4     | Not implemented. |

| AHBL_Sx_HTRANS    | In        | 2     | _                |

| AHBL_Sx_HBURST    | In        | 3     | Not implemented. |

| AHBL_Sx_HMASTLOCK | In        | 1     | Not implemented. |

| AHBL_Sx_HWDATA    | In        | 32    | _                |

| AHBL_Sx_HRDATA    | Out       | 32    | -                |

| AHBL_Sx_HREADY    | Out       | 1     | _                |

| AHBL_Sx_HRESP     | Out       | 1     | _                |

#### Note:

- 1. Refer to the AMBA3 AHBL Protocol Specification for more detailed descriptions of these responses.

- 2. Sx represents the subordinate number from 0 to 7.

### 2.3.4. Interrupt Interface

**Table 2.5. Interrupt Ports**

| Name | Туре | Width | Description          |

|------|------|-------|----------------------|

| Irq0 | Out  | 1     | Interrupt for Port0. |

| lrq1 | Out  | 1     | Interrupt for Port1. |

### 2.4. Attribute Summary

The configurable attributes of the Mailbox IP are listed and described in Table 2.6 and Table 2.7.

The attributes can be configured through the Lattice Propel Builder software.

**Table 2.6. Configurable Attributes**

| Attribute                   | Selectable Values          | Default   | Dependency on Other Attributes |

|-----------------------------|----------------------------|-----------|--------------------------------|

| Mailbox FIFO Depth          | 16 to 8192 four-byte words | 16        | _                              |

| Mailbox FIFO Type           | EBR, Distributed-RAM       | EBR       | _                              |

| Enable Output Register      | Checked, Unchecked         | Unchecked | _                              |

| Write Threshold Reset Value | 1 to (FIFO Depth – 1)      | 15        | _                              |

| Read Threshold Reset Value  | 1 to (FIFO Depth – 1)      | 1         | _                              |

| Interface Type              | AXI-L, AHB-L               | AXI-L     | _                              |

**Table 2.7. Attributes Description**

| Attribute                   | Description                           |

|-----------------------------|---------------------------------------|

| Mailbox FIFO Depth          | Mailbox FIFO depth                    |

| Mailbox FIFO Type           | Mailbox FIFO implementation type      |

| Enable Output Register      | FIFO output register                  |

| Write Threshold Reset Value | FIFO WR_Threshold reset value         |

| Read Threshold Reset Value  | FIFO RD_Threshold reset value         |

| Interface Type              | Memory-mapped register interface type |

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

## 3. Mailbox IP Generation

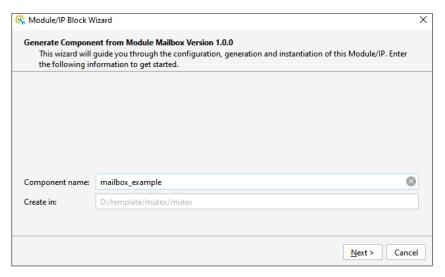

This section provides information on how to generate the Mailbox IP module using the Lattice Propel Builder software. To generate the Mailbox IP module:

- 1. In the Lattice Propel Builder software, create a new design. Select the Mailbox package.

- 2. Enter the component name. Click **Next**, as shown in Figure 3.1.

Figure 3.1. Entering Component Name

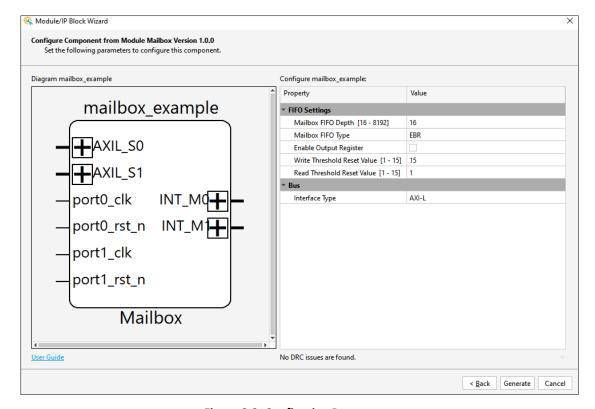

3. Configure the parameters as needed. Click Generate (Figure 3.2).

Figure 3.2. Configuring Parameters

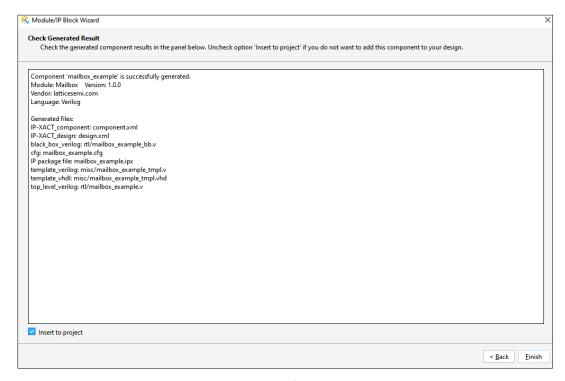

4. Verify the information. Click **Finish** (Figure 3.3).

Figure 3.3. Verifying Results

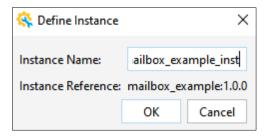

5. Confirm or modify the module instance name. Click **OK** (Figure 3.4).

Figure 3.4. Specifying Instance Name

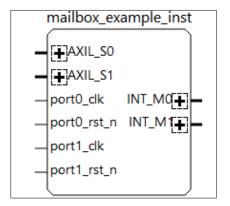

6. The Mailbox IP instance is successfully generated, as shown in Figure 3.5.

Figure 3.5. Generated Instance

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 4. Example Design

A system design that incorporates the Mailbox IP can be generated using the RISC-V MC Multi-Processor Project template available in Lattice Propel 2025.2. This design is referred to as the Example Design throughout this guide. The Example Design is documented in the accompanying README file and validated through a C code test sequence. Additional notes and explanations are provided as comments within the test code to help you understand the implementation and behavior of the Mailbox IP.

You can find the README.txt file at the following location:

<Propel Installation Path>/templates/MULTI\_PROCESSOR\_Template01/Readme.txt

This example design enables you to compile and test the Mailbox IP functionality on the following Lattice evaluation board:

Avant-E Evaluation Board

## 4.1. Supported Configuration

In the example design, the following IP configuration is applied to the Mailbox IP.

**Note**: In Table 4.1, "V" refers to a checked option for Mailbox IP in the example design and "x" refers to an unchecked option or a non-applicable option in the Mailbox IP.

Table 4.1. Mailbox IP Configuration Used in Example Design

| Mailbox IP GUI Parameter           | Mailbox IP Configuration |  |  |

|------------------------------------|--------------------------|--|--|

| FIFO Settings                      |                          |  |  |

| Mailbox FIFO Depth [16–8192]       | 32                       |  |  |

| Mailbox FIFO Type                  | EBR                      |  |  |

|                                    | mailbox01_inst: V        |  |  |

|                                    | mailbox02_inst: ×        |  |  |

| Enable Output Register             | mailbox03_inst: ×        |  |  |

|                                    | mailbox04_inst: ×        |  |  |

|                                    | mailbox05_inst: ×        |  |  |

| Write Threshold Reset Value [1–31] | 15                       |  |  |

| Read Threshold Reset Value [1–31]  | 1                        |  |  |

| Bus                                |                          |  |  |

| Interface Type                     | AHB-Lite                 |  |  |

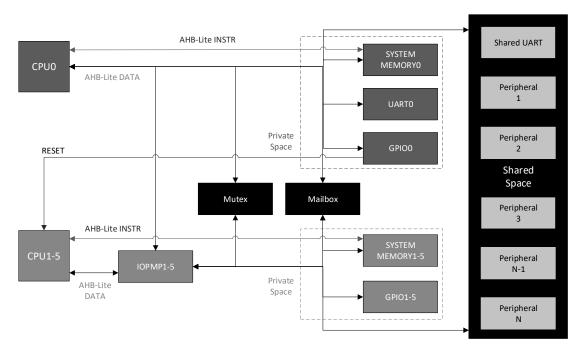

## 4.2. Overview of the Example Design and Features

The example design discussed in this section is generated using the RISC-V MC Multi-Processor Project template in the Lattice Propel Development Suite. The project generated includes the following components:

- Processor

- CPU0 (Main) RISC-V MC with PIC and timer

- CPU1-5 RISC-V MC with PIC

- AHBL to APB Bridge

- AHBL Interconnect

- APB Interconnect

- GPIO

- Mailbox

- Mutex

- IOPMP

- UART

- System Memory

This example design demonstrates the functionality of the Mailbox IP in a multi-core system.

The system comprises six CPUs, from CPU0 to CPU5. CPU0 acts as the system controller, responsible for distributing tasks to CPU1—CPU5. These worker CPUs receive their assigned tasks through the Mailbox, execute the computations independently, and then send their results and status back to CPU0 using the same Mailbox mechanism.

For status output, all CPUs share a common UART interface. To prevent concurrent access to the UART, a Mutex is employed. This ensures that only one CPU can transmit data at a time, while others wait until the Mutex is released, maintaining data integrity and avoiding conflicts.

Figure 4.1 shows the block diagram of the RISC-V MC Multi-Processor project with the Mailbox IP.

Figure 4.1. RISC-V MC Multi-Processor Project with Mailbox IP Block Diagram

Note: The block diagram does not cover all components of the example design and serves only as a guideline.

## 4.3. Generating the Example Design

The Lattice Propel Builder and Lattice Propel SDK are used to create an embedded system that includes an SoC design with an embedded processor and system software. This section outlines the procedure for generating an example design that incorporates the Mailbox IP. The hardware design is created using Lattice Propel Builder, while the software workspace is set up and managed within Lattice Propel SDK to develop, build, and deploy the corresponding firmware for each processor core.

To generate the example design:

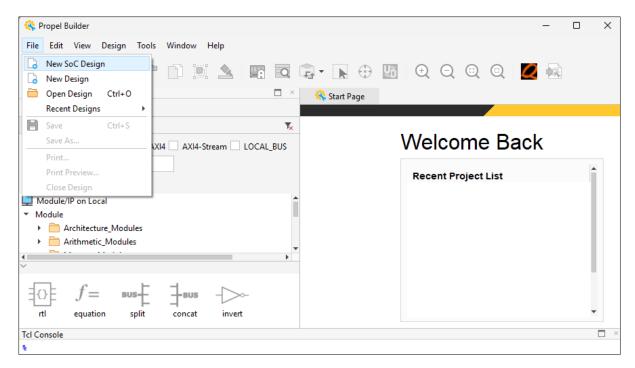

1. Launch Lattice Propel Builder.

Open the application, then navigate to File > New SoC Design, as shown in Figure 4.2.

Figure 4.2. Lattice Propel Builder - Create New SoC Design

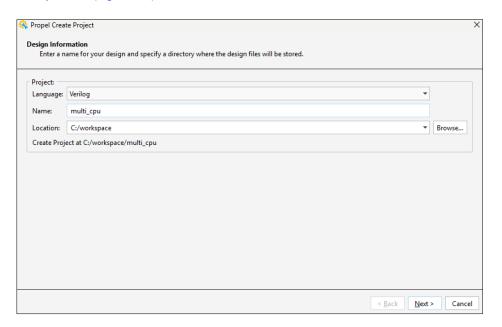

2. Enter the project Information.

In the **Create Project > Design Information** window:

- a. Enter a name for your project.

- b. Browse to select a directory for the project location.

- c. Click **Next** to proceed (Figure 4.3).

Figure 4.3. Create Project – Design Information

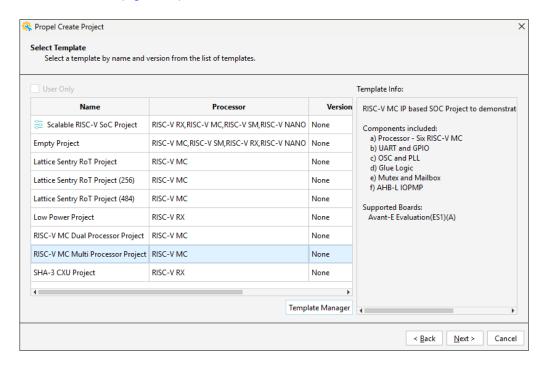

3. Select a Project Template.

In the Create Project > Select Template window:

- a. Choose RISC-V MC Multi-Processor Project from the list of available templates.

- b. Click Next to continue (Figure 4.4).

Figure 4.4. Select Template - RISC-V MC Multi-Processor Project

4. Select the Target Device.

In the Create Project > Select Device window:

- Select Avant-E Evaluation (ES1) as the target device.

- b. Click Next, then click Finish to complete the project setup (Figure 4.5).

Figure 4.5. Select Target Device – Avant-E Evaluation (ES1)

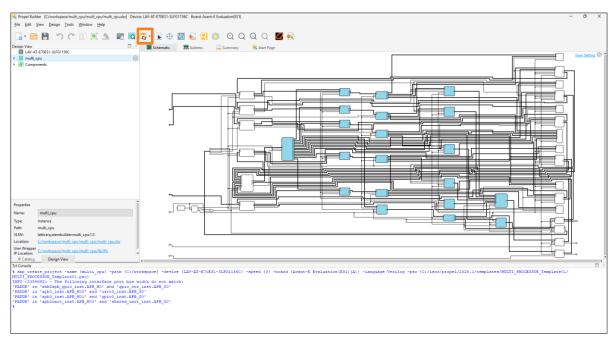

- 5. Generate the SoC design.

- a. Once the project is created, the **Lattice Propel Builder** main window opens.

- b. Click the Generate button to build the SoC design (Figure 4.6).

Note: Warnings related to TIMER\_IRQ and INT may appear. These are expected and can be safely ignored.

Figure 4.6. Lattice Propel Builder - Generate SoC Design

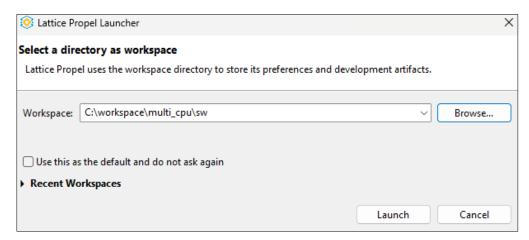

- 6. Launch Lattice Propel SDK.

- a. Open Lattice Propel SDK. The Lattice Propel Launcher window appears.

- b. Browse to select a directory for your workspace.

- c. Click Launch to open the SDK environment (Figure 4.7).

Figure 4.7. Lattice Propel SDK – Select Workspace and Launch

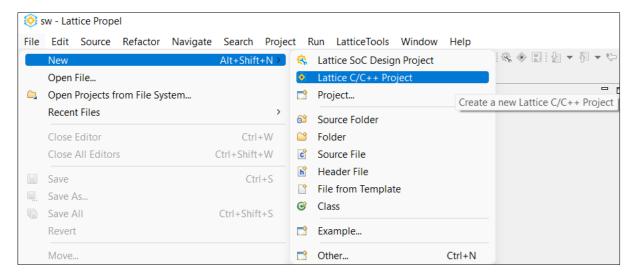

7. Create a New C/C++ Project.

In Lattice Propel SDK:

Navigate to File > New > Lattice C/C++ Project to begin creating a new software project (Figure 4.8).

Figure 4.8. Lattice Propel SDK – Create New C/C++ Project

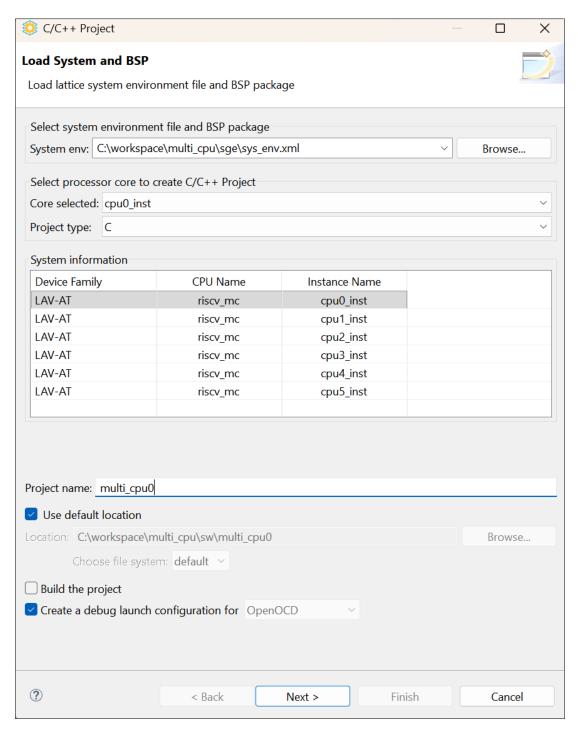

- 8. Load System and BSP Configuration.

- a. Browse to the sys\_env.xml file generated by Lattice Propel Builder, as shown in Figure 4.9.

- b. Select cpu0\_inst as the target processor.

- c. Enter a name for your project.

- d. Click **Next**. Then, click **Finish** to complete the setup.

Figure 4.9. Load System and BSP - Select cpu0\_inst

### 9. Repeat steps 7 and 8 for Remaining CPUs.

Repeat **Step 7 and Step 8** for each of the remaining CPUs, from CPU1 to CPU5. Select the corresponding processor instance, such as cpu1\_inst, cpu2\_inst, and so on during each setup, as shown in Table 4.2.

Table 4.2. Load System and BSP - Select Remaining CPUs

| Core Selected | Project Name |

|---------------|--------------|

| cpu0_inst     | multi_cpu0   |

| cpu1_inst     | multi_cpu1   |

| cpu2_inst     | multi_cpu2   |

| cpu3_inst     | multi_cpu3   |

| cpu4_inst     | multi_cpu4   |

| cpu5_inst     | multi_cpu5   |

### 10. Build all software projects.

After all CPU software projects, from CPU0 to CPU5, have been created: Navigate to **Project > Build All** to compile all projects simultaneously (Figure 4.10).

> 📀 sw - Lattice Propel File Edit Source Refactor Navigate Search Project Run LatticeTools Window Help 🗂 🕶 🔚 🐚 | 🚳 🕶 🔦 🕶 🛗 🗎 🖳 🐞 🕹 🖯 🛈 🚉 🍕 Open Project 월 ▼ 취 ▼ t> c> c> ▼ c Close Project -  $blue{}$  Project Explorer imes igwedgeBuild All □\$₹ ; **Build Configurations** > 📂 multi\_cpu0 Build All **Build Project** > 📂 multi\_cpu1 > 📂 multi\_cpu2 **Build Working Set** > 📂 multi\_cpu3 Clean... > 📂 multi\_cpu4 **Build Automatically** > 📂 multi\_cpu5 Create Lattice Application Template Update Lattice C/C++ Project...

Figure 4.10. Lattice Propel SDK - Build All Projects

C/C++ Index Properties

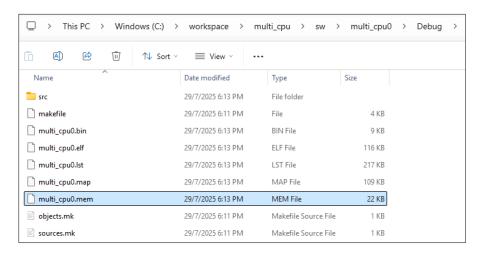

### 11. Verify the .mem file generation.

Ensure that a .mem file is generated for each project (Figure 4.11). These files should be located in the following directory: C:\workspace\multi\_cpu\sw\multi\_cpu\*\Debug

Note: \* represents CPU indices 0 through 5.

Figure 4.11. File Explorer – .mem Files for Each CPU Project

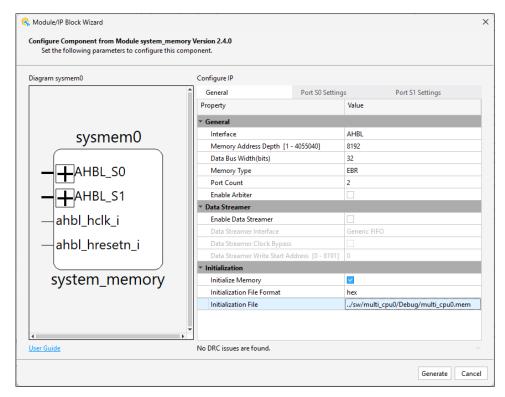

12. Initialize System Memory in Lattice Propel Builder (Figure 4.12).

In Lattice Propel Builder, initialize each system memory block (sysmem)\* with its corresponding .mem file, as shown in Table 4.3.

Figure 4.12. Lattice Propel Builder - Initialize System Memory with .mem Files

Table 4.3. Initialize System Memory with .mem Files

| System Memory Instance Name | .mem File Name |

|-----------------------------|----------------|

| sysmem0_inst                | multi_cpu0.mem |

| sysmem1_inst                | multi_cpu1.mem |

| sysmem2_inst                | multi_cpu2.mem |

| sysmem3_inst                | multi_cpu3.mem |

| sysmem4_inst                | multi_cpu4.mem |

| sysmem5_inst                | multi_cpu5.mem |

13. Regenerate the SoC design.

After the memory initialization:

Click the **Generate** button again in Lattice Propel Builder to update the design with the new memory contents (Figure 4.13).

Figure 4.13. Lattice Propel Builder – Regenerate Design After Memory Initialization

14. Launch the Lattice Radiant software and compile the design.

#### Within Lattice Propel Builder:

- a. Launch the Lattice Radiant software.

- b. Compile the design to complete the hardware build process (Figure 4.14).

Figure 4.14. Launch Lattice Radiant - Compile Design

### 4.4. Running the Example Design

To view the output, set up a UART terminal as described in the instructions below. The bitstream file generated in the Generating the Example Design section is downloaded to the Avant-E Evaluation Board using the Lattice Radiant Programmer.

### 4.4.1. Setting Up the UART Terminal

The software code in this example design displays messages on a terminal through the UART interface. To view the output, follow steps below to set up a UART terminal:

- 1. Launch Tera Term, or use Serial Terminal in SDK, or PuTTY.

- 2. Go to File > New Connection.

- 3. Select Serial.

- 4. Choose the correct COM port, which is usually the higher number.

- 5. Click OK.

- 6. Go to **Setup > Serial Port** and configure:

- Baud Rate: 115200

- Data: 8 bits

- · Parity: None

- Stop Bits: 1

- Flow Control: None

- Transmit Delay: 0 msec/char; 0 msec/line

- 7. Click **New Setting** to complete the setup process.

### 4.4.2. Programming the FPGA Bitstream

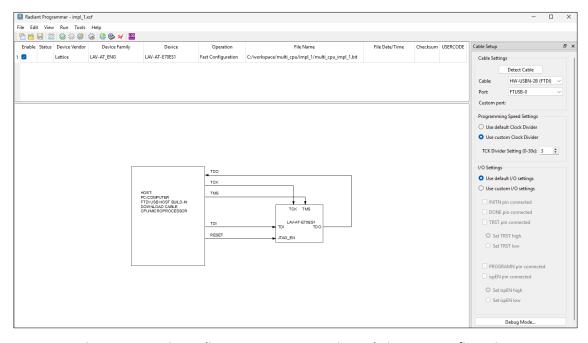

To program the bitstream into the device, follow these steps:

1. Launch Radiant Programmer.

Open the Lattice Radiant software, then go to Tools > Programmer (Figure 4.15).

Figure 4.15. Launching Radiant Programmer

2. Configure the programmer settings.

In the Lattice Radiant Programmer window:

- a. Ensure the Device Family, Device, and Operation match the configuration shown in Figure 4.16.

- b. Select the .bit file generated from previous steps using the Lattice Radiant software.

Figure 4.16. Lattice Radiant Programmer – Device and Bitstream Configuration

Detect the programming cable.

In the Cable Setup window, click Detect Cable (Figure 4.17).

Figure 4.17. Cable Setup – Detecting Cable

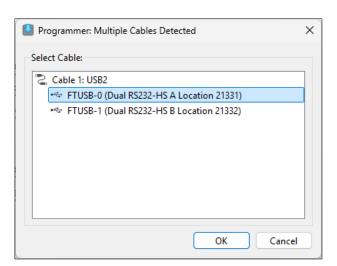

4. Select the programming cable.

In the **Select Cable** window:

- a. Choose FTUSB-0 from the list.

- b. Click **OK** to confirm (Figure 4.18).

Figure 4.18. Select Cable – FTUSB-0 Option

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

5. Program the device.

In the Lattice Radiant Programmer main interface:

- a. Go to Run > Program Device.

- b. The Output Console displays a message indicating that the operation is successful (Figure 4.19).

```

Output

INFO <85021078> - Check configuration setup: Successful.

INFO <85021278> - Device1 LAV-AT-E70ES1: Fast Configuration

INFO <85021298> - Operation Done. No errors.

INFO <85021371> - Elapsed time: 00 min : 35 sec

INFO <85021373> - Operation: successful.

```

Figure 4.19. Output Console - Programming the FPGA Bitstream

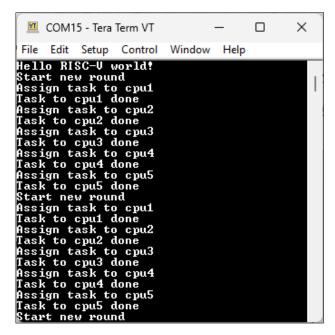

### 4.4.3. Verifying Results

Verify the UART terminal output.

After programming the FPGA and running the design, check the UART terminal, such as Tera Term, to ensure the printed messages match the expected output, as shown in Figure 4.20.

Figure 4.20. UART Terminal - Expected Output Messages

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# **Appendix A. Resource Utilization**

### Table A.1. Resource Utilization in LFCPNX-100 Device

| Configuration                                 | LUTs | Registers | sysMEM EBRs |

|-----------------------------------------------|------|-----------|-------------|

| Interface = AHB-Lite, FIFO Depth = 16, FIFO   | 360  | 195       | 2           |

| Type = EBR                                    | 300  | 195       | 2           |

| Interface = AHB-Lite, FIFO Depth = 16, FIFO   | 456  | 259       | 0           |

| Type = Distributed-RAM                        | 436  | 259       | 0           |

| Interface = AHB-Lite, FIFO Depth = 8192, FIFO | 750  | 440       | 22          |

| Type = EBR                                    | 759  | 440       | 32          |

### Table A.2. Resource Utilization in LAV-AT-E70 Device

| Configuration                                 | LUTs | Registers | sysMEM EBRs |

|-----------------------------------------------|------|-----------|-------------|

| Interface = AHB-Lite, FIFO Depth = 16, FIFO   | 341  | 183       | 2           |

| Type = EBR                                    | 341  | 105       | 2           |

| Interface = AHB-Lite, FIFO Depth = 16, FIFO   | 441  | 247       | 0           |

| Type = Distributed-RAM                        | 441  | 247       | O           |

| Interface = AHB-Lite, FIFO Depth = 8192, FIFO | 728  | 404       | 16          |

| Type = EBR                                    | 720  | 404       | 10          |

## References

- Lattice Propel Builder 2025.2 User Guide (FPGA-UG-02243)

- Lattice Memory Mapped Interface and Lattice Interrupt Interface User Guide (FPGA-UG-02039)

- AMBA AXI and ACE Protocol Specification

- AMBA 3 AHB-Lite Protocol Specification

### For more information, refer to:

- Lattice Propel web page

- Lattice Certus-N2 Family Devices web page

- Lattice Avant-E Family Devices web page

- Lattice Avant-G Family Devices web page

- Lattice Avant-X Family Devices web page

- MachXO5-NX Family Devices web page

- Certus-NX Family Devices web page

- CertusPro-NX Family Devices web page

- CrossLink-NX Family Devices web page

- Lattice Insights for Training Series and Learning Plans

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

For frequently asked questions, refer to the Lattice Answer Database at www.latticesemi.com/Support/AnswerDatabase.

# **Revision History**

### Revision 1.0, IP v1.0.0, December 2025

| Section | Change Summary      |

|---------|---------------------|

| All     | Production release. |

www.latticesemi.com