## **CrossLinkU-NX USB3 Vision**

# **Reference Design**

FPGA-RD-02319-1.0

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Cont | tents    |                                                 | 3        |

|------|----------|-------------------------------------------------|----------|

| Abbı | reviatio | ons in This Document                            | 8        |

| 1.   | Introd   | duction                                         | g        |

| 1.   | 1.       | Quick Facts                                     | <u> </u> |

| 1.   | 2.       | Features                                        | 10       |

| 1.   | 3.       | Naming Conventions                              | 10       |

|      | 1.3.1.   | Nomenclature                                    | 10       |

|      | 1.3.2.   | Signal Names                                    | 10       |

| 2.   | Direct   | tory Structure and Files                        | 11       |

| 3.   | Funct    | ional Description                               | 12       |

| 3.   | 1.       | Design Components                               | 12       |

|      | 3.1.1.   | PLL                                             | 12       |

|      | 3.1.2.   | USB23 Controller                                | 15       |

|      | 3.1.3.   | AHB-Lite to LMMI Bridge                         | 15       |

|      | 3.1.4.   | RISC-V RX Processor                             | 15       |

|      | 3.1.5.   | UART                                            | 18       |

|      | 3.1.6.   | Remote Wakeup GPIO                              | 19       |

|      | 3.1.7.   | ·                                               |          |

|      | 3.1.8.   | USB2 PHY Reset GPIO                             | 21       |

|      | 3.1.9.   | Octal SPI Controller                            | 22       |

|      | 3.1.10   | O. I2C Controller                               |          |

|      |          | 1. Tightly Coupled Memory                       |          |

|      |          | 2. AXI4 to AHB-Lite Bridge                      |          |

|      |          | 3. AHBL Interconnect                            |          |

|      |          | 4. AHB-Lite to APB Convertor                    |          |

|      |          | 5. APB Interconnect                             |          |

|      |          | 5. CSI-2/DSI D-PHY Receiver                     |          |

|      |          | 7. MIPI Packet Decoder                          |          |

|      |          | 8. Byte-to-Pixel Converter IP Core              |          |

|      |          | 9. Byte-to-Pixel (B2P) to AXI Stream Conversion |          |

|      |          | D. Debayer IP Core                              |          |

|      |          | 1. AXI Stream to Parallel Conversion            |          |

|      |          | 2. Pixel Data Conversion                        |          |

|      |          | 3. Color Space Converter                        |          |

|      |          | 4. YUV422 to UVC Bridge                         |          |

|      |          | 5. YUV422 Test Pattern Generator                |          |

|      |          | 5. IEBM IN FIFO Interface                       |          |

|      |          | 7. In Endpoint Buffer Manager (IEBM)            |          |

|      |          | 8. TDP Memory and AHB-Lite to Memory Bridge     |          |

|      |          | 9. U3V Register Interface                       |          |

|      |          | D. USB23 AXI Manager to Memory Interface Bridge |          |

|      |          | 1. Dual Boot Wrapper                            |          |

| 3.   |          | Clocking Scheme                                 |          |

| 3.   |          | Reset Scheme                                    |          |

| _    |          | Design Operations                               |          |

| ٠.   | 3.4.1.   |                                                 |          |

|      | 3.4.2.   |                                                 |          |

|      | 3.4.3.   |                                                 |          |

|      | 3.4.4.   | _                                               |          |

|      | 3.4.5.   |                                                 |          |

|      | 3.4.6.   |                                                 |          |

| 4.   | -        | Reference Design Signal Description             |          |

|      | -        | 5 6 1                                           |          |

| 5. Run   | nning the U3V Demo on Evaluation Board                                            |    |

|----------|-----------------------------------------------------------------------------------|----|

| 5.1.     | Extracting Reference Design Files                                                 | 56 |

| 5.2.     | Pleora eBUS Player Installation                                                   | 56 |

| 5.3.     | CrossLinkU-NX LIFCL-33U Evaluation Board Connection                               | 56 |

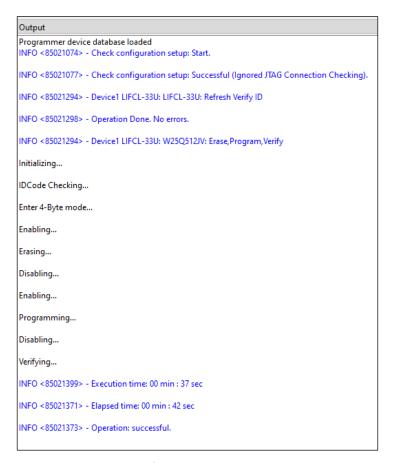

| 5.4.     | Programming FPGA Bitstream to Flash                                               | 56 |

| 5.5.     | Connect Evaluation Board to PC                                                    | 57 |

| 5.6.     | USB3 Vision Demonstration                                                         | 58 |

| 5.6.     | .1. Device Connection to eBUS Player                                              | 58 |

| 5.6.     | .2. Video Streaming from Camera Sensor                                            | 58 |

| 5.6.     | .3. Video Streaming from YUV422 Test Pattern                                      | 59 |

| 5.6.     | .4. SPI File Write Operation Using USB Test Application                           | 59 |

| 6. Buile | Iding the Reference Design                                                        | 64 |

| 6.1.     | Running Propel Builder Design                                                     | 64 |

| 6.1.     | .1. Install IPs on Local from File                                                | 64 |

| 6.1.     | .2. Opening the Propel Builder Design                                             | 66 |

| 6.1.     | .3. Generate the Propel Builder System                                            | 66 |

| 6.2.     | Running the Radiant Software Project                                              | 67 |

| 6.3.     | Building RISC-V Zephyr                                                            | 67 |

| 6.3.     | .1. Set Up Zephyr Build Environment                                               | 67 |

| 6.3.     | .2. Apply Patch and Build Zephyr Binary                                           | 68 |

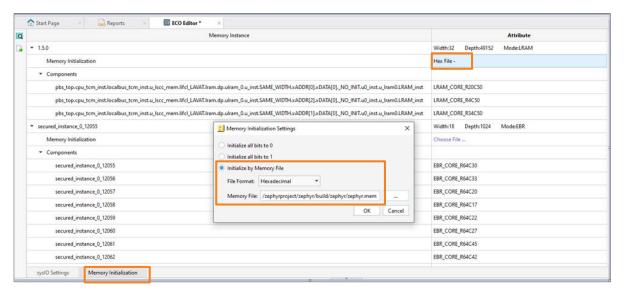

| 6.3.     | .3. Regenerate Bitstream Using the ECO Editor                                     | 69 |

| 7. Cust  | stomizing the Reference Design                                                    | 71 |

| 7.1.     | Changing the Camera Resolution                                                    |    |

| 7.1.     | .1. Updating Radiant IP Parameters Configuration                                  | 71 |

| 7.2.     | Changing to the Other Supported Resolutions                                       | 71 |

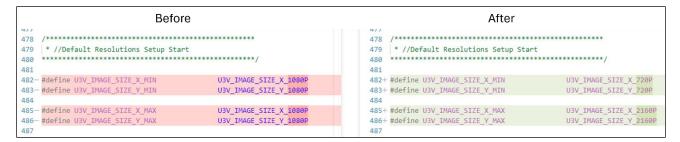

| 7.2.     | .1. Modifying the Zephyr Code                                                     | 71 |

| Appendix | x A. Resource Utilization                                                         | 72 |

| Appendix | x B. IN Endpoint Buffer Manager                                                   |    |

| B.1.     | IP Ports and Parameters                                                           |    |

|          | B-Lite Interface                                                                  |    |

|          | Interface                                                                         |    |

|          | O Interface                                                                       |    |

|          | scellaneous Ports                                                                 |    |

|          | er Configurable Parameters                                                        |    |

| B.2.     | Register Offset Map                                                               |    |

| В.З.     | Register Details                                                                  |    |

| _        | VERSION                                                                           |    |

|          | RATCH                                                                             |    |

| _        | _EN                                                                               |    |

| _        | SRC                                                                               |    |

|          | FR_CNFG                                                                           |    |

|          | /_PARAMS_INFO                                                                     |    |

| CTR      |                                                                                   |    |

|          | FR_TRACKER_INFO                                                                   |    |

|          | FR_AVAILABILITY_INFO                                                              |    |

|          | FR_XCHNG_CTRL                                                                     |    |

| _        | _BUFR_INFO_FOR_FW                                                                 |    |

|          | MESTAMP                                                                           |    |

|          | LID_LINES_IN_FRAME                                                                |    |

| B.4.     | IN Endpoint Buffer Management Architecture  Buffer Read and Write Management Flow |    |

| B.5.     | fer Write Flow                                                                    |    |

|          | fer Read Flow                                                                     |    |

|          | Core Operation                                                                    |    |

| В.6.     | Core Operation                                                                    | 84 |

| IP Core Configuration or Reconfiguration                                                                                  |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

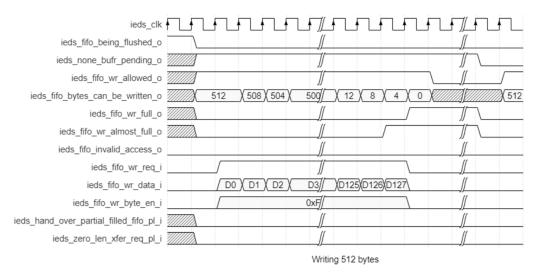

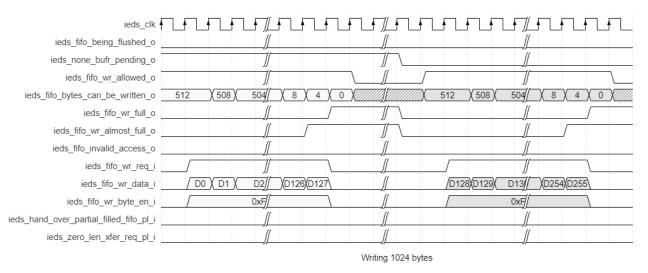

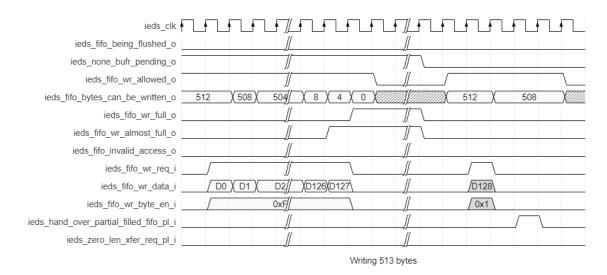

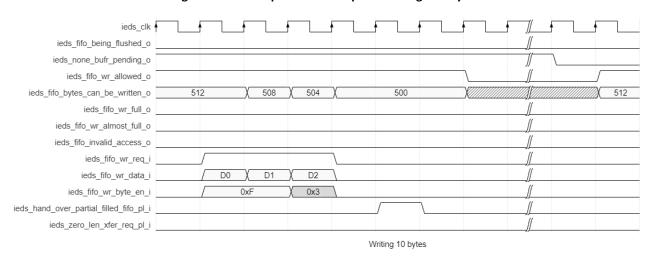

| FIFO Write Operation                                                                                                      |    |

| FIFO Write Examples                                                                                                       | 86 |

| References                                                                                                                |    |

| Technical Support Assistance                                                                                              |    |

| Revision History                                                                                                          | 91 |

|                                                                                                                           |    |

|                                                                                                                           |    |

| Figures                                                                                                                   |    |

|                                                                                                                           | 11 |

| Figure 2.1. Directory Structure                                                                                           |    |

| Figure 3.1. Reference Design Block Diagram<br>Figure 3.2. PLL Configuration – General, Reference Clock, and Primary Clock |    |

|                                                                                                                           |    |

| Figure 3.3. PLL Configuration – Secondary Clock                                                                           |    |

| · ·                                                                                                                       |    |

| Figure 3.5. RISC-V General Tab Configuration                                                                              |    |

| Figure 3.6. RISC-V Debug Tab Configuration                                                                                |    |

|                                                                                                                           |    |

| Figure 3.8. RISC-V Interrupt Tab Configuration                                                                            |    |

| Figure 3.9. UART Configuration                                                                                            |    |

| Figure 3.10. Remote Wakeup GPIO                                                                                           |    |

| Figure 3.11. Hardware Version Definition in RTL                                                                           |    |

| Figure 3.12. Hardware Version GPIO IP                                                                                     |    |

| Figure 3.13. USB2 PHY Reset GPIO                                                                                          |    |

| Figure 3.14. Octal SPI Controller                                                                                         |    |

| Figure 3.15. Lattice I2C Master Configuration                                                                             |    |

| Figure 3.16. TCM General Configuration                                                                                    |    |

| Figure 3.17. TCM Port S0 Configuration                                                                                    |    |

| Figure 3.18. TCM Port S1 Configuration                                                                                    |    |

| Figure 3.19. AXI4 to AHB-Lite Bridge Configuration                                                                        |    |

| Figure 3.20. AHB-Lite Interconnect General Configuration                                                                  |    |

| Figure 3.21. AHB-Lite Interconnect Main Configuration                                                                     |    |

| Figure 3.22. AHB-Lite Interconnect Manager Priority Settings                                                              |    |

| Figure 3.23. AHB-Lite Interconnect Max Burst Settings                                                                     |    |

| Figure 3.24. AHB-Lite to APB Configuration                                                                                |    |

| Figure 3.25. APB Interconnect General Configuration                                                                       |    |

| Figure 3.26. APB Interconnect Main Settings Configuration                                                                 |    |

| Figure 3.27. RX DPHY General Configuration                                                                                |    |

| Figure 3.28. RX DPHY RX FIFO Configuration                                                                                |    |

| Figure 3.29. RX DPHY Soft PHY Configuration                                                                               |    |

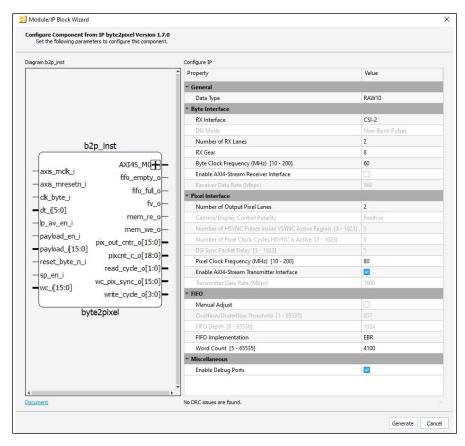

| Figure 3.30. Byte-to-Pixel Configuration                                                                                  |    |

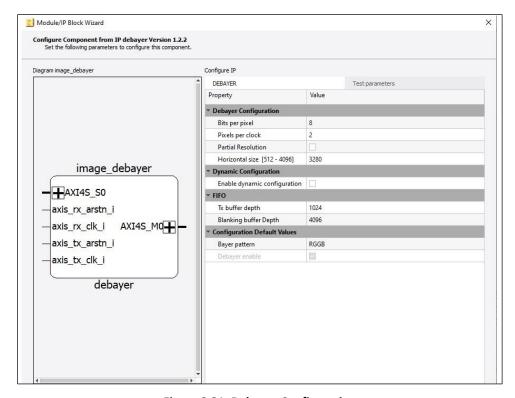

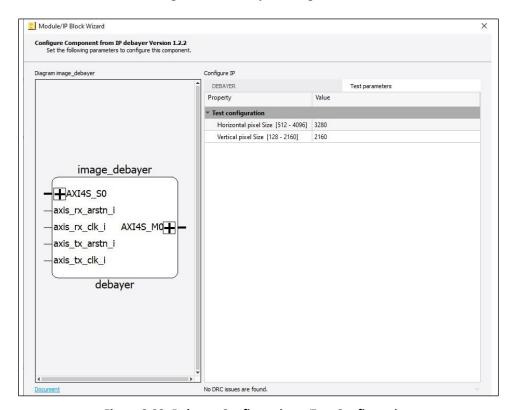

| Figure 3.31. Debayer Configuration                                                                                        |    |

| Figure 3.32. Debayer Configuration – Test Configuration                                                                   |    |

| Figure 3.33. Color Space Converter Configuration                                                                          |    |

| Figure 3.34. Color Space Converter Configuration – Output and Precision Control                                           |    |

| Figure 3.35. IEBM Configuration                                                                                           |    |

| Figure 3.36. AHB-Lite to Memory Bridge Configuration                                                                      |    |

| Figure 3.37. USB23 AXI Bridge to Memory Bridge Architecture                                                               |    |

| Figure 3.38. USB3 Vision Reference Design Clocking Scheme                                                                 |    |

| Figure 3.39. Reset Scheme                                                                                                 |    |

| Figure 3.40. Data Flow During Streaming                                                                                   |    |

| Figure 3.41. Test Pattern Inquiry Register Offset in XML File                                                             |    |

| Figure 3.42. Data Structure—Value of Test Pattern Inquiry Register                                                        |    |

| Figure 3.43. Test Pattern Register Offset in XML File                                                                     | 50 |

|                                                                                                                           |    |

| Figure 3.44. Data Structure—Value of Test Pattern Register      | 50 |

|-----------------------------------------------------------------|----|

| Figure 3.45. U3V Design Video IP Path Block Diagram             | 51 |

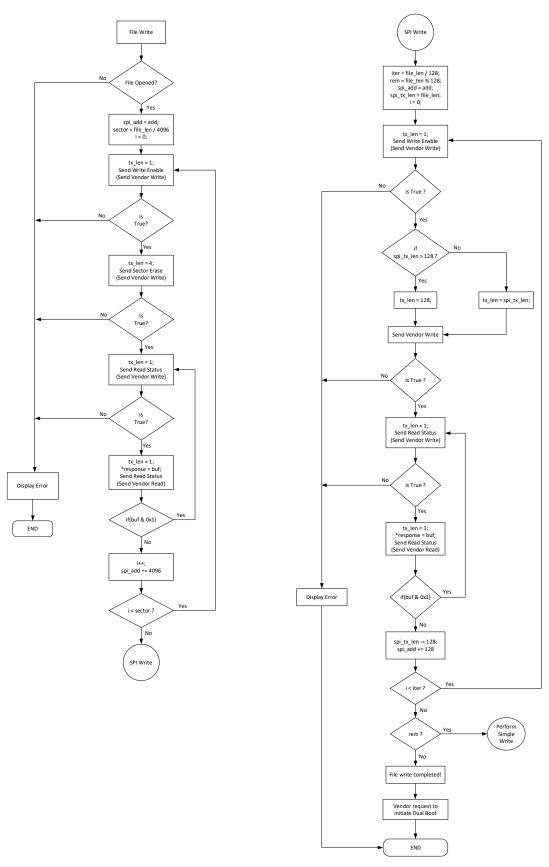

| Figure 3.46. SPI File Write Operation Flow Chart                | 53 |

| Figure 5.1. Device Properties Options                           | 56 |

| Figure 5.2. Successful Device Programming Operation             | 57 |

| Figure 5.3. U3V USB Enumeration                                 | 58 |

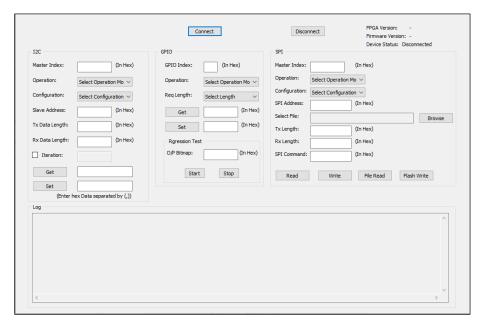

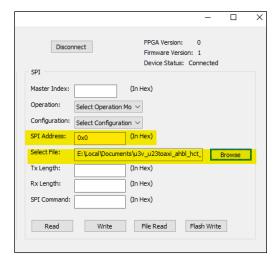

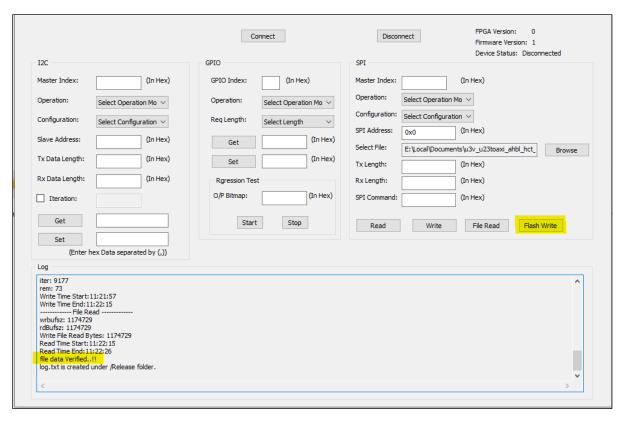

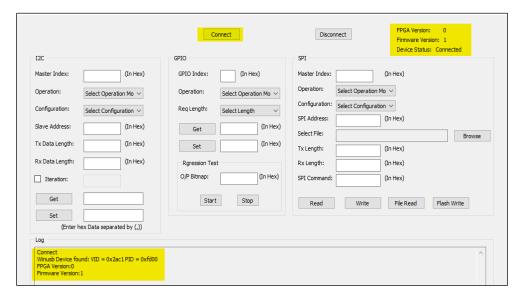

| Figure 5.4. USB Test Application                                | 59 |

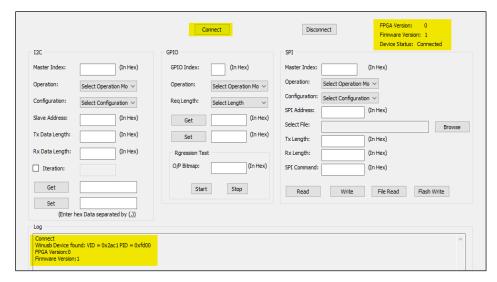

| Figure 5.5. Device Connected to USB Test Application            | 60 |

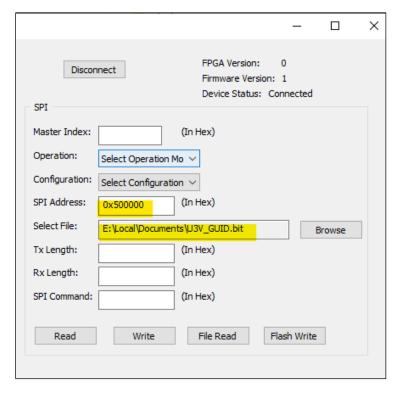

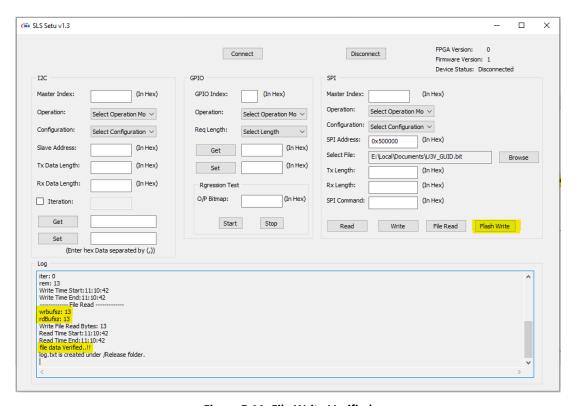

| Figure 5.6. SPI File Write Settings                             |    |

| Figure 5.7. File Write Successful                               | 61 |

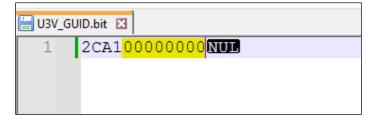

| Figure 5.8. U3V GUID Bitstream File Contents                    | 61 |

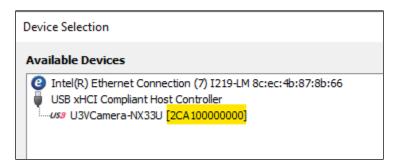

| Figure 5.9. Successful Connection                               | 62 |

| Figure 5.10. U3V GUID Bit Selection                             | 62 |

| Figure 5.11. File Write Verified                                | 63 |

| Figure 5.12. Device Selection List is Updated with New GUID     | 63 |

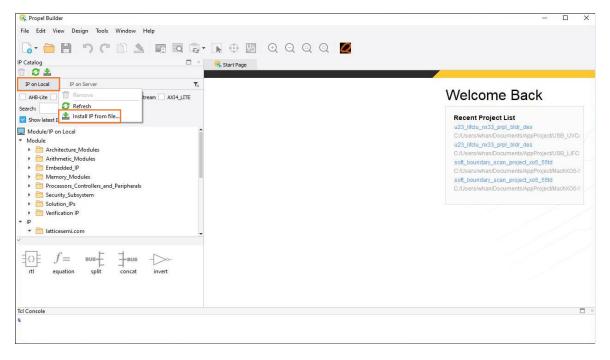

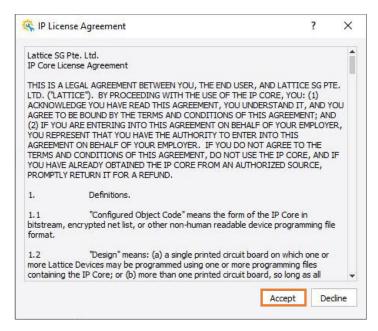

| Figure 6.1. Install IP from File                                | 64 |

| Figure 6.2. Accept IP License Agreement                         | 65 |

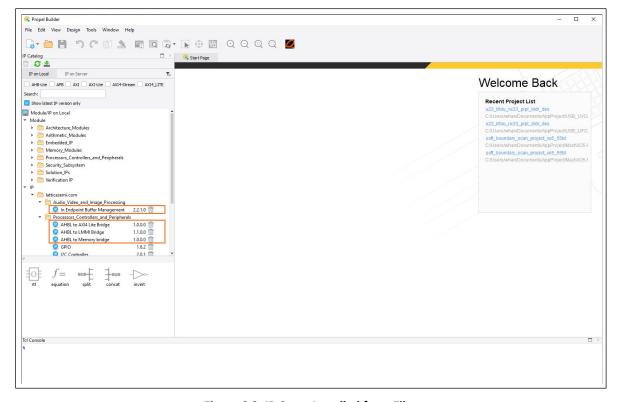

| Figure 6.3. IP Cores Installed from Files                       | 65 |

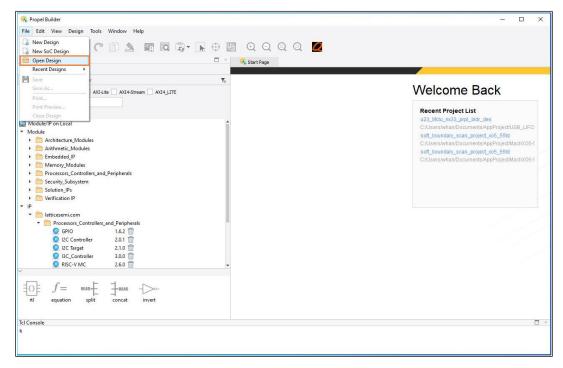

| Figure 6.4. Open the Propel Builder Design                      | 66 |

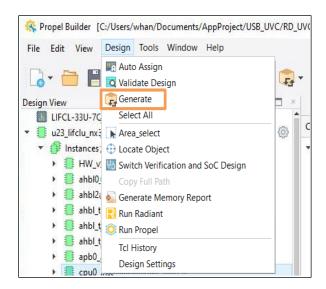

| Figure 6.5. Generate the Propel Builder System                  | 66 |

| Figure 6.6. Export Files to Start Bitstream Compilation         |    |

| Figure 6.7. Zephyr Build Environment                            | 68 |

| Figure 6.8. Reset the Zephyr Repository                         | 68 |

| Figure 6.9. Zephyr Repository is at Tag v3.7.0                  | 69 |

| Figure 6.10. Apply Zephyr Patch                                 | 69 |

| Figure 6.11. Rerun Export Files to Generate New Bitstream       | 70 |

| Figure 6.12. ECO Editor Settings                                | 70 |

| Figure 7.1. Zephyr Code Change to Support Other Resolutions     | 71 |

| Figure B.1. IN Endpoint Buffer Management Block Diagram         | 81 |

| Figure B.2. Buffer Write Operation Flow                         | 82 |

| Figure B.3. Buffer Read Operation Flow                          | 83 |

| Figure B.4. FIFO Operation Example – Writing 512 Bytes          | 86 |

| Figure B.5. FIFO Operation Example – Writing 1,024 Bytes        | 86 |

| Figure B.6. FIFO Operation Example – Writing 513 Bytes          | 87 |

| Figure B.7. FIFO Operation Example – Writing 10 Bytes           | 87 |

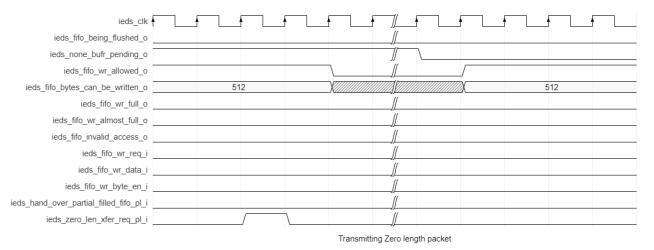

| Figure B.8. FIFO Operation Example – Zero Length Packet Request | 87 |

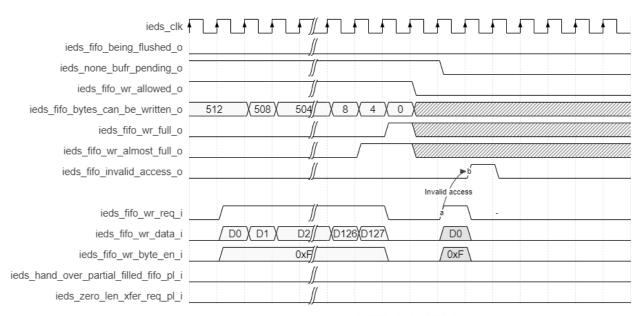

| Figure B.9. FIFO Operation Example – Invalid IN FIFO Access     | 88 |

| Tables                                                          |    |

| Table 1.1. Summary of the Reference Design                      | a  |

| Table 2.1. File List                                            |    |

| Table 3.1. Clock and Reset Ports                                |    |

| Table 3.2. Native Memory Interface Ports                        |    |

| Table 3.3. AXI4 Interface Ports                                 |    |

| Table 3.4. Reset Domains                                        |    |

| Table 3.5. Common Command Data Format                           |    |

| Table 3.6. Read Manifest Table Data Structure                   |    |

| Table 3.7. Read Manifest Table Response Data Structure          |    |

| Table 3.8. Frame Start Event Data Structure                     |    |

| Table 3.9. Manifest Table Layout                                |    |

| Table 3.3. Iviainiest Table Layout                              | 4/ |

| Table 3.10. Manifest Entry Layout                                              | 48 |

|--------------------------------------------------------------------------------|----|

| Table 3.11. USB3 Vision Mandatory Features for the Camera XML Description File | 49 |

| Table 4.1. Primary I/O                                                         | 55 |

| Table A.1. Resource Utilization for LIFCL-33U-9CTG104C                         | 72 |

| Table B.1. AHB-Lite Subordinate Interface                                      | 73 |

| Table B.2. AXI Subordinate Interface                                           | 73 |

| Table B.3. FIFO Interface                                                      | 74 |

| Table B.4. FIFO Interface                                                      | 75 |

| Table B.5. User Configurable Parameters                                        | 75 |

| Table B.6. IEBM Register Offset Map                                            | 75 |

| Table B.7. IP_VERSION, Offset = 0x00                                           | 76 |

| Table B.8. SCRATCH, Offset = 0x04                                              | 76 |

| Table B.9. INT_EN, Offset = 0x08                                               | 76 |

| Table B.10. INT_SRC, Offset = 0x0C                                             | 77 |

| Table B.11. BUFR_CNFG, Offset = 0x10                                           |    |

| Table B.12. HW_PARAMS_INFO, Offset = 0x14                                      | 78 |

| Table B.13. CTRL, Offset = 0x18                                                | 78 |

| Table B.14. BUFR_TRACKER_INFO, Offset = 0x1C                                   | 79 |

| Table B.15. BUFR_AVAILABILITY_INFO, Offset = 0x20                              |    |

| Table B.16. BUFR_XCHNG_CTRL, Offset = 0x24                                     | 79 |

| Table B.17. SEL_BUFR_INFO_FOR_FW, Offset = 0x28                                | 80 |

| Table B.18. TIMESTAMP_W0, Offset = 0x30                                        | 80 |

| Table B.19. TIMESTAMP_W0, Offset = 0x34                                        |    |

| Table B.20. BUFR_XCHNG_CTRL (Offset = 0x24)                                    | 81 |

| Table B.21. Input Ports Related to FIFO Write Operation                        | 82 |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviations | Definition                                  |

|---------------|---------------------------------------------|

| AXI4          | Advanced Extensible Interface 4             |

| AHB           | Advanced High-Performance Bus               |

| AHB-Lite      | Advanced High-Performance Bus – Lite        |

| APB           | Advanced Peripheral Bus                     |

| B2P           | Byte to Pixel                               |

| CCM           | Color Correction Matrix                     |

| CPU           | Central Processing Unit                     |

| CSI-2         | Camera Serial Interface 2                   |

| DMA           | Direct Memory Access                        |

| FIFO          | First In First Out                          |

| FPGA          | Field Programmable Gate Array               |

| FPS           | Frame Per Second                            |

| GPIO          | General Purpose Input/Output                |

| HAL           | Hardware Abstraction Layer                  |

| IEBM          | In Endpoint Buffer Manager                  |

| IEDS          | In Endpoint Data Source                     |

| I2C           | Inter-Integrated Circuit                    |

| INT           | Interrupt                                   |

| IP            | Intellectual Property                       |

| IRQ           | Interrupt Request                           |

| ISP           | Image Signal Processing                     |

| LED           | Light Emitting Diode                        |

| LMMI          | Lattice Memory Mapped Interface             |

| MC            | Microcontroller                             |

| MIPI          | Mobile Industry Processor Interface         |

| PC            | Personal Computer                           |

| PLL           | Phase-Locked Loop                           |

| RAM           | Random Access Memory                        |

| RGB           | Red Green Blue                              |

| RISC-V        | Reduced Instruction Set Computer – Five     |

| RTL           | Register Transfer Level                     |

| SCL           | Serial Clock Line                           |

| SDA           | Serial Data Line                            |

| SPI           | Serial Peripheral Interface                 |

| TDP           | True Dual Port                              |

| TRB           | Transfer Request Block                      |

| UART          | Universal Asynchronous Receiver/Transmitter |

| USB           | Universal Serial Bus                        |

|               |                                             |

## 1. Introduction

The Lattice Semiconductor CrossLinkU™-NX USB3 Vision (U3V) reference design provides you a template for video streaming from camera sensor over USB using the USB hard IP in a CrossLinkU-NX device. The U3V is an interface standard for industrial cameras. This design implements the standard defined in the U3V specifications.

## 1.1. Quick Facts

Download the reference design files from the U3V reference design web page.

Table 1.1. Summary of the Reference Design

|                       | Target Devices                   | LIFCL-33U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General               | Source Code Format               | C code, RTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | Functional Simulation            | Not supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Simulation            | Timing Simulation                | Not supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | Hardware Validation              | Fully validated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | Software Tool and Version        | <ul> <li>Lattice Propel™ SDK 2024.2</li> <li>Lattice Propel Builder 2024.2</li> <li>Lattice Radiant™ Software version 2024.2</li> <li>Lattice Radiant Programmer version 2024.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Software Requirements | Propel Software Soft IP Version  | <ul> <li>RISC-V RX version 2.5.0</li> <li>Tightly Coupled Memory version 1.5.0</li> <li>AXI4 to AHB-Lite Bridge version 1.3.0</li> <li>AHB-Lite Interconnect version 1.3.2</li> <li>AHB-Lite to APB Bridge version 1.1.2</li> <li>AHB-Lite Feedthrough version 1.0.0</li> <li>APB Interconnect version 1.2.1</li> <li>I2C Controller version 2.2.0</li> <li>UART version 1.4.0</li> <li>Octal SPI Controller version 1.0.0</li> <li>GPIO version 1.7.0</li> </ul> Custom IP: <ul> <li>IEMB 2.2.1.0</li> <li>AHB-Lite to Memory Bridge version 1.0.0</li> <li>AHB-Lite to AXI-Lite Bridge version 1.0.0</li> <li>AHB-Lite to LMMI Bridge version 1.0.0</li> </ul> |

|                       | Radiant Software Soft IP Version | <ul> <li>Byte-to-Pixel Converter version 1.7.0</li> <li>Color Space Converter version 2.3.0</li> <li>Debayer version 1.2.2</li> <li>CSI-2/DSI D-PHY Receiver version 1.9.0</li> <li>FIFO_DC version 2.4.0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | Board                            | LIFCL-33U-EVN Evaluation Board REV-B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | Camera Sensor                    | Raspberry PI Camera Module V2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Hardware Requirements | Cables                           | <ul> <li>USB 3.0 Superspeed Data cable (USB C to USB C cable, or USB C to USB A cable)</li> <li>USB A to Micro USB cable</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

FPGA-RD-02319-1.0

### 1.2. Features

Key features of the CrossLinkU-NX USB3 Vision reference design include:

- USB3 Vision specifications, which include device identification, device control, and data streaming.

- GenICam-compliant XML file.

- Video data streaming at USB 3 SuperSpeed at 3.4 Gbps.

- Multiple video formats and resolutions:

- RAW8, RAW10, Mono8, Mono10, and YCbCr422.

- 1280x720 (at 45 FPS), 1920x1080 (at 30 FPS) and 3280x2160 (at 14 FPS).

- Works with Pleora eBUS Player to control the imaging source parameters and view the video stream.

- RISC-V processor system with running Zephyr real-time operating system (RTOS).

- Soft Mobile Industry Processor Interface (MIPI) D-PHY and Camera Serial Interface (CSI-2) for image sensor aggregation. The Lattice Semiconductor D-PHY Receiver IP converts CSI-2 data to 8-bit data.

- The Lattice Semiconductor Byte-to-Pixel Converter IP converts CSI-2 standard-based video payload packets from the D-PHY Receiver module output to pixel format.

- The Lattice Semiconductor Debayer IP converts raw image data into an RGB image.

- Hard USB IP for USB video class to stream the video from the image sensor to a PC through USB Type C connector.

- Primarily targets the Raspberry PI Camera Module 2. For more information, refer to the Raspberry Pi Camera Module 2 web page.

## 1.3. Naming Conventions

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.3.2. Signal Names

- \_n are active low signals, asserted when value is logic 0.

- i are input signals.

- o are output signals.

## 2. Directory Structure and Files

This reference design source code release is controlled. Only the demo bitstream and binary files are released on the public web page. Contact Lattice Sales or Technical Support to obtain the complete source code.

The following figure shows the directory structure for this reference design with source code.

Figure 2.1. Directory Structure

The following table shows the list of files included in the reference design package.

Table 2.1. File List

| Attribute                    | Description                                                                                    |

|------------------------------|------------------------------------------------------------------------------------------------|

| embedded\u3v_xml (1)         | Contains the XML file used for USB3 Vision camera.                                             |

| embedded\zephyr (1)          | Contains the Zephyr source code in patch format.                                               |

| hardware\component (1)       | Contains the custom IP and RTL used in this reference design.                                  |

| hardware\ref_design (1)      | Contains the complete Radiant software and Propel Builder software project files.              |

| hardware\ref_design/demo (2) | Contains the design demo file.                                                                 |

| software\utilities (2)       | Contains the Windows® application for performing SPI flash operation in this reference design. |

#### Notes:

- 1. Files that are only available in the source code-controlled release.

- 2. Files are available in both controlled and public releases.

## 3. Functional Description

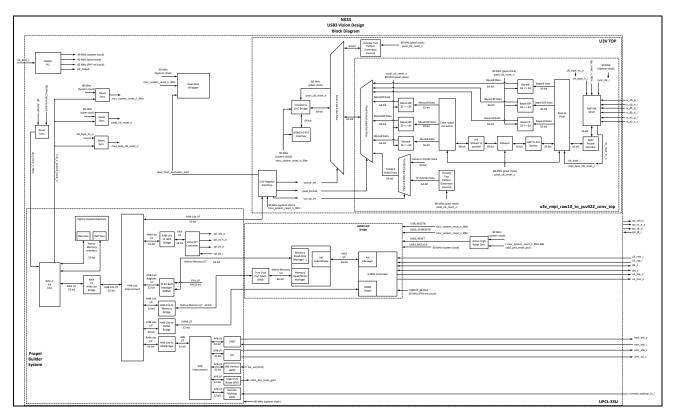

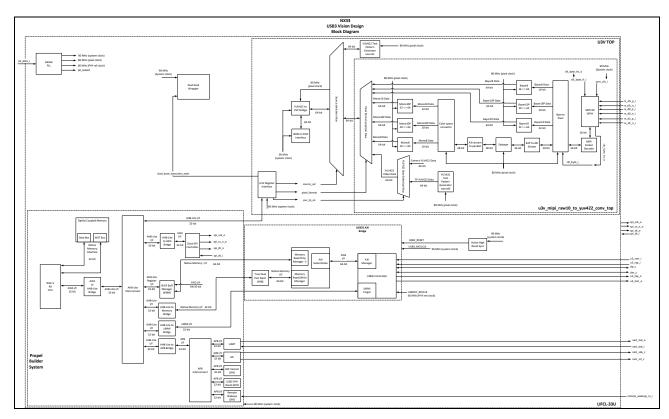

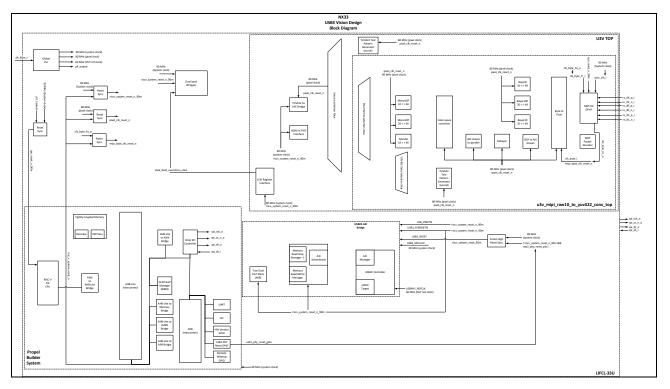

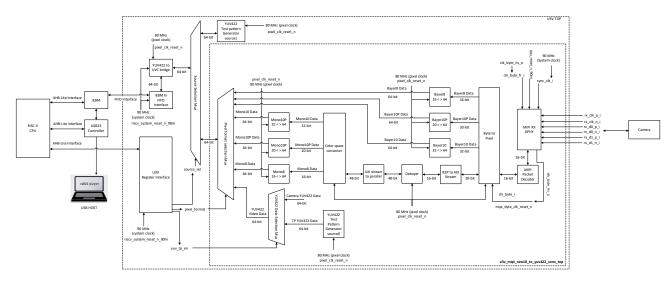

The block diagram of the CrossLinkU-NX USB3 Vision reference design is shown in the figure below. Refer to the Design Components section for the details of each component in this block diagram.

Figure 3.1. Reference Design Block Diagram

## 3.1. Design Components

This section describes all the blocks used in the CrossLinkU-NX USB3 Vision reference design.

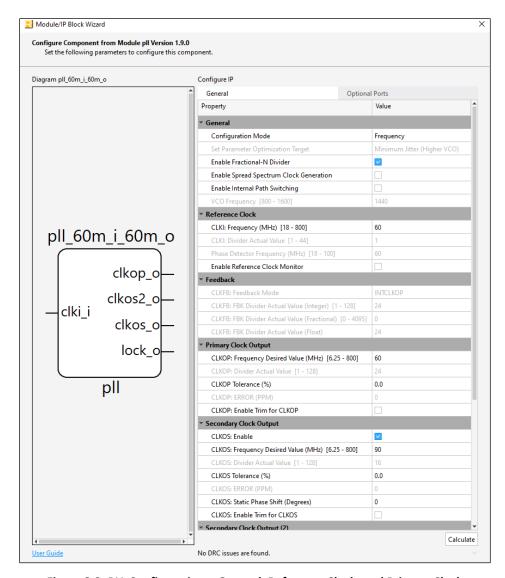

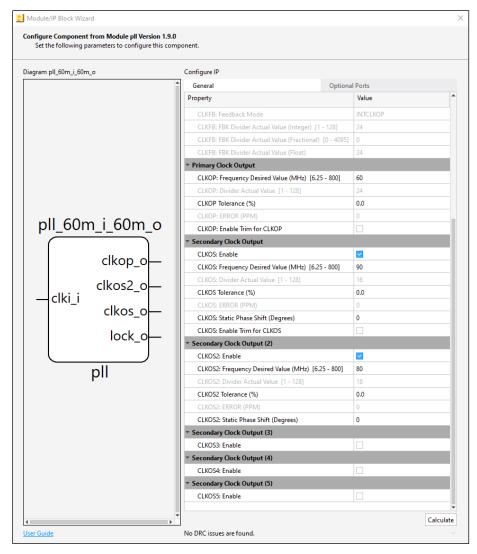

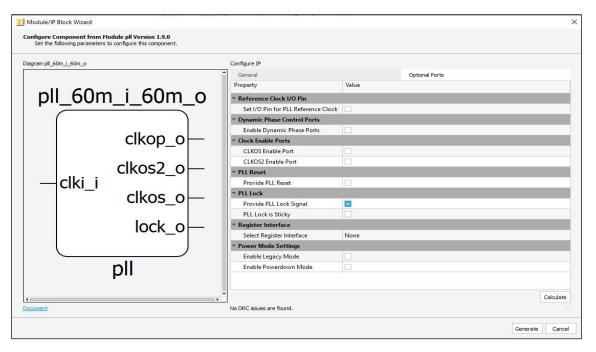

#### 3.1.1. PLL

The phase-locked loop (PLL) IP generates three clocks output with different frequencies, which are used by various blocks in the design. The USB23 PHY operates at 60 MHz, the MIPI RX DPHY and video IP operate at 80 MHz, and RISC-V subsystem operates at 90 MHz.

Figure 3.2, Figure 3.3, and Figure 3.4 show the general and optional ports configuration of the PLL IP.

Figure 3.2. PLL Configuration – General, Reference Clock, and Primary Clock

Figure 3.3. PLL Configuration - Secondary Clock

Figure 3.4. PLL Configuration - Optional Ports

#### 3.1.2. USB23 Controller

The USB23 controller is the hardened IP core in CrossLinkU-NX FPGAs. This IP handles the USB2 and USB3 communication between the FPGA and the Host PC.

The AXI4 Manager interface of the USB23 controller is connected to the following two different memories via the USB23 AXI bridge:

- For USB Bulk transfers, the USB23 controller fetches data from IN Endpoint Buffer Manager (IEBM) block. This IEBM memory is not shared with any other manager in the system including the RISC-V processor.

- For other operations, USB23 controller access the shared memory block to communicate with the RISC-V processor.

## 3.1.3. AHB-Lite to LMMI Bridge

The USB23 controller register interface can be configured through its LMMI interface. The AHB-Lite to LMMI bridge allows the RISC-V processor to access the LMMI interface on the USB23 controller registers.

#### 3.1.4. RISC-V RX Processor

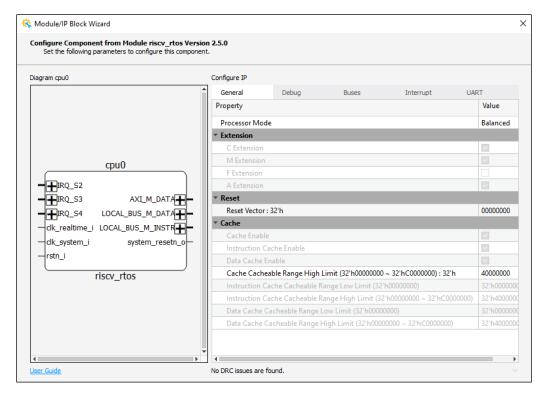

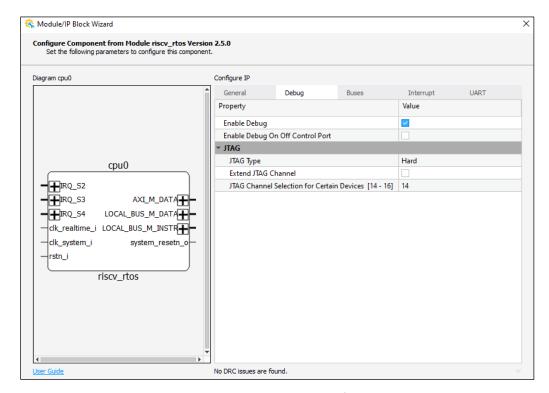

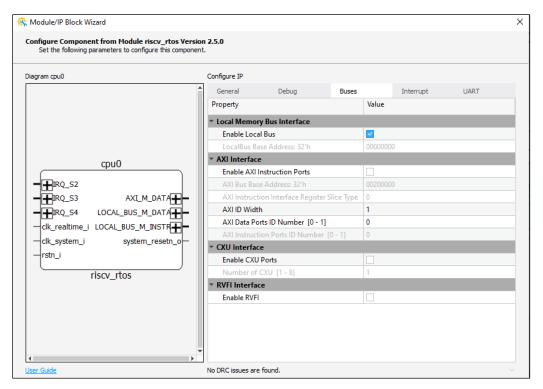

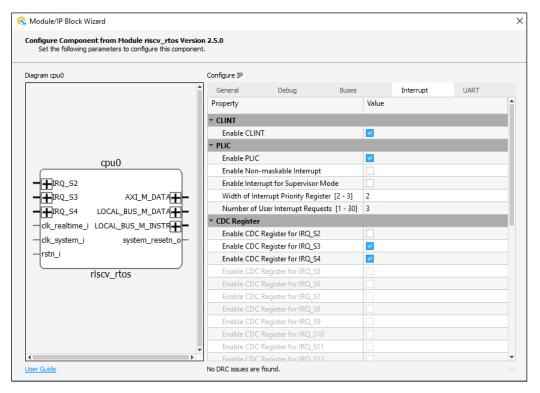

The RISC-V RX processor manages the system including USB controller and endpoint operations, I2C transfers, prints messages via UART processes and others. The processor executes the Zephyr RTOS with driver support for peripherals in the system. The processor handles the external interrupts from USB23 controller and IEBM core. The RISC-V RX processor configuration is shown in Figure 3.5, Figure 3.6, Figure 3.7, and Figure 3.8.

Figure 3.5. RISC-V General Tab Configuration

Figure 3.6. RISC-V Debug Tab Configuration

Figure 3.7. RISC-V Buses Tab Configuration

Figure 3.8. RISC-V Interrupt Tab Configuration

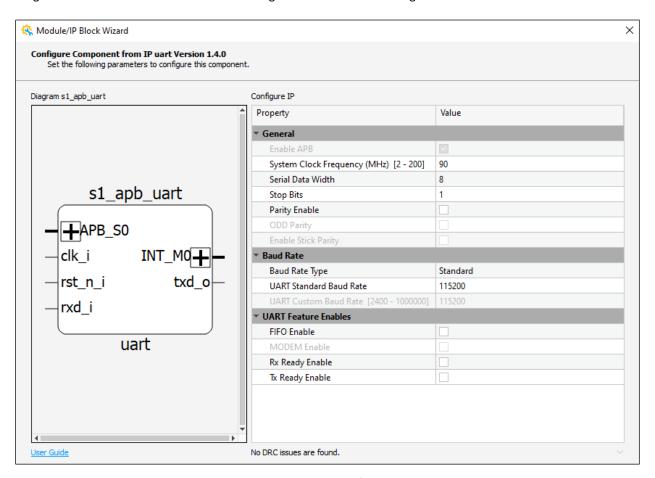

#### 3.1.5. UART

The UART IP core performs serial-to-parallel conversion on data characters received from a peripheral UART device and parallel-to-serial conversion on data characters received from the host (RISC-V processor) located inside the FPGA through an APB Interface. The UART IP core configuration is shown in the figure below.

Figure 3.9. UART Configuration

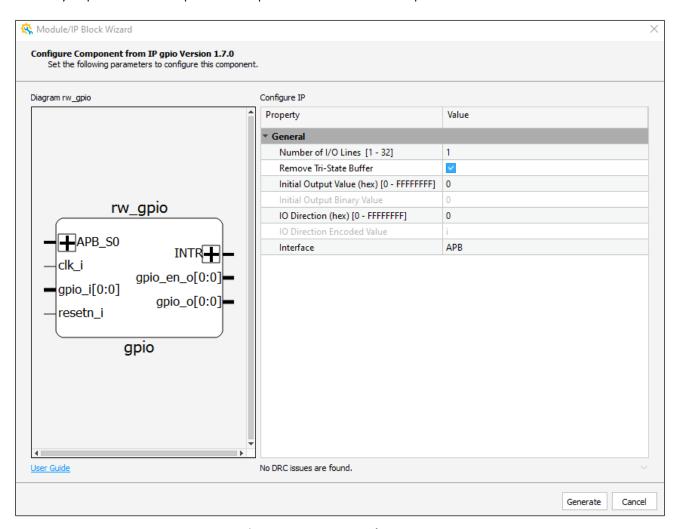

#### 3.1.6. Remote Wakeup GPIO

The Remote Wakeup GPIO input pin is typically used to trigger a wake-up event from a low-power or sleep mode through an external GPIO signal. When the remote\_wakeup\_in\_i pin is activated (For example, button press or signal transition), it generates an interrupt to the RISC-V processor. This interrupt prompts the processor to take the necessary steps to exit the low-power or sleep state and resume normal operation.

Figure 3.10. Remote Wakeup GPIO

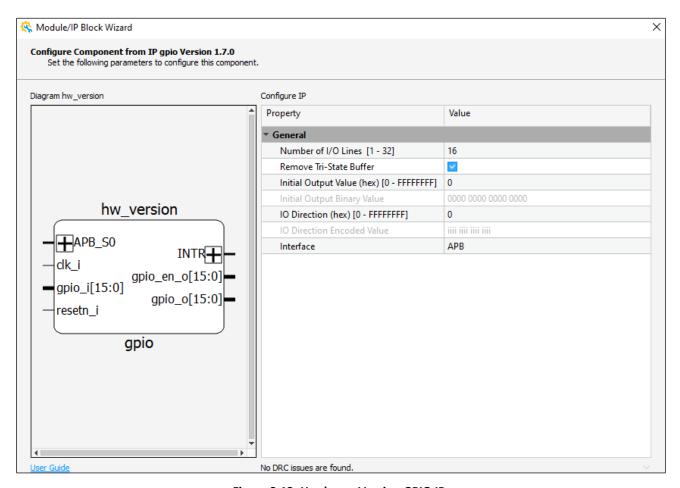

### 3.1.7. Hardware Version GPIO

The hardware version GPIO tracks the version of the hardware design and the RISC-V firmware reads to know the current hardware version supported by the design. The GPIO input signals are connected to the following local parameters in the design top-level RTL file (u3v\_u23toaxi\_ahbl\_revBbd\_des.sv) as shown in the figure below.

```

// HW Design Major version

localparam FPGA_DES_MAJOR_VERSION = 8'h01;

// HW Design Minor version

localparam FPGA_DES_MINOR_VERSION = 8'h00;

// HW_VERSION indicator

// HW_VERSION indicator

SPGA_VERSION_TRACKER = { FPGA_DES_MAJOR_VERSION , FPGA_DES_MINOR_VERSION};

```

Figure 3.11. Hardware Version Definition in RTL

The figure below shows the GPIO IP parameters configured in the Propel Builder software project. The GPIO IP is set to has 16-bit input signal that is connected to local parameters as mentioned above.

Figure 3.12. Hardware Version GPIO IP

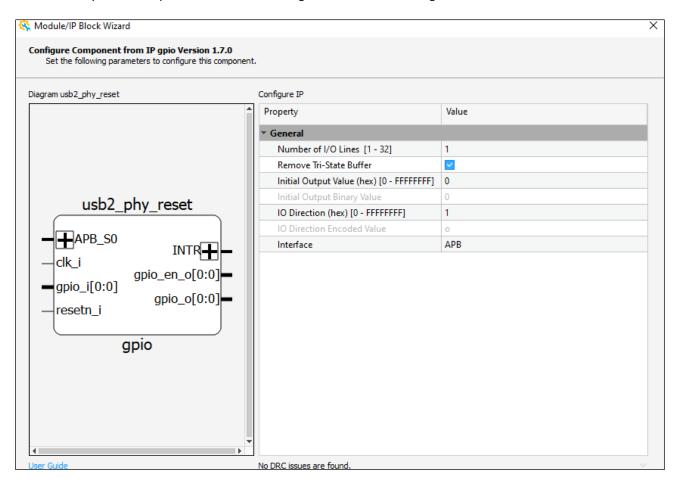

### 3.1.8. USB2 PHY Reset GPIO

While switching between USB2 and USB3 modes, the current state of the USB2 PHY must be reset. This reset operation is controlled by the RISC-V processor firmware through a GPIO IP where its signal is connected to the USB2 PHY reset.

Figure 3.13. USB2 PHY Reset GPIO

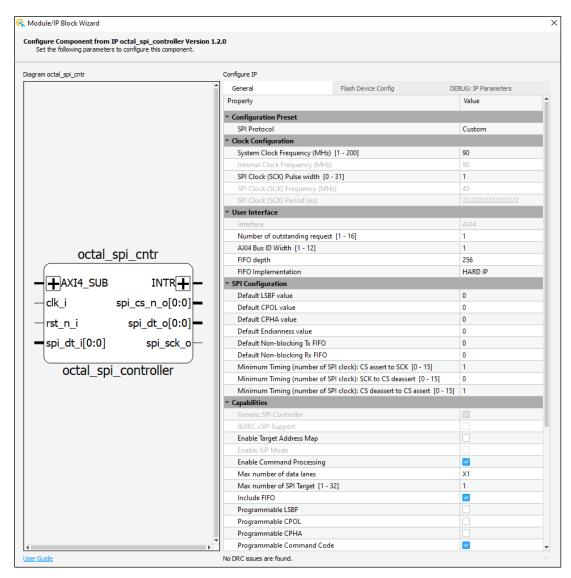

### 3.1.9. Octal SPI Controller

The Octal SPI Controller is used to communicate with high-speed flash memory available on the NX33U board.

Figure 3.14. Octal SPI Controller

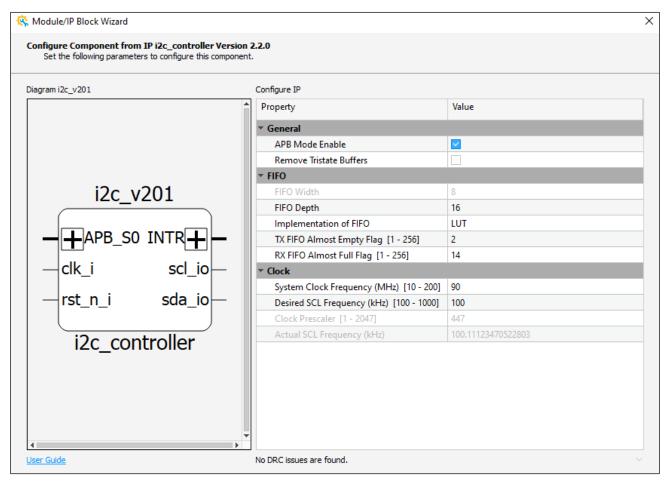

#### 3.1.10. I2C Controller

The I2C Controller IP core is used to communicate with the I2C devices. I2C write and I2C read operations can be performed to the I2C device that is connected to the CrossLinkU-NX FPGA on the board. In this design the RISC-V processor configures the external camera sensor register via the I2C interface using the I2C Controller IP. The I2C Controller IP core configuration is shown in the figure below.

Figure 3.15. Lattice I2C Master Configuration

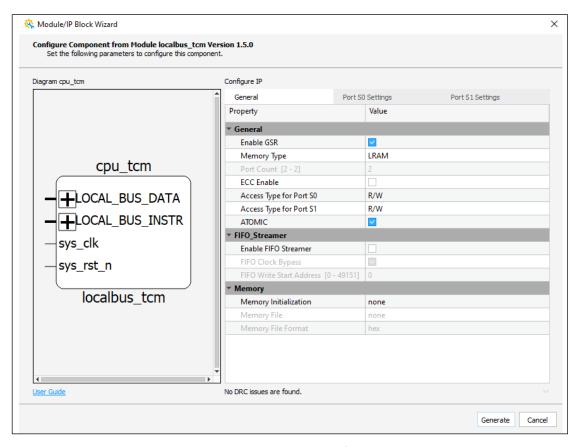

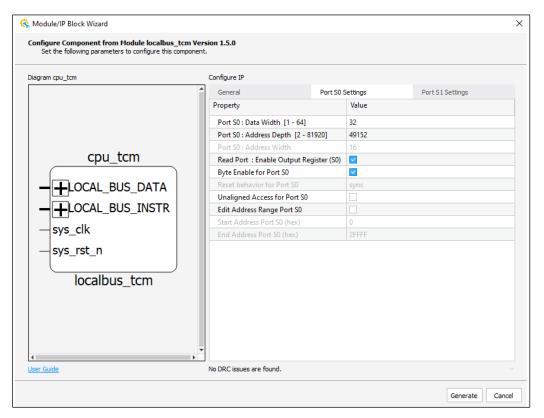

#### 3.1.11. Tightly Coupled Memory

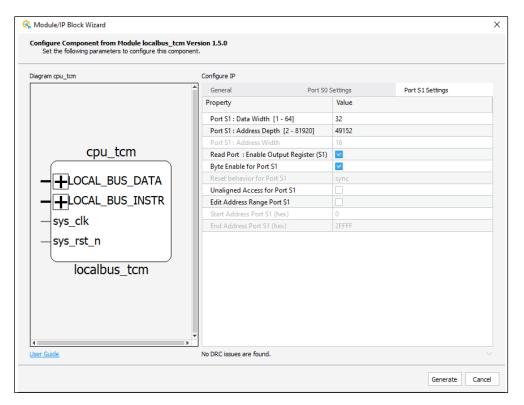

The Tightly Coupled Memory (TCM) IP core is the main memory used by the RISC-V processor. The RISC-V processor reads the instructions stored in this memory via the local bus memory interface and execute the instructions accordingly. The TCM memory also holds the data required for RISC-V processor execution. This IP core has two local bus interfaces by which the processor can communicate with. The dedicated connection between processor and TCM provides faster reading of instructions and data, and improves the overall system performance. A total of 192 Kb of TCM memory space is available for RISC-V processor usage. The TCM IP core configuration is shown in Figure 3.16, Figure 3.17, and Figure 3.18.

Figure 3.16. TCM General Configuration

Figure 3.17. TCM Port S0 Configuration

Figure 3.18. TCM Port S1 Configuration

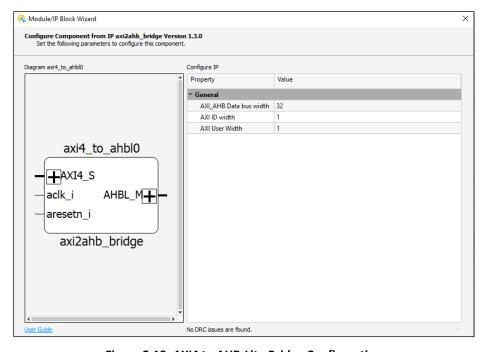

### 3.1.12. AXI4 to AHB-Lite Bridge

The RISC-V RX AXI4-based data interface is used to access and control various peripherals in the system including UART, I2C controller, USB register, and others. The AHB-Lite interconnect is used in this system to arbitrate the access from the RISC-V processor to multiple peripherals subordinate interfaces. Therefore, you must convert the processor AXI4 interface to AHB-Lite using the AXI4 to AHB-Lite Bridge IP. This IP has configurations shown in the figure below.

Figure 3.19. AXI4 to AHB-Lite Bridge Configuration

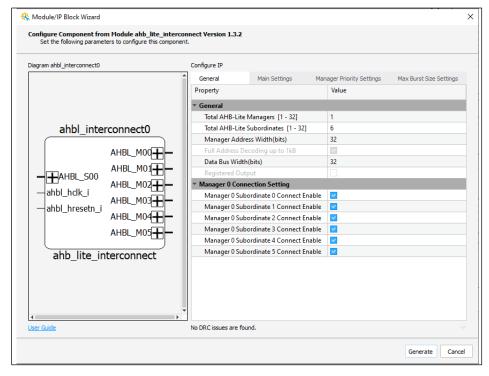

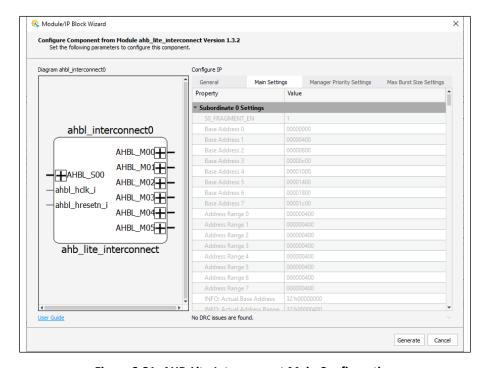

#### 3.1.13. AHBL Interconnect

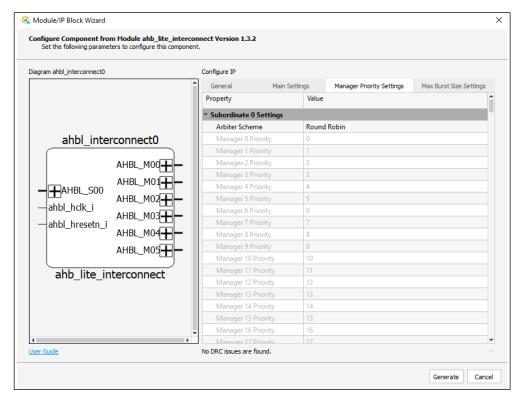

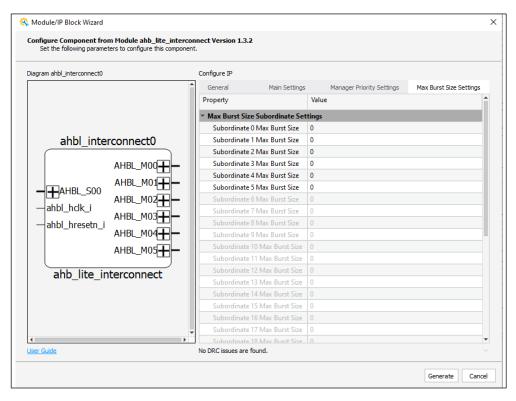

This IP provides the communication interface between RISC-V RX processor and peripherals (UART, I2C Controller, IEBM, RISCV to TDP RAM bridge and USB AHB-Lite to LMMI bridge) which supports AHB-Lite interface. Figure 3.20, Figure 3.21, Figure 3.22, and Figure 3.23 show the AHB-Lite interconnect configuration.

Figure 3.20. AHB-Lite Interconnect General Configuration

Figure 3.21. AHB-Lite Interconnect Main Configuration

Figure 3.22. AHB-Lite Interconnect Manager Priority Settings

Figure 3.23. AHB-Lite Interconnect Max Burst Settings

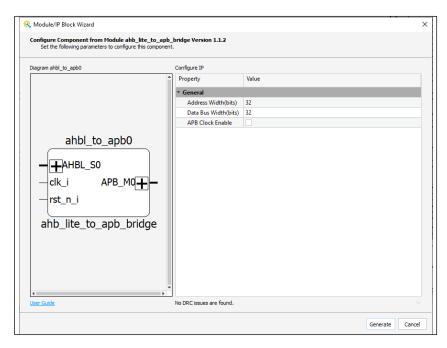

#### 3.1.14. AHB-Lite to APB Convertor

The AHB-Lite to APB bridge provides an interface between the AHB-Lite manager and APB subordinate. Read-and-write transfers on the AHB-Lite are converted into equivalent transfers on the APB. This conversion is required to allow the RISC-V RX processor access to APB-based peripherals such as UART and I2C controller. The AHB-Lite to APB Convertor IP core configuration is shown in the figure below.

Figure 3.24. AHB-Lite to APB Configuration

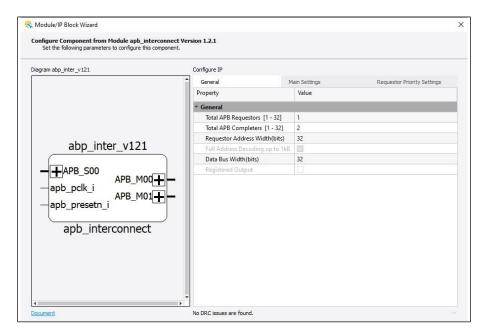

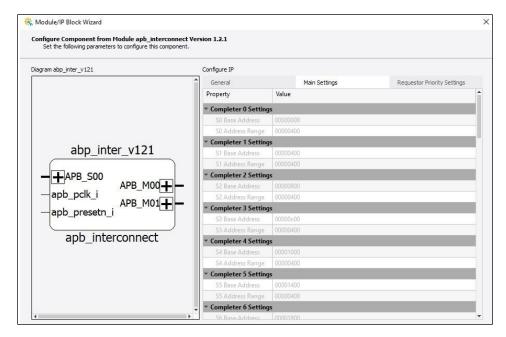

#### 3.1.15. APB Interconnect

The APB Interconnect IP arbitrate RISC-V processor manager access to various subordinates in the system such as the UART and I2C Controller that support the APB interface. The APB interconnect configuration is shown in Figure 3.25 and Figure 3.26.

Figure 3.25. APB Interconnect General Configuration

Figure 3.26. APB Interconnect Main Settings Configuration

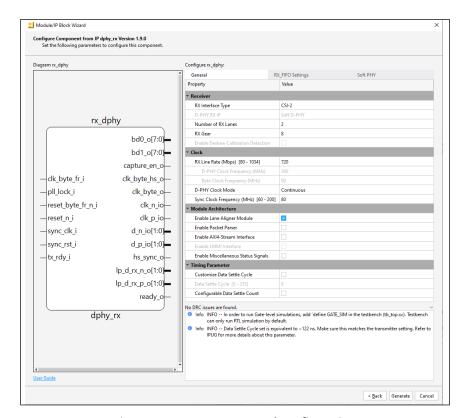

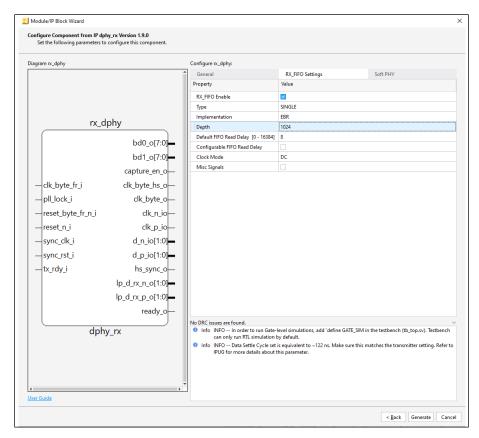

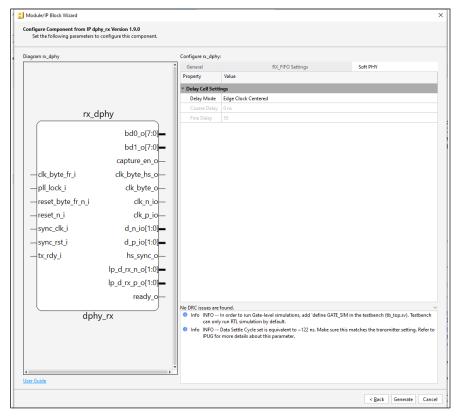

## 3.1.16. CSI-2/DSI D-PHY Receiver

The CSI-2/DSI D-PHY Receiver IP core converts the CSI-2 data from the Raspberry Pi MIPI camera to 8-bit data for the subsequent processing in the FPGA. The MIPI camera sensor data enters FPGA in serial form and this IP converts those serial data into parallel by following MIPI CSI-2 protocol. The IP configuration is shown in Figure 3.27, Figure 3.28, and Figure 3.29.

Figure 3.27. RX DPHY General Configuration

Figure 3.28. RX DPHY RX FIFO Configuration

Figure 3.29. RX DPHY Soft PHY Configuration

#### 3.1.17. MIPI Packet Decoder

This module decodes the data packet from the camera sensor that is received via the RX D-PHY interface. These packets include data, control, synchronization, and configuration information. After decoding the packets, the RAW10 data is passed to the Byte-to-Pixel Converter IP core. This module is a custom block that is not part of Lattice IP in the IP Catalog Server.

## 3.1.18. Byte-to-Pixel Converter IP Core

The Byte-to-Pixel Converter IP core converts the incoming RAW10 data (from MIPI Packet Decoder) into pixel format. It receives raw bytes from a parser and rearranges them to output pixels. This module outputs 2-Pixels (each pixel of 10-bit) in one clock with a valid signal and its configuration is shown in the figure below.

Figure 3.30. Byte-to-Pixel Configuration

### 3.1.19. Byte-to-Pixel (B2P) to AXI Stream Conversion

This module converts the pixel data according to the AXI Stream protocol to meet Lattice Debayer AXI Stream input requirement. This module act as a bridge between the Lattice Byte-to-Pixel Converter IP core and Lattice Debayer IP core. This module is a custom block that is not part of Lattice IP in the IP Catalog Server.

#### 3.1.20. Debayer IP Core

The camera sensor produces pixel data in Bayer format. The Debayer IP core extracts the red, green, and blue (RGB) component from the Bayer data. The Debayer converts RAW10 image data into an RGB component and its configuration is shown in the figure below.

Figure 3.31. Debayer Configuration

Figure 3.32. Debayer Configuration – Test Configuration

#### 3.1.21. AXI Stream to Parallel Conversion

This module converts the AXI Stream protocol signal to parallel data. In this design, this module acts as a bridge between the Lattice Debayer IP core and Lattice CSC IP core. This module is a custom block that is not part of Lattice IP in the IP Catalog Server.

#### 3.1.22. Pixel Data Conversion

Multiple conversion modules are used (as shown in Figure 3.1) after the Byte-to-Pixel Converter IP to convert the RAW10 pixel data into different formats such as Bayer8, Bayer10 Packed, and Bayer 10. This module is a custom block that is not part of Lattice IP in the IP Catalog Server.

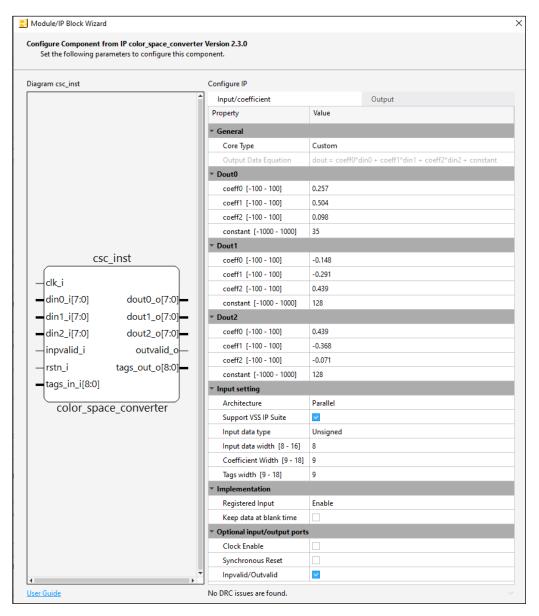

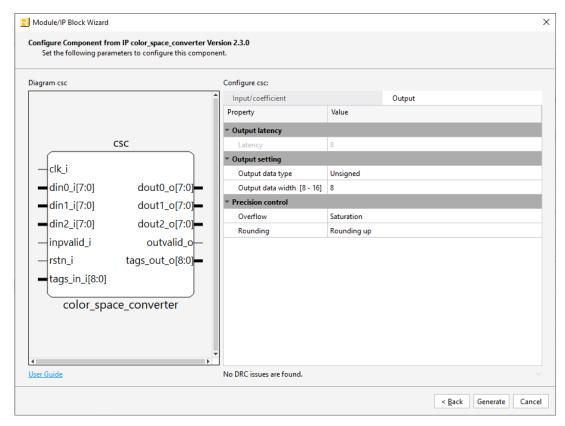

## 3.1.23. Color Space Converter

This IP block converts RGB data into YUV format and its configuration is shown in Figure 3.33 and Figure 3.34

Figure 3.33. Color Space Converter Configuration

Figure 3.34. Color Space Converter Configuration - Output and Precision Control

## 3.1.24. YUV422 to UVC Bridge

This module features an internal DC-FIFO called YUV422 FIFO that is designed to store incoming YUV422 data along with associated data indicator codes. The FIFO Write interface works on Pixel Clock and the Read interface works on the IEBM clock. The YUV422 FIFO plays a critical role in managing and buffering video data, ensuring smooth data flow and processing. This module is a custom block that is not part of Lattice IP in the IP Catalog Server.

### 3.1.25. YUV422 Test Pattern Generator

This block generates the YUY422 solid color test pattern. It allows generating test pattern to test the video to USB path in this design. The video data source selection can be made in the Host PC via the Pleora eBUS Player software, to either selecting the camera sensor (for YUV422 format) or this pattern generator video data. A multiplexer is implemented in the design to facilitate this selection.

#### 3.1.26. IEBM IN FIFO Interface

When the IEBM block grants permission to write the data, the IN FIFO controller module initiates the process. It reads the data from the YUV422 FIFO of the YUV422 to UVC Bridge, where the video data is temporarily stored and write into the IEBM buffers.

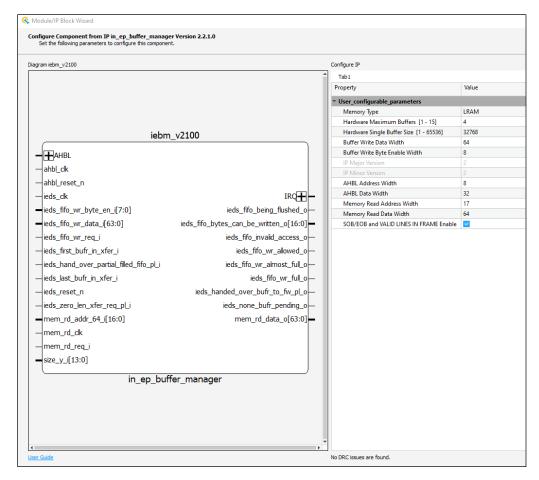

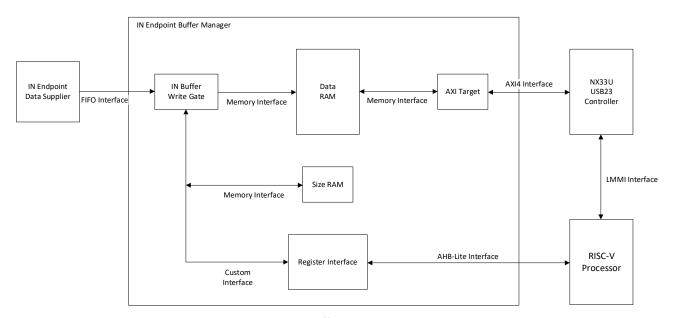

## 3.1.27. In Endpoint Buffer Manager (IEBM)

The IEBM is responsible for managing the IN endpoint buffers for the USB23 Controller. It handles the efficient and orderly flow of video data from the camera sensor or a test pattern generator. The data is written into different buffers sequentially through the First-In-First-Out (FIFO) interface. Once the data is available in these buffers, the USB23 Controller reads it through the AXI interface. This entire process, from managing the FIFO writes to facilitating the AXI reads, is managed by this IEBM module. The IEBM IP configuration is shown in the figure below.

FPGA-RD-02319-1.0

Figure 3.35. IEBM Configuration

The IEMB has an AHB-Lite based interface for accesses to its registers. This interface is connected to the RISC-V RX for control via firmware. The FIFO interface on the IEBM is configured as 64 bit in this design, and it is connected to the IN FIFO block described in the previous section. The FIFO interface is used to supply the video data into the IEBM before it is retrieved by the USB23 Controller to perform IN Endpoint transfer upon request by the Host PC. The USB23 Controller reads data out from the IEBM via the Memory Native interface.

The Appendix B section describes the details of the IEBM IP core.

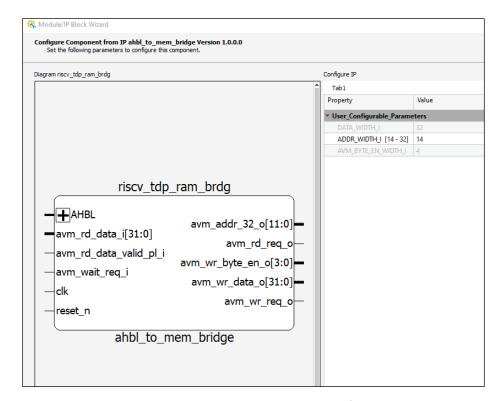

#### 3.1.28. TDP Memory and AHB-Lite to Memory Bridge

This block helps the RISC-V data manager to access True Dual Port memory that is dedicated for USB operations. This block converts AHB-Lite subordinate signals in to native memory manager interface signals. True Dual Port (TDP) memory is used as communication between the RISC-V firmware and the USB23 Controller for operations such as control data and USB events handling, creating USB3 Vision leader and trailer data and others. The TDP memory has 32-bit and 64-bit data interfaces for RISC-V and USB23 Controller accesses respectively, and these interfaces are not AMBA AHB-Lite based. Hence, the AHB-Lite to Memory Bridge IP is used to allow the RISC-V processor access to the TDP memory. The IP configuration is shown in the figure below.

Figure 3.36. AHB-Lite to Memory Bridge Configuration

## 3.1.29. U3V Register Interface

This is an AHB-Lite register interface module for USB3 Vision registers set. The U3V Register interface stores user configuration during runtime such as the image format, image height and width, test pattern enable, and others. This module is a custom block that is not part of Lattice IP in the IP Catalog Server.

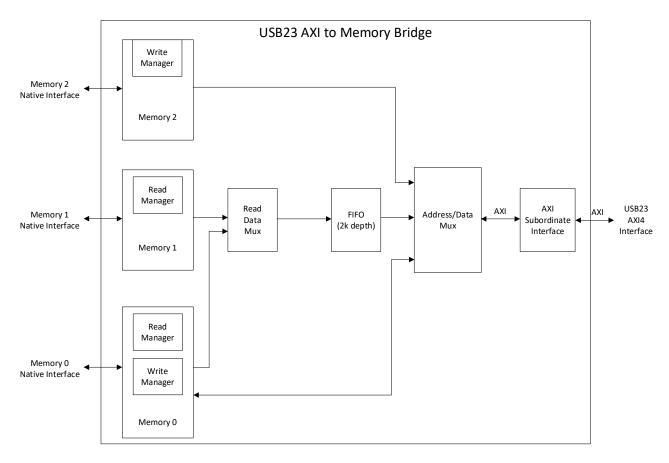

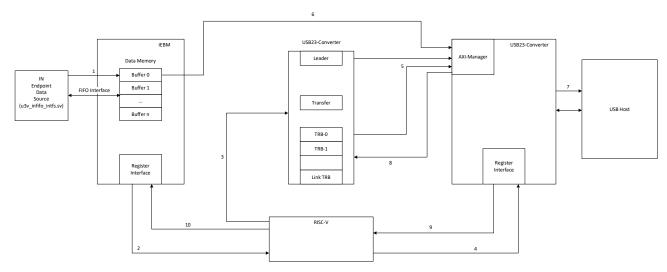

## 3.1.30. USB23 AXI Manager to Memory Interface Bridge

This section describes the architecture, functionality, and other technical information of the USB23 AXI manager to memory interface bridge. This bridge enables the conversion of AXI4 transfer signals into the native memory interface, which is crucial for performing read-and-write operations with the TDP memory. The USB23 Controller uses this path to access data provided by the RISC-V processor. Furthermore, the bridge offers a secondary memory interface that allows the USB23 controller to retrieve data from the IEBM data RAM.

#### 3.1.30.1. USB23 AXI Manager to Memory Bridge Architecture

The architecture of the USB23 AXI manager to memory bridge is shown in the figure below. The bridge can be configured to have native memory read-only and write-only interfaces. The read-only interface is used to read data from buffer that corresponds to a USB IN Endpoint, while the write-only interface writes data into a buffer that corresponds to a USB OUT Endpoint. In this reference design, only one IN Endpoint is used for streaming the video data, therefore it is configured to have only the read-only interface.

Figure 3.37. USB23 AXI Bridge to Memory Bridge Architecture

# 3.1.30.2. Block Description

The functional blocks are described in the following sections.

# **AXI Subordinate Interface**

The AXI subordinate interface is connected to the AXI4 bus of the USB23 Controller.

### Address/Data Mux

This block decodes the write address or read address of the specific memory block.

#### **FIFO**

This FIFO acts as the intermediate storage when the AXI manager is not ready to accept data. The FIFO size is 2048 KB, 256 in depth, and 64-bits data width.

### **Read Data Mux**

This block decodes the memory block that requires a read operation based on the read address.

### Memory 0

This block contains both a write manager and a read manager, enabling it to perform both read-and-write operations.

#### Memory 1

This block contains a read manager that is designed to handle read operations.

### Memory 2

This block contains a read manager that is designed to handle read operations.

### 3.1.30.3. IP Core Port and Parameters

This section provides details of the USB23 AXI manager to Memory Bridge IP ports and interface.

### **Clock and Global Reset**

The table below describes ports for clock and global reset.

**Table 3.1. Clock and Reset Ports**

| Signal Name | Width | Direction | Description               |  |

|-------------|-------|-----------|---------------------------|--|

| clk         | 1     | Input     | Global clock.             |  |

| reset_n     | 1     | Input     | Global reset, active low. |  |

# **Native Memory Interface**

The table below describes ports for the native memory interface.

**Table 3.2. Native Memory Interface Ports**

| Signal Name  | Width | Direction | Description        |  |

|--------------|-------|-----------|--------------------|--|

| wr_req_o     | 1     | Input     | Write request.     |  |

| wr_addr_8_o  | 18    | Output    | Write address.     |  |

| wr_data_o    | 64    | Output    | Write data.        |  |

| wr_byte_en_o | 8     | Output    | Write byte enable. |  |

| rd_data_i    | 64    | Input     | Read data.         |  |

| rd_req_o     | 1     | Output    | Read request.      |  |

| rd_addr_8_o  | 18    | Output    | Read address.      |  |

## **AXI4 Interface**

The table below describes ports of the native AXI4 interface.

**Table 3.3. AXI4 Interface Ports**

| Signal Name       | Width | Direction | Description                                                                                                                 |  |

|-------------------|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------|--|

| axis_mi_awid_i    | 8     | Input     | Write Transaction ID: A unique identifier for the write transaction.                                                        |  |

| axis_mi_awaddr_i  | 32    | Input     | Write Address: The address of the write operation. It is used by the subordinate to determine where to write data.          |  |

| axis_mi_awlen_i   | 8     | Input     | Write Burst Length: The number of transfers in a burst that is measured in bytes.                                           |  |

| axis_mi_awsize_i  | 3     | Input     | Write Burst Size: The size of each transfer in the burst, such as 8 bit, 16 bit, and 32 bit.                                |  |

| axis_mi_awburst_i | 2     | Input     | Write Burst Type: The type of burst transfer, such as fixed, incrementing, or wrapping.                                     |  |

| axis_mi_awvalid_i | 1     | Input     | Write Address Valid: Indicates that a valid write address is available from manager.                                        |  |

| axis_mi_awready_o | 1     | Output    | Write Address Ready: Indicates that the subordinate is ready to accept the write address.                                   |  |

| axis_mi_wdata_i   | 64    | Input     | Write Data: The data being written to the subordinate. The subordinate stores this data at the address specified in AWADDR. |  |

| axis_mi_wstrb_i   | 8     | Input     | Write Strobes: A set of byte-enable signals that indicate which bytes of the data are valid for writing.                    |  |

| axis_mi_wlast_i   | 1     | Input     | Write Last: This signal indicates the last transfer in a write burst.                                                       |  |

| axis_mi_wvalid_i  | 1     | Input     | Write Data Valid: Indicates that valid data is available on the WDATA bus for the subordinate.                              |  |

| axis_mi_wready_o  | 1     | Output    | Write Data Ready: Indicates that the subordinate is ready to accept the write data.                                         |  |

| Signal Name       | Width | Direction | Description                                                                                                                                 |  |

|-------------------|-------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| axis_mi_bid_o     | 8     | Output    | Write Transaction ID: A unique identifier for the write transaction that is used to match the response with the request.                    |  |

| axis_mi_bresp_o   | 2     | Output    | Write Response: The status of the write operation. It can indicate a successful operation represented by OKAY, or an error, such as SLVERR. |  |

| axis_mi_bvalid_o  | 1     | Output    | Write Response Valid: Indicates that the subordinate has a valid response for the write transaction.                                        |  |

| axis_mi_bready_i  | 1     | Input     | Write Response Ready: Indicates that the manager is ready to receive the write response from the subordinate.                               |  |

| axis_mi_arid_i    | 8     | Input     | Read address ID: This signal is the identification tag for the read address group of signals.                                               |  |

| axis_mi_araddr_i  | 32    | Input     | Read address: The read address gives the address of the first transfer in a read burst transaction.                                         |  |

| axis_mi_arlen_i   | 8     | Input     | Burst length: This signal indicates the exact number of transfers in a burst.                                                               |  |

| axis_mi_arsize_i  | 3     | Input     | Burst size: This signal indicates the size of each transfer in the burst.                                                                   |  |

| axis_mi_arburst_i | 2     | Input     | Burst type: The burst type and the size information determine how the address for each transfer within the burst is calculated.             |  |

| axis_mi_arvalid_i | 1     | Input     | Read address valid: This signal indicates that the channel is signaling valid read address and control information.                         |  |

| axis_mi_arready_o | 1     | Output    | Read address ready: This signal indicates that the subordinate is ready to accept an address and associated control signals.                |  |

| axis_mi_rready_i  | 1     | Input     | Read Data Ready: Indicates that the manager is ready to accept read data from the subordinate.                                              |  |

| axis_mi_rid_o     | 8     | Output    | Read Transaction ID: A unique identifier for the read transaction that is used to match the response with the request.                      |  |

| axis_mi_rdata_o   | 64    | Output    | Read Data: The data being read from the subordinate. The manager reads this data at the address specified in ARADDR.                        |  |

| axis_mi_rresp_o   | 2     | Output    | Read Response: The status of the read operation. It can indicate a successful operation, represented by OKAY, or an error, such as SLVERR.  |  |

| axis_mi_rlast_o   | 1     | Output    | Read last: This signal indicates the last transfer in a read burst.                                                                         |  |

| axis_mi_rvalid_o  | 1     | Output    | Read Data Valid: Indicates that valid read data is available for the manager to read.                                                       |  |

# 3.1.31. Dual Boot Wrapper

This dual boot wrapper module consists of the following IP or modules that are responsible for the dual boot functionality, which has been added in the design:

- Internal oscillator—This IP is an oscillator module. It generates clock sources, sys\_clk and lmmi\_clk, to the LMMI host controller and CONFIG\_LMMIA primitive.

- CONFIG\_LMMIA—Lattice Memory Mapped Interface (LMMI) interfaces to the configuration block.

- LMMI Host Controller—This controller implements a state machine controller to send the necessary commands to the CONFIG\_LMMIA block, and sends the boot address to the MULTIBOOT primitive to boot the desired alternate pattern stored in the internal or external SPI flash.

- MULTIBOOT Primitive—This primitive is a wrapper for the interface to perform the multi-boot functionality. It

enables the booting to load the desired alternate pattern through sending the Refresh command to the

CONFIG LMMIA block.

For more information about the dual boot feature, refer to the Multi-Boot User Guide for Nexus Platform (FPGA-TN-02145).

# 3.2. Clocking Scheme

The CrossLinkU-NX USB3 Vision Reference Design use a PLL to generate the 90 MHz system clock, 80 MHz pixel clock for image signal processing and 60 MHz USBPHY clock. All these clocks are generated from the 60 MHz crystal oscillator on LIFCL-33U Evaluation Board. An overview of the design clocking scheme is shown in the figure below.

Figure 3.38. USB3 Vision Reference Design Clocking Scheme

# 3.3. Reset Scheme

The overview of reset scheme for U3V Reference Design is shown in Figure 3.39. The following table summarizes the reset domains in the design.

**Table 3.4. Reset Domains**

| Reset                    | Source                                                                    | Destination                                                                                           |

|--------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| cpu_reset_n_90m          | PLL lock signal synchronized to PLL clkos_o (CPU clock).                  | RISC-V CPU rstn_i and MIPI RX DPHY.                                                                   |

| riscv_system_reset_n     | RISC-V RX.                                                                | All components in the Propel software subsystem.                                                      |

| riscv_system_reset_n_90m | riscv_system_reset_n synchronized to PLL clkos_o (CPU clock).             | USB23 Controller and the AXI Bridge subsystem,<br>YUV422 to UVC Bridge and IEBM In FIFO<br>interface. |

| pixel_clk_reset_n        | riscv_system_reset_n synchronized to PLL clkos2_o (Pixel clock).          | All video IP in the U3V subsystem.                                                                    |

| mipi_byte_clk_reset_n    | riscv_system_reset_n synchronized to clk_byte_hs_o from the MIPI RX DPHY. | MIPI packet decoder and Byte-to-Pixel Converter IP.                                                   |

Figure 3.39. Reset Scheme

# 3.4. Design Operations

This section describes the design operations of the reference design.

# 3.4.1. USB3 Vision Enumeration

USB3 Vision is an interface standard for industrial cameras using USB 3.0. The enumeration process of a USB3 Vision device follows the standard USB enumeration process with additional steps specific to the USB3 Vision protocol.

After the physical connection is established, the following USB standard enumeration process occurs:

- Device Detection:

- The host detects the presence of the USB3 Vision camera.

- The host issues a Reset on the USB bus to ensure the device is in a known state.

- Device Descriptor Request—The host requests the Device Descriptor (PID, VID, class, and subclass) using GET\_DESCRIPTOR requests. This helps identify the device as a USB3 Vision camera from the class and subclass field sent by the USB device in response to this request.

- Address Assignment—The host assigns a unique address to the device.

- Configuration Descriptor Request—The host requests the Configuration Descriptor to determine available interfaces and endpoints. It sets the device to the configured state.

- Interface Descriptor Processing—The host retrieves the Interface Descriptor supported by the USB3 Vision device, which includes USB class and subclass values specific to USB3 Vision. In response to the interface descriptor request from the USB host, the USB device provides details about the supported interfaces, such as control interface, streaming interface, event interface, and so on.

After the standard USB enumeration is completed, the host software (such as a USB3 Vision-compliant) interacts with the camera using GenICam and USB3 Vision Protocol.

The following list describes the USB3 Vision specific enumeration:

- Discovery of USB3 Vision Camera:

- The host software checks if the device supports USB3 Vision Protocol by reading the GenICam XML Descriptor.

- The XML file describes the camera register map, features, and control parameters.

- Vendor-Specific Control Transfers:

The host sends Vendor-Specific Requests over Control Transfers (Endpoint 0) to:

- Read the device capabilities.

- Retrieve the GenICam XML file.

- Configure the camera operational settings.

- Bulk Endpoints Setup

The USB3 vision device exposes Bulk IN and Bulk OUT endpoints:

- Bulk IN Endpoint: Used for streaming image data to the host.

- Bulk OUT Endpoint: Used for sending control commands to the camera.

After the camera is enumerated, the USB host queries the supported pixel formats, resolutions, and frame rates. The camera can be configured dynamically via the GenlCam interface. The host can start image acquisition by triggering data transfer over bulk endpoints. Then USB3 vision device starts sending the camera data over the BULK IN endpoints and the USB host software processes the data in real time.

### 3.4.2. USB3 Vision Interfaces

This section intends to give user basic information about USB3 Vision design data flow from USB perspective. The USB3 Vision Interfaces implemented in this reference design follows the definition in USB3 Vision Specifications. This reference design assumes that you have basic familiarity with USB3 Vision standard and USB interface.

This reference design has the following interfaces:

- Device Control Interface (DCI)

- Device Event Interface (DEI)

- Device Streaming Interface (DSI)

These interfaces are discussed in the following subsections.

## 3.4.2.1. Device Control Interface

This interface is used to control the USB3 Vision aspects of the device. It follows the Generic Control Protocol (GenCP), which is part of the GenlCam Standard.

The following register maps are required and defined in the USB3 Vision design. All these registers are managed via the DCI:

- Technology Agnostic Bootstrap Register Map (ABRM)

- Technology Specific Bootstrap Register Map (SBRM)

- Event Interface Register Map (EIRM)

- Streaming Interface Register Map (SIRM)

Refer to USB3 Vision specification on details about each of these registers.

In this reference design, the USB3 Vision registers are implemented as structures in the RISC-V Zephyr firmware code. The structures are defined in the *usbd u3v.c* file that includes U3VABRM, U3VSBRM, U3VEIRM, and U3VSIRM.

The offset of these registers are defined in the *usbd\_u3v.h* file and are listed below:

The first 64 KB of the bootstrap register map is used for ABRM. Therefore, ABRM has base offset 0x0. While rest register maps can be started on a free manufacturer-specific address space after address 0xFFFF.

To read or write any register, the host sends command over Bulk OUT endpoint and device responses to that command over Bulk IN endpoint. In this reference design, the RISC-V firmware decodes command packet received over OUT endpoint, takes necessary action, and prepares response to be sent over IN endpoint. For more information, refer to the Control and Event Channel Protocol section.

#### 3.4.2.2. Device Event Interface

This interface is used to pass transmission of asynchronous events from the device to the host. Events are generated only when the *Event Enable* flag in El Control Register (part of EIRM) is set.

This reference design supports two types of events:

- U3V Event Test—This is used to test device event interface. This is sent when *TriggerEventTest* bit in Event Test Control register (part of EIRM) is set.

- Start of Frame event test—This is used to send event at the start of frame. This is controlled via its corresponding event notification register. This register is a part of XML-based registers.

One Bulk IN endpoint is used to send event packets to the host. The RISC-V firmware prepares data for this Bulk IN endpoint. Based on request received from the host via the DCI, the firmware decides when this event is sent. For more information on how protocols are used, refer to the Control and Event Channel Protocol section.

### 3.4.2.3. Device Streaming Interface

This interface is used to pass video streaming data. One Bulk IN endpoint is used to pass this data. Registers controlling this interface are defined in SIRM.

The *Stream Enable* flag that is available in the SI control register (part of SIRM) is used to control streaming. The host sets the *Stream Enable* bit to start streaming. Once that is set, the device streams data over the stream endpoint. When the host wants to stop streaming, it clears the *Stream Enable* bit.

When you start the video streaming using any U3V application (such as eBUS Player), the host sends a command to enable the *Stream Enable* flag. When you stop the streaming from any U3V application, the host sends a command to clear the *Stream Enable* flag. Follow the same method described earlier to perform register access via the DCI.

To allow the separation of user requested payload data and USB3 Vision protocol specific data, USB3 Vision standard uses the concept of a *leader - payload - trailer* data sequence. Streaming control registers (SIRM) are used to pass information about leader/payload/trailer layout. These registers are also controlled via the DCI. Refer to the U3V specification to get idea about various registers related to this.

Image resolution and pixel format can also be changed from a U3V application if supported by the device. This reference design supports this feature. Registers controlling image resolution and pixel format are part of XML-based registers. Based on XML file content, U3V application knows which registers to be updated whenever you update image resolution and/or pixel format. These registers are accessed via the DCI.

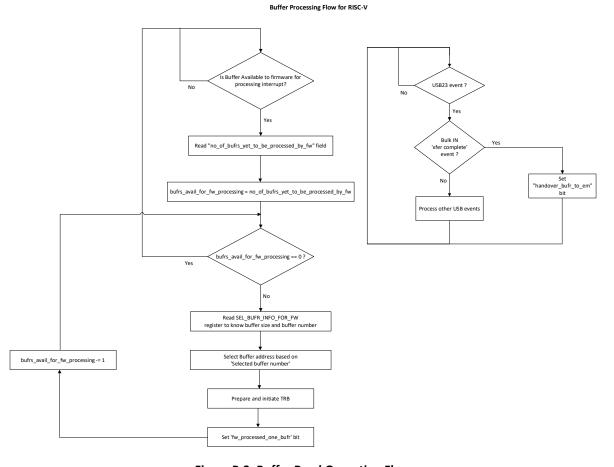

# 3.4.3. Streaming Data Transfer via IEBM

This section provides a high-level overview of how streaming data from a camera sensor or test pattern generator module is transmitted to a USB host. Kindly have a look at the following image.

Figure 3.40. Data Flow During Streaming

The IEBM block is configured to accept data from the IN endpoint data source.

Based on the figure above, the streaming data transfers happen in the following sequences:

- Data from the IN endpoint data source is written into the internal buffer of the IEBM via the FIFO interface.

Information about the start of frame and end of frame is also passed to the IEBM to facilitate preparation of Leader and Trailer data.

- 2. After a buffer is filled, the IEBM generates an interrupt to the RISC-V processor. Meanwhile, if the IEBM has a free buffer available, it switches to that buffer, allowing the IN endpoint data source to continue filling data via the FIFO interface.