# SLVS-EC to MIPI CSI-2 with CertusPro-NX Devices

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                            | 3  |

|-------------------------------------|----|

| Acronyms in This Document           | θ  |

| 1. Introduction                     |    |

| 1.1. Supported Device and IP        |    |

| 1.2. Features List                  |    |

| 1.3. Block Diagram                  |    |

| 1.4. Functional Description         | 8  |

| 1.5. Conventions                    | 8  |

| 1.5.1. Nomenclature                 | 8  |

| 1.5.2. Data Ordering and Data Types | 8  |

| 1.5.3. Signal Names                 | g  |

| 2. Parameters and Port List         | 10 |

| 2.1. Synthesis Directives           | 10 |

| 2.2. Simulation Directives          | 10 |

| 2.3. Top-Level I/O                  | 11 |

| 3. Design and Module Description    | 13 |

| 3.1. rx_slvs_ec                     | 13 |

| 3.2. p2b                            | 14 |

| 3.3. slvsec_to_p2b                  | 15 |

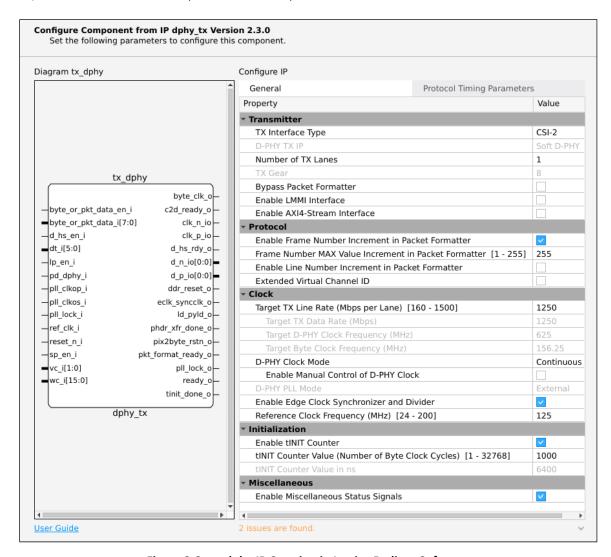

| 3.4. tx_dphy                        | 17 |

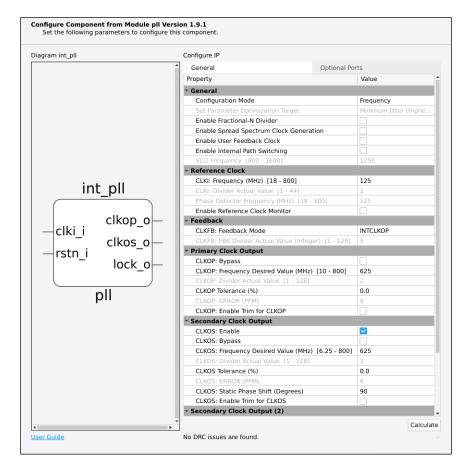

| 3.5. int_pll                        | 18 |

| 4. Design and File Modifications    | 20 |

| 4.1. Top-level RTL                  | 20 |

| 5. Design Simulation                | 21 |

| 6. Known Limitations                | 23 |

| 7. Design Package and Project Setup | 24 |

| 8. Resource Utilization             | 25 |

| References                          | 26 |

| Technical Support Assistance        | 27 |

| Revision History                    | 28 |

# **Figures**

| Figure 1.1. SLVS-EC to MIPI Reference Design Block Diagram                     | 8  |

|--------------------------------------------------------------------------------|----|

| Figure 1.2. Camera Sensor Parallel Input Bus Waveform                          |    |

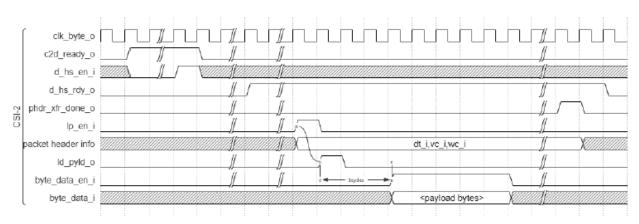

| Figure 3.1. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2 Interface | 13 |

| Figure 3.2. rx_slvs_ec IP Creation in Lattice Radiant Software                 | 14 |

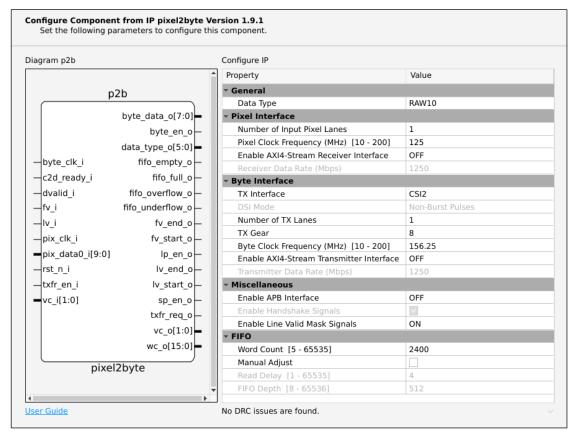

| Figure 3.3. p2b IP Creation in Lattice Radiant Software                        | 15 |

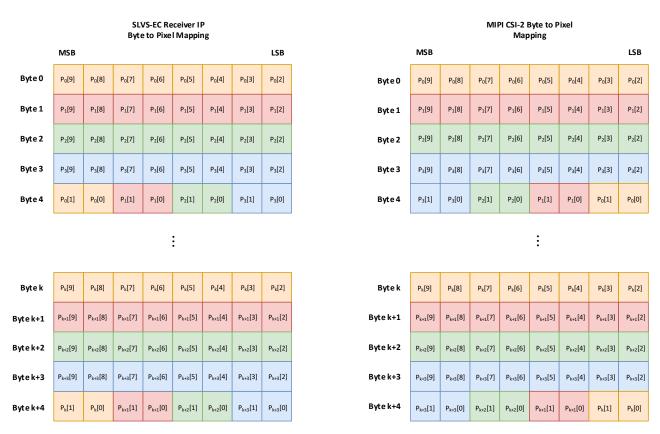

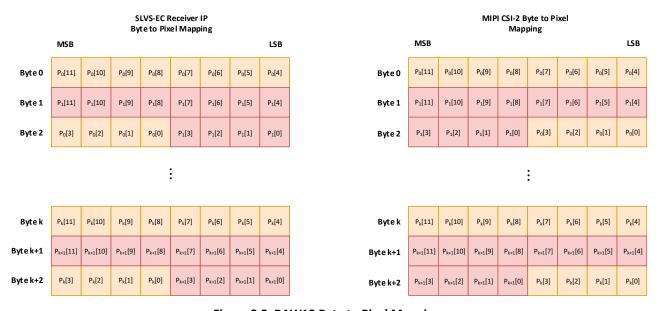

| Figure 3.4. RAW10 Byte to Pixel Mapping                                        | 16 |

| Figure 3.5. RAW12 Byte to Pixel Mapping                                        | 16 |

| Figure 3.6. tx_dphy IP Creation in Lattice Radiant Software                    | 17 |

| Figure 3.7. int_pll IP Creation in Lattice Radiant Software                    | 19 |

| Figure 5.1. Simulation Done Statement                                          | 21 |

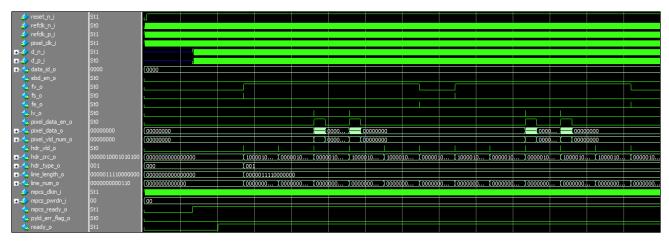

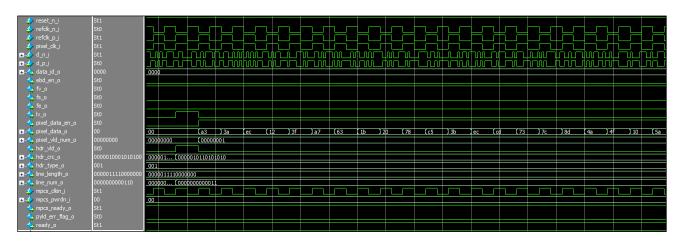

| Figure 5.2. Simulation Waveform for CSI-2 (1/2)                                |    |

| Figure 5.3. Simulation Waveform for CSI-2 (2/2)                                | 22 |

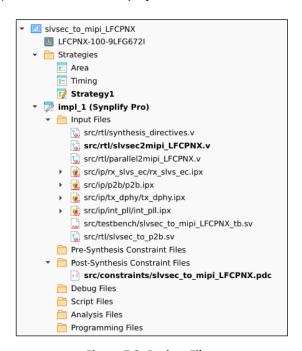

| Figure 7.1. Directory Structure                                                | 24 |

| Figure 7.2. Project Files                                                      | 24 |

## **Tables**

| Table 1.1. Supported Device and IP              | 7  |

|-------------------------------------------------|----|

| Table 1.2. Pixel Data Order                     |    |

| Table 2.1. Synthesis Directives                 |    |

| Table 2.2. Simulation Directives                |    |

| Table 2.3. SLVS-EC to MIPI Top Level I/O        | 11 |

| Table 6.1. Combinations of RX SLVS EC Data Type |    |

| Table 8.1. Resource Utilization Examples        |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                                          |

|---------|-----------------------------------------------------|

| APB     | Advanced Peripheral Bus                             |

| AXI4    | Advanced eXtensible Interface Version 4             |

| CMOS    | Complementary Metal-Oxide-Semiconductor             |

| CRC     | Cyclic Redundancy Check                             |

| CSI-2   | Camera Serial Interface 2                           |

| D-PHY   | Physical Layer                                      |

| DPI     | Display Pixel Interface                             |

| DSI     | Display Serial Interface                            |

| DT      | Data Type                                           |

| EBR     | Embedded Block RAM                                  |

| ECC     | Error Correction Code                               |

| EoT     | End of Transmission                                 |

| ЕоТр    | End of Transmission Packet                          |

| FF      | Flip-Flop                                           |

| GPLL    | General Purpose PLL                                 |

| HDL     | Hardware Description Language                       |

| HS      | High Speed                                          |

| IP      | Intellectual Property                               |

| LSB     | Least Significant Bit                               |

| LP      | Low Power                                           |

| LUT     | Look Up Table                                       |

| LVDS    | Low-Voltage Differential Signaling                  |

| LVCMOS  | Low-Voltage Complementary Metal-Oxide-Semiconductor |

| MIPI    | Mobile Industry Processor Interface                 |

| MSB     | Most Significant Bit                                |

| P2B     | Pixel2Byte                                          |

| PLL     | Phase Locked Loop                                   |

| PMA     | Physical Medium Attachment                          |

| RX      | Receiver                                            |

| SLVS-EC | Scalable Low Voltage Signaling with Embedded Clock  |

| TX      | Transmitter                                         |

| VC      | Virtual Channel                                     |

| WC      | Word Count                                          |

## 1. Introduction

The Mobile Industry Processor Interface (MIPI®) D-PHY is developed primarily to support camera and display interconnections in mobile devices, and it has become the industry's primary high-speed PHY solution for these applications in smartphones. It is used in conjunction with MIPI camera serial interface-2 (CSI-2) and MIPI display serial interface (DSI) protocol specifications. It meets the demanding requirements of low power, low noise generation, and high noise immunity that mobile phone designs demand.

MIPI D-PHY is a practical PHY for the typical camera, display applications and designed to replace traditional parallel buses based on low-voltage complementary metal-oxide-semiconductor (LVCMOS) or low-voltage differential signaling (LVDS). However, many processors and displays/cameras still use RGB, complementary metal-oxide-semiconductor (CMOS), or MIPI display pixel interface (DPI) as an interface.

The scalable low voltage signaling with embedded clock (SLVS-EC) to MIPI reference design allows the quick interface to receive serial data from CMOS Image Sensors and convert the incoming serial data to MIPI CSI-2 data format. The Lattice Semiconductor SLVS-EC to MIPI D-PHY Interface reference design provides this conversion for Lattice Semiconductor CertusPro™-NX devices. This is useful for wearable, tablet, human-machine interfacing, medical equipment, and many other applications.

The reference design is available on the SLVS-EC to MIPI CSI-2 with CertusPro-NX web page.

## 1.1. Supported Device and IP

This reference design supports the following devices with IP versions.

Table 1.1. Supported Device and IP

| Device Family | Part Number         | Compatible IP                            |  |

|---------------|---------------------|------------------------------------------|--|

|               |                     | SLVS-EC Receiver IP version 1.2.3        |  |

| CertusPro-NX  | LFCPNX-100-9LFG672I | Pixel-to-Byte Converter IP version 1.9.1 |  |

|               |                     | D-PHY Transmitter IP version 2.3.0       |  |

The IPs above are supported by the Lattice Radiant™ software version 2025.1 or later.

#### 1.2. Features List

The key features of the SLVS-EC to MIPI Reference Design are:

- Compliant with SLVS-EC Protocol specification v2.0

- Back compatibility with SLVS-EC Protocol specification v1.2

- Compliant with MIPI D-PHY v1.2, and MIPI CSI-2 v1.2 Specifications

- Supports MIPI CSI-2 interfacing up to 5 Gb/s for SLVS-EC and 6 Gb/s for Soft TX D-PHY

- Supports 1, 2, or 4 data lanes

- Supports 1, 2, or 4 MIPI TX D-PHY data lanes

- Supports low-power (LP) mode during the vertical and horizontal blanking

- Supports common MIPI CSI-2 compatible video formats (RAW8, RAW10, RAW12, or RAW16)

## 1.3. Block Diagram

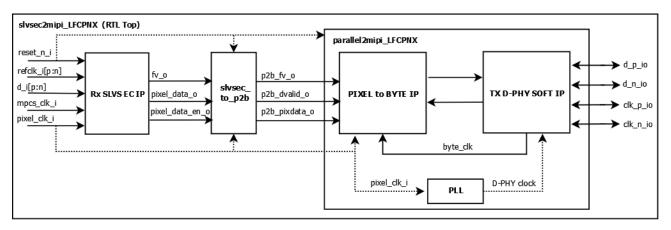

Figure 1.1 shows the block level diagram of the SLVS-EC to MIPI Reference Design.

Figure 1.1. SLVS-EC to MIPI Reference Design Block Diagram

As shown in Figure 1.1, the block level diagram of the SLVS-EC to MIPI reference design mainly consists of the SLVS-EC IP, Pixel to Byte IP, and TX D-PHY IP. The pixel data output from SLVS EC IP given is to slvsec\_to\_p2b module that provides support to feed pixel data to Pixel to Byte IP as per its Byte data output extraction format. In CertusPro-NX devices, TX D-PHY IP uses Soft D-PHY, which requires input clocks that matches with the targeted D-PHY clock frequency, and general purpose PLL (GPLL) used is to create an appropriate TX D-PHY clock frequency.

## 1.4. Functional Description

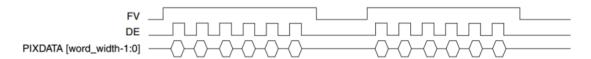

The SLVS-EC to MIPI D-PHY Reference Design converts incoming serial video data from the CMOS image sensor back into MIPI CSI-2 serial data format. The SLVS-EC receiver interface consists of two clock lanes and a configurable number of data lanes and as per the configured data type RAW10, provides frame valid, line valid, and parallel pixel data. The design converts this parallel output further from Pixel to byte and transmits the serial data over MIPI D-PHY lanes using TX-DPHY IP.

Figure 1.2. Camera Sensor Parallel Input Bus Waveform

This serial bus in Figure 1.2 is converted to the appropriate CSI-2 output format. The CSI-2 output serializes HS (High Speed) data, controls LP (Low Power) data, and transfers them through MIPI D-PHY IP. MIPI D-PHY also has a maximum of 5 lanes per channel. It consists of one clock lane and up to 4 data lanes. The maximum D-PHY data rate per lane is 1.5 Gb/s by TX Soft D-PHY IP.

## 1.5. Conventions

#### 1.5.1. Nomenclature

The nomenclature used in this document is based on Verilog Hardware Description Language (HDL). This includes radix indications and logical operators.

#### 1.5.2. Data Ordering and Data Types

The highest bit within a data bus is the most significant bit. 10-bit parallel data is serialized to a 1-bit data stream on each MIPI D-PHY data lane where bit 0 is the first transmitted bit.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Table 1.2 lists pixel data order coming from core module.

#### Table 1.2. Pixel Data Order

| Data Type | Format       |

|-----------|--------------|

| RAW       | RAW [MSB: 0] |

## 1.5.3. Signal Names

Signal names that end with:

- \_n are active low

- \_i are input signals

- Some signals are declared as bidirectional (I/O) but are only used as input. Hence, \_i identifier is used.

- \_o are output signals

- Some signals are declared as bidirectional (I/O) but are only used as output. Hence, \_o identifier is used.

- \_io are bidirectional signals

## 2. Parameters and Port List

There are two directive files for this reference design:

- synthesis\_directives.v used for design synthesis by the Lattice Radiant software and simulation

- simulation\_directives.sv used for simulation

These directives can be modified according to the required configuration. The settings in these files must match SLVS-EC IP, Pixel to Byte IP, and TX D-PHY IP settings created by the Lattice Radiant software.

## 2.1. Synthesis Directives

Table 2.1 shows the synthesis directives that affect this reference design. They are used for both synthesis and simulation. Some restricted parameter selections are by other parameter settings as shown in Table 2.1 and Table 2.2.

**Table 2.1. Synthesis Directives**

| Category                            | Directive             | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                     | NUM_RX_LANE_1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Number of RX Lane                   | NUM_RX_LANE_2         | Only one of these directives must be selected as per SLVS-EC lanes configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                     | NUM_RX_LANE_4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Number of Bits per<br>Pixel lane    | BIT_PER_PIXEL {value} | Number of Bits per Pixel lane for SLVS EC, Set value {n} for Raw{n} data type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Pixel count per line                | LINE_LENGTH {value}   | Number of pixels count in SLVS-EC, Set to 1920.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                     | BAUD_GRADE_1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Baud Grade                          | BAUD_GRADE_2          | Only one of these directives must be selected as per SLVS-EC baud grade configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | BAUD_GRADE_3          | Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| D-PHY Type                          | TX_CSI2               | SLVS-EC supports only CSI-2. Hence, CSI-2 is always used for transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                     | RAW8                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                     | RAW10                 | Type of video data to convert from Serial to Pixel for SLVS-EC and from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Video Data Type                     | RAW12                 | pixel format to byte format for Pixel to Byte converter. Must match with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                     | RAW14                 | SLVS-EC configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | RAW16                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                     | NUM_TX_LANE_1         | Oak and of the self-self-self-self-self-self-self-self-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Number of TX Lane                   | NUM_TX_LANE_2         | Only one of these directives must be selected as per TX DPHY lanes configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                     | NUM_TX_LANE_4         | comigaration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Noveles and Division Dec            | NUM_PIX_LANE_1        | Only and of the section of the secti |  |

| Number of Pixels Per<br>Pixel Clock | NUM_PIX_LANE_2        | Only one of these four directives must be defined, Number of pixels per pixel clock used for the input to the Pixel to Byte converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| FIXEL CIOCK                         | NUM_PIX_LANE_4        | pixel clock used for the hipat to the Fixel to byte converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| TX D-PHY Clock Gear                 | TX_GEAR_8             | TX D-PHY Clock Gear is always Gear 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Miscellaneous                       | TX_CSI2               | Enables internal signals monitored by test-bench. Always ON.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Number of Pixels                    | NUM_PIXELS {value}    | Number of active Pixels per Line, set to 1920.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                     | TX_CLK_MODE_HS_ONLY   | TVD DIV Clock made only one of these two divertives must be defined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Clock Mode                          | TX_CLK_MODE_HS_LP     | TX D-PHY Clock mode, only one of these two directives must be defined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Use GPLL                            | USE_GPLL              | Always defined to generate D-PHY clock frequency for TX D-PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

Note: HS\_LP mode means non-continuous clock mode and HS\_ONLY means continuous clock mode for the TX D-PHY.

#### 2.2. Simulation Directives

Table 2.2 shows the simulation directives for this reference design.

**Table 2.2. Simulation Directives**

| Category                  | Directive          | Remarks                                                     |  |  |

|---------------------------|--------------------|-------------------------------------------------------------|--|--|

| Pixel clock period        | PIX_CLK {value}    | Pixel clock period in ns                                    |  |  |

| Number of video frames    | NUM_FRAMES {value} | Number of video frames to be transmitted                    |  |  |

| Number of lines per frame | NUM_LINES {value}  | Number of active lines per frame                            |  |  |

| Horizontal Front Porch    | HFRONT {value}     | Number of blanking cycles before HSYNC signal is asserted   |  |  |

| Horizontal Back Porch     | HBACK {value}      | Number of blanking cycles after HSYNC signal is de-asserted |  |  |

| Vertical Front Porch      | VFRONT {value}     | Number of blanking lines before VSYNC signal is asserted    |  |  |

| Vertical Back Porch       | VBACK {value}      | Number of blanking lines after VSYNC signal is de-asserted  |  |  |

## 2.3. Top-Level I/O

Table 2.3 shows the top-level I/O of this reference design. Actual I/O depends on your configurations and compiler directives automatically declare all necessary I/O ports.

Table 2.3. SLVS-EC to MIPI Top Level I/O

| Port Name                             | Direction | Description                                                                                                                                                                                                                                 |  |  |

|---------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clocks and Reset                      |           |                                                                                                                                                                                                                                             |  |  |

| pixel_clk_i <sup>1</sup>              | I         | Pixel clock input.                                                                                                                                                                                                                          |  |  |

| reset_n_i                             | 1         | Active low asynchronous reset.                                                                                                                                                                                                              |  |  |

| refclk_p_i                            | T         | Differential Reference Clock, CLK+.                                                                                                                                                                                                         |  |  |

| refclk_n_i                            | I         | Differential Reference Clock, CLK                                                                                                                                                                                                           |  |  |

| mpcs_clkin_i                          | I         | Clock source for physical medium attachment (PMA) in SLVS-EC IP, use 125 MHz.                                                                                                                                                               |  |  |

| mpcs_pwrdn_i                          | I         | PHY power down. 2'b00: Operational. 2'b10: Low-power state. Rx CDRPLL is powered-down. The PHY starts in this low-power mode to perform calibration. 2'b11: Deep low-power state. TX driver is in electrical Idle II (static low). All PLLs |  |  |

| Primary I/O                           |           | are powered down and clock shutdown.                                                                                                                                                                                                        |  |  |

| d_p_i                                 | 1         | Differential Reference Clock, CLK+.                                                                                                                                                                                                         |  |  |

| d_n_i                                 | 1         | Differential Reference Clock, CLK                                                                                                                                                                                                           |  |  |

| setup_i                               | I         | Active high setup signal from Client-side interface to commence start-up for SLVS-EC.                                                                                                                                                       |  |  |

| APB Interface                         |           |                                                                                                                                                                                                                                             |  |  |

| apb_pclk_i                            | 1         | APB clock, Use 125 MHz.                                                                                                                                                                                                                     |  |  |

| apb_preset_n_i                        | 1         | APB active low reset.                                                                                                                                                                                                                       |  |  |

| apb_paddr_i                           | 1         | Address signal.                                                                                                                                                                                                                             |  |  |

| apb_psel_i                            | 1         | Select signal. This indicates that the completer device is selected and a data transfer is required.                                                                                                                                        |  |  |