# MachXO4 Hardened Control Functions Reference Guide

# **Technical Note**

FPGA-TN-02404-1.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

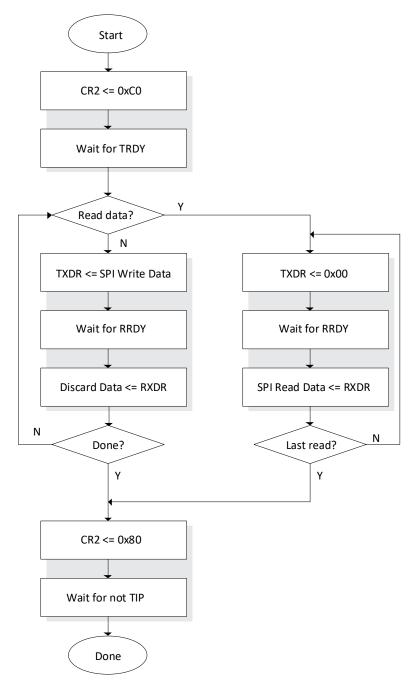

| Abb | reviat | ions in This Document                          | 7  |

|-----|--------|------------------------------------------------|----|

| 1.  | Intro  | ductionduction                                 | 8  |

| 1.  | 1.     | EFB Register Map                               | 9  |

| 1.  | 2.     | WISHBONE Bus Interface                         | 9  |

| 1.  | 3.     | WISHBONE Write Cycle                           | 10 |

| 1.  | 4.     | WISHBONE Read Cycle                            | 11 |

| 1.  | 5.     | WISHBONE Reset Cycle                           | 13 |

| 2.  | Hard   | lened I2C IP Cores                             | 14 |

| 2.  | 1.     | I2C Registers                                  | 14 |

| 3.  | Typic  | cal I2C Transactions                           | 22 |

| 4.  | I2C F  | unctional Waveforms                            | 23 |

| 5.  | I2C T  | iming Diagram                                  | 27 |

| 6.  | I2C S  | imulation Model                                | 28 |

| 7.  | Hard   | lened SPI IP Core                              | 34 |

| 8.  | SPI R  | legisters                                      | 35 |

| 9.  | Typic  | cal SPI Transactions                           | 44 |

| 10. | SPI F  | unctional Waveforms                            | 45 |

| 11. |        | iming Diagrams                                 |    |

| 12. | SPI S  | imulation Model                                | 49 |

| 13. | Hard   | lened Timer/Counter PWM                        | 52 |

| 13  | 3.1.   | Timer/Counter Registers                        | 52 |

| 14. | Time   | r Counter Simulation Model                     |    |

|     |        | n Access                                       |    |

| 15  | 5.1.   | Flash Access Ports                             | 65 |

| 15  | 5.2.   | Flash Access through WISHBONE Target Interface |    |

| 15  | 5.3.   | Command and Data Transfers to Flash Space      |    |

| 15  | 5.4.   | Command Summary by Application                 |    |

| 15  | 5.5.   | Command Descriptions by Command Code           |    |

| 16. | Inter  | face to Flash                                  |    |

| 17. | Com    | mand Framing                                   | 88 |

|     | 7.1.   | I2C Framing                                    |    |

| 17  | 7.2.   | SPI Framing                                    |    |

| 17  | 7.3.   | WISHBONE Framing                               |    |

|     |        | Write and Read Examples                        |    |

|     |        | n Performance                                  |    |

|     |        | e/Program/Verify Time Calculation Example      |    |

|     |        | 25                                             |    |

|     |        | Support Assistance                             |    |

|     |        | listory                                        | 98 |

# **Figures**

| Figure 1.1. Embedded Function Block (EFB)                                                 | 8  |

|-------------------------------------------------------------------------------------------|----|

| Figure 1.2. WISHBONE Bus Interface between the FPGA Core and the EFB Module               | 9  |

| Figure 1.3. WISHBONE Bus Write Operation                                                  | 11 |

| Figure 1.4. WISHBONE Bus Read Operation                                                   | 12 |

| Figure 1.5. EFB WISHBONE Interface Reset                                                  | 13 |

| Figure 2.1. I2C Controller Read/Write Example (through WISHBONE)                          | 20 |

| Figure 2.2. I2C Target Read/Write Example (through WISHBONE)                              | 21 |

| Figure 3.1. Simple I2C Command (for example, ISC_ERASE)                                   | 22 |

| Figure 3.2. I2C Command with Write Data (for example, LSC_PROG_INCR_NV)                   | 22 |

| Figure 3.3. I2C Command with Read Data (for example, LSC_READ_STATUS)                     |    |

| Figure 4.1. EFB Controller – I2C Write                                                    | 23 |

| Figure 4.2. EFB Controller – I2C Read                                                     | 24 |

| Figure 4.3. EFB Target – I2C Write                                                        | 25 |

| Figure 4.4. EFB Target – I2C Read                                                         | 26 |

| Figure 5.1. I2C Bit Transfer Timing                                                       | 27 |

| Figure 8.1. SPI Controller Read/Write Example (through WISHBONE) – Production Silicon     | 42 |

| Figure 8.2. SPI Target Read/Write Example (through WISHBONE) – Production Silicon         | 43 |

| Figure 9.1. Simple SPI Command (for example, ISC_ERASE)                                   | 44 |

| Figure 9.2. SPI Command with Write Data (for example, LSC_PROG_INCR_NV)                   | 44 |

| Figure 9.3. SPI Command with Read Data (for example, LSC_READ_STATUS)                     | 44 |

| Figure 10.1. Fully Specified SPI Transaction (MachXO4 Device as SPI Controller or Target) | 45 |

| Figure 10.2. Minimally Specified SPI Transaction Example (MachXO4 Device as SPI Target)   | 45 |

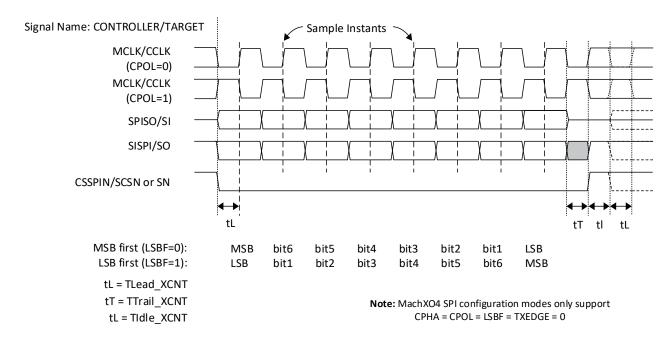

| Figure 11.1. SPI Control Timing (SPICR2[CPHA]=0, SPICR1[TXEDGE]=0)                        |    |

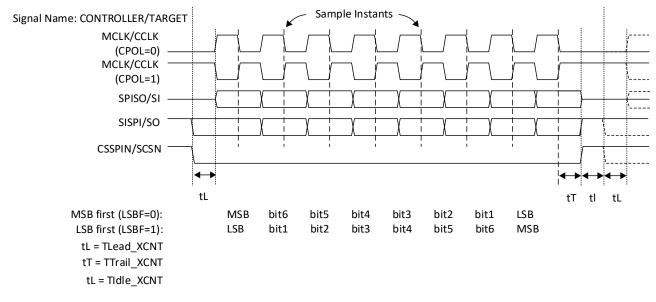

| Figure 11.2. SPI Control Timing (SPICR2[CPHA]=1, SPICR1[TXEDGE]=0)                        | 46 |

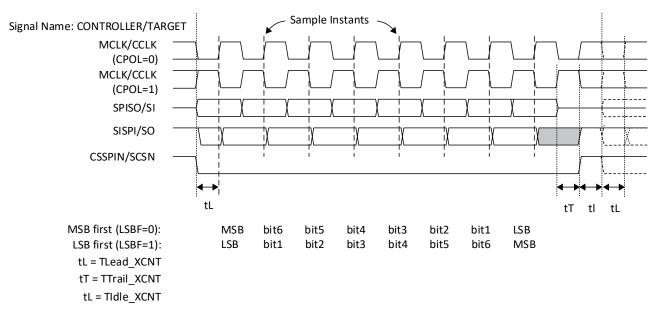

| Figure 11.3. SPI Control Timing (SPICR2[CPHA]=0, SPICR1[TXEDGE]=1)                        | 47 |

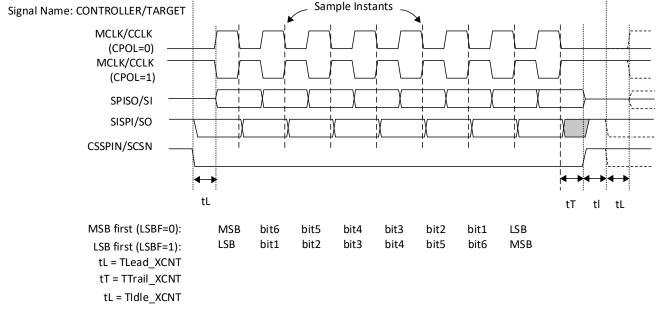

| Figure 11.4. SPI Control Timing (SPICR2[CPHA]=1, SPICR1[TXEDGE]=1)                        | 47 |

| Figure 11.5. Target SPI Dummy Byte Response (SPICR2[SDBRE]) Timing                        | 48 |

| Figure 15.1. Interfaces to the Flash Sectors                                              | 65 |

| Figure 16.1. Basic Configuration UFM Program Example                                      | 87 |

| Figure 17.1. I2C Read Device ID Example                                                   | 88 |

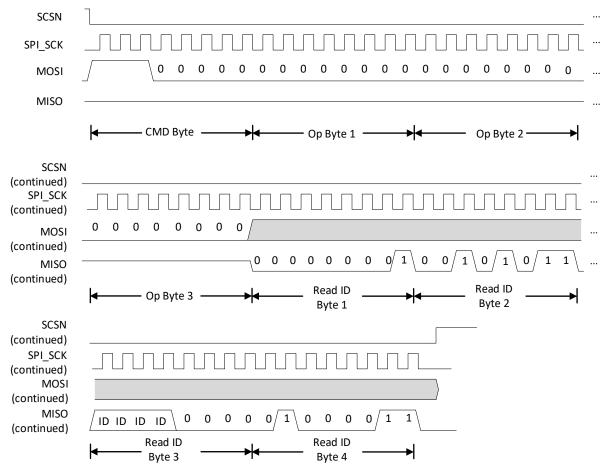

| Figure 17.2. SSPI Read Device ID Example                                                  | 89 |

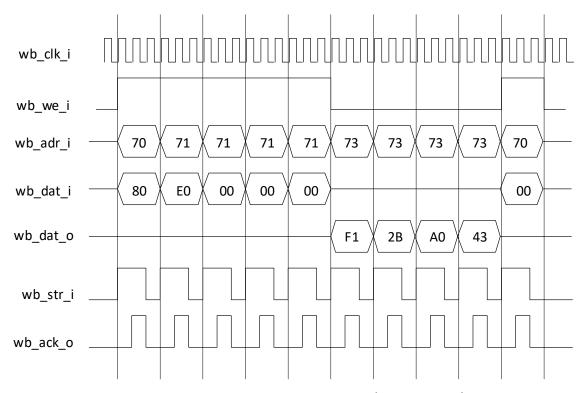

| Figure 17.3. WISHRONF Read Device ID Example (-015 HC Device)                             | 90 |

# **Tables**

| Table 1.1. EFB Register Map                                    | 9  |

|----------------------------------------------------------------|----|

| Table 1.2. WISHBONE Target Interface Signals of the EFB Module | 10 |

| Table 2.1. I2C Registers                                       | 14 |

| Table 2.2. I2C Control (Primary/Secondary)                     | 14 |

| Table 2.3. I2C Command (Pri/Sec)                               | 15 |

| Table 2.4. I2C Clock Prescale 0 (Primary/Secondary)            | 16 |

| Table 2.5. I2C Clock Prescale 1 (Primary/Secondary)            | 16 |

| Table 2.6. I2C Transmit Data Register (Primary/Secondary)      |    |

| Table 2.7. I2C Status (Primary/Secondary)                      | 16 |

| Table 2.8. I2C General Call Data Register (Primary/Secondary)  | 18 |

| Table 2.9. I2C Receive Data Register (Primary/Secondary)       | 18 |

| Table 2.10. I2C Interrupt Status (Primary/Secondary)           | 18 |

| Table 2.11. I2C Interrupt Enable (Primary/Secondary)           |    |

| Table 6.1. I2C Primary Simulation Mode                         | 28 |

| Table 6.2. I2C Secondary Simulation Mode                       | 31 |

| Table 8.1. SPI Registers                                       | 35 |

| Table 8.2. SPI Control 0                                       | 35 |

| Table 8.3. SPI Control 1                                       | 36 |

| Table 8.4. SPI Control 2                                       | 37 |

| Table 8.5. SPI Clock Pre-scale                                 | 38 |

| Table 8.6. SPI Controller Chip Select                          | 38 |

| Table 8.7. SPI Transmit Data Register                          | 38 |

| Table 8.8. SPI Status                                          |    |

| Table 8.9. SPI Receive Data Register                           |    |

| Table 8.10. SPI Interrupt Status                               |    |

| Table 8.11. SPI Interrupt Enable                               |    |

| Table 12.1. SPI Simulation Model                               |    |

| Table 13.1. Timer/Counter Registers                            |    |

| Table 13.2. Timer/Counter Control                              |    |

| Table 13.3. Timer/Counter Control 1                            |    |

| Table 13.4. Timer/Counter Set Top Counter Value 0              |    |

| Table 13.5. Timer/Counter Set Top Counter Value 1              |    |

| Table 13.6. Timer/Counter Set Compare Counter Value 0          |    |

| Table 13.7. Timer/Counter Set Compare Counter Value 1          |    |

| Table 13.8. Timer/Counter Control 2                            |    |

| Table 13.9. Timer/Counter Counter Value 0                      |    |

| Table 13.10. Timer/Counter Counter Value 1                     |    |

| Table 13.11. Timer/Counter Current Top Counter Value 0         |    |

| Table 13.12. Timer/Counter Current Top Counter Value 1         |    |

| Table 13.13. Timer/Counter Current Compare Counter Value 0     |    |

| Table 13.14. Timer/Counter Current Compare Counter Value 1     |    |

| Table 13.15. Timer/Counter Current Capture Counter Value 0     |    |

| Table 13.16. Timer/Counter Current Capture Counter Value 1     |    |

| Table 13.17. Timer/Counter Status Register                     |    |

| Table 13.18. Timer/Counter Interrupt Status                    |    |

| Table 13.19. Timer/Counter Interrupt Enable                    |    |

| •                                                              |    |

| Table 15.1. WISHBONE to Flash Logic Registers                  |    |

| Table 15.2. Flash Control                                      |    |

| Table 15.4. Flash Status                                       |    |

| Table 15.4. Flash Receive Data                                 |    |

| Table 13.3. Flash receive Data                                 |    |

| Table 15.6. Flash Interrupt Status                               | 68 |

|------------------------------------------------------------------|----|

| Table 15.7. Flash Interrupt Enable                               | 69 |

| Table 15.8. Unused (Reserved) Register                           | 69 |

| Table 15.9. EFB Interrupt Source                                 | 70 |

| Table 15.10. UFM Commands                                        |    |

| Table 15.11. Configuration Flash (Sector 0) Commands             | 72 |

| Table 15.12. Non-Volatile Register (NVR) Commands                | 73 |

| Table 15.13. Erase Flash (0x0E)                                  | 73 |

| Table 15.14. Read TraceID Code (0x19)                            | 73 |

| Table 15.15. Disable Configuration Interface (0x26)              | 74 |

| Table 15.16. Read Status Register (0x3C)                         | 74 |

| Table 15.17. Reset CFG Address (0x46)                            | 75 |

| Table 15.18. Reset UFM Address (0x47)                            | 75 |

| Table 15.19. Program DONE (0x5E)                                 | 75 |

| Table 15.20. Program Configuration Flash (0x70)                  | 75 |

| Table 15.21. Read Configuration Flash (0x73) (SPI)               | 75 |

| Table 15.22. Read Configuration Flash (0x73) (I2C/SPI)           | 76 |

| Table 15.23. Read Configuration Flash (0x73) (WISHBONE)          | 76 |

| Table 15.24. Enable Configuration Interface (Transparent) (0x74) | 77 |

| Table 15.25. Refresh (0x79)                                      |    |

| Table 15.26. STANDBY (0x7D)                                      |    |

| Table 15.27. Set Address (0xB4)                                  |    |

| Table 15.28. Read USERCODE (0xC0)                                |    |

| Table 15.29. Program USERCODE (0xC2)                             | 79 |

| Table 15.30. Enable Configuration Interface (Offline) (0xC6)     |    |

| Table 15.31. Program UFM (0xC9)                                  | 79 |

| Table 15.32. Read UFM (0xCA) (SPI)                               |    |

| Table 15.33. Read UFM (0xCA) (SPI/I2C)                           |    |

| Table 15.34. Read UFM (0xCA) (WISHBONE)                          |    |

| Table 15.35. Erase UFM (0xCB)                                    |    |

| Table 15.36. Program SECURITY (0xCE)                             |    |

| Table 15.37. Program SECURITY PLUS (0xCF)                        |    |

| Table 15.38. Read Device ID Code (0xE0)                          |    |

| Table 15.39. Device ID                                           |    |

| Table 15.40. Verify Device ID Code (0xE2)                        |    |

| Table 15.41. Program Feature (0xE4)                              |    |

| Table 15.42. Read Feature Row (0xE7)                             |    |

| Table 15.43. Check Busy Flag (0xF0)                              |    |

| Table 15.44. Program FEABITs (0xF8)                              |    |

| Table 15.45. Read FEABITs (0xFB)                                 |    |

| Table 15.46. Bypass (Null Operation) (0xFF)                      |    |

| Table 17.1. Command Framing Protocol, by Interface               |    |

| Table 17.2. Command Framing Protocol, by Interface               |    |

| Table 17.3. Command Framing Protocol, by Interface               |    |

| Table 18.1. Write Two UFM Pages                                  |    |

| Table 18.2. Read One UFM Page (All Devices, WISHBONE/SPI)        |    |

| Table 18.3. Read Two UFM Pages (WISHBONE/SPI)                    |    |

| Table 19.1. Flash Performance in the MachXO4 Device <sup>1</sup> |    |

| Table 20.1. E/P/V Calculation Parameters                         | 95 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                        |

|--------------|---------------------------------------------------|

| EFB          | Embedded Function Block                           |

| FPGA         | Field Programmable Gate Array                     |

| GSR          | Global Set/Reset                                  |

| 1/0          | Input/Output                                      |

| I2C          | Inter-Integrated Circuit                          |

| IEEE         | Institute of Electrical and Electronics Engineers |

| IP           | Intellectual Property                             |

| LSB          | Least Significant Bit                             |

| MSB          | Most Significant Bit                              |

| PLD          | Programmable Logic Device                         |

| PLL          | Phase Locked Loop                                 |

| SPI          | Serial Peripheral Interface                       |

| SRAM         | Static Random-Access Memory                       |

| SSM          | Synchronous State Machine                         |

| UFM          | User Flash Memory                                 |

# 1. Introduction

This reference guide supplements the MachXO4 Hardened Control Functions User Guide (FPGA-TN-02403), which explains the software usage. In this document, you can find:

- WISHBONE Protocol

- EFB Register Map

- Command Sequences

- Examples

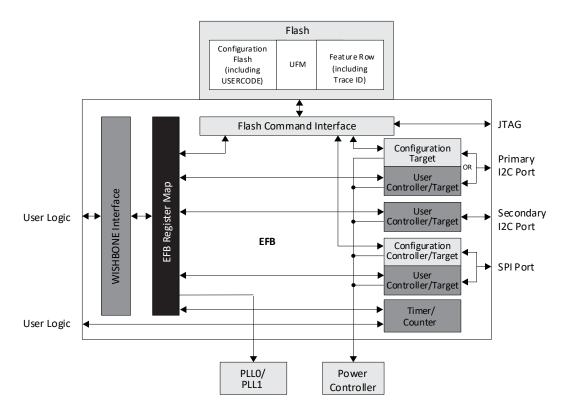

As an overview, the MachXO4™ FPGA family combines a high-performance, low power, FPGA fabric with built-in, hardened control functions. The hardened control functions ease design implementation and save general purpose resources such as LUTs, registers, clocks, and routing. The hardened control functions are physically located in the Embedded Function Block (EFB). All MachXO4 devices include an EFB module. The EFB block includes the following control functions:

- Two I2C Cores

- One SPI Core

- One 16-bit Timer/Counter

- Interface to Flash memory which includes:

- User Flash Memory

- Configuration logic

- Interface to Dynamic PLL configuration settings

- Interface to On-chip Power Controller through I2C and SPI

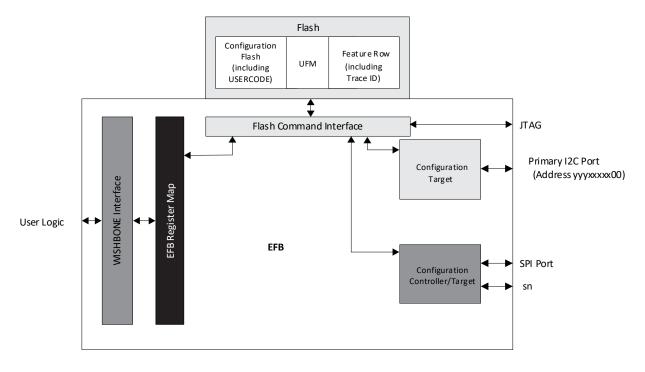

Figure 1.1 shows the EFB architecture and the interface to the FPGA core logic.

Figure 1.1. Embedded Function Block (EFB)

# 1.1. EFB Register Map

The EFB module has a Register Map to allow the service of the hardened functions through the WISHBONE bus interface a read/write operations. Each hardened function has dedicated 8-bit Data and Control registers, except for the Flash. These are access through the same set of registers. Table 1.1 documents the register map of the EFB module. The PLL registers are located in the Flash in the MachXO4 devices PLL modules, but are access through the EFB WISHBONE read/write cycles.

Table 1.1. EFB Register Map

| Address (Hex) | Hardened Function    |

|---------------|----------------------|

| 0x00-0x1F     | PLL0 Dynamic Access1 |

| 0x20-0x3F     | PLL1 Dynamic Access1 |

| 0x40-0x49     | I2C Primary          |

| 0x4A-0x53     | I2C Secondary        |

| 0x54-0x5D     | SPI                  |

| 0x5E-0x6F     | Timer/Counter        |

| 0x70-0x75     | Flash                |

| 0x76-0x77     | EFB Interrupt Source |

#### Note:

Address spaces that are not defined in Table 1.1 are invalid and results in non-deterministic results. Ensure valid addresses are presented to the EFB WISHBONE target interface.

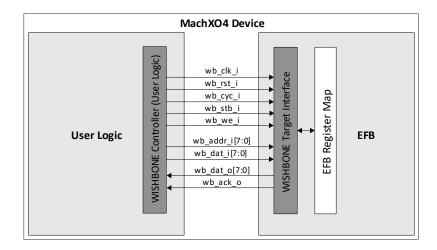

# 1.2. WISHBONE Bus Interface

The WISHBONE bus in the MachXO4 is compliant with the WISHBONE standard from OpenCores. It provides connectivity between FPGA user logic and the EFB functional blocks. You can implement a WISHBONE controller interface to interact with the EFB WISHBONE target interface or a LatticeMico8™ soft processor core can be used to interact with the EFB WISHBONE.

The block diagram in Figure 1.2 shows the supported WISHBONE bus signals between the FPGA core and the EFB. Table 1.2 provides a detailed definition of the supported signals.

Figure 1.2. WISHBONE Bus Interface between the FPGA Core and the EFB Module

<sup>1.</sup> There can be up to two PLLs in a MachXO4 device. PLL0 has an address range from 0x00 to 0x1F. PLL1 (if present) has an address range from 0x20 to 0x3F. Refer to the MachXO4 sysCLOCK PLL Design User Guide (FPGA-TN-02391) for details on the PLL configuration registers and recommended usage.

Table 1.2. WISHBONE Target Interface Signals of the EFB Module

| Signal Name | 1/0    | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wb_clk_i    | Input  | 1     | Positive edge clock used by WISHBONE Interface registers and hardened functions within the EFB module. Supports clock speeds up to 133 MHz. When used in conjunction with the I2C User Target or Configuration Target ports, the clock speed must be at least 7.5× the I2C bus speed (for example, >3.0 MHz when I2C rate = 400 kHz). When used in conjunction with SPI Target port, the WISHBONE clock speed must be at least twice the SPI clock speed. |

| wb_rst_i    | Input  | 1     | Active-high, synchronous reset signal that only resets the WISHBONE interface logic. This signal does not affect the contents of any registers. It only affects ongoing bus transactions. Wait 1 us after de-assertion before starting any subsequent WISHBONE transactions.                                                                                                                                                                              |

| wb_cyc_i    | Input  | 1     | Active-high signal, asserted by the WISHBONE controller, indicates a valid bus cycle is present on the bus.                                                                                                                                                                                                                                                                                                                                               |

| wb_stb_i    | Input  | 1     | Active-high strobe, input signal, indicating the WISHBONE target is the target for the current transaction on the bus. The EFB module asserts an acknowledgment in response to the assertion of the strobe.                                                                                                                                                                                                                                               |

| wb_we_i     | Input  | 1     | Level sensitive Write/Read control signal. Low indicates a Read operation, and High indicates a Write operation.                                                                                                                                                                                                                                                                                                                                          |

| wb_adr_i    | Input  | 8     | 8-bit wide address used to select a specific register from the register map of the EFB module.                                                                                                                                                                                                                                                                                                                                                            |

| wb_dat_i    | Input  | 8     | 8-bit input data path used to write a byte of data to a specific register in the register map of the EFB module.                                                                                                                                                                                                                                                                                                                                          |

| wb_dat_o    | Output | 8     | 8-bit output data path used to read a byte of data from a specific register in the register map of the EFB module.                                                                                                                                                                                                                                                                                                                                        |

| wb_ack_o    | Output | 1     | Active-high, transfer acknowledge signal asserted by the EFB module, indicating the requested transfer is acknowledged.                                                                                                                                                                                                                                                                                                                                   |

To interface to the EFB you must create a WISHBONE controller in the User Logic. In a multiple-Controller configuration, the WISHBONE Controller outputs are multiplexed in a user-defined arbiter. A LatticeMico8 soft processor can also be utilized along with the Mico System Builder (MSB) platform, which can implement multi-controller bus configurations. If two Controller request the bus in the same cycle, only the outputs of the arbitration winner reach the Target interface.

The EFB WISHBONE bus supports the Classic version of the WISHBONE standard. Given that the WISHBONE bus is an open source standard, not all features of the standard are implemented or required:

- Tags are not supported in the WISHBONE Target interface of the EFB module. Given that the EFB is a hardened block, these signals cannot be added.

- The Target WISHBONE bus interface of the EFB module does not require the byte select signals (sel\_i or sel\_o), since the data bus is only a single byte wide.

- The EFB WISHBONE Target interface does not support the optional error and retry access termination signals. If the target receives an access to an invalid address, it responds by asserting wb\_ack\_o signal. Ensure to stay within the valid address range.

# 1.3. WISHBONE Write Cycle

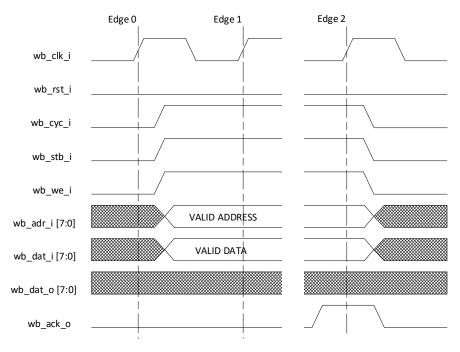

Figure 1.3 shows the waveform of a Write cycle from the perspective of the EFB WISHBONE Target interface. During a single Write cycle, only one byte of data is written to the EFB block from the WISHBONE Controller. A Write operation requires a minimum three clock cycles.

On clock Edge 0, the Controller updates the address, data and asserts control signals. During this cycle:

- The Controller updates the address on the wb adr i[7:0] address lines.

- Updates the data that is written to the EFB block, wb dat i[7:0] data lines.

- Asserts the write enable wb\_we\_i signal, indicating a write cycle.

- Asserts the wb cyc i to indicate the start of the cycle.

- Asserts the wb stb i, selecting a specific target module.

On clock Edge 1, the EFB WISHBONE Target decodes the input signals presented by the controller. During this cycle:

- The Target decodes the address presented on the wb\_adr\_i[7:0] address lines.

- The Target prepares to latch the data presented on the wb\_dat\_i[7:0] data lines.

- The Controller waits for an active-high level on the wb\_ack\_o line and prepares to terminate the cycle on the next clock edge, if an active-high level is detected on the wb ack o line.

- The EFB may insert wait states before asserting wb\_ack\_o, thereby allowing it to throttle the cycle speed. Any number of wait states may be added.

- The Target asserts wb\_ack\_o signal.

The following occurs on clock Edge 2:

- The Target latches the data presented on the wb dat i[7:0] data lines.

- The Controller de-asserts the strobe signal, wb\_stb\_i, the cycle signal, wb\_cyc\_i, and the write enable signal, wb we i.

- The Target de-asserts the acknowledge signal, wb\_ack\_o, in response to the Controller de-assertion of the strobe signal.

Figure 1.3. WISHBONE Bus Write Operation

# 1.4. WISHBONE Read Cycle

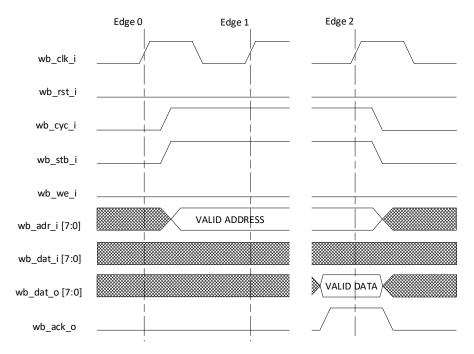

Figure 1.4 shows the waveform of a Read cycle from the perspective of the EFB WISHBONE Target interface. During a single Read cycle, only one byte of data is read from the EFB block by the WISHBONE controller. A Read operation requires a minimum three clock cycles.

On clock Edge 0, the Controller updates the address, data and asserts control signals. The following occurs during this cycle:

- The Controller updates the address on the wb\_adr\_i[7:0] address lines.

- De-asserts the write enable wb\_we\_i signal, indicating a Read cycle.

- Asserts the wb cyc i to indicate the start of the cycle.

- Asserts the wb\_stb\_i, selecting a specific Target module.

On clock Edge 1, the EFB WISHBONE target decodes the input signals presented by the controller. The following occurs during this cycle:

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

- The Target decodes the address presented on the wb adr i[7:0] address lines.

- The Controller prepares to latch the data presented on wb dat o[7:0] data lines from the EFB WISHBONE target on the following clock edge.

- The Controller waits for an active-high level on the wb ack o line and prepares to terminate the cycle on the next clock edge, if an active-high level is detected on the wb ack o line.

- The EFB may insert wait states before asserting wb\_ack\_o, thereby allowing it to throttle the cycle speed. Any number of wait states may be added.

- The Target presents valid data on the wb\_dat\_o[7:0] data lines.

- The Target asserts wb ack o signal in response to the strobe, wb stb i signal.

The following occurs on clock Edge 2:

- The Controller latches the data presented on the wb dat o[7:0] data lines.

- The Controller de-asserts the strobe signal, wb\_stb\_i, and the cycle signal, wb\_cyc\_i.

- The Target de-asserts the acknowledge signal, wb ack o, in response to the controller de-assertion of the strobe

Figure 1.4. WISHBONE Bus Read Operation

To avoid simulation mismatch in functional simulations, add a delay of 100 ps to wb cyc i and wb stb i assertion assignments. See the examples below. The examples assume the wb cyc i gen signal is generated elsewhere in the design, for example from a synchronous state machine (SSM).

Verilog example: (assumes timescale 1 ns / 100 ps)

#### VHDL example:

Additionally, ensure your logic monitors for wb ack o, and deassert wb cyc i and wb stb i immediately.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

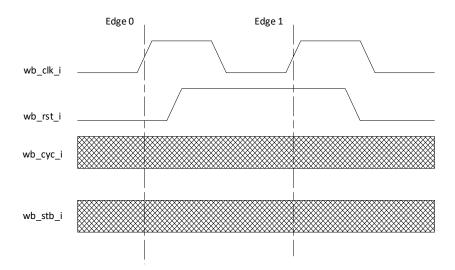

#### **WISHBONE Reset Cycle** 1.5.

Figure 1.5 shows the waveform of the synchronous wb\_rst\_i signal. Asserting the reset signal, resets the WISHBONE interface logic. This signal does not affect the contents of any registers in the EFB register map. It only affects ongoing bus transactions.

Figure 1.5. EFB WISHBONE Interface Reset

The wb rst i signal can be asserted for any length of time.

# 2. Hardened I2C IP Cores

I2C is a widely used two-wire serial bus for communication between devices on the same board. Every MachXO4 device contains two hardened I2C IP cores designated as the Primary and Secondary I2C IP cores. Either of the two cores can be operated as an I2C Controller or as an I2C Target. The difference between the two cores is that the Primary core has pre-assigned I/O pins while the ports of the secondary core can be assigned to any general purpose I/O. In addition, the Primary I2C core can be used for accessing the Flash. However, the Primary I2C port cannot be used for both Flash access and user functions in the same design. When instantiating the Hardened I2C IP cores for Target operations, the Embedded Function Block (EFB)  $wb\_clk\_i$  input must be connected to a valid clock source of at least 7.5× the I2C bus rate (for example, >3.0 MHz when I2C rate = 400 kHz).

# 2.1. I2C Registers

Both I2C cores communicate with the EFB WISHBONE interface through a set of control, command, status, and data registers. Table 2.1 shows the register names and their functions. These registers are a subset of the EFB register map.

Table 2.1. I2C Registers

| I2C Primary<br>Register Name | I2C Secondary<br>Register Name | Register Function | Address I2C Primary | Address I2C<br>Secondary | Access     |

|------------------------------|--------------------------------|-------------------|---------------------|--------------------------|------------|

| I2C_1_CR                     | 12C_2_CR                       | Control           | 0x40                | 0x4A                     | Read/Write |

| I2C_1_CMDR                   | I2C_2_CMDR                     | Command           | 0x41                | 0x4B                     | Read/Write |

| I2C_1_BR0                    | I2C_2_BR0                      | Clock Pre-scale   | 0x42                | 0x4C                     | Read/Write |

| I2C_1_BR1                    | I2C_2_BR1                      | Clock Pre-scale   | 0x43                | 0x4D                     | Read/Write |

| I2C_1_TXDR                   | I2C_2_TXDR                     | Transmit Data     | 0x44                | 0x4E                     | Write      |

| I2C_1_SR                     | 12C_2_SR                       | Status            | 0x45                | 0x4F                     | Read       |

| I2C_1_GCDR                   | I2C_2_GCDR                     | General Call      | 0x46                | 0x50                     | Read       |

| I2C_1_RXDR                   | I2C_2_RXDR                     | Receive Data      | 0x47                | 0x51                     | Read       |

| I2C_1_IRQ                    | I2C_2_IRQ                      | IRQ               | 0x48                | 0x52                     | Read/Write |

| I2C_1_IRQEN                  | I2C_2_IRQEN                    | IRQ Enable        | 0x49                | 0x53                     | Read/Write |

**Note:** Unless otherwise specified, all reserved bits in writable registers are written as 0.

Table 2.2. I2C Control (Primary/Secondary)

| I2C_1_CR / I2C_2_CR |       |      |        |            |         |           |            |   |  |  |

|---------------------|-------|------|--------|------------|---------|-----------|------------|---|--|--|

| Bit                 | 7     | 6    | 5      | 4          | 3       | 2         | 1          | 0 |  |  |

| Name                | I2CEN | GCEN | WKUPEN | (Reserved) | SDA_DEL | _SEL[1:0] | (Reserved) |   |  |  |

| Default             | 0     | 0    | 0      | 0          | 0       | 0         | 0          | 0 |  |  |

| Access              | R/W   | R/W  | R/W    | -          | R/W     | R/W       | -          | _ |  |  |

Note: A write to this register causes the I2C core to reset.

#### **I2CEN**

I2C System Enable Bit – This bit enables the I2C core functions. If I2CEN is cleared, the I2C core is disabled and forced into idle state.

0: I2C function is disabled

1: I2C function is enabled

#### **GCEN**

Enable bit for General Call Response – Enables the general call response in target mode.

0: Disable

1: Enable

The General Call address is defined as 0000000 and works with either 7-bit or 10-bit addressing.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## **WKUPEN**

Wake-up from Standby/Sleep (by Target Address matching) Enable Bit – When this bit is enabled the I2C core can send a wake-up signal to the on-chip power manager to wake the device up from standby/sleep. The wake-up function is activated when the MachXO4 Target Address is matched during standby/sleep mode.

0: Disable1: Enable

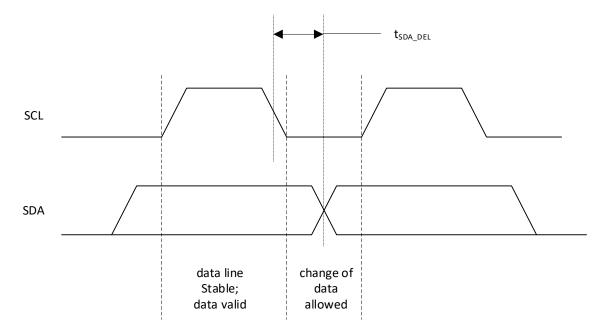

#### SDA DEL SEL[1:0]

SDA Output Delay (Tdel) Selection (see Figure 5.1).

| 00: | 300 ns (min) | 300 ns + 2000/[wb_clk_i frequency in MHz] (max) |

|-----|--------------|-------------------------------------------------|

| 01: | 150 ns (min) | 150 ns + 2000/[wb_clk_i frequency in MHz] (max) |

| 10: | 75 ns (min)  | 75 ns + 2000/[wb_clk_i frequency in MHz] (max)  |

| 11: | 0 ns (min)   | 0 ns + 2000/[wb_clk_i frequency in MHz] (max)   |

# Table 2.3. I2C Command (Pri/Sec)

| 12C_1_CMDR / I2C_2_CMDR |     |     |     |     |     |        |            |   |  |  |

|-------------------------|-----|-----|-----|-----|-----|--------|------------|---|--|--|

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2      | 1          | 0 |  |  |

| Name                    | STA | STO | RD  | WR  | ACK | CKSDIS | (Reserved) |   |  |  |

| Default                 | 0   | 0   | 0   | 0   | 0   | 0      | 0          | 0 |  |  |

| Access                  | R/W | R/W | R/W | R/W | R/W | R/W    | _          | _ |  |  |

#### **STA**

Generate START (or Repeated START) condition (Controller operation)

#### STO

Generate STOP condition (Controller operation)

#### RD

Indicate Read from target (Controller operation)

#### WR

Indicate Write to target (Controller operation)

#### ACK

Acknowledge Option - when receiving, ACK transmission selection

0: Send ACK1: Send NACK

#### **CKSDIS**

Clock Stretching Disable. The I2C cores support a wait state or clock stretching from the target, meaning the target can enforce a wait state if it needs time to finish the task. If necessary, you can disable the clock stretching using the CKSDIS bit. In this case, the overflow flag must be monitored. For Controller operations, set this bit to 0. Clock stretching is used by the MachXO4 EFB I2C Target during both *read* and *write* operations (from the Controller perspective) when I2C Command Register bit CKSDIS=0.

During a read operation (Target transmitting), clock stretching occurs when TXDR is empty (under-run condition). During a write operation (Target receiving) clock stretching occurs when RXDR is full (over-run condition).

Translated into I2C Status register bits, the I2C clock-stretches if TRRDY=1. The decision to enable clock stretching is done on the 8TH SCL + 2 WISHBONE clocks.

0: Enabled1: Disabled

Table 2.4. I2C Clock Prescale 0 (Primary/Secondary)

| I2C_1_BR0 / I2C_2_BR0 0x4 |     |                   |     |     |     |     |     |     |  |  |

|---------------------------|-----|-------------------|-----|-----|-----|-----|-----|-----|--|--|

| Bit 7 6 5 4 3 2 1         |     |                   |     |     |     |     |     | 0   |  |  |

| Name                      |     | I2C_PRESCALE[7:0] |     |     |     |     |     |     |  |  |

| Default                   | 0   | 0                 | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| Access                    | R/W | R/W               | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

Note: Hardware default value may be overridden by EFB component instantiation parameters. See discussion below.

Table 2.5. I2C Clock Prescale 1 (Primary/Secondary)

| I2C_1_BR1 / I | _1_BR1 / I2C_2_BR1 |                             |   |   |   |   |     |     |  |  |

|---------------|--------------------|-----------------------------|---|---|---|---|-----|-----|--|--|

| Bit           | 7                  | 6                           | 5 | 4 | 3 | 2 | 1   | 0   |  |  |

| Name          |                    | (Reserved) I2C_PRESCALE[7:0 |   |   |   |   |     |     |  |  |

| Default       | 0                  | 0                           | 0 | 0 |   |   |     |     |  |  |

| Access        | _                  | _                           | _ | _ | _ | _ | R/W | R/W |  |  |

Note: Hardware default value may be overridden by EFB component instantiation parameters. See discussion below.

#### I2C PRESCALE[9:0]

I2C Clock Prescale value. A write operation to I2CBR [9:8] causes an I2C core reset. The WISHBONE clock frequency is divided by (I2C\_PRESCALE\*4) to produce the Controller I2C clock frequency supported by the I2C bus (50 kHz, 100 kHz, 400 kHz).

#### **Notes:**

- Different from transmitting a Controller, the practical limit for Target I2C bus speed support is (WISHBONE clock)/2048. For example, the maximum WISHBONE clock frequency to support a 50 kHz Target I2C operation is 102 MHz.

- The digital value is calculated by the IP Catalog when the I2C core is configured in the I2C tab of the EFB GUI. The calculation is based on the WISHBONE Clock Frequency and the I2C Frequency, which are user-entered. The digital value of the divider is programmed in the MachXO4 device during device programming. After power-up or device reconfiguration, the data is loaded onto the I2C\_1\_BR1/0 and I2C\_2\_BR1/0 registers.

Registers I2C\_1\_BR1/0 and I2C\_2\_BR1/0 have Read/Write access from the WISHBONE interface. You can update these clock pre-scale registers dynamically during device operation; however, care must be taken to not violate the I2C bus frequencies.

Table 2.6. I2C Transmit Data Register (Primary/Secondary)

| I2C_1_TXDR / | OR / I2C_2_TXDR |                   |   |   |   |   |   |   |  |  |

|--------------|-----------------|-------------------|---|---|---|---|---|---|--|--|

| Bit          | 7               | 7 6 5 4 3 2 1     |   |   |   |   |   |   |  |  |

| Name         |                 | I2C_Transmit[7:0] |   |   |   |   |   |   |  |  |

| Default      | 0               | 0 0 0 0 0 0 0     |   |   |   |   |   |   |  |  |

| Access       | W               | W                 | W | W | W | W | W | W |  |  |

#### I2C Transmit Data[7:0]

I2C Transmit Data. This register holds the byte to be transmitted on the I2C bus during the Write Data phase. Bit 0 is the LSB and is transmitted last. When transmitting the target address, Bit 0 represents the Read/Write bit.

Table 2.7. I2C Status (Primary/Secondary)

| ······································ |     |      |      |     |      |       |      |     |  |  |

|----------------------------------------|-----|------|------|-----|------|-------|------|-----|--|--|

| I2C_1_SR / I2C_2_SR                    |     |      |      |     |      |       |      |     |  |  |

| Bit                                    | 7   | 6    | 5    | 4   | 3    | 2     | 1    | 0   |  |  |

| Name                                   | TIP | BUSY | RARC | SRW | ARBL | TRRDY | TROE | HGC |  |  |

| Default                                | _   | _    | _    | _   | _    | _     | _    | _   |  |  |

| Access                                 | R   | R    | R    | R   | R    | R     | R    | R   |  |  |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-TN-02404-1.0

## TIP

Transmit In Progress. The current data byte is being transferred. Note that the TIP flag suffers one-half SCL cycle latency right after the START condition because of the signal synchronization. Also, note that this bit can be high after configuration wake-up and before the first valid I2C transfer starts (when BUSY is low), and it is not indicating byte in transfer, but an invalid indicator.

- 1: Byte transfer in progress

- 0: Byte transfer complete

#### **BUSY**

I2C Bus busy. The I2C bus is involved in a transaction. This is set at START condition and cleared at STOP. Make sure this bit is set before treating any other I2C SR bits as valid indicators for a valid transfer.

- I2C bus busy

- 0: I2C bus not busy

#### **RARC**

Received Acknowledge. An acknowledge response is received by the acknowledge bit monitor. All ACK/NACK bits are monitored and reported, regardless of Controller/Target source or Read/Write mode.

- 1: No acknowledge received

- 0: Acknowledge received

#### **SRW**

Target Read/Write. Indicates transmit or receive mode.

- 1: Controller receiving/target transmitting

- 0: Controller transmitting/target receiving

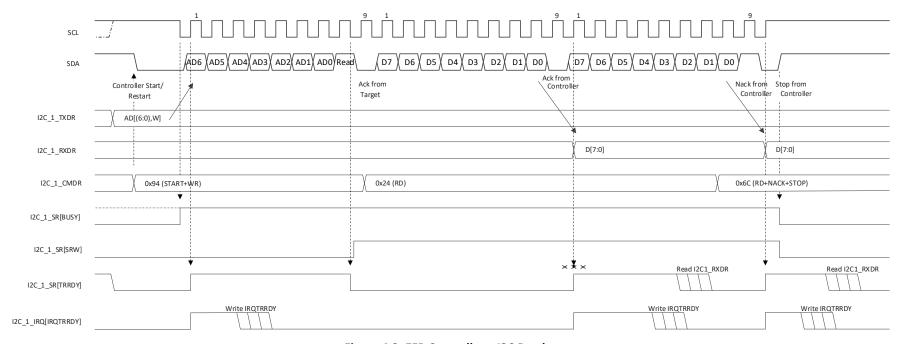

**Note:** SRW is valid after TRRDY=1 following a synchronization delay of up to four WISHBONE clock cycles. Do not test both SRW and TRRDY in the same WISHBONE transaction, but test SRW at least four WISHBONE clock cycles after TRRDY is tested true. This delay is represented in Figure 4.4.

#### **ARBL**

Arbitration Lost. The core has lost arbitration in Controller mode. This bit is capable of generating an interrupt.

- 1: Arbitration Lost

- 0: Normal

# **TRRDY**

Transmitter or Receiver Ready. The I2C Transmit Data register is ready to receive transmit data, or the I2C Receive Data Register contains receive data (dependent upon controller/target mode and SRW status). This bit is capable of generating an interrupt.

- 1: Transmitter or Receiver is ready

- 0: Transmitter of Receiver is not ready

#### TROE

Transmitter/Receiver Overrun Error. A transmit or receive overrun error has occurred (dependent upon controller/target mode and SRW status).

**Note:** When acting as a transmitter (Controller Write or Target Read) a No Acknowledge received asserts TROE indicating a possible orphan data byte exists in TXDR.

This bit is capable of generating an interrupt.

- 1: Transmitter or Receiver Overrun detected or NACK received

- 0: Normal

## HGC

Hardware General Call Received. A hardware general call has been received in target mode. The corresponding command byte is available in the General Call Data Register. This bit is capable of generating an interrupt.

- 1: General Call Received in target mode

- 0: Normal

Table 2.8. I2C General Call Data Register (Primary/Secondary)

| I2C_1_GCDR | R / I2C_2_GCDR |                  |   |   |   |   |   |   |  |  |

|------------|----------------|------------------|---|---|---|---|---|---|--|--|

| Bit        | 7              | 7 6 5 4 3 2 1    |   |   |   |   |   |   |  |  |

| Name       |                | I2C_GC_Data[7:0] |   |   |   |   |   |   |  |  |

| Default    | _              |                  |   |   |   |   |   |   |  |  |

| Access     | R              | R                | R | R | R | R | R | R |  |  |

# I2C\_GC \_Data[7:0]

I2C General Call Data. This register holds the second (command) byte of the General Call transaction on the I2C bus.

Table 2.9. I2C Receive Data Register (Primary/Secondary)

| I2C_1_RXDR | 12C_2_RXDR |                       |   |   |   |   |   |   |  |  |

|------------|------------|-----------------------|---|---|---|---|---|---|--|--|

| Bit        | 7          | 6                     | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| Name       |            | I2C_Receive_Data[7:0] |   |   |   |   |   |   |  |  |

| Default    | _          | _                     | _ | _ | _ | _ | _ | _ |  |  |

| Access     | R          | R                     | R | R | R | R | R | R |  |  |

# I2C\_ Receive \_Data[7:0]

I2C Receive Data. This register holds the byte captured from the I2C bus during the Read Data phase. Bit 0 is LSB and is received last.

Table 2.10. I2C Interrupt Status (Primary/Secondary)

| 12C_1_IRQ / 12C_2_IRQ |   |       |        |   |         |          |         |        |  |  |

|-----------------------|---|-------|--------|---|---------|----------|---------|--------|--|--|

| Bit                   | 7 | 6     | 5      | 4 | 3       | 2        | 1       | 0      |  |  |

| Name                  |   | (Rese | erved) |   | IRQARBL | IRQTRRDY | IRQTROE | IRQHGC |  |  |

| Default               | - | -     | -      | _ | _       | _        | _       | _      |  |  |

| Access                | - | -     | -      | _ | R/W     | R/W      | R/W     | R/W    |  |  |

# **IRQARBL**

Interrupt Status for Arbitration Lost. When enabled, indicates ARBL is asserted. Write a 1 to this bit to clear the interrupt.

- 1: Arbitration Lost Interrupt

- 0: No interrupt

## **IRQTRRDY**

Interrupt Status for Transmitter or Receiver Ready. When enabled, indicates TRRDY is asserted. Write a 1 to this bit to clear the interrupt.

- 1: Transmitter or Receiver Ready Interrupt

- 0: No interrupt

## **IRQTROE**

Interrupt Status for Transmitter/Receiver Overrun or NACK received. When enabled, indicates TROE is asserted. Write a 1 to this bit to clear the interrupt.

- 1: Transmitter or Receiver Overrun or NACK received Interrupt

- 0: No interrupt

## **IRQHGC**

Interrupt Status for Hardware General Call Received. When enabled, indicates HGC is asserted. Write a 1 to this bit to clear the interrupt.

- 1: General Call Received in target mode Interrupt

- 0: No interrupt

Table 2.11. I2C Interrupt Enable (Primary/Secondary)

| I2C_1_IRQEN / I2C_2_IRQEN |   |       |       |   |           |            |           |          |  |

|---------------------------|---|-------|-------|---|-----------|------------|-----------|----------|--|

| Bit                       | 7 | 6     | 5     | 4 | 3         | 2          | 1         | 0        |  |

| Name                      |   | (Rese | rved) |   | IRQARBLEN | IRQTRRDYEN | IRQTROEEN | IRQHGCEN |  |

| Default                   | 0 | 0     | 0     | 0 | 0         | 0          | 0         | 0        |  |

| Access                    | _ | _     | _     | _ | R/W       | R/W        | R/W       | R/W      |  |

# **IRQARBLEN**

Interrupt Enable for Arbitration Lost

- 1: Interrupt generation enabled

- 0: Interrupt generation disabled

## **IRQTRRDYEN**

Interrupt Enable for Transmitter or Receiver Ready

- 1: Interrupt generation enabled

- 0: Interrupt generation disabled

## **IRQTROEEN**

Interrupt Enable for Transmitter/Receiver Overrun or NACK Received

- 1: Interrupt generation enabled

- 0: Interrupt generation disabled

## **IRQHGCEN**

Interrupt Enable for Hardware General Call Received

- 1: Interrupt generation enabled

- 0: Interrupt generation disabled

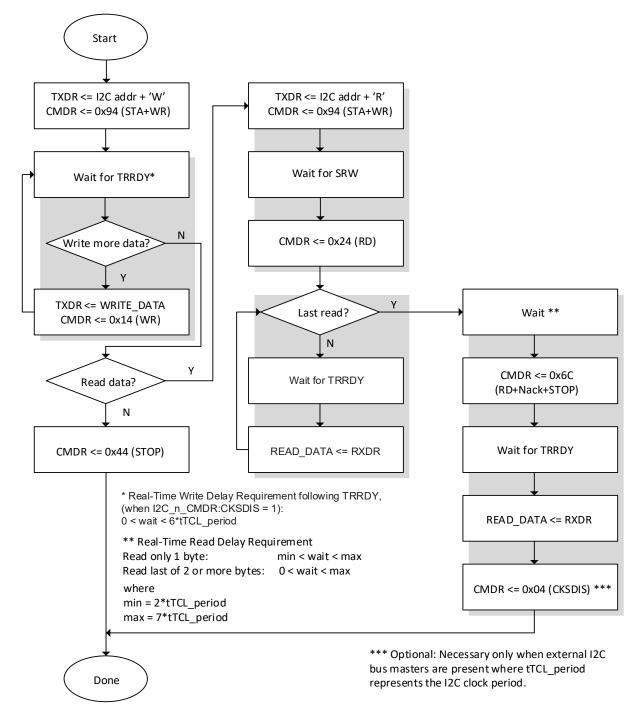

Figure 2.1 shows a flow diagram for controlling Controller I2C reads and writes initiated through the WISHBONE interface. The following sequence is for the Primary I2C but the same sequence applies to the Secondary I2C.

Figure 2.1. I2C Controller Read/Write Example (through WISHBONE)

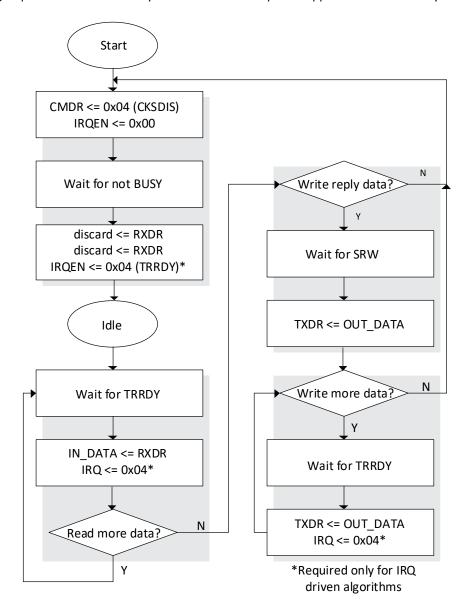

Figure 2.2 shows a flow diagram for reading and writing from an I2C Target device through the WISHBONE interface. The following sequence is for the Primary I2C but the same sequence applies to the Secondary I2C.

Figure 2.2. I2C Target Read/Write Example (through WISHBONE)

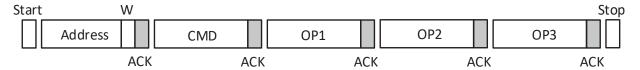

#### 3. **Typical I2C Transactions**

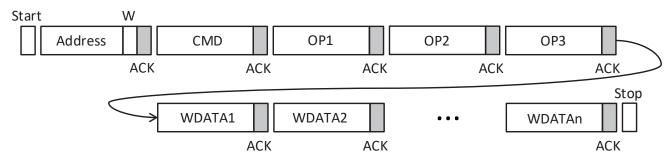

Figure 3.1, Figure 3.2, and Figure 3.3 illustrate typical User I2C bus protocol transactions that are supported by the Controller and Target flows shown in Figure 2.1 and Figure 2.2. Additionally, the figures below reference typical sysConfig Configuration commands structures.

Figure 3.1. Simple I2C Command (for example, ISC\_ERASE)

Figure 3.2. I2C Command with Write Data (for example, LSC\_PROG\_INCR\_NV)

Figure 3.3. I2C Command with Read Data (for example, LSC\_READ\_STATUS)

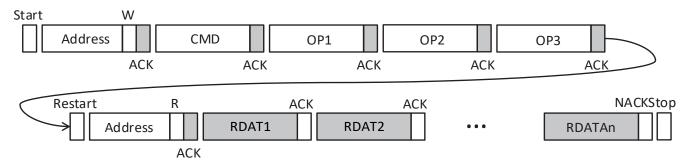

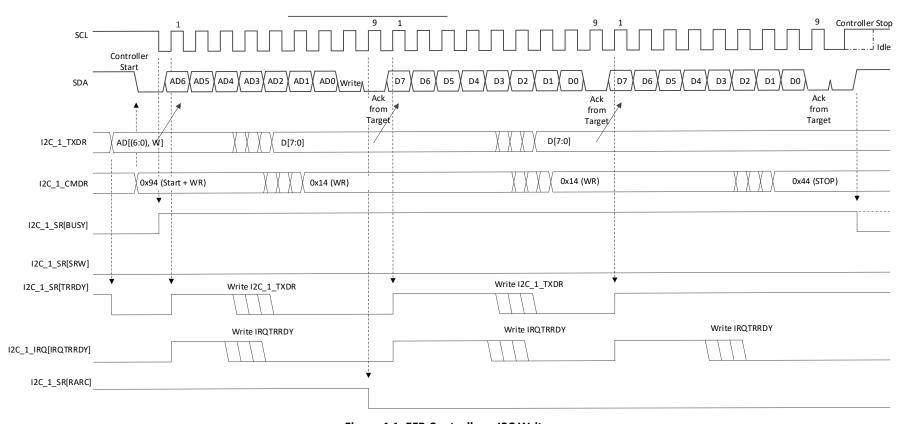

# 4. I2C Functional Waveforms

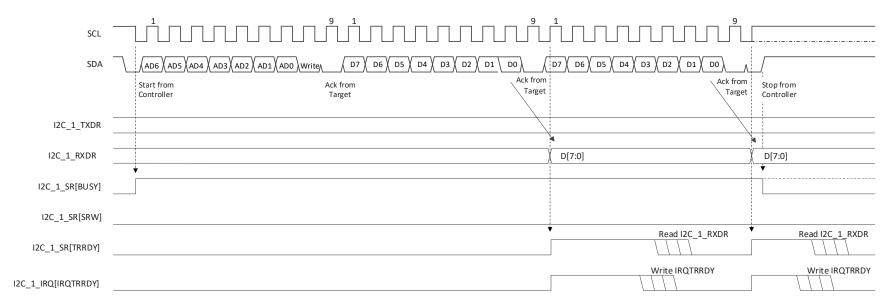

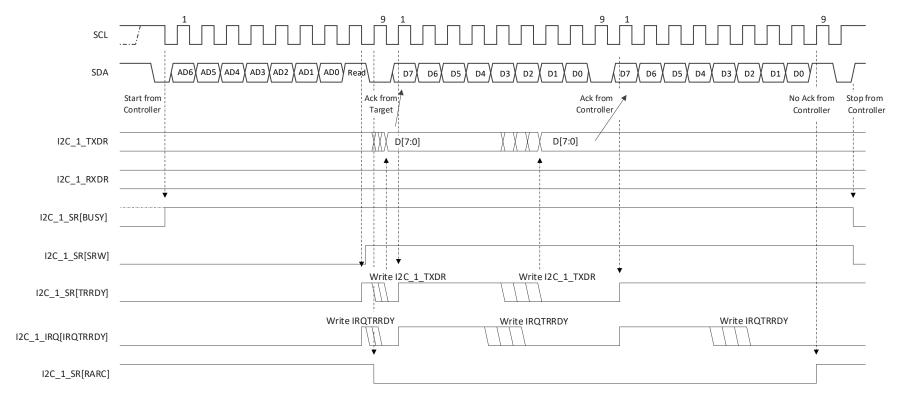

Figure 4.1. EFB Controller – I2C Write

Figure 4.2. EFB Controller - I2C Read

Figure 4.3. EFB Target – I2C Write

Figure 4.4. EFB Target - I2C Read

# 5. I2C Timing Diagram

Figure 5.1. I2C Bit Transfer Timing

# 6. I2C Simulation Model

The I2C EFB Register Map translation to the MachXO4 EFB software simulation model is provided in the tables below.

**Table 6.1. I2C Primary Simulation Mode**

| I2C Primary Register Name | Register Size/Bit<br>Location | Register<br>Function | Address I2C<br>Primary | Access     | Simulation Model<br>Register Name | Simulation Model Register Path                                              |

|---------------------------|-------------------------------|----------------------|------------------------|------------|-----------------------------------|-----------------------------------------------------------------------------|

| I2C_1_CR                  | [7:0]                         | Control              | 0x40                   | Read/Write | i2ccr1[7:0]                       | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| 12CEN                     | 7                             | _                    | _                      | _          | i2c_en                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| GCEN                      | 6                             | _                    | _                      | _          | i2c_gcen                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| WKUPEN                    | 5                             | _                    | _                      | _          | i2c_wkupen                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| SDA_DEL_SEL[1:0]          | [3:2]                         | _                    | _                      | _          | sda_del_sel                       | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| I2C_1_CMDR                | [7:0]                         | Command              | 0x41                   | Read/Write | i2ccmdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| STA                       | 7                             | _                    | _                      | _          | i2c_sta                           | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| STO                       | 6                             | _                    | _                      | _          | i2c_sto                           | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| RD                        | 5                             | _                    | _                      | _          | i2c_rd                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| WR                        | 4                             | _                    | _                      | _          | i2c_wt                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| АСК                       | 3                             | _                    | _                      | _          | i2c_nack                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| CKSDIS                    | 2                             | _                    | _                      | _          | i2c_cksdis                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| I2C_1_BR0                 | [7:0]                         | Clock Pre-<br>scale  | 0x42                   | Read/Write | i2cbr[7:0]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| I2C_PRESCALE[7:0]         | [7:0]                         | _                    | _                      | _          | i2cbr[7:0]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/ |

| I2C Primary Register Name | Register Size/Bit<br>Location | Register<br>Function | Address I2C<br>Primary | Access     | Simulation Model<br>Register Name | Simulation Model Register Path                                               |

|---------------------------|-------------------------------|----------------------|------------------------|------------|-----------------------------------|------------------------------------------------------------------------------|

| I2C_1_BR1                 | [7:0]                         | Clock Pre-<br>scale  | 0x43                   | Read/Write | i2cbr[9:8]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/  |

| I2C_PRESCALE[9:8]         | [1:0]                         | _                    | _                      | _          | i2cbr[9:8]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/  |

| I2C_1_TXDR                | [7:0]                         | Transmit<br>Data     | 0x44                   | Write      | i2ctxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/  |

| I2C_Transmit_Data[7:0]    | [7:0]                         | _                    | _                      | _          | i2ctxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/  |

| I2C_1_SR                  | [7:0]                         | Status               | 0x45                   | Read       | i2csr[7:0]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/njport_unit/i2c_1st/  |

| TIP                       | 7                             | _                    | _                      | _          | i2c_tip_sync                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| BUSY                      | 6                             | _                    | _                      | _          | i2c_busy_sync                     | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| RARC                      | 5                             | _                    | _                      | _          | i2c_rarc_sync                     | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| SRW                       | 4                             | _                    | _                      | _          | i2c_srw_sync                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| ARBL                      | 3                             | _                    | _                      | _          | i2c_arbl                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| TRRDY                     | 2                             | _                    | _                      | _          | i2c_trrdy                         | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| TROE                      | 1                             | _                    | _                      | _          | i2c_troe                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| HGC                       | 0                             | _                    | _                      | _          | i2c_hgc                           | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| I2C_1_GCDR                | [7:0]                         | General Call         | _                      | _          | i2cgcdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| I2C_GC_Data[7:0]          | [7:0]                         | _                    | _                      | _          | i2cgcdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| I2C_1_RXDR                | [7:0]                         | Receive<br>Data      | _                      | -          | i2crxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| I2C Primary Register Name | Register Size/Bit<br>Location | Register<br>Function | Address I2C<br>Primary | Access | Simulation Model<br>Register Name                                                                                       | Simulation Model Register Path                                               |

|---------------------------|-------------------------------|----------------------|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| I2C_Receive_Data[7:0]     | [7:0]                         | _                    | _                      | _      | i2crxdr[7:0]                                                                                                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu<br>/ njport_unit/i2c_1st/ |

| I2C_1_IRQ                 | [7:0]                         | IRQ                  | _                      | _      | {1'b0, 1'b0, 1'b0,<br>1'b0,<br>i2csr_1st_irqsts_3,<br>i2csr_1st_irqsts_2,<br>i2csr_1st_irqsts_1,<br>i2csr_1st_irqsts_0} | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQARBL                   | 3                             | _                    | _                      | _      | i2csr_1st_irqsts_3                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQTRRDY                  | 2                             | _                    | _                      | _      | i2csr_1st_irqsts_2                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQTROE                   | 1                             | _                    | _                      | _      | i2csr_1st_irqsts_1                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQHGC                    | 0                             | _                    | _                      | _      | i2csr_1st_irqsts_0                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| I2C_1_IRQEN               | [7:0]                         | IRQ Enable           | _                      | _      | {1'b0, 1'b0, 1'b0,<br>1'b0,<br>i2csr_1st_irqena_3,<br>i2csr_1st_irqena_2,<br>i2csr_1st_irqena_1,<br>i2csr_1st_irqena_0} | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQARBLEN                 | 3                             | _                    | _                      | _      | i2csr_1st_irqena_3                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQTRRDYEN                | 2                             | _                    | _                      | _      | i2csr_1st_irqena_2                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQTROEEN                 | 1                             | _                    | _                      | _      | i2csr_1st_irqena_1                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

| IRQHGCEN                  | 0                             | _                    | _                      | _      | i2csr_1st_irqena_0                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/                                         |

**Table 6.2. I2C Secondary Simulation Mode**

| I2C Secondary Register Name | Register Size/Bit<br>Location | Register<br>Function | Address I2C<br>Secondary | Access     | Simulation Model<br>Register Name | Simulation Model Register Path                                              |

|-----------------------------|-------------------------------|----------------------|--------------------------|------------|-----------------------------------|-----------------------------------------------------------------------------|

| I2C_2_CR                    | [7:0]                         | Control              | 0x4A                     | Read/Write | i2ccr1[7:0]                       | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2CEN                       | 7                             | _                    | _                        | _          | i2c_en                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| GCEN                        | 6                             | _                    | _                        | _          | i2c_gcen                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| WKUPEN                      | 5                             | _                    | _                        | _          | i2c_wkupen                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| SDA_DEL_SEL[1:0]            | [3:2]                         | _                    | _                        | _          | sda_del_sel                       | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_CMDR                  | [7:0]                         | Command              | 0x4B                     | Read/Write | i2ccmdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| STA                         | 7                             | _                    | _                        | _          | i2c_sta                           | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| STO                         | 6                             | _                    | _                        | _          | i2c_sto                           | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| RD                          | 5                             | _                    | _                        | _          | i2c_rd                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| WR                          | 4                             | _                    | _                        | _          | i2c_wt                            | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| ACK                         | 3                             | _                    | _                        | _          | i2c_nack                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| CKSDIS                      | 2                             | _                    | _                        | _          | i2c_cksdis                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_BR0                   | [7:0]                         | Clock Pre-<br>scale  | 0x4C                     | Read/Write | i2cbr[7:0]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_PRESCALE[7:0]           | [7:0]                         | _                    | _                        | _          | i2cbr[7:0]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_BR1                   | [7:0]                         | Clock Pre-<br>scale  | 0x4D                     | Read/Write | i2cbr[9:8]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_PRESCALE[9:8]           | [1:0]                         | _                    | _                        | _          | i2cbr[9:8]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/                         |

| I2C Secondary Register Name | Register Size/Bit<br>Location | Register<br>Function | Address I2C<br>Secondary | Access     | Simulation Model<br>Register Name | Simulation Model Register Path                                              |

|-----------------------------|-------------------------------|----------------------|--------------------------|------------|-----------------------------------|-----------------------------------------------------------------------------|

|                             |                               |                      |                          |            |                                   | njport_unit/i2c_2nd/                                                        |

| I2C_2_TXDR                  | [7:0]                         | Transmit<br>Data     | 0x4E                     | Write      | i2ctxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_Transmit_Data[7:0]      | [7:0]                         | _                    | _                        | _          | i2ctxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_SR                    | [7:0]                         | Status               | 0x4F                     | Read       | i2csr[7:0]                        | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| TIP                         | 7                             | _                    | _                        | _          | i2c_tip_sync                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| BUSY                        | 6                             | _                    | _                        | _          | i2c_busy_sync                     | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| RARC                        | 5                             | _                    | _                        | _          | i2c_rarc_sync                     | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| SRW                         | 4                             | _                    | _                        | _          | i2c_srw_sync                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| ARBL                        | 3                             | _                    | _                        | _          | i2c_arbl                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| TRRDY                       | 2                             | _                    | _                        | _          | i2c_trrdy                         | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| TROE                        | 1                             | _                    | _                        | _          | i2c_troe                          | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| HGC                         | 0                             | _                    | _                        | _          | i2c_hgc                           | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_GCDR                  | [7:0]                         | General Call         | 0x50                     | Read       | i2cgcdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_GC_Data[7:0]            | [7:0]                         | _                    | _                        | _          | i2cgcdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_RXDR                  | [7:0]                         | Receive<br>Data      | 0x51                     | Read       | i2crxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_Receive_Data[7:0]       | [7:0]                         | _                    | _                        | _          | i2crxdr[7:0]                      | /efb_top/config_plus_inst/config_core_inst/cfg_cdu/<br>njport_unit/i2c_2nd/ |

| I2C_2_IRQ                   | [7:0]                         | IRQ                  | 0x52                     | Read/Write | {1'b0, 1'b0, 1'b0,                | /efb_top/efb_pll_sci_inst/u_efb_sci/                                        |

| I2C Secondary Register Name | Register Size/Bit<br>Location | Register<br>Function | Address I2C<br>Secondary | Access     | Simulation Model<br>Register Name                                                                                       | Simulation Model Register Path       |

|-----------------------------|-------------------------------|----------------------|--------------------------|------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                             |                               |                      |                          |            | 1'b0,<br>i2csr_2nd_irqsts_3,<br>i2csr_2nd_irqsts_2,<br>i2csr_2nd_irqsts_1,<br>i2csr_2nd_irqsts_0}                       |                                      |

| IRQARBL                     | 3                             | _                    | _                        | _          | i2csr_2nd_irqsts_3                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/ |

| IRQTRRDY                    | 2                             | _                    | _                        | _          | i2csr_2nd_irqsts_2                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/ |

| IRQTROE                     | 1                             | _                    | _                        | _          | i2csr_2nd_irqsts_1                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/ |

| IRQHGC                      | 0                             | _                    | _                        | _          | i2csr_2nd_irqsts_0                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/ |

| I2C_2_IRQEN                 | [7:0]                         | IRQ Enable           | 0x53                     | Read/Write | {1'b0, 1'b0, 1'b0,<br>1'b0,<br>i2csr_2nd_irqena_3,<br>i2csr_2nd_irqena_2,<br>i2csr_2nd_irqena_1,<br>i2csr_2nd_irqena_0} | /efb_top/efb_pll_sci_inst/u_efb_sci/ |

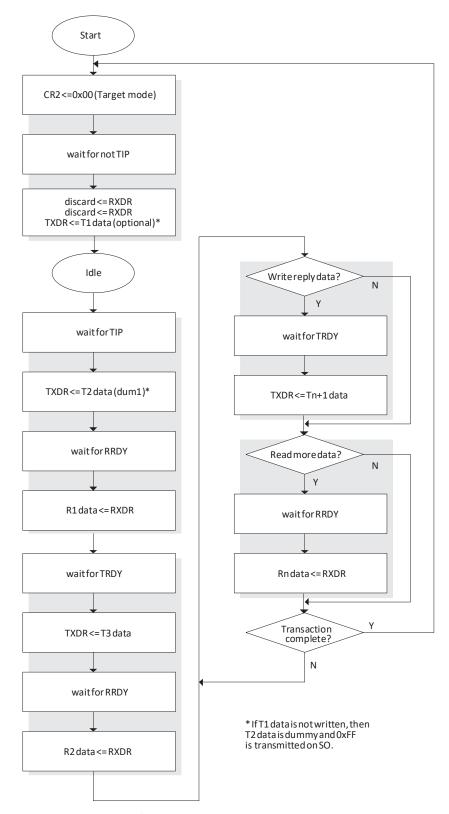

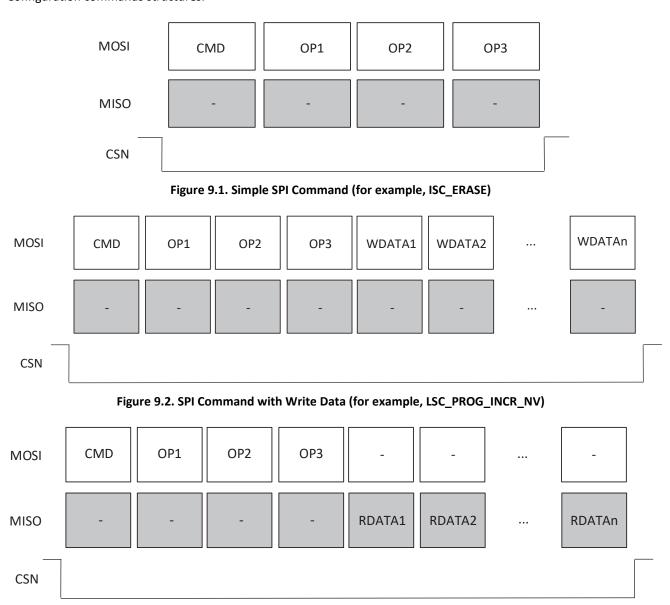

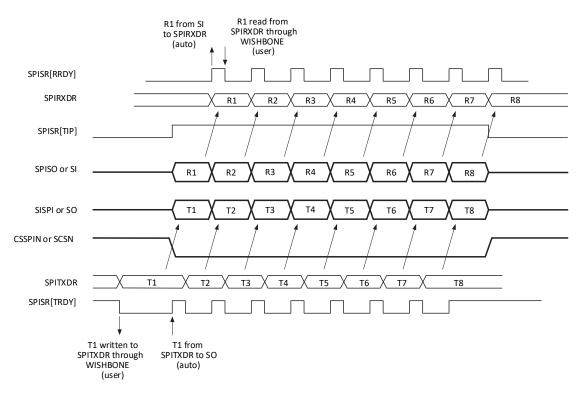

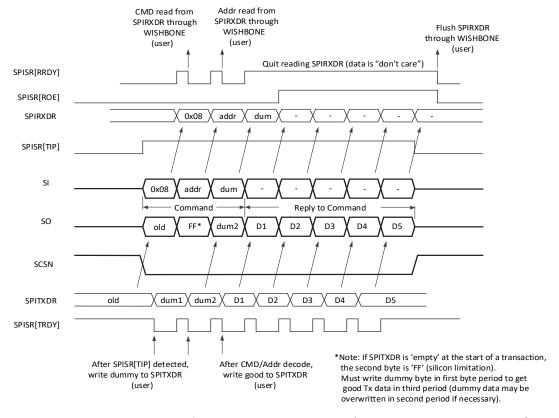

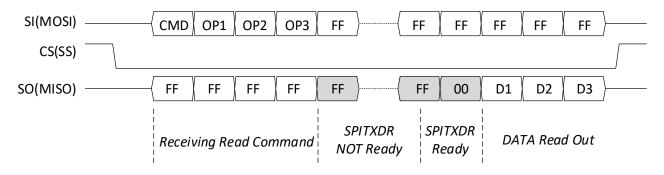

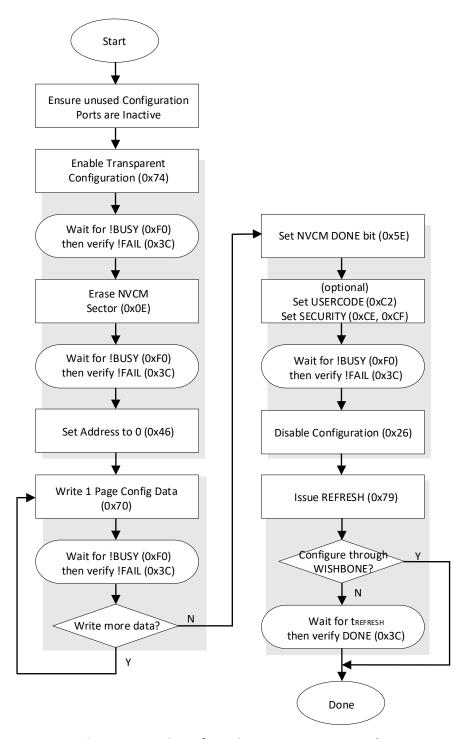

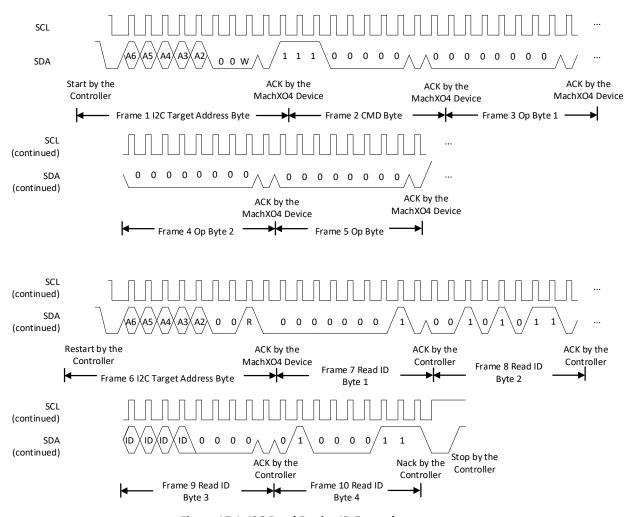

| IRQARBLEN                   | 3                             | _                    | _                        | _          | i2csr_2nd_irqena_3                                                                                                      | /efb_top/efb_pll_sci_inst/u_efb_sci/ |