# **SEDC Controller IP**

IP Version: v1.1.0

# **User Guide**

FPGA-IPUG-02290-1.2

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

|             | ns in This Document                                                                      |    |

|-------------|------------------------------------------------------------------------------------------|----|

| 1. Introdu  | ıction                                                                                   | 8  |

| 1.1. C      | Overview of the IP                                                                       | 8  |

| 1.2. C      | Quick Facts                                                                              | 8  |

| 1.3. II     | Support Summary                                                                          | g  |

| 1.4. F      | eatures                                                                                  | 10 |

| 1.5. L      | icensing Information                                                                     | 10 |

| 1.5.1.      | Ordering Part Number                                                                     | 10 |

| 1.6. N      | Ainimum Device Requirements                                                              | 10 |

| 1.7. N      | laming Conventions                                                                       | 11 |

| 1.7.1.      | Nomenclature                                                                             | 11 |

| 1.7.2.      | Signal Names                                                                             | 11 |

| 1.7.3.      | Attribute Names                                                                          | 11 |

| 2. Function | onal Description                                                                         | 12 |

| 2.1. II     | P Architecture Overview                                                                  | 12 |

| 2.1.1.      | SEDC Hard Block Overview                                                                 | 13 |

| 2.1.2.      | SEDC Controller IP Configuration Modes                                                   | 14 |

| 2.1.3.      | SEDC Controller IP Flow                                                                  | 15 |

| 2.2. C      | locking                                                                                  | 16 |

| 2.3. R      | eset                                                                                     | 17 |

| 2.4. L      | Iser Interfaces                                                                          | 18 |

| 3. IP Para  | meter Description                                                                        | 19 |

| 4. Signal ( | Description                                                                              | 20 |

| •           | lock Interface                                                                           |    |

| 4.2. R      | eset Interface                                                                           | 20 |

| 4.3. C      | ontrol Interface                                                                         | 20 |

|             | Nonitor Interface                                                                        |    |

| 5. Designi  | ing with the IP                                                                          | 23 |

|             | Senerating and Instantiating the IP                                                      |    |

| 5.1.1.      | Generated Files and File Structure                                                       |    |

| 5.2. D      | Pesign Implementation                                                                    | 25 |

|             | pecifying the Strategy                                                                   |    |

|             | unning Functional Simulation                                                             |    |

| 5.4.1.      | Simulation Results                                                                       |    |

| 5.4.2.      | Limitations of the SEDC Hard Block Simulation Model                                      | 29 |

| 5.4.3.      | Testbench Files and Structure                                                            | 29 |

| 5.4.4.      | Input Stimulus Patterns                                                                  | 31 |

| 6. Debugg   | zing                                                                                     |    |

| 7. Design   | Considerations                                                                           | 34 |

| 7.1. A      | synchronous Reset (arst i) Timing Requirements                                           | 34 |

| 7.2. A      | .ssert and Hold auto_correct_i High throughout a Complete SEDC Scan                      | 34 |

|             | ssert and Hold continuous_i High throughout Consecutive SEDC Scans                       |    |

|             | rocess Error Information Only when status_update_o Asserts                               |    |

|             | vailability of Clock Divider Value after Initialization                                  |    |

|             | dd Debouncer on Signal Driven by Mechanical Switch/Button                                |    |

|             | mplement Reset Synchronizer for Asynchronous Reset Signal                                |    |

|             | Issues                                                                                   |    |

|             | ncorrect Clock Divider Value in Simulation                                               |    |

|             | EDC Unable to Detect Errors After 1-bit or 2-bit SEI Bitstream Injection                 |    |

|             | rror Bit and Region Location Mismatch Between Hardware and Radiant SEI Bitstream Profile |    |

| Appendix A. |                                                                                          |    |

|             |                                                                                          |    |

| Appendix B.  | Walkthrough of Example Simulation Waveforms                                        | 39 |

|--------------|------------------------------------------------------------------------------------|----|

| B.1. Po      | ort-Driven Dynamic Mode                                                            | 39 |

| B.2. Co      | ontinuous Mode                                                                     | 42 |

| B.2.1.       | Scenario 1: 1-bit Correctable Error in Continuous Mode (Auto-Correction Mode = ON) | 42 |

| B.2.2.       | Scenario 2: Multi-bit Error in Continuous Mode (Auto-Correction Mode = ON)         | 44 |

| Appendix C.  | Example of Including +define+LSCC_SEDC_CONTROLLER_RTL_SIM in Generated *.f File    | 46 |

| Appendix D.  | Example Verilog/SystemVerilog Code on Asynchronous Reset Timing Requirements       |    |

| Appendix E.  | Example Verilog/SystemVerilog Code for Debouncer                                   | 49 |

| Appendix F.  | Example Verilog/SystemVerilog Code for Reset Synchronizer                          | 50 |

| References   |                                                                                    |    |

| Technical Su | pport Assistance                                                                   | 52 |

| '            | ory                                                                                |    |

# **Figures**

| Figure 2.1. SEDC Controller IP Block Diagram                                                                      | 12 |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2. SEDC Hard Block System Block Diagram                                                                  | 13 |

| Figure 2.3. SEDC Controller IP Flowchart                                                                          | 15 |

| Figure 2.4. SEDC Controller IP Clock Domain Block Diagram                                                         | 16 |

| Figure 2.5. SEDC Controller IP Resets Block Diagram                                                               | 17 |

| Figure 5.1. Module/IP Block Wizard                                                                                | 23 |

| Figure 5.2. IP Configuration                                                                                      | 24 |

| Figure 5.3. Check Generated Result                                                                                | 24 |

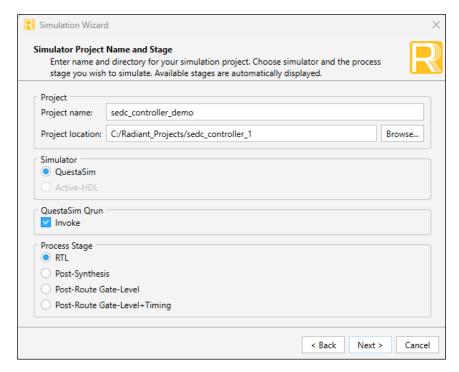

| Figure 5.4. Simulation Wizard                                                                                     | 26 |

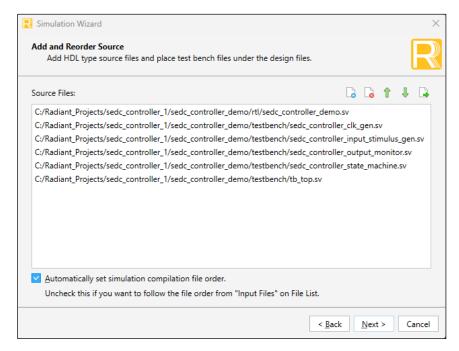

| Figure 5.5. Add and Reorder Source                                                                                | 26 |

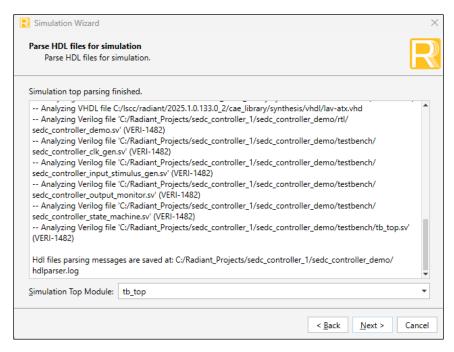

| Figure 5.6. Parse HDL files for Simulation                                                                        | 27 |

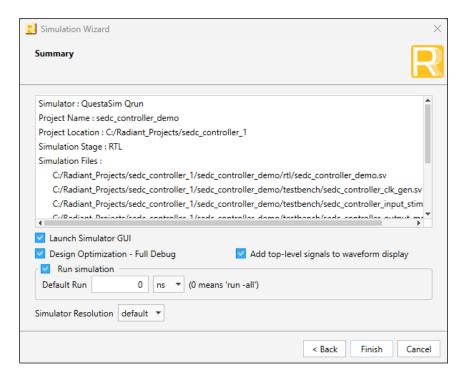

| Figure 5.7. Summary                                                                                               | 27 |

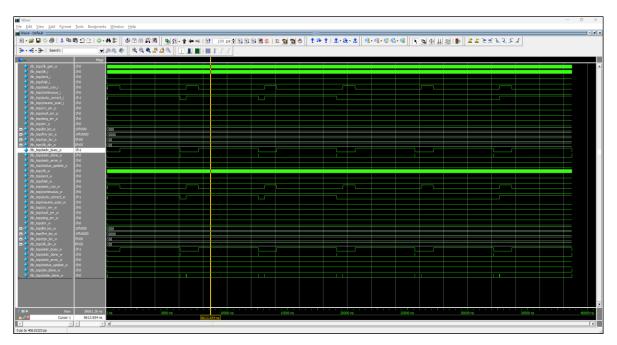

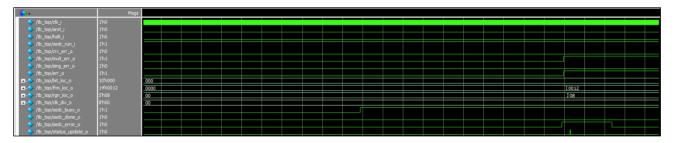

| Figure 5.8. Simulation Waveform                                                                                   |    |

| Figure 5.9. Simulation Completion Log                                                                             | 28 |

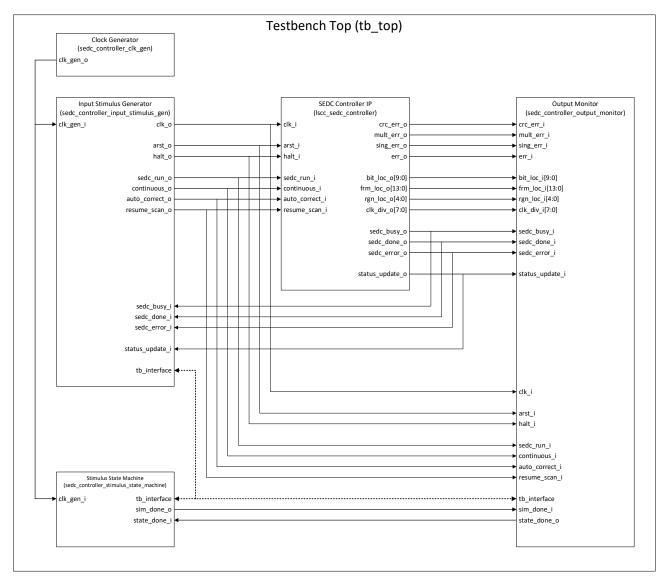

| Figure 5.10. Testbench Structure                                                                                  | 30 |

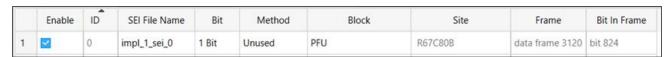

| Figure 8.1. Combination of 1-bit and 2-bit SEI Bitstreams                                                         | 36 |

| Figure 8.2. Example of 1-bit SEI Bitstream                                                                        | 36 |

| Figure 8.3. Reveal Analyzer Waveform for 1-bit SEI Bitstream                                                      | 37 |

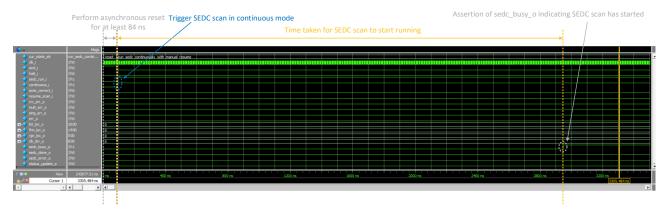

| Figure B.1. Asynchronous Reset and Triggering of SEDC Scan in Continuous ModeMode                                 |    |

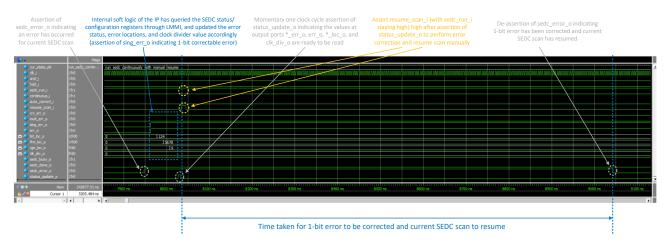

| Figure B.2. 1-bit Error Occurrence and Manual Error Correction/Resume Scan                                        | 39 |

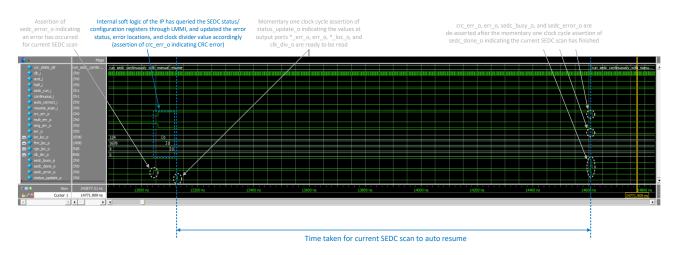

| Figure B.3. CRC Error Occurrence and Auto Resume Scan                                                             |    |

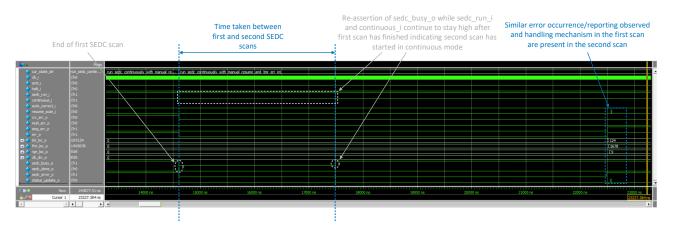

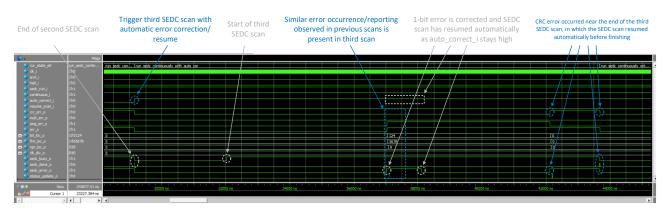

| Figure B.4. End of First SEDC Scan and Triggering/1-bit Error Occurrence of Second SEDC Scan in Continuous Mode . | 40 |

| Figure B.5. End of Second SEDC Scan and Triggering/Error Occurrences/End of Third SEDC Scan in Continuous and     |    |

| Automatic Error Correction Modes                                                                                  |    |

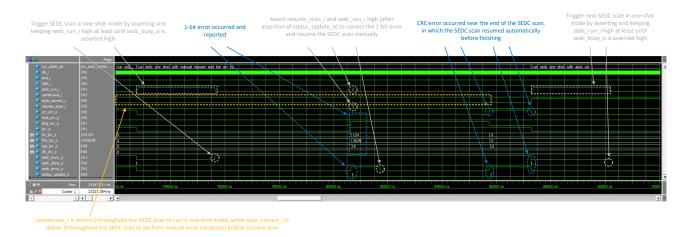

| Figure B.6. Triggering/Error Occurrences/End of SEDC Scan in One-Shot Mode                                        | 41 |

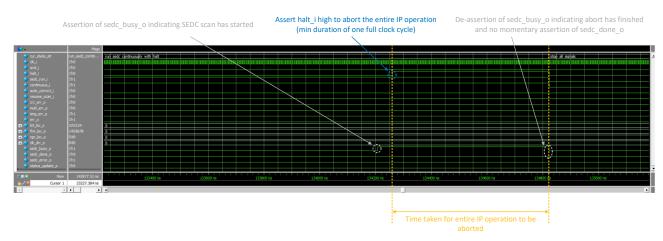

| Figure B.7. Aborting of SEDC Scan                                                                                 |    |

| Figure B.8. Asynchronous Reset De-assertion and Triggering of SEDC Scan in Continuous Mode (1-bit Error)          |    |

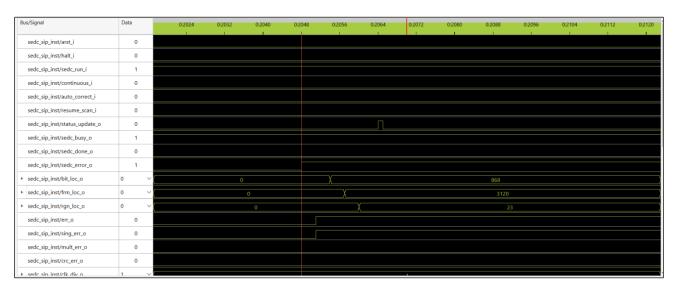

| Figure B.9. 1-bit Error Detection and Auto-Correction                                                             |    |

| Figure B.10. CRC Error Occurrence and End of First SEDC Scan                                                      | 43 |

| Figure B.11. Second SEDC Scan in Continuous Mode                                                                  |    |

| Figure B.12. Asynchronous Reset De-assertion and Triggering of SEDC Scan in Continuous Mode (Multi-bit Error)     |    |

| Figure B.13. Multi-bit Error Detection and Resume Scan                                                            |    |

| Figure B.14. CRC Error and End of First SEDC Scan (Multi-bit Error)                                               | 45 |

| Figure B.15. Second SEDC Scan in Continuous Mode (Mult-bit Error)                                                 | 45 |

# **Tables**

| Table 1.1. Summary of the SEDC Controller IP                        | 8        |

|---------------------------------------------------------------------|----------|

| Table 1.2. SEDC Controller IP Support Readiness                     | <u>C</u> |

| Table 2.1. SEDC Controller IP Modules                               | 12       |

| Table 2.2. SEDC Controller IP Configuration Modes                   | 14       |

| Table 2.3. SEDC Controller IP Processes                             | 15       |

| Table 2.4. SEDC_CLK Frequencies with Different Clock Divider Values | 16       |

| Table 2.5. User Interfaces                                          | 18       |

| Table 3.1. SEDC Controller IP Attributes                            |          |

| Table 4.1. Clock Port                                               | 20       |

| Table 4.2. Reset Ports                                              | 20       |

| Table 4.3. Control Ports                                            | 20       |

| Table 4.4. Monitor Ports                                            | 22       |

| Table 5.1. Generated File List                                      |          |

| Table 5.2. Testbench Components and File List                       |          |

| Table 5.3. Input Stimulus Description                               | 31       |

| Table A.1. Resource Utilization                                     | 38       |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                         |  |  |  |

|--------------|----------------------------------------------------|--|--|--|

| ASCII        | American Standard Code for Information Interchange |  |  |  |

| ASR          | Address Shift Register                             |  |  |  |

| CRAM         | Configuration Random Access Memory                 |  |  |  |

| CRC          | Cyclic Redundancy Check                            |  |  |  |

| CRC32        | Cyclic Redundancy Check – 32 bits                  |  |  |  |

| DSR          | Data Shift Register                                |  |  |  |

| DUT          | Design Under Test                                  |  |  |  |

| EBR          | Embedded Block RAM                                 |  |  |  |

| ECC          | Error Correction Code                              |  |  |  |

| FPGA         | Field Programmable Gate Array                      |  |  |  |

| FSM          | Finite State Machine                               |  |  |  |

| GPIO         | General Purpose I/O                                |  |  |  |

| GUI          | Graphical User Interface                           |  |  |  |

| HDL          | Hardware Description Language                      |  |  |  |

| I/O          | Input/Output                                       |  |  |  |

| IP           | Intellectual Property                              |  |  |  |

| LMMI         | Lattice Memory Mapped Interface                    |  |  |  |

| LSE          | Lattice Synthesis Engine                           |  |  |  |

| LUT          | Lookup Table                                       |  |  |  |

| OSC          | Oscillator                                         |  |  |  |

| PDC          | Post-Synthesis Design Constraint                   |  |  |  |

| PLL          | Phase Locked Loop                                  |  |  |  |

| POR          | Power On Reset                                     |  |  |  |

| RAM          | Random Access Memory                               |  |  |  |

| RTL          | Register Transfer Level                            |  |  |  |

| SEC          | Soft Error Correction                              |  |  |  |

| SED          | Soft Error Detection                               |  |  |  |

| SEDC         | Soft Error Detection/Correction                    |  |  |  |

| SEU          | Single Event Upset                                 |  |  |  |

| TMR          | Triple Modular Redundancy                          |  |  |  |

## 1. Introduction

Soft error detection (SED) and soft error correction (SEC), collectively referred to as soft error detection and correction (SEDC), are features that enable the detection and correction of soft errors in the configuration memory of an FPGA device. This document describes the SEDC Controller IP.

#### 1.1. Overview of the IP

The SEDC Controller IP is designed to ensure the effective and reliable operation of the SEDC system by integrating additional soft logic around the SEDC hard block. This integration simplifies the interface and enhances overall functionality, making it easier for users to implement and benefit from advanced error detection and correction features. The IP manages state transitions, drives inputs, captures outputs, and provides internal feedback, all while ensuring robust performance and high reliability through the implementation of triple modular redundancy (TMR).

This IP is suitable for applications requiring high reliability and robust error detection and correction, such as:

- Aerospace and defense: Ensuring system reliability in harsh environments

- Automotive: Enhancing safety and reliability in critical systems

- Industrial automation: Maintaining system integrity in industrial control systems

- Medical devices: Providing reliable operation in life-critical applications

- Telecommunications: Ensuring data integrity in communication systems

### 1.2. Quick Facts

Table 1.1. Summary of the SEDC Controller IP

|                      | Supported Devices        | Lattice Avant™, Certus™-N2                                                                           |  |  |  |

|----------------------|--------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| IP Requirements      | IP Changes               | Refer to the SEDC Controller IP Release Notes (FPGA-RN-02081).                                       |  |  |  |

| Danas I Itiliantias  | Supported User Interface | General purpose I/O (GPIO)                                                                           |  |  |  |

| Resource Utilization | Resources                | Refer to Appendix A. Resource Utilization.                                                           |  |  |  |

|                      | Lattice Implementation   | IP Core v1.0.0 – Lattice Radiant™ Software 2025.1 IP Core v1.1.0 – Lattice Radiant Software 2025.1.1 |  |  |  |

| Design Tool Support  | Synthesis                | Synopsys® Synplify Pro® for Lattice                                                                  |  |  |  |

|                      | Simulation               | Refer to the Lattice Radiant Software User Guide for the list of supported simulators.               |  |  |  |

# **1.3.** IP Support Summary

**Table 1.2. SEDC Controller IP Support Readiness**

| TUDIC TIE | table 1121 of the Controller in Support Redumess |                                                   |           |            |       |                     |            |     |                    |                          |                                        |

|-----------|--------------------------------------------------|---------------------------------------------------|-----------|------------|-------|---------------------|------------|-----|--------------------|--------------------------|----------------------------------------|

| IP        | Radiant                                          | adiant Synthesis Mapping Place and Timing Bitstre | Bitstream | Simulation |       |                     |            |     |                    |                          |                                        |

| Version   | Version                                          | Synplify<br>Pro                                   | LSE       |            | Route |                     | Generation | RTL | Post-<br>Synthesis | Post-Route<br>Gate-Level | Post-Route<br>Gate-Level<br>and Timing |

| 1.0.0     | 2025.1                                           | Yes                                               | _         | Yes        | Yes   | Closed at<br>80 MHz | Yes        | Yes | Yes                | Yes                      | Yes                                    |

#### 1.4. Features

Key features of the SEDC Controller IP include:

- Soft IP features (soft logic)

- Modes: Supports four modes of operation through combinations of the following:

- One-shot or continuous scanning

- No error correction or automatic error correction

- Finite state machine (FSM): Controls the system's operational states and ensures smooth transitions between them

- Signal management: Efficiently handles the signals sent to and received from the SEDC hard block, ensuring seamless communication

- Error and status reporting: Monitors the SEDC hard block output ports to provide accurate error and status reporting

- Simulation support: Supports error injection for easy simulation of system response

- Triple modular redundancy (TMR): Ensures high reliability by applying TMR to critical registers, protecting against errors

- Simplified interfaces: Simplifies the Lattice memory mapped interface (LMMI) with internal translation, making

it easier for users to implement and interact with the SEDC hard block

- Hard IP features (SEDC hard block)

- Frame by frame SED check

- Multiple regions (four regions as hardware default) run in parallel for fast SED and SEC performance

- 1-bit and multi-bit error detection

- Error correction code (ECC) to correct 1-bit errors at the frame level

- 32-bit cyclic redundancy check (CRC32) calculation on the entire configuration RAM (CRAM) in parallel with FCC

- Programmable SED clock with a wide frequency range

- Force error capability for system-level simulation

### 1.5. Licensing Information

The SEDC Controller IP is provided at no additional cost with the Lattice Radiant software.

#### 1.5.1. Ordering Part Number

The SEDC Controller IP does not require an ordering part number.

#### 1.6. Minimum Device Requirements

The minimum device requirements for the SEDC Controller IP are as follows:

- Supports SEDC.

- Meets the resource utilization as captured in Table A.1. Resource utilization for soft logic (LUTs and registers) by this IP is relatively small and primarily dependent on logic optimization by synthesis and place-and-route.

Therefore, Lattice does not expect significant differences in resource utilization across different devices.

# 1.7. Naming Conventions

#### 1.7.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.7.2. Signal Names

Signal names that end with:

- \_n are active low signals (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

#### 1.7.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

# 2. Functional Description

#### 2.1. IP Architecture Overview

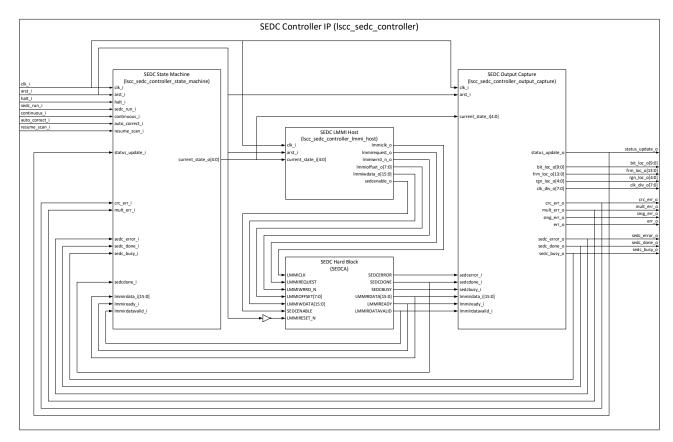

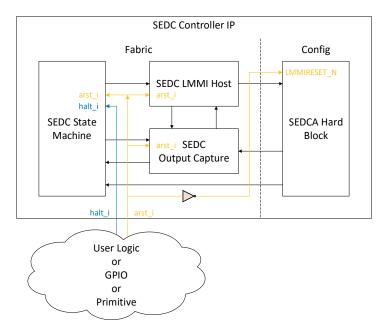

Figure 2.1 shows the SEDC Controller IP block diagram. The IP includes several modules as described in Table 2.1. Additionally, an inverter is implemented on the internal connection between the top-level input port arst\_i and the LMMIRESET\_N port of the SEDC hard block. This inverter ensures that the appropriate signal level is presented at the SEDC hard block so that reset operations of all modules in the IP are aligned.

Figure 2.1. SEDC Controller IP Block Diagram

**Table 2.1. SEDC Controller IP Modules**

| Module              | Module Name in HDL                  | Description                                                                                                                                                                                                                                                                                                               |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEDC State Machine  | lscc_sedc_controller_state_machine  | This module contains the FSM that performs state transition based on user input signals and/or feedback signals from the SEDC output capture module and SEDC hard block. Internal registers are implemented with TMR.                                                                                                     |

| SEDC LMMI Host      | lscc_sedc_controller_lmmi_host      | This module drives the inputs of the SEDC hard block based on the state of the FSM. Internal registers are implemented with TMR.                                                                                                                                                                                          |

| SEDCA Primitive     | SEDCA                               | Primitive representing the SEDC hard block. Refer to the SEDC Hard Block Overview section for more information.                                                                                                                                                                                                           |

| SEDC Output Capture | lscc_sedc_controller_output_capture | This module monitors and captures the output signals from the SEDC hard block into internal registers and reports out the signals to the top-level output ports as necessary, based on the state of the FSM. The module also provides feedback signals to the state machine. Internal registers are implemented with TMR. |

#### 2.1.1. SEDC Hard Block Overview

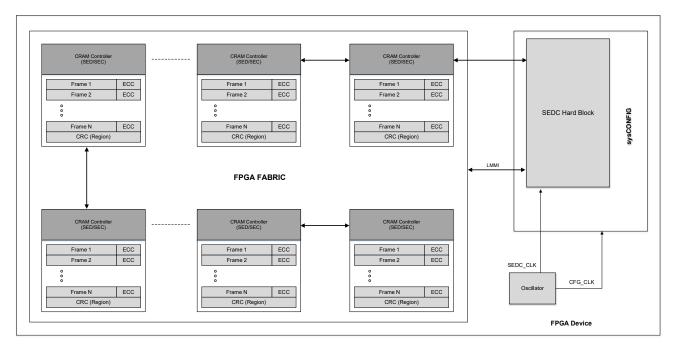

Figure 2.2 shows the system-level view of the SEDC hard block. The SEDC hard block is part of the configuration (sysCONFIG) block in supported FPGA devices. Configuration data is divided into frames across multiple regions, allowing the FPGA device to be programmed either as a whole or in specific regions. The SED hardware reads serial data from the FPGA device configuration memory frame-by-frame in the background while the device is in user function mode and performs ECC calculations on every frame of configuration data.

Figure 2.2. SEDC Hard Block System Block Diagram

When a 1-bit error is detected, an error indicator for 1-bit error is generated and the SED resumes operation. If SEC is enabled, the 1-bit error is corrected before the SED resumes operation. The corrected value is rewritten to the frame using ECC information. If multiple 1-bit errors are detected within a frame of configuration data, an error indicator for multi-bit error is generated.

In parallel, cyclic redundancy check (CRC) is calculated for the entire CRAM content along with ECC. After ECC is calculated on all frames of the configuration data, CRC is calculated for the configuration data in the entire device. Full-chip CRC and frame-by-frame ECC calculations do not include the embedded block RAM (EBR). EBRs provide a separate and optional ECC for SED or SEC of the EBR content. Distributed RAM data stored in the CRAM are masked during SED or SEC because RAM content may change during user operation and hence cannot be covered by the SEDC hard block without generating false SEDC errors. The distributed RAM enable bit set in CRAM is covered during SED or SEC.

# 2.1.2. SEDC Controller IP Configuration Modes

The SEDC Controller IP has four different configuration modes as described in Table 2.2. The SEDC Controller IP only configures the SEDC hard block in one-shot and no auto-correction modes. All other modes are supported through soft logic around the SEDC hard block.

**Table 2.2. SEDC Controller IP Configuration Modes**

| SEDC Mode       | Error Correction Mode   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continuous Mode | Auto-Correction Mode    | The SEDC Controller IP continuously scans frames. Scanning continues regardless of any errors detected.  If a 1-bit error is detected, the IP notifies the user about the error, corrects the error automatically, and resumes scanning frames (without re-checking whether error is corrected) immediately after the correction.  If a multi-bit or CRC error is detected, the IP continues scanning frames without halting and notifies the user about the error.                                           |

| Continuous Mode | No Auto-Correction Mode | The SEDC Controller IP continuously scans frames. Scanning halts only when a 1-bit error is detected and continues after manual intervention.  If a 1-bit error is detected, the IP halts and notifies the user about the error. The IP only resumes scanning frames after the error is corrected through manual intervention.  If a multi-bit or CRC error is detected, the IP continues scanning frames without halting and notifies the user about the error.                                              |

| One-Shot Mode   | Auto-Correction Mode    | The SEDC Controller IP performs a one-time scan of all frames. Scanning continues regardless of any errors detected until all frames are scanned.  If a 1-bit error is detected, the IP notifies the user about the error, corrects the error automatically, and resumes scanning frames (without re-checking whether error is corrected) immediately after the correction.  If a multi-bit or CRC error is detected, the IP continues scanning frames without halting and notifies the user about the error. |

| One-Shot Mode   | No Auto-Correction Mode | The SEDC Controller IP performs a one-time scan of all frames.  Scanning halts only when a 1-bit error is detected and continues after manual intervention until all frames are scanned.  If a 1-bit error is detected, the IP halts and notifies the user about the error. The IP only resumes scanning frames after the error is corrected through manual intervention.  If a multi-bit or CRC error is detected, the IP continues scanning frames without halting and notifies the user about the error.   |

#### 2.1.3. SEDC Controller IP Flow

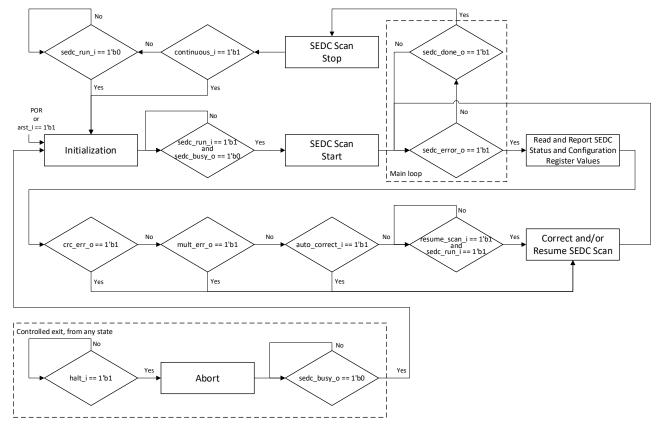

Figure 2.3 shows the high-level flowchart of the SEDC Controller IP. Because of the complexity of the FSM, which comprises over 30 states, this flowchart does not capture details on the complete implementation of the internal FSM. However, this flowchart attempts to facilitate the conceptual understanding of the SEDC Controller IP flow.

Figure 2.3. SEDC Controller IP Flowchart

Table 2.3 describes each of the processes. For more details on IP behaviors, you can explore the testbench that simulates IP behavior as illustrated by the example waveforms in the Walkthrough of Example Simulation Waveforms section. Follow the steps in the Running Functional Simulation section so that the necessary simulation files are included when launching the simulation.

**Table 2.3. SEDC Controller IP Processes**

| Process                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initialization                                                         | <ul> <li>Clears all output registers that drive the output signals crc_err_o, mult_err_o, sing_err_o, err_o, bit_loc_o, frm_loc_o, rgn_loc_o, and clk_div_o to 0.</li> <li>Configures the SEDC hard block through LMMI write transactions.</li> <li>Reads the clock divider value from the SEDC hard block through LMMI read transaction and updates the register that drives the output signal clk_div_o.</li> </ul>                                                          |

| SEDC Scan Start                                                        | <ul> <li>Internal soft logic drives the SEDCENABLE signal of the SEDC hard block high to start a SEDC scan.</li> <li>The output signal sedc_busy_o asserts high once the SEDC hard block starts the scan.</li> </ul>                                                                                                                                                                                                                                                           |

| Read and Report<br>SEDC Status and<br>Configuration<br>Register Values | <ul> <li>Reads the SEDC hard block status and configuration register values through LMMI read transactions.</li> <li>Captures these values into output registers that drive the output signals crc_err_o, mult_err_o, sing_err_o, err_o, bit_loc_o, frm_loc_o, rgn_loc_o, and clk_div_o.</li> <li>Asserts the output signal status_update_o high momentarily for one clock cycle after the error status and locations of all output registers are ready to be read.</li> </ul> |

| Correct and/or<br>Resume SEDC Scan                                     | <ul> <li>Performs error correction and/or resumes scan by informing the SEDC hard block through LMMI write transaction.</li> <li>The output signal sedc_error_o is de-asserted low by the SEDC hard block once it completes the error correction and/or resumes the scan operation.</li> </ul>                                                                                                                                                                                 |

FPGA-IPUG-02290-1.2

| Process        | Description                                                                                       |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------|--|--|--|

| SEDC Scan Stop | Indicates the SEDC hard block has finished the current SEDC scan cycle on all frames.             |  |  |  |

|                | De-asserts the output signal sedc_busy_o low.                                                     |  |  |  |

|                | Asserts the output signal sedc_done_o high momentarily for one clock cycle, immediately after the |  |  |  |

|                | sedc_busy_o signal is de-asserted low.                                                            |  |  |  |

|                | Internal soft logic drives SEDCENABLE signal of the SEDC hard block low.                          |  |  |  |

| Abort          | Aborts the SEDC Controller IP operation gracefully from any state.                                |  |  |  |

|                | Stops all LMMI transactions and/or current SEDC scan.                                             |  |  |  |

|                | Clears all output registers to 0.                                                                 |  |  |  |

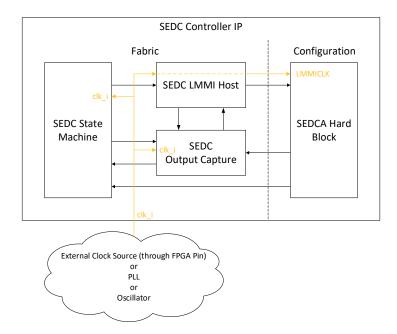

## 2.2. Clocking

Figure 2.4 shows the high-level block diagram of the clock domain for the SEDC Controller IP. There are two clock domains within the sysCONFIG block namely SEDC\_CLK and LMMI clock. However, only the LMMI clock is accessible by the SEDC Controller IP. SEDC\_CLK is hardened to be sourced from the internal oscillator of the FPGA device. The single clock input for the entire IP (clk\_i) can be driven by an external clock source (through an FPGA I/O pin), PLL, or oscillator. This clock is used to clock all soft logic registers and drive the LMMICLK of the SEDC hard block. For the clock frequencies supported by the SEDC Controller IP, refer to Table 4.1. The PLL and oscillator can be instantiated through the FPGA device PLL IP and OSC IP from the Lattice Radiant software IP Catalog, respectively.

Figure 2.4. SEDC Controller IP Clock Domain Block Diagram

While the SEDC\_CLK is not accessible by the SEDC Controller IP, its frequency can be adjusted through the *Clock Divider* attribute. Table 2.4 lists the SEDC\_CLK frequencies with different clock divider values, calculated using the following equation:

$$SEDC\_CLK (MHz) = \frac{400}{Clock \ Divider \ Value}$$

Table 2.4. SEDC\_CLK Frequencies with Different Clock Divider Values

| Clock Divider Value | SEDC_CLK Frequency (MHz) |  |

|---------------------|--------------------------|--|

| 2                   | 200                      |  |

| 3                   | 133.33                   |  |

|                     |                          |  |

| 256                 | 1.56                     |  |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02290-1.2

Clock frequency settings are important for optimizing both performance and power consumption. A slower clk i correspondingly slows the SEDC Controller IP response time. However, the power impact is small because of the SEDC Controller IP's relatively small resource usage (see resource utilization captured in Table A.1). The selection of SEDC CLK directly impacts the SEDC scan and correction times. For example, with the lowest clock divider value of 2, the SEDC CLK frequency is 200 MHz, resulting in shorter scan and correction times. Conversely, with the highest clock divider value of 256, the SEDC CLK frequency is 1.56 MHz, resulting in longer scan and correction times. While the power impact of the SEDC Controller IP is generally small, it can become significantly more pronounced during continuous operation, making careful clock frequency management crucial for maintaining optimal system performance and efficiency.

#### 2.3. Reset

Figure 2.5 shows the high-level block diagram of the resets for the SEDC Controller IP. There are two reset types namely asynchronous reset (arst i) and synchronous halt (halt i). Both resets can be driven by user logic outside of the IP, GPIO, or other primitives.

Figure 2.5. SEDC Controller IP Resets Block Diagram

For asynchronous reset, you must assert this reset high and wait at least 60 µs after the device is configured and has entered user mode before releasing it low. Following this, you can proceed to start the SEDC scan operation. For any subsequent assertions of asynchronous reset, the minimum duration of reset assertion is 84 ns. Asynchronous reset, when asserted high, resets the LMMI logic of the SEDC hard block and immediately clears all the registers in the SEDC state machine, SEDC LMMI host, and SEDC output capture modules to 0. The SEDC LMMI host also drives 0 to all its signals feeding into the SEDC hard block. Note that an inverter is implemented before asynchronous reset is connected to the LMMIRESET N port of the SEDC hard block because LMMIRESET N is an active low signal. If asynchronous reset is asserted high during an on-going SEDC Controller IP operation, the SEDC state machine immediately returns to the initialization state. After the initialization state, the SEDC Controller IP only allows you to start a new SEDC scan after the SEDC hard block is no longer busy.

The halt reset is used to gracefully abort an on-going SEDC Controller IP operation from any state. At the positive clock edge when halt is high, the SEDC state machine enters the abort state, which immediately causes the SEDC LMMI host to stop LMMI transactions and/or the SEDC scan. All registers in the SEDC output capture module are reset to 0. At the immediate positive clock edge after halt is low, the SEDC state machine returns to the initialization state when the SEDC hard block is no longer busy. The minimum duration of reset assertion for halt is one full clock cycle.

# 2.4. User Interfaces

Table 2.5 lists the available user interfaces of the SEDC Controller IP.

**Table 2.5. User Interfaces**

| User Interface | Communication Standard | d Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Clock          | Digital/Binary         | A single clock input for the entire IP (clk_i) that can be driven by an external clock source (through GPIO), PLL, or oscillator. Clocks all soft logic registers and drives the LMMICLK of the SEDC hard block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Reset          | Digital/Binary         | There are two resets: asynchronous reset (arst_i) and synchronous halt (halt_i). Both resets can be driven by user logic outside of the IP, GPIO, or other primitives. Asynchronous reset resets the LMMI logic of the SEDC hard block and immediately clears all the registers in the SEDC state machine, SEDC LMMI host, and SEDC output capture modules to 0. Halt gracefully aborts an on-going SEDC Controller IP operation from any state.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Control        | Digital/Binary         | Input signals (sedc_run_i, continuous_i, auto_correct_i, and resume_scan_i) to control IP operations such as:  Continuous mode Executes SEDC scans continuously, one after another.  Error correction and resume scan Performs error correction on correctable error. Resumes scan upon error detection. Configures SEC as either automatic or manual. IP handles LMMI communications with the SEDC hard block, eliminating need for user involvement.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Monitor        | Digital/Binary         | Output signals (status_update_o, bit_loc_o, frm_loc_o, rgn_loc_o, clk_div_o, crc_err_o, sing_err_o, mult_err_o, err_o, sedc_error_o, sedc_done_o, and sedc_busy_o) to monitor the IP such as:  • Error status and location  • Reports error status and location information. IP retrieves information from the SEDC hard block through LMMI, eliminating the need for user involvement.  • Error statuses include 1-bit error (correctable), multi-bit error (uncorrectable), and CRC error.  • Error locations include bit location, frame location, and region location.  • Clock divider value  • Reports the clock divider value. IP retrieves information from the SEDC hard block through LMMI, eliminating the need for user involvement.  • SEDC scan status  • Reports the status of the current SEDC can (busy or done). |  |  |  |  |

# 3. IP Parameter Description

The configurable attributes of the SEDC Controller IP are shown in the following table. You can configure the IP by setting the attributes accordingly in the IP Catalog Module/IP wizard of the Lattice Radiant software.

Wherever applicable, default values are in bold.

**Table 3.1. SEDC Controller IP Attributes**

| Attribute                                                           | Selectable Values                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration                                                       | ·                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| SEDC Mode  Continuous Mode, One-Shot Mode, Port-Driven Dynamic Mode |                                                                                                            | Specifies the SEDC mode and determines whether the SEDC mode is static (Continuous Mode or One-Shot Mode) or dynamic (Port-Driven Dynamic Mode, switches between static modes).  When Port-Driven Dynamic Mode is selected, an additional user interface port continuous_i is exposed.                                                                                                                                       |  |  |  |  |

| Error Correction Mode                                               | Auto-Correction Mode, No Auto-Correction Mode, Port-Driven Dynamic Mode                                    | Determines whether the error correction mode is automatic (Auto-Correction Mode), manual (No Auto-Correction Mode), or dynamically switches between the two (Port-Driven Dynamic Mode).  When No Auto-Correction Mode is selected, an additional user port interface resume_scan_i is exposed.  When Port-Driven Dynamic Mode is selected, two additional user interface ports auto_correct_i and resume_scan_i are exposed. |  |  |  |  |

| Clock Divider                                                       | <b>2</b> –256                                                                                              | Specifies the clock divider value for the SEDC. The mapping of <i>Clock Divider</i> setting (N) to the hardware value reported in clk_div_o is N – 1. For example, when <i>Clock Divider</i> = 2, the clk_div_o readout is 1.                                                                                                                                                                                                |  |  |  |  |

| Disable Triple Modular Redundancy  Checked, <b>Unchecked</b>        |                                                                                                            | Specifies whether to disable the TMR on all registers (checked). For highest reliability, Lattice recommends this remain unchecked (TMR enabled).                                                                                                                                                                                                                                                                            |  |  |  |  |

| Clock Frequency (MHz) 0.0000000—<br><b>80.0000000</b>               |                                                                                                            | Specifies the clock frequency for port clk_i. For highest reliability, Lattice recommends rounding off to a conservative number.                                                                                                                                                                                                                                                                                             |  |  |  |  |

| <b>CRAM Error Injection in Si</b>                                   | mulation                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Types of Error Injection                                            | No CRAM Error, Simulate Correctable CRAM Error, Simulate Uncorrectable CRAM Error, Simulate CRC CRAM Error | Determines whether to enable the fake error injection capability in simulation, and if so, the type of error to inject.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| CRAM Error Location in Si                                           | mulation                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Bit Error Location <b>0</b> –1023                                   |                                                                                                            | Specifies the data shift register (DSR) bit location of the fake error injected.  Applicable when <i>Types of Error Injection</i> = Simulate Correctable CRAM Error.                                                                                                                                                                                                                                                         |  |  |  |  |

| Frame Error Location <b>0</b> –16383                                |                                                                                                            | Specifies the address shift register (ASR) bit location of the fake error injected.  Applicable when <i>Types of Error Injection</i> = Simulate Correctable CRAM Error or Simulate Uncorrectable CRAM Error.                                                                                                                                                                                                                 |  |  |  |  |

| Region Error Location                                               | 0-31                                                                                                       | Specifies the region location of the fake error injected.  Applicable when <i>Types of Error Injection</i> = Simulate Correctable CRAM Error or Simulate Uncorrectable CRAM Error.                                                                                                                                                                                                                                           |  |  |  |  |

# 4. Signal Description

This section describes the SEDC Controller IP ports.

### 4.1. Clock Interface

#### Table 4.1. Clock Port

| Port  | Туре  | Description                                                                                                                       |  |  |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| clk_i | Input | Input clock that drives all soft logic registers and the LMMICLK of the SEDC hard block.  Clock frequency must not exceed 80 MHz. |  |  |

#### 4.2. Reset Interface

#### **Table 4.2. Reset Ports**

| Port   | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| arst_i | Input | Asynchronous reset to reset all soft logic registers and the LMMI logic of the SEDC hard block when asserted high. This signal must be asserted high and can only be released low 60 µs after the device is configured and has entered user mode. Subsequent assertions require a minimum reset assertion duration of 84 ns. The SEDC state machine module proceeds to initialize the SEDC hard block at the immediate positive clock edge after the de-assertion of this signal. |

| halt_i | Input | Reset to abort the entire IP operation from any state when asserted high.  It is synchronous to clk_i. The minimum duration of assertion is one full clock cycle. The SEDC state machine module returns to the initialization state when the SEDC hard block is no longer busy. This occurs at the immediate positive clock edge after de-assertion of this signal.                                                                                                               |

#### 4.3. Control Interface

Table 4.3. Control Ports

| Port       | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| sedc_run_i | Input | Signal to start and run the SEDC scan. This signal must remain high until sedc_busy_o is asserted high. Following this, it can continue to remain high or be de-asserted any time.  Requirements in each SEDC Mode:                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|            |       | <ul> <li>Continuous Mode – This signal may remain high from one SEDC scan to the next, as long as you want to run the SEDC scans continuously.</li> <li>One-Shot Mode – This signal must be re-asserted high after the assertion of sedc_done_o to start a new SEDC scan.</li> <li>Port-Driven Dynamic Mode – This signal must be re-asserted high after the assertion of sedc_done_o if continuous_i is low to start a new SEDC scan. If continuous_i is high from one SEDC scan to the next, this signal must also remain high to run the SEDC scans continuously.</li> </ul> |  |  |  |

|            |       | Requirements in each Error Correction Mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|            |       | <ul> <li>Auto-Correction Mode – This signal can be high or low when an error<br/>occurs because it does not impact error correction and/or resumption of<br/>the current SEDC scan.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|            |       | <ul> <li>No Auto-Correction Mode – This signal must be re-asserted or remain<br/>high together with the assertion of resume_scan_i when an error occurs<br/>to perform error correction and/or resume the current SEDC scan.</li> </ul>                                                                                                                                                                                                                                                                                                                                         |  |  |  |

FPGA-IPUG-02290-1.2

| Port           | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |       | Port-Driven Dynamic Mode – This signal must be re-asserted or remain high together with the assertion of resume_scan_i if auto_correct_i is low when an error occurs to perform error correction and/or resume the current SEDC scan. If auto_correct_i is high when an error occurs, this signal can be high or low because it does not impact error correction and/or resumption of the current SEDC scan.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| continuous_i   | Input | Signal to run the SEDC scan continuously.  1 – Continuous mode  0 – One-shot mode  This signal must remain high together with sedc_run_i from one SEDC scan to the next to run the SEDC scans continuously.  Exposure of this signal depends on the configuration of SEDC Mode:  Continuous Mode – This signal is tied off to 1'b1 internally and not exposed as a user interface port.  One-Shot Mode – This signal is tied off to 1'b0 internally and not exposed as a user interface port.  Port-Driven Dynamic Mode – This signal is exposed as a user interface port.                                                                                                                                                                                                                                                         |

| auto_correct_i | Input | Signal to perform automatic error correction and/or resume the SEDC scan when an error occurs.  1 – Auto-Correction Mode is ON  0 – Auto-Correction Mode is OFF  This signal must remain high throughout the SEDC scan (if one-shot) or consecutive SEDC scans (if continuous) to ensure smooth automatic error correction and/or resumption of the SEDC scan when an error occurs, while also providing the benefit of minimal latency.  Exposure of this signal depends on the configuration of Error Correction Mode:  Auto-Correction Mode – This signal is tied off to 1'b1 internally and not exposed as a user interface port.  No Auto-Correction Mode – This signal is tied off to 1'b0 internally and not exposed as a user interface port.  Port-Driven Dynamic Mode – This signal is exposed as a user interface port. |

| resume_scan_i  | Input | Signal to perform error correction and/or resume the SEDC scan manually when a 1-bit error occurs.  If Auto-Correction Mode is OFF, whenever 1-bit error is detected, this signal must be asserted/remain high together with sedc_run_i after the assertion of status_update_o.  Exposure of this signal depends on the configuration of Error Correction Mode:  • Auto-Correction Mode – This signal is tied off to 1'b0 internally and not exposed as a user interface port.  • No Auto-Correction Mode – This signal is exposed as a user interface port.  • Port-Driven Dynamic Mode – This signal is exposed as a user interface port.                                                                                                                                                                                        |

# 4.4. Monitor Interface

#### **Table 4.4. Monitor Ports**

| Port               | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| status_update_o    | Output | Signal to indicate that the status and configuration register outputs are ready to be read, which includes crc_err_o, mult_err_o, sing_err_o, err_o, bit_loc_o, frm_loc_o, and rgn_loc_o.  This signal is asserted high momentarily for one clock cycle only. Consume the error statuses and locations immediately when status_update_o is asserted high. Otherwise, the error statuses and locations may become outdated or invalid. |  |  |

| bit_loc_o[9:0]     | Output | Signal to indicate the DSR bit location of the last 1-bit error.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| frm_loc_o[13:0]    | Output | Signal to indicate the ASR frame location of the last 1-bit/multi-bit error.                                                                                                                                                                                                                                                                                                                                                          |  |  |

| rgn_loc_o[4:0]     | Output | Signal to indicate the region location of the last 1-bit/multi-bit error.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| clk_div_o[7:0]     | Output | Signal to indicate the clock divider value.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| crc_err_o          | Output | Signal to indicate the occurrence of a CRC error. Asserted high when CRC error occurs.                                                                                                                                                                                                                                                                                                                                                |  |  |

| mult_err_o         | Output | Signal to indicate the occurrence of a multi-bit error. Asserted high when multi-bit error occurs.                                                                                                                                                                                                                                                                                                                                    |  |  |

| sing_err_o         | Output | Signal to indicate the occurrence of a 1-bit error. Asserted high when 1-bit error occurs.                                                                                                                                                                                                                                                                                                                                            |  |  |

| err_o Output       |        | Signal to indicate the occurrence of an error. Asserted high when an error occurs.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| sedc_error_o       | Output | Signal to indicate whether SEDC has detected an error. Asserted high when an error occurs.                                                                                                                                                                                                                                                                                                                                            |  |  |

| sedc_done_o        | Output | Signal to indicate whether the SEDC scan has finished. This signal is asserted high momentarily for one clock cycle only.                                                                                                                                                                                                                                                                                                             |  |  |

| sedc_busy_o Output |        | Signal to indicate whether the SEDC scan is running.  1 – SEDC scan is running.  0 – SEDC can is idle.                                                                                                                                                                                                                                                                                                                                |  |  |

# Designing with the IP

This section provides information on how to generate the IP Core using the Lattice Radiant software and how to run simulation and synthesis. For more details on the Lattice Radiant software, refer to the Lattice Radiant Software User Guide.

### 5.1. Generating and Instantiating the IP

You can use the Lattice Radiant software to generate IP modules and integrate them into the device architecture. The steps below describe how to generate the SEDC Controller IP in the Lattice Radiant software.

To generate the SEDC Controller IP:

- 1. Create a new Lattice Radiant software project or open an existing project.

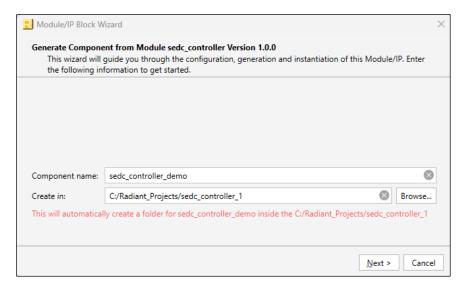

- 2. In the IP Catalog tab, double-click SEDC Controller under IP on Local > Architecture\_Modules category. The Module/IP Block Wizard opens as shown in Figure 5.1. Enter values in the Component name and the Create in fields and click Next.

Figure 5.1. Module/IP Block Wizard

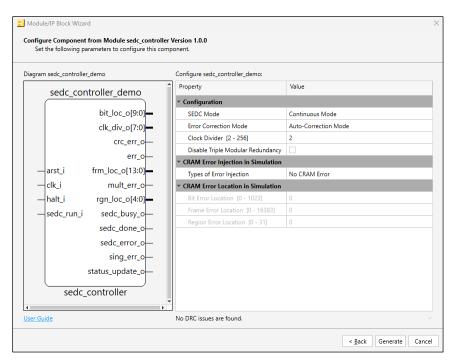

3. In the next **Module/IP Block Wizard** window, customize the selected SEDC Controller IP using drop-down lists and check boxes. Figure 5.2 shows an example configuration of the SEDC Controller IP. For details on the configuration options, refer to the IP Parameter Description section.

Figure 5.2. IP Configuration

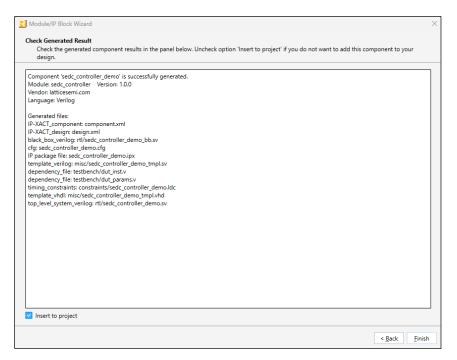

4. Click **Generate**. The **Check Generated Result** dialog box opens, showing design block messages and results as shown in Figure 5.3.

Figure 5.3. Check Generated Result

5. Click **Finish**. All the generated files are placed under the directory paths in the **Create in** and the **Component name** fields shown in Figure 5.1.

#### 5.1.1. Generated Files and File Structure