# **Lattice CertusPro-NX PROFINET Stack**

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                                                              | 3  |

|---------------------------------------------------------------------------------------|----|

| Abbreviations in This Document                                                        | 6  |

| 1. Introduction                                                                       | 7  |

| 1.1. Quick Facts                                                                      | 7  |

| 1.2. Features                                                                         | 8  |

| 1.3. PROFINET Overview                                                                | 8  |

| 1.3.1. PROFINET Real-Time Communication and Cyclic Data Exchange                      | 8  |

| 1.3.2. Establishing a Real-Time Connection                                            | 8  |

| 1.3.3. Cyclic Exchange of Real-Time Data                                              | 9  |

| 2. Directory Structure and Files                                                      | 10 |

| 3. Functional Description                                                             | 12 |

| 3.1. PROFINET Architecture Overview                                                   | 12 |

| 3.2. PROFINET System Components                                                       | 13 |

| 3.2.1. Soft IP Data Transmission Blocks                                               | 13 |

| 3.2.2. Soft IP Control Blocks                                                         | 13 |

| 3.2.3. Hardware Components                                                            |    |

| 3.3. PROFINET Stack System Flow                                                       | 14 |

| 3.3.1. PROFINET System Memory Map                                                     | 15 |

| 4. PROFINET Reference Design Parameter Description                                    | 16 |

| 4.1. Scatter Gather DMA IP for PROFINET Stack                                         | 16 |

| 4.2. ADIN and TSE MAC Integrated Design                                               | 17 |

| 5. PROFINET Application Description                                                   | 18 |

| 5.1. PROFINET Reference Design Build Configuration                                    | 18 |

| 5.2. PROFINET Software Stack Functional Description                                   | 18 |

| 5.2.1. IwIP Stack Functions                                                           |    |

| 5.2.2. ADIN1200 and ADIN1300 Driver API Functions                                     | 18 |

| 5.2.3. SGDMA Driver API functions                                                     | 19 |

| 5.2.4. UDP Stack Functions                                                            | 19 |

| 5.2.5. PROFINET Stack Basic Functions                                                 | 20 |

| 5.3. Communication Between PLC and PROFINET I/O System                                | 21 |

| 5.3.1. Messages from PLC to ADI MCB System                                            | 21 |

| 5.3.2. P-DCP                                                                          | 21 |

| 5.3.3. Link Layer Discovery Protocol (LLDP)                                           | 22 |

| 5.3.4. PNIO-CM                                                                        |    |

| 5.3.5. PNIO-PS                                                                        | 22 |

| 5.3.6. PNIO                                                                           | 22 |

| 6. Running the Reference Design                                                       | 23 |

| 6.1. Compiling the Reference Design C Code in the Propel Software                     | 23 |

| 6.2. Generating the Bitstream File in the Lattice Radiant™ Software                   |    |

| 7. Testing the Application with PROFINET Demo Setup                                   | 24 |

| 7.1. Demo Overview                                                                    |    |

| 7.1.1. Hardware Components                                                            | 24 |

| 7.1.2. Software Components                                                            | 28 |

| 7.2. Evaluation Board Configuration with Lattice Radiant Programmer                   | 30 |

| 7.3. Scanning the Network for Accessible PROFINET Devices with Siemens PRONETA        |    |

| 7.4. Configuring the PROFINET Device Names and IP Addresses with Siemens PRONETA      |    |

| 7.5. Quick Start with the Siemens TIA Sample Project and Programming the FPGA Device  |    |

| 7.6. Testing of basic PROFINET I/O Device Functions                                   |    |

| 7.6.1. Connection of PMOD Test Modules to the Lattice ADI Evaluation Board            |    |

| 7.6.2. Testing the Digital System Output (Flashing LED) on PMODO Peripheral Connector |    |

| 7.6.3. Testing of Digital User Outputs and Inputs on PMOD Peripheral Connectors       |    |

| 7.7. Capturing and Analyzing the PROFINET Cyclic Ethernet Data Transfers              |    |

|                                                                                       |    |

3

| 7.8. Setting Up a New Demo Project Using Siemens TIA                               | 38 |

|------------------------------------------------------------------------------------|----|

| 7.8.1. Creating a New Project                                                      |    |

| 7.8.2. Adding the Siemens PLC Device                                               | 38 |

| 7.8.3. Adding the GSDML Files to the Current Project                               | 38 |

| 7.8.4. Adding the Phoenix Contact I/O Device as Reference                          | 39 |

| 7.8.5. Adding the RT-Labs GSDML File and I/O Device                                | 39 |

| 7.8.6. Adding the I/O Module of the Phoenix Contact I/O Device Head Module         | 39 |

| 7.8.7. Adding the I/O Module to the RT-Labs I/O Device Head Module                 | 39 |

| 7.8.8. Checking the Current Device Names and IP Addresses                          | 40 |

| 7.8.9. Assigning the I/O Devices to the Siemens PLC Device                         |    |

| 7.8.10. PLC and I/O Device Configuration                                           | 40 |

| 7.8.11. Checking the Device I/O Addressing within the PLC System Memory            | 40 |

| 7.8.12. Setting Up the PLC Tags to Enable Symbolic Addressing of the Process Image | 42 |

| 7.8.13. Setting Up the PLC Program Block in Main [OB1]                             | 43 |

| 7.8.14. Compiling and Loading the PROFINET System Configuration                    | 45 |

| 7.8.15. Checking the System Status Online                                          |    |

| 7.9. I/O Cycle Timing Constraints                                                  | 45 |

| 8. Resource Utilization                                                            | 46 |

| 9. Debugging                                                                       | 47 |

| 9.1. Packet Inspection                                                             |    |

| References                                                                         |    |

| Technical Support Assistance                                                       | 51 |

| Revision History                                                                   | 52 |

# **Figures**

| Figure 2.1. PROFINET Stack on FreeRTOS Directory Structure                           |    |

|--------------------------------------------------------------------------------------|----|

| Figure 2.2. ADINI200 PHY Verilog File Location                                       |    |

| Figure 3.1. ADI MCB Evaluation Board                                                 |    |

| Figure 3.2. PROFINET Stack with ADIN PHY Solution Based on Lattice GSRD              | 13 |

| Figure 3.3. PROFINET System Flow Diagram                                             |    |

| Figure 3.4. ADI Motion Control Block                                                 |    |

| Figure 4.1. SGDMA Driver API Receive                                                 |    |

| Figure 4.2. SGDMA Driver API Transmit                                                |    |

| Figure 4.3. ADIN1200 Ports Located on the ADI MCB                                    |    |

| Figure 4.4. ADIN1300 Ports Located on the ADI MCB                                    |    |

| Figure 5.1. Build Configuration for PROFINET FreeRTOS Reference Design               |    |

| Figure 5.2. UDP Receive Stack                                                        |    |

| Figure 5.3. UDP Transmit Stack                                                       |    |

| Figure 6.1. PROFINET Build Artifact Location in Propel                               |    |

| Figure 7.1. PROFINET Demo Setup Overview<br>Figure 7.2. PROFINET Demo Hardware Setup |    |

| Figure 7.3. ADI CertusPro-NX Motion Control Evaluation Board                         |    |

| Figure 7.4. ADI CertusPro-NX Motion Control Block Diagram                            |    |

| Figure 7.5. DIGITAL I/O Setup for LED                                                |    |

| Figure 7.6. ISO Image for TIA Portal                                                 |    |

| Figure 7.7. Start Button to Install                                                  |    |

| Figure 7.8. Bit File Programming for ADI MCB                                         |    |

| Figure 7.9. Configuring Bit File Programming for ADI MCB                             |    |

| Figure 7.10. Demo PMOD Modules for LED I/O                                           |    |

| Figure 7.11. Testing Methods for Output                                              |    |

| Figure 7.12. Testing Methods for Input                                               |    |

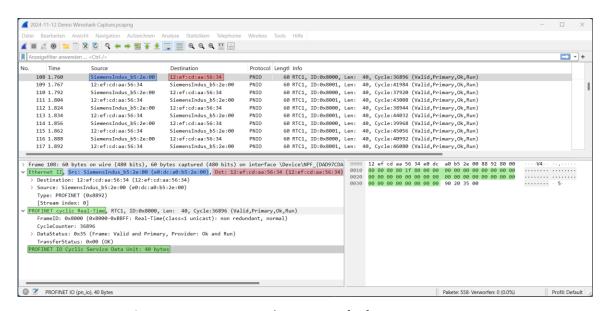

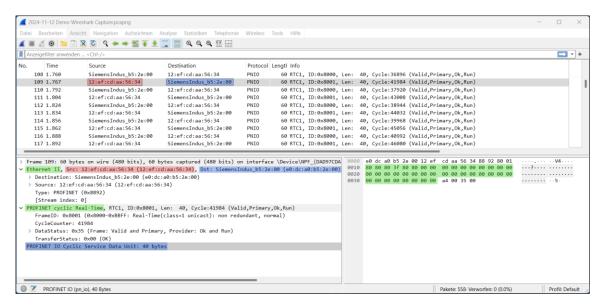

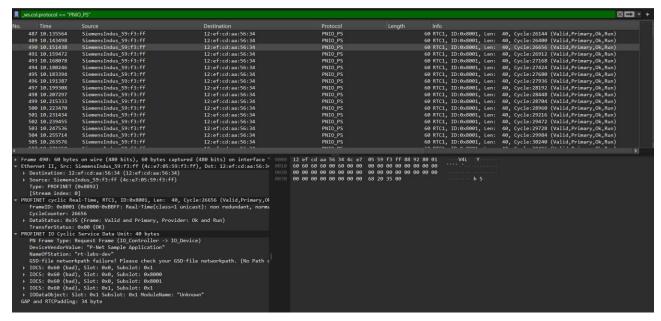

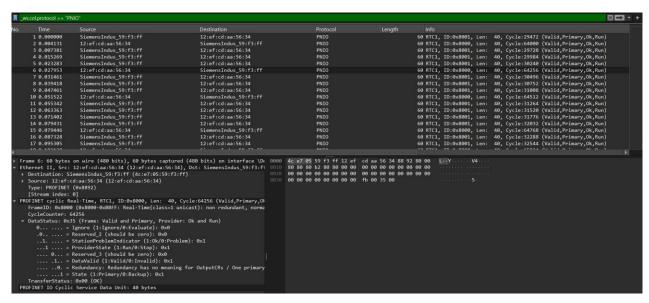

| Figure 7.13. PROFINET Cycle Data Transfer from PLC to ADI MCB                        | 37 |

| Figure 7.14. PROFINET Cycle Data Transfer from ADI MCB to PLC                        | 38 |

| Figure 7.15. Siemens TIA Portal PLC Tags Setup for Demo                              | 42 |

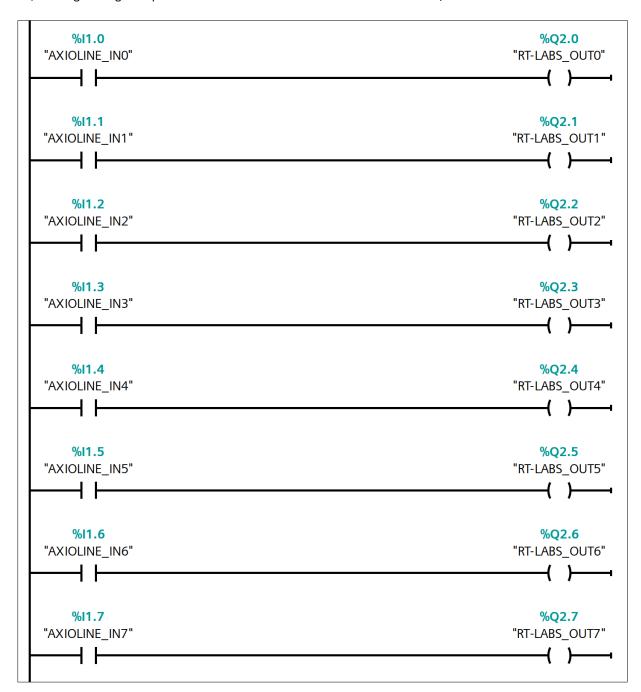

| Figure 7.16. Siemens TIA Portal Main Block Setup for Demo for Output                 | 43 |

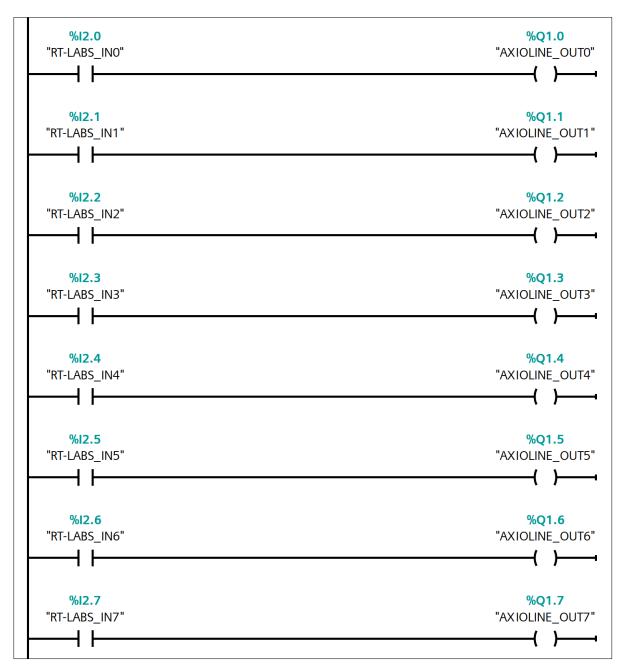

| Figure 7.17. Siemens TIA Portal Main Block Setup for Demo for Input                  | 44 |

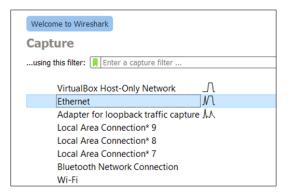

| Figure 9.1. Wireshark Tool: Ethernet Selection                                       |    |

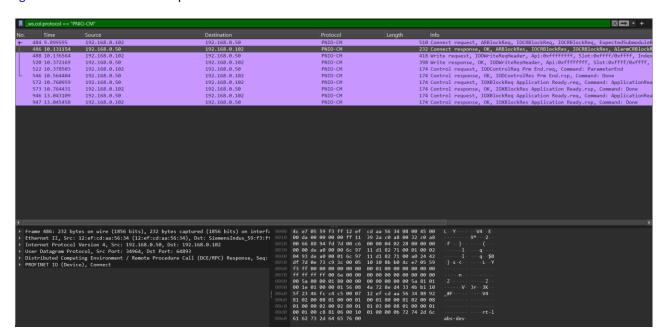

| Figure 9.2. Wireshark Tool Filter _ws.col.protocol == "PNIO"                         |    |

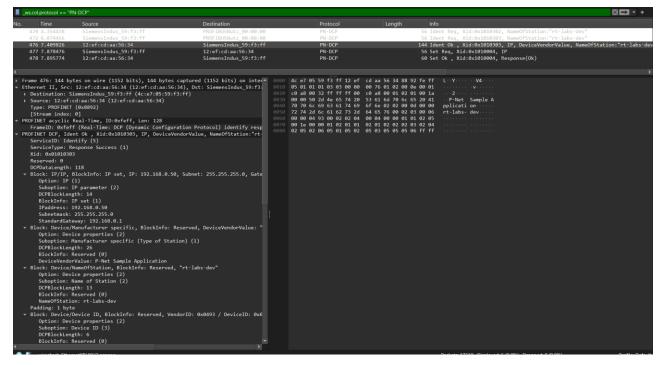

| Figure 9.3. Wireshark Tool Filter _ws.col.protocol == "PN-DCP"                       |    |

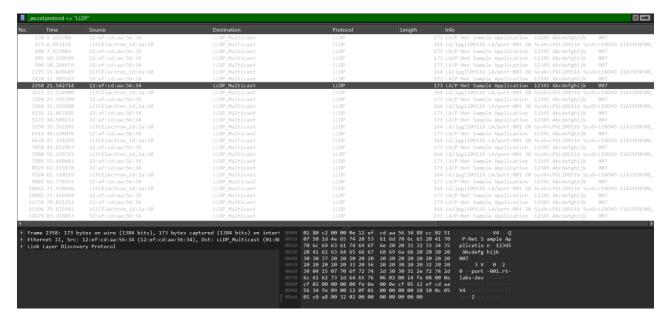

| Figure 9.4. Wireshark Tool Filter " _ws.col.protocol == "LLDP"                       |    |

| Figure 9.5. Wireshark Tool Filter "_ws.col.protocol == "PNIO-PS"                     |    |

| Figure 9.6. Wireshark Tool Filter " _ws.col.protocol == "PNIO-PS"                    | 49 |

|                                                                                      |    |

|                                                                                      |    |

|                                                                                      |    |

| Tables                                                                               |    |

|                                                                                      |    |

| Table 1.1. Summary of the Reference Design                                           |    |

| Table 2.1. ADIN1200 File List                                                        |    |

| Table 2.2. ADIN1300 File List                                                        |    |

| Table 3.1. PROFINET Stack Memory Map                                                 |    |

| Table 8.1. Main System Resource Utilization                                          |    |

| Table 8.2. PROFINET Total Resource Utilization                                       | 46 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                  |  |  |  |

|--------------|---------------------------------------------|--|--|--|

| AHBL         | Advanced High-performance Bus-Lite          |  |  |  |

| ADI          | Analog Devices                              |  |  |  |

| APB          | Advanced Peripheral Bus                     |  |  |  |

| API          | Application Programming Interface           |  |  |  |

| AXI          | Advanced Extensible Interface               |  |  |  |

| CPU          | Central Processing Unit                     |  |  |  |

| DCP          | Data Consistency Protocol                   |  |  |  |

| DMA          | Direct Memory Access                        |  |  |  |

| FIFO         | First-In-First-Out                          |  |  |  |

| FPGA         | Field Programmable Gate Array               |  |  |  |

| FreeRTOS     | Free Real Time Operating System             |  |  |  |

| GPIO         | General Purpose Input Output                |  |  |  |

| GSRD         | Golden Software Reference Design            |  |  |  |

| ICMP         | Internet Control Protocol Message           |  |  |  |

| IPK          | Lattice IP Package                          |  |  |  |

| ISR          | Interrupt Service Routines                  |  |  |  |

| LPDDR        | Low Power Double Data Rate Generation 4     |  |  |  |

| LPDDR4       | Low Power Double Data Rate Generation 4     |  |  |  |

| LwIP         | Light weight Internet Protocol              |  |  |  |

| MCB          | Motion Control Board                        |  |  |  |

| MPMC         | Multi-Port Memory Controller                |  |  |  |

| PHY          | Physical Network Interface                  |  |  |  |

| PLC          | Programmable Logic Controller               |  |  |  |

| PNIO         | PROFINET I/O                                |  |  |  |

| PNIO-CM      | PROFINET I/O Configuration Manager          |  |  |  |

| PNIO-PS      | PROFINET I/O Protocol Stack                 |  |  |  |

| PROFINET     | Process Field Network                       |  |  |  |

| QSPI         | Quad Serial Peripheral Interface            |  |  |  |

| RISC-V       | Reduced Instruction Set Computer-V          |  |  |  |

| RTL          | Register-Transfer Level                     |  |  |  |

| SGDMA        | Scatter-Gather Direct Memory Access         |  |  |  |

| TIA          | Totally Integrated Automation               |  |  |  |

| TSEMAC       | Tri-Speed Ethernet Media Access Controller  |  |  |  |

| UART         | Universal Asynchronous Receiver-Transmitter |  |  |  |

| UDP          | User Data gram Protocol                     |  |  |  |

### 1. Introduction

Process Field Network (PROFINET) is an industrial Ethernet standard that facilitates real-time data exchange between controllers such as PLCs and devices such as sensors and actuators for precise control in automation. It supports various network topologies and offers safety, energy management, and IT integration features. The PROFINET architecture is scalable and allows easy system expansion, making it ideal for diverse industrial applications.

Field-Programmable Gate Array (FPGA) devices enable PROFINET by providing the necessary hardware acceleration for real-time data processing. FPGA devices handle high-speed deterministic data exchanges to ensure minimal latency and precise timing. FPGA devices can be configured to implement various PROFINET protocols. Additionally, FPGAs can integrate with standard Ethernet controllers, supporting various network topologies and ensuring seamless communication between devices. The reconfigurable nature of FPGAs makes it easier to scale and adapt PROFINET systems to different industrial applications.

This reference design demonstrates an implementation of a PROFINET subsystem implemented on a Lattice CertusPro™-NX FPGA device.

### 1.1. Quick Facts

The reference design files are packaged together with the PROFINET reference design.

Table 1.1. Summary of the Reference Design

|                       | Target Devices             | LFCPNX-100                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General               | Source code format         | C Language                                                                                                                                                                                                                                                                                                                                             |  |  |

| Simulation            | Functional simulation      | Not performed                                                                                                                                                                                                                                                                                                                                          |  |  |

|                       | Timing simulation          | Not performed                                                                                                                                                                                                                                                                                                                                          |  |  |

|                       | Test bench                 | Not available                                                                                                                                                                                                                                                                                                                                          |  |  |

|                       | Test bench format          | Not available                                                                                                                                                                                                                                                                                                                                          |  |  |

|                       | Software tool and version  | FreeRTOS, Lattice Propel™ 2023.2, Lattice Propel Builder 2023.2                                                                                                                                                                                                                                                                                        |  |  |

| Software Requirements | IP version (if applicable) | <ul> <li>ADIN1200 MII (Available in the design as Verilog)</li> <li>ADIN1300 RGMII (Available in the design as Verilog)</li> <li>SGDMA 2.1.1</li> <li>TSE MAC 1.5.0</li> <li>AXI Interconnect 1.2.2</li> <li>RISCV 2.3.0</li> <li>AHBL Interconnect 1.2.0</li> <li>LPDDR4 2.1.0</li> <li>GPIO 1.6.2</li> <li>QSPI 1.1.1</li> <li>MPMC 1.0.0</li> </ul> |  |  |

| Hardwara Baguiramanta | Board                      | ADI Motion Control Board (MCB)                                                                                                                                                                                                                                                                                                                         |  |  |

| Hardware Requirements | Cable                      | Lattice Programming Cable, Cat 6 LAN Cable                                                                                                                                                                                                                                                                                                             |  |  |

### 1.2. Features

Key features of the PROFINET reference design include:

- PROFINET (RT-Labs p-net stack) functionality on ADI MCB with Lattice CertusPro-NX device GSRD

- Ethernet communication with ICMP packet response and reply

- Supports 100 Mbps Ethernet communication with an ADIN1200 module

For more information on the GSRD features, refer to the Golden System Reference Design Demo User Guide (FPGA-UG-02205).

For more information on the ADI MCB, refer to ADI MCB system.

For more information on the PROFINET p-net stack, refer to RT-Labs PROFINET Stack.

For more information on the ADIN1200 module, refer to ADIN1200.

### 1.3. PROFINET Overview

PROFINET is a modern industrial communication protocol designed to replace traditional fieldbus systems in factory automation. Fieldbuses have been crucial for industrial communication, but PROFINET, built on the IEEE 802.3 Ethernet standard, provides significant advantages such as higher data speeds, better scalability, and seamless integration with IT systems. By using Ethernet, PROFINET can leverage the familiar infrastructure while adding industrial-grade reliability and determinism for real-time applications.

In terms of protocols, PROFINET supports both standard IP-based communication (TCP/IP and UDP/IP) for non-time-critical data and a specific EtherType (0x8892) for real-time communication, which bypasses standard IP layers to achieve lower latency. This combination allows PROFINET to be highly flexible, supporting both general network traffic and high-performance real-time data exchange in the same network.

The adoption of PROFINET is widespread across industries such as automotive, manufacturing, process industries, and energy, due to its robust performance, flexibility, and compatibility with Industry 4.0 standards. The protocol has become a popular choice for industrial automation due to its support for complex, scalable systems while maintaining high-speed, reliable communication needed for modern industrial processes.

### 1.3.1. PROFINET Real-Time Communication and Cyclic Data Exchange

In PROFINET, real-time communication is essential for the deterministic behavior required in industrial automation, such as controlling machines and processes. To achieve this, PROFINET uses specialized mechanisms to set up real-time connections and handle cyclic data exchange with minimal delays.

#### 1.3.2. Establishing a Real-Time Connection

When a PROFINET system is initialized, the I/O Controller (typically a PLC or industrial PC) configures communication with the I/O devices (sensors and actuators) based on the application requirements. This process involves the following steps:

- Device Discovery and Assignment The I/O Controller scans the network for connected I/O devices. Each I/O

device has a unique Device Name and IP address assigned, which helps the controller to identify and communicate

with it.

- Communication Setup After identifying the devices, the I/O Controller configures the I/O devices by setting up

cyclic data exchange intervals. The communication parameters, such as update rates, priority, and real-time class,

are defined during this step.

- Real-Time Channel Creation PROFINET uses a specific EtherType (0x8892) to set up a real-time (RT) channel.

### 1.3.3. Cyclic Exchange of Real-Time Data

Once the connection is established, the cyclic data exchange begins. This process involves the continuous transmission of real-time process data between the I/O Controller and I/O devices at predefined intervals.

- Cyclic Data Frames PROFINET employs periodic data frames for sending and receiving real-time information. Each device process data (such as sensor readings or actuator commands) is exchanged within these frames.

- PROFINET RT Real-Time Class This class ensures that real-time communication takes place within the standard Ethernet structure by reducing the delays caused by IP layer processing. Cycle times typically range from 1 to 10 ms, making RT suitable for standard automation tasks

# 2. Directory Structure and Files

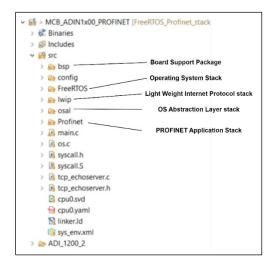

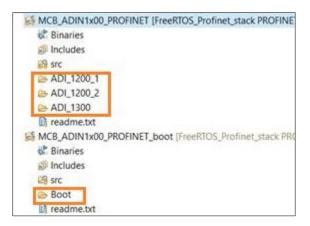

Figure 2.1 shows the directory structure.

Figure 2.1. PROFINET Stack on FreeRTOS Directory Structure

For the FPGA GSRD stack, refer to the Golden System Reference Design Demo User Guide (FPGA-UG-02205).

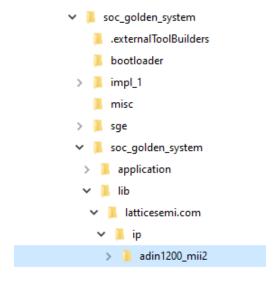

The ADIN1200 mii1, 1200\_mii2 or ADIN1300 IP is available in the design release folder below. Except for the IP mentioned above, the rest are similar with the GSRD design published for 2023.2.

Figure 2.2. ADINI200 PHY Verilog File Location

Apart from the GSRD for each different ADIN connector, there are different IP supporting it. Table 2.1 shows the list of files included in the reference design package for ADIN1200.

Table 2.1. ADIN1200 File List

| Tubic 2.1. Adiri 200 Tile List |                                                                                                    |  |

|--------------------------------|----------------------------------------------------------------------------------------------------|--|

| Attribute                      | Description                                                                                        |  |

| adin1200_mii1_inst.ipx         | This file contains the information on the files associated to the generated IP for ETHERCAT port 1 |  |

| adin1200_mii2_inst.ipx         | This file contains the information on the files associated to the generated IP for ETHERCAT port 2 |  |

| adin1200_mii1.cfg              | This file contains the parameter values used in IP configuration for ETTHERCAT port 1              |  |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-RD-02303-1.0

| Attribute                                                | Description                                                                                  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| adin1200_mii2.cfg                                        | This file contains the parameter values used in IP configuration for ETTHERCAT port 2        |  |  |

| component.xml                                            | Contains the ipxact:component information of the IP.                                         |  |  |

| design.xml                                               | Documents the configuration parameters of the IP in IP-XACT 2014 format.                     |  |  |

| rtl adin1200_mii1.v                                      | This file provides an example RTL top file that instantiates the module. For ETHERCAT port 1 |  |  |

| rtl/adin1200_mii2.v                                      | This file provides an example RTL top file that instantiates the module. For ETHERCAT port 2 |  |  |

| rtl/adin1200_mii1_bb.v                                   | This file provides the synthesis closed box for ETHERCAT port 1                              |  |  |

| rtl/adin1200_mii2_bb.v                                   | This file provides the synthesis closed box for ETHERCAT port 2                              |  |  |

| misc/adin1200_mii1_tmpl.v<br>misc/adin1200_mii1_tmpl.vhd | These files provide instance templates for ETHERCAT port 1                                   |  |  |

| misc/adin1200_mii2_tmpl.v<br>misc/adin1200_mii2_tmpl.vhd | These files provide instance templates for ETHERCAT port 2                                   |  |  |

Table 2.2 shows the list of files included in the reference design package for ADIN1300.

### Table 2.2. ADIN1300 File List

| Attribute                                              | Description                                                                                   |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| adin1300_mii_inst.ipx                                  | This file contains the information on the files associated to the generated IP.               |  |  |

| adin1300_mii.cfg                                       | This file contains the parameter values used in IP configuration.                             |  |  |

| component.xml                                          | Contains the ipxact:component information of the IP.                                          |  |  |

| design.xml                                             | Documents the configuration parameters of the IP in IP-XACT 2014 format.                      |  |  |

| rtl adin1300_mii.v                                     | This file provides an example RTL top file that instantiates the module. For ETHERCAT port 1. |  |  |

| rtl/adin1300_mii_bb.v                                  | This file provides the synthesis closed box for ETHERCAT port 1.                              |  |  |

| misc/adin1300_mii_tmpl.v<br>misc/adin1300_mii_tmpl.vhd | These files provide instance templates for ETHERCAT port 1.                                   |  |  |

## 3. Functional Description

### 3.1. PROFINET Architecture Overview

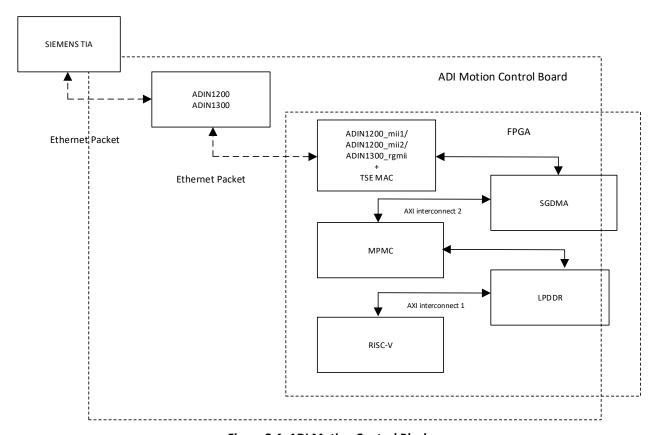

PROFINET is an industrial Ethernet standard used for communication between automation devices. The FPGA design to demonstrate PROFINET is based on the Lattice Golden System Reference Design with the inclusion of an ADIN1200 Soft IP wrapper, which is ADIN1200\_mii2, from the Analog Devices to communicate with the external ADIN1200 PHY module.

The ADI MCB board has two other PHY modules available for PROFINET: *ADIN1200* and *ADIN1300*. However, in this document, the reference design use case focuses on the ADIN1200 PHY module. Similar configuration methods discussed in this document can be directly applied to the other two interfaces using its respective wrapper design ADIN1200\_mii1 and ADIN1300\_rgmii. The specific configuration methods of these interfaces are further explained in the ADIN and TSE MAC Integrated Design section. The choice of the interface is for purpose of demonstration only. The other interface designs provided can be setup similarly based its corresponding requirements and dependencies.

The PROFINET software stack runs on FreeRTOS executed using a soft RISC-V core. Lattice developed BSP drivers facilitate communication between the hardware elements on the FPGA and FreeRTOS software. During boot up, these drivers initialize and configure FPGA peripherals to establish effective coordination with the RISC-V processor. For details on the boot flow, refer to the Golden System Reference Design Demo User Guide (FPGA-UG-02205).

The ADIN1200\_mii2 and ADIN1200\_mii1 wrappers allow PROFINET to perform communication over Lattice Triple Speed Ethernet (TSE) MAC Soft IP with the ADIN1200 PHY module. This applies to the ADIN1300 and ADIN1300 PHY module as well.

The SGDMA IP transfers data between the system LPDDR4 memory and the ADIN1200 TSE interface.

The PROFINET software stack execution in this reference design is built on top of the lwIP (lightweight IP) stack. The lwIP Stack is an open-source TCP/IP stack designed for embedded systems, focusing on reducing memory and processing requirements. The lwIP stack sends and retrieves network data using the SGDMA IP firmware API and diverts all PROFINET related protocol packets to the PROFINET software stack.

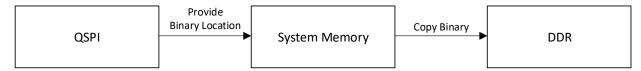

The QSPI controller is required to copy the PROFINET software stack binary from QSPI flash to the LPPDR4 memory where the software stack is executed from. System memory is used for bootloader operations.

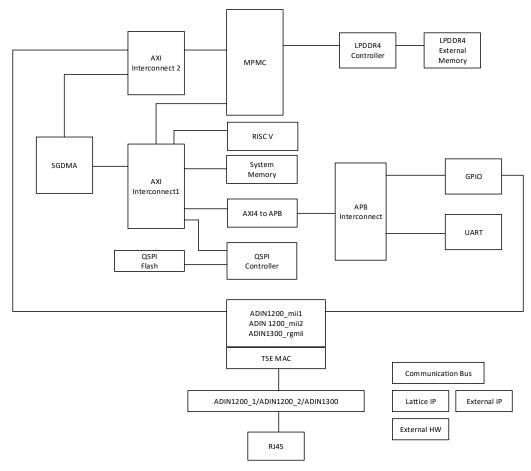

Figure 3.2 shows the FPGA design used to run the PROFINET software stack on an LFCPNX-100 device with an ADIN IP variant connected to the ADIN PHY module.

Figure 3.1. ADI MCB Evaluation Board

Figure 3.2. PROFINET Stack with ADIN PHY Solution Based on Lattice GSRD

### 3.2. PROFINET System Components

The GSRD architecture includes the following IP blocks and hardware connections in the PROFINET design.

### 3.2.1. Soft IP Data Transmission Blocks

- AXI Interconnect 2 Manages the communication between different IP blocks within the system.

- APB Interconnect Facilitates communication between the Advanced Peripheral Bus (APB) and other system components.

- MPMC Controls access to multiple memory ports.

- AXI4 to Memory Map Bridge Converts AXI4 protocol transactions to memory-mapped transactions.

### 3.2.2. Soft IP Control Blocks

- SGDMA Manages data transfer between memory and peripherals.

- RISCV V CPU register access for system configuration and control.

- LPDDR4 Controller Manages the interface and communication with LPDDR4 memory.

- GPIO Interfaces for general-purpose digital signals.

- UART Serial communication interface.

- ADIN1200\_mii1/ADIN1200\_mii2/ ADIN1300\_rgmii Non-Lattice Ethernet physical layer transceiver for network connectivity.

- TSE MAC Manages Ethernet data transmission and reception.

- System Memory Stores the boot firmware run-time memory

### 3.2.3. Hardware Components

- QSPI Flash Provides non-volatile storage for the system.

- LPDDR4 Memory Main External Memory

- ADIN1200 PHY/ADIN 1300 PHY module Ethernet communication device

### 3.3. PROFINET Stack System Flow

This section describes the boot process and Ethernet data flow from an external source (Siemens TIA).

The PROFINET software binary is stored in the external SPI flash. During boot, the boot loader copies the instruction code from external flash to LPDDR. Boot loader process sets the ISR function pointer to a pre-determined LPDDR4 memory address through the memory controller.

Figure 3.3. PROFINET System Flow Diagram

The SGDMA IP transfers incoming AXI streams from the TSE MAC IP to the LPDDR4 through AXI interconnect2 as shown in Figure 3.4. When data transfer is complete for an Ethernet packet transaction, SGDMA sets the transaction complete bit within the Buffer Descriptor block located in the LPDDR4 memory.

The MPMC IP arbitrates between multiple sources to route data to the LPDDR4 memory controller.

The PROFINET software stack running on the RISC-V module periodically polls the SGDMA buffer through AXI interconnect1 to determine if there is a network packet to be processed.

Figure 3.4. ADI Motion Control Block

### 3.3.1. PROFINET System Memory Map

The PROFINET system is based on the Lattice GSRD implementation. Table 3.1 shows the memory location of each of the IP blocks accessible by the OS.

**Table 3.1. PROFINET Stack Memory Map**

| Base Address | End Address | Range (Bytes) | Range<br>(Bytes in hex) | Size (KB) | Block                |

|--------------|-------------|---------------|-------------------------|-----------|----------------------|

| 00300000     | 0037FFFF    | 512000        | 80000                   | 512       | SPI FLASH CONTROLLER |

| 00000000     | 0003FFFF    | 256000        | 40000                   | 256       | CPU Data Ram         |

| 10000000     | 10000FFF    | 4096          | 1000                    | 4         | GPIO                 |

| 10001000     | 10004FFF    | 16384         | 4000                    | 16        | TSE MAC              |

| 10090000     | 10090FFF    | 4096          | 1000                    | 4         | UART                 |

| 10091000     | 10091FFF    | 4096          | 1000                    | 4         | GPIO RST IRQ         |

| 10092000     | 10092FFF    | 4096          | 1000                    | 4         | LPDDR4 APB           |

| 10093000     | 10093FFF    | 4096          | 1000                    | 4         | SGDMA                |

| 1009B000     | 1009BFFF    | 4096          | 1000                    | 4         | FPGA CONFIG APB      |

| 10110000     | 5010FFFF    | 1073741824    | 40000000                | 1048576   | LPDDR4 AXI           |

| F2000000     | F20FFFFF    | 1048576       | 100000                  | 1024      | CLINT (CPU)          |

| FC000000     | FC3FFFFF    | 4194304       | 400000                  | 4096      | PLIC (CPU)           |

| F0000400     | FFFFFFF     | 262144000     | FA00000                 | 256000    | RESERVED (CPU)       |

# 4. PROFINET Reference Design Parameter Description

This section describes the IP configuration changes and software components added to the Lattice GSRD to enable the PROFINET software stack. Using GSRD as the base design, the configuration changes for SGDMA IP, such as buffer depth, are necessary for system performance optimization. The TSE MAC and PHY are also changed to support interfacing with the ADIN1200 PHY module.

Further information on PROFINET software stack is found in RT-Labs PROFINET Stack. The subsequent sections in the document describe in detail the changes made to the GSRD.

### 4.1. Scatter Gather DMA IP for PROFINET Stack

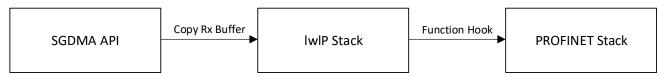

Ethernet communication for PROFINET stack requires the SGDMA IP to move data from TSE MAC to and from LPDDR4 through AXI Interconnect2, as shown in Figure 4.1. The FIFO depth of the SGDMA IP block is configured to be 4096 bytes. The PROFINET stack data processing utilizes IwIP stack as the network driver for FreeRTOS.

The IwIP stack configures the SGDMA IP parameters upon power up through the SGDMA driver API. The IwIP stack also allocates in LPDDR4 memory, transmit and receive buffers, as well as buffer descriptors for SGDMA operations. Once configuration for SGDMA operation has completed, the IwIP stack continuously polls data from the SGDMA buffer descriptor field on LPDDR4 to determine the readiness of receive or transmit data. When either receive or transmit data is available for transfer, the IwIP stack retrieves the Buffer Descriptor Address Pointer from LPDDR4, which identifies where the buffered data are located.

When receiving packet from TSE MAC, the transfer operation from SDGMA to LPDDR4 is initiated by IwIP stack (see the *Single Buffer Descriptor per Request* section of the SGDMA Controller IP Core User Guide (FPGA-IPUG-02131) document) by triggering the SGDMA streaming request. Once the data streaming is completed, the Descriptor Status Complete bit in the Buffer Descriptor is set to 1 (Bit 31 in the Buffer Descriptor, in the *S2MM\_STATUS* (*Offset 0x0C*) section, of the SGDMA Controller IP Core User Guide (FPGA-IPUG-02131)). The IwIP stack copies the data from the Buffer Descriptor and push it upstream to the PROFINET stack for processing.

Figure 4.1. SGDMA Driver API Receive

When transmitting packet to TSE MAC, the lwIP stack copies the data from the PROFINET stack to the transmit buffer through a callback function. The transfer operation to SDGMA from LPDDR4 is initiated by lwIP stack (see the *Single Buffer Descriptor per Request* section of the SGDMA Controller IP Core User Guide (FPGA-IPUG-02131) document) by triggering the SGDMA streaming request. The SGDMA driver API streams the data out to ADIN1200 mii2 directly.

Figure 4.2. SGDMA Driver API Transmit

For more details, refer to the SGDMA Controller IP Core User Guide (FPGA-IPUG-02131).

### 4.2. ADIN and TSE MAC Integrated Design

The ADI Motion Control Board (MCB) includes three ports with two ADIN1200 PHY module and a single ADIN1300 PHY module. The ports are ADIN1200 for port 1, ADIN1200 for port 2, and ADIN1300 port. The ADIN1200 ports are labelled as ETHERCAT-1 and ETHERCAT-2 ports on the board as shown in Figure 4.3 and ADIN1300 port is shown as Ethernet port in Figure 4.4. Depending on which ADIN1200 port is selected, the corresponding FPGA bit stream file and software configuration binary to be used is described in the PROFINET Application Description section. In this reference design, the ADIN1200 port 2 is used.

Figure 4.3. ADIN1200 Ports Located on the ADI MCB

Figure 4.4. ADIN1300 Ports Located on the ADI MCB

The ADIN1200 port selection on the ADI MCB board is configured in the GPIO setting. Depending on which port is chosen, the FreeRTOS BSP driver function is used to configure GPIO RST IRQ Address offset 7 for ADIN1200 port 1 (ETHERCAT-1) and GPIO RST IRQ Address offset 6 for ADIN1200 port 2 (ETHERCAT-2) accordingly.

For ADIN1300 to work on PROFINET some changes are required on the FreeRTOS:

- Change the PHY Register Control bit 9 to 0 to disable 1 Gbps advertising

- Change the PHY Register for Auto Negotiation to value 0x1e1

- Configure GPIO RST IRQ Address offset to 1 upon power up

The lwIP stack configures the IEEE 802.3 Clause 22 registers in the ADIN1200 PHY module and ADIN1300 PHY module through the individual interface driver APIs. The designation of these registers is found in the related documentation for the individual PHY modules

For more details on the ADIN1200 module, refer to the ADIN1200 page.

For more details on the ADIN1300 module, refer to the ADIN1300 page.

For more information on the ADI MCB, refer to the ADI MCB system page.

For more information on the TSEMAC IP, refer to the Tri-Speed Ethernet MAC IP User Guide (FPGA-IPUG-02084).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 5. PROFINET Application Description

### 5.1. PROFINET Reference Design Build Configuration

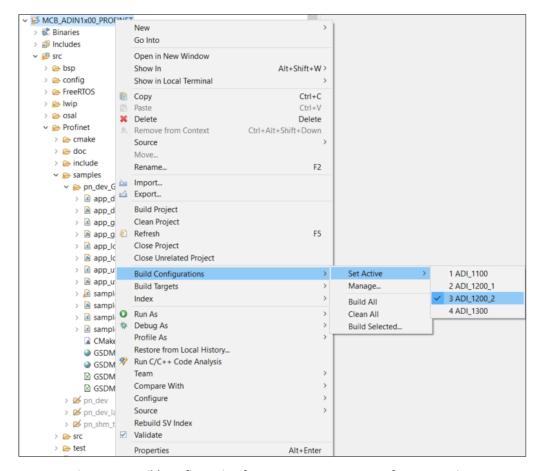

To build the FreeRTOS PROFINET reference design, select the appropriate ADIN interface. In the example shown in Figure 5.1, ADIN1200\_2 is selected.

Figure 5.1. Build Configuration for PROFINET FreeRTOS Reference Design

### 5.2. PROFINET Software Stack Functional Description

#### 5.2.1. IwIP Stack Functions

The Ethernet and Internet Protocol stacks used in the PROFINET reference design is developed using the lwIP Stack . The implementation is ported into the FreeRTOS framework. The lwIP stack has function hooks that are adapted to the PROFINET network function

The current network address is set to 192.168.0.50. You can change the IP address in *ethernet\_config.h* and recompile to change the network address.

### 5.2.2. ADIN1200 and ADIN1300 Driver API Functions

ADIN1200 and ADIN1300 driver performs several key functions.

### 5.2.2.1. ADIN\_init()

This API is used to identify the PHY interface for the ADIN1200 or ADIN1300 module.

#### 5.2.2.2. phy\_write()

phy\_write (tsemac\_handle\_t \*handle,unsigned int phy\_LPDDR,unsigned int reg\_offset,unsigned

int data)

This API writes the respective ADIN module parameters for IEEE clause 22 registers. Refer to ADIN1200 or ADIN1300 for more details.

### 5.2.2.3. phy\_read()

phy\_read(tsemac\_handle\_t \*handle,unsigned int phy\_addr, unsigned int reg\_offset)

This API reads the respective ADIN module parameters for IEEE clause 22 registers. Refer to ADIN1200 or ADIN1300 for more details.

### 5.2.2.4. adin\_GetLinkStatus()

adin\_GetLinkStatus(adinPhy\_DeviceHandle\_t hDevice, adi\_phy\_LinkStatus\_e \*status)

This API detects the link status of the respective ADIN module. This function is used in the lwIP stack low level Ethernet tasks that run continuously on the FreeRTOS.

#### 5.2.3. SGDMA Driver API functions

The functions that are required to implement SGDMA controls are based on SGDMA Controller IP Core User Guide (FPGA-IPUG-02131).

#### 5.2.3.1. sgdmaAppInit()

This API initializes the DMA with TX and RX buffers.

#### 5.2.3.2. sgdmaGetRxLength()

This API gets the length of the DMA using the SGDMA driver s2mm\_buf\_desc\_dma() and returns the length of the buffer.

### 5.2.3.3. sgdmaReadFromMAC()

sgdmaReadFromMAC(unsigned int \*pBuffer,unsigned short readlen)

This API reads from the buffer pointer and copies it into the network buffer to be sent upstream.

#### 5.2.3.4. sgdmaWritetoMAC()

sgdmaWritetoMAC(unsigned int \*OutputBuffer, int total\_bytes)

This API copies the buffer sent from the upstream network stack to be pushed out into the network.

### 5.2.4. UDP Stack Functions

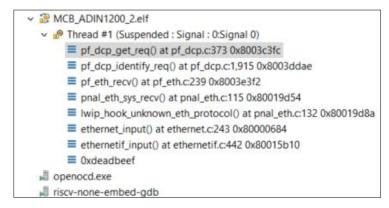

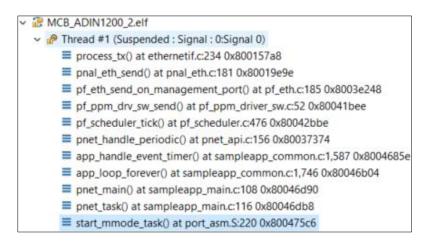

The UDP stack pushes the UDP communication up the lwlp stack. The UDP receive function stack is shown in Figure 5.2.

Figure 5.2. UDP Receive Stack

The ethernetif\_input() function constantly polls the PROFINET UDP packet buffered in the SGDMA IP block. When it acquires the buffer, the Ethernet pushes the packet from the SGDMA buffer through the lwip\_hook\_unknown\_eth\_protocol() function for further upstream processing required by the PROFINET Ethernet application APIs. The UDP transmit function stack is shown below in Figure 5.3.

Figure 5.3. UDP Transmit Stack

To transmit data, the PROFINET stack pushes the packet out using the TCP messaging thread in the LWIP stack. The TCP thread sends the packet out by pushing the buffer into the UDP Ethernet stack to be transmited through process\_tx().

#### 5.2.5. PROFINET Stack Basic Functions

The PROFINET stack implemented in this reference design is provided by RT-Labs. The stack is located as an open-source repository: https://github.com/rtlabs-com/p-net .

Below are some key points that is required to be configured in the ADI MCB implementation for PROFINET:

- The PROFINET initialization requires a heap memory stack of 256 KB on the DDR RAM

- The default configuration for sample applications is derived from pn\_dev as developed by RT-Labs

- The network interfaces are configured by app\_utils\_pnet\_cfg\_init\_netifs() to ensure that the available interfaces are configured

The functions performed in pnet\_init are as follows:

- pf\_cpm\_init(net)

- Cyclic Process Management (CPM) is a core concept in the PROFINET protocol that enables the synchronized

execution of tasks across a network of devices. It provides a deterministic and efficient mechanism for

controlling the timing and sequence of operations in industrial automation systems.

- pf\_ppm\_init(net)

- Process Parameter Mapping (PPM) maps process variables between different devices or systems. It involves

defining the correspondence between the variables, including their names, data types, units, and other

relevant attributes.

- pf\_alarm\_init(net)

- Alarms in PROFINET are critical components for monitoring and managing industrial processes. They are used

to alert operators or systems of abnormal conditions or potential issues that may affect the safety, efficiency,

or quality of operations.

- pf eth init(net, p cfg)

- Ethernet initialization to enable the Ethernet stack.

- pf bg worker init(net)

- PROFINET background worker is used to save the configuration during run-time.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-RD-02303-1.0

- pf cmina init(net)

- Communication Module Interface for Network Access (CMINA) is a fundamental component in the PROFINET

protocol that provides a standardized interface for connecting communication modules to the network. It

defines the physical and electrical characteristics, as well as the communication protocols, required for

modules to interact with PROFINET devices.

- pf\_dcp\_exit(net) and pf\_dcp\_init(net)

- Diagnostic Communication Profile (DCP) is a standardized communication profile within the PROFINET protocol that provides a framework for exchanging diagnostic information between devices on the network. It enables devices to monitor their own health, detect faults, and provide detailed diagnostic data to help troubleshoot and maintain the system.

- pf port init(net)

- PROFINET port initialization and interface configuration

- pf lldp init(net)

- Link Layer Discovery Protocol (LLDP) is a network protocol used in PROFINET to discover and exchange

information about neighboring devices on the network. It provides a mechanism for devices to automatically

configure themselves and establish connections, simplifying network management and troubleshooting.

- pf pdport init(net)

- PROFINET physical device management port initialization.

#### 5.2.5.1. Tasks

There are five events to be handled by the PROFINET task:

- APP EVENT READY FOR DATA

- Event to handle application data sent from the PLC

- APP EVENT ALARM

- Alarm events that occur within the stack and to be sent to the PLC

- APP EVENT SM RELEASED

- Sub module events from the I/O module to be sent to the PLC

- APP\_EVENT\_ABORT

- Abort event in the case of error sent from I/O module to the PLC

- APP EVENT TIMER

- Timer event scheduled periodically by the I/O module to be sent to the PLC or consumed internally

### 5.2.5.2. Application Control

The application control for the PROFINET stack resides in the *sampleapp* framework. The *sampleapp* can be used to toggle five LEDs and receive six inputs based on the GSDML file and the Siemens TIA project settings provided in this reference design.

### 5.3. Communication Between PLC and PROFINET I/O System

This connection is implemented using the Ethernet interface. Most of the messages should be in ASCII to facilitate debugging using a terminal program on the host system.

### 5.3.1. Messages from PLC to ADI MCB System

- PNIO-DCP

- LLDP Hello packet

- PNIO-CM

- PNIO-PS

- PMIO

#### 5.3.2. P-DCP

P-DCP stands for PROFINET Data Consistency Protocol. It is a crucial component of the PROFINET protocol that guarantees consistent and reliable transmission of data between devices in a PROFINET network

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 5.3.3. Link Layer Discovery Protocol (LLDP)

PROFINET devices use LLDP to discover other network devices, such as switches and routers, that are connected to the same physical network.

### 5.3.4. PNIO-CM

PNIO-CM stands for PROFINET I/O Configuration Manager. It is a crucial component of the PROFINET protocol that plays a vital role in configuring and managing I/O devices in a PROFINET network.

#### 5.3.5. PNIO-PS

PNIO-PS stands for PROFINET I/O Protocol Stack. It is the underlying communication protocol that governs the exchange of data between I/O devices and controllers in a PROFINET network.

### 5.3.6. PNIO

PNIO stands for PROFINET I/O. It is the core protocol responsible for communication between I/O devices, such as sensors and actuators, and a central controller in a PROFINET network.

For more information on PROFINET protocols, refer to the PROFINET Specification page.

# 6. Running the Reference Design

### 6.1. Compiling the Reference Design C Code in the Propel Software

Refer to the Lattice Propel Training for the basic Propel compilation steps.

The C code for the running firmware must be compiled based on the ADIN interface used for the project, which is slightly different from the GSRD.

The active build selection is either ADIN1300, ADIN1200\_2, or ADIN1200\_1. Examples shown in this document are based on ADIN1200\_2. For the bootloader firmware, the active build selection must be *Boot*.

The build artifact location is shown in Figure 6.1.

Figure 6.1. PROFINET Build Artifact Location in Propel

### 6.2. Generating the Bitstream File in the Lattice Radiant™ Software

To generate the bitstream file, refer to Golden System Reference Design User Guide (FPGA-RD-02283).

# **Testing the Application with PROFINET Demo Setup**

#### 7.1. **Demo Overview**

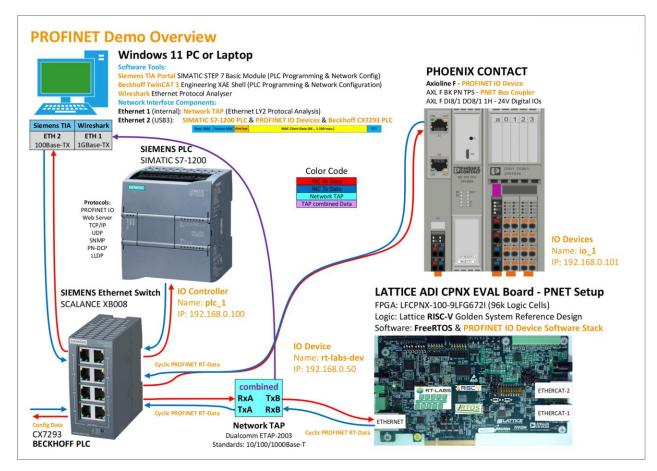

Figure 7.1. PROFINET Demo Setup Overview

### 7.1.1. Hardware Components

### 7.1.1.1. Windows 11 PC or Laptop

- **Ethernet Requirements**

- Option 1: Two RJ45 Ports (10/100/1000BASE-T)

- Option 2: One RJ45 Port (most Laptops today) and additional external USB-Ethernet Adapter

- USB-Ethernet Adapter (optional for Laptops with only one Ethernet Port)

- For example, Amazon Basics USB3 Gigabit Ethernet Adapter

- Standards: 10/100/1000BASE-T

- PHY Chip: ASIX AX88179

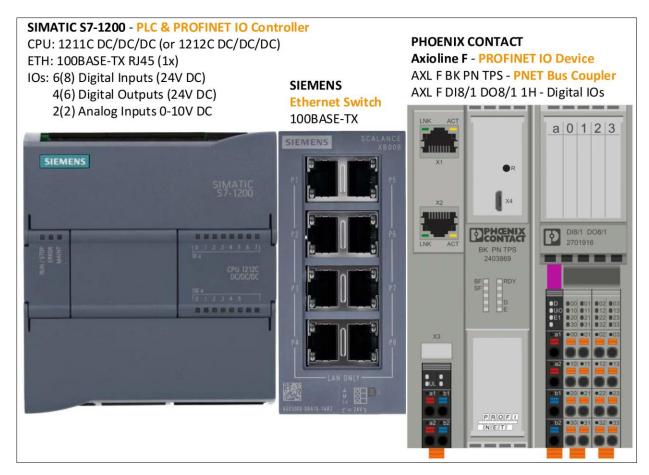

Figure 7.2 shows the overview of the PROFINET Devices: PLC, Ethernet Switch and I/O Device.

Figure 7.2. PROFINET Demo Hardware Setup

### 7.1.1.2. Siemens Simatic S7-1200 PLC and PROFINET I/O Controller

The Siemens Simatic S7-1200 Programmable Logic Controller (PLC) is a compact, modular controller designed for small to mid-sized automation tasks. As a PROFINET I/O Controller, it manages communication with distributed I/O devices over a PROFINET network, ensuring real-time data exchange and precise control. The S7-1200 also supports running PLC programs for testing and demonstration purposes, making it ideal for system development, testing, troubleshooting and validation.

The following are the details of the PLC and PROFINET I/O Controller:

- Manufacturer: Siemens

- Description: PLC and PROFINET I/O Controller

- Type: SIMATIC S7-1200

- Version: CPU 1211C DC/DC/DC (optional with CPU 1212C DC/DC/DC)

- Part Number: 6ES7211-1AE40-0XB0 (6ES7212-1AE40-0XB0)

### 7.1.1.3. Siemens 100BASE-TX Ethernet Switch

The following are the details of the Ethernet Switch:

- Manufacturer: Siemens

- Description: Ethernet Switch (unmanaged industrial 10/100BASE-T Network Switch)

- Type: SCALANCE XB008 (8 RJ45 Ports)Part Number: 6GK5008-0BA10-1AB2

### 7.1.1.4. PHOENIX CONTACT PROFINET I/O Device

This PROFINET Bus Coupler with 24 V Digital I/O is a reliable, *known good device* is essential for setting up the demo network controlled by the Siemens PLC before adding the Lattice CertusPro-NX evaluation board as new PROFINET I/O device. This ensures the proper functionality of the existing I/O controller and PROFINET network, enabling us to identify and analyze any issues that may arise during software development.

The following are the details of the PROFINET I/O device:

- Manufacturer: PHOENIX CONTACT

- Description: PROFINET I/O Device (Known Good Reference Device)

- Type: Axioline F PROFINET Bus coupler and 24 V Digital I/O Module (8x Input, 8x Output)

- Part Numbers: AXL F BK PN TPS (Article # 2403869) and AXL F DI8/1 DO8/1 1H (Article # 2701916)

#### 7.1.1.5. Ethernet Network TAP

A Network TAP (Test Access Point) or Ethernet TAP, serves as a crucial hardware component inserted inline within a network link to effectively capture real-time data traffic traversing the network. This captured data is subsequently forwarded to a monitoring tool (such as Wireshark) for analysis.

The Dualcomm TAP provides the following features.

- Tested at a full 1 Gbps data throughput with no single packet loss

- Blocks ingress traffic of the monitor port to prevent a monitoring device such as a computer from injecting packets into the network

The following are the details of the Ethernet Network TAP:

- Manufacturer: Dualcomm Technology, Inc.

- Description: 10/100/1000Base-T Network TAP (active store-and-forward TAP)

- Model: ETAP-2003

#### 7.1.1.6. Cat 6 UTP Network Cables

- Option 1: Cat 6 UTP Network Cable 0.3 m black

- Usage: PLC, PROFINET I/O Devices and Network TAP Connections

- Option 2: Cat 6 UTP Network Cable 2m white

- Usage: Ethernet Connections to Laptop

### 7.1.1.7. Siemens Simatic S7-1200 Input Switch Adapter

This adapter module enables manually control of the 24 V inputs on Siemens PLCs. Using the module switches, input[0:7] can be toggled on or off. It is designed to connect directly to the PLC input terminal block.

The following are the details of the input switch adapter:

- Manufacturer: Siemens

- Description: Input Simulator Module with Switches

- Type: SIM 1274, 8 DI (eight Input Switches)

- For PLC: SIMATIC S7-1200

- With CPU: 1211C (6 DI 24 V DC) or 1212C (8 DI 24 V DC)

- Part Number: 6ES7274-1XF30-0XA0

#### 7.1.1.8. ADI Motion Control Board

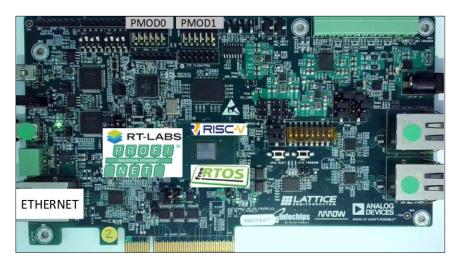

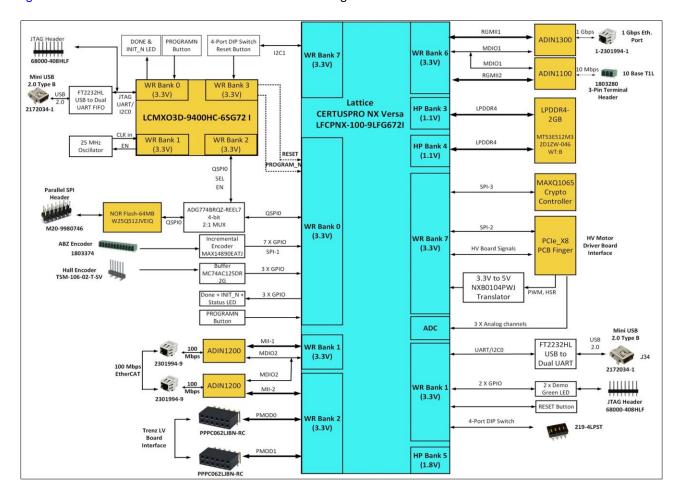

Figure 7.3. ADI CertusPro-NX Motion Control Evaluation Board

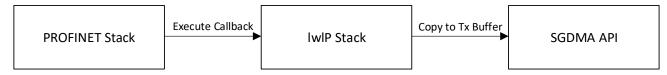

Figure 7.4 shows the CertusPro-NX motion control block diagram.

Figure 7.4. ADI CertusPro-NX Motion Control Block Diagram

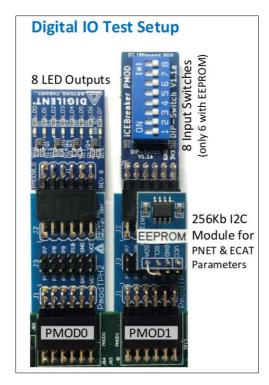

#### 7.1.1.9. PMOD Test Headers and Modules

The PMOD interface (peripheral module interface) is an open standard defined by Digilent in the PMOD Interface Specification for connecting the peripheral modules to the FPGA and Microcontroller development boards.

The following are the details of the test headers and modules:

- Manufacturer: Digilent

- Option 1: PMOD TPH2 (12-pin Test Header)

- Description: 12 external pins to easily test the GPIO signals passing through each of the PMOD pins.

- Option 2: PMOD 8LD (Eight High-brightness LEDs)

- Description: Eight LEDs with driver, each LED can be individually illuminated from a logic high signal.

- Manufacturer: 1BitSquared

- Description: PMOD DIP-Switch V1.1a (8 Inputs switching to +3.3 V with 10K pull-down resistors)

#### 7.1.1.10. PMOD Configuration Options

### **Digital IO Test Setup**

Figure 7.5. DIGITAL I/O Setup for LED

#### 7.1.2. Software Components

#### 7.1.2.1. Lattice Radiant Programmer – FPGA Fabric and System Memory Configuration Tool

The Lattice Radiant software offers all the tools and features to help you develop your FPGA applications. The Radiant Programmer is part of the Radiant Design software, but a standalone version is also available.

- Functions

- Download of bitstream (BIT) configuration files to setup the FPGA fabric and system memory directly or to store the configuration data in an external SPI Flash memory to enable FPGA configuration and initialization of internal system memory during power-up

- Download of binary (BIN) data files to the external SPI Flash memory to enable the bootloader software moving the data to the external LP-DDR4 RISC-V code memory

- License: Free Node-locked License available with Lattice Semiconductor account

#### 7.1.2.2. Siemens PRONETA – Diagnostics Tool for PROFINET Networks

PRONETA is a PC-based commissioning and diagnostics tool for PROFINET Networks. The free basic version is used in this Demo for scanning the PROFINET Network. A licensed version with additional functionalities is also available for a simple commissioning of the network and an easy check of the distributed I/O of connected I/O devices, without PLC.

- Demo Functions: Scanning the network for accessible devices, setup of IP addresses and device names

- License Options: free Software (basic version) and licensed version with more functions

- Download Links: PRONETA Basic 3.8 (or higher)

- Npcap 1.80 installer for Windows (free software)

To install the Siemens PRONETA, perform the following:

- 1. Download the ZIP File from Siemens website

- 2. Unpack the ZIP and store the PRONETA.exe file

- No Installation is required, but the NPCAP driver is needed to run PRONETA. 3.

- Install the NPCAP version 1.80 or higher before starting PRONETA the first time.

NPCAP allows the Windows software to capture raw network traffic (such as the Ethernet) using a simple, portable API. NPCAP allows you to send raw packets as well. The Mac and Linux systems already include the NPCAP API, so NPCAP allows popular software such as Wireshark to run on all these platforms with a single codebase.

### 7.1.2.3. Siemens TIA Portal – Engineering and Diagnostics Tool (SIMATIC STEP 7 Basic Module)

The Siemens TIA Portal (Totally Integrated Automation Portal) is a powerful engineering software platform designed for configuring and programming industrial automation systems, with a focus on PROFINET networks and I/O device integration. It simplifies PLC programming, network setup, and device configuration with a unified interface for managing PROFINET-enabled devices.

The following are the details of the Siemens TIA Portal:

- Function: PLC Engineering Software for Network Configuration and PLC Programming

- Type: TIA Portal

- Module: SIMATIC STEP 7 Basic

- Version: V19 (or higher)

The following are the guidelines and notes to installing and testing the Siemens TIA with the reference design:

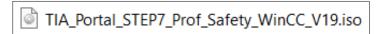

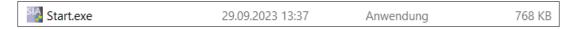

Image File: C:\Tools\Siemens\TIA\_Portal\_STEP7\_Prof\_Safety\_WinCC\_V19.iso Note: The ISO Image is shown with Disk Symbol (see Figure 7.7).

Figure 7.6. ISO Image for TIA Portal

To install the Siemens TIA portal, perform the following:

- Double-click on the mounted DVD Drive to open the DVD disk image.

- Click **start.exe**. Install Option is *Minimal* (not *Typical*, not user defined).

Figure 7.7. Start Button to Install

After the reboot, open the DVD Disk Image again after the no DVD Drive detected message.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 7.1.2.4. Wireshark Network Protocol Analyzer

Wireshark is a powerful network analyzer tool used for capturing and analyzing network traffic in real time. It provides detailed insights into Ethernet Layer two frames, allowing you to inspect protocols (identified by a unique EtherType value) like IPv4 (UDP and TCP), ARP, LLDP and PROFINET.

For PROFINET analysis, Wireshark decodes the protocol's real-time communication between I/O controllers and I/O devices, offering precise diagnostics and troubleshooting for industrial automation networks.

The following are the details of the Wireshark Network Protocol Analyzer:

- Functions: Capturing of the Ethernet LY2 frames and analysis of IP and PROFINET protocols

- License: free software

- Download: Wireshark tool

### 7.2. Evaluation Board Configuration with Lattice Radiant Programmer

You must configure the Lattice ADI Evaluation Board with the provided PROFINET Demo Example before you can use it properly. The following components must be programmed first using the Lattice Radiant Programmer software tool. Once configured, the board can be fully tested to verify the functionality of the PROFINET setup and the Evaluation Board itself. This process ensures the board is ready for further testing with the customer development project.

The following are the description for the binaries used in the Reference Design

- FPGA Logic Fabric with the Lattice Hardware Reference Design

This is the content of the project bitstream programming file (for example, with RISC-V MCU IP and Ethernet MAC IP).

- Bootloader Software that is part of the Lattice Software Reference Design

This is the content of the project bitstream programming file to setup the FPGA system memory.

- PROFINET Software Stack, TCP/IP Stack and Application Software

This is the content of the project Binary programming file, to enable the bootloader to move the software code to the external LP-DDR4 memory.

The .bit and .bin files are programmed separately to different locations of the FPGA SPI Flash configuration memory as described below.

To program the bit file to Start Address 0x0000 0000, perform the following:

- 1. Download and install the Lattice Radiant Programmer Software in the Lattice website.

- 2. Connect the USB port aside the green connector on the left side of the board to your PC or Laptop.

- 3. Power-up the evaluation board.

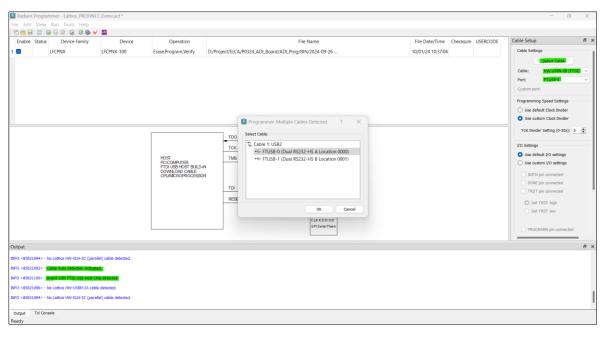

- 4. Start the Radiant Programmer. Create a new project or open the *existing project* within the demo zip file. Figure 7.8 is displayed after clicking on *Detect Cable*, if everything is fully functional.

- 5. Click **OK** to go back to the default screen.

- 6. Repeat the *Detect Cable* process in case of any error messages.

Figure 7.8. Bit File Programming for ADI MCB

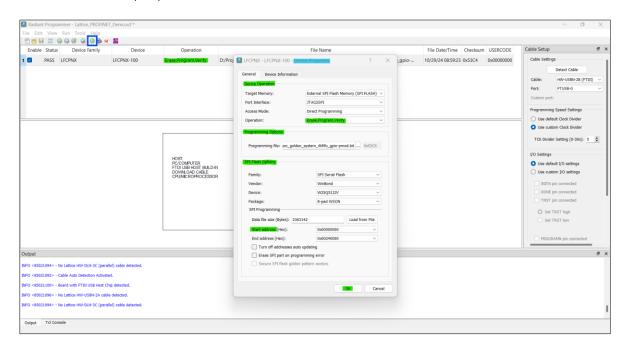

- 7. Enter the bitstream file name.

- 8. Double-click on the *Erase/Program/Verify* field or any other mode that may be displayed to open the Device Properties window.

- 9. Apply the settings for **Device Operation**, **Programming Options (Programming file)** and **SPI Flash Options** as shown in Figure 7.9.

- a. Set the operation mode to Erase/Program/Verify.

- b. Make sure that the following addresses are correct:

- Start Address (Hex) 0x00000000

- End Address (Hex) 0x00240000

Figure 7.9. Configuring Bit File Programming for ADI MCB

- 10. Click **OK** to close the Device Properties window

- 11. Click the **Program Device** icon in the main menu to start the programming process.

- 12. The bitstream file is programmed to Start Address 0x0000 0000 of the SPI Flash configuration memory.

- 13. The following sequence is displayed on the **Output** window once the operation is successful.

```

INFO <85021096> - No Lattice HW-USBN-2A cable detected.

INFO <85021094> - No Lattice HW-DLN-3C (parallel) cable detected.

INFO <85021074> - Check configuration setup: Start.

INFO <85021077> - Check configuration setup: Successful (Ignored JTAG Connection

Checking).

INFO <85021294> - Device1 LFCPNX-100: LFCPNX-100: Refresh Verify ID

INFO <85021298> - Operation Done. No errors.

INFO <85021294> - Device1 LFCPNX-100: W250512JV: Erase, Program, Verify

Initializing...

IDCode Checking...

Enter 4-Byte mode...

Enabling...

Erasing...

Enabling... Programming... Disabling... Verifying...

INFO <85021399> - Execution time: 01 min : 18 sec

INFO <85021371> - Elapsed time: 01 min : 24 sec

INFO <85021373> - Operation: successful.

```

To program the bin file to Start Address 0x020A 0000, perform the following:

- 1. Enter the binary file name.

- 2. Double-click on the Erase/Program/Verify field or any other mode that may be displayed to open the Device Properties window.

- 3. Check the settings for Device Operation, Programming Options (Programming file) and SPI Flash Options as shown in Figure 7.9.

- Set the operation mode to Erase/Program/Verify.

- b. Make sure that the following addresses are correct:

- Start Address (Hex) -0x00240000

- End Address (Hex) 0x00000000

The new end address is automatically calculated using the end address after loading as offset.

- 4. Click **OK** to close the Device Properties window.

- 5. Click the **Program Device** icon in the main menu to start the programming process.

- 6. The bitstream file is programmed to Start Address 0x020A0000 of the SPI Flash configuration memory.

- 7. The following sequence is displayed on the Output window in case of a successful operation.

#### 7.3. Scanning the Network for Accessible PROFINET Devices with Siemens **PRONETA**

Before adding a new I/O device to a PROFINET network, use the PRONETA scanning tool to confirm that the device is functioning and accessible. If the device cannot be detected or accessed, the configuration process with the TIA Portal engineering tool fails. PRONETA ensures that the device is connected and ready, making the subsequent configuration process successful.

PRONETA is a quick and easy solution for verifying a PROFINET I/O device setup without the need to install the more complex TIA Portal software.

Note: Set the local IP address of the used Ethernet Adapter to 192.168.0.1 (subnet: 255.255.255.0).

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

To scan the network, perform the following:

- 1. Start the **PRONETA.exe** and click *Network Analysis*.

- 2. Click Online Refresh.

- 3. After the successful scan process, the accessible devices are listed in the **Device Table**.

- 4. Select the device within the table to view the details. The information of the selected device is displayed in the *Device Details* window.

# 7.4. Configuring the PROFINET Device Names and IP Addresses with Siemens PRONETA

**Note**: This an easy and direct approach to prepare the I/O Device Names and IP Addresses before using the Siemens TIA Portal software.

To configure the PROFINET device name and IP address, perform the following:

- 1. Scan the network as described in the Scanning the Network for Accessible PROFINET Devices with Siemens PRONETA section.

- 2. In the Network Analysis Online Graphical View window, select device io\_1 to show the device details.

- 3. Double-click on the device (for example, io 1) to open the Set Network Parameters window.

- 4. Set the **Device Name**, **Static IP Address**, and **Subnet Mask**.

- 5. Select **Apply settings permanently** and click the **Set** button to change the device settings.

# 7.5. Quick Start with the Siemens TIA Sample Project and Programming the FPGA Device

The Siemens TIA sample project is available that directly works with the hardware setup shown in the PROFINET Demo Overview diagram in the Demo Overview section.

The TIA sample project enables a quick start of the PROFINET Demo by following the guidelines below.

- 1. Order the PROFINET demo network hardware components.

- Review the manufacturer product links and ordering information in the Hardware Components section.

- 2. Build the PROFINET demo hardware setup.

- Review the demo overview diagram in the Demo Overview section.

- Follow the manufacturer product datasheets and installation instructions.

- 3. Download and install the Lattice Radiant Programmer software.

**Note:** The Radiant Programmer is part of the Radiant Design software.

- Sign-In or Register for a Lattice Semiconductor account.

- Download the Windows version of the Radiant Design software.

- Follow the Installation Guides or download and install the Programmer Standalone 2024.1.1 64-bit for Windows.

- Request a free Node-locked License.

- 4. Run Radiant Programmer to program the qSPI Flash on the Lattice ADI MCB evaluation board

- Open the programmer sample project of the demo ZIP file (PROFINET Demo.xcf).

- Program the bitstream file (FPGA fabric and bootloader software) to Start Address 0x0000 0000.

- Program the binary file (PROFINET stack and application software) to Start Address 0x020A 0000.

- 5. Download and Install the Siemens PRONETA software tool.

- Review the product information and download link in the Software Components section.

- Follow the guidelines described in the Software Components section.

- 6. Run PRONETA to scan and setup the network.

- Scan the network for accessible devices as mentioned in the Scanning the Network for Accessible PROFINET

Devices with Siemens PRONETA section.

- The Siemens PLC, Phoenix Contact I/O device, and rt-labs-dev I/O device appears.

- Configure the PROFINET names and IP addresses according to the overview diagram in the Demo Overview section.

- Follow the guidelines in the Testing of basic PROFINET I/O Device Functions section for any changes, and then scan the network again to check the status.

- 7. Download and install the Siemens TIA Portal software tool.

- Review the product information and download link in the Software Components section.

- Follow the guidelines described in the Software Components section.

- 8. Run TIA Portal with the PROFINET demo sample project.

- Open the TIA sample project of the demo zip file.

- 9. Check current device name and IP address configuration

- Use the guidelines in the Checking the Current Device Names and IP Addresses section.

- The settings must be the same as defined in the PROFINET overview diagram.

- 10. Compile and load the PLC configuration and control software.

- Follow the guidelines in the Compiling and Loading the PROFINET System Configuration section.

- 11. Go online and check the PROFINET network status.

- Follow the guidelines in the Checking the System Status Online section.

- Check the status symbols in the project tree window.

- All status symbols should be green as in screenshot in the Checking the System Status Online section.

- Switch on the local inputs [0:3] of the Siemens PLC device.

- This sets the local outputs [0:3] of the PLC device to the active HI state (LEDs on).

- For io\_1 and rt-labs-dev device tests, refer to the Testing of basic PROFINET I/O Device Functions section.

### 7.6. Testing of basic PROFINET I/O Device Functions

The PROFINET I/O functionality of the example application implemented on the Lattice ADI evaluation board (see the configuration in the Evaluation Board Configuration with Lattice Radiant Programmer section) can be tested with a Siemens TIA Portal demo project provided by Lattice. For general guidance on using the TIA software, a complete tutorial on setting up a project from scratch is available in the Setting Up a New Demo Project Using Siemens TIA section.

The TIA demo project includes the following functions:

- Verification of Siemens PLCs PROFINET I/O Controller functionality with a simple PLC control program

- Verification of PROFINET I/O Reference Device functionality by using its digital inputs and outputs

- Testing and demonstration of PROFINET I/O user device functionality on the Lattice ADI Evaluation Board

The TIA demo project provides the following features for testing the Lattice PROFINET sample application:

- Testing of one digital system output on PMOD0[5] (PROFINET Flash LED diagnostic feature)

- Testing of five digital user outputs on PMOD0[0:4]

- Testing of six digital user inputs on PMOD1[0:5], PMOD1[6:7] is reserved for an I2C EEPROM module

### 7.6.1. Connection of PMOD Test Modules to the Lattice ADI Evaluation Board