# Closed Loop Brushless Direct Current (BLDC) Motion Control User Guide

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents                                                                             | 3  |

|--------------------------------------------------------------------------------------|----|

| Abbreviations in This Document                                                       | 6  |

| 1. Introduction                                                                      | 7  |

| 1.1. Quick Facts                                                                     | 7  |

| 1.2. Features                                                                        | 8  |

| 1.3. Naming Conventions                                                              | g  |

| 1.3.1. Nomenclature                                                                  |    |

| 1.3.2. Signal Names                                                                  | g  |

| 2. Directory Structure and Files                                                     | 10 |

| 3. Functional Description                                                            |    |

| 3.1. Design Components                                                               |    |

| 3.1.1. RISC-V MC CPU                                                                 |    |

| 3.1.2. Encoder Subsystem                                                             | 13 |

| 3.1.3. Motor Control                                                                 |    |

| 3.1.4. SPI Controller                                                                | 27 |

| 3.1.5. UART                                                                          | 28 |

| 3.1.6. GPIO                                                                          | 28 |

| 3.2. Data Flow                                                                       | 28 |

| 3.3. Clocking Scheme                                                                 | 29 |

| 3.3.1. Clocking Overview                                                             |    |

| 3.4. Reset Scheme                                                                    | 30 |

| 3.4.1. Reset Overview                                                                |    |

| 3.5. Software                                                                        |    |

| 3.5.1. RISC-V Bare Metal Program                                                     |    |

| 3.5.2. Encoder Driver for the EnDat2.2 Master IP                                     |    |

| 3.5.3. Encoder Driver for the HIPERFACE DSL Master IP                                |    |

| 3.5.4. Encoder Driver for the MB100 BiSS Interface Master IP                         |    |

| 3.5.5. Demo GUI Application                                                          | 33 |

| 4. Signal Description                                                                | 34 |

| 5. Running the Reference Design                                                      | 36 |

| 5.1. Opening the Reference Design in the Lattice Propel Builder Software             | 36 |

| 5.2. Compiling the Reference Design in the Lattice Radiant Software                  | 37 |

| 5.3. Programming the Bitstream into the FPGA Device                                  | 38 |

| 5.4. Simulating the Reference Design                                                 | 40 |

| 6. Implementing the Reference Design on Board                                        | 44 |

| 6.1. Extracting the Reference Design Files                                           | 44 |

| 6.2. Setting Up the Evaluation Board                                                 | 44 |

| 6.3. Setting Up the Encoder Board                                                    | 45 |

| 6.4. Setting Up the UART Terminal                                                    | 46 |

| 6.4.1. Setting Up the Tera Term Software                                             | 46 |

| 6.4.2. Setting Up the Demo GUI Application                                           | 47 |

| 6.5. Running the Motor from Demo GUI Application                                     | 48 |

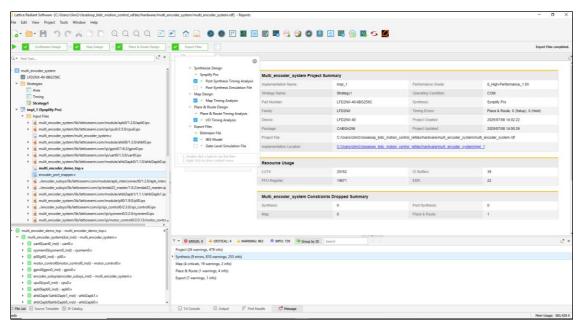

| 7. Resource Utilization                                                              | 50 |

| 8. Debugging                                                                         | 51 |

| 8.1. Motor Unable to Run After Configured in Either Closed Loop or Open Loop Control | 51 |

| 8.2. Motor Unable to Accelerate or Decelerate Correctly for Closed Loop Control      | 51 |

| 8.3. Proportional and Integration Constant Tuning                                    | 51 |

| 8.4. GUI Hang, Not Responding, or Exit Abruptly                                      | 52 |

| 8.5. UART Serial Terminal Prints Incorrect Characters                                | 52 |

| 9. Integrating with a Different Motor                                                | 53 |

| 9.1. Overcurrent Fault                                                               | 53 |

| 9.1.1. Power Parameter Tuning                                                        | 53 |

| 9.1.2. Reducing Target RPM Value                                                        | 53 |

|-----------------------------------------------------------------------------------------|----|

| 9.1.3. Debugging Mode from the Motor Control IP                                         | 53 |

| 10. Integrating with a Different Encoder                                                | 57 |

| 10.1. Encoder Resolutions                                                               | 57 |

| 10.2. Custom Encoder Master IPs                                                         | 57 |

| References                                                                              | 59 |

| Technical Support Assistance                                                            | 60 |

| Revision History                                                                        | 61 |

| ·                                                                                       |    |

|                                                                                         |    |

|                                                                                         |    |

| Figures                                                                                 |    |

| Figure 2.1. Directory Structure of the Closed Loop BLDC Motion Control Reference Design |    |

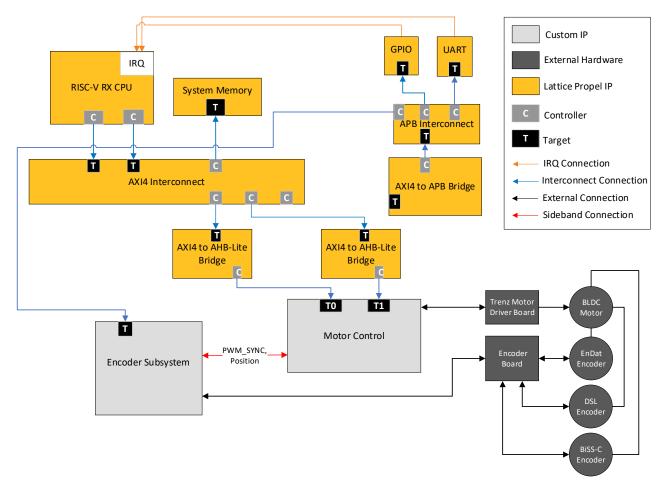

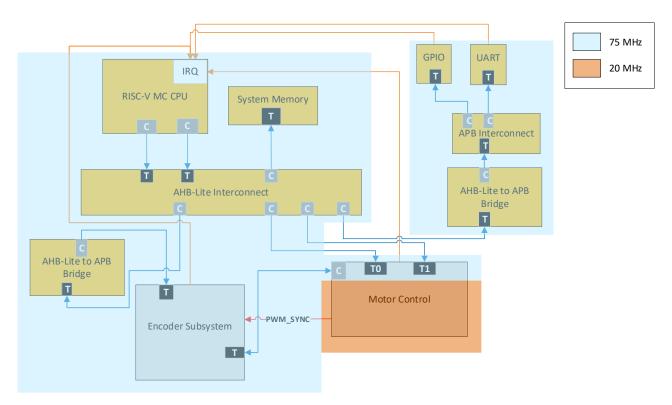

| Figure 3.1. Closed Loop Motor Control System Architecture (CertusPro-NX)                | 11 |

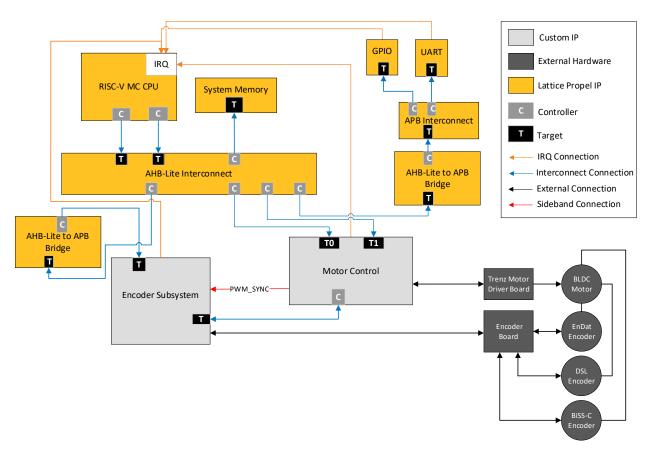

| Figure 3.2. Closed Loop Motor Control System Architecture (Certus-NX)                   | 12 |

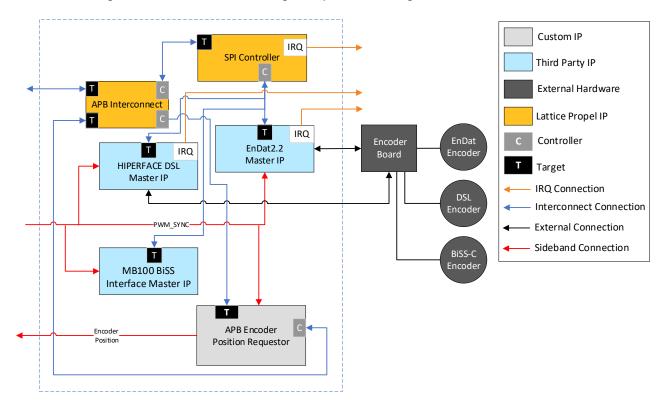

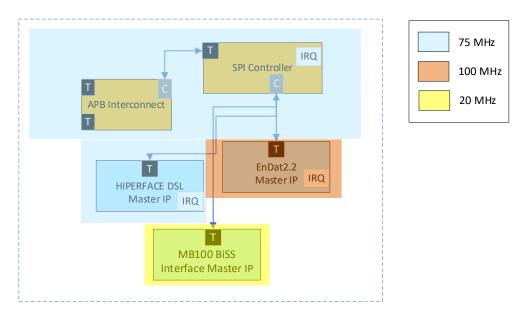

| Figure 3.3. Encoder Subsystem Architecture                                              | 13 |

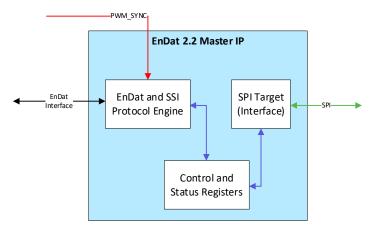

| Figure 3.4. EnDat2.2 Master IP                                                          | 14 |

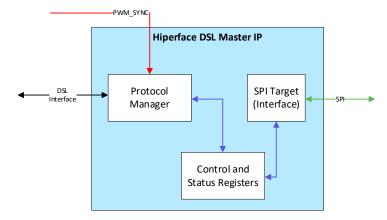

| Figure 3.5. HIPERFACE DSL Master IP                                                     | 14 |

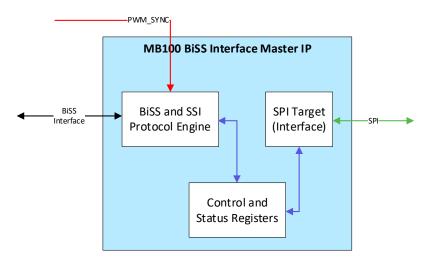

| Figure 3.6. MB100 BiSS Interface Master IP                                              |    |

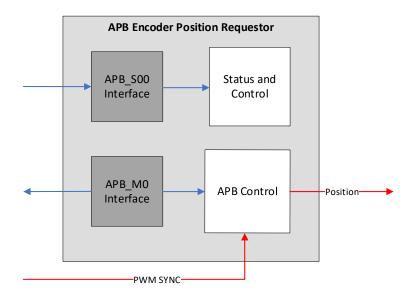

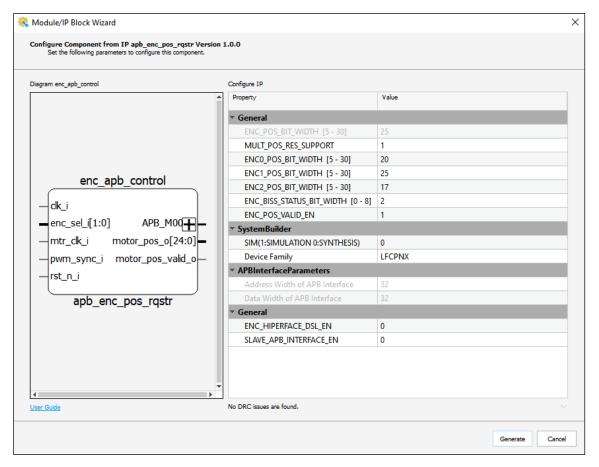

| Figure 3.7. APB Encoder Position Requestor IP                                           | 16 |

| Figure 3.8. APB Encoder Position Requestor IP Block Wizard                              | 16 |

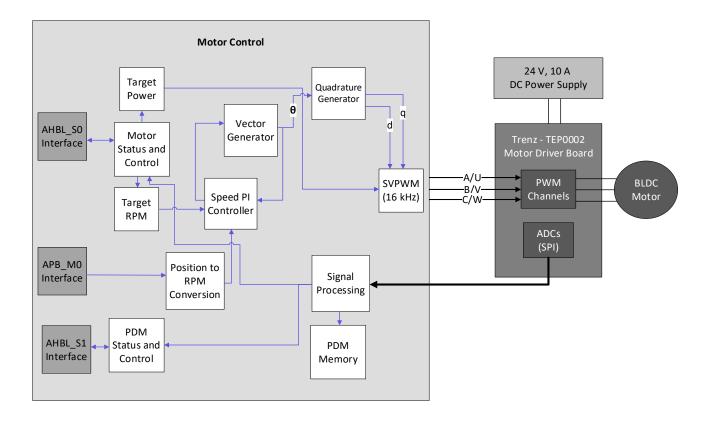

| Figure 3.9. Motor Control IP                                                            | 19 |

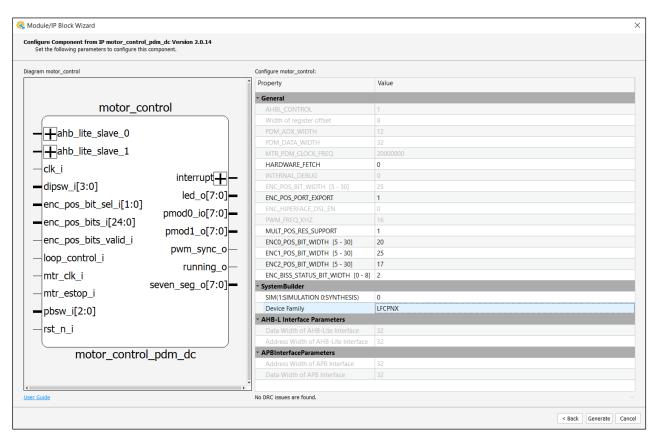

| Figure 3.10. Motor Control IP Block Wizard                                              | 21 |

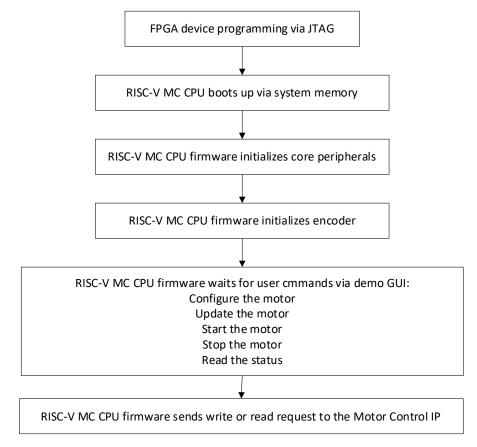

| Figure 3.11. General Application Flow                                                   |    |

| Figure 3.12. Overall System Clocking Domain                                             | 30 |

| Figure 3.13. Encoder Subsystem Clocking Domain                                          | 30 |

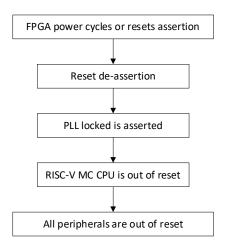

| Figure 3.14. Reset Sequence Flow                                                        | 31 |

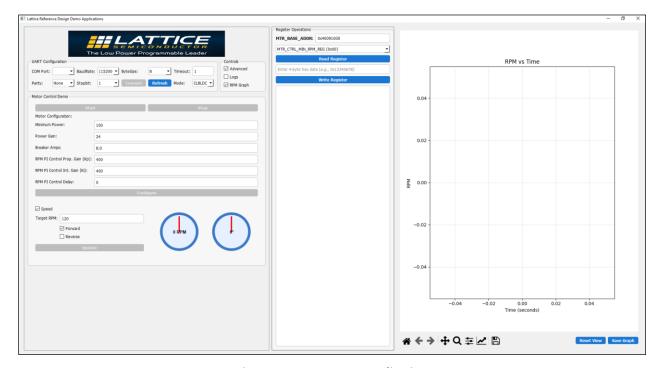

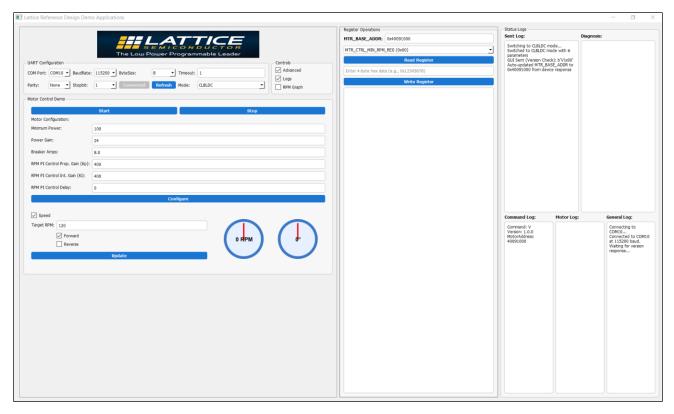

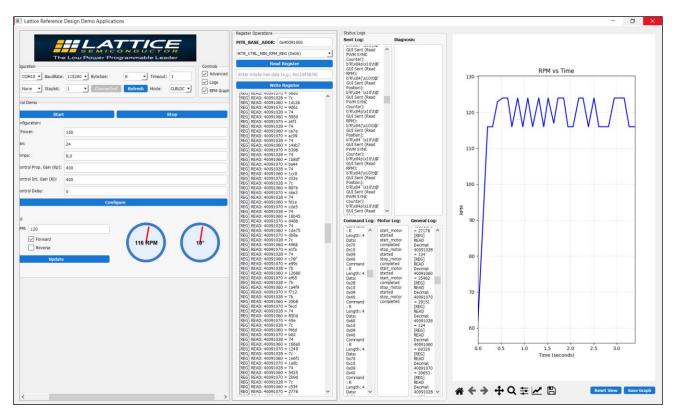

| Figure 3.15. Demo GUI Application                                                       | 33 |

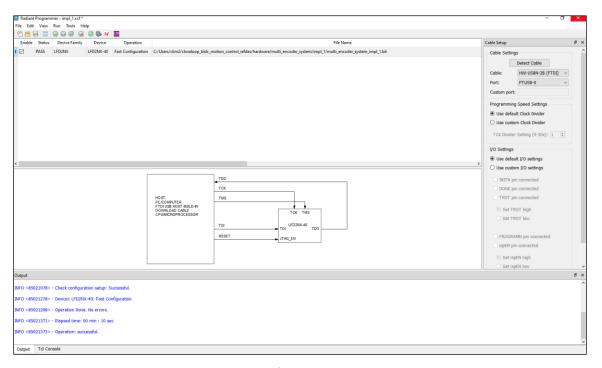

| Figure 5.1. Lattice Propel Builder Software                                             |    |

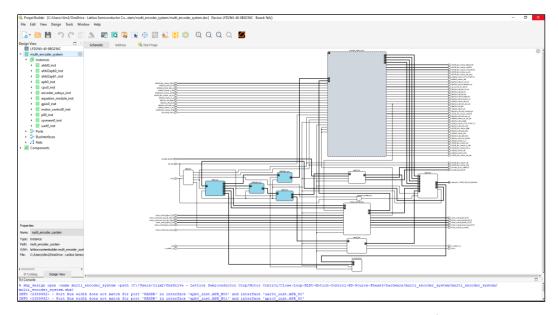

| Figure 5.2. Opening the Design in the Lattice Propel Builder Software                   | 37 |

| Figure 5.3. Lattice Radiant Software                                                    |    |

| Figure 5.4. Opening the Project File in the Lattice Radiant Software                    |    |

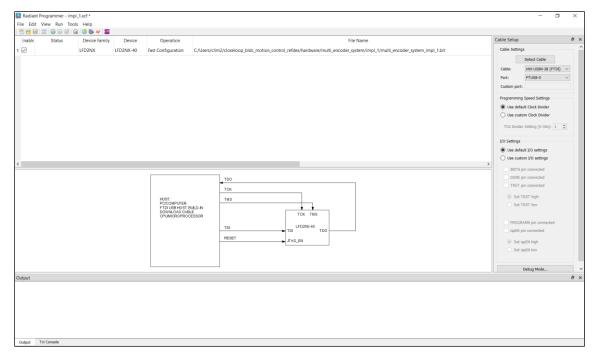

| Figure 5.5. Lattice Radiant Programmer                                                  |    |

| Figure 5.6. Successful Bitstream Programming                                            | 39 |

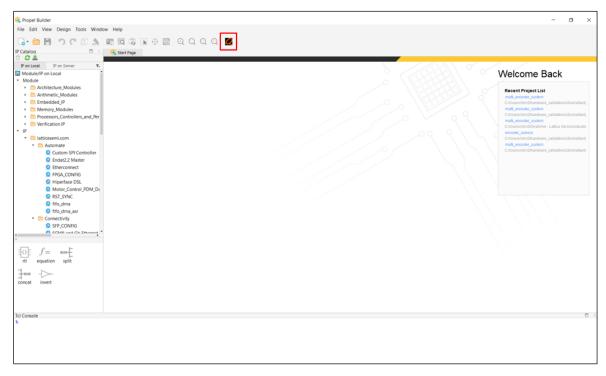

| Figure 5.7. Opening the QuestaSim Software in the Lattice Propel Builder Software       |    |

| Figure 5.8. RISC-V MC CPU Out of Reset                                                  |    |

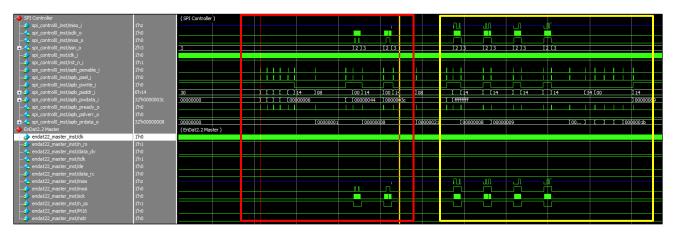

| Figure 5.9. EnDat2.2 Master SPI Transaction                                             |    |

| Figure 5.10. MB100 BiSS Transaction                                                     |    |

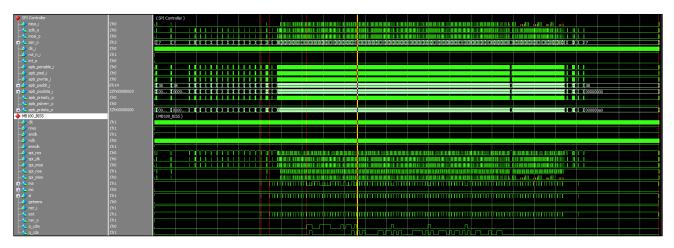

| Figure 5.11. MB100 BiSS Transaction (Zoom In)                                           | 42 |

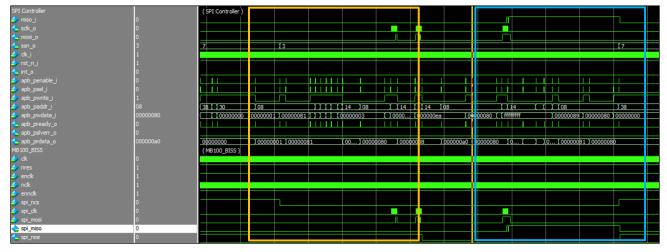

| Figure 5.12. Motor Control Configuration Register Updates                               |    |

| Figure 5.13. Motor Control Configuration Register Updates (Zoom In)                     | 43 |

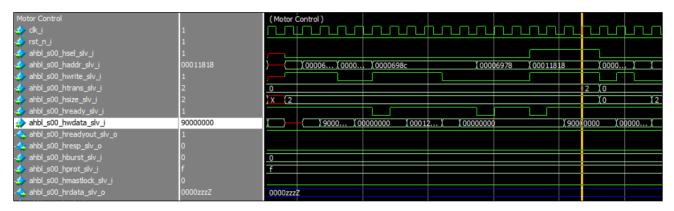

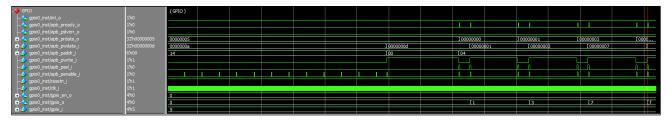

| Figure 5.14. GPIO Output Updates                                                        | 43 |

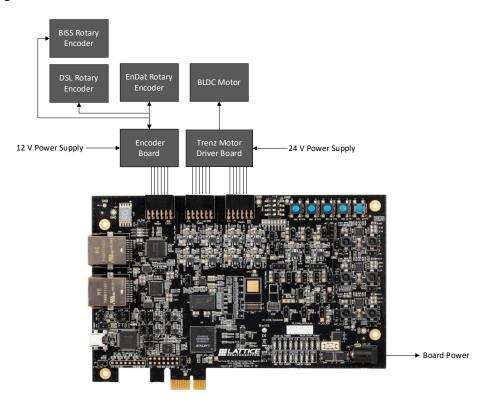

| Figure 6.1. Certus-NX Versa Evaluation Board Setup                                      | 44 |

| Figure 6.2. CertusPro-NX Evaluation Board Setup                                         | 45 |

| Figure 6.3. Tera Term Software Setup                                                    |    |

| Figure 6.4. Demo GUI Application UART Test Tab Setup                                    | 48 |

| Figure 6.5. Demo GUI Application Motor Control Demo Tab                                 | 49 |

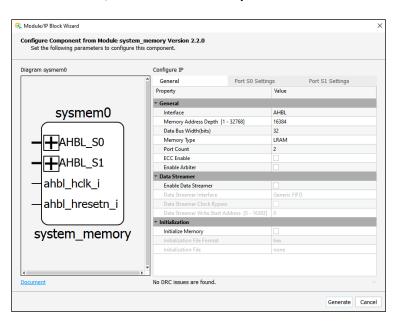

| Figure 9.1. System Memory IP Block Wizard                                               | 54 |

|                                                                                         |    |

# **Tables**

| Table 1.1. Summary of the Reference Design                                         |    |

|------------------------------------------------------------------------------------|----|

| Table 2.1. File List in the Reference Design Package                               | 10 |

| Table 3.1. APB Encoder Position Requestor IP Attributes                            |    |

| Table 3.2. APB Encoder Position Requestor IP Attributes Description                | 17 |

| Table 3.3. Access Types                                                            | 18 |

| Table 3.4. APB Encoder Position Requestor IP Registers                             | 18 |

| Table 3.5. APB_CTRL_REG                                                            |    |

| Table 3.6. APB_STATUS_REG                                                          |    |

| Table 3.7. Subblocks Operation of the Motor Control IP                             | 20 |

| Table 3.8. Motor Control IP Attributes                                             |    |

| Table 3.9. Motor Control IP Attributes Description                                 | 22 |

| Table 3.10. Access Types                                                           |    |

| Table 3.11. Motor Control IP Registers                                             | 23 |

| Table 3.12. Minimum RPM                                                            |    |

| Table 3.13. Maximum RPM                                                            |    |

| Table 3.14. RPM PI Ki                                                              |    |

| Table 3.15. RPM PI Kp                                                              |    |

| Table 3.16. Synchronization Delay and Control                                      | 24 |

| Table 3.17. Target RPM                                                             | 25 |

| Table 3.18. Status RPM                                                             |    |

| Table 3.19. System Status                                                          |    |

| Table 3.20. Predictive Maintenance Control0                                        |    |

| Table 3.21. Predictive Maintenance Status                                          |    |

| Table 3.22. Predictive Maintenance Current/Voltage Data (for Register Offset 0x3C) |    |

| Table 3.23. Predictive Maintenance Current/Voltage Data (for Register Offset 0x40) |    |

| Table 3.24. Versa Board LED                                                        |    |

| Table 3.25. Encoder Position                                                       |    |

| Table 3.26. PWM_SYNC IRQ Status                                                    |    |

| Table 3.27. Clocking                                                               |    |

| Table 3.28. Reset                                                                  |    |

| Table 3.29. Main APIs                                                              |    |

| Table 3.30. Encoder Driver APIs for the EnDat2.2 Master IP                         |    |

| Table 3.31. Encoder Driver APIs for the HIPERFACE DSL Master IP                    |    |

| Table 3.32. Encoder Driver APIs for the MB100 BiSS Interface Master IP             |    |

| Table 4.1. Primary I/O Interface Signals for the multi_encoder_demo_top Module     |    |

| Table 7.1. Resource Utilization for Certus-NX Devices                              |    |

| Table 8.1. K <sub>p</sub> and K <sub>i</sub> Gain Effects in Closed Loop System    |    |

| Table 10.1. Motor Control IP Settings for Other Encoder Models                     |    |

| Table 10.2. APB Encoder Position Requestor IP Settings for Other Encoder Models    | 57 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviations  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ADC            | Analog to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| AHB            | Advanced High-performance Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| APB            | Advanced Peripheral Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| BiSS-C         | Bidirectional Synchronous Serial – Continuous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| BLDC           | Brushless Direct Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CNC            | Computer Numerical Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| CPU            | Central Processing Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| CRC            | Cyclic Redundancy Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| DIP            | Dual Inline Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| DSP            | Digital Signal Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| EBR            | Embedded Block RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| FPGA           | Field-Programmable Gate Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| GPIO           | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| GUI            | Graphical User Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| IP             | Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| K <sub>I</sub> | Integral Term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Kp             | Proportional Term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| LED            | Light-Emitting Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| LMMI           | Lattice Memory Mapped Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| MISO           | Master In Slave Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| MOSI           | Master Out Slave In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PC             | Personal Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PI             | Proportional-Integral Proportional Proportio |  |  |

| PDM            | Predictive Data Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| PLL            | Phase-locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PWM            | Pulse Width Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RISC-V         | Reduced Instruction Set Computer Five                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| SCD            | Single-cycle Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SPI            | Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |