# **CrossLinkU-NX USB Video Class**

# **Reference Design**

FPGA-RD-02306-1.1

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same, LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                   | 3  |

|--------------------------------------------|----|

| Abbreviations in This Document             | 8  |

| 1. Introduction                            |    |

| 1.1. Quick Facts                           |    |

| 1.2. Features                              |    |

| 1.3. Naming Conventions                    |    |

| 1.3.1. Nomenclature                        | 10 |

| 1.3.2. Signal Names                        | 10 |

| 2. Directory Structure and Files           | 11 |

| 3. Functional Description                  | 12 |

| 3.1. Design Components                     | 12 |

| 3.1.1. PLL                                 | 12 |

| 3.1.2. USB23 Controller                    | 14 |

| 3.1.3. AHB-Lite to LMMI Converter          | 14 |

| 3.1.4. RISC-V Microcontroller              | 14 |

| 3.1.5. System Memory                       | 15 |

| 3.1.6. UART                                |    |

| 3.1.7. GPIO                                | 17 |

| 3.1.8. Lattice I2C Controller              | 18 |

| 3.1.9. AHB-Lite Interconnect               | 19 |

| 3.1.10. APB Interconnect                   |    |

| 3.1.11. APB-Lite to APB Converter          | 24 |

| 3.1.12. RX DPHY                            |    |

| 3.1.13. MIPI Packet Decoder                |    |

| 3.1.14. Byte to Pixel                      |    |

| 3.1.15. B2P to AXI Stream Conversion       |    |

| 3.1.16. Debayer                            |    |

| 3.1.17. Color Correction Matrix            |    |

| 3.1.18. AXI Stream to Parallel Conversion  |    |

| 3.1.19. Color Space Converter              |    |

| 3.1.20. YUV422 to UVC Bridge               |    |

| 3.1.21. IEBM In FIFO Interface             |    |

| 3.1.22. In Endpoint Buffer Manager         |    |

| 3.1.23. AHB-Lite to Memory Bridge          |    |

| 3.1.24. USB23 to AXI Bridge                |    |

| 3.1.25. RAW10 Test Pattern Generator       |    |

| 3.1.26. YUV422 Test Pattern Generator      |    |

| 3.1.27. YUV422 Test Pattern In FIFO Bridge |    |

| 3.2. Clocking Scheme                       |    |

| 3.2.1. Clocking Overview                   |    |

| 3.3. Reset Scheme                          |    |

| 3.3.1. Reset Overview                      |    |

| 4. IN Endpoint Buffer Manager Architecture |    |

| 4.1. IP Ports and Parameters               |    |

| 4.1.1. AHB-Lite Interface                  |    |

|                                            |    |

| 4.1.3. FIFO Interface                      |    |

|                                            |    |

|                                            |    |

| 4.2. Register Offset Map                   |    |

| 4.3.1. IP VERSION                          |    |

| 7.3.1. IF_VENSION                          |    |

| 4.3.2.     | SCRATCH                                              | 37 |

|------------|------------------------------------------------------|----|

| 4.3.3.     | INT_EN                                               |    |

| 4.3.4.     | INT_SRC                                              | 38 |

| 4.3.5.     | BUFR_CNFG                                            | 38 |

| 4.3.6.     | HW PARAMS INFO                                       | 39 |

| 4.3.7.     | CTRL                                                 | 39 |

| 4.3.8.     | BUFR TRACKER INFO                                    | 40 |

| 4.3.9.     | BUFR AVAILABILITY INFO                               | 40 |

| 4.3.10.    | BUFR_XCHNG_CTRL                                      | 40 |

| 4.3.11.    | SEL_BUFR_INFO_FOR_FW                                 | 41 |

| 4.3.12.    | TIMESTAMP                                            | 41 |

| 4.3.13.    | VALID_LINES_IN_FRAME                                 | 42 |

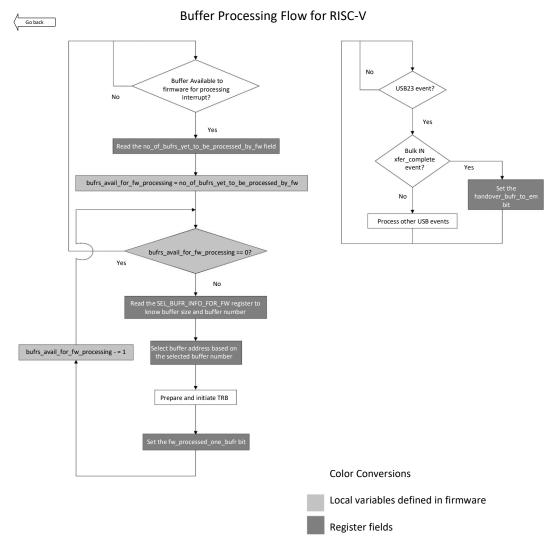

| 4.4.       | N Endpoint Buffer Management Architecture            | 42 |

| 4.5. B     | Suffer Read and Write Management Flow                | 42 |

| 4.5.1.     | Buffer Write Flow                                    | 42 |

| 4.5.2.     | Buffer Read Flow                                     | 43 |

| 4.6. C     | Core Operation                                       | 45 |

| 4.6.1.     | IP Core Configuration or Reconfiguration             | 45 |

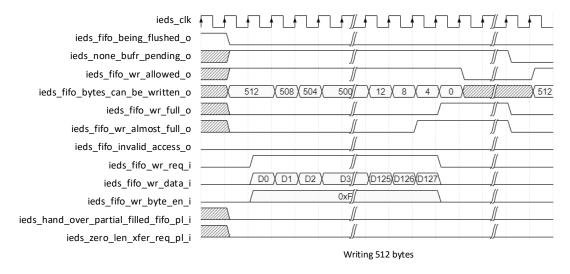

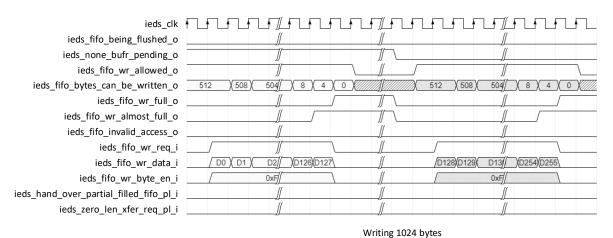

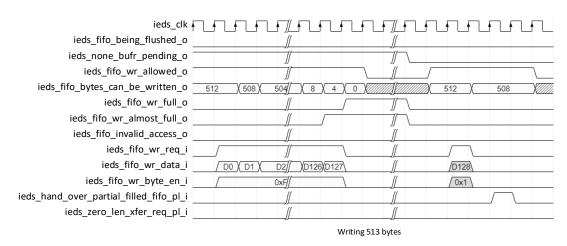

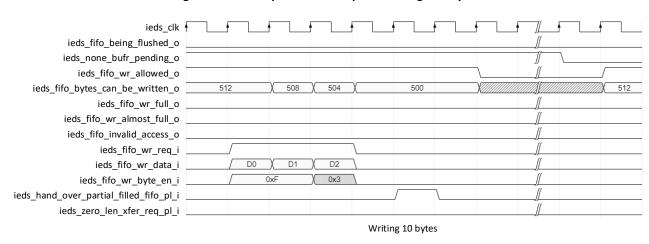

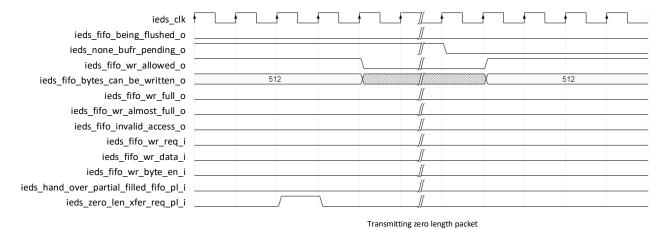

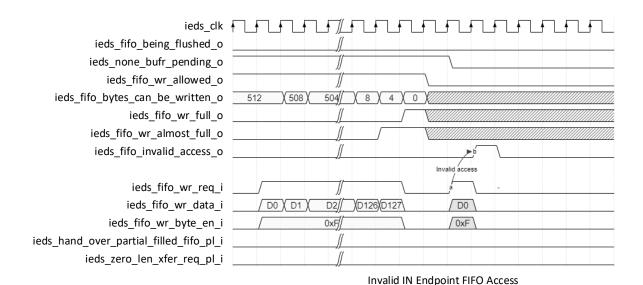

| 4.6.2.     | FIFO Write Operation                                 | 45 |

| 4.6.3.     | FIFO Write Examples                                  | 47 |

| 5. USB23   | AXI Manager to Memory Interface Bridge               | 50 |

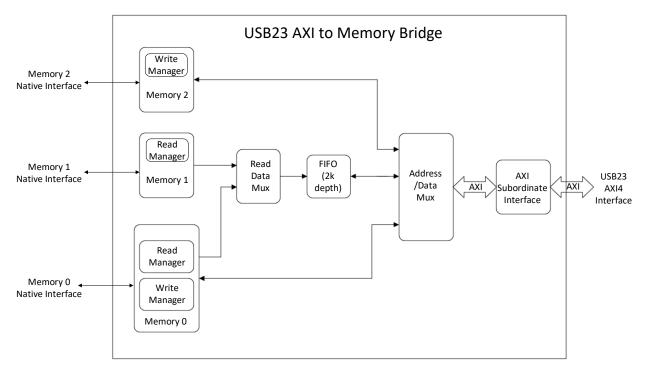

| 5.1. U     | JSB23 AXI Manager to Memory Bridge Architecture      | 50 |

| 5.2. B     | Block Description                                    | 50 |

| 5.2.1.     | AXI Subordinate Interface                            | 50 |

| 5.2.2.     | Address/Data Mux                                     | 50 |

| 5.2.3.     | FIFO                                                 | 50 |

| 5.2.4.     | Read Data Mux                                        | 50 |

| 5.2.5.     | Memory 0                                             | 51 |

| 5.2.6.     | Memory 1                                             | 51 |

| 5.2.7.     | Memory 2                                             | 51 |

| 5.3. IF    | P Core Port and Parameters                           |    |

| 5.3.1.     | Clock and Global Reset                               |    |

| 5.3.2.     | Native Memory Interface                              | 51 |

| 5.3.3.     | AXI4 Interface                                       | 51 |

| 5.3.4.     | Configurable Parameters                              |    |

| 6. UVC Re  | eference Design Signal Description                   | 54 |

| 7. Buildin | g the Reference Design                               | 55 |

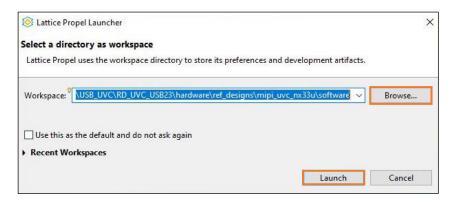

| 7.1. R     | Running Propel SDK Project                           | 55 |

| 7.1.1.     | Opening Propel SDK Project                           | 55 |

| 7.1.2.     | Navigating Propel SDK Project                        | 56 |

| 7.1.3.     | Generating Output MEM file                           |    |

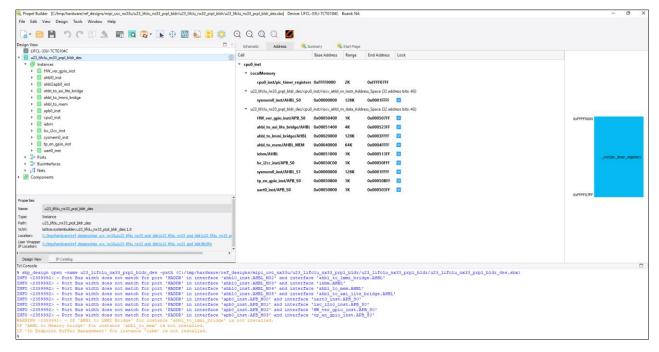

| 7.2. R     | Running Propel Builder Design                        | 58 |

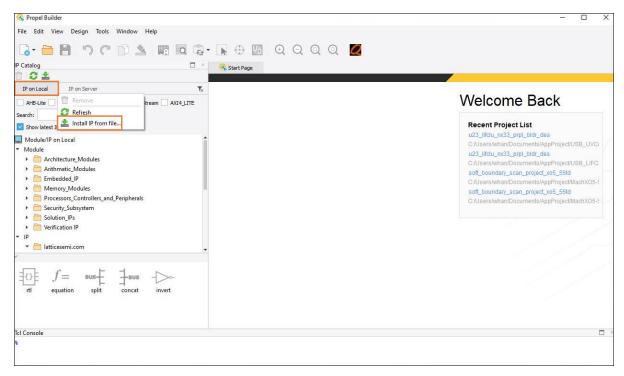

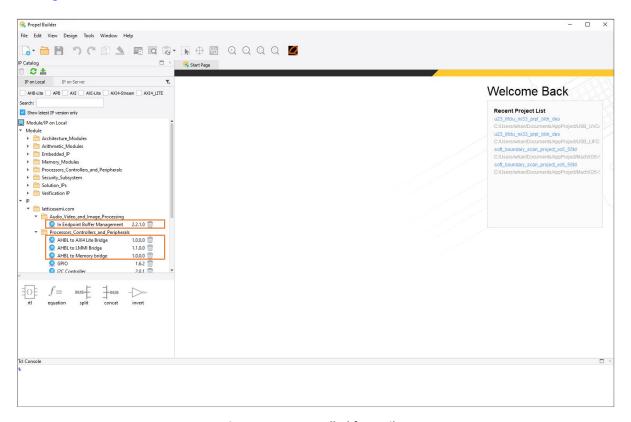

| 7.2.1.     | Install IPs at Local from File                       |    |

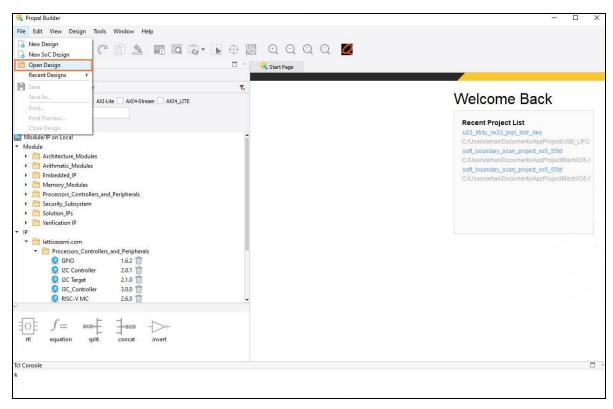

| 7.2.2.     | Opening Propel Builder Design                        | 60 |

| 7.2.3.     | Mapping Design with Firmware                         | 61 |

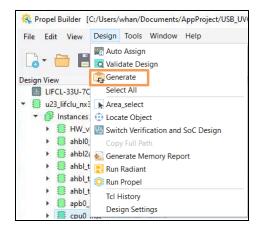

| 7.2.4.     | Exporting Design to Lattice Radiant Software         | 63 |

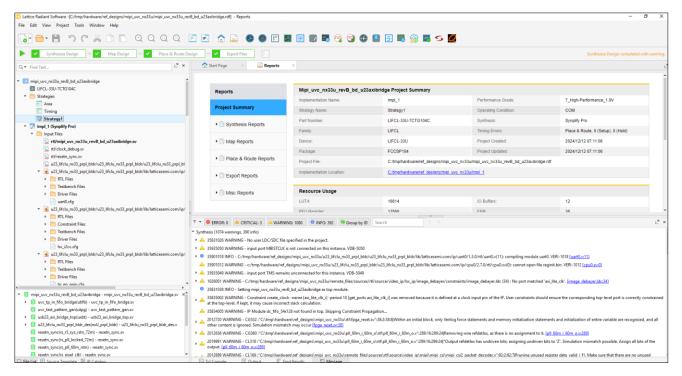

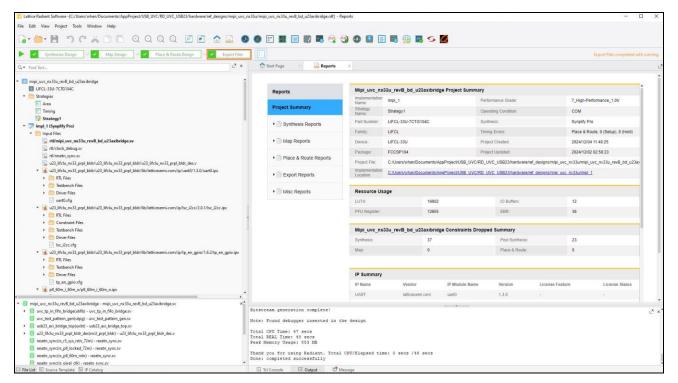

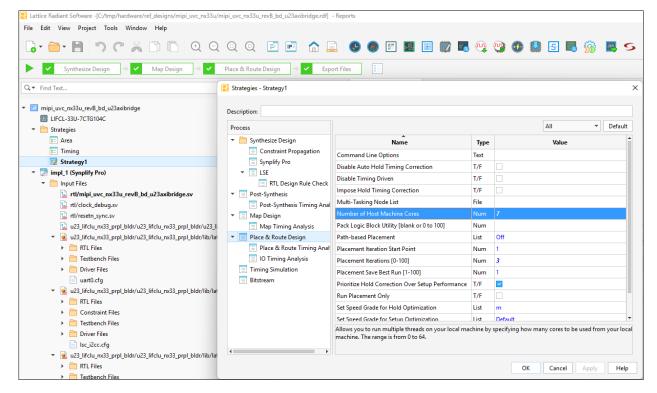

| 7.3. R     | Running Radiant Project                              |    |

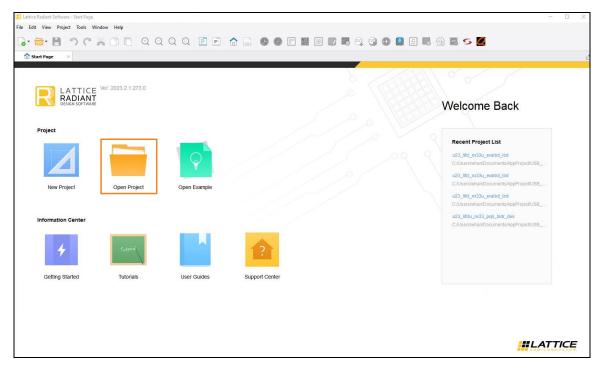

| 7.3.1.     | Opening Radiant Project                              |    |

| 7.3.2.     | Generating Bitstream File                            | 64 |

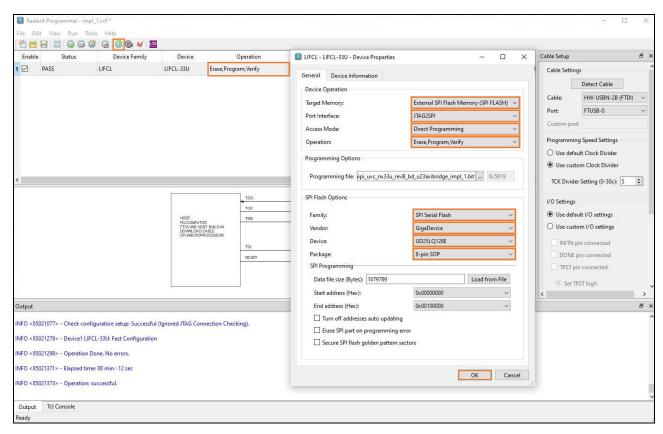

|            | 3U Evaluation Board Programming                      |    |

| 8.1. L     | IFCL-33U Evaluation Board Connection for Programming | 66 |

|            | Radiant Programmer GUI Setup                         |    |

|            | Programming the Evaluation Board                     |    |

| 9. Runnin  | g the Reference Design on Evaluation Board           | 68 |

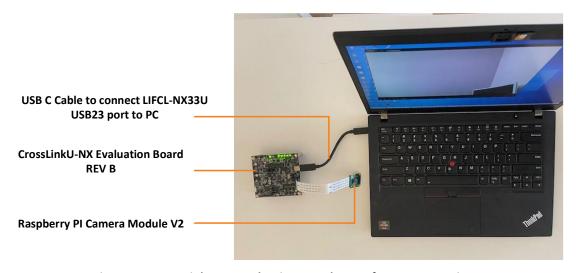

| 9.1. LIFCL-33U Evaluation Board Connection                        | 68 |

|-------------------------------------------------------------------|----|

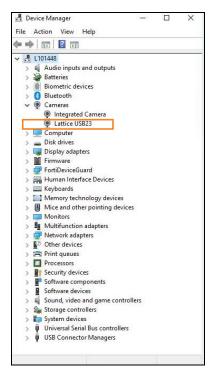

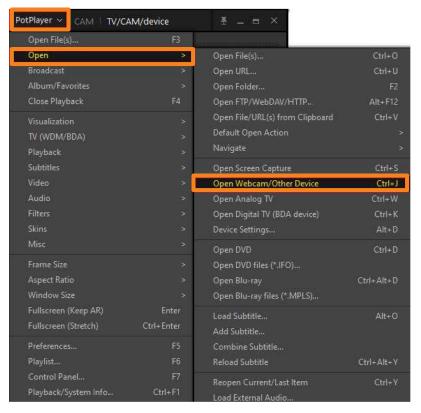

| 9.2. UVC Demonstration                                            | 69 |

| LO. Customizing the Reference Design                              | 72 |

| 10.1. Change the Camera Resolution                                |    |

| 10.1.1. Update the user_cnfg_param.v File                         |    |

| 10.1.2. Update RISC-V Firmware                                    |    |

| 10.1.3. Update Lattice Radiant IP Parameters Configuration        |    |

| 10.2. Steps to Enable YUV422 Test Pattern                         |    |

| 10.3. Steps to Select Memory Type for the In Endpoint Buffer N    | •  |

| 10.3.1. Steps for IEBM Memory Type Selection                      |    |

| 10.3.2. Firmware Modification                                     |    |

| 10.4. Steps to Migrate from the FCCSP104 Package to the WLCS      |    |

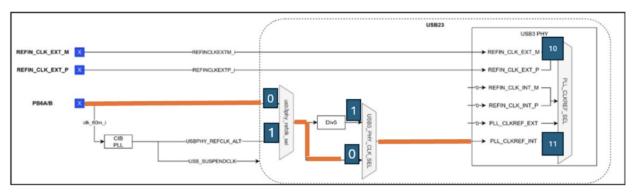

| 10.4.1. Reference Clock Selection for USB Controller              |    |

| 10.4.2. Firmware Configuration                                    |    |

| Appendix A. Resource Utilization                                  |    |

| References                                                        |    |

| Fechnical Support Assistance                                      |    |

| Revision History                                                  | 80 |

|                                                                   |    |

|                                                                   |    |

| Figures                                                           |    |

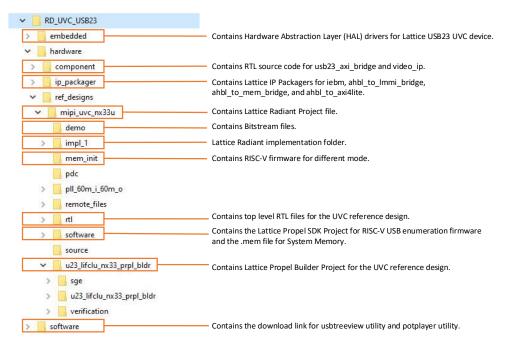

| Figure 2.1. Directory Structure                                   | 11 |

| Figure 3.1. Reference Design Block Diagram                        |    |

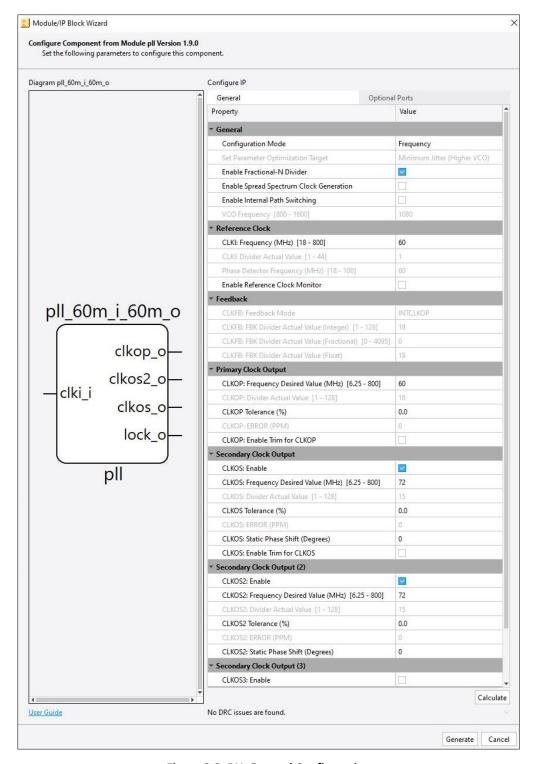

| Figure 3.2. PLL General Configuration                             |    |

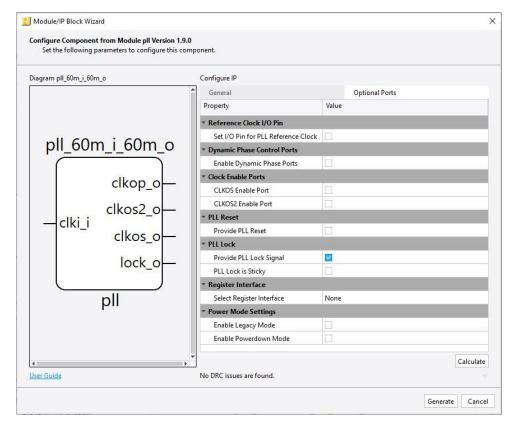

| Figure 3.3. PLL Optional Ports Configuration                      |    |

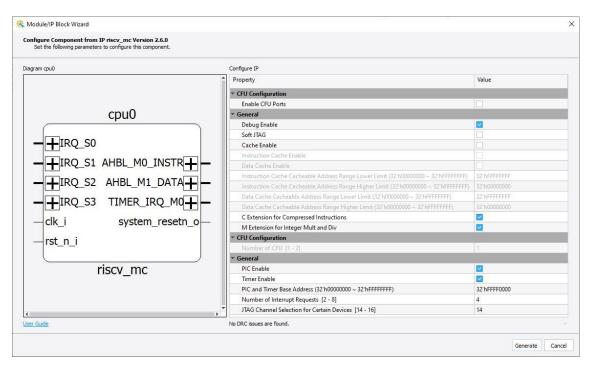

| Figure 3.4. RISC-V MC IP Configuration                            |    |

| Figure 3.5. System Memory General Configuration                   |    |

| Figure 3.6. System Memory Port SO Configuration                   |    |

| Figure 3.7. System Memory Port S1 Configuration                   |    |

| Figure 3.8. UART Configuration                                    |    |

| Figure 3.9. Hardware Version GPIO Configuration                   |    |

| Figure 3.10. Test Pattern Enable GPIO Configuration               |    |

| Figure 3.11. Lattice I2C Controller Configuration                 |    |

| Figure 3.12. AHB-Lite Interconnect General Configuration          | 19 |

| Figure 3.13. AHB-Lite Interconnect Main Configuration             |    |

| Figure 3.14. AHB-Lite Interconnect Manager Priority Setting       | 21 |

| Figure 3.15. AHB-Lite Interconnect Max Burst Setting              |    |

| Figure 3.16. APB Interconnect General Configuration               | 23 |

| Figure 3.17. APB Interconnect Main Settings Configuration         | 24 |

| Figure 3.18. APB-Lite to APB Converter Configuration              | 25 |

| Figure 3.19. RX DPHY General Configuration                        | 25 |

| Figure 3.20. RX DPHY RX FIFO Configuration                        | 26 |

| Figure 3.21. RX DPHY Soft PHY Configuration                       | 26 |

| Figure 3.22. Byte to Pixel IP Configuration                       | 27 |

| Figure 3.23. Debayer Configuration                                |    |

| Figure 3.24. Debayer Test Parameters Configuration                |    |

| Figure 3.25. Color Correction Matrix Configuration                |    |

| igure 3.26. Color Space Converter Input/Coefficient Configuration |    |

| Figure 3.27. Color Space Converter Output Configuration           |    |

| igure 3.28. IEBM IP Configuration                                 |    |

| Figure 3.29. Reference Design Clock Domain Block Diagram          |    |

| Figure 3.30. Reference Design Reset Scheme Diagram                |    |

| Figure 4.1. IN Endpoint Buffer Management Block Diagram           | 42 |

|                                                                   |    |

| Figure 4.2. Buffer Write Operation Flow                                        | 43 |

|--------------------------------------------------------------------------------|----|

| Figure 4.3. Buffer Read Operation Flow                                         | 44 |

| Figure 4.4. FIFO Operation Example – Writing 512 Bytes                         | 47 |

| Figure 4.5. FIFO Operation Example – Writing 1024 Bytes                        | 47 |

| Figure 4.6. FIFO Operation Example – Writing 513 Bytes                         | 48 |

| Figure 4.7. FIFO Operation Example – Writing 10 Bytes                          | 48 |

| Figure 4.8. FIFO Operation Example – Zero Length Packet Request                |    |

| Figure 4.9. FIFO Operation Example – Invalid IN FIFO Access                    |    |

| Figure 5.1. USB23 AXI Bridge to Memory Bridge Architecture                     |    |

| Figure 7.1. Launch Lattice Propel SDK                                          |    |

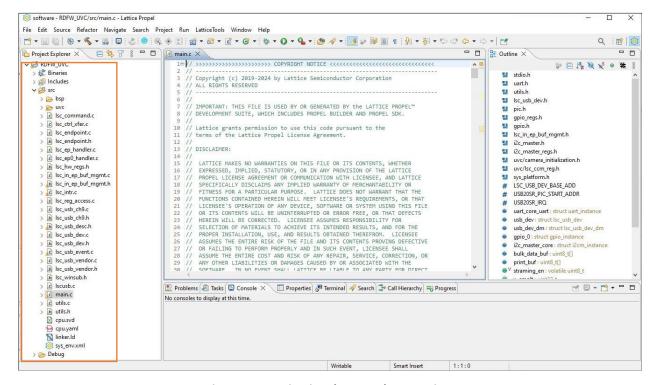

| Figure 7.2. Propel SDK Project Opened in Lattice Propel SDK                    |    |

| Figure 7.3. Navigating the Propel SDK Project                                  |    |

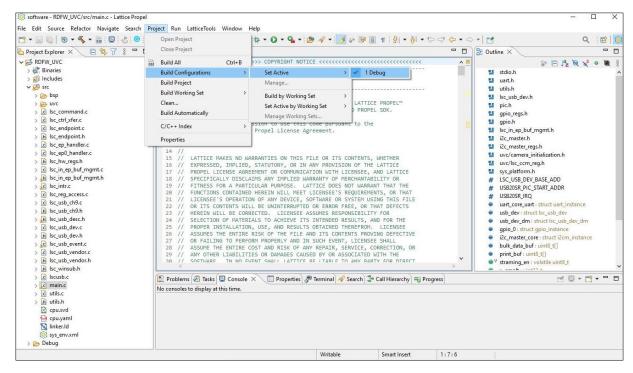

| Figure 7.4. Set Propel Build Configuration Mode                                |    |

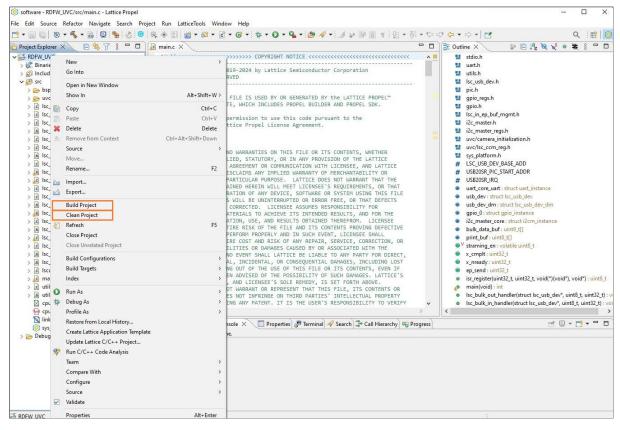

| Figure 7.5. Launch the Project Building Process                                |    |

| Figure 7.6. Install IP from File                                               |    |

| Figure 7.7. Accept IP License Agreement                                        |    |

| Figure 7.8. IPs Installed from Files                                           |    |

| Figure 7.9. Open the Propel Builder Design                                     |    |

| Figure 7.10. Opening System Memory Module Block Wizard                         |    |

| Figure 7.11. Mapping the System Memory Initialization File                     |    |

| Figure 7.12. Base Address Assignment                                           |    |

| Figure 7.13. Export the Propel Builder Design to Radiant Software              |    |

| Figure 7.14. Lattice Radiant Software<br>Figure 7.15. Open the Radiant Design  |    |

|                                                                                |    |

| Figure 7.16. Generated Bitstream LogFigure 7.17. Place & Route Design Strategy |    |

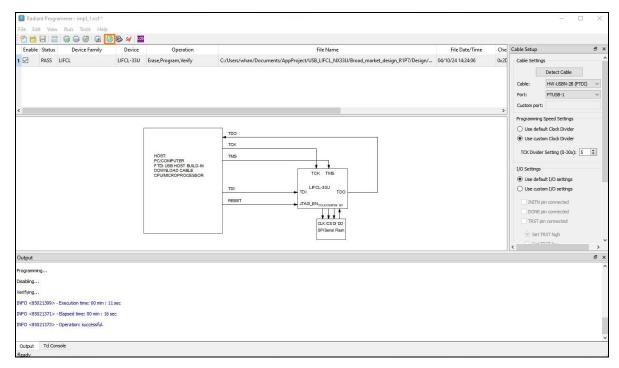

| Figure 8.1. Radiant Programmer GUI                                             |    |

| Figure 8.2. Program the Device                                                 |    |

| Figure 9.1. CrossLinkU-NX Evaluation Board Setup for Demonstration             |    |

| Figure 9.2. USB Enumeration                                                    |    |

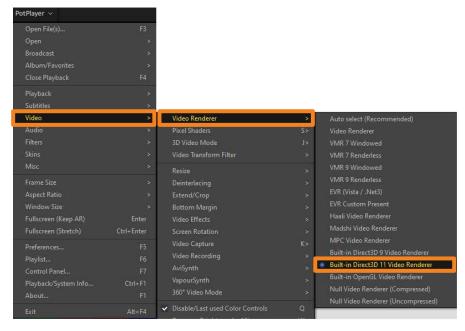

| Figure 9.3. Open Webcam/Other Device in PotPlayer                              |    |

| Figure 9.4. Video Output on PotPlayer                                          |    |

| Figure 9.5. Video Renderer Option                                              |    |

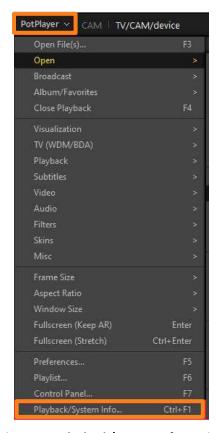

| Figure 9.6. Playback/System Information                                        |    |

| Figure 9.7. Example of Video Information                                       |    |

| Figure 10.1. User Configuration Parameter File                                 |    |

| Figure 10.2. Camera PLL Configurations                                         |    |

| Figure 10.3. Camera PLL Configurations                                         |    |

| Figure 10.4. Firmware Code to Enable the UYV422 Test Pattern                   |    |

| Figure 10.5. Firmware Configurable Registers                                   |    |

| Figure 10.6. USB Reference Clock Selection                                     |    |

|                                                                                |    |

|                                                                                |    |

|                                                                                |    |

|                                                                                |    |

| Tables                                                                         |    |

| Table 1.1. Summary of the Reference Design                                     | 0  |

| Table 2.1. File List                                                           |    |

| Table 4.1. AHB-Lite Subordinate Interface                                      |    |

| Table 4.2. AXI Subordinate Interface                                           |    |

| Table 4.3. FIFO Interface                                                      |    |

| Table 4.4. Miscellaneous Ports                                                 |    |

| Table 4.5. User Configurable Parameters                                        |    |

|                                                                                |    |

| Table 4.6. IEBM Register Offset Map                     | 36 |

|---------------------------------------------------------|----|

| Table 4.7. IP_VERSION, Offset = 0x00                    | 37 |

| Table 4.8. SCRATCH, Offset = 0x04                       | 37 |

| Table 4.9. INT_EN, Offset = 0x08                        | 37 |

| Table 4.10. INT_SRC, Offset = 0x0C                      | 38 |

| Table 4.11. BUFR_CNFG, Offset = 0x10                    | 38 |

| Table 4.12. HW_PARAMS_INFO, Offset = 0x14               | 39 |

| Table 4.13. CTRL, Offset = 0x18                         | 39 |

| Table 4.14. BUFR_TRACKER_INFO, Offset = 0x1C            | 40 |

| Table 4.15. BUFR_AVAILABILITY_INFO, Offset = 0x20       | 40 |

| Table 4.16. BUFR_XCHNG_CTRL, Offset = 0x24              | 40 |

| Table 4.17. SEL_BUFR_INFO_FOR_FW, Offset = 0x28         | 41 |

| Table 4.18. TIMESTAMP_W0, Offset = 0x30                 | 41 |

| Table 4.19. TIMESTAMP_W0, Offset = 0x34                 |    |

| Table 4.20. BUFR_XCHNG_CTRL (Offset = 0x24)             | 42 |

| Table 4.21. Input Ports Related to FIFO Write Operation | 45 |

| Table 5.1. Clock and Reset Ports                        | 51 |

| Table 5.2. Native Memory Interface Ports                | 51 |

| Table 5.3. AXI4 Interface Ports                         |    |

| Table 5.4. User Configurable Parameters                 | 53 |

| Table 6.1. Primary I/O                                  | 54 |

| Table A.1. Resource Utilization for LIFCL-33U-9CTG104C  | 77 |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviations    | Definition                                  |

|------------------|---------------------------------------------|

| AXI4             | Advanced Extensible Interface 4             |

| AHB              | Advanced High-Performance Bus               |

| AHB-Lite         | Advanced High-Performance Bus – Lite        |

| APB              | Advanced Peripheral Bus                     |

| ВТР              | Byte to Pixel                               |

| CCM              | Color Correction Matrix                     |

| CPU              | Central Processing Unit                     |

| CSI-2            | Camera Serial Interface 2                   |

| DMA              | Direct Memory Access                        |

| FIFO             | First In First Out                          |

| FPGA             | Field Programmable Gate Array               |

| FPS              | Frame Per Second                            |

| GPIO             | General Purpose Input/Output                |

| HAL              | Hardware Abstraction Layer                  |

| IEBM             | In Endpoint Buffer Manager                  |

| IEDS             | In Endpoint Data Source                     |

| I <sup>2</sup> C | Inter-Integrated Circuit                    |

| INT              | Interrupt                                   |

| IP               | Intellectual Property                       |

| IRQ              | Interrupt Request                           |

| ISP              | Image Signal Processing                     |

| LED              | Light Emitting Diode                        |

| LMMI             | Lattice Memory Mapped Interface             |

| MC               | Microcontroller                             |

| MIPI             | Mobile Industry Processor Interface         |

| PC               | Personal Computer                           |

| PLL              | Phase-Locked Loop                           |

| RAM              | Random Access Memory                        |

| RGB              | Red Green Blue                              |

| RISC-V           | Reduced Instruction Set Computer – Five     |

| RTL              | Register Transfer Level                     |

| SCL              | Serial Clock Line                           |

| SDA              | Serial Data Line                            |

| SPI              | Serial Peripheral Interface                 |

| TDP              | True Dual Port                              |

| TRB              | Transfer Request Block                      |

| UART             | Universal Asynchronous Receiver/Transmitter |

| USB              | Universal Serial Bus                        |

|                  | USB Video Class                             |

## 1. Introduction

The Lattice Semiconductor CrosslinkU™-NX USB Video Class (UVC) reference design provides you with a template for video streaming from a camera sensor, utilizing the USB hard IP in a CrosslinkU-NX device.

## 1.1. Quick Facts

Download the reference design files from the UVC reference design web page.

Table 1.1. Summary of the Reference Design

| Comment               | Target Devices            | LIFCL-33U                                           |

|-----------------------|---------------------------|-----------------------------------------------------|

| General               | Source Code Format        | C code, RTL                                         |

|                       | Functional Simulation     | Not supported.                                      |

| Simulation            | Timing Simulation         | Not supported.                                      |

|                       | Hardware Validation       | Fully validated.                                    |

|                       |                           | Lattice Propel™ SDK 2024.2                          |

|                       | Software Tool and Version | Lattice Propel Builder 2024.2                       |

|                       | Software roof and version | Lattice Radiant™ Software Version 2024.2            |

|                       |                           | Lattice Radiant Programmer Version 2024.2           |

|                       |                           | RISC-V MC Version 2.7.0                             |

|                       |                           | System Memory Version 2.3.0                         |

|                       | Propel Soft IP Version    | AHB-Lite Interconnect Version 1.3.2                 |

|                       |                           | AHB-Lite to APB Bridge Version 1.1.2                |

| Software Requirements |                           | AHB-Lite Feedthrough Version 1.0.0                  |

| Software Requirements |                           | APB Interconnect Version 1.2.1                      |

|                       |                           | GPIO Version 1.6.2                                  |

|                       |                           | I2C Controller Version 2.0.1                        |

|                       |                           | UART Version 1.3.0                                  |

|                       |                           | Byte to Pixel Converter Version 1.7.0               |

|                       |                           | Color Space Converter Version 2.2.0                 |

|                       | Radiant Soft IP Version   | Debayer Version 1.2.2                               |

|                       |                           | CSI-2/DSI D-PHY Receiver Version 1.7.0              |

|                       |                           | FIFO_DC Version 2.3.0                               |

|                       | Board                     | LIFCL-33U-EVN Evaluation Board REV-B                |

| Hardwara Baguiramanta | Camera Sensor             | Raspberry PI Camera Module V2                       |

| Hardware Requirements | Cable                     | USB C to USB C cable, or USB C to USB A 9-pin cable |

|                       | Cable                     | USB A to Micro USB cable                            |

## 1.2. Features

Key features of the CrosslinkU-NX USB Video Class reference design include:

- Soft Mobile Industry Processor Interface (MIPI) D-PHY and Camera Serial Interface (CSI-2) for image sensor aggregation. The Lattice Semiconductor D-PHY Receiver IP converts CSI-2 data to 8-bit data.

- The Lattice Semiconductor Byte-to-Pixel Converter IP converts CSI-2 standard based video payload packets from the D-PHY Receiver module output to pixel format.

- The Lattice Semiconductor Debayer IP converts raw image data into an RGB image.

- Hardware USB IP for USB video class to stream the video from the image sensor to a PC through USB Type C connector.

- This reference design primarily targets the Raspberry PI Camera Module 2.

Refer to https://www.raspberrypi.com/products/camera-module-v2/ for more information.

FPGA-RD-02306-1.1

## 1.3. Naming Conventions

## 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.3.2. Signal Names

- \_n are active low, asserted when value is logic 0.

- \_i are input signals.

- \_o are output signals.

# 2. Directory Structure and Files

Figure 2.1 shows the directory structure.

Figure 2.1. Directory Structure

Table 2.1 shows the list of files included in the reference design package.

Table 2.1. File List

| TODIC EIET THE EIGT                                                                             |                                                                                 |  |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| Attribute                                                                                       | Description                                                                     |  |  |

| <component name="">.ipx</component>                                                             | This file contains the information on the files associated to the generated IP. |  |  |

| <component name="">.cfg</component>                                                             | This file contains the parameter values used in IP configuration.               |  |  |

| component.xml                                                                                   | Contains the ipxact:component information of the IP.                            |  |  |

| design.xml                                                                                      | Documents the configuration parameters of the IP in IP-XACT 2014 format.        |  |  |

| rtl/ <component name="">.v</component>                                                          | This file provides an example RTL top file that instantiates the module.        |  |  |

| rtl/ <component name="">_bb.v</component>                                                       | This file provides the synthesis closed box.                                    |  |  |

| misc/ <component name="">_tmpl.v<br/>misc /<component name="">_tmpl.vhd</component></component> | These files provide instance templates for the module.                          |  |  |

# 3. Functional Description

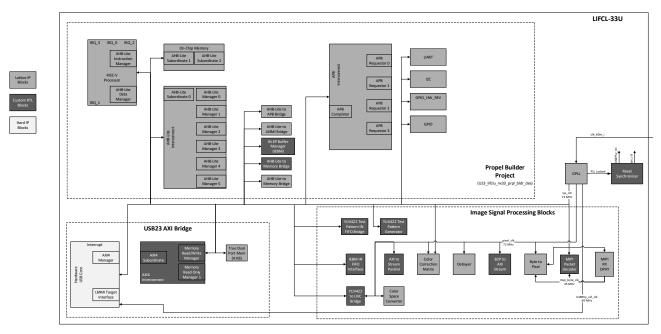

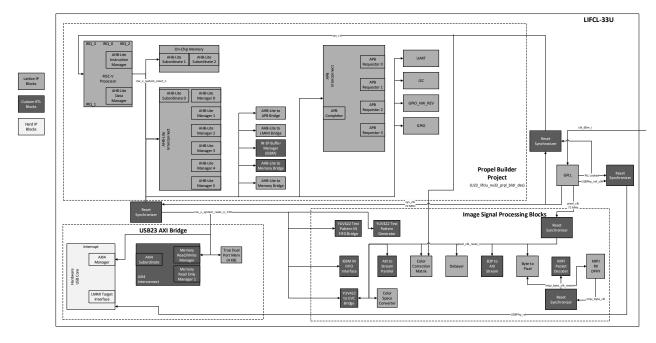

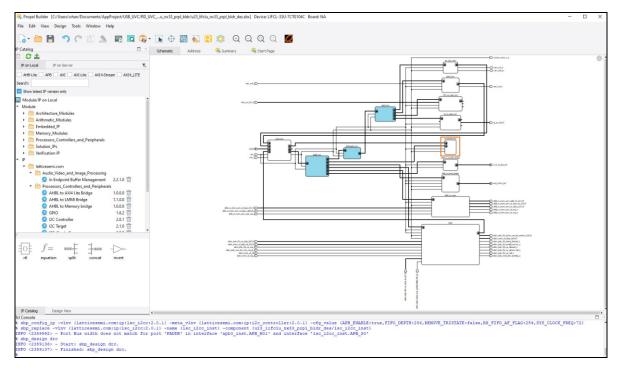

The top-level block diagram of the CrosslinkU-NX USB Video Class reference design is shown in Figure 3.1 below.

Figure 3.1. Reference Design Block Diagram

## 3.1. Design Components

The CrosslinkU-NX USB Video Class reference design includes blocks described in the following sections, from PLL to YUV422 Test Pattern In FIFO Bridge.

### 3.1.1. PLL

To operate some modules, a 60 MHz clock and a 72 MHz clock are needed. These clock signals can be generated from a 60 MHz input clock produced by the on-board crystal oscillator, and a Phase-Locked Loop (PLL) is utilized to do this. The PLL generates the 60 MHz clock and a 72 MHz clock signals, which are then routed to the submodules for further processing. MIPI RX-DPHY and the whole system operate at 72 MHz. USB23 PHY operates at 60 MHz PLL clock and all the Image Signal Processing (ISP) blocks operate on the MIPI byte clock.

Figure 3.2 and Figure 3.3 show the general and optional ports configuration of the PLL IP.

Figure 3.2. PLL General Configuration

Figure 3.3. PLL Optional Ports Configuration

#### 3.1.2. USB23 Controller

This is the USB23 Device Controller hardened IP. This IP communicates with the system memory through the Advanced eXtensible Interface 4 (AXI4) to Advanced High-Performance Bus – Lite (AHB-Lite) convertor module.

The AXI Direct Memory Access (DMA) Controller of the USB23 Controller is connected to two different memories through the AXI Interconnect Bridge.

- For Bulk transfer, the USB controller fetches data from the In Endpoint Buffer Manager (IEBM) module's data Random Access Memory (RAM). This RAM is not shared with any other controller and/or RISC-V processor.

- For all other operations, the USB controller talks to the system memory, which is shared with the RISC-V processor.

This kind of architecture helps to achieve higher Bulk throughput.

#### 3.1.3. AHB-Lite to LMMI Converter

The USB23 controller register interface can be configured through its Lattice Memory Mapped Interface (LMMI). Since RISC-V MC supports only the AHB-Lite interface, we need an AHB-Lite to LMMI converter.

#### 3.1.4. RISC-V Microcontroller

All the serial peripheral blocks are connected to the RISC-V MC soft processor through the AHB-Lite interface. The RISC-V MC CPU IP processes data and instructions while monitoring external interrupts coming from the USB23 controller and IEBM core. The RISC-V MC processor configuration is shown in Figure 3.4 below.

Figure 3.4. RISC-V MC IP Configuration

## 3.1.5. System Memory

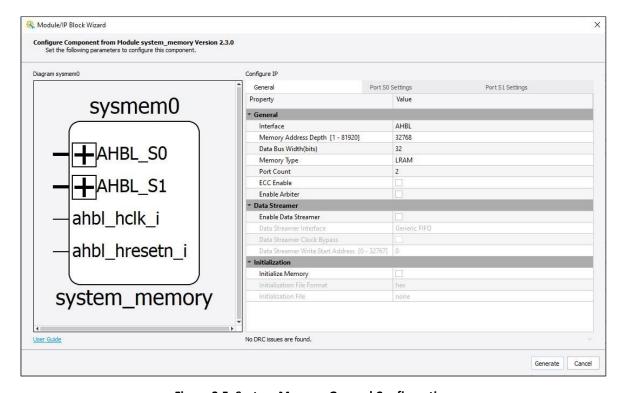

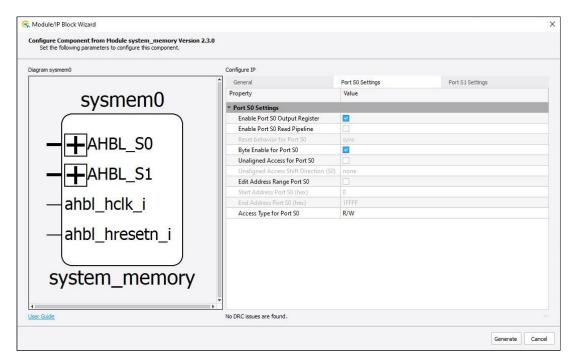

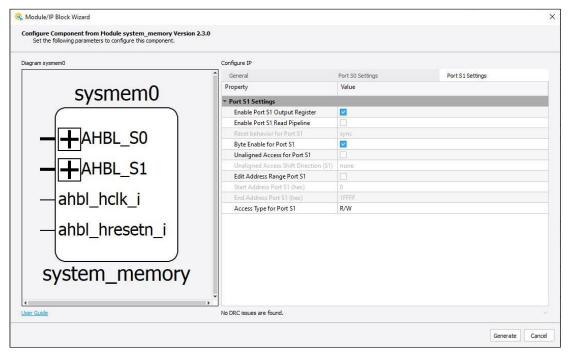

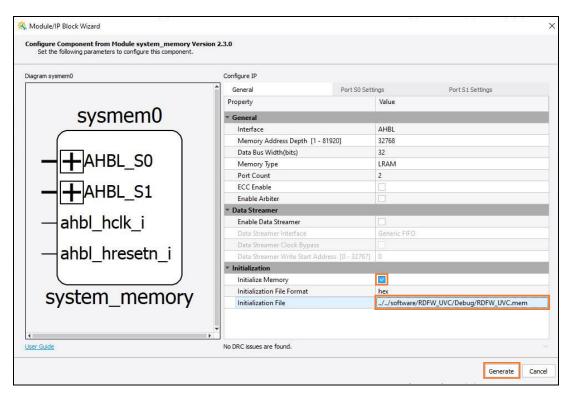

This IP is a soft IP for memory which is used by the RISC-V MC processor. The processor reads the instructions stored in this memory through the AHB-Lite interface and takes actions accordingly. This IP has two interfaces, AHB-Lite and AXI4, through which the manager can communicate with it. The AHB-Lite interface is used to communicate with the RISC-V processor. The System Memory IP configuration is shown in Figure 3.5, Figure 3.6, and Figure 3.7.

Figure 3.5. System Memory General Configuration

Figure 3.6. System Memory Port SO Configuration

Figure 3.7. System Memory Port S1 Configuration

#### 3.1.6. UART

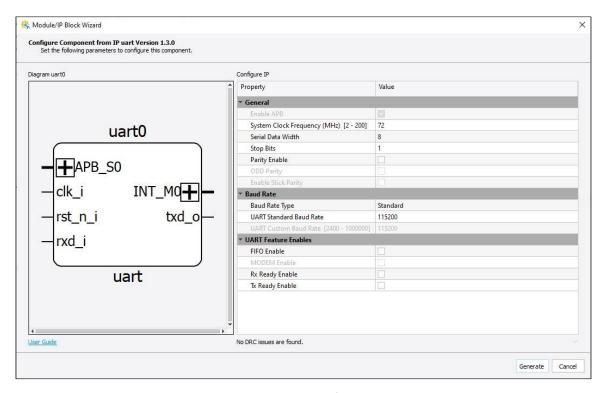

The RISC-V MC processor can communicate with the UART and GPIO cores through its Advanced Peripheral Bus (APB) interface. Hence, the UART and GPIO cores are connected to the soft processor through the AHB-Lite to APB Bridge. Generally, the UART IP performs serial-to-parallel conversion on data characters received from a peripheral UART device. The IP performs parallel-to-serial conversion on data characters received from the host through an APB interface. In this reference design, the host is the RISC-V processor inside the FPGA. The UART IP configuration is shown in Figure 3.8.

Figure 3.8. UART Configuration

## 3.1.7. GPIO

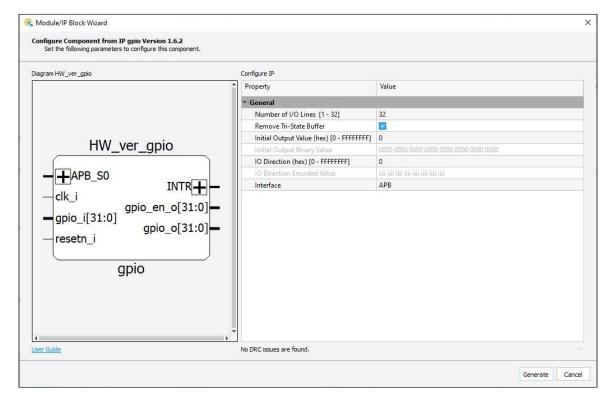

There is a 32-bit input GPIO, the hardware version GPIO, to monitor the FPGA design version for a particular release. The hardware version GPIO IP configuration is shown in Figure 3.9.

Figure 3.9. Hardware Version GPIO Configuration

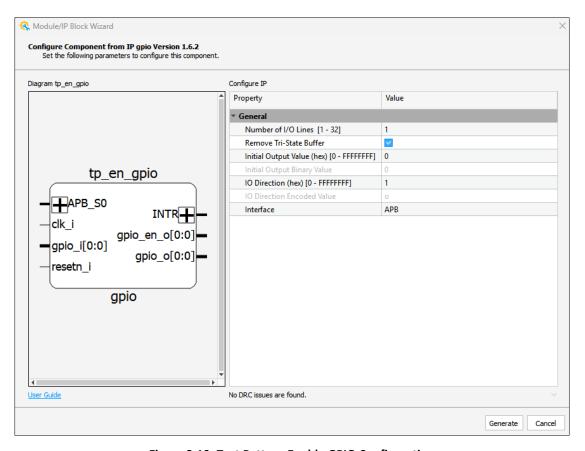

Also, there is a 2-bit output GPIO, that is, the test pattern enable GPIO. This GPIO is used to select the data either from the camera sensor RX DPHY or MIPI RAW10 Test Pattern Generator, and Image Signal Processing stream or YUV422 Test Pattern Generator. The test pattern enable GPIO IP configuration shown in Figure 3.10.

Figure 3.10. Test Pattern Enable GPIO Configuration

## 3.1.8. Lattice I2C Controller

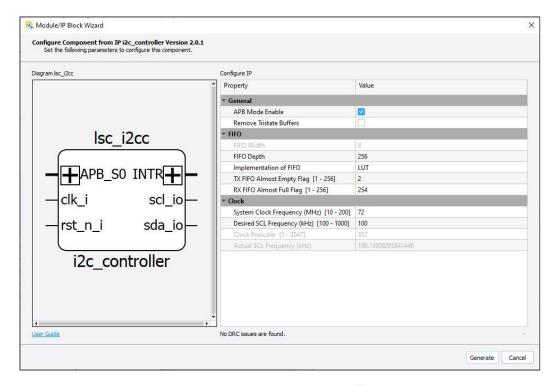

This is a Lattice I2C Controller IP used to communicate with any I2C target device. With this IP, you can perform I2C write, I2C read, and I2C write followed by read operation on the I2C target device connected to it. In this design, the RISC-V MC processor configures the MIPI Camera Sensor register through this I2C Controller IP. The I2C Controller IP configuration is shown in Figure 3.11.

Figure 3.11. Lattice I2C Controller Configuration

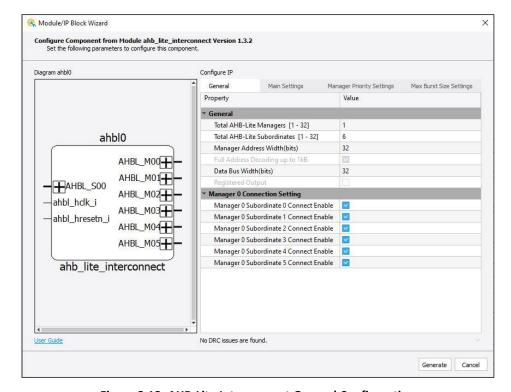

## 3.1.9. AHB-Lite Interconnect

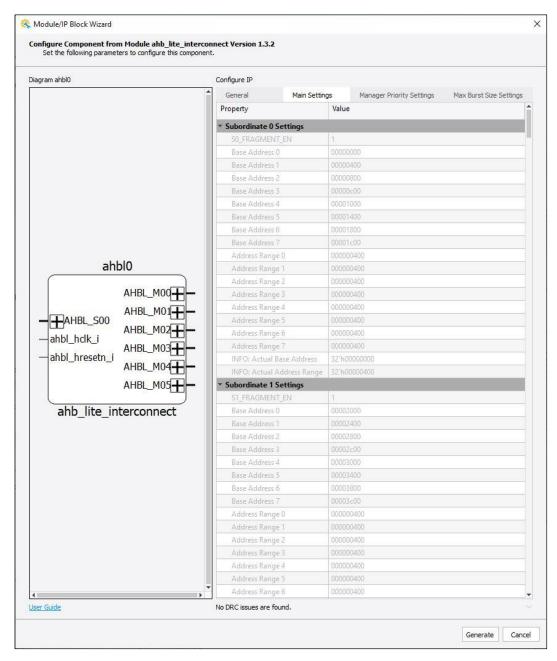

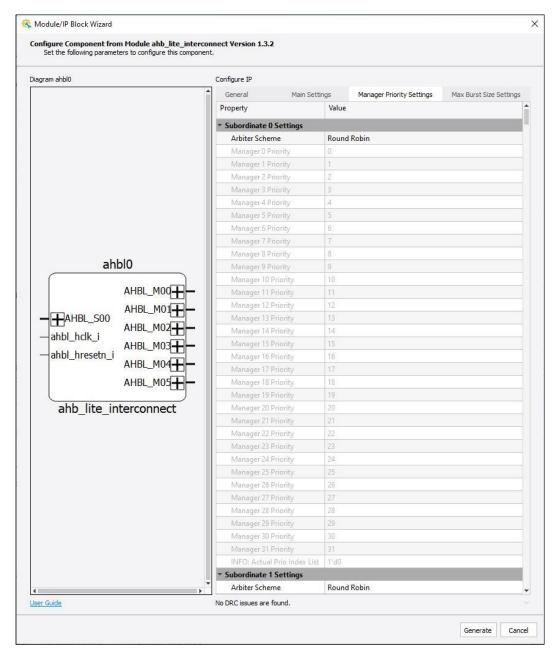

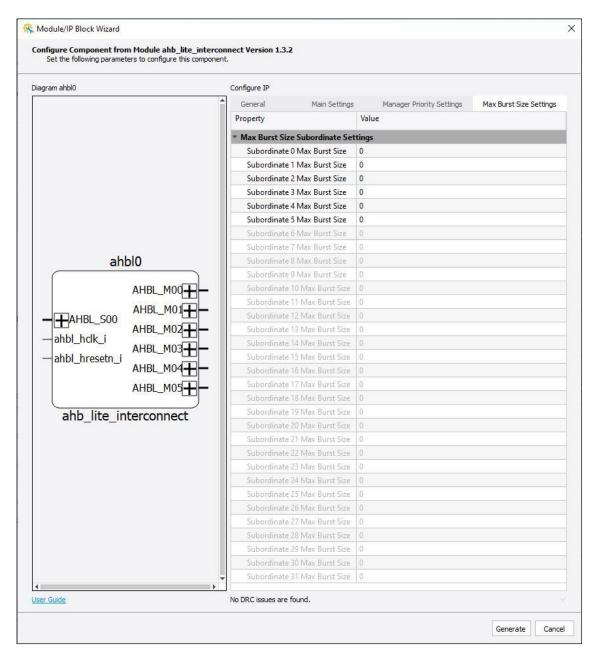

This IP provides the communicating interface between RISC-V soft processor and peripherals that support AHB-Lite interface, such as System Memory and AHB-Lite to LMMI Bridge. The AHB-Lite Interconnect module configuration is shown in the following figures, from Figure 3.12 to Figure 3.15.

Figure 3.12. AHB-Lite Interconnect General Configuration

Figure 3.13. AHB-Lite Interconnect Main Configuration

Figure 3.14. AHB-Lite Interconnect Manager Priority Setting

Figure 3.15. AHB-Lite Interconnect Max Burst Setting

#### 3.1.10. APB Interconnect

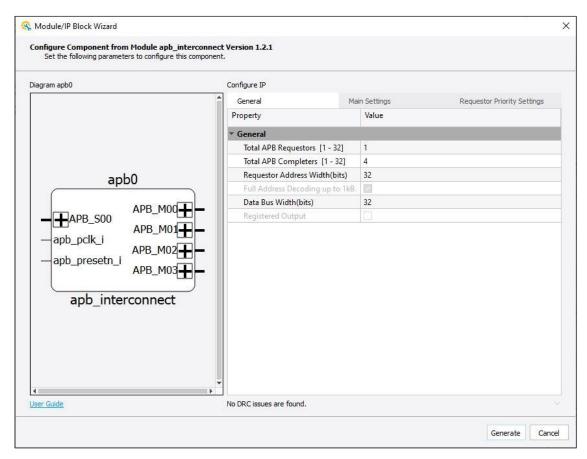

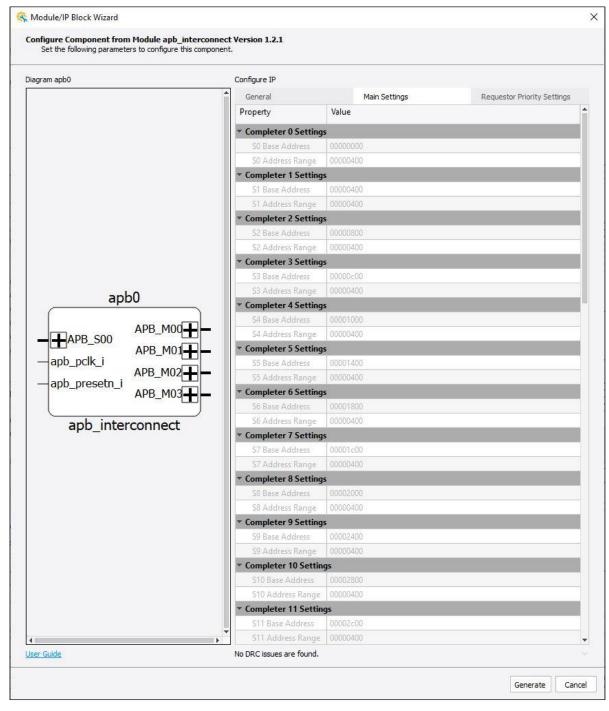

This IP provides the communicating interface between the RISC-V MC soft processor and other slow peripherals that support the APB interface, such as UART and GPIO. APB interconnect configuration is shown in Figure 3.16 and Figure 3.17.

Figure 3.16. APB Interconnect General Configuration

Figure 3.17. APB Interconnect Main Settings Configuration

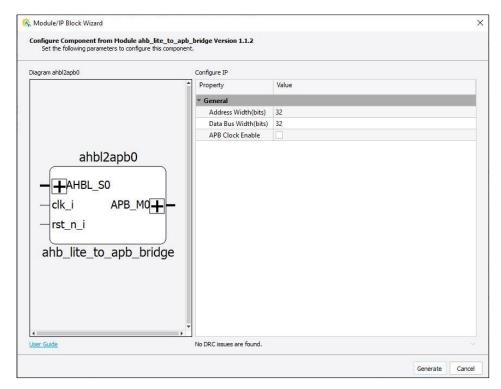

#### 3.1.11. APB-Lite to APB Converter

The AHB-Lite to APB Bridge provides an interface between the AHB-Lite manager and APB completer. Read and write transfers on the AHB are converted into equivalent transfers on the APB. The AHB-Lite to APB Converter IP configuration is shown in Figure 3.18.

Figure 3.18. APB-Lite to APB Converter Configuration

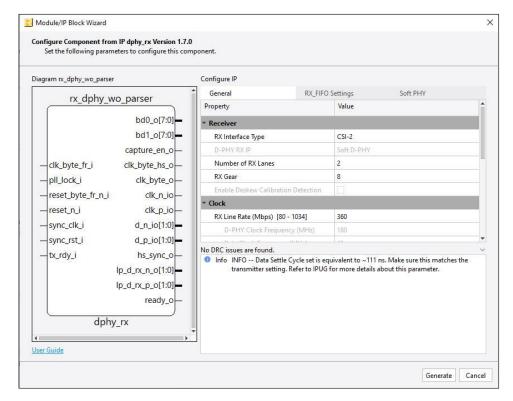

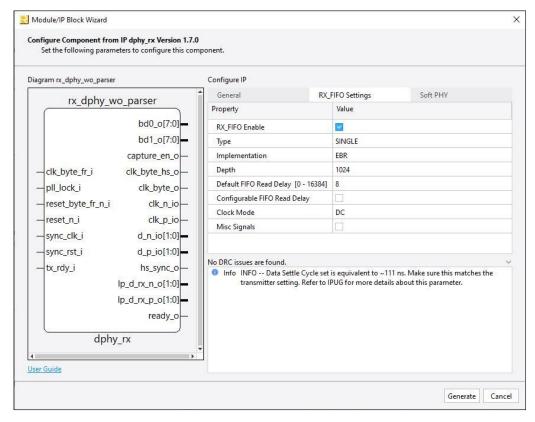

## 3.1.12. RX DPHY

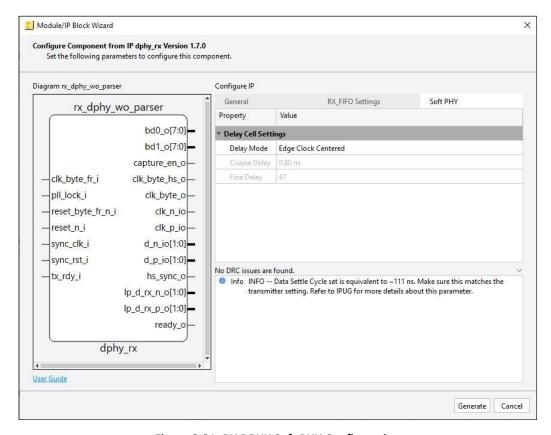

The MIPI camera sensor's data that you receive is in serial form. Hence, this IP converts those serial data into parallel by following the MIPI CSI-2 protocol. The RX DPHY IP configuration is shown in Figure 3.19, Figure 3.20, and Figure 3.21.

Figure 3.19. RX DPHY General Configuration

Figure 3.20. RX DPHY RX FIFO Configuration

Figure 3.21. RX DPHY Soft PHY Configuration

#### 3.1.13. MIPI Packet Decoder

This module decodes the data packet coming from the camera sensor. These packets may include data, control, synchronization, or configuration information. After decoding the packets, the RAW10 data is passed to the Byte to Pixel IP.

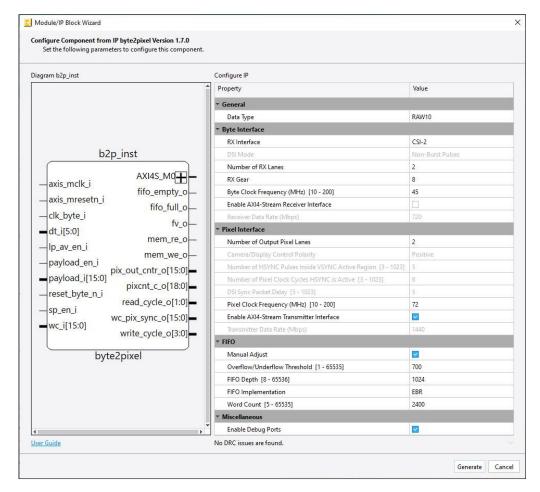

### 3.1.14. Byte to Pixel

This module converts the incoming RAW10 data into the pixel format. It receives raw bytes from a parser and rearranges them to output pixels. This module outputs 2-pixels in one clock cycle with valid signal. Each pixel is of 10-bit. The configuration of the Byte to Pixel IP is shown in Figure 3.22.

Figure 3.22. Byte to Pixel IP Configuration

### 3.1.15. B2P to AXI Stream Conversion

This module converts the pixel data according to the AXI Stream protocol to meet Lattice Debayer AXI Stream input requirement. Therefore, this module acts as a bridge between Lattice Byte to Pixel and Lattice Debayer IPs.

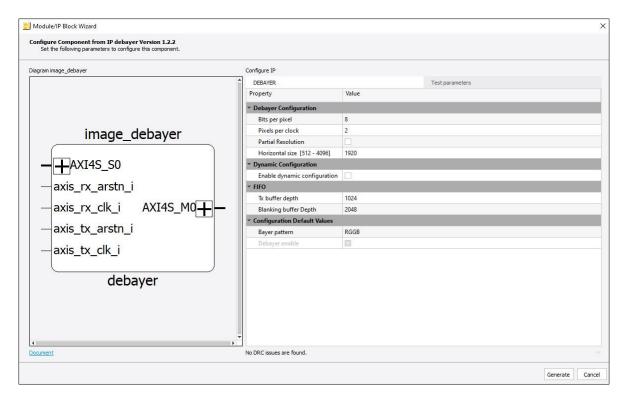

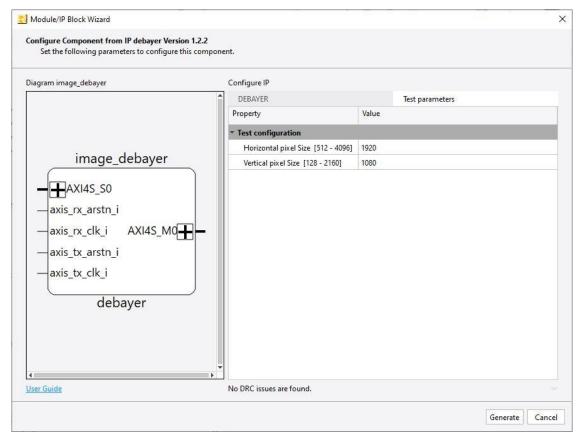

## 3.1.16. Debayer

The image sensor outputs pixel data in the Bayer format. In order to extract the R, G, and B components from Bayer data, we need the Debayer function. The Debayer converts raw10 image data into an RGB component. The Debayer IP configuration is shown in Figure 3.23 and Figure 3.24.

Figure 3.23. Debayer Configuration

Figure 3.24. Debayer Test Parameters Configuration

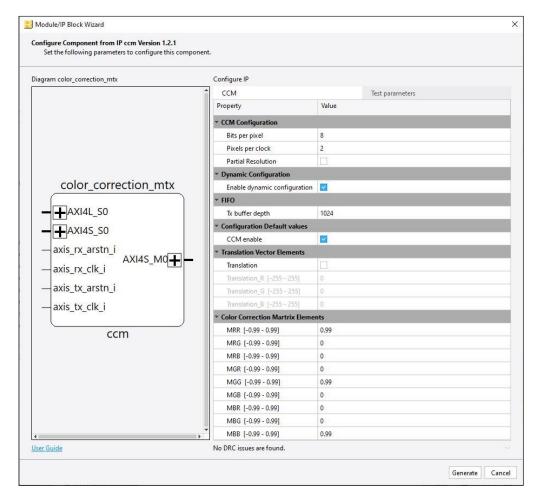

#### 3.1.17. Color Correction Matrix

To obtain the correct colors, the pixels need to be mapped from sensor RGB color space to standard RGB color space. This linear mapping of the color components is achieved by using a 3x3 matrix, called color correction matrix (CCM). The configuration of the CCM IP is shown in Figure 3.25.

Figure 3.25. Color Correction Matrix Configuration

#### 3.1.18. AXI Stream to Parallel Conversion

This module converts the AXI Stream protocol signal to parallel data. In this design, this module acts as a bridge between Lattice Debayer IP and Lattice CSC IP.

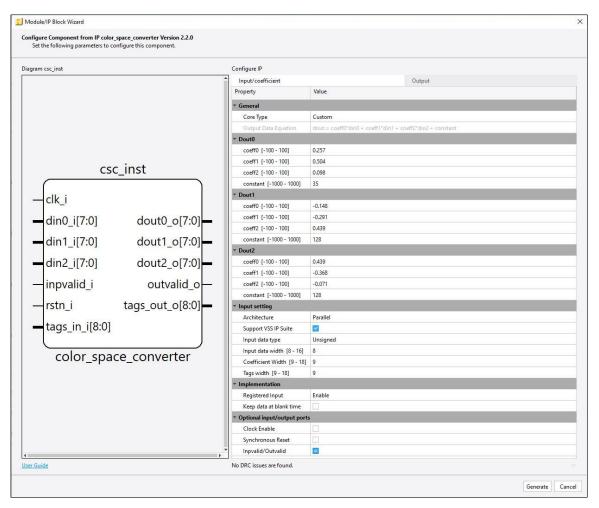

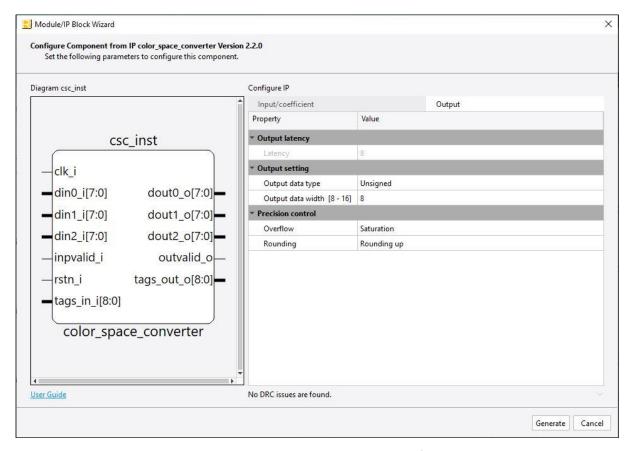

## 3.1.19. Color Space Converter

The Color Space Converter IP block converts RGB data into the YUV format and its configuration is shown in Figure 3.26 and Figure 3.27.

Figure 3.26. Color Space Converter Input/Coefficient Configuration

Figure 3.27. Color Space Converter Output Configuration

#### 3.1.20. YUV422 to UVC Bridge

This module features an internal DC-FIFO called YUV422 FIFO, designed to store incoming YUV422 data along with associated data indicator codes. This write interface of this FIFO works on the pixel clock and the read interface works on the same clock as the IEBM. The YUV422 FIFO plays a critical role in managing and buffering video data, ensuring smooth data flow and processing.

#### 3.1.21. IEBM In FIFO Interface

When the IEBM block grants permission to write the data, the IN FIFO controller module initiates the process. It reads the data from the YUV FIFO, where the video data is temporarily stored. Before writing this data into the IEBM buffers, the IN FIFO controller adds a two-byte UVC header at the start of each frame. Once the header is appended, the combined data, the header plus the YUV data, is written into the IEBM buffers.

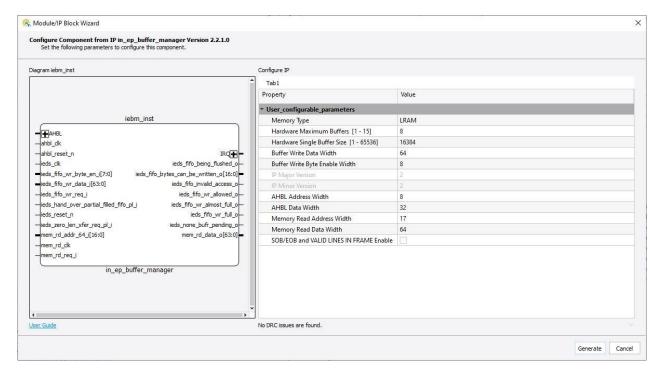

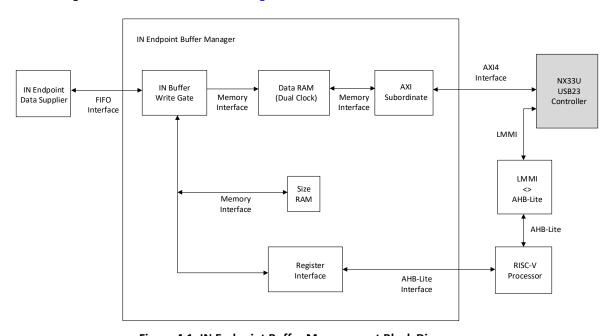

## 3.1.22. In Endpoint Buffer Manager

The IEBM is responsible for managing the IN endpoint buffers for the USB23 controller. It handles the efficient and orderly flow of video data from the camera sensor or a test pattern generator. The data is written into different buffers sequentially through the FIFO interface. Once the data is available in these buffers, the USB23 controller reads it through the AXI interface. The entire process, from managing the FIFO writes to facilitating the AXI reads, is managed by this IEBM module. For more details about IEBM IP, refer to the IN Endpoint Buffer Manager Architecture section.

Figure 3.28. IEBM IP Configuration

## 3.1.23. AHB-Lite to Memory Bridge

This block helps RISC-V data manager to access the True Dual-Port (TDP) memory, which is dedicated for USB operations. This block converts the AHB-Lite subordinate signal into the native memory controller interface signals.

#### 3.1.24. USB23 to AXI Bridge

The USB23 to AXI Bridge block helps the USB23 controller to access various memories. USB23 controller has an AXI manager interface while this block has an AXI subordinate interface. This converts AXI subordinate signals into native memory controller interface signals. This block also acts as a decoder to select appropriate memory-based input address.

#### 3.1.25. RAW10 Test Pattern Generator

This block generates the RAW10 format color bar test pattern.

#### 3.1.26. YUV422 Test Pattern Generator

This block generates the YUV422 solid color test pattern.

#### 3.1.27. YUV422 Test Pattern In FIFO Bridge

This bridge receives the YUV422 solid color pattern from the Video Pattern Generator module, adds UVC header at the start of frame, and writes it into the IEBM buffer when the IEBM module allows for write.

## 3.2. Clocking Scheme

The CrosslinkU-NX USB Video Class Reference Design uses a PLL to generate the 72 MHz system clock, 72 MHz pixel clock for image signal processing, and 60 MHz USBPHY clock. All these clocks are generated from the 60 MHz crystal oscillator on LIFCL-33U Evaluation Board.

## 3.2.1. Clocking Overview

An overview of the CrosslinkU-NX USB Video Class Reference Design clocking scheme is shown in Figure 3.29.

Figure 3.29. Reference Design Clock Domain Block Diagram

## 3.3. Reset Scheme

Synchronize resets are generated for each clock domain from the PLL lock signal and corresponding PLL clock outputs.

## 3.3.1. Reset Overview

An overview of the CrosslinkU-NX USB Video Class Reference Design clocking scheme is shown in Figure 3.30.

Figure 3.30. Reference Design Reset Scheme Diagram

# **IN Endpoint Buffer Manager Architecture**

This section provides technical information about the IEBM IP.

#### **IP Ports and Parameters** 4.1.

This section provides details of the IEBM IP ports and interface.

#### 4.1.1. AHB-Lite Interface

This interface is used to access the registers of the IP. This AHB-Lite subordinate must be connected to the processor. This interface is synchronous to the AHB-Lite clock, ahbl\_clk. Table 4.1 describes ports of the AHB-Lite subordinate interface.

Table 4.1. AHB-Lite Subordinate Interface

| Signal Name      | Width | Direction | Description                                                                                                             |

|------------------|-------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| ahbl_clk         | 1     | Input     | AHB-Lite clock                                                                                                          |

| ahbl_reset_n     | 1     | Input     | AHB-Lite reset, active low                                                                                              |

| ahbl_haddr_i     | 8     | Input     | AHB-Lite address                                                                                                        |

| ahbl_hburst_i    | 3     | Input     | AHB-Lite burst type                                                                                                     |

| ahbl_hmastlock_i | 1     | Input     | AHB-Lite manager lock                                                                                                   |

| ahbl_hprot_i     | 4     | Input     | AHB-Lite protection control                                                                                             |

| ahbl_hready_i    | 1     | Input     | AHB-Lite ready                                                                                                          |

| ahbl_hsel_i      | 1     | Input     | AHB-Lite subordinate select                                                                                             |

| ahbl_hsize_i     | 3     | Input     | AHB-Lite size                                                                                                           |

| ahbl_htrans_i    | 2     | Input     | AHB-Lite transfer type                                                                                                  |

| ahbl_hwdata_i    | 32    | Input     | AHB-Lite write data                                                                                                     |

| ahbl_hwrite_i    | 1     | Input     | AHB-Lite transfer direction. When HIGH, this signal indicates a write transfer. When LOW, it indicates a read transfer. |

| ahbl_hrdata_o    | 32    | Output    | AHB-Lite read data                                                                                                      |

| ahbl_hreadyout_o | 1     | Output    | AHB-Lite ready out, indicates the transfer has finished on the bus.                                                     |

| ahbl_hresp_o     | 1     | Output    | Valid lines in the One Frame register                                                                                   |

## 4.1.2. AXI Interface

This subordinate interface is used to read the data from IP's data memory. This interface is synchronous to the AXI clock, axi clk. Table 4.2 describes ports of the AXI subordinate interface.

Table 4.2. AXI Subordinate Interface

| Table 4.2. Axi Suborullate iliterrace |                |           |                        |

|---------------------------------------|----------------|-----------|------------------------|

| Signal Name                           | Width          | Direction | Description            |

| axi_clk                               | 1              | Input     | AXI clock              |

| axi_reset_n                           | 1              | Input     | AXI reset, active low  |

| axi_to_mem_araddr_i                   | 8 <sup>1</sup> | Input     | AXI Read address       |

| axi_to_mem_arburst_i                  | 2              | Input     | AXI Read burst type    |

| axi_to_mem_arid_i                     | 8              | Input     | AXI Read address ID    |

| axi_to_mem_arlen_i                    | 8              | Input     | AXI Read burst length  |

| axi_to_mem_arsize_i                   | 3              | Input     | AXI Read burst size    |

| axi_to_mem_arvalid_i                  | 1              | Input     | AXI Read address valid |

| axi_to_mem_arready_o                  | 3              | Output    | AXI Read address ready |

| axi_to_mem_awaddr_i                   | 81             | Input     | AXI Write address      |

| axi_to_mem_awburst_i                  | 2              | Input     | AXI Write burst type   |

| axi_to_mem_awid_i                     | 8              | Input     | AXI Write address ID   |

| Signal Name          | Width | Direction | Description              |

|----------------------|-------|-----------|--------------------------|

| axi_to_mem_awlen_i   | 8     | Input     | AXI Write burst length   |

| axi_to_mem_awsize_i  | 3     | Input     | AXI Write burst size     |

| axi_to_mem_awvalid_i | 1     | Input     | AXI Write address valid  |

| axi_to_mem_awready_o | 1     | Output    | AXI Write address ready  |

| axi_to_mem_wdata_i   | 64    | Input     | AXI Write data           |

| axi_to_mem_wlast_i   | 1     | Input     | AXI Write last           |

| axi_to_mem_wstrb_i   | 8     | Input     | AXI Write strobe         |

| axi_to_mem_wvalid_i  | 1     | Input     | AXI Write valid          |

| axi_to_mem_wready_o  | 1     | Output    | AXI Write ready          |

| axi_to_mem_bready_i  | 1     | Input     | AXI Write response ready |

| axi_to_mem_bid_o     | 8     | Output    | AXI Write response ID    |

| axi_to_mem_bresp_o   | 2     | Output    | AXI Write response       |

| axi_to_mem_bvalid_o  | 1     | Output    | AXI Write response valid |

| axi_to_mem_rready_i  | 1     | Input     | AXI Read ready           |

| axi_to_mem_rdata_o   | 64    | Output    | AXI Read data            |

| axi_to_mem_rid_o     | 8     | Output    | AXI Read ID              |

| axi_to_mem_rlast_o   | 1     | Output    | AXI Read last            |

| axi_to_mem_rresp_o   | 2     | Output    | AXI Read response        |

| axi_to_mem_rvalid_o  | 1     | Output    | AXI Read valid           |

#### Note:

1. AXI Address width and data width are configurable. Based on the corresponding selection, this value changes. Depending on the FIFO data width selection, this value also changes. For example, if the selected FIFO data width is 16, this value is 2. If the selected FIFO data width is 32, this value is 4. If the selected FIFO data width is 64, this value is 8.

#### 4.1.3. FIFO Interface

This interface is used to communicate with the external FIFO controller, efm. The external FIFO controller can read or write into the endpoint's buffer using this FIFO interface. This interface is synchronous to the external FIFO controller, clock, efm\_clk. Table 4.3 describes ports of the FIFO interface. Refer to the FIFO Write Operation section for more detail.

Table 4.3. FIFO Interface

| Signal Name                             | Width | Direction | Description                         |

|-----------------------------------------|-------|-----------|-------------------------------------|

| ieds_clk                                | 1     | Input     | External FIFO controller clock      |

| ieds_fifo_wr_req_i                      | 1     | Input     | Write request                       |

| ieds_fifo_wr_data_i                     | 321   | Input     | Write data                          |

| ieds_fifo_wr_byte_en_i                  | 42    | Input     | Byte enable                         |

| ieds_hand_over_partial_filled_fifo_pl_i | 1     | Input     | Partial transfer request pulse      |

| ieds_zero_len_xfer_req_pl_i             | 1     | Input     | Zero length transfer request pulse  |

| ieds_fifo_invalid_access_o              | 1     | Output    | Invalid FIFO access                 |

| ieds_fifo_wr_full_o                     | 1     | Output    | FIFO is full.                       |

| ieds_fifo_wr_almost_full_o              | 1     | Output    | FIFO is almost full.                |

| ieds_fifo_wr_allowed_o                  | 1     | Output    | Write is allowed.                   |

| ieds_none_bufr_pending_o                | 1     | Output    | No buffer is pending.               |

| ieds_fifo_being_flushed_o               | 1     | Output    | FIFO is being flushed.              |

| ieds_fifo_bytes_can_be_written_o        | 10    | Output    | Number of bytes that can be written |

#### Notes:

- 1. FIFO data width is configurable. Based on the corresponding selection, this value changes.

- 2. Depending upon FIFO data width selection, this value changes. For example, if the selected FIFO data width is 16, this value is 2. If the selected FIFO data width is 32, this value is 4. If the selected FIFO data width is 64, this value is 8.

## 4.1.4. Miscellaneous Ports

Table 4.4 describes the miscellaneous ports of the IP.

**Table 4.4. Miscellaneous Ports**

| Signal Name             | Width | Direction | Description                                  |

|-------------------------|-------|-----------|----------------------------------------------|

| timestamp_i             | 64    | Input     | Timestamp value                              |

| valid_lines_per_frame_i | 13    | Input     | This indicates the valid lines in one frame. |

| first_bufr_in_xfer_i    | 1     | Input     | First buffer in transfer indication          |

| last_bufr_in_xfer_i     | 3     | Input     | Last buffer in transfer indication           |

## 4.1.5. User Configurable Parameters

Table 4.5 provides the list of the user configurable parameters for the IP.

**Table 4.5. User Configurable Parameters**

| Parameter                    | Description                                                                                                             |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| IEBM_AXI4_ADDR_WIDTH_I       | This parameter defines the address width of the AXI interface.                                                          |  |

| IEBM_AXI4_DATA_WIDTH_I       | This parameter defines the read and write data width of AXI4 interface.  Valid values: 32, 64, and 128                  |  |

| IEBM_AXI4_BYTE_EN_WIDTH_I    | This parameter defines the byte enable width of the AXI interface.  Calculated based on the IEBM_AXI4_DATA_WIDTH_I/8    |  |

| IEBM_AHBL_ADDR_WIDTH_I       | This parameter defines the address width of the AHB-Lite interface.                                                     |  |

| IEBM_AHBL_DATA_WIDTH_I       | This parameter defines the read and write data width of AHB-Lite interface.  Valid values: 32                           |  |

| IEBM_HW_MAX_BUFRS_I          | This parameter defines the number of total buffers allocated for hardware.  Valid values: 1 to 15                       |  |

| IEBM_HW_SINGLE_BUFR_SIZE_I   | This parameter defines the In Endpoint Buffer Manager's single buffer depth in terms of bytes.  Valid values: 1 to 4096 |  |

| IEBM_BUFR_WR_DATA_WIDTH_I    | This parameter defines the In Endpoint Buffer Manager's write data width in terms of bits.  Valid values: 32, 64, 128   |  |

| IEBM_BUFR_WR_BYTE_EN_WIDTH_I | This parameter defines the In Endpoint Buffer Manager's write data width.  Valid values: 4, 8, 16                       |  |

| IEBM_IP_MAJOR_VER_I          | This parameter defines the major version for the IP.                                                                    |  |

| IEBM_IP_MINOR_VER_I          | This parameter defines the minor version for the IP.                                                                    |  |

## 4.2. Register Offset Map

This section provides a register offset map for the IN Endpoint Buffer Manager IP.

**Table 4.6. IEBM Register Offset Map**

| Register          | Offset | Description                              |  |

|-------------------|--------|------------------------------------------|--|

| IP_VERSION        | 0x00   | IP version register                      |  |

| SCRATCH           | 0x04   | Scratch register                         |  |

| INT_EN            | 0x08   | Interrupt enable register                |  |

| INT_SRC           | 0x0C   | Interrupt source register                |  |

| BUFR_CNFG         | 0x10   | Buffer configuration register            |  |

| HW_PARAMS_INFO    | 0x14   | Hardware parameters information register |  |

| CTRL              | 0x18   | Control register                         |  |

| BUFR_TRACKER_INFO | 0x1C   | Buffer tracker information register      |  |

FPGA-RD-02306-1.1

| Register               | Offset | Description                                       |

|------------------------|--------|---------------------------------------------------|

| BUFR_AVAILABILITY_INFO | 0x20   | Buffer availability information register          |

| BUFR_XCHNG_CTRL        | 0x24   | Buffer exchange control register                  |

| SEL_BUFR_INFO_FOR_FW   | 0x28   | Selected buffer information for firmware register |

| Reserved               | 0x2C   | Reserved                                          |

| TIMESTAMP_W0           | 0x30   | Timestamp lower bytes register                    |

| TIMESTAMP_W1           | 0x34   | Timestamp upper bytes register                    |

| VALID_LINES_IN_FRAME   | 0x38   | Valid Lines in one frame register                 |

# 4.3. Register Details

#### 4.3.1. IP\_VERSION

This register contains information about the IP version.

Table 4.7. IP\_VERSION, Offset = 0x00

| Bit   | Access | Default Value          | Description      |

|-------|--------|------------------------|------------------|

| 31:24 | RO     | Varies upon IP release | IP major version |

| 23:16 | RO     | Varies upon IP release | IP minor version |

| 15:0  | RO     | 0x0                    | Reserved         |

#### **4.3.2. SCRATCH**

This register can be used for testing and debugging purposes. When being read, the register returns the same value that is written to it.

Table 4.8. SCRATCH, Offset = 0x04

| Bit  | Access | Default Value | Description                                                                                                                                                                                                                                                                               |

|------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RW     | 0x0           | This field can be used for testing and debugging purposes. When being read, the register returns the same value that is written to it.  Typically, this is used to check whether firmware is able to communicate with the IP properly or not during the initial design development phase. |

#### 4.3.3. INT\_EN

This register indicates the interrupt enable which controls the reporting of interrupt to the software. It contains direct mapping to the INT\_SRC register. When a bit is set and the corresponding interrupt is active.

Table 4.9. INT EN, Offset = 0x08

| Bit  | Access | Default Value | Description                                                                                                                     |

|------|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| 31:1 | RO     | 0x0           | Reserved                                                                                                                        |

| 0    | RW     | 0x0           | Enable buffer available to firmware for processing interrupt.  1: Enable buffer available to firmware for processing interrupt. |

|      |        |               | 0: Disable buffer available to firmware for processing interrupt.                                                               |

#### 4.3.4. INT\_SRC

This register indicates the interrupt source, defining the events that determine the interrupt generation.

Table 4.10. INT\_SRC, Offset = 0x0C

| Bit  | Access | Default Value | Description                                                                      |

|------|--------|---------------|----------------------------------------------------------------------------------|

| 31:1 | RO     | 0x0           | Reserved                                                                         |

|      |        |               | Buffer available to firmware for processing interrupts.                          |

|      |        |               | This field indicates that there is at least one buffer available to firmware for |

| 0    | RO     | 0x0           | further processing.                                                              |

|      |        |               | This field remains high as long as no_of_bufrs_pending_to_be_processed_by_fw is  |

|      |        |               | not zero.                                                                        |

#### 4.3.5. BUFR\_CNFG

This register allows firmware to configure buffer parameters according to different requirements. Firmware shall update this register upon steps such as initialization, configuration, or reconfiguration.

**Warning:** The firmware shall modify this register only when Configured Flag is zero. Failing to meet this requirement may cause unexpected behavior.

Table 4.11. BUFR\_CNFG, Offset = 0x10

| Bit   | Access | Default Value                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:22 | RO     | 0x0                          | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21:17 | RW     | HW_MAX_BUFRS                 | FW_ALLOCATED_TOTAL_BUFRS This field defines the total number of buffers allocated by the firmware for this endpoint. This field must be less than or equal to HW_MAX_BUFRS, the hardware parameter which describes maximum buffers that can be used for this endpoint. This field shall not be zero. Typically, the firmware should use maximum buffers allowed by hardware design, that is, upon HW_MAX_BUFRS. The firmware may use a smaller number for debugging purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16:0  | RW     | HW_SINGLE_BUFR<br>_MAX_DEPTH | FW_ALLOCATED_SINGLE_BUFR_DEPTH This field defines single buffer depth in terms of bytes This field must be less than or equal to HW_SINGLE_BUFR_MAX_DEPTH, the hardware parameter that defines the maximum depth of a single buffer in terms of bytes. This field should not be zero. This field must be in multiples of the endpoint's maximum packet size. This ensures data packet to be sent on the USB bus is not split across multiple buffers. Examples: (1) Suppose HW_SINGLE_BUFR_MAX_DEPTH is 2048 and endpoint's maximum packet size is 512 bytes. In this case, valid values for this field are: 512, 1024, 1536, and 2048. (2) Suppose HW_SINGLE_BUFR_MAX_DEPTH is 512 and endpoint's maximum packet size is 64 bytes. In this case, valid values for this field are: 64, 128, 192, 256, 320, 384, 448, and 512. (3) Suppose HW_SINGLE_BUFR_MAX_DEPTH is 4096 and endpoint's maximum packet size is 700 bytes. In this case, valid values for this field are: 700, 1400, 2100, 2800, and 3500 |

#### 4.3.6. HW\_PARAMS\_INFO

This register contains information about parameters set in the hardware design.

Table 4.12. HW\_PARAMS\_INFO, Offset = 0x14

| Bit   | Access | Default Value                          | Description                                                                                                |

|-------|--------|----------------------------------------|------------------------------------------------------------------------------------------------------------|

|       |        | Based on the                           | HW_MAX_BUFRS                                                                                               |

| 31:28 | RO     | hardware                               | This field indicates the hardware parameter value that describes the maximum                               |

|       |        | parameters                             | buffers that can be used for this endpoint.                                                                |

| 27    | RO     | 0x0                                    | Reserved                                                                                                   |

|       |        | Based on the<br>hardware<br>parameters | HW_SINGLE_BUFR_MAX_DEPTH  This field indicates the hardware parameter value that defines the maximum depth |

| 26:10 | RO     |                                        | of a single buffer in terms of bytes.                                                                      |

|       |        |                                        | This field shall be in multiples of 8.                                                                     |

| 9:8   | RO     | 0x0                                    | Reserved                                                                                                   |

|       |        | Based on the                           | HW_FIFO_DATA_WIDTH                                                                                         |

| 7:0   | RO     | hardware                               | This field indicates the hardware parameter value for the data width of FIFO interface                     |

|       |        | parameters                             | in terms of bits.                                                                                          |

### 4.3.7. CTRL

This register is used by the firmware to control the bridge IP's functionality. The firmware shall access this register for IP initialization, configuration, or reconfiguration steps.

Table 4.13. CTRL, Offset = 0x18

| Bit  | Access | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:2 | RO     | 0x0           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1    | RW     | 0x0           | <ul> <li>Flush Buffers flush_bufrs</li> <li>The firmware sets this field to request the bridge IP to flush corresponding buffers. Upon detecting this field going high, the IP takes the following actions:</li> <li>1. Resets the IN Endpoint Buffer Manager Buffer Tracker and Firmware Buffer Tracker to 0.</li> <li>2. Loads the number of buffers available to the IN Endpoint Buffer Manager with a value equal to the FW_ALLOCATED_TOTAL_BUFRS field.</li> <li>3. Resets the number of buffers pending to be processed by the firmware to 0.</li> <li>4. Resets other appropriate local variables.</li> <li>5. Asserts one signal for 10 clock cycles of the FIFO clock to indicate to the IN Endpoint Buffer Manager about the re-initialization process. That block should reinitialize its local variables for a fresh start.</li> <li>6. After this, the IP resets this field.</li> <li>The firmware can only write 1 to this field. Writing 0 has no effect. This field is automatically cleared by the IP.</li> </ul> |

| 0    | RW     | 0x0           | Configured This field indicates the firmware has configured or reconfigured the bridge IP and the IN endpoint data supplier block can now access the FIFO interface. The firmware shall configure or reconfigure the bridge IP every time the corresponding endpoint is configured or re-initialized. Typically, the endpoint is configured or re-initialized upon the following requests: SET configuration, SET interface, and Clear feature of Endpoint Halt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### 4.3.8. BUFR\_TRACKER\_INFO

This register is used to track buffer pointers.

Table 4.14. BUFR\_TRACKER\_INFO, Offset = 0x1C

| Bit  | Access | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:4 | RO     | 0x0           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3:0  | RO     | 0x0           | Firmware Buffer Tracker fw_bufr_tracker  This field indicates the buffer which is either being accessed or is to be accessed by firmware.  This field is incremented by one once one buffer is processed by the firmware. This rolls over to 0 once it reaches the value that equals FW_ALLOCATED_TOTAL_BUFRS. In other words, the value of this field is in the range 0 to (FW_ALLOCATED_TOTAL_BUFRS-1).  This is reset to 0 when the flush buffers bit of the control register is set. |

#### 4.3.9. BUFR\_AVAILABILITY\_INFO

This register is used to get information about buffer availability.

Table 4.15. BUFR\_AVAILABILITY\_INFO, Offset = 0x20

| Bit  | Access | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:5 | RO     | 0x0           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |