## **Lattice Nexus 2 Hardware Checklist**

# **Preliminary** Technical Note

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility

## **Contents**

| Content  | S                                                                      | 3        |

|----------|------------------------------------------------------------------------|----------|

| Abbrevia | ations in This Document                                                | θ        |

| 1. Intr  | oduction                                                               |          |

| 2. Pov   | wer Supplies                                                           |          |

| 2.1.     | Power Noise                                                            | <u>C</u> |

| 2.2.     | Power Source                                                           | g        |

| 3. Pov   | wer Supply Filtering                                                   | 10       |

| 3.1.     | Recommended Power Filtering Groups and Components                      | 10       |

| 3.2.     | Ground Pins                                                            | 12       |

| 3.3.     | EXT_RES pins                                                           | 12       |

| 3.4.     | ERASEKEY                                                               | 12       |

| 3.4      | .1. ERASEKEY Schematics                                                | 12       |

| 3.5.     | Unused GPIO Pins                                                       |          |

| 3.6.     | Unused Banks (V <sub>CCIOx</sub> )                                     | 13       |

| 3.7.     | Unused SERDES Quads (V <sub>CCH_MPQx and</sub> V <sub>CCA_MPQx</sub> ) | 13       |

| 3.8.     | Clock Oscillator Supply Filtering                                      | 13       |

| 4. Pov   | wer                                                                    | 14       |

| 4.1.     | Power Sequencing                                                       | 14       |

| 4.2.     | Power Estimation                                                       | 14       |

| 5. Cor   | mponent Selection                                                      | 15       |

| 5.1.     | Ferrite Bead Selection                                                 | 15       |

| 5.2.     | Capacitor Selection                                                    | 15       |

| 5.2      | .1. Capacitor Dielectric                                               | 15       |

| 5.2      | .2. Voltage Rating                                                     | 15       |

| 5.2      | .3. Size                                                               | 15       |

| 5.2      | .4. Mounting Location                                                  | 15       |

|          | ck Inputs                                                              |          |

| 7. Cor   | nfiguration Considerations                                             | 17       |

| 7.1.     | JTAG                                                                   | 17       |

| 7.2.     | SPI Configuration                                                      | 17       |

| 7.3.     | Configuration Pins per Programming Mode                                | 18       |

| 8. Ext   | ernal SPI FLASH                                                        | 20       |

| 9. I/O   | Pin Assignments                                                        | 21       |

| 9.1.     | Early I/O Release                                                      | 21       |

| 9.2.     | Series Termination Resistors                                           | 21       |

| 10. Fun  | nctional Blocks Rule-Based Pinout Considerations                       | 22       |

| 10.1.    | LVDS, MIPI, and Differential Pair Assignments                          | 22       |

| 10.2.    | HSUL and SSTL Pin Assignments                                          | 22       |

| 10.3.    | LVSTL I and LVSTL II Pin Assignments                                   | 22       |

| 10.4.    | SERDES Pin Considerations                                              | 22       |

| 11. Lay  | out Recommendations                                                    | 23       |

| 12. Sim  | nulation and Board Measurement of Critical Signals                     |          |

| 12.1.    | Critical Signals                                                       | 24       |

| 12.2.    | Simulation                                                             | 24       |

| 12.3.    | Board Measurements                                                     | 24       |

| 13. SSC  | O (Simultaneous Switching Output) Design Check                         | 25       |

| 13.1.    | SSO Failures – Each of the following can lead to SSO failures          | 25       |

| 13.2.    | SSO Mitigations                                                        | 25       |

| 14. Che  | ecklist                                                                | 26       |

| Referen  | ces                                                                    | 31       |

|          | al Support Assistance                                                  |          |

| Revision | History                                                                | 33       |

## **Figures**

| Figure 3.1. Recommended Power Filters                                                 | 11 |

|---------------------------------------------------------------------------------------|----|

| Figure 3.2. ERASEKEY Schematics                                                       | 12 |

| Figure 3.3. Clock Oscillator Bypassing                                                | 13 |

| Figure 6.1. PCB Dual Footprint Supporting HCSL and LVDS Oscillators                   | 16 |

| Figure 7.1. Typical Connections for Programming SRAM or External Flash via JTAG       | 18 |

| Figure 7.2. Typical Connections for Programming SRAM or External Flash via Target SPI |    |

| Figure 11.1. Ground Vias Implementation                                               | 23 |

| Figure 11.2. Stitching Vias Implementation                                            | 23 |

## **Tables**

| Table 2.1. Supply Rails                                             | 8  |

|---------------------------------------------------------------------|----|

| Table 3.1. Recommended Power Filtering Groups and Components        |    |

| Table 5.1. Recommended Capacitor Sizes                              |    |

| Table 7.1. JTAG Pin Recommendations                                 |    |

| Table 7.2. Pull-up/Pull-down Recommendations for Configuration Pins | 17 |

| Table 7.3. Configuration Pins Needed per Programming Mode           | 18 |

| Table 14.1. Hardware Checklist                                      |    |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                           |

|--------------|--------------------------------------|

| AC           | Alternating Current                  |

| BGA          | Ball Grid Array                      |

| BBRAM        | Battery-Backed RAM                   |

| DC           | Direct Current                       |

| DLL          | Delay-Locked Loop                    |

| DDR          | Double Data Rate                     |

| DQS          | Data Strobe                          |

| ESR          | Equivalent Series Resistance         |

| FPGA         | Field-Programmable Gate Array        |

| HCSL         | High-Speed Current Steering Logic    |

| HSUL         | High-Speed Unterminated Logic        |

| IBIS         | I/O Buffer Information Specification |

| 1/0          | Input/Output                         |

| INITN        | Initialization Pin (Active Low)      |

| JTAG         | Joint Test Action Group              |

| LPDDR        | Low-Power Double Data Rate memory    |

| LVDS         | Low-Voltage Differential Signaling   |

| LVSTL        | Low-Voltage Swing Terminated Logic   |

| MIB          | Memory Interface Block               |

| MIPI         | Mobile Industry Processor Interface  |

| PCB          | Printed Circuit Board                |

| PLL          | Phase-Locked Loop                    |

| POR          | Power-On Reset                       |

| RAM          | Random Access Memory                 |

| RES_EXT      | External Resistor                    |

| REXT         | External Reference Resistor          |

| SCLK         | SPI Clock                            |

| SERDES       | Serializer/Deserializer              |

| SI           | Signal Integrity                     |

| SPI          | Serial Peripheral Interface          |

| SRAM         | Static RAM                           |

| SSTL         | Stub Series-Terminated Logic         |

| SSO          | Simultaneous Switching Output        |

| TCK          | Test Clock                           |

| TDI          | Test Data In                         |

| TDO          | Test Data Out                        |

| TMS          | Test Mode Select                     |

| USB          | Universal Serial Bus                 |

| VCC          | Voltage Common Collector             |

### 1. Introduction

When designing complex hardware with the Lattice Nexus<sup>™</sup> 2 device, you must pay close attention to critical hardware configuration requirements. This technical note outlines key implementation considerations specific to the Lattice Nexus 2 device. While it does not provide detailed step-by-step instructions, it offers a high-level checklist to support the design process.

Hardware Checklists are developed after evaluation boards and incorporate optimized designs that improve upon the circuitry of evaluation boards. If you copy circuits from evaluation boards, ensure to optimize your designs according to the hardware checklists.

The Lattice Nexus 2 platform comprises Certus-N2. This variant has Wide Range I/O, High Speed I/O, PCIe, Ethernet, and SERDES Channels.

This technical note assumes familiarity with the Lattice Nexus 2 device features as described in the Lattice Nexus 2 Platform - Overview Data Sheet (FPGA-DS-02122) and Lattice Nexus 2 Platform - Specifications Data Sheet (FPGA-DS-02121). These data sheets provide the functional specification for the device, including (but not limited to):

- High-level functional overview

- Pinouts and packaging information

- Signal descriptions

- Device-specific information about peripherals and registers

- Electrical specifications

This technical note addresses the following critical hardware areas. For additional details, refer to the Lattice Nexus 2 Platform - Overview Data Sheet (FPGA-DS-02122) and Lattice Nexus 2 Platform - Specifications Data Sheet (FPGA-DS-02121).

- Power supplies and how to connect them to the PCB and the associated system

- Configuration mode selection for proper power-up behavior

- Device I/O interface and critical signals

**Important**: Refer to the following documents for detailed recommendations.

- Lattice Nexus 2 sysCONFIG User Guide (FPGA-TN-02370)

- Lattice Nexus 2 sysl/O User Guide (FPGA-TN-02365)

- Lattice Nexus 2 sysCLOCK PLL Design and User Guide (FPGA-TN-02364)

- Lattice Nexus 2 Embedded Memory User Guide (FPGA-TN-02366)

- Lattice Nexus 2 High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02372)

- Lattice Nexus 2 sysDSP User Guide (FPGA-TN-02362)

- Thermal Management (FPGA-TN-02044)

- Electrical Recommendations for Lattice SERDES (FPGA-TN-02077)

- High-Speed PCB Design Considerations (FPGA-TN-02178)

- Power Decoupling and Bypass Filtering for Programmable Devices (FPGA-TN-02115)

- LatticeSC<sup>™</sup> SERDES Jitter (TN1084)

- HSPICE SERDES simulation package Available under NDA, contact the license administrator at lic admin@latticesemi.com

- Lattice Nexus 2 Pinout (FPGA-SC-02063)

## 2. Power Supplies

At power up, the  $V_{CC}$ ,  $V_{CCAUX}$ ,  $V_{CCI01}$ , and  $V_{CCI02}$  power supplies are monitored to determine when the Lattice Nexus 2 device should deassert its internal Power-On Reset (POR) state and enter Power Good condition initializing device initialization and configuration. These supplies must ramp up monotonically. Other supplies are not monitored during power-up but must reach a valid stable level before configuration completes.

Table 2.1 lists the required power supplies and their corresponding voltage levels for each supply.

**Table 2.1. Supply Rails**

| Supply Rail                                                                                     | Voltage<br>(Nominal Value) <sup>1</sup>                                                                                                                       | Description                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>                                                                                 | _                                                                                                                                                             | Ground for internal FPGA logic and I/O                                                                                                                                                                           |

| V <sub>SSR</sub>                                                                                | _                                                                                                                                                             | Reserved. Connect to ground.                                                                                                                                                                                     |

| V <sub>CC</sub>                                                                                 | 0.82 V                                                                                                                                                        | FPGA core power supply. Required for Power Good condition.                                                                                                                                                       |

| V <sub>CCA_PLL_W</sub> , V <sub>CCA_PLL10</sub> , V <sub>CCA_PLL4</sub> , V <sub>CCA_PLL7</sub> | 0.82 V                                                                                                                                                        | Power supply for PLL blocks.                                                                                                                                                                                     |

| V <sub>CCAUX</sub>                                                                              | 1.8 V                                                                                                                                                         | Auxiliary power supply. Used for generating stable drive current for the I/O. Required for Power Good condition.                                                                                                 |

| V <sub>CCAUXA</sub>                                                                             | 1.8 V                                                                                                                                                         | Auxiliary power supply for internal analog circuitry.                                                                                                                                                            |

| V <sub>CC_BAT</sub>                                                                             | 1.5 V                                                                                                                                                         | Optional power supply to allow a battery to preserve the volatile configuration battery backed RAM (BBRAM) when the other DC supplies are absent.                                                                |

| V <sub>CCIO[14:0]</sub>                                                                         | Wide Voltage Range Banks 0, 1, 2, 12, 13, and 14: 1.2 V, 1.8 V, 2.5 V, 3.3 V.  High-Performance Banks 3–11: 0.9 V, 1.0 V, 1.1 V, 1.2 V, 1.35 V, 1.5 V, 1.8 V. | I/O driver supply voltage for each bank. Each bank has its own $V_{\text{CCIO}}$ supply. $V_{\text{CCIO1}}$ and $V_{\text{CCIO2}}$ are required for Power Good conditions as they are used during configuration. |

| V <sub>CCA_MPQx</sub>                                                                           | 0.80 V (≤ 16Gbps) <sup>2</sup><br>0.90 V (> 16Gbps) <sup>2</sup>                                                                                              | Power supply for the SERDES Blocks' analog circuitry. Voltage depends on data rate speed. X = 0, 1, 2, 3, 4, 5, 6                                                                                                |

| V <sub>ССН_МРQх</sub>                                                                           | 1.5 V (≤ 16Gbps) <sup>2</sup><br>1.8 V (> 16Gbps) <sup>2</sup>                                                                                                | Power supply for the SERDES Blocks' digital circuitry. Voltage depends on data rate speed. X = 0, 1, 2, 3, 4, 5, 6                                                                                               |

#### Notes:

- The Lattice Nexus 2 device includes a power-on-reset (POR) state machine that depends on several monitored power supplies.

These supplies must ramp up monotonically. Device initialization does not proceed until all monitored power supplies reach their minimum operating voltages.

- 2. Protocol performance speeds were achieved with the LFG and CBG packages. Other packages are limited to 10 Gbps.

#### 2.1. Power Noise

FPGA power rails allow a worst-case operating tolerance of  $\pm 3\%$  of their nominal voltages. This tolerance includes all noise sources. An exception is the  $V_{CC\ BAT}$  rail which allows supports a wider operating range of 1.0 V to 1.55 V.

#### 2.2. Power Source

It is recommended that the designed voltage regulators are accurate to within 2% of the optimum voltage to allow power noise design margin.

When calculating total voltage regulator tolerance, consider the following:

- Regulator voltage reference tolerance

- Regulator line tolerance

- Regulator load tolerance

- Tolerances of any resistors connected to the regulator's feedback pin which sets the regulator's output voltage

- Expected voltage drops due to power filtering ferrite bead's ESR x expected current draw

- Expected voltage drops due to the current measuring resistor's ESR x expected current draw

With 2% tolerance allocated to the voltage source, the design has a remaining 1% tolerance for noise and layout related issues. The lower voltage rails (< 1.2 V) are especially sensitive to noise (for the 0.82 V rail every 8.2 mV is 1% of the rail voltage).

For SERDES power rails, aim for  $\leq$  0.5% peak noise; for PLLs, target  $\leq$  0.25% peak noise.

## 3. Power Supply Filtering

Providing well-filtered power is essential for all supply rails and especially critical for analog rails. Each supply should be decoupled using appropriate power filters. Bypass capacitors must be placed close as possible to the device package pins, with minimal trace length to reduce inductance.

For optimal performance, assign pins carefully to avoid placing noisy I/O signals near sensitive functional pins. PCB-related crosstalk often originates from FPGA outputs routed too close to sensitive power supply lines. A careful PCB layout is required to ensure noise immunity, particularly for analog supplies affected by switching noise from FPGA outputs. While this document provides filtering guidelines, robust layout practice is essential to prevent noise coupling into sensitive analog rails.

Extremely low-noise, well-filtered supplies are essential for the Lattice Nexus 2 SERDES, PLLs, and V<sub>CCAUXA</sub> rail.

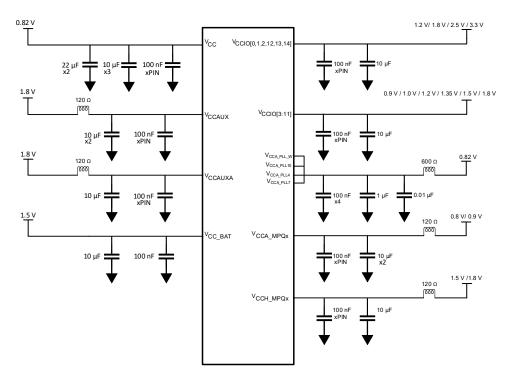

## 3.1. Recommended Power Filtering Groups and Components

Table 3.1. Recommended Power Filtering Groups and Components

| Power Input                                                                                                      | Recommended Filter                                                           | Notes                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub>                                                                                                  | 22 μF x 2 + 10 μF x 3 + 100 nF per pin                                       | Core and clock logic. High current rail; source using switching regulator. 0.82 V                                               |

| V <sub>CCA_PLL_W</sub> , V <sub>CCA_PLL10</sub> , V <sub>CCA_PLL4</sub> ,<br>V <sub>CCA_PLL7</sub> tied together | 600 Ω FB 0805 (ESR $\leq$ 0.06 Ω) + 1.0 μF + 100 nF x4 + 0.01 μF             | Sensitive PLL supply. Low current; Use LDO regulator for low noise. Tie all listed PLL supplies together. 0.82 V                |

| V <sub>CCAUX</sub>                                                                                               | 120 $\Omega$ FB (ESR $\leq$ 0.1 $\Omega$ ) + 10 $\mu$ F x 2 + 100 nF per pin | Auxiliary power supply for internal analog circuitry.  1.8 V                                                                    |

| Vccauxa                                                                                                          | 120 $\Omega$ FB (ESR $\leq$ 0.1 $\Omega$ ) + 10 $\mu$ F + 100 nF per pin     | Sensitive Auxiliary power supply for internal analog circuitry. This rail must not be combined with V <sub>CCAUX</sub> .  1.8 V |

| V <sub>CC_BAT</sub>                                                                                              | 10 μF + 100 nF                                                               | Optional power supply to allow a battery to preserve the volatile configuration RAM (BBRAM) when other DC supplies are absent.  |

|                                                                                                                  |                                                                              | If not used the rail pin may be left unconnected.  1.5 V                                                                        |

| Power Input           | Recommended Filter                                                                                                                                           | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCIOx</sub>    | 10 μF + 100 nF per pin                                                                                                                                       | Power supply for I/O banks. $x = Specific Bank number$ . For unused banks, the 10 $\mu$ F capacitor may be omitted. For banks with > 15 outputs or high capacitive loads, use 22 $\mu$ F or an additional 10 $\mu$ F. Use Lattice SSO tool to verify noise levels. Wide-Range Banks: $x = 0, 1, 2, 12, 13,$ and 14 supported $V_{CCIOx}$ voltages: 1.2 V, 1.8 V, 2.5 V, or 3.3 V. High-Performance Banks: $x = 3 - 11$ supported $V_{CCIOx}$ voltages: 0.9 V, 1.0 V, 1.1 V, 1.2 V, 1.35 V, 1.5 V, or 1.8 V. |

| V <sub>CCA_MPQx</sub> | $0.80$ V For data rate $\leq 16$ Gbps <sup>1</sup><br>0.90 V For data rate > $16$ Gbps <sup>1</sup><br>120 $\Omega$ FB + $10$ $\mu$ F x 2 + $100$ nF per pin | Power supply for the SERDES Block analog circuitry. Voltage depends on data rate speed. $X=0,1,2,3,4,5,6$ Separate FB + Capacitor filter for each $V_{\text{CCA\_MPQX}}.$                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CCH_MPQx</sub> | 1.5 V For data rate ≤ 16Gbps¹ 1.8 V For data rate > 16Gbps¹ 120 Ω FB + 10 μF + 100 nF per pin                                                                | Power supply for the SERDES Block digital circuitry. Voltage depends on data rate speed. $X=0,1,2,3,4,5,6$ Separate FB + Capacitor filter for each $V_{\text{CCH\_MPQX}}$ .                                                                                                                                                                                                                                                                                                                                 |

#### Note:

1. Protocol performance speeds were achieved with the LFG and CBG packages. Other packages are limited to 10 Gbps.

Figure 3.1. Recommended Power Filters

#### 3.2. Ground Pins

All ground pins (V<sub>SS</sub> and V<sub>SSR</sub>) need to be connected to the board's ground plane.

### 3.3. EXT\_RES pins

- These pins are dedicated to resistor connection to ground or bank V<sub>CCIO</sub> only.

- Connect 240 Ω ±1% to ground on banks which use standards LVDS, subLVDS, SLVS, HSUL, POD, MIPI D-PHY.

- Connect 240  $\Omega$  ±1% to  $V_{CCIO}$  on banks which use LVSTL 110 standard.

- Connect 180  $\Omega$  ±1% to  $V_{CCIO}$  on banks which use LVSTL II IO standard.

- Leave unconnected if the bank is not using one of the above standards.

Refer to the Lattice Nexus 2 High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02372) for more information.

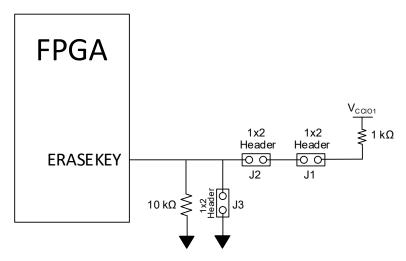

#### 3.4. ERASEKEY

The ERASEKEY pin enables secure erasure of customer keys stored in either One-Time Programmable (OTP) memory or Battery-Backed RAM (BBRAM).

Ground the ERASEKEY pin by default, and when not using the ERASEKEY function. By default, the ERASEKEY pin is disabled. It can be permanently enabled by blowing an OTP fuse. Once enabled, the erase function is initiated by asserting the pin HIGH for at least 350 ms.

Selection of OTP or BBRAM is made using BBRAM\_EN fuse:

#### BBRAM EN=0 (Default)

Security processor firmware will trigger a hardware state machine to permanently set all bits to 1s in the OTP memory key space.

#### BBRAM\_EN=1

Security processor firmware will set all bits to 0s in the BBRAM key space.

#### 3.4.1. ERASEKEY Schematics

Figure 3.2. ERASEKEY Schematics

Note: J2 and J3 are optional and provide additional protection against accidental ERASEKEY activation.

Default configuration (ERASEKEY pin grounded)

- J1: OPEN

- J2: OPEN

- J3: INSTALLED

© 2024-2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-TN-02382-0.82

To activate ERASEKEY, the ERASEKEY pin must be held high for ≥ 350 ms.

Activation configuration (pin held high ≥ 350 ms)

J1: INSTALLED

J2: INSTALLED

J3: OPEN

After activation, set to default configuration (ERASEKEY pin grounded)

J1: OPEN

J2: OPEN

J3: INSTALLED

#### 3.5. Unused GPIO Pins

All unused GPIO pins can be left open.

## 3.6. Unused Banks (V<sub>CCIOx</sub>)

- Connect unused V<sub>CCIOx</sub> pins to a valid power rail. Do not leave them floating.

- Bypass each unused rail pin with a 100 nF capacitor.

## 3.7. Unused SERDES Quads (V<sub>CCH MPQx and</sub> V<sub>CCA MPQx</sub>)

For unused SERDES quads, ground the following pins:

- Power pins VCCH MPQx and VCCA MPQx.

- Differential Input Pairs MPQx RXP/N.

- Clock reference pins MPQx\_REFCLKP/N.

- External Reference Resistor Input REXT MPQx (use 200  $\Omega$ ).

- Leave differential outputs MPQx\_TXP/N, unconnected.

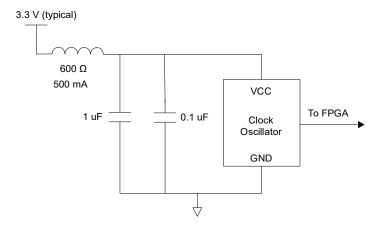

## 3.8. Clock Oscillator Supply Filtering

When using an external reference clock (single-ended or differential), ensure the oscillator's power supply is properly isolated and decoupled. A typical bypassing circuit is shown in Figure 3.3.

Figure 3.3. Clock Oscillator Bypassing

### 4. Power

### 4.1. Power Sequencing

The Lattice Nexus 2 device does not require a specific power rail sequence for either power-up or power-down.

#### 4.2. Power Estimation

After selecting the Lattice Nexus 2 device density, package, and logic implementation, estimate power consumption of the system environment using the Power Calculator included in the Lattice Radiant™ design tool. When estimating power, consider the following key objectives:

- Ensure power supply capacity accounts for the highest of the following: power-up in-rush current, configuration current, and maximum DC/AC operating current under expected system environmental conditions.

- Confirm that the system environment and the package can maintain the device's junction temperature within the specified maximum operating limit.

Addressing these two criteria early in the design phase ensures accurate power budgeting and thermal planning for the Lattice Nexus 2 device .

## 5. Component Selection

#### 5.1. Ferrite Bead Selection

- Most designs perform well with ferrite beads rated between 120  $\Omega$  and 240  $\Omega$  at 100 MHz .

- The noise voltage caused by ferrite bead ESR × CURRENT should remain below 0.5% of the rail voltage for non-analog rails, and below 0.25% for sensitive analog rails.

- For non-PLL rails, select ferrite beads with ESR between 0.01  $\Omega$  and 0.10  $\Omega$  based on the expected current load .

- PLL rails draw low current, which allow ferrite beads with ESR  $\leq$  0.40  $\Omega$ .

- Smaller package ferrite beads typically exhibit higher ESR than larger packages of the same impedance rating.

- Within the same package size, higher impedance ferrite beads generally have higher ESR than low impedance ones.

### 5.2. Capacitor Selection

Select good-quality ceramic capacitors in small packages, and place them as close as possible to the clock oscillator supply pins. *Good quality* bypass capacitors typically meet the following criteria:

#### 5.2.1. Capacitor Dielectric

Use stable dielectric types such as X5R, X7R, and similar, which maintain capacitance within ±20% across the operating temperature range. Avoid dielectrics like Y5V, Z5U, and similar, which exhibit poor capacitance.

#### 5.2.2. Voltage Rating

Capacitor effective capacitance decreases non-linearly under higher DC bias conditions. To ensure capacitance stability, select capacitors with voltage ratings at least 80% higher than the maximum voltage of the rail. For example, for a 3.3 V rail, use bypass capacitors rated at a minimum of 6.3 V.

#### 5.2.3. Size

Smaller body capacitors have lower inductance, work to higher frequencies, and improve board layout. Note that smaller capacitors within the same voltage rating are typically more expensive than their larger counterparts. Balancing cost and electrical performance, the recommended capacitor size are shown below:

**Table 5.1. Recommended Capacitor Sizes**

| Capacitance    | Size Preferred | Size Next Best |

|----------------|----------------|----------------|

| 0.1 μF         | 0201           | 0402           |

| 1.0 μF, 2.2 μF | 0402           | 0201           |

| 4.7 μF         | 0402           | 0603           |

| 10 μF          | 0402           | 0603           |

| 22 μF          | 0805           | 0603           |

#### 5.2.4. Mounting Location

Place the  $0.1 \mu F$  capacitors as close as possible to the Lattice Nexus 2 FPGA's associated power rail pins. Using 0201-sized  $0.1 \mu F$  capacitors enables placement on the PCB underside, between via holes beneath the FPGA ball pads.

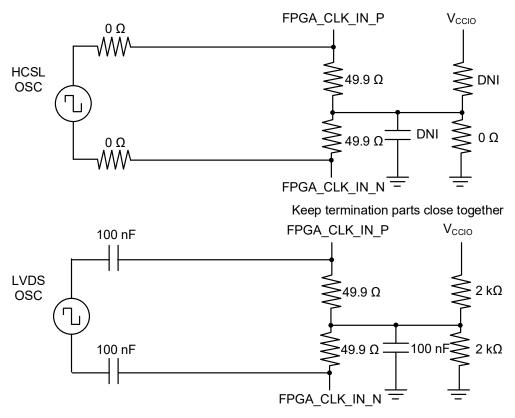

## 6. Clock Inputs

The Lattice Nexus 2 device designates certain pins in each I/O bank for use as clock inputs. These pins are shared and may also function as general-purpose I/O.

When using these pins for clock input, it is critical to minimize signal noise to ensure reliable clock performance. Refer to Lattice Nexus 2 High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02372).

These shared clock input pins, typically named GPLL and PCLK, are listed under the *Dual Function* column in the device's *pinlist .csv* file. For high-speed differential interfaces (such as MIPI), route the differential clock pair to dedicated differential clock input pins labeled *PCLKTx\_y* (+true) and *PCLKCx\_y* (-complement). For single-ended I/Os, use only PCLKT pins as primary CLK pads.

Ensure that the output voltage of any external reference oscillator does not exceed the  $V_{CCIO}$  voltage of the target I/O bank. For banks operating at  $V_{CCIO} \le 1.5$  V, use an HCSL oscillator to ensure the clock signal remains with the bank voltage limit. Alternatively, an LVDS oscillator may be used if AC-coupled and DC-biased to half the  $V_{CCIO}$  voltage. Figure 6.1. illustrates a dual-footprint PCB layout that supports both HCSL and LVDS oscillators.

Figure 6.1. PCB Dual Footprint Supporting HCSL and LVDS Oscillators

## 7. Configuration Considerations

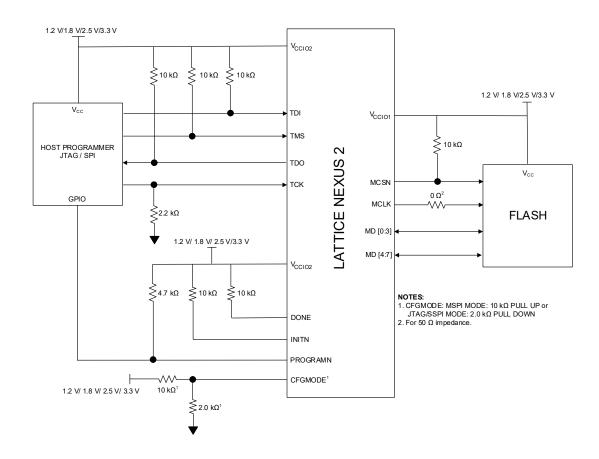

#### 7.1. JTAG

The Lattice Nexus 2 device supports configuration via the JTAG interface as well as through various sysCONFIG modes. The JTAG interface uses a 4-pin connection and requires specific PCB design considerations, detailed in Table 7.1.

**Table 7.1. JTAG Pin Recommendations**

| JTAG Pin | PCB Recommendation                                          |

|----------|-------------------------------------------------------------|

| CFGMODE  | $2.0~k\Omega$ pull-down to GND to enable JTAG Configuration |

| TCK      | 2.2 kΩ pull-down to GND                                     |

| TMS      | 10 kΩ pull-up to $V_{CCIO2}$                                |

| TDI      | 10 kΩ pull-up to $V_{CCIO2}$                                |

| TDO      | 10 kΩ pull-up to V <sub>CCIO2</sub>                         |

The JTAG port enables debugging in the final system. It is recommended that all PCBs provide accessible JTAG pins, even if JTAG is not the primary configuration method. For best results, route the VCCIO2, TCK, TDI, TDO, TMS, CFGMODE, PROGRAMN, INITN, DONE, GND signals to a common test header.

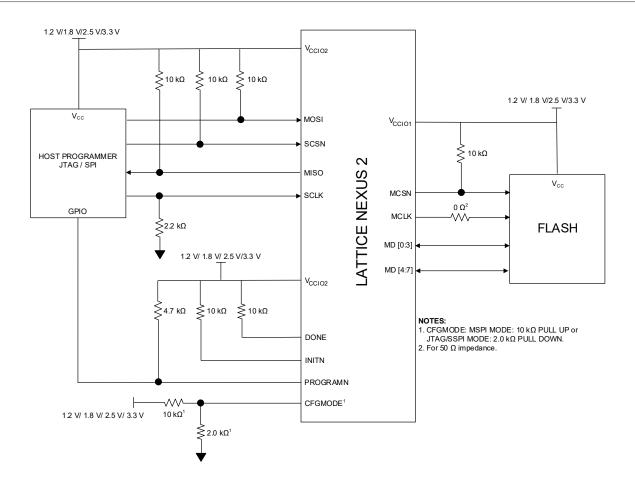

### 7.2. SPI Configuration

The Lattice Nexus 2 device supports configuration via both Controller (MSPI) and Target (SSPI) SPI interfaces.

The pins listed in Table 7.2 have internal weak pull resistors, pull-up resistors to the appropriate bank  $V_{\text{CCIO}}$  and pull-down resistors to board ground. It is recommended to provide external pull resistors as indicated on the table.

Table 7.2. Pull-up/Pull-down Recommendations for Configuration Pins

| Pin       | PCB Connection                                                                        |

|-----------|---------------------------------------------------------------------------------------|

| PROGRAMN  | 4.7 kΩ pull-up to $V_{CCIO2}$                                                         |

| INITN     | 10 $k\Omega$ pull-up to $V_{CCIO2}$                                                   |

| DONE      | 10 $k\Omega$ pull-up to $V_{CCIO2}$                                                   |

| CFGMODE   | 10.0 $k\Omega$ pull-up to $V_{\text{CCIO2}}$ for MSPI configuration                   |

|           | $2.0~k\Omega$ pull-down to GND for SSPI or JTAG configuration                         |

| MCSN      | 10 k $\Omega$ pull-up to $V_{CCIO1}$                                                  |

| MCLK      | 1.0 $k\Omega$ pull-down to GND (Not installed by default)                             |

|           | 1.0 k $\Omega$ pull-up to $V_{\text{CCIO1}}$ (Not installed by default)               |

|           | Series resistor placed near TX side <sup>1</sup>                                      |

| MDQ0/MOSI | 10 $k\Omega$ pull-up to $V_{\text{CCIO1}}$ (Not installed by default)                 |

| MDQ1/MISO | 10 $k\Omega$ pull-up to $V_{\text{CCIO1}}$ (Not installed by default)                 |

| MDQ2-MDQ7 | 10 $k\Omega$ pull-up to $V_{\text{CCIO1}}$ (Not installed by default)                 |

| MDS       | MSPI Octal Mode Data Strobe, 10 $k\Omega$ pull-down to GND (Not installed by default) |

| SCSN      | 4.7 kΩ pull-up to $V_{CCIO2}$                                                         |

| SCLK      | 1.0 $k\Omega$ pull-down to GND (Not installed by default)                             |

|           | 1.0 k $\Omega$ pull-up to $V_{\text{CCIO}2}$ (Not installed by default)               |

| SDQ0/MOSI | 10 $k\Omega$ pull-up to $V_{CCIO2}$ (Not installed by default)                        |

| SDQ1/MISO | 10 $k\Omega$ pull-up to $V_{CCIO2}$ (Not installed by default)                        |

| SDQ2-SDQ7 | 10 $k\Omega$ pull-up to $V_{\text{CCIO2}}$ (Not installed by default)                 |

| SDS       | SSPI octal mode data strobe, 10 $k\Omega$ pull-down to GND (Not installed by default) |

#### Note:

1. Series resistor value depends on the PCB design. It ranges from 0  $\Omega$  (PCB impedance: 50  $\Omega$ ) to 10  $\Omega$  (PCB impedance: 60  $\Omega$ ).

## 7.3. Configuration Pins per Programming Mode

Table 7.3 summarizes the required signal pins for each supported configuration-programming mode.

**Table 7.3. Configuration Pins Needed per Programming Mode**

| Configuration     | Bank | Enablement       | Clo  | ock    | Bus  | Pins                                 |

|-------------------|------|------------------|------|--------|------|--------------------------------------|

| Mode              |      |                  | Pin  | 1/0    | Size |                                      |

| JTAG <sup>1</sup> | 2    | CFGMODE pin Low  | TCLK | Input  | 1    | TCK, TMS, TDI, TDO                   |

| MSPI              | 1    | CFGMODE pin High | MCLK | Output | 1    | MCLK, MCSN, MOSI, MISO               |

|                   |      |                  |      |        | 2    | MCLK, MCSN, MD0, MD1                 |

|                   |      |                  |      |        | 4    | MCLK, MCSN, MD0, MD1, MD2, MD3       |

|                   |      |                  |      |        | 8    | MCLK, MCSN, MDS, MD0, MD1, MD2,      |

|                   |      |                  |      |        |      | MD3,                                 |

|                   |      |                  |      |        |      | MD4, MD5, MD6, MD7                   |

| SSPI              | 1    | CFGMODE pin Low  | SCLK | Input  | 1    | SCLK, SCSN, SI, SO                   |

|                   |      |                  |      |        | 2    | SCLK, SCSN, SD0, SD1                 |

|                   |      |                  |      |        | 4    | SCLK, SCSN, SD0, SD1, SD2, SD3       |

|                   |      |                  |      |        | 8    | SCLK, SCSN, SDS, SD0, SD1, SD2, SD3, |

|                   |      |                  |      |        |      | SD4, SD5, SD6, SD7                   |

#### Note:

1. The JTAG port takes precedence over SSPI.

Figure 7.1. Typical Connections for Programming SRAM or External Flash via JTAG

Figure 7.2. Typical Connections for Programming SRAM or External Flash via Target SPI

## 8. External SPI FLASH

The SPI Flash device voltage must match the  $V_{\text{CCIO1}}$  voltage level.

It is recommended to use an SPI flash device that is supported by the Lattice Radiant Programmer. To view the list of supported devices, open the Lattice Radiant Programmer, navigate to the **Help** menu, and search for **SPI Flash support**. If your SPI Flash device is not listed, you may still be able to use it by configuring the **Custom Flash** option in the Radiant

If your SPI Flash device is not listed, you may still be able to use it by configuring the **Custom Flash** option in the Radiant Programmer.

## 9. I/O Pin Assignments

While the Lattice Nexus 2 device packages help reduce crosstalk coupling, PCB layout can still introduce significant noise due to closely spaced I/O pins and parallel trace routing over long distances. For optimal jitter performance, assign noisy I/O pins away from sensitive power rails such as those for PLL and SERDES. Use PCB crosstalk or signal integrity simulation tool to evaluate and refine potentially problematic trace layouts.

Refer to PCB Layout Recommendations for BGA Packages (FPGA-TN-02024) for layout and breakout guidance.

Designers typically select FPGA pinouts early in the design cycle, which requires careful planning. For the FPGA designer, this requires detailed knowledge of the targeted FPGA device. Designers often use a spreadsheet program to initially capture the list of the design I/O. Lattice Semiconductor provides detailed pinout information that can be downloaded from the Lattice Semiconductor website in .csv format for designers to use as a resource to create pinout information. For example, by navigating to the pinout.csv file, you can gather the details for all the different package offerings of the device in the family, including I/O banking, differential pairing, Dual Function of the pins, and input and output details.

## 9.1. Early I/O Release

The Lattice Nexus 2 device supports an Early I/O Release feature, enabling I/Os to assume predefined drive states early during the bitstream processing. The Early I/O release feature releases the I/O after processing the I/O configuration which is located near the head of the bitstream data. Once data is programmed in the left/right Memory Interface Block (MIB) the I/O is released to a predefined state. Enable this feature by setting EARLY\_IO\_RELEASE to ON in the Lattice Radiant Device Constraint Editor.

#### 9.2. Series Termination Resistors

When using series termination resistors, locate the resistors close to the transmitting pins.

Configuration pins to external devices (such as SPI FLASH) default to 50RS (50  $\Omega$ ) drive strength. For these pins, start with a value of 0  $\Omega$  for PCB impedance of 50  $\Omega$ . For higher PCB impedances increase the series termination resistance, for example 10  $\Omega$  for PCB impedance of 60  $\Omega$ .

Optimum series termination resistance value for user mode output pins depends on the PCB etch impedance and selected output drive strength. Use IBIS models to simulate and determine the optimal starting resistance value. Further, test with oscilloscope and optimize the series termination resistance of critical signals for best signal integrity.

### 10. Functional Blocks Rule-Based Pinout Considerations

The Lattice Nexus 2 devices support a wide range of high-speed interfaces, each with specific rule-based pinout requirement that must be considered during PCB design. Pinout selection should be guided by a clear understanding of the FPGA's internal interface building block. These include I/O LOGIC blocks such as Soft MIPI, clock resource connectivity, and PLL usage. Refer to Lattice Nexus 2 High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02372) for rules pertaining to these interface types.

### 10.1. LVDS, MIPI, and Differential Pair Assignments

True LVDS and MIPI signaling inputs and outputs are available on the bottom I/O pins of the FPGA device (High-Performance banks 3–11). Differential input pairing under the High-Speed column in the *pinlist .csv* file.

- The positive signal of a differential pair should connect to an I/O ending in A (such as, HPIOx\_yA).

- The negative signal of a differential pair should connect to an I/O ending in B (such as, HPIOx yB).

The Wide Range banks (0, 1, 2, 12, 13, 14) on the top side I/O banks do not support true LVDS or MIPI standards, but can emulate LVDS outputs using external termination resistors. For implementation details, refer to the Lattice Nexus 2 sysI/O User Guide (FPGA-TN-02365).

- Set the bank voltage to 1.8 V to support LVDS.

- Set the bank voltage to 1.2 V to support MIPI.

### 10.2. HSUL and SSTL Pin Assignments

The HSUL and SSTL interfaces are referenced to I/O standards that require an external reference voltage (V<sub>REF</sub>). These standards are supported only on the bottom-side High-Performance Banks (3–11).

- The VREF pin(s) should be prioritized during PCB pin assignment.

- These pins are labeled  $V_{REF}$  in the *Dual Function* column of the *pinlist .csv* file.

- Each bank has its own V<sub>REF</sub> voltage, which sets the threshold for the referenced input buffers.

- Each I/O is individually configurable based on the bank's supply and reference voltages.

### 10.3. LVSTL I and LVSTL II Pin Assignments

The LVSTL I and LVSTL II interfaces require external reference resistor and are supported only on the device bottom-side High-Performance Banks (3-11).

- These pins are labeled RES\_EXT in the *Dual Function* column of the *pinlist .csv* file.

- Each bank has a separate RES\_EXT voltage.

- Refer to the RES EXT pins subsection for resistor values and implementations details.

- For pinout and grouping requirements of memory-mapped interfaces, see the Lattice Nexus 2 High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02372).

#### 10.4. SERDES Pin Considerations

High-speed signaling requires meticulous PCB design to maintain proper transmission line characteristics.

- Ensure a continuous ground reference is maintained along high-speed signal paths.

- Differential pairs must be tightly length-matched, with a maximum mismatched of ±4 mil (±0.1 mm).

- Minimize discontinuities such as vias in high-speed routes.

For detailed guidance, refer to High-Speed PCB Design Considerations (FPGA-TN-02178).

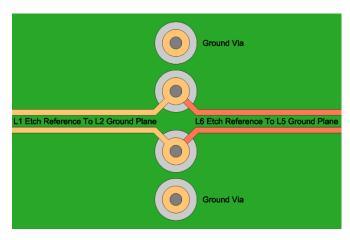

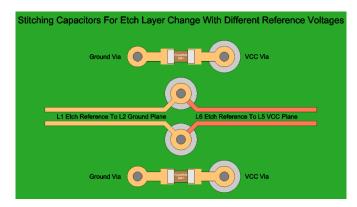

## 11. Layout Recommendations

A good schematic design should be reflected in a good layout to ensure proper noise and power distribution. Below are some of the recommended layouts in general.

- All power must come from power planes to ensure reliable power delivery and thermal stability.

- Each power pin should have its own decoupling capacitor, typically 100 nF, placed as close as possible to the pin. 2.

- Place analog circuits away from digital circuits and high-switching components.

- High-speed signals should maintain a clearance of five times the trace width from other signals.

- 5. High-speed signals transitioning between layers should include a corresponding ground via if both reference planes are ground. If the reference plane V<sub>CC</sub>; use a stitching capacitor between ground and V<sub>CC</sub>.

Figure 11.1. Ground Vias Implementation

Figure 11.2. Stitching Vias Implementation

- High-speed signals have specific impedance requirements. Calculate the necessary trace width and differential gap based on the stack-up, and verify dimensions with the PCB vendor.

- For differential pairs, match trace lengths as closely as possible—ideally within ±5mils.

For further information on layout recommendations, refer to:

- PCB Layout Recommendations for BGA Packages (FPGA-TN-02024)

- PCB Layout Recommendations for Leaded Packages (FPGA-TN-02160)

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-TN-02382-0.82

## 12. Simulation and Board Measurement of Critical Signals

To ensure design reliability and high manufacturing yield, critical signals should be simulated during the design phase and then measured on the PCB assembly to verify proper function.

### 12.1. Critical Signals

Signals sensitive to signal integrity (SI) degradation are considered critical and require additional design and verification attention.

Typical critical signals include:

- Differential Pairs (LVDS, subLVDS, SLVS, MIPI, USB, and the like.)

- Clocks (oscillator inputs, output clocks)

- Data with embedded clocks

- Interrupts (edge-triggered)

- Logic signals traveling long distances requiring termination

#### 12.2. Simulation

Lattice Semiconductor provides an IBIS (I/O Buffer Information Specification) file for use with simulation tools. Popular simulation tools include:

- HyperLynx

- Sigrity

- SpectraQuest

- Micro-Cap (Free)

Most SI simulation tools are expensive and often require a recurring subscription fee. The expensive tools can import board design files and can easily supply accurate simulations which include crosstalk and other SI degrading effects.

Free IBIS tools (such as Micro-cap) can provide basic simulations, but require additional effort to model SI effects across multiple signals with varying transmission line lengths, lossy lines, and crosstalk.

Use simulation results to optimize each critical signal for signal integrity:

- Set output pin drive strength

- Set output pin slew rate

- Design the output pin termination (such as, output series termination resistor value)

- Configure internal pin pull-up and pull-down resistors

- Refine PCB layout.

### 12.3. Board Measurements

Measure critical signals on the assembled PCB using an oscilloscope. Verify proper signal function and integrity (that is, eye diagram, SI parameters).

Use measurement results to optimize each critical signal for signal integrity:

- · Adjust output pin drive strength

- Adjust output pin slew rate

- Modify output pin termination design (such as, output series termination resistor value).

- Configure internal pin pull-up and pull-down resistors.

Specification compliance testing is recommended for common signaling standards (such as, USB, MIPI).

## 13. SSO (Simultaneous Switching Output) Design Check

Users should verify designs to ensure they do not experience functional failures due to SSO voltage drops (sometimes call SSO noise, Ground Bounce, or Power Bounce).

SSO voltage drops result from package inductance combined with dynamic switching current which causes Ldi/dt voltage drops.

The Lattice SSO Tool should be used to estimate SSO voltage drop.

### 13.1. SSO Failures – Each of the following can lead to SSO failures

- 1. Many simultaneous switching outputs in the same I/O bank. The more outputs that switch simultaneously, the greater the *di* current, and consequently, the greater the Ldi/dt voltage drops.

- 2. I/O slew rates set to FAST (and sometimes MEDIUM). Faster slew rates reduce the *dt* time and thus increase Ldi/dt voltage drops.

- 3. I/O output current set high (for example, 8 mA 16 mA). Higher I/O output current increases the *di* current and, therefore, the Ldi/dt voltage drops.

- 4. I/O capacitive loading is relatively high (especially > 15 pF). High capacitance loading increases the *di* current and, therefore, the Ldi/dt voltage drops.

- 5. I/O banks with low voltage rails (for example LVCMOS 1.0 V LVCMOS 1.5 V) have smaller voltage margins and are more susceptible to Ldi/dt ground and power violations.

### 13.2. SSO Mitigations

- 1. Split up simultaneous switching outputs across multiple banks (where timing permits.) Fewer simultaneous outputs per bank reduce the *di* current and, therefore, the Ldi/dt voltage drops.

- 2. Reduce I/O slew rates to MEDIUM or preferably SLOW, if timing allows. Increasing slew time increases *dt* and reduces Ldi/dt voltage drops.

- 3. Reduce I/O output current (for example 4 mA), where timing and signal quality permit. Lower output current reduces di current and, therefore, Ldi/dt voltage drops.

- 4. Reduce I/O capacitive loading (this typically requires PCB design changes). Lower capacitance reduces di current and, therefore, Ldi/dt voltage drops.

- 5. Increase I/O bank voltage rails (this often requires PCB design changes). If the above mitigations are insufficient, increasing bank voltage can improve absolute voltage margins and ensure enough design margin for reliable operation.

## 14. Checklist

#### Table 14.1. Hardware Checklist

|        | Item                                                                                                                                                  | ОК | NA |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|

| 1      | FPGA Power Supplies                                                                                                                                   |    |    |

| 1.1    | System Supplies                                                                                                                                       |    |    |

| 1.1.1  | Voltage rails have ±3% tolerance. Use voltage regulator ≤ ±2% tolerance to allow for ±1% power noise.                                                 |    |    |

| 1.1.2  | Follow Table 3.1 for proper decoupling of each power rail.                                                                                            |    |    |

| 1.1.3  | V <sub>CC</sub> and V <sub>CCA PLLx</sub> at 0.82 V ±3%                                                                                               |    |    |

| 1.1.4  | Use a PCB plane for V <sub>CC</sub> core with proper decoupling.                                                                                      |    |    |

| 1.1.5  | V <sub>CC</sub> core sized to meet power requirement calculation from software.                                                                       |    |    |

| 1.1.6  | V <sub>CCCLK</sub> , V <sub>CCHP</sub> , V <sub>CCA_PLLx</sub> must be quiet and isolated from other switching noises and each other.                 |    |    |

| 1.1.7  | V <sub>CCAUX</sub> and V <sub>CCAUXA</sub> at 1.8 V ±3%.                                                                                              |    |    |

| 1.1.8  | V <sub>CCAUX</sub> and V <sub>CCAUXA</sub> must be quiet and isolated from other switching noises and each other.                                     |    |    |

| 1.1.9  | V <sub>CCAUX</sub> pins should be tied together, and a solid PCB plane is recommended.                                                                |    |    |

| 1.1.10 | V <sub>CCAUXA</sub> pins are sensitive and should be filtered separately from V <sub>CCAUX</sub> pins.                                                |    |    |

| 1.1.11 | V <sub>CC BAT</sub> pin at 1.5 V +3%/-33%; if not used, leave the pin open.                                                                           |    |    |

| 1.2    | I/O Supplies                                                                                                                                          |    |    |

| 1.2.1  | All Wide-Range V <sub>CCIO</sub> (Banks 0, 1, 2, 12, 13, and 14)                                                                                      |    |    |

|        | V <sub>CCIOx</sub> voltages: 1.2 V, 1.8 V, 2.5 V, or 3.3 V.                                                                                           |    |    |

| 1.2.2  | All High-Performance banks (3–11)                                                                                                                     |    |    |

|        | $V_{\text{CCIO}_{X}}$ voltages: 0.9 V, 1.0 V, 1.1 V, 1.2 V, 1.35 V, 1.5 V, or 1.8 V.                                                                  |    |    |

| 1.2.3  | $V_{\text{CCH MPQx}}$ pins must be quiet and isolated from other switching noises.                                                                    |    |    |

| 1.3    | SERDES Power Supplies                                                                                                                                 |    |    |

| 1.3.1  | V <sub>CCA MPQx</sub> pins:                                                                                                                           |    |    |

|        | 0.80 V for data rate ≤ 16Gbps                                                                                                                         |    |    |

|        | 0.90 V for data rate > 16Gbps.                                                                                                                        |    |    |

| 1.3.2  | $V_{\text{CCA\_MPQx}}$ pins must be quiet and isolated from other switching noises.                                                                   |    |    |

| 1.3.3  | V <sub>CCH_MPQx</sub> pins:                                                                                                                           |    |    |

|        | 1.50 V for data rate ≤16Gbps                                                                                                                          |    |    |

|        | 1.8 V for data rate > 16Gbps.                                                                                                                         |    |    |

| 1.4    | Grounds                                                                                                                                               |    |    |

| 1.4.1  | All ground pins (V <sub>SS</sub> and V <sub>SSR</sub> ) must be connected to a low-impedance dedicated ground plane.                                  |    |    |

| 1.5    | Unused Blocks                                                                                                                                         |    |    |

| 1.5.1  | Connect unused $V_{\text{CCIOx}}$ pins to a power rail. Do not leave them open. It is recommended to bypass unused rail pins with a 100 nF capacitor. |    |    |

| 1.5.2  | Connect unused quads $V_{\text{CCH\_MPQx}}$ and $V_{\text{CCA\_MPQx}}$ pins to ground.                                                                |    |    |

|        | Also, tie reference pins $M_{PQx\_REFCLKP}$ and $M_{PQx\_REFCLKN}$ to ground.                                                                         |    |    |

| 1.6    | Power Sequencing is not required.                                                                                                                     |    |    |

| 2      | JTAG                                                                                                                                                  |    |    |

| 2.1    | CFGMODE pin pulled high with 10 k $\Omega$ resistor or low using 2.0 k $\Omega$ resistor per Table 7.1.                                               |    |    |

| 2.2    | Keep CFGMODE accessible on the PCB to recover the JTAG port, especially during development.                                                           |    |    |

| 2.3    | Keep JTAG port pins accessible on the PCB, especially during development.                                                                             |    |    |

| 2.3.1  | JTAG header: VCCIO2, TCK, TDI, TDO, TMS, CFGMODE, PROGRAMN, INITN, DONE, GND.                                                                         |    |    |

| 2.4    | Apply a pull-down resistor on TCK, as specified in Table 7.1.                                                                                         |    |    |

| 2.5    | Apply a pull-up resistor on TMS, TDI, and TDO, as specified in Table 7.1.                                                                             |    |    |

| 3      | MSPI and SSPI Configuration                                                                                                                           |    |    |

| 3.1    | V <sub>CCIO1</sub> , V <sub>CCIO2</sub> bank voltages must match the sysCONFIG peripheral devices (for example, SPI Flash, external connections).     |    |    |

|       | Item                                                                                                                                                                                                                                                                   | ОК | NA       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|

| 3.2   | CFGMODE pin                                                                                                                                                                                                                                                            |    |          |

|       | Apply a 10 $k\Omega$ pull-up resistor to $V_{\text{CCIO2}}$ for MSPI configuration.                                                                                                                                                                                    |    |          |

|       | Apply a 2.0 kΩ pull-down resistor to GND for SSPI configuration.                                                                                                                                                                                                       |    |          |

| 3.3   | Apply pull-up or pull-down resistors to persisted configuration specific pins as specified Table 7.1 and Table 7.2.                                                                                                                                                    |    |          |

| 4     | External Flash                                                                                                                                                                                                                                                         |    |          |

| 4.1   | The external flash voltage must match V <sub>CCIO1</sub> voltage.                                                                                                                                                                                                      |    |          |

| 5     | Special Pin Assignments                                                                                                                                                                                                                                                |    |          |

| 5.1   | Pinout is chosen to address FPGA resource connections to I/O logic and clock resources per Lattice Nexus 2 High-Speed I/O and External Memory Interface User Guide (FPGA-TN-02372).                                                                                    |    |          |

| 5.2   | Shared general-purpose I/O are used as inputs for FPGA PLLs and clock input signals.                                                                                                                                                                                   |    |          |

| 5.3   | Bank V <sub>CCIOX</sub> voltage                                                                                                                                                                                                                                        |    |          |

| 5.3.1 | Set the bank voltage to 1.8 V to support LVDS signaling.                                                                                                                                                                                                               |    |          |

| 5.3.2 | Set the bank voltage to 1.2 V to support MIPI signaling.                                                                                                                                                                                                               |    | <u> </u> |

| 5.4   | Referenced I/O standards.                                                                                                                                                                                                                                              |    |          |

| 5.4.1 | HSUL and SSTL are supported on the device's bottom banks only (High-Performance banks 3–11).                                                                                                                                                                           |    |          |

| 5.4.2 | Decouple the $V_{REF}$ pin using a 0.1 $\mu F$ capacitor.                                                                                                                                                                                                              |    | -        |

| 5.5   | Termination Impedance: Rext <sup>1</sup> resistor.                                                                                                                                                                                                                     |    |          |

| 5.5.1 | LVSTL I require a 240 $\Omega$ ±1% resistor from Rext <sup>1</sup> to V <sub>CCIOX</sub> for proper termination impedances.                                                                                                                                            |    |          |

| 5.5.2 | LVSTL II requires a 180 $\Omega$ ±1% resistor from Rext <sup>1</sup> to $V_{CCIOX}$ for proper termination impedances.                                                                                                                                                 |    |          |

| 5.5.3 | For POD or SSTL I/O standards, connect a 240 $\Omega$ ±1% resistor from Rext <sup>1</sup> to ground.                                                                                                                                                                   |    |          |

| 5.5.4 | For non-memory I/O standards, leave open.                                                                                                                                                                                                                              |    |          |

| 6     | Clock Inputs                                                                                                                                                                                                                                                           |    |          |

| 6.1   | High-speed differential interfaces (such as MIPI), when received by the FPGA, must route their differential clock pair into a pair of inputs that support differential clocking, labeled PCLKTx_y (+true)                                                              |    |          |

|       | and PCLKCx_y (-complement)                                                                                                                                                                                                                                             |    | _        |

| 6.2   | For single-ended I/Os, use only PCLKT pins as primary CLK pads.                                                                                                                                                                                                        |    |          |

| 6.3   | When providing an external reference clock to the FPGA, ensure that the oscillator's output voltage does not exceed the bank's voltage .                                                                                                                               |    |          |

| 6.4   | For banks with $V_{CCIO} \le 1.5$ V, it is recommended to use an HCSL oscillator to keep the clock voltage less than or equal to the bank's $V_{CCIO}$ . An LVDS oscillator may also be used if AC-coupled and then DC-biased at half the $V_{CCIO}$ . See Figure 6.1. |    |          |

| 7     | MIPI Interface Requirements                                                                                                                                                                                                                                            |    |          |

| 7.1   | Soft MIPI is supported only on bottom banks (High-Performance banks 3–11).                                                                                                                                                                                             |    |          |

| 7.2   | Set V <sub>CCIOX</sub> to 1.2 V.                                                                                                                                                                                                                                       |    |          |

| 7.3   | Target 100 $\Omega$ impedance.                                                                                                                                                                                                                                         |    |          |

| 7.4   | Differential pairs must reference a ground plane without slots or breaks. It should be continuous between the FPGA and destination or source.                                                                                                                          |    |          |

| 7.5   | Design differential pairs as <i>loosely coupled</i> with separation between the positive and negative traces of a pair of at least twice the etch width (intra-pair spacing).                                                                                          |    |          |

| 7.6   | Provide separation between each differential pair of at least six times the etch width (inter-pair spacing).                                                                                                                                                           |    |          |

| 7.7   | Match the lengths of clock and data lane pair traces within 0.1 mm for both intra-pair and inter-pair etches.                                                                                                                                                          |    |          |

| 7.8   | The RX at the FPGA should have the clock differential pair routed to clock pins labeled PCLKTx_y (+true) and PCLKCx_y (-complement).                                                                                                                                   |    |          |

| 8     | LVDS Interface Requirements                                                                                                                                                                                                                                            |    |          |

| 8.1   | LVDS supported only on bottom banks (High-Performance banks 3–11).                                                                                                                                                                                                     |    |          |

| 8.2   | Set V <sub>CCIOX</sub> to 1.8 V.                                                                                                                                                                                                                                       |    |          |

| 8.3   | Target 100 $\Omega$ impedance.                                                                                                                                                                                                                                         |    | 1        |

| 8.4   | Differential pairs must reference a ground plane without slots or breaks. It should be continuous                                                                                                                                                                      |    |          |

|       | Item                                                                                                                                                                                                  | ОК | NA |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|

|       | between the FPGA and the destination or source.                                                                                                                                                       |    |    |

| 8.5   | Design differential pairs as <i>loosely coupled</i> with separation between positive and negative traces of a pair of at least twice the etch width (intra-pair spacing).                             |    |    |