# Lattice Nexus 2 Embedded Memory User Guide

## **Preliminary** Technical Note

FPGA-TN-02366-0.81

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                                 | 3  |

|----------------------------------------------------------|----|

| Abbreviations in This Document                           | 6  |

| 1. Introduction                                          |    |

| 2. Memory Generation                                     | 8  |

| 2.1. IP Catalog Flow                                     | 8  |

| 2.2. Utilizing PMI                                       | 10 |

| 2.3. Utilizing Direct Instantiation of Memory Primitives | 10 |

| 3. Memory Features                                       | 11 |

| 3.1. ECC in Memory Modules                               | 11 |

| 3.2. Byte Enable                                         | 11 |

| 4. Memory Modules                                        | 12 |

| 4.1. Memory Cascading                                    | 12 |

| 4.1.1. Input and Output Register                         | 12 |

| 4.1.2. Reset                                             | 12 |

| 4.1.3. Timing                                            | 12 |

| 4.2. Single-Port RAM – EBR-Based                         | 13 |

| 4.3. True Dual-Port RAM – EBR-Based                      | 16 |

| 4.4. Pseudo Dual-Port RAM – EBR-Based                    | 21 |

| 4.5. Read Only Memory – EBR-Based                        | 24 |

| 5. FIFO Memory                                           | 27 |

| 5.1. Single-Clock FIFO – EBR-Based or LUT-Based          | 27 |

| 6. Dual-Clock FIFO – EBR-Based or LUT-Based              | 36 |

| 6.1. FIFO_DC Flags                                       | 38 |

| 7. Distributed Single-Port RAM – PFU-Based               | 47 |

| 8. Distributed Dual-Port RAM – PFU-Based                 |    |

| 9. Distributed ROM – PFU-Based                           | 53 |

| 10. Initializing Memory                                  | 55 |

| 10.1. Initialization File Formats                        | 55 |

| 10.1.1. Binary File                                      | 55 |

| 10.1.2. Hex File                                         | 56 |

| References                                               | 57 |

| Technical Support Assistance                             | 58 |

| Revision History                                         | 59 |

## **Figures**

| Figure 2.1. Mamory Modules Available in ID Catalog                                                                                                                                 | 0  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. Memory Modules Available in IP Catalog                                                                                                                                 |    |

| Figure 2.2. IP Catalog in the Lattice Radiant Software                                                                                                                             |    |

| Figure 2.4. Example: Generating Pseudo Dual-Port RAM ram_dp Osing iP Catalog<br>Figure 2.4. Example: Generating Pseudo Dual-Port RAM ram_dp Module Customization – General Options |    |

|                                                                                                                                                                                    |    |

| Figure 4.1. Single-Port Memory Module Generated by IP Catalog                                                                                                                      |    |

| Figure 4.2. Single-Port RAM Primitive for Lattice Nexus 2 Platform Devices                                                                                                         |    |

| Figure 4.3. Single-Port RAM Timing Waveform – without Output Registers                                                                                                             |    |

| Figure 4.4. Single-Port RAM Timing Waveform – with Output Registers                                                                                                                |    |

| Figure 4.5. True Dual-Port Memory Module Generated by IP Catalog                                                                                                                   |    |

| Figure 4.6. True Dual-Port RAM Primitive for Lattice Nexus 2 Platform Devices                                                                                                      |    |

| Figure 4.7. True Dual-Port RAM Timing Waveform – without Output Registers                                                                                                          |    |

| Figure 4.8. True Dual-Port RAM Timing Waveform – with Output Registers                                                                                                             |    |

| Figure 4.9. Pseudo Dual-Port Memory Module Generated by IP Catalog                                                                                                                 |    |

| Figure 4.10. Pseudo-Dual Port RAM Primitive for Lattice Nexus 2 Platform Devices                                                                                                   |    |

| Figure 4.11. Pseudo Dual-Port RAM Timing Diagram – without Output Registers                                                                                                        |    |

| Figure 4.12. Pseudo Dual-Port RAM Timing Diagram – with Output Registers                                                                                                           |    |

| Figure 4.13. ROM – Read Only Memory Module Generated by IP Catalog                                                                                                                 |    |

| Figure 4.14. ROM Timing Waveform – without Output Registers                                                                                                                        |    |

| Figure 4.15. ROM Timing Waveform – with Output Registers                                                                                                                           |    |

| Figure 5.1. FIFO Module Generated by IP Catalog                                                                                                                                    |    |

| Figure 5.2. FIFO Without Output Registers – Start of Data Write Cycle                                                                                                              |    |

| Figure 5.3. FIFO Without Output Registers – End of Data Write Cycle                                                                                                                |    |

| Figure 5.4. FIFO Without Output Registers – Start of Data Read Cycle                                                                                                               |    |

| Figure 5.5. FIFO Without Output Registers – End of Data Read Cycle                                                                                                                 |    |

| Figure 5.6. FIFO with Output Registers – Start of Data Write Cycle                                                                                                                 |    |

| Figure 5.7. FIFO with Output Registers – End of Data Write Cycle                                                                                                                   |    |

| Figure 5.8. FIFO with Output Registers – Start of Data Read Cycle                                                                                                                  | 33 |

| Figure 5.9. FIFO with Output Registers – End of Data Read Cycle                                                                                                                    | 34 |

| Figure 5.10. FIFO with Output Registers and RdEn on Output Registers                                                                                                               | 35 |

| Figure 6.1. FIFO_DC Module Generated by IP Catalog                                                                                                                                 | 36 |

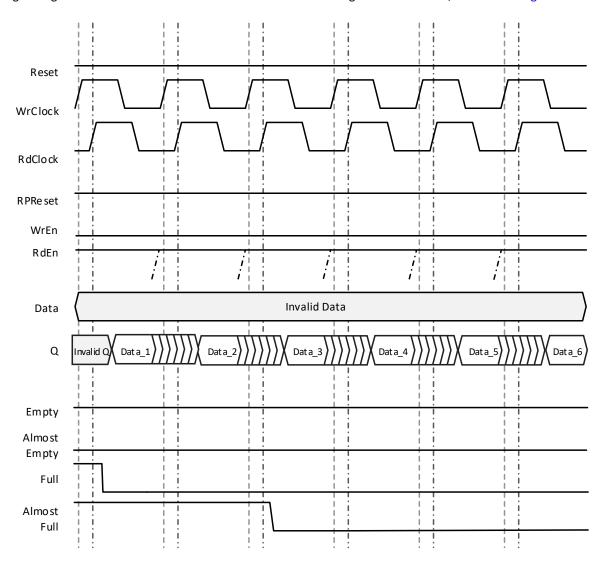

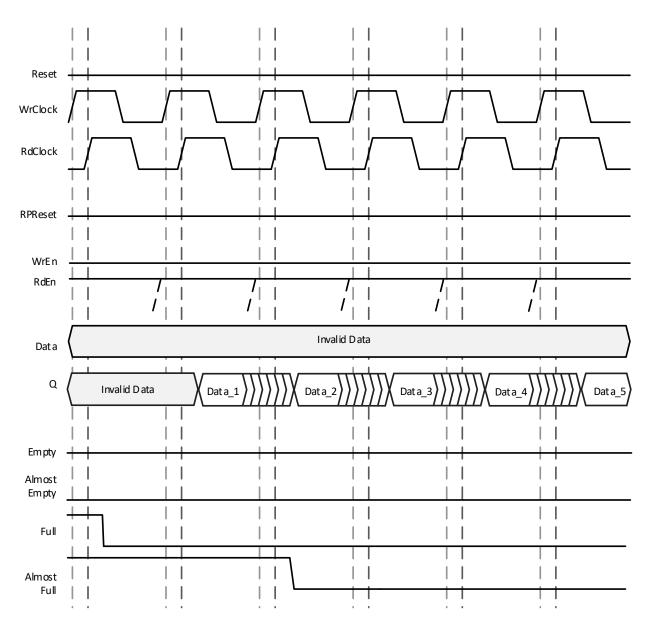

| Figure 6.2. FIFO_DC Without Output Registers – Start of Data Write Cycle                                                                                                           | 38 |

| Figure 6.3. FIFO_DC Without Output Registers – End of Data Write Cycle                                                                                                             | 39 |

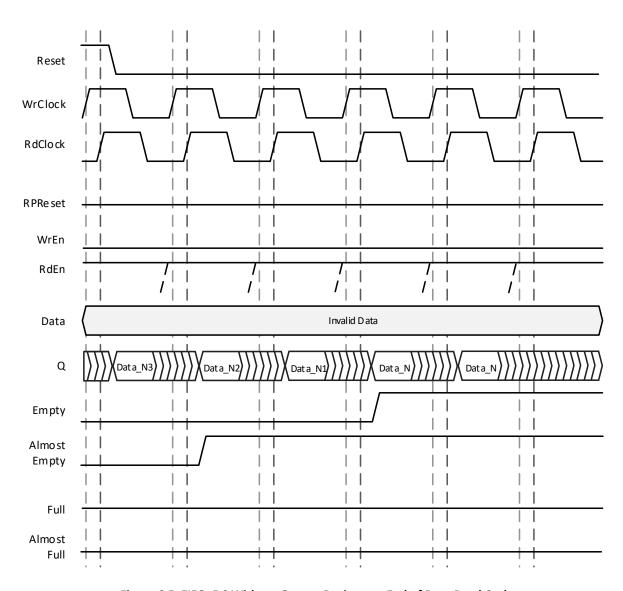

| Figure 6.4. FIFO_DC Without Output Registers – Start of Data Read Cycle                                                                                                            | 40 |

| Figure 6.5. FIFO_DC Without Output Registers – End of Data Read Cycle                                                                                                              | 41 |

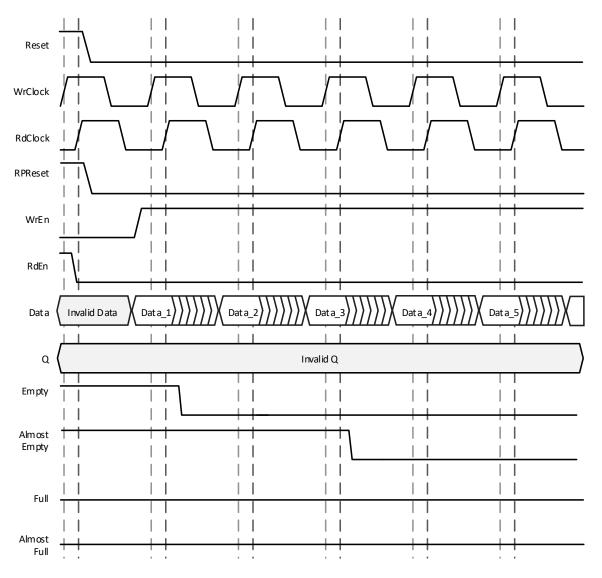

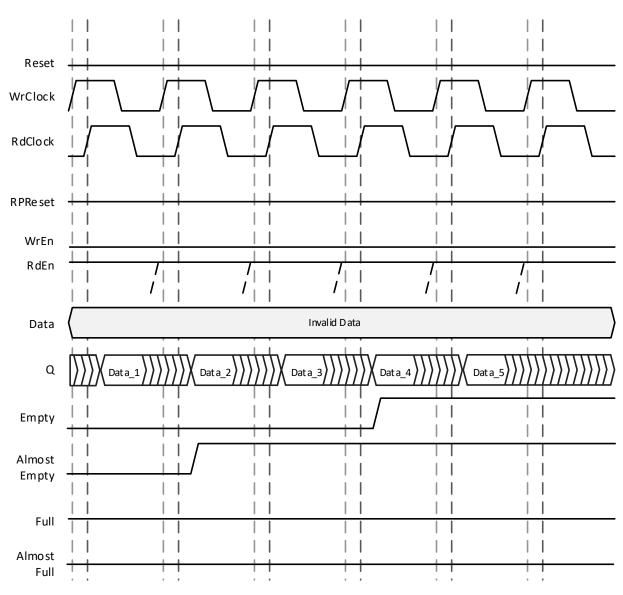

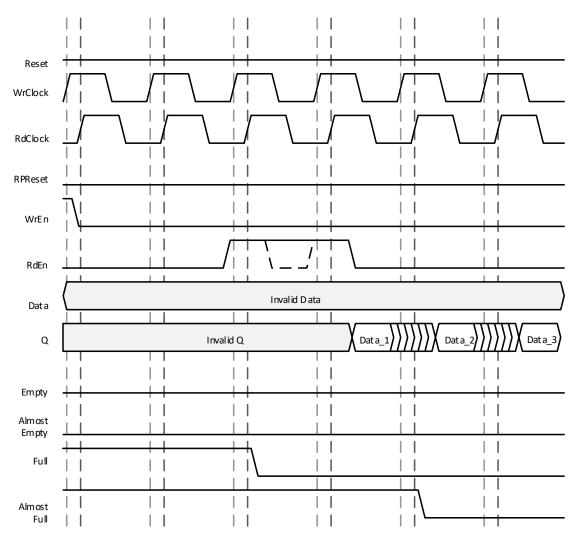

| Figure 6.6. FIFO_DC with Output Registers – Start of Data Write Cycle                                                                                                              | 42 |

| Figure 6.7. FIFO_DC with Output Registers – End of Data Write Cycle                                                                                                                | 43 |

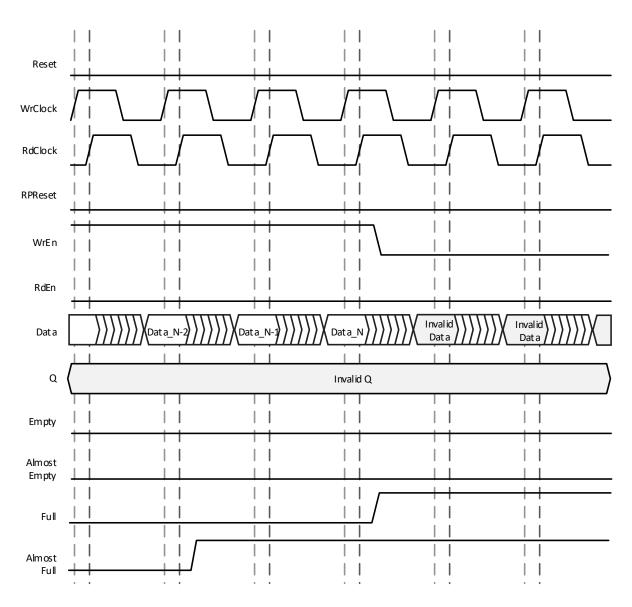

| Figure 6.8. FIFO_DC with Output Registers – Start of Data Read Cycle                                                                                                               | 44 |

| Figure 6.9. FIFO_DC with Output Registers – End of Data Read Cycle                                                                                                                 | 45 |

| Figure 6.10. FIFO_DC with Output Registers and RdEn on Output Registers                                                                                                            | 46 |

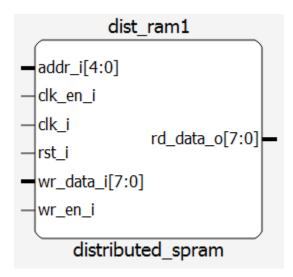

| Figure 7.1. Distributed Single-Port RAM Module Generated by IP Catalog                                                                                                             | 47 |

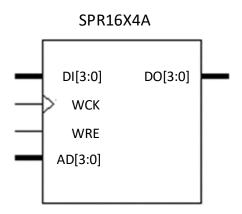

| Figure 7.2. Single-Port Distributed RAM Primitive for Lattice Nexus 2 Platform Devices                                                                                             | 47 |

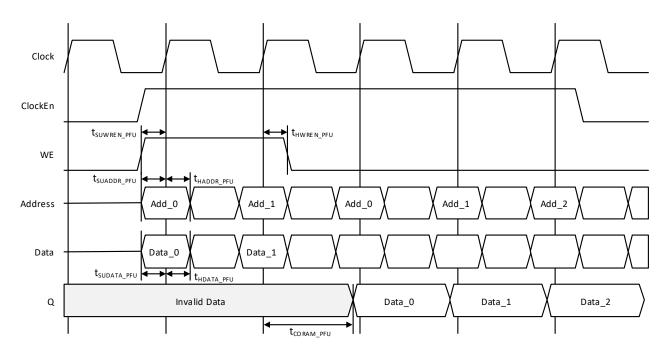

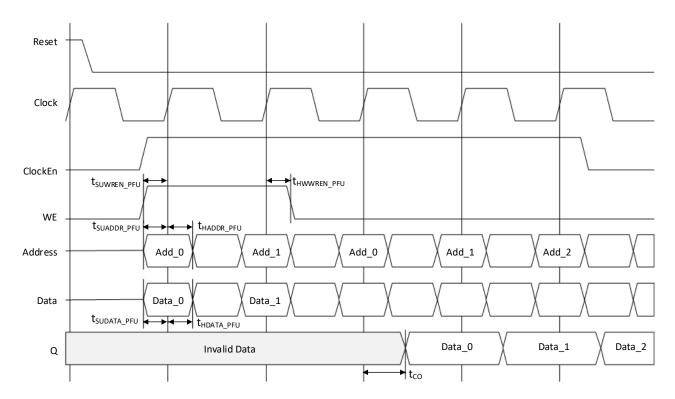

| Figure 7.3. PFU-Based Distributed Single-Port RAM Timing Waveform – without Output Registers                                                                                       |    |

| Figure 7.4. PFU-Based Distributed Single-Port RAM Timing Waveform – with Output Registers                                                                                          |    |

| Figure 8.1. Distributed Dual-Port RAM Module Generated by IP Catalog                                                                                                               |    |

| Figure 8.2. Dual-Port Distributed RAM Primitive for Lattice Nexus 2 Platform Devices                                                                                               |    |

| Figure 8.3. PFU-Based Distributed Dual-Port RAM Timing Waveform – without Output Registers                                                                                         |    |

| Figure 8.4. PFU-Based Distributed Dual-Port RAM Timing Waveform – with Output Registers                                                                                            |    |

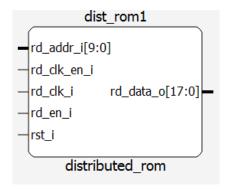

| Figure 9.1. Distributed ROM Generated by IP Catalog                                                                                                                                |    |

| Figure 9.2. PFU-Based Distributed Dual-Port RAM Timing Waveform – without Output Registers                                                                                         |    |

| Figure 9.3. PFU-Based Distributed Dual-Port RAM Timing Waveform – with Output Registers                                                                                            |    |

|                                                                                                                                                                                    |    |

## **Tables**

| Table 3.1. Masked Data in Bits for a 9-Bit Byte Size                                           | 11 |

|------------------------------------------------------------------------------------------------|----|

| Table 4.1. EBR-Based Single-Port Memory Port Definitions <sup>1</sup>                          |    |

| Table 4.2. Single-Port Memory Sizes for 36 kb Memory in Lattice Nexus 2 Platform Devices       |    |

| Table 4.3. Single-Port Memory Attributes in Lattice Nexus 2 Platform Devices                   |    |

| Table 4.4. EBR-Based True Dual-Port Memory Port Definitions                                    |    |

| Table 4.5. Dual-Port Memory Sizes for 36 kb Memory for Lattice Nexus 2 Platform Devices        |    |

| Table 4.6. True Dual-Port RAM Attributes for Lattice Nexus 2 Platform Devices                  |    |

| Table 4.7. EBR-Based True Dual-Port Memory Port Definitions                                    | 22 |

| Table 4.8. Pseudo-Dual Port Memory Sizes for 36 kb Memory for Lattice Nexus 2 Platform Devices | 22 |

| Table 4.9. Pseudo Dual-Port RAM Attributes for Lattice Nexus 2 Platform Devices                | 22 |

| Table 4.10. EBR-Based ROM Port Definitions                                                     | 25 |

| Table 4.11. ROM Memory Sizes for 36 kb Memory for Lattice Nexus 2 Platform Devices             | 25 |

| Table 4.12. ROM Attributes for Lattice Nexus 2 Platform Devices                                | 25 |

| Table 5.1. Port Names and Definitions for FIFO                                                 | 27 |

| Table 5.2. FIFO Attributes for Lattice Nexus 2 Platform Devices                                | 28 |

| Table 6.1. Port Names and Definitions for FIFO_DC                                              | 36 |

| Table 6.2. FIFO_DC Attributes for Lattice Nexus 2 Platform Devices                             | 37 |

| Table 7.1. PFU-Based Distributed Single-Port RAM Port Definitions                              | 48 |

| Table 7.2. Distributed_SPRAM Attributes for Lattice Nexus 2 Platform Devices                   | 48 |

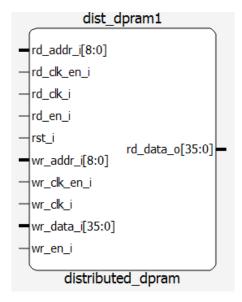

| Table 8.1. PFU-Based Distributed Dual-Port RAM Port Definitions                                | 51 |

| Table 8.2. Distributed_DPRAM Attributes for Lattice Nexus 2 Platform Devices                   | 51 |

| Table 9.1. PFU-Based Distributed ROM Port Definitions                                          | 53 |

| Table 9.2. Distributed ROM Attributes for Lattice Nexus 2 Platform Devices                     | 53 |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                         |

|--------------|----------------------------------------------------|

| ASCII        | American Standard Code for Information Interchange |

| ECC          | Error Correction Code                              |

| EBR          | Embedded Block RAM                                 |

| FIFO         | First In First Out                                 |

| GSR          | Global Set/Reset                                   |

| IP           | Intellectual Property                              |

| LSB          | Least Significant Bit                              |

| LUT          | Look Up Table                                      |

| MSB          | Most Significant Bit                               |

| PFU          | Programmable Function Unit                         |

| PMI          | Parameterizable Module Instantiation               |

| RAM          | Random Access Memory                               |

| ROM          | Read Only Memory                                   |

| RST          | Reset                                              |

| SRAM         | Static Random Access Memory                        |

| VHDL         | VHSIC Hardware Description Language                |

## 1. Introduction

This technical note discusses memory usage for the Lattice Semiconductor devices built on the Lattice Nexus™ 2 platform. It is intended to be used by design engineers as a guide when integrating the embedded block RAM (EBR)-based and Programmable Function Unit (PFU)-based memories for these device families in the Lattice Radiant™ software.

The architecture of these devices provides many resources for memory-intensive applications. The sysMEM™ EBR complements its distributed PFU-based memory. Single-port random access memory (RAM), dual-port RAM, pseudo dual-port RAM, First In First Out (FIFO), and read only memory (ROM) can be constructed using the EBR. The look-up tables (LUTs) and PFUs can implement distributed single-port RAM, dual-port RAM, and ROM. LUTs within PFUs can implement distributed single-port RAM, dual-port RAM, and ROM.

The capabilities of the EBR and PFU RAM are described in this document. You can utilize the memory primitives in three separate ways:

- Through the IP Catalog The IP Catalog interface allows you to specify the memory type and size required. The IP Catalog takes this specification and constructs a netlist to implement the desired memory by using one or more of the memory primitives.

- Through Parameterizable Module Inferencing (PMI) PMI allows you to skip the graphical interface and utilize the configurable memory primitives on-the-fly from the Lattice Radiant project navigator. You can set the parameters and the control signals needed either in Verilog or VHDL. The top-level design has the parameters defined and signals declared so the interface can automatically generate the black box during synthesis.

- Through the Instantiation of memory primitives Memory primitives are called directly by the top-level module

and instantiated in the design. This is an advanced method and requires a thorough understanding of memory

hook-ups and design interfaces.

The remainder of this document discusses these methods.

## 2. Memory Generation

You can use the IP Catalog to easily specify a variety of memories in the designs. These modules are constructed using one or more memory primitives along with general-purpose routing and LUTs as required.

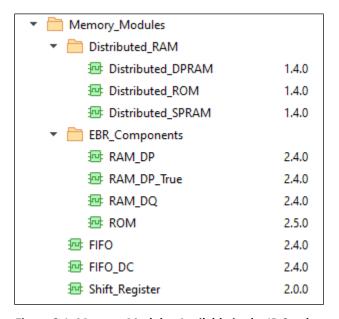

The available modules in the IP Catalog are as follows.

- Distributed memory modules

- Distributed pseudo dual-port RAM, Distributed DPRAM

- Distributed ROM, Distributed ROM

- Distributed single-port RAM, Distributed SPRAM

- EBR components or EBR-based modules

- Dual-port RAM, RAM\_DP\_TRUE

- Pseudo dual-port RAM, RAM\_DP

- Single-port RAM, RAM\_DQ

- Read only memory, ROM

- First In First Out memory, EBR-based or LUT-based

- Single-clock FIFO, FIFO

- Dual-clock FIFO, FIFO DC

Figure 2.1 shows the memory modules under the IP Catalog in the Lattice Radiant software.

Figure 2.1. Memory Modules Available in the IP Catalog

## 2.1. IP Catalog Flow

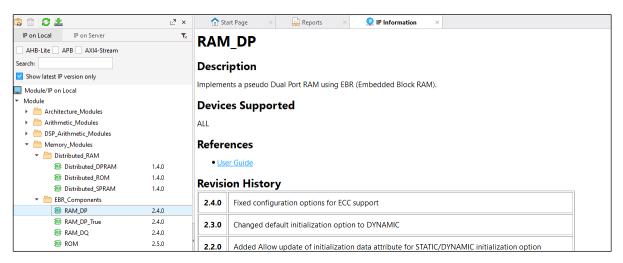

The IP Catalog allows you to generate, create, or open any of the available modules for Lattice Nexus 2 platform devices. In the Lattice Radiant software, choose **View** > **Show Views** > **IP Catalog**, or click the IP Catalog icon in the toolbar. This opens the IP Catalog window, as shown in Figure 2.2.

Figure 2.2. IP Catalog in the Lattice Radiant Software

The left section of the IP Catalog window includes the module tree. The memory modules are categorized as Distributed RAM, EBR Components, FIFOs, and Shift Register. The right section of the window shows the description of the module selected and links to the documentation for additional information.

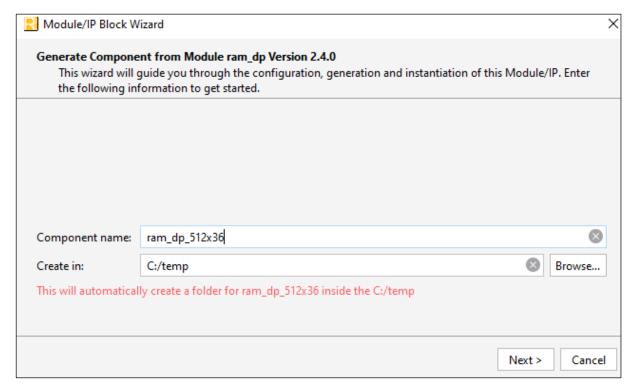

This section provides an example of generating an EBR-based pseudo dual-port RAM of size 512 x 36.

To generate an EBR-based pseudo dual-port RAM:

- 1. Double-click ram\_dp under EBR\_Components.

- 2. Fill out the module information, as shown in Figure 2.3.

- 3. Click the **Next** button.

Figure 2.3. Example: Generating Pseudo Dual-Port RAM ram\_dp Using the IP Catalog

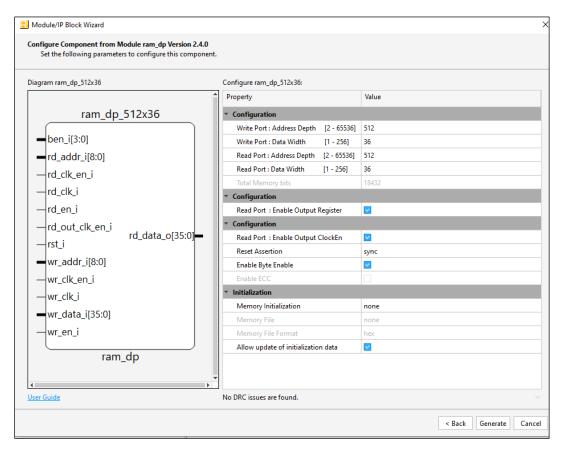

Customize the EBR-based DPRAM in the Module/IP Block Wizard window, as shown in Figure 2.4.

Figure 2.4. Example: Generating Pseudo Dual-Port RAM ram\_dp Module Customization – General Options

When all the options of the module being generated are filled out, click Generate.

Once this module is in the Lattice Radiant project, it can be instantiated within other modules.

## 2.2. Utilizing PMI

You can set the parameters and control signals needed in either Verilog or VHDL. The top-level design includes the defined memory parameters and declared signals. The interface can then automatically generate the black box during synthesis and the Lattice Radiant software can generate the netlist on-the-fly. Lattice memories are the same as industry standard memories, so you can get the parameters for each module from any memory-related guide, which is available through the Online Help system.

To do this, create a Verilog or VHDL behavior code for the memory and the synthesis tool automatically identifies it as memory and synthesizes it as a distributed or EBR memory. In general, memory sizes smaller than 1 kb are automatically mapped to the Distributed mode and those larger than 1 kb are implemented using EBRs. This default option can be overridden using the syn\_ramstyle or syn\_romstyle attribute in Synopsys Synplify Pro®.

## 2.3. Utilizing Direct Instantiation of Memory Primitives

Another way to use the memories in the designs is by directly instantiating the memory primitives for the Lattice Nexus 2 platform devices. When instantiating the primitives, you must work at the EBR block level. In case there is a need to have a memory that spans multiple modules, you are required to create the cascading memory on its own.

Lattice provides library files containing all of the primitives in a VHDL/Verilog file under the cae\_library/synthesis folder in the Lattice Radiant software installation folder.

## 3. Memory Features

The RAMs can be generated with error correction and byte enable features that mask selective bits. These features are available in the EBR-based RAM modules.

## 3.1. ECC in Memory Modules

An error correction code (ECC) is a system of adding redundant data or parity data to a message, such that it can be recovered by a receiver even when a number of errors are introduced, either during the process of transmission or on storage.

EBR-based memory modules IP Catalog allows you to implement ECC. There is a check box to enable ECC in the Configuration tab for the module.

Enable ECC check box allows error correction of single errors and detection of 2-bit errors. ECC write is supported only in x64 write mode with 8-bit ECC. ECC read may be performed in x1, x2, x4, x8, x16, x32, or x64 modes.

The two bits indicate the error, if any, and the following shows you what each of these bits means:

- one err det o = 1 indicates there is a 1-bit error that is fixed.

- two\_err\_det\_o = 1 indicates there is a 2-bit error that cannot be corrected.

The error flags are aligned to the output data and are available in the same cycle as the respective data.

## 3.2. Byte Enable

Byte enable is a feature available in selected RAM modules where you can mask the bytes written in the RAM. The byte enable feature is available only when data width is greater than nine bits. Each byte enable bit controls the write data operation enable for the nine bits. The selection can be made in the IP Catalog while generating the module.

Each bit of the BE signal corresponds to the corresponding 9-bit selection, starting from the LSB side. For example, if you add byte enable to a 72-bit wide RAM, then Table 3.1 explains how the written data, that is, Data In, is masked for a 9-bit byte size. Bits 8, 17, 26, 35, 44, 53, 62, and 71 are parity bits, which you ignore in x8, x16, x32, and x64 modes.

Table 3.1. Masked Data in Bits for a 9-Bit Byte Size

| Byte Enable Bit | Data In Bits that Get Masked<br>with 9-bit Byte Size |

|-----------------|------------------------------------------------------|

| ByteEn(0)       | Data(8:0)                                            |

| ByteEn(1)       | Data(17:9)                                           |

| ByteEn(2)       | Data(26:18)                                          |

| ByteEn(3)       | Data(35:27)                                          |

| ByteEn(4)       | Data(44:36)                                          |

| ByteEn(5)       | Data(53:45)                                          |

| ByteEn(6)       | Data(62:54)                                          |

| ByteEn(7)       | Data(71:63)                                          |

Note that in the ECC mode, all bytes of write data are written regardless of the value of ByteEn bits.

TN-02366-0.81

## 4. Memory Modules

The following sections discuss the different memory modules, the size of memory that each EBR block or the distributed primitive can support, and any special options for the module.

When you specify the width and depth of the memory in the IP Catalog, the tool generates the memory by depth cascading and/or width cascading, or EBR blocks, or distributed RAM primitives. The IP Catalog automatically allows you to create memories larger than the width and depth supported for each primitive.

## 4.1. Memory Cascading

For memory sizes that are smaller than what can fit in a single EBR block or the distributed primitive, the module utilizes the complete block or primitive.

For memory sizes larger than that of a single module, multiple modules are cascaded either in depth or width to create a larger module.

#### 4.1.1. Input and Output Register

The architecture of the EBR blocks in Lattice Nexus 2 platform devices is designed such that the inputs that go into the memory are always registered. This means that the input data and address are always registered at the input of the memory array. The output data of the memory is optionally registered at the output. You can choose this option by selecting the Enable Output Register check box in the IP Catalog while customizing the module.

Control signals like WE and Byte Enable that go into the EBR block are also registered.

#### 4.1.2. Reset

The EBRs also support the Reset signal. The Reset or RST signal only resets input and output registers of the RAM. It does not reset the contents of the memory. The Global set/reset (GSR) signal also controls the output registers.

#### 4.1.3. Timing

To correctly write to a memory cell in the EBR block, the correct address must be registered by the logic. Hence, it is important to note that while running the trace on the EBR blocks, there should be no setup and hold time violations on the address registers. Failing to meet these requirements can result in incorrect addressing and hence, lead to corruption of memory contents.

During a read cycle, a similar issue can occur such that the correct contents are not read if the address is not correctly registered in the memory.

A post-place and route timing report in the Lattice Radiant design software can be run to verify that no such timing errors occur. For more information, refer to the timing preferences in the Online Help document of the Lattice Radiant software.

#### 4.2. Single-Port RAM – EBR-Based

This section describes the single-port RAM, RAM\_DQ, which is EBR-based.

FPGAs built on the Lattice Nexus 2 platform support all the features of the single port RAM memory module, RAM\_DQ. The IP Catalog allows you to generate the Verilog-HDL or VHDL for the memory size as per design requirement.

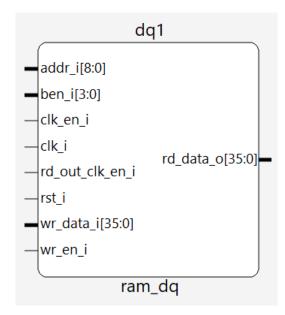

The IP Catalog generates the memory module, as shown in Figure 4.1.

Figure 4.1. Single-Port Memory Module Generated by the IP Catalog

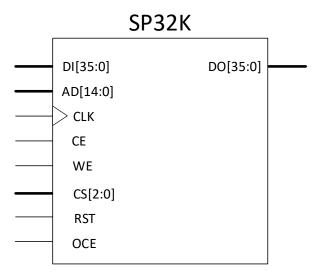

Figure 4.2 shows the primitive that can be instantiated for the single-port RAM. The primitive name is SP32K and it can be directly instantiated in the code. Check the details on the port and port names under the primitives available under cae library/synthesis folder in the Lattice Radiant software installation folder.

Note that each EBR can accommodate 36 kb of memory. If the memory required is larger than 36 kb, then cascading can be used using the CS port. In this case, the CS port is CS[2:0].

Figure 4.2. Single-Port RAM Primitive for Lattice Nexus 2 Platform Devices

The various ports and definitions for the single-port memory are listed in Table 4.1. The table below lists the corresponding ports for the module generated by the IP Catalog.

Table 4.1. EBR-Based Single-Port Memory Port Definitions<sup>1</sup>

| Port Name       | Direction | Width Description |                                                                       |

|-----------------|-----------|-------------------|-----------------------------------------------------------------------|

| clk_i           | Input     | 1                 | Clock                                                                 |

| rst_i           | Input     | 1                 | Reset                                                                 |

| clk_en_i        | Input     | 1                 | Input Clock Enable                                                    |

| rd_out_clk_en_i | Input     | 1                 | Read Output Register Enable Present if Enable Output Register == TRUE |

| wr_en_i         | Input     | 1 Write Enable    |                                                                       |

| wr_data_i       | Input     | Data Width        | Data Input                                                            |

| addr_i          | Input     | Address Width     | Address Bus                                                           |

| rd_data_o       | Output    | Data Width        | Data Output                                                           |

| ben_i           | Input     | Byte Enable Width | Byte Enable                                                           |

#### Note:

Each EBR block consists of 36,864 bits of RAM. See Table 4.2 for each EBR block's address value, x, and data value, y.

Table 4.2. Single-Port Memory Sizes for 36 kb Memory in Lattice Nexus 2 Platform Devices

| Single-Port Memory Size | Input Data | Output Data | Address [MSB:LSB] |

|-------------------------|------------|-------------|-------------------|

| 32,768 × 1              | DI         | DO          | AD[14:0]          |

| 16,384 × 2              | DI[1:0]    | DO[1:0]     | AD[13:0]          |

| 8,192 × 4               | DI[3:0]    | DO[3:0]     | AD[12:0]          |

| 4,096 × 9               | DI[8:0]    | DO[8:0]     | AD[11:0]          |

| 2,048 × 18              | DI[17:0]   | DO[17:0]    | AD[10:0]          |

| 1,024 × 36              | DI[35:0]   | DO[35:0]    | AD[9:0]           |

| 512 × 72                | DI[71:0]   | DO[71:0]    | AD[8:0]           |

Table 4.3 shows the various attributes available for the single-port memory, RAM\_DQ. You can select some of these attributes through the IP Catalog interface.

The ones without selectable options in the IP Catalog are handled by the engine. However, you can access these options if you are working with the direct primitive instantiation.

Table 4.3. Single-Port Memory Attributes in Lattice Nexus 2 Platform Devices

| Configuration Tab Attribute | Description                                                                                                        | Value                                                       | Default<br>Value |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|

| Address Depth               | Address depth of the read and write port.                                                                          | 2– <max can="" device="" fit="" in="" that="" the=""></max> | 512              |

| Data Width                  | Data word width of the read and write port.                                                                        | 1, 2, 4, 8/9, 16/18, or 36                                  | 36               |

| Enable Output<br>Register   | Data Out port, Q, can be configured as registered or not using this selection.                                     | True or false                                               | true             |

| Enable Output ClockEn       | Clock Enable for the output clock. This option requires enabling Enable Output Register.                           | True or false                                               | false            |

| Enable Byte Enable          | Allows you to select Byte Enable options.                                                                          | true or false                                               | false            |

| Reset Assertion             | Selection for the Reset to be synchronous or asynchronous to the Clock                                             | async or sync                                               | sync             |

| Memory Initialization       | Allows you to initialize the memories to all 1s, 0s, or to use a custom initialization by providing a memory file. | none, 0s, 1s, or file                                       | none             |

| Memory File                 | When Memory File is selected, you can browse to the memory file for custom initialization of RAM.                  | <u> </u>                                                    | _                |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-TN-02366-0.81

<sup>1.</sup> Address width is calculated from address depth.

| Configuration Tab Attribute | Description                                                                        | Value         | Default<br>Value |

|-----------------------------|------------------------------------------------------------------------------------|---------------|------------------|

| Memory File Format          | This option allows you to select if the memory file is formatted as binary or hex. | binary or hex | hex              |

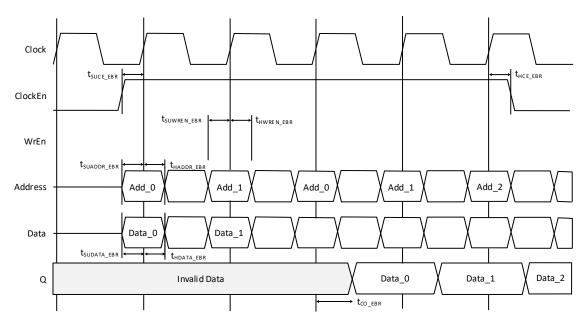

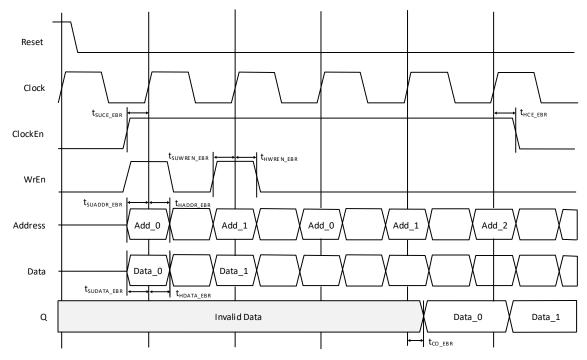

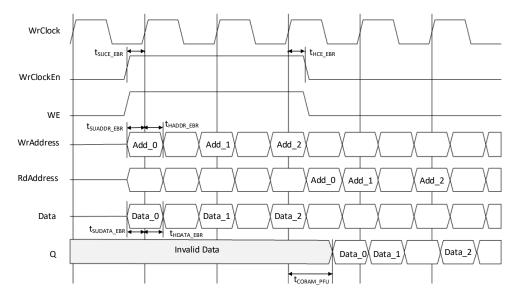

You have the option to enable the output registers for RAM\_DQ. The waveforms in Figure 4.3 and Figure 4.4 show the internal timing waveforms for the single-port RAM RAM\_DQ, without output registers and with output registers respectively.

Figure 4.3. Single-Port RAM Timing Waveform – without Output Registers

Figure 4.4. Single-Port RAM Timing Waveform - with Output Registers

#### 4.3. True Dual-Port RAM - EBR-Based

This section describes the true dual-port RAM, RAM\_DP\_True, which is EBR-based.

The EBR blocks in the Lattice Nexus 2 platform devices can be configured as true dual-port RAM, RAM\_DP\_TRUE. The IP Catalog allows you to generate the Verilog-HDL or VHDL for the memory size as per design requirements.

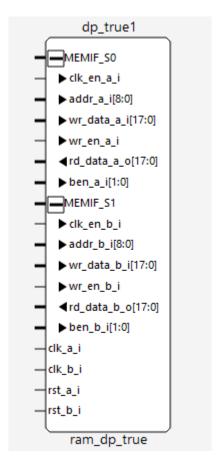

The IP Catalog generates the memory module, as shown in Figure 4.5.

Figure 4.5. True Dual-Port Memory Module Generated by the IP Catalog

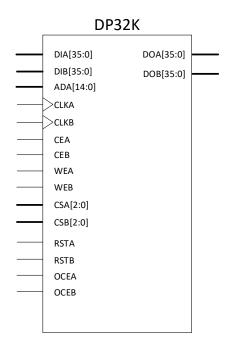

Figure 4.6 provides the primitive that can be instantiated for the true dual-port RAM. The primitive name is DP32K and it can be directly instantiated in the code. Check the details of the ports and port names under the primitives available under the cae library/synthesis folder in the Lattice Radiant software installation folder.

Note that each EBR can accommodate 36 kb of memory. If the memory required is larger than 36 kb, then, cascading can be used using the CS ports. In this case, the CS ports are CSA[2:0] and CSB[2:0].

Figure 4.6. True Dual-Port RAM Primitive for Lattice Nexus 2 Platform Devices

The various ports and definitions for the true dual-port RAM are listed in Table 4.4. The table lists the corresponding ports for the module generated by the IP Catalog.

**Table 4.4. EBR-Based True Dual-Port Memory Port Definitions**

| Port Name   | Direction | Width             | Description             |

|-------------|-----------|-------------------|-------------------------|

| clk_a_i     | Input     | 1                 | Clock for Port A        |

| rst_a_i     | Input     | 1                 | Reset for Port A        |

| clk_en_a_i  | Input     | 1                 | Clock Enable for Port A |

| wr_en_a_i   | Input     | 1                 | Write Enable for Port A |

| wr_data_a_i | Input     | Data Width        | Data Input for Port A   |

| addr_a_i    | Input     | Address Width     | Address Bus for Port A  |

| rd_data_a_o | Output    | Data Width        | Data Output for Port A  |

| ben_a_i     | Input     | Byte Enable Width | Byte Enable for Port A  |

| clk_b_i     | Input     | 1                 | Clock for Port B        |

| rst_b_i     | Input     | 1                 | Reset for Port B        |

| clk_en_b_i  | Input     | 1                 | Clock Enable for Port B |

| wr_en_b_i   | Input     | 1                 | Write Enable for Port B |

| wr_data_b_i | Input     | Data Width        | Data Input for Port B   |

| addr_b_i    | Input     | Address Width     | Address Bus for Port B  |

| rd_data_b_o | Output    | Data Width        | Data Output for Port B  |

| ben_b_i     | Input     | Byte Enable Width | Byte Enable for Port B  |

Each EBR block consists of 36,864 bits of RAM. See Table 4.5 for each EBR block's address value, w and x, and data value, y and z.

Table 4.5. Dual-Port Memory Sizes for 36 kb Memory for Lattice Nexus 2 Platform Devices

| Dual-Port<br>Memory Size | Input Data<br>Port A | Input Data<br>Port B | Output Data<br>Port A | Output Data<br>Port B | Address Port A | Address Port B |  |

|--------------------------|----------------------|----------------------|-----------------------|-----------------------|----------------|----------------|--|

| 32,768 × 1               | DataInA              | DataInB              | QA                    | QB                    | AddressA(14:0) | AddressB(14:0) |  |

| 16,384× 2                | DataInA(1:0)         | DataInB(1:0)         | QA(1:0)               | QB(1:0)               | AddressA(13:0) | AddressB(13:0) |  |

FPGA-TN-02366-0.81

| Dual-Port<br>Memory Size | Input Data<br>Port A | Input Data<br>Port B | Output Data<br>Port A | Output Data<br>Port B | Address Port A | Address Port B |

|--------------------------|----------------------|----------------------|-----------------------|-----------------------|----------------|----------------|

| 8,192 × 4                | DataInA(3:0)         | DataInB(3:0)         | QA(3:0)               | QB(3:0)               | AddressA(12:0) | AddressB(12:0) |

| 4,096 × 9                | DataInA(8:0)         | DataInB(8:0)         | QA(8:0)               | QB(8:0)               | AddressA(11:0) | AddressB(11:0) |

| 2,048 × 18               | DataInA(17:0)        | DataInB(17:0)        | QA(17:0)              | QB(17:0)              | AddressA(10:0) | AddressB(10:0) |

| 1,024 × 36               | DataInA(35:0)        | DataInB(35:0)        | QA(35:0)              | QB(35:0)              | AddressA(9:0)  | AddressB(9:0)  |

Table 4.6 shows the various attributes available for the true dual-port memory, RAM\_DP. You can select some of these attributes through the IP Catalog interface.

Table 4.6. True Dual-Port RAM Attributes for Lattice Nexus 2 Platform Devices

| Configuration Tab Attribute      | Description                                                                                                        | Value                                                       | Default<br>Value |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|

| Port A<br>Address Depth          | Port A Address depth of the read and write port                                                                    | 2- <max can="" device="" fit="" in="" that="" the=""></max> | 512              |

| Port A<br>Data Width             | Port A Data word width of the read and write port                                                                  | 1–512                                                       | 18               |

| Port B<br>Address Depth          | Port B Address depth of the read and write port                                                                    | 2- <max can="" device="" fit="" in="" that="" the=""></max> | 512              |

| Port B Data Width                | Port B Data word width of the read and write port                                                                  | 1–512                                                       | 18               |

| Port A Enable<br>Output Register | Port A Data Out port, QA, can be configured as registered or not using this selection.                             | true or false                                               | true             |

| Port B Enable<br>Output Register | Port B Data Out port, QB, can be configured as registered or not using this selection.                             | true or false                                               | true             |

| Byte Enable A                    | Allows you to select Byte Enable options.                                                                          | true or false                                               | false            |

| Byte Enable B                    | Allows you to select Byte Enable options.                                                                          | true or false                                               | false            |

| Reset Assertion A                | Selection for the Reset to be synchronous or asynchronous to the Clock                                             | async or sync                                               | sync             |

| Reset Assertion B                | Selection for the Reset to be synchronous or asynchronous to the Clock                                             | async or sync                                               | sync             |

| Memory<br>Initialization         | Allows you to initialize the memories to all 1s, 0s, or to use a custom initialization by providing a memory file. | none, 0s, 1s, or file                                       | none             |

| Memory File                      | When Memory File is selected, you can browse to the memory file for custom initialization of RAM.                  | _                                                           | _                |

| Memory File<br>Format            | This option allows you to select if the memory file is formatted as binary or hex.                                 | binary or hex                                               | hex              |

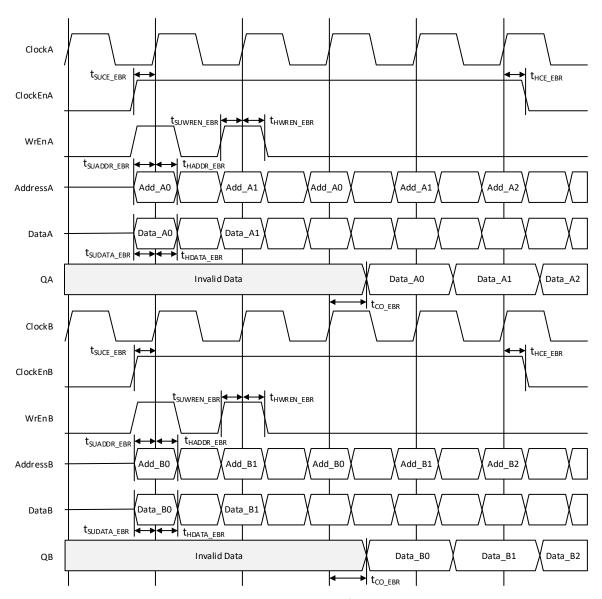

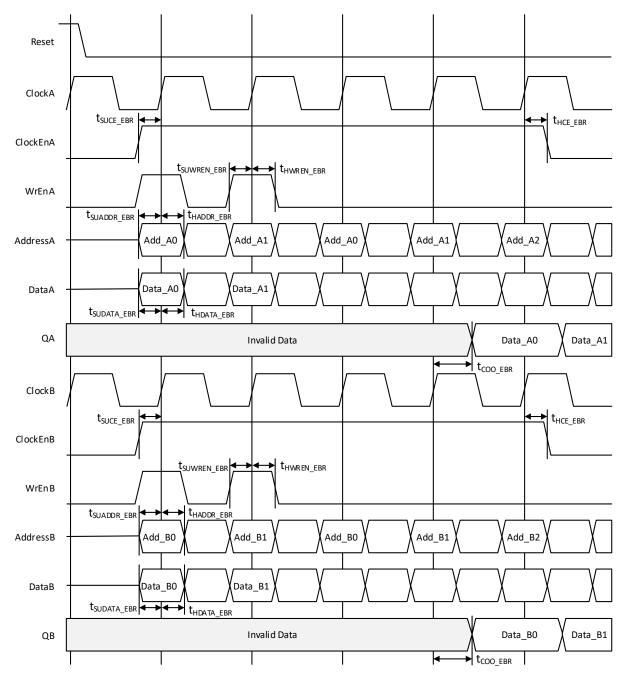

You have the option to enable the output registers for RAM\_DP\_TRUE. Waveforms in Figure 4.7 and Figure 4.8 show the internal timing waveforms for the true dual-port RAM RAM DP TRUE, without output registers and with output registers respectively.

Figure 4.7. True Dual-Port RAM Timing Waveform - without Output Registers

Figure 4.8. True Dual-Port RAM Timing Waveform – with Output Registers

#### 4.4. Pseudo Dual-Port RAM – EBR-Based

This section describes the pseudo dual-port RAM, RAM DP, which is EBR-based.

FPGAs built on the Lattice Nexus 2 platform support all the features of the pseudo dual-port RAM memory module, RAM\_DP. The IP Catalog allows you to generate the Verilog-HDL or VHDL for the memory size as per design requirement.

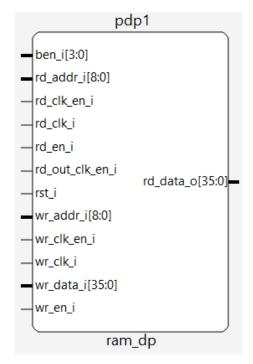

The IP Catalog generates the memory module, as shown in Figure 4.9.

Figure 4.9. Pseudo Dual-Port Memory Module Generated by the IP Catalog

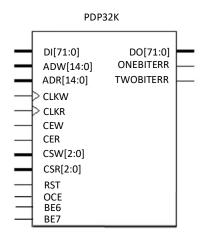

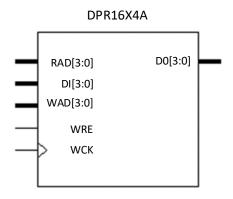

Figure 4.10 shows the primitive that can be instantiated for the pseudo-dual port RAM. The primitive name is PDP32K and it can be directly instantiated in the code. Check the details of the ports and port names under the primitives available under the cae\_library/synthesis folder in the Lattice Radiant software installation folder.

Note that each EBR can accommodate 36 kb of memory. If the memory required is larger than 36 kb, then cascading can be used using the CS ports. In this case, the CS ports are CSW[2:0] and CSR[2:0].

Figure 4.10. Pseudo-Dual Port RAM Primitive for Lattice Nexus 2 Platform Devices

The various ports and definitions for the pseudo dual-port memory are listed in Table 4.7. The table below lists the corresponding ports for the module generated by the IP Catalog.

**Table 4.7. EBR-Based True Dual-Port Memory Port Definitions**

| Port Name       | Direction | Width                    | Description                       |

|-----------------|-----------|--------------------------|-----------------------------------|

| wr_clk_i        | Input     | 1                        | Write Clock                       |

| rd_clk_i        | Input     | 1                        | Read Clock                        |

| rst_i           | Input     | 1                        | Reset                             |

| wr_clk_en_i     | Input     | 1                        | Write Clock Enable                |

| rd_en_i         | Input     | 1                        | Read Enable                       |

| rd_clk_en_i     | Input     | 1                        | Read Clock Enable                 |

| rd_out_clk_en_i | Input     | 1                        | Read Output Register Clock Enable |

| wr_en_i         | Input     | 1                        | Write Enable                      |

| ben_i           | Input     | Byte Enable Width        | Byte Enable                       |

| wr_data_i       | Input     | Write Port Data Width    | Write Data                        |

| wr_addr_i       | Input     | Write Port Address Width | Write Address                     |

| rd_addr_i       | Input     | Read Address Width       | Read Address                      |

| rd_data_o       | Output    | Read Port Data Width     | Read Data                         |

Each EBR block consists of 36,864 bits of RAM. See Table 4.8 for each EBR block's address value, w and x, and data value, y and z.

Table 4.8. Pseudo-Dual Port Memory Sizes for 36 kb Memory for Lattice Nexus 2 Platform Devices

| <b>Dual-Port Memory Size</b> | Input Data Write Port | Output Data Read Port | Address Write Port | Address Read Port |  |

|------------------------------|-----------------------|-----------------------|--------------------|-------------------|--|

| 32,768 × 1                   | Data                  | Q                     | WrAddress(14:0)    | RdAddress(14:0)   |  |

| 16,384 × 2                   | Data(1:0)             | Q(1:0)                | WrAddress(13:0)    | RdAddress(13:0)   |  |

| 8,192 × 4                    | Data(3:0)             | Q(3:0)                | WrAddress(12:0)    | RdAddress(12:0)   |  |

| 4,096 × 9                    | Data(8:0)             | Q(8:0)                | WrAddress(11:0)    | RdAddress(11:0)   |  |

| 2,048 × 18                   | Data(17:0)            | Q(17:0)               | WrAddress(10:0)    | RdAddress(10:0)   |  |

| 1,024 × 36                   | Data(35:0)            | Q(35:0)               | WrAddress(9:0)     | RdAddress(9:0)    |  |

| 512 × 72                     | Data(71:0)            | Q(71:0)               | WrAddress(8:0)     | RdAddress(8:0)    |  |

Table 4.9 shows the various attributes available for the pseudo dual-port memory, RAM\_DP. You can select some of these attributes through the IP Catalog interface.

Table 4.9. Pseudo Dual-Port RAM Attributes for Lattice Nexus 2 Platform Devices

| Configuration Tab Attribute | Description                                                                                                         | Value                 | Default Value |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|

| Read Port Address Depth     | Read Port Address depth of the read and write port                                                                  | 2–65536               | 512           |

| Read Port Data Width        | Read Port Data word width of the read and write port                                                                | 1–256                 | 36            |

| Write Port Address Depth    | Write Port Address depth of the read and write port                                                                 | 2-65536               | 512           |

| Write Port Data Width       | Write Port Data word width of the read and write port                                                               | 1–256                 | 36            |

| Enable Output Register      | Data Out port, Q, can be configured as registered or not using this selection.                                      | true or false         | true          |

| Enable Output ClockEn       | Clock Enable for the output clock This option requires enabling Enable Output Register.                             | true or false         | false         |

| Enable Byte Enable          | Allows you to select Byte Enable options.                                                                           | true or false         | false         |

| Enable ECC                  | This option allows you to enable error correction codes.                                                            | true or false         | false         |

| Reset Assertion             | Selection for the Reset to be synchronous or asynchronous to the Clock                                              | async or sync         | sync          |

| Memory Initialization       | Allows you to initialize the memories to all 1s, 0s, or to have a custom initialization by providing a memory file. | none, 0s, 1s, or file | none          |

| Configuration Tab Attribute | Description                                                                                       | Value         | Default Value |

|-----------------------------|---------------------------------------------------------------------------------------------------|---------------|---------------|

| Memory File                 | When Memory File is selected, you can browse to the memory file for custom initialization of RAM. | _             | _             |

| Memory File Format          | This option allows you to select if the memory file is formatted as binary or hex.                | binary or hex | hex           |

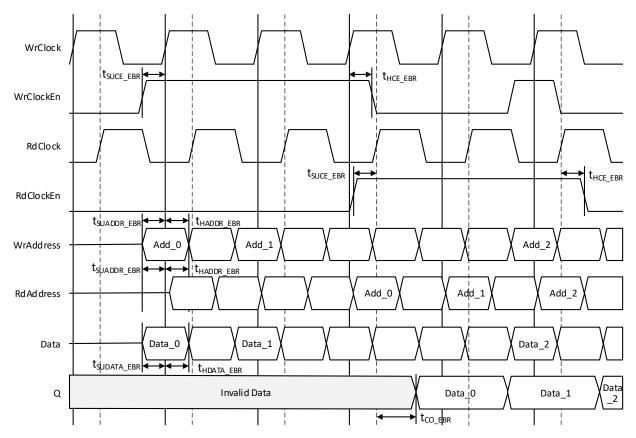

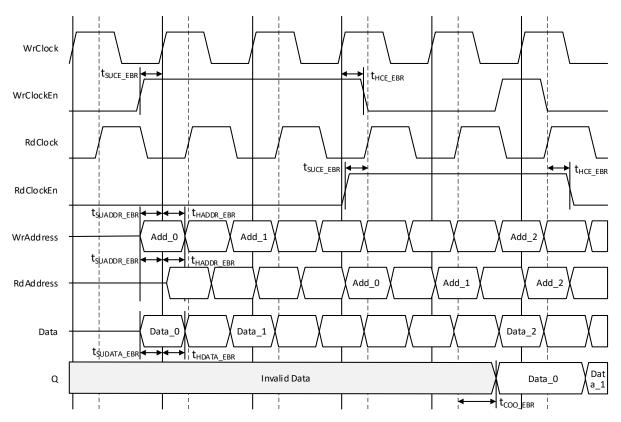

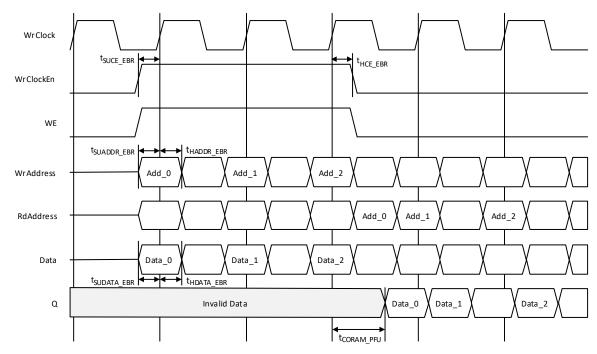

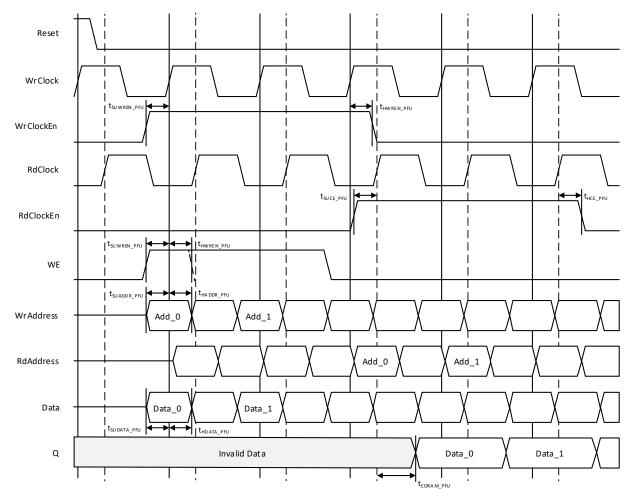

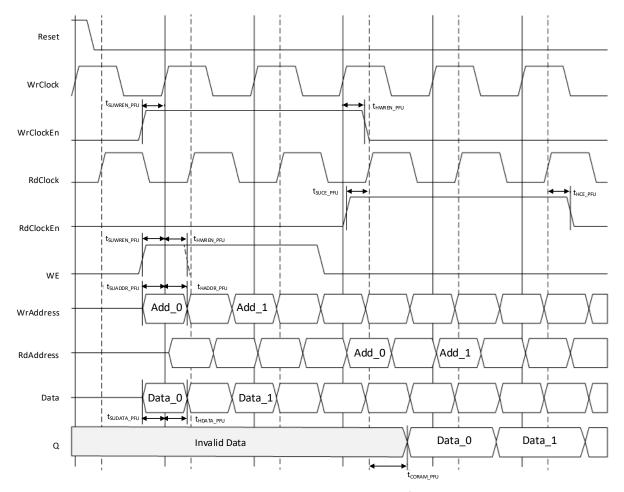

You have the option to enable the output registers for the pseudo-dual port RAM, RAM\_DP. Waveforms in Figure 4.11 and Figure 4.12 show the internal timing waveforms for the pseudo-dual port RAM without output registers and with output registers respectively.

Figure 4.11. Pseudo Dual-Port RAM Timing Diagram – without Output Registers

Figure 4.12. Pseudo Dual-Port RAM Timing Diagram – with Output Registers

#### 4.5. Read Only Memory – EBR-Based

This section describes the read only memory, ROM, which is EBR-based.

FPGAs built on the Lattice Nexus 2 platform support all the features of the ROM memory module. The IP Catalog allows you to generate the Verilog-HDL or VHDL for the memory size as per design requirements. You must provide the ROM memory content in the form of an initialization file.

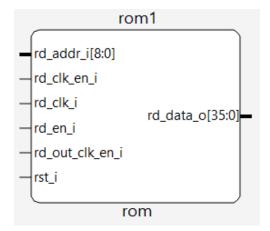

The IP Catalog generates the memory module, as shown in Figure 4.13.

Figure 4.13. ROM – Read Only Memory Module Generated by the IP Catalog

The various ports and definitions are listed in Table 4.10. The table below lists the corresponding ports for the module generated by the IP Catalog and for the ROM primitive.

**Table 4.10. EBR-Based ROM Port Definitions**

| Port Name       | Direction | Width         | Description         |

|-----------------|-----------|---------------|---------------------|

| rd_clk_i        | Input     | 1             | Clock               |

| rst_i           | Input     | 1             | Reset               |

| rd_en_i         | Input     | 1             | Read Enable         |

| rd_clk_en_i     | Input     | 1             | Input Clock Enable  |

| rd_out_clk_en_i | Input     | 1             | Output Clock Enable |

| rd_addr_i       | Input     | Address Width | Address Bus         |

| rd_data_o       | Input     | Data Width    | Data Output         |

When generating ROM using the IP Catalog, you must provide the initialization file to pre-initialize the contents of the ROM. These files are the \*.mem files and they can be of binary or hex formats. The initialization files are discussed in detail in the Initializing Memory section.

Each EBR block consists of 36,864 bits of RAM. See Table 4.11 for each EBR block's address value, x, and data value, y.

Table 4.11. ROM Memory Sizes for 36 kb Memory for Lattice Nexus 2 Platform Devices

| Dual-Port Memory Size | Output Data Read Port | Address Read Port |

|-----------------------|-----------------------|-------------------|

| 32,768 × 1            | Q                     | RdAddress(14:0)   |

| 16,384 × 2            | Q(1:0)                | RdAddress(13:0)   |

| 8,192 × 4             | Q(3:0)                | RdAddress(12:0)   |

| 4,096 × 9             | Q(8:0)                | RdAddress(11:0)   |

| 2,049 × 18            | Q(17:0)               | RdAddress(10:0)   |

| 1,024 × 36            | Q(35:0)               | RdAddress(9:0)    |

| 512 × 72              | Q(71:0)               | RdAddress(8:0)    |

Table 4.12 shows the various attributes available for the read only memory, ROM. You can select some of these attributes through the IP Catalog interface.

Table 4.12. ROM Attributes for Lattice Nexus 2 Platform Devices

| Configuration Tab Attribute | Description                                                                                                        | Value           | Default Value |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|---------------|

| Address Depth               | Address depth of the read and write port                                                                           | 2–65536         | 512           |

| Data Width                  | Data word width of the read and write port                                                                         | 1–512           | 36            |

| Enable Output Register      | Data Out port, Q, can be registered or not using this selection.                                                   | true or false   | true          |

| Enable Output ClockEn       | Enables read output clock.                                                                                         | true or false   | false         |

| Reset Assertion             | Selection for the Reset to be synchronous or asynchronous to the Clock                                             | async or sync   | sync          |

| Memory Initialization       | Allows you to initialize the memories to all 1s, 0s, or to use a custom initialization by providing a memory file. | 0s, 1s, or file | Os            |

| Memory File                 | When Memory File is selected, you can browse to the memory file for custom initialization of RAM.                  | _               | _             |

| Memory File Format          | This option allows you to select if the memory file is formatted as binary or hex.                                 | binary or hex   | hex           |

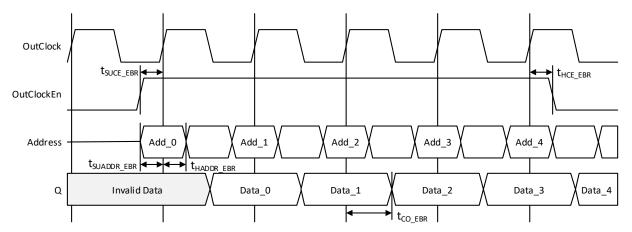

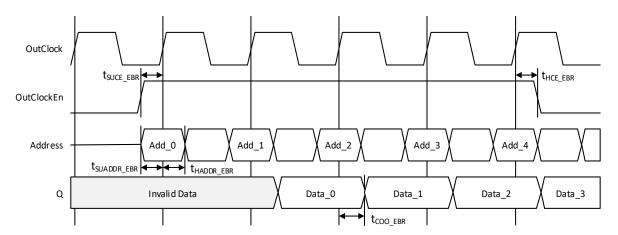

You have the option to enable the output registers for read only memory, ROM. Figure 4.14 and Figure 4.15 show the internal timing waveforms for ROM without output registers and with output registers respectively.

FPGA-TN-02366-0.81

Figure 4.14. ROM Timing Waveform – without Output Registers

Figure 4.15. ROM Timing Waveform – with Output Registers

## 5. FIFO Memory

Lattice Nexus 2 platform devices support two different types of FIFOs:

- Single-clock FIFO, FIFO

- Dual-clock FIFO, FIFO DC

The EBR blocks in Lattice Nexus 2 platform devices can be configured as LUT-based or EBR-based, as well as single-clock First In First Out memory, FIFO, or dual-clock First In First Out memory, FIFO\_DC. The IP Catalog allows you to generate the Verilog-HDL or VHDL netlist for various memory sizes depending on design requirements.

The IP Catalog generated FIFO modules and the operation are discussed in detail in the following sections.

## 5.1. Single-Clock FIFO – EBR-Based or LUT-Based

This section describes the single-clock FIFO, which is named FIFO and can be EBR-based or LUT-based.

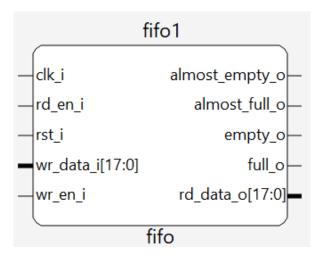

Figure 5.1 shows the module generated by the IP Catalog for FIFO.

Figure 5.1. FIFO Module Generated by the IP Catalog

The various ports and definitions for the FIFO are listed in Table 5.1.

Table 5.1. Port Names and Definitions for FIFO

| Port Name      | Direction | Width         | Description                                       |

|----------------|-----------|---------------|---------------------------------------------------|

| clk_i          | Input     | 1             | Write Clock                                       |

| rst_i          | Input     | 1             | Reset                                             |

| wr_en_i        | Input     | 1             | Write Enable                                      |

| rd_en_i        | Input     | 1             | Read Enable                                       |

| wr_data_i      | Input     | Data Width    | Write Data                                        |

| rd_data_o      | Output    | Data Width    | Read Data                                         |

| full_o         | Output    | 1             | Full Flag                                         |

| empty_o        | Output    | 1             | Empty Flag                                        |

| almost_full_o  | Output    | 1             | Almost Full Flag                                  |

| almost_empty_o | Output    | 1             | Almost Empty Flag                                 |

| data_cnt_o     | Output    | Address Width | Data Counter Width based on the MEM Address Width |

FPGA-TN-02366-0.81

#### Table 5.2. FIFO Attributes for Lattice Nexus 2 Platform Devices

| Configuration Tab Attribute     | Description                                                                                                                                                                                                                                                                                                                                            |                                                                      | Default Value |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|--|

| Implementation Type             | EBR-based or LUT-based                                                                                                                                                                                                                                                                                                                                 | EBR, LUT                                                             | EBR           |  |

| Address Depth                   | Address depth of the read and write port Values are powers of two.                                                                                                                                                                                                                                                                                     | 2- <max that<br="">can fit in the<br/>device&gt;</max>               | 1024          |  |

| Controller<br>Implementation    | FIFO controller implementation option  To enable the implementation type as LUT-based, or enable the Data Count output, you need to select LUT.                                                                                                                                                                                                        | LUT or HW                                                            | HW            |  |

| Enable FWFT                     | Enables the First Word Fall Through mode. This is only available in HW mode.                                                                                                                                                                                                                                                                           | true or false                                                        | false         |  |

| Data Width                      | Data word width of the read and write port                                                                                                                                                                                                                                                                                                             | 1–256                                                                | 18            |  |

| Enable Output Register          | Data Out port, Q, can be registered or not using this selection.                                                                                                                                                                                                                                                                                       | true or false                                                        | true          |  |

| Reset Assertion                 | Selection for the Reset to be synchronous or asynchronous to the Clock                                                                                                                                                                                                                                                                                 | async or sync                                                        | sync          |  |

| Enable Almost Empty Flag        | Enables the generation of the Almost Empty flag.                                                                                                                                                                                                                                                                                                       | true or false                                                        | true          |  |

| Almost Empty Assertion<br>Type  | This option allows you to select the type of threshold to be used for the Almost Empty flag. The static threshold is set by the constant parameter, while the dynamic threshold is set through the input ports.  The single threshold provides only the assertion level, while the dual threshold provides both the assertion and de-assertion levels. | Static-Single,<br>Static-Dual,<br>Dynamic-Single,<br>or Dynamic-Dual | Static-Dual   |  |

| Almost Empty Assert Level       | This option allows you to set the assertion level of the Almost Empty flag. This is applicable for the Static-Single/Static-Dual threshold mode.                                                                                                                                                                                                       | 1–Address<br>Depth                                                   | 1             |  |

| Almost Empty De-assert<br>Level | This option allows you to set the de-assertion level of the Almost Empty flag after it goes high. This is applicable only for the Static-Dual threshold mode.                                                                                                                                                                                          | 1–Address<br>Depth                                                   | 2             |  |

| Enable Almost Full Flag         | Enables the generation of the Almost Full flag.                                                                                                                                                                                                                                                                                                        | true or false                                                        | true          |  |

| Almost Full Assertion Type      | This option allows you to select the type of threshold to be used for the Almost Full flag. The Static threshold is set by the constant parameter, while the Dynamic threshold is set through the input ports.  The single threshold provides only the assertion level, while the dual threshold provides both the assertion and de-assertion levels.  | Static-Single,<br>Static-Dual,<br>Dynamic-Single,<br>or Dynamic-Dual | Static-Dual   |  |

| Almost Full Assert Level        | This option allows you to set the assertion level of the Almost Full flag. This is applicable for the Static-Single/Static-Dual threshold mode.                                                                                                                                                                                                        | 1–Address<br>Depth                                                   | 1023          |  |

| Almost Full De-assert<br>Level  | This option allows you to set the de-assertion level of the Almost Full flag after it goes high. This option is applicable only for the Static-Dual threshold mode.                                                                                                                                                                                    | 1–Address<br>Depth                                                   | 1022          |  |

| Enable Data Count               | This option allows you to enable the generation of the write data count.                                                                                                                                                                                                                                                                               | true or false                                                        | false         |  |

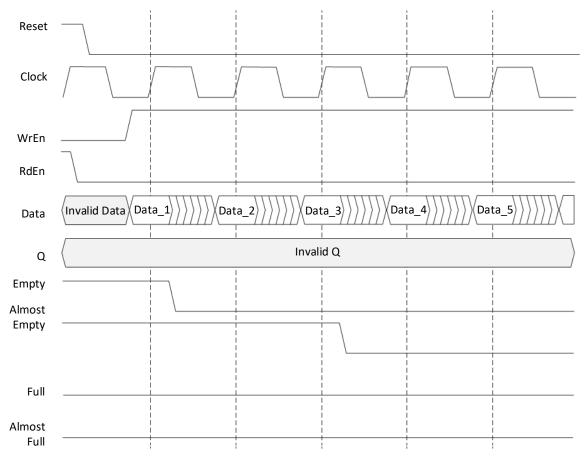

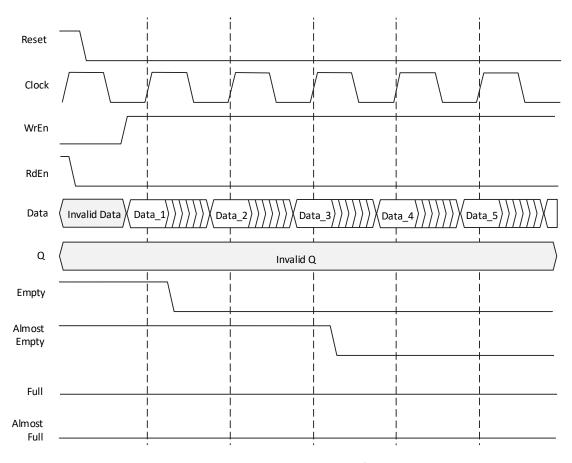

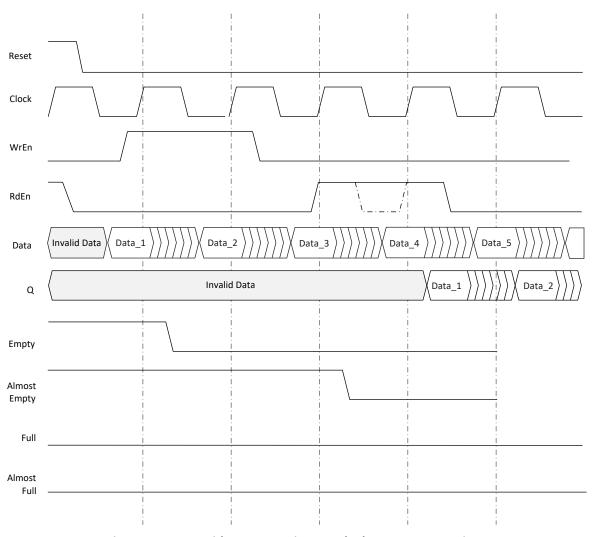

Let us first discuss the non-pipelined or the FIFO without output registers. Figure 5.2 shows the operation of the FIFO when it is empty and the data begins to be written into the FIFO.

Figure 5.2. FIFO Without Output Registers – Start of Data Write Cycle

The WrEn signal must be high to start writing to the FIFO. The Empty and Almost Empty flags are high to begin and the Full and Almost Full flags are low.

When the first data is written to the FIFO, the Empty flag de-asserts or goes low since the FIFO is no longer empty. In this figure, it is assumed that the Almost Empty flag setting is three, address location three. As such, the Almost Empty flag is de-asserted when the third address location is filled.

Assume that you continue to write into the FIFO to fill it. When the FIFO is filled, the Almost Full and Full flags are asserted. Figure 5.3 shows the behavior of these flags. In this figure, it is assumed that the FIFO depth is N.

Figure 5.3. FIFO Without Output Registers - End of Data Write Cycle

In Figure 5.3, the Almost Full flag is two locations before the FIFO is filled. The Almost Full flag is asserted when the N-2 location is written, and the Full flag is asserted when the last word is written into the FIFO.

Data\_X data inputs are not written because the FIFO is full, with the Full flag being high.

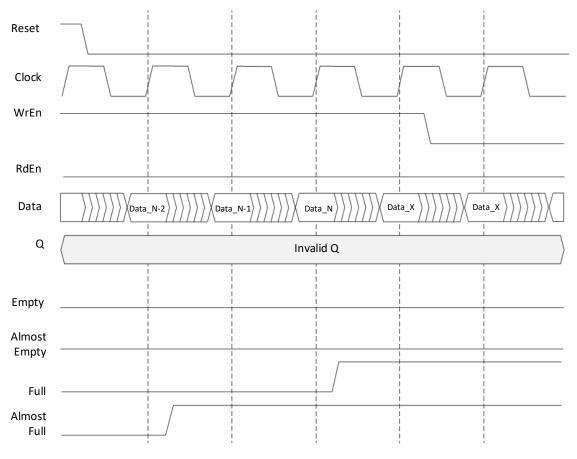

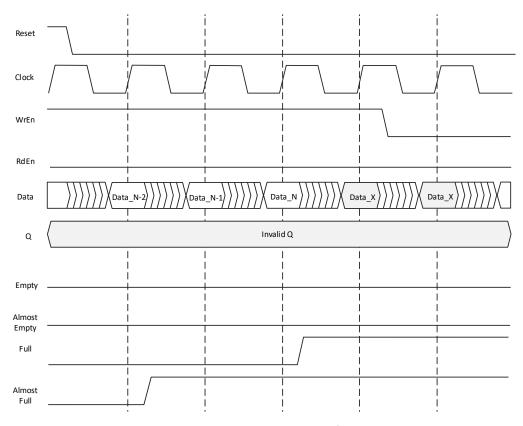

Examine the waveforms when the contents of the FIFO are read out. Figure 5.4 shows the start of the read cycle. The RdEn signal goes high and the data read starts. The Full and Almost Full flags are de-asserted.

Figure 5.4. FIFO Without Output Registers - Start of Data Read Cycle

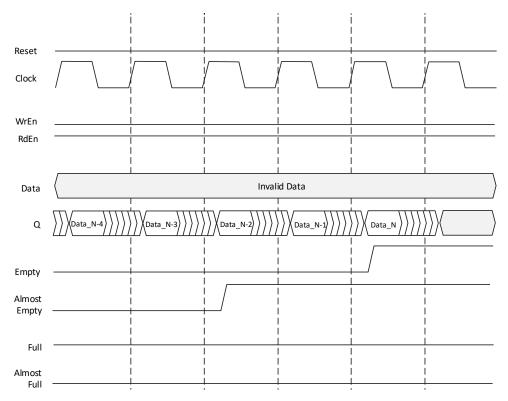

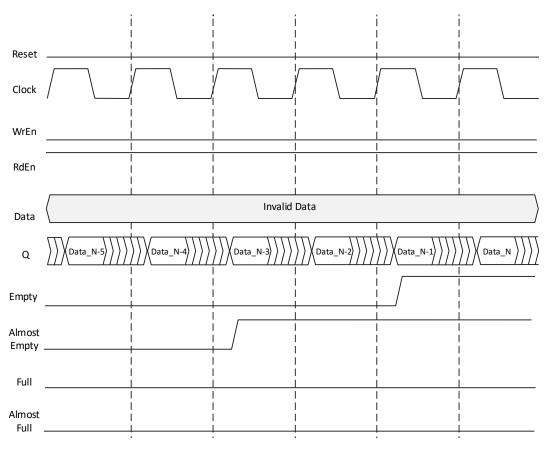

Similarly, as the data is read out and the FIFO is emptied, the Almost Empty and Empty flags are asserted (Figure 5.5).

Figure 5.5. FIFO Without Output Registers - End of Data Read Cycle

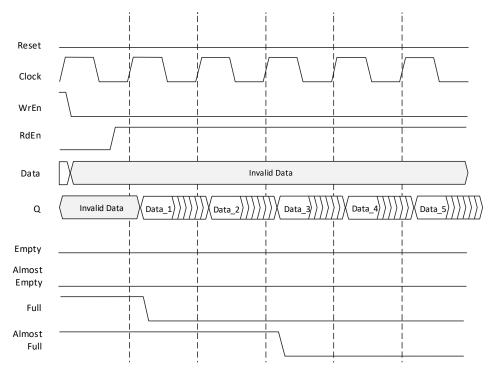

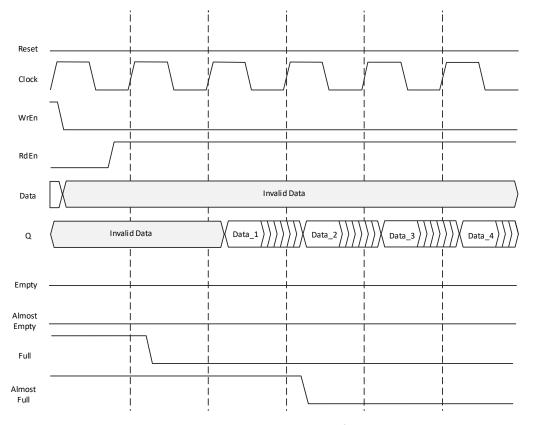

Figure 5.2 to Figure 5.5 show the behavior of non-pipelined FIFO or FIFO without output registers. When the registers are pipelined, the output data is delayed by one clock cycle. There is also an option for output registers to be enabled by the RdEn signal.

Figure 5.6 to Figure 5.9 show similar waveforms for the FIFO with output registers and Figure 5.10 shows the FIFO with output registers enable by RdEn. Note that flags are asserted and de-asserted with similar timing to the FIFO without output registers.

Only the data out Q is delayed by one clock cycle.

Figure 5.6. FIFO with Output Registers – Start of Data Write Cycle

Figure 5.7. FIFO with Output Registers – End of Data Write Cycle

Figure 5.8. FIFO with Output Registers – Start of Data Read Cycle

Figure 5.9. FIFO with Output Registers – End of Data Read Cycle

If the option enable output register with RdEn is selected, it still delays the data out by one clock cycle, as compared to the non-pipelined FIFO. RdEn must be high during that clock cycle, otherwise, the data takes an extra clock cycle when RdEn goes true.

Figure 5.10. FIFO with Output Registers and RdEn on Output Registers

## 6. Dual-Clock FIFO – EBR-Based or LUT-Based

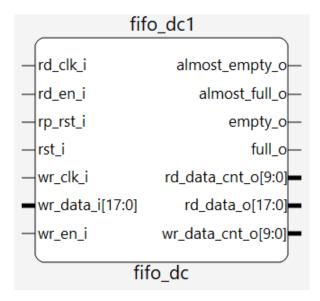

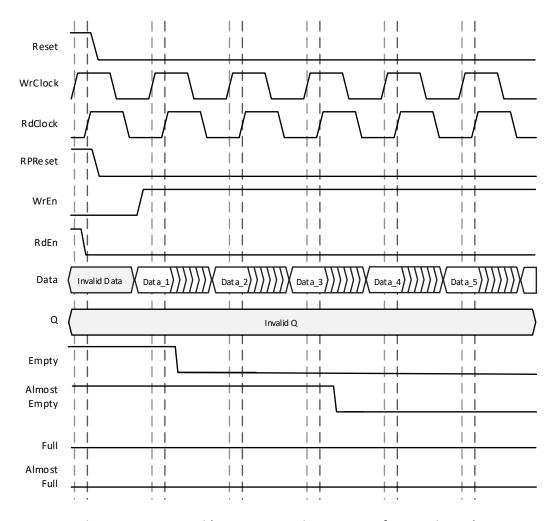

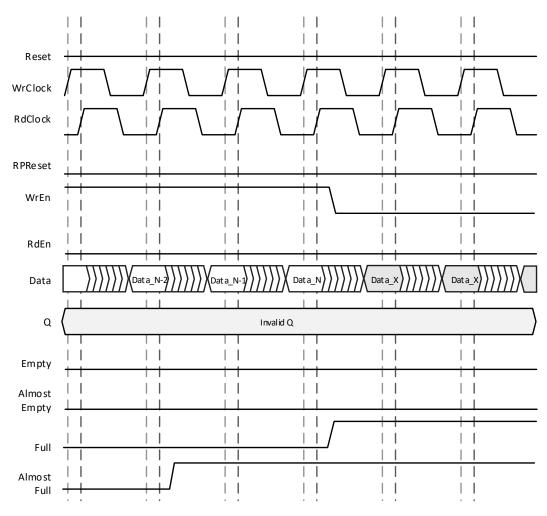

This section describes the dual-clock FIFO, FIFO\_DC, which can be EBR-based or LUT-based. Figure 6.1 shows the module generated by the IP Catalog for FIFO.

Figure 6.1. FIFO\_DC Module Generated by the IP Catalog

The various ports and definitions for the FIFO\_DC are listed in Table 6.1. The software attributes are listed in Table 6.2.

Table 6.1. Port Names and Definitions for FIFO\_DC

| Port Name      | Direction | Width         | Description        |

|----------------|-----------|---------------|--------------------|

| wr_clk_i       | Input     | 1             | Write Clock        |

| rd_clk_i       | Input     | 1             | Read Clock         |

| rst_i          | Input     | 1             | Reset              |

| rp_rst_i       | Input     | 1             | Read Pointer Reset |

| wr_en_i        | Input     | 1             | Write Enable       |

| rd_en_i        | Input     | 1             | Read Enable        |

| wr_data_i      | Input     | Data Width    | Write Data         |

| rd_data_o      | Output    | Data Width    | Read Data          |

| full_o         | Output    | 1             | Full Flag          |

| empty_o        | Output    | 1             | Empty Flag         |

| almost_full_o  | Output    | 1             | Almost Full Flag   |

| almost_empty_o | Output    | 1             | Almost Empty Flag  |

| wr_data_cnt_o  | Output    | Address Width | Write Data Counter |

| rd_data_cnt_o  | Output    | Address Width | Read Data Counter  |

FPGA-TN-02366-0.81

Table 6.2. FIFO\_DC Attributes for Lattice Nexus 2 Platform Devices

| Configuration Tab Attribute                             | Description                                                                                                                                                                                                                                                                                                                                        | Value                                                                | Default Value |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|

| Write Address Depth                                     | Address depth of the write port Values are powers of two.                                                                                                                                                                                                                                                                                          | 2- <max can="" device="" fit="" in="" that="" the=""></max>          | 512           |

| Write Data Width                                        | Data word width write port                                                                                                                                                                                                                                                                                                                         | 1–256                                                                | 18            |

| Read Address Depth                                      | Address depth of the read port.  Note: If not equal to Write Address Depth, the valid values are powers of two such that the ratio between Write and Read data widths is also powers of two.                                                                                                                                                       | 2- <max can="" device="" fit="" in="" that="" the=""></max>          | 512           |

| Read Data Width                                         | Data word width read port                                                                                                                                                                                                                                                                                                                          | 1–256                                                                | 18            |