# **eSPI Target IP**

IP Version: v2.2.0

# **User Guide**

FPGA-IPUG-02260-1.1

November 2024

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                                    |    |

|-------------------------------------------------------------|----|

| Abbreviations in This Document                              | 6  |

| 1. Introduction                                             |    |

| 1.1. Overview of the IP                                     | 7  |

| 1.2. Quick Facts                                            | 7  |

| 1.3. IP Support Summary                                     | 7  |

| 1.4. Features                                               | 7  |

| 1.5. Licensing and Ordering Information                     | 8  |

| 1.6. Hardware Support                                       | 8  |

| 1.7. Minimum Device Requirements                            | 8  |

| 1.8. Naming Conventions                                     | 8  |

| 1.8.1. Nomenclature                                         | 8  |

| 1.8.2. Signal Names                                         | 8  |

| 2. Functional Description                                   | 9  |

| 2.1. IP Architecture Overview                               | 9  |

| 2.2. Clocking                                               | 10 |

| 2.2.1. Clocking Overview                                    | 10 |

| 2.3. Reset                                                  | 10 |

| 2.3.1. Reset Overview                                       | 10 |

| 2.4. User Interfaces                                        | 11 |

| 2.5. Blocks                                                 | 11 |

| 2.5.1. AHB-Lite/APB                                         | 11 |

| 2.5.2. CSR                                                  | 12 |

| 2.6. Other IP Specific Blocks/Layers/Interfaces             | 12 |

| 2.6.1. eSPI Commands                                        |    |

| 2.6.2. Virtual Wire – Simple Implementation                 | 12 |

| 2.6.3. Virtual Wire – GPIO Expander                         |    |

| 2.6.4. eSPI Avail Status Valid Register Bits                |    |

| 2.6.5. eSPI Free Status Valid Register Bits                 |    |

| 2.6.6. Program Flow for Writing Data to FIFO                | 16 |

| 2.6.7. Program Flow for Reading Data from FIFO              | 17 |

| 2.6.8. Program Flow for Using GET Channel Commands          | 18 |

| 2.6.9. Program Flow for Using PUT Channel Commands          |    |

| 2.7. Error Handling                                         | 24 |

| 3. IP Parameter Description                                 | 25 |

| 3.1. General                                                | 25 |

| 3.2. Capabilities and Configuration Register Default Values | 26 |

| 4. Signal Description                                       | 27 |

| 4.1. Clock Interface                                        | 28 |

| 5. Register Description                                     | 29 |

| 5.1. Device Identification                                  | 29 |

| 5.2. General Capabilities and Configurations                | 29 |

| 5.2.1. Channel 0 Capabilities and Configurations            | 31 |

| 5.2.2. Channel 1 Capabilities and Configurations            | 33 |

| 5.2.3. Channel 2 Capabilities and Configurations            | 34 |

| 5.2.4. Channel 3 Capabilities and Configurations            | 35 |

| 5.2.5. eSPI Target IP Registers                             | 36 |

| 6. Example Design                                           |    |

| 6.1. Example Design Supported Configuration                 |    |

| 6.2. Overview of the Example Design and Features            |    |

| 6.3. Example Design Components                              |    |

| 6.4. Simulating the Example Design                          |    |

|                                                             |    |

| 7. Designing with the IP                                         | 48 |

|------------------------------------------------------------------|----|

| 7.1. Generating and Instantiating the IP                         | 48 |

| 7.1.1. Generated Files and File Structure                        | 50 |

| 7.2. Design Implementation                                       | 52 |

| 7.3. Timing Constraints                                          | 52 |

| 7.4. Specifying the Strategy                                     | 52 |

| 7.5. Running Functional Simulation                               | 52 |

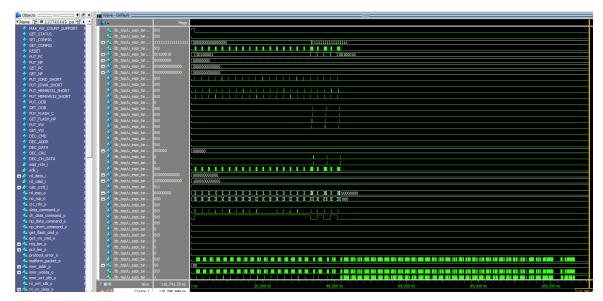

| 7.5.1. Simulation Results                                        | 53 |

| Appendix A. Resource Utilization                                 | 54 |

| References                                                       | 55 |

| Technical Support Assistance                                     | 56 |

| Revision History                                                 | 57 |

| Figures                                                          |    |

| Figure 2.1. Lattice ESPI Target X4 Core Block Diagram            |    |

| Figure 2.2. eSPI Target IP Clock Domain Block Diagram            |    |

| Figure 2.3. Virtual Wire IN Interface                            |    |

| Figure 2.4. Virtual Wire OUT Interface                           |    |

| Figure 2.5. Select GPIO Input First                              |    |

| Figure 2.6. Select GPIO Output First                             |    |

| Figure 2.7. Input or Output Not Divisible by Four                |    |

| Figure 2.8. GPIO Expander Input                                  |    |

| Figure 2.9. GPIO Expander Output                                 |    |

| Figure 2.10. PUT VWIRE Interrupt Assertion Timing                |    |

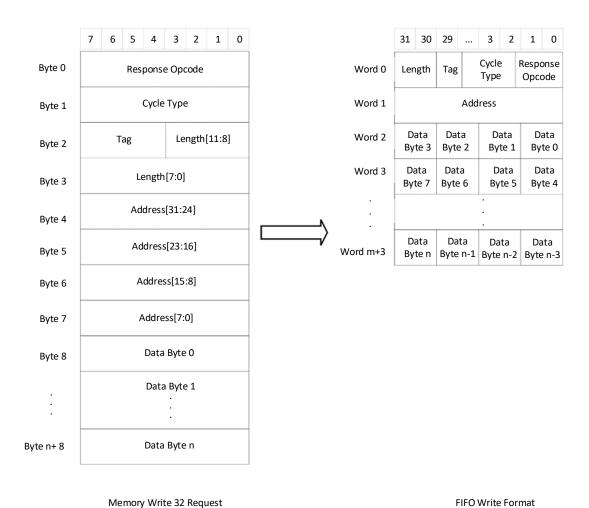

| Figure 2.11. FIFO Write Format                                   |    |

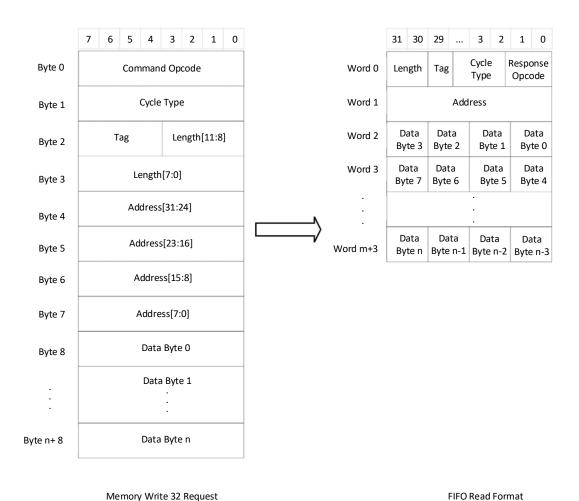

| Figure 2.12. FIFO Read Format                                    |    |

| Figure 2.13. GET PC – Completion with DataFigure 2.14. GET VWIRE |    |

| Figure 2.15. GET OOB                                             |    |

| Figure 2.16. GET FLASH NP – Flash Write                          |    |

| Figure 2.17. PUT PC Command                                      |    |

| Figure 2.18. PUT VWIRE                                           |    |

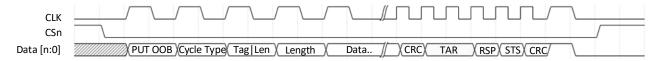

| Figure 2.19. PUT OOB – Completion with data                      |    |

| Figure 2.20. PUT FLASH C – Completion with Data                  |    |

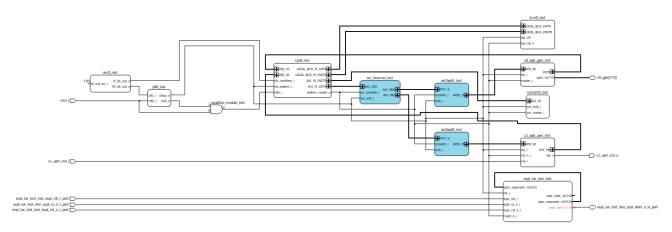

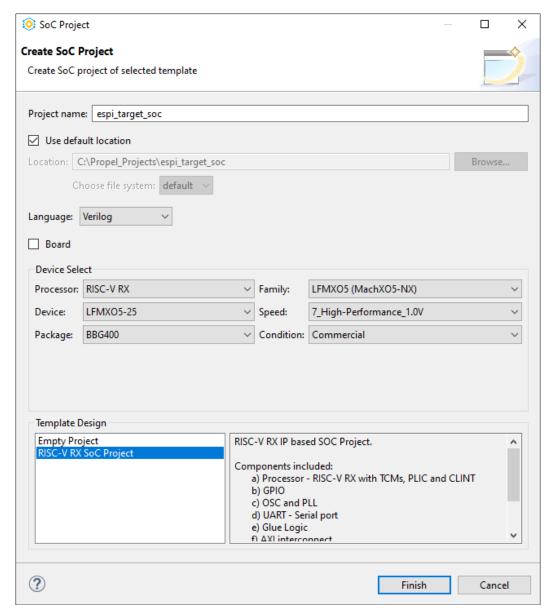

| Figure 6.1. eSPI Target IP in Propel SoC Project                 |    |

| Figure 6.2. Create SoC Project                                   |    |

| Figure 6.3. Instantiating eSPI Target IP Module                  |    |

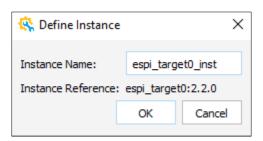

| Figure 6.4. Defining Instances                                   |    |

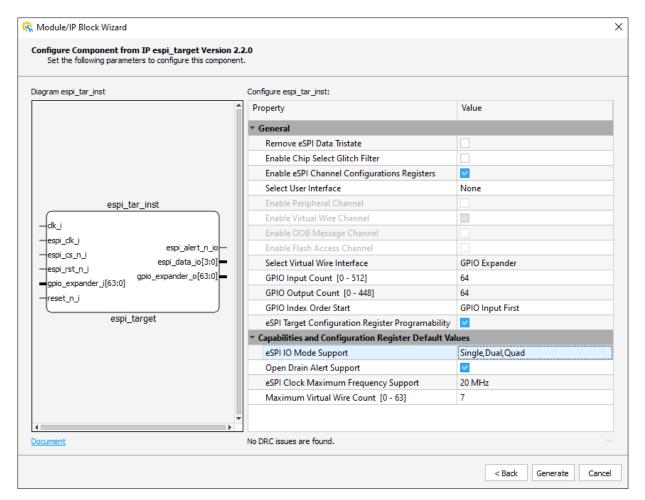

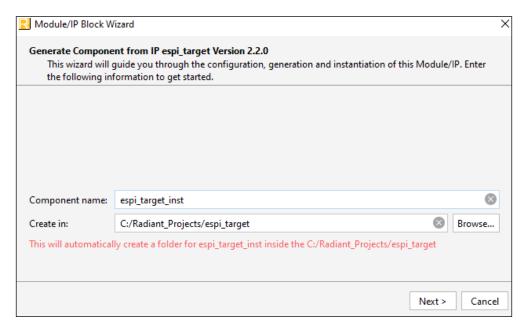

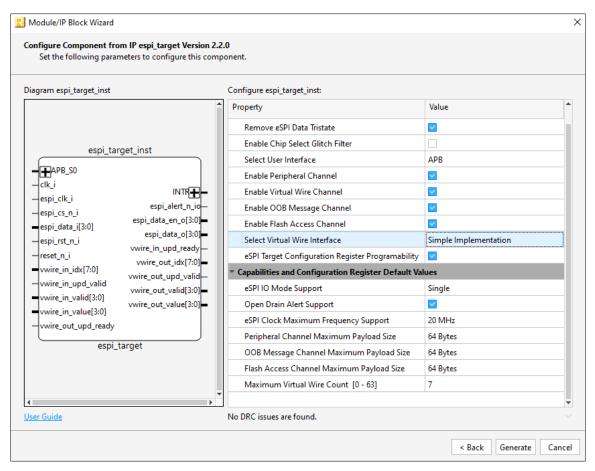

| Figure 7.1. Module/IP Block Wizard                               |    |

| Figure 7.2. IP Configuration                                     |    |

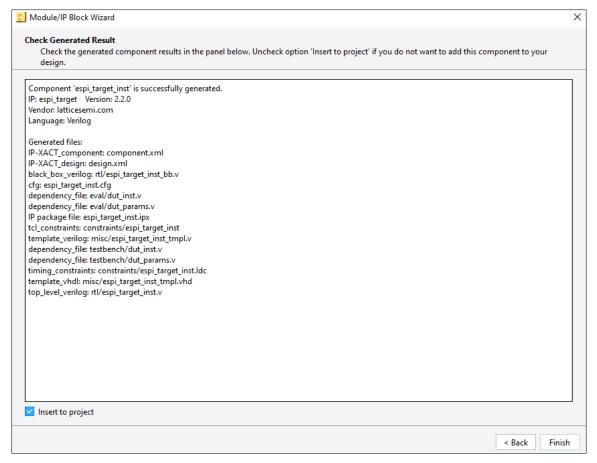

| Figure 7.3. Check Generated Result                               |    |

| Figure 7.4. Timing Constraint File (.pdc) for the eSPI Target IP |    |

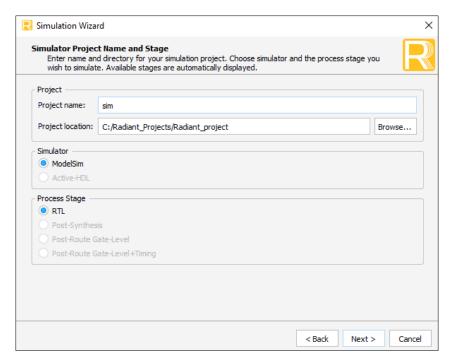

| Figure 7.5. Simulation Wizard                                    |    |

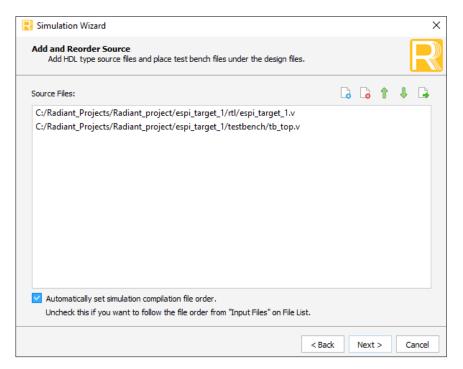

| Figure 7.6. Add and Reorder Source                               | 52 |

| Figure 7.7. Simulation Waveform                                  | 53 |

|                                                                  |    |

## **Tables**

| Table 1.1. Summary of eSPI Target IP                                    | 7  |

|-------------------------------------------------------------------------|----|

| Table 1.2. eSPI Target IP Support Readiness                             | 7  |

| Table 2.1. User Interfaces and Supported Protocols                      | 11 |

| Table 2.2. AHB-Lite Signal                                              |    |

| Table 3.1. General Attributes                                           | 25 |

| Table 3.2. Capabilities and Configuration Register Attributes           | 26 |

| Table 4.1 Clock Ports                                                   | 28 |

| Table 5.1. Summary of eSPI Target IP Core Registers                     | 29 |

| Table 5.2. Access Type Definition                                       |    |

| Table 6.1. eSPI Target IP Configuration Supported by the Example Design | 43 |

| Table 7.1. Generated File List                                          |    |

# **Abbreviations in This Document**

A list of acronyms and abbreviations used in this document.

| Abbreviation | Definition                                                 |

|--------------|------------------------------------------------------------|

| AXI          | Advanced Extensible Interface                              |

| AHB-Lite     | Advanced High-Performance Bus – Lite                       |

| APB          | Advanced Peripheral Bus                                    |

| CRC          | Cyclic Redundancy Check                                    |

| CS           | Chip Select                                                |

| CSR          | Configuration and Status Registers                         |

| EBR          | Embedded Block RAM                                         |

| eSPI         | Enhanced Serial Peripheral Interface                       |

| FIFO         | First In First Out                                         |

| FPGA         | Field Programmable Gate Array                              |

| GPIO         | General Purpose Input/Output                               |

| GUI          | Graphical User Interface                                   |

| IP           | Intellectual Property                                      |

| LSE          | Lattice Synthesis Engine                                   |

| LUT          | Look Up Table                                              |

| MC           | Micro-Controller, RISC-V for Micro-Controller Applications |

| ООВ          | Out of Band                                                |

| PDC          | Physical Design Constraint                                 |

| PLL          | Phase-Locked Loop                                          |

| RISC-V       | Reduced Instruction Set Computer-V (Five)                  |

| Rx           | Receiver                                                   |

| SDK          | Software Development Kit                                   |

| SPI          | Serial Peripheral Interface                                |

| SoC          | System on Chip                                             |

| Tx           | Transmitter                                                |

| VW           | Virtual Wire                                               |

## 1. Introduction

This document contains all the information about the Lattice Enhanced Serial Peripheral Interface (eSPI) Target IP. As this IP is compliant with Intel eSPI specifications, details about the specification are not discussed in this document.

For the Intel eSPI specifications, you can refer to Enhanced Serial Peripheral Interface (eSPI) Interface Base Specification (for Client and Server Platforms).

### 1.1. Overview of the IP

eSPI Target IP is compliant with the Intel eSPI specifications. It has its own virtual wire channel in the user interface while implementing peripheral channels, namely, Out of Band (OOB) Message Channel and Flash Access Channel in FIFO that are accessible by the Advanced Peripheral Bus (APB) or Advanced High-Performance Bus – Lite (AHB-Lite) interface.

### 1.2. Quick Facts

Table 1.1. Summary of eSPI Target IP

| ID De contracto      | Supported FPGA Family    | MachXO5™-NX, Mach™-NX, MachXO3D™, MachXO3™, and MachXO2™                                                    |  |

|----------------------|--------------------------|-------------------------------------------------------------------------------------------------------------|--|

| IP Requirements      | IP Changes               | For a list of changes to the IP, refer to the eSPI Target IP Release Notes (FPGA-RN-02002).                 |  |

|                      | Targeted Devices         | LFMXO5, LFMNX, LAMXO3D, LCMXO3D, LAMXO3LF, LCMXO3LF, LCMXO3L, and LCMXO2                                    |  |

| Resource Utilization | Supported User Interface | APB, AHB-Lite, Virtual Wire Interface                                                                       |  |

|                      | Resources                | Refer to Table A.1, Table A.2, Table A.3, and Table A.4.                                                    |  |

|                      | Lattice Implementation   | IP v.2.2.0 – Lattice Radiant™ Software 2023.2 or later,<br>Lattice Propel™ Builder Software 2023.2 or later |  |

| Design Tool Support  | Synthesis                | Lattice Synthesis Engine (LSE) Synopsys® Synplify Pro for Lattice                                           |  |

|                      | Simulation               | For a list of supported simulators, see the Lattice Radiant Software User Guide.                            |  |

## 1.3. IP Support Summary

Table 1.2. eSPI Target IP Support Readiness

| <b>Device Family</b> | IP          | Rank   | eSPI Data Width | Data Rate (Mbps) | Radiant Timing Model | Hardware Validated |

|----------------------|-------------|--------|-----------------|------------------|----------------------|--------------------|

|                      |             | Single | X1              | 7 to 126         | Preliminary          | Yes                |

| MachXO5-NX           | eSPI Target | Dual   | X2              | 15 to 132        | Preliminary          | Yes                |

|                      |             | Quad   | X4              | 33 to 265        | Preliminary          | Yes                |

#### 1.4. Features

Key features of the eSPI Target IP include:

- eSPI Base Specification Revision 1.0 features

- Supports all eSPI commands except Short Read commands.

- Supports all required error detection in eSPI specification.

- Supports Single, Dual, and Quad SPI mode.

- Cyclic Redundancy Check (CRC)

- No response error detection in eSPI command

- Fatal error detection in eSPI command

- Supports APB/AHB-Lite user interface.

- Supports peripheral channel transactions controlled by the host using the APB/AHB-Lite interface.

- Supports OOB message channel transactions controlled by the host using the APB/AHB-Lite interface.

- Supports flash access channel transactions controlled by the host using the APB/AHB-Lite interface.

- Simple implementation interface for virtual wire channel transactions

- General purpose input/output (GPIO) expander interface for virtual wire channel transactions

- Soft resets for configuration and status registers (CSR), Serial Peripheral Interface(SPI), and FIFO

Note: The following features are not supported in this IP:

- Optional non-fatal error detection of the eSPI target

- Soft reset by writing zero to the enable bit of the channels. Refer to the Channel Capabilities and Configurations section

- Peripheral Short Read commands. This IP version responds with NON-FATAL ERROR response to peripheral channel Short Read commands.

## 1.5. Licensing and Ordering Information

The eSPI Target IP is provided at no additional cost with the Lattice Radiant software.

## 1.6. Hardware Support

Refer to the Example Design section for more information on the board used.

## 1.7. Minimum Device Requirements

There is no limitation in device speed grade for the use of eSPI Target IP. See the maximum clock frequency in the Clocking section for more details.

## 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.8.2. Signal Names

- \_n are active low, asserted when value is logic 0.

- \_i are input signals.

- o are output signals.

- \_io are bidirectional signals.

9

# 2. Functional Description

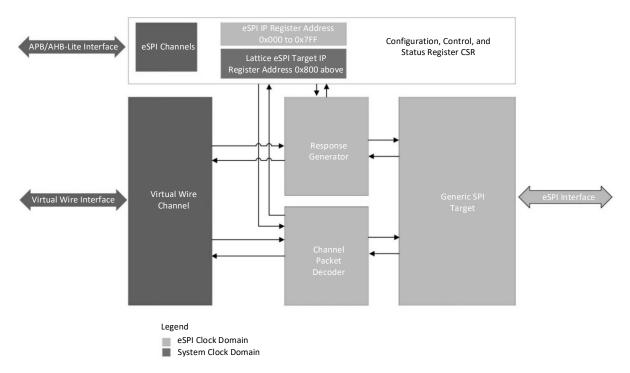

### 2.1. IP Architecture Overview

#### eSPI Target with Common Channel Interface 25 MHz-100 MHz eSPI Target Top clk i FIFO Mapping Configuration, Control, and Status Register (CSR) APB/AHB-Lite Interface (Optional) Generic SPI Target cfg\_spi\_io\_width[1:0] 20 MHz-66 MHz wr\_valid sclk\_i wr\_ready espi\_rst\_n\_i Generator espi\_cs\_n\_i wr\_data[7:0] Virtual Wire Interface/GPIO Expander Serializer Tx<sup>I</sup>Queue wr\_eop CRCS (Optional) Generato espi\_data\_io[3:0] Virtual Wire De-Serializer espi\_alert\_n\_o rd\_ready rd \_valid rd\_data [7:0] RxiQueue Control SM rd\_eop Channel calc\_crc[7:0] GPIO Decoder int\_alert Expander (Optional)

Figure 2.1. Lattice ESPI Target X4 Core Block Diagram

The eSPI Target IP includes the following components:

- APB/AHB-Lite Interface

- Virtual Wire Channel

- CSR

- Response Generator

- Channel Packet Decoder

- Generic SPI Target

## 2.2. Clocking

Figure 2.2. eSPI Target IP Clock Domain Block Diagram

### 2.2.1. Clocking Overview

- System Clock: clk\_i

- Supported frequency range: 25–100 MHz

- System Clock must be faster than eSPI Clock.

- eSPI Clock: espi\_clk\_i

- Supported frequency range: 20–66 MHz

### 2.3. Reset

There are two resets for the eSPI Target IP. One is eSPI active-low reset, espi\_reset\_n. The other is system active-low reset, reset\_n.

## 2.3.1. Reset Overview

Both resets are asynchronous reset. The reset assertion can be asynchronous but reset deassertion is synchronized inside the eSPI Target IP. When deasserted, output ports and registers are forced to their reset values.

## 2.4. User Interfaces

**Table 2.1. User Interfaces and Supported Protocols**

| User Interface                           | Supported Protocols   | Description                                                                                                                                                                                                                                                                                                                                                                |  |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CSR Interface                            | AHB-Lite              | The AHB-Lite interface is used in this IP for register and memory access. See Signal Description and Register Description for more details.  For AHB-Lite interface, refer to AMBA 3 AHB-Lite Protocol Specification for information and timing diagram of the AHB-Lite interface.  • Write transaction has no wait state;  • Read transaction has one to two wait states. |  |

|                                          | АРВ                   | The APB interface is used in this IP for register and memory access. See Signal Description and Register Description for more details. For APB Interface, refer to AMBA 3 APB Protocol Specification for information and timing diagram of the APB interface.                                                                                                              |  |

|                                          | Simple Implementation | The simple implementation supports virtual wire feature with minimal usage of I/O ports in the eSPI Target IP. For more information, refer to Virtual Wire – Simple Implementation.                                                                                                                                                                                        |  |

| Virtual Wire Interface                   | GPIO Expander         | The GPIO expander virtual wire interface implements the GPIO expander feature of the eSPI Target specification. Enabling this feature requires more resource than the simple implementation. For more details, refer to Virtual Wire – GPIO Expander.                                                                                                                      |  |

| Device Receiver/Transmitter<br>Interface | eSPI                  | The eSPI interface can receive and send using all the eSPI commands stated in the Intel eSPI specifications.                                                                                                                                                                                                                                                               |  |

## 2.5. Blocks

## 2.5.1. AHB-Lite/APB

### 2.5.1.1. APB

The APB target in this IP is compliant with the AMBA APB Protocol Specification.

## 2.5.1.2. AHB-Lite

The AHB-Lite in this IP only supports single burst type.

Table 2.2. AHB-Lite Signal

| Signal Name | Direction | Description                                                                                               |  |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------|--|

| HCLK        | In        | AHB-Lite signal timing                                                                                    |  |

| HRESETn     | In        | Active-low reset                                                                                          |  |

| HADDR[31:0] | In        | Read/Write address                                                                                        |  |

| HBURST[2:0] | In        | Indicates the burst type. Not supported in this IP. Not supported as the IP is always using single burst. |  |

| HMASTLOCK   | In        | Indicates that the current transaction is part of a locked sequence.  Not supported in this IP.           |  |

| HPROT[3:0]  | In        | The protection control signal. Not supported in this IP.                                                  |  |

| HSIZE[2:0]  | In        | Indicates the size of the transfer.                                                                       |  |

| Signal Name  | Direction | Description                                                                                                                                                   |

|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HTRANS[1:0]  | In        | Indicates the transfer type of the current transfer.                                                                                                          |

| HWDATA[31:0] | In        | Write data                                                                                                                                                    |

| HWRITE       | In        | Indicates if the current transaction is write or read.                                                                                                        |

| HRDATA[31:0] | Out       | Read data                                                                                                                                                     |

| HREADYOUT    | Out       | Indicates that transfer is finished.                                                                                                                          |

| HRESP        | Out       | The transfer response. 0 indicates an OKAY response, which means the transfer is successful. Meanwhile, 1 indicates that an error occurs during the transfer. |

| HSELx        | In        | AHB target select bit sent by the controller                                                                                                                  |

#### 2.5.2. CSR

CSR contains the configuration and status registers, which are written either by the system controller through the AHB-Lite, APB interface, or by the eSPI controller through the eSPI bus. The access type for every register is different for the AHB-Lite, APB interface, and the eSPI controller. More details on access type are discussed in the Other IP Specific Blocks/Layers/Interfaces section.

## 2.6. Other IP Specific Blocks/Layers/Interfaces

### 2.6.1. eSPI Commands

All the eSPI commands in the Intel eSPI specification are supported in the Lattice eSPI Target IP, except the Short Read commands. For details of eSPI commands timing and specification, you can refer to the Intel eSPI specification document.

For Short Read commands, the eSPI Target IP responds with the NON-FATAL ERROR response.

## 2.6.2. Virtual Wire - Simple Implementation

The Virtual Wire Simple Implementation is an additional feature in the Lattice eSPI Target IP to allow access to the other Virtual Group Index without using additional resources for the additional I/O ports.

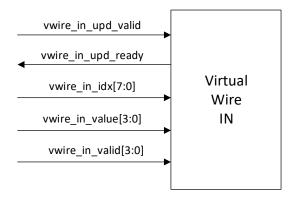

#### 2.6.2.1. Virtual Wire IN

Figure 2.3. Virtual Wire IN Interface

The Virtual Wire IN interface (Figure 2.3) is in the system clock domain.

Below are the instructions on how to use the Virtual Wire IN interface and read in eSPI using the GET VW command.

13

#### In Virtual Wire In Interface

- 1. Drive vwire\_in\_upd\_valid to 1. While this signal is high, the Virtual Wire IN interface samples all vwire inputs every system clock posedge.

- 2. Drive vwire\_in\_idx to the virtual wire index.

- 3. Drive vwire\_in\_value[3:0] and vwire\_in\_valid[3:0]. vwire\_in\_value bits hold the value of the virtual wire data while the corresponding bit in vwire\_in\_valid indicates if vwire\_in\_valid changes.

#### In eSPI Interface

- 1. Wait for the alert signal from the eSPI Target.

- 2. Use the eSPI SET STATUS command in address 0x020 bit [0] to enable the Virtual Wire Channel Enable bit. Skip this step when the specified register bit is already set to 1.

- 3. Use the eSPI GET CONFIG command in address 0x020 bit [1] to check if Virtual Wire Channel Ready is asserted.

- 4. Use the eSPI GET STATUS command and check if VWIRE Avail is high. If the response modifier is enabled, GET VWIRE appends to this GET STATUS transaction. See virtual wire packet format in Figure 41 of Enhanced Serial Peripheral Interface (eSPI) Interface Base Specification.

- 5. Use the eSPI GET VWIRE command. Repeat until VWIRE Avail in the eSPI status is low.

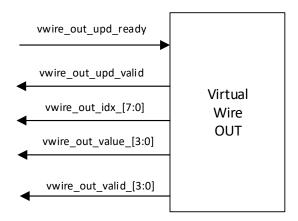

#### 2.6.2.2. Virtual Wire OUT

Figure 2.4. Virtual Wire OUT Interface

The Virtual Wire OUT interface (Figure 2.4) is in the system clock domain.

Below are the instructions on how to use the Virtual Wire IN interface and read in eSPI using the GET VW command.

#### In eSPI Interface

- 1. Use the eSPI GET STATUS command to check if VWIRE FREE is asserted.

- 2. Use the eSPI SET STATUS in address 0x020 bit[0] to enable the Virtual Wire Enable bit.

- 3. Use the eSPI GET CONFIG in address 0x020 bit [1] to check if Virtual Wire Channel Ready is asserted.

- 4. The eSPI PUT VWIRE command is 8'h04. See virtual wire packet format in Figure 41 of the Enhanced Serial Peripheral Interface (eSPI) Interface Base Specification.

#### In VW OUT Interface

- Wait for the assertion of vwire\_out\_upd\_valid.

- 2. Read vwire out idx[7:0], vwire out value[3:0], and vwire out valid[3:0].

- 3. Drive vwire\_out\_upd\_ready after reading the Virtual Wire OUT data.

- 4. Repeat until vwire\_out\_upd\_valid deasserts to zero. When vwire\_out\_upd\_valid is zero, it means there is no valid data from the virtual wire.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

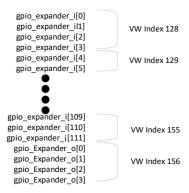

#### 2.6.3. Virtual Wire - GPIO Expander

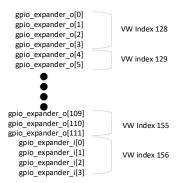

The GPIO Expander is compliant with the Intel eSPI specification. In the Lattice eSPI target IP, general-purpose I/Os are assigned automatically to the Virtual Wire Index. d128 is the minimum index and d255 is the maximum index.

The size of GPIO input and output is configurable in the parameter GUI. The priority of assigning GPIO to virtual wire index is also configurable in the GUI.

An example of GPIO to virtual wire index assignment is shown below.

If GPIO Input First is selected in the GUI, general-purpose inputs are assigned first and general-purpose outputs assigning starts at the next index after assigning all inputs (Figure 2.5).

Figure 2.5. Select GPIO Input First

If GPIO Output First is selected in the GUI. General-purpose outputs are assigned first and general-purpose inputs assigning starts at the next index after assigning all outputs (Figure 2.6).

Figure 2.6. Select GPIO Output First

If the input or output count is not divisible by four, it still utilizes one virtual wire index in the most significant bits.

Figure 2.7. Input or Output Not Divisible by Four

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

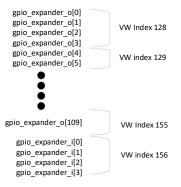

#### 2.6.3.1. GPIO Expander Input

In this section, the term GPIO Group is used to describe GPIOs that are assigned to the same virtual wire index.

When using the GPIO Expander input, you must change the value of the GPIO Expander input bit to trigger the GPIO IN to send virtual wire data to the eSPI controller. Changing one bit in a GPIO Group is enough to send virtual wire data of the GPIO Group to the Virtual Wire channel. The difference is unchanged GPIO inputs have zero value in their assigned virtual wire valid bit to indicate that the virtual wire data bit is not changed.

Figure 2.8. GPIO Expander Input

In Figure 2.8, the vw\_data[7:4] is the value after driving the GPIO Group while the vw\_data\_level[3:0] indicates if it changes. In the example above, the value of the vw\_index 8'h80 is used to show that the virtual wire index is changed.

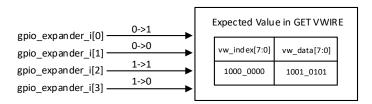

### 2.6.3.2. GPIO Expander Output

#### **GPIO** Group assigned to h80

Figure 2.9. GPIO Expander Output

In the GPIO Expander, Virtual Wire data bits with zero virtual wire valid bits are not reflected in the GPIO Expander output bits, in compliance with the eSPI Specification (Figure 2.9). In the example above, the virtual wire index 8'h80 is the index assigned to gpio\_expander\_o[3:0].

Changes in the GPIO Expander outputs are only reflected after the eSPI controller stops driving low-active eSPI Chip Select# (Figure 2.10).

Figure 2.10. PUT VWIRE Interrupt Assertion Timing

#### 2.6.4. eSPI Avail Status Valid Register Bits

The eSPI Target IP has Avail Status valid register bits, tx\_avail\_valid (0x808 [29:24]) and tx\_avail\_order (0x810). tx\_avail\_order (0x810) shows the order of the status assertion of PC AVAIL (3'd0), NP AVAIL (3'd1), OOB AVAIL (3'd2), FLASH NP AVAIL (3'd3), and FLASH C AVAIL(3'd4).

Example: If you intend to transmit VWIRE, OOB\_AVAIL, and NP sequentially, the tx\_free\_valid bits [5:0] should be set to 6'b000111 to indicate the three available packets. Then, tx\_free\_order should be set to {9'd0, 3'd1, 3'd2, 3'd4}.

The IP first asserts the VWIRE AVAIL status since it is the first in the order. Once GET VWIRE is received and transmission is completed, the VWIRE AVAIL status is cleared and OOB AVAIL is asserted. The tx\_avail\_valid and tx\_avail\_order should shift and show 6'b0011, and {12'd0, 3'd1, 3'd2} respectively. The process continues until all packets are transmitted and tx\_avail\_valid shows 6'b000000.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 2.6.5. eSPI Free Status Valid Register Bits

The eSPI Target IP has Free Status valid register bits, rx\_free\_valid (0x808 [19:16]) and rx\_free\_order (0x810). rx\_free\_order (0x810) shows which of the status is asserted: PC\_FREE(2'd0), NP\_FREE(2'd1), OOB\_FREE(2'd2), and FLASH\_NP\_FREE(2'd3).

Example: If you are able to receive PC, FLASH\_NP, and NP, the rx\_free\_valid[3:0] should be set to 4'b0111 to indicate the three free allocation. Then, rx free order should be set to {don't care, 2'd3, 2'd1, 2'd0}.

The IP asserts PC\_FREE, NP\_FREE, and FLASH\_NP\_FREE in the status during response. Once a packet is received, for example, PUT\_PC, the corresponding status PC\_FREE is cleared. The corresponding rx\_free\_valid bit should also be cleared. The process continues until all packets are received and rx\_free\_valid shows 4'b0000. If the Rx FIFO cannot receive a new packet, then the status sent during response is cleared and is only asserted once the Rx FIFO can accept a new packet.

## 2.6.6. Program Flow for Writing Data to FIFO

Writing data to FIFO is used when the microcontroller is sending data to the eSPI controller and the controller receives the data using GET <CHANNEL> eSPI commands. While writing to the FIFO, the payload header must be sent first, then, the payload data is sent. After writing data to the FIFO, the microcontroller needs to write to control the eSPI target status to assert the AVAIL register bit for their respective channel depending on the transaction.

In the APB/AHB-Lite Interface

- 1. Write the header and payload to the Tx FIFO Queue Write register. The sequence of the data write is payload header first, then, the payload data.

- Write to the Tx Avail Valid register (0x808) and Tx Avail Order register (0x810) to assert the avail signal in the eSPI Status register. See the eSPI Avail Status Valid Register Bits section for more information on Tx Avail Valid and Tx Avail Order registers. See the eSPI Target IP Registers section for more information on specific registers of the eSPI Target IP.

Since the data width of APB/AHB-Lite is limited to 32 bits. The data is sent word by word. For example, the eSPI target is sending a 64-bit request peripheral memory write to the controller. The first word includes the cycle type, tag, length, and address bits 31 to 24. The second word contains the remainder of the address and the first byte of the payload data. The data write to the FIFO is shown in Figure 2.11.

Figure 2.11. FIFO Write Format

### 2.6.7. Program Flow for Reading Data from FIFO

Reading data from the FIFO is performed when the interrupt status indicates that the FIFO is not empty. The data to be read from the FIFO includes the command opcode, payload header, and optional payload data.

In the APB/AHB-Lite Interface

- 1. Assert the Free eSPI Status register bits.

- 2. Write to the Rx Avail Valid register (0x808) and Rx Avail Order register (0x810) to assert the free signal in the eSPI Status register. See the eSPI Free Status Valid Register Bits section for more information on Rx Avail Valid and Rx Avail Order registers. See the eSPI Target IP Registers section for more information on specific registers of the eSPI Target IP.

- 3. After using GET Channel Command, read the FIFO.

- 4. Read the header and payload from the RX FIFO Queue Write register. The sequence of the data write is header first, then the payload data.

Since the data width of APB/AHB-Lite is limited to 32 bits. The data is sent word by word. For example, the eSPI controller is sending a 32-bit request to write to the peripheral memory of the target. The first word includes the command opcode, cycle type, tag, and length. The second word contains the address. After that, the payload data, which is optional because there are transactions without message, is sent. The data read to the FIFO is shown in Figure 2.12.

Figure 2.12. FIFO Read Format

### 2.6.8. Program Flow for Using GET Channel Commands

In this section, the GET Channel commands refer to all eSPI channel commands where the eSPI Controller receives data from the four available channels, Peripheral Channel, Virtual Wire Channel, OOB Message Channel, and Flash Access Channel. Although there may be a large number of FIFO and GET Channel commands, they all follow a general flow: what goes in FIFO IN goes out through the GET Channel commands. Below are examples of executing GET Channel commands in the eSPI Target IP.

For command opcode values of GET Channel commands, see Table 3 Command Opcode Encodings of Enhanced Serial Peripheral Interface (eSPI) Interface Base Specification. For the packet format, see Section 5.2 Channels of the base specification.

#### 2.6.8.1. GET Channel Commands – Peripheral Channel

In this section, the example used is a scenario where the eSPI controller receives a GET PC command of the Completion with Data cycle type. If you use other command opcode, data values in the payload header and payload data change depending on the specified values in the Intel eSPI base specification.

#### In APB/AHB-Lite Interface

- Write the payload address and the payload data in the FIFO.

The format is discussed in the Program Flow for Writing Data to FIFO section.

- 2. Write to the eSPI Avail Status Valid register to set the PC AVAIL bit. Refer to eSPI Avail Status Valid Register Bits for more details. Additionally, set bit 0 to 1 in the eSPI Target Channel Control 0 register. The bit field is named Peripheral Channel Ready.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if PC AVAIL is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x010 to save the current value of the Peripheral Channel Configuration register.

- 5. For the Peripheral Channel, use the eSPI SET CONFIG command in bit 0 of address 0x010 to enable the Peripheral Channel Enable bit. All the other values fetched in the earlier transaction do not change.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x010 for the Peripheral Channel. Check the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the GET PC command.

Figure 2.13 shows the timing diagram of the eSPI GET PC transaction.

Figure 2.13. GET PC - Completion with Data

#### 2.6.8.2. GET Channel Commands - Virtual Wire Channel

For the Virtual Wire Channel, there are no additional steps required. There is a dedicated interface for this channel, which means the virtual wire channel does not use the FIFO to read the virtual wire data. For more information, refer to the Virtual Wire Channel section.

#### In Virtual Wire Interface

- If Simple Interface is used:

- a. Write value in vwire in value[3:0], vwire in valid[3:0], and vwire in idx[7:0].

- b. Check if vwire in upd ready is HIGH.

- c. Assert the vwire\_in\_upd\_valid input port.

- If GPIO Expander is used:

Change the value of gpio expander i[GPIO IN COUNT-1:0].

In the APB/AHB-Lite Interface

Write the value 1 to bit 1 of the eSPI Target Channel Control 0 register. The bit field is named Virtual Wire Channel Ready.

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if VW AVAIL is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x020 to save the current value of the Virtual Wire Channel configuration register.

- 5. For the Virtual Wire Channel, use the eSPI SET STATUS command in bit 0 of address 0x020 to enable the Virtual Wire Channel Enable bit. All the other bits in the register retain the value fetched from the transaction earlier.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x020 for Virtual Wire Channel. Read the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the GET VWIRE command.

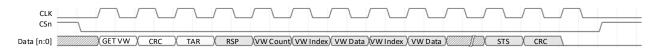

Figure 2.14 shows the timing diagram of the eSPI GET VWIRE transaction.

Figure 2.14. GET VWIRE

#### 2.6.8.3. GET Channel Commands - OOB Message Channel

The only valid cycle type for GET OOB is the OOB Tunneled SMBus Message. This cycle type is used for the programming flow discussed in this section.

#### In APB/AHB-Lite Interface

- 1. Write the payload address and the payload data in the FIFO. The format is discussed in the Program Flow for Writing Data to FIFO section.

- 2. Write to the eSPI Avail Status Valid register to set the PC AVAIL bit. Refer to eSPI Avail Status Valid Register Bits for more details. Additionally, set bit 2 to 1 in the eSPI Target Channel Control 0 register. The bit field is named OOB Message Channel Ready.

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if OOB AVAIL is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x030 to save the current value of the OOB Message Channel Configuration register.

- 5. For the OOB Message Channel, use eSPI SET STATUS command in bit 0 of address 0x030 to enable the OOB Message Channel Enable bit. Other bits retain the value fetched from the transaction earlier.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x030 for the OOB Message Channel. Read the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the GET OOB command.

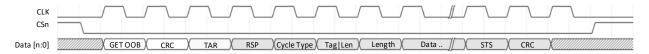

Figure 2.15 shows the timing diagram of the eSPI GET OOB transaction.

Figure 2.15. GET OOB

#### 2.6.8.4. GET Channel Commands - Flash Access Channel

In this section, the program flow shows a transaction with the Flash Write cycle type for the GET FLASH NP command opcode.

### In APB/AHB-Lite Interface

- Write the payload address and the payload data in the FIFO.

The format is discussed in the Program Flow for Writing Data to FIFO section.

- Write to the eSPI Avail Status Valid register bit to set the PC AVAIL bit.

Refer to the eSPI Avail Status Valid Register Bits section for more details. Additionally, set bit 3 to 1 in the eSPI Target Channel Control 0 register. The bit field is named Flash Access Channel Ready.

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if FLASH NP AVAIL is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x040 to save the current value of the Flash Access Channel Configuration register.

- 5. For Flash Access Channel, use the eSPI SET STATUS command in bit 0 of address 0x040 to enable the Flash Access Channel Enable bit. Other bits retain the value fetched from the transaction earlier.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x040 for the Flash Access Channel. Read the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the GET FLASH NP command.

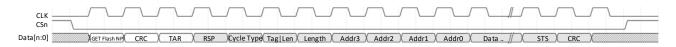

Figure 2.16 shows the timing diagram of the GET FLASH NP transaction.

Figure 2.16. GET FLASH NP - Flash Write

### 2.6.9. Program Flow for Using PUT Channel Commands

In this document, PUT Channel commands refer to all eSPI channel commands where the eSPI controller sends data to the four available channels, Peripheral Channel, Virtual Wire Channel, OOB Message Channel, and Flash Access Channel. Although there may be a large number of FIFO and PUT Channel commands, they all follow a general flow: what goes in through the GET Channel commands goes out in the FIFO OUT. Below are examples of executing PUT Channel commands in the eSPI Target IP.

#### 2.6.9.1. PUT Channel Commands - Peripheral Channel

In APB Interface

Write to the eSPI Avail Status Valid register bit to set the PC FREE bit. See the eSPI Free Status Valid Register Bits section for more details. Additionally, set bit 0 to 1 in the eSPI Target Channel Control 0 register. The bit field is named Peripheral Channel Ready.

In the eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if PC Free is asserted.

- 4. Use the eSPI GET CONFIG command in the address 0x010 to save the current value of the Peripheral Channel Configuration register.

- 5. For the Peripheral Channel, use the eSPI SET CONFIG command in address 0x010 bit[0] to enable Peripheral Channel Enable bit. All the other values fetched in the earlier transaction do not change.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x010 for the Peripheral Channel. Check the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the PUT PC command.

22

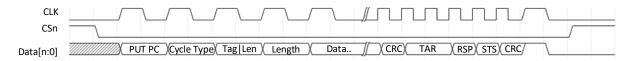

Figure 2.17 below shows the timing diagram of PUT PC transaction.

Figure 2.17. PUT PC Command

#### In APB Interface

Read the data in the FIFO. The format is discussed in the Program Flow for Writing Data to FIFO section.

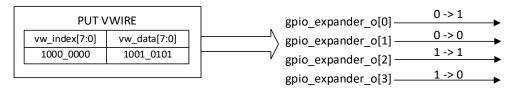

#### 2.6.9.2. PUT Channel Commands – Virtual Wire Channel

In the eSPI Status register, VW FREE is always 1. There is no need to assert the FREE bit for the virtual wire.

In APB/AHB-Lite Interface

Write the value 1 to bit 1 of the eSPI Target Channel Control 0 register. The bit field is named Virtual Wire Channel Ready.

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if VW AVAIL is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x020 to save the current value of the Virtual Wire Channel Configuration register.

- 5. For the Virtual Wire Channel, use the eSPI SET STATUS command in bit 0 of address 0x020 to enable the Virtual Wire Channel Enable bit. All the other bits in the register retain the value fetched from the transaction earlier.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x020 for the Virtual Wire Channel. Read the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the PUT VWIRE command.

Figure 2.18 shows the timing diagram of the eSPI PUT VWIRE transaction.

Figure 2.18. PUT VWIRE

#### In Virtual Wire Interface

- If Simple Interface is used:

- a. Check if vwire\_out\_upd\_valid is high.

- b. Read value in vwire\_out\_value[3:0], vwire\_out\_valid[3:0], and vwire\_out\_idx[7:0].

- c. Assert the vwire out upd ready input port. This triggers the signals mentioned in the second step to display the next virtual wire value.

- If GPIO Expander is used:

The values are displayed in gpio\_expander\_o[GPIO\_OUT\_COUNT-1:0].

#### 2.6.9.3. PUT Channel Commands - OOB Message Channel

#### In APB Interface

Write to eSPI Avail Status Valid register bit to set the OOB FREE bit. Refer to eSPI Free Status Valid Register Bits for more details. Additionally, set bit 2 to 1 in the eSPI Target Channel Control 0 register. The bit field is named OOB Message Channel Ready.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-IPLIG-02260-1 1

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from the eSPI GET STATUS command to check if OOB FREE is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x030 to save the current value of the OOB Message Channel configuration register.

- 5. For the OOB Message Channel, use the eSPI SET STATUS command in bit 0 of the address 0x030 to enable the OOB Message Channel Enable bit. Other bits retain the value fetched from the transaction earlier.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x030 for the OOB Message Channel. Read the value of bit 1 to check if the Channel Ready bit is asserted.

- 7. Initiate the PUT OOB command.

Figure 2.19 shows the timing diagram of the eSPI PUT OOB transaction.

Figure 2.19. PUT OOB - Completion with data

#### In APB Interface

Read the data in the FIFO. The format is discussed in the Program Flow for Writing Data to FIFO section.

#### 2.6.9.4. PUT Channel Commands - Flash Access Channel

#### In the APB Interface

Write to the eSPI Avail Status Valid register to set the FLASH C FREE bit. Refer to eSPI Free Status Valid Register Bits for more details. Additionally, set bit 3 to 1 in the eSPI Target Channel Control 0 register. The bit field is named Flash Access Channel Ready.

#### In eSPI Interface

- 1. Wait for the deassertion of the port espi\_alert\_n\_o. If the open-drain alert support is enabled, the name of the port is espi\_alert\_n\_io.

- 2. Execute the eSPI GET STATUS command.

- 3. Use the status data from eSPI GET STATUS command to check if FLASH C Free is asserted.

- 4. Use the eSPI GET CONFIG command in address 0x040 to save the current value of the Flash Access Channel configuration register.

- 5. For Flash Access Channel, use the eSPI SET STATUS command in address 0x040 bit 0 to enable the Flash Access Channel Enable bit. Other bits retain the value fetched from the transaction earlier.

- 6. Use the eSPI GET CONFIG command in the respective channel address you are using. The address is 0x040 for the Flash Access Channel. Read the value of bit 1 to check if the Channel Ready bit is asserted.

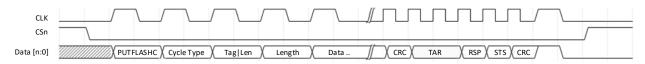

- 7. Initiate the PUT FLASH C command.

Figure 2.20 shows the timing diagram of the PUT FLASH C transaction.

Figure 2.20. PUT FLASH C - Completion with Data

### In the APB Interface

Read the data in the FIFO. The format is discussed in the Program Flow for Writing Data to FIFO section.

## 2.7. Error Handling

| Error                                                    | Description                                       | Supported | Required |

|----------------------------------------------------------|---------------------------------------------------|-----------|----------|

| Invalid Command Operado                                  | NO_RESPONSE Response Code.                        | Yes       | Yes      |

| Invalid Command Opcode                                   | The command is discarded.                         | res       | res      |

| Invalid Cycle Type                                       | NO_RESPONSE Response Code.                        | Vaa       | .,       |

| with respect to specific command                         | The command is discarded.                         | Yes       | Yes      |

| Comment where CDC Farrer                                 | NO_RESPONSE Response Code.                        | Vaa       |          |

| Command phase CRC Error                                  | The command is discarded.                         | Yes       | Yes      |

|                                                          | Target tri-state the bus tSHQZ after              |           |          |

| Unexpected deassertion of                                | Chip Select# is deasserted.                       |           |          |

| Chip Select#                                             | <b>Note:</b> The controller is expected to detect | Yes       | Yes      |

| Chip Selectin                                            | CRC errors during the response phase if           |           |          |

|                                                          | CRC checking is enabled.                          |           |          |

| Protocol Error                                           | FATAL_ERROR Response Code.                        |           |          |

| PUT without FREE                                         | The command is discarded.                         | Yes       | Yes      |

| GET without AVAIL                                        | The command is discarded.                         |           |          |

| Malformed Packet during Command Phase                    | FATAL_ERROR Response Code.                        |           |          |

| Peripheral Channel:                                      | The command is discarded.                         |           |          |

| • Payload length > Max Payload Size aligned              | or                                                |           |          |

| • Read request size > Max Read Request Size              | FATAL_ERROR Virtual Wire.                         |           |          |

| aligned                                                  | Before signalling the FATAL ERROR Virtual         |           |          |

| • (Address + Length) crosses 4 KB aligned                | Wire, the transaction is completed on the         |           |          |

| boundary                                                 | eSPI bus with the ACCEPT RESPONSE and             | Yes       | Yes      |

| Virtual Wire Channel:                                    | the following outcomes:                           | 163       | 163      |

| Virtual Wire Count > Max Virtual Wire Count              | Posted: The command is discarded.                 |           |          |

| OOB Channel:                                             | Completion: The command is discarded.             |           |          |

| SMBus Byte Count > Max Payload Size                      | Non-posted: Unsuccessful completion               |           |          |

| Flash Access Channel:                                    | without data is returned and the                  |           |          |

| <ul> <li>Payload length &gt; Max Payload Size</li> </ul> | command is discarded.                             |           |          |

| • Read request size > Max Read Request Size              | Virtual Wire: The command is discarded.           |           |          |

| PUT_MEMRD32_SHORTS                                       | NON_FATAL_ERROR Response Code. It is              | Yes       | Optional |

| PUT_IORD_SHORT                                           | not supported in this eSPI Target IP.             | res       | Ориона   |

# 3. IP Parameter Description

The configurable attributes of the eSPI Target IP are shown in Table 3.1 and Table 3.2. You can configure the IP by setting the attributes accordingly in the IP Catalog's Module/IP wizard of the Lattice Radiant software. Wherever applicable, default values are in bold.

## 3.1. General

**Table 3.1. General Attributes**

| Attribute                            | Selectable Values                      | Description                                                                | Parameter                                  |  |  |  |

|--------------------------------------|----------------------------------------|----------------------------------------------------------------------------|--------------------------------------------|--|--|--|

|                                      |                                        | Parameter for removing tristate                                            | REMOVE_TRISTATE                            |  |  |  |

| Remove Tristate <b>0</b> ,1          |                                        | input/output of eSPI data.                                                 | 0 – Tristate eSPI Data I/O.                |  |  |  |

|                                      |                                        | inputy output of ear i data.                                               | 1 – Remove tristate eSPI Data I/O.         |  |  |  |

| Frankla Chia Calaat                  |                                        | Decree to face and live alitable file of a                                 | EN_CS_FILTER                               |  |  |  |

| Enable Chip Select<br>Glitch Filter  | 0,1                                    | Parameter for enabling glitch filter for                                   | 0 – Disabled.                              |  |  |  |

| Gitter                               |                                        | chip select.                                                               | 1 – Enabled.                               |  |  |  |

|                                      |                                        |                                                                            | USER_INTERFACE_SELECT                      |  |  |  |

| Select User                          | ADD ALIDI mana                         | Parameter for selecting the SoC Interface.                                 | APB – APB User Interface.                  |  |  |  |

| Interface                            | APB, AHBL, none                        | If None is selected, Virtual Wire must be enabled.                         | AHBL – AHB-Lite User Interface.            |  |  |  |

|                                      |                                        | enabled.                                                                   | None – no available User Interface.        |  |  |  |

|                                      |                                        |                                                                            | PERIPHERAL_CHANNEL_ENABLE                  |  |  |  |

| Peripheral Channel                   | 0,1                                    | Parameter for peripheral channel                                           | 0 – Disable the eSPI Peripheral Channel.   |  |  |  |

| Enable                               |                                        | enable/disable.                                                            | 1 – Enable the eSPI Peripheral Channel.    |  |  |  |

|                                      |                                        | Parameter for VW channel                                                   | VIRTUAL_WIRE_INTERFACE_SELECT              |  |  |  |

| Virtual Wire                         | <b>0</b> ,1                            | enable/disable. It is automatically enabled                                | 0 – Disable eSPI Virtual Wire Channel.     |  |  |  |

| Channel Enable                       | 0,1                                    | when the USER_INTERFACE_SELECT value                                       | 1 – Enable eSPI Virtual Wire Channel.      |  |  |  |

|                                      |                                        | is None.                                                                   | 1 – Lilable esti viitual vviie Cilaililei. |  |  |  |

| OOR Mossago                          |                                        | Parameter for OOB Message channel                                          | OOB_MESSAGE_CHANNEL_ENABLE                 |  |  |  |

| OOB Message<br>Channel Enable        |                                        | enable/disable.                                                            | 0 – Disable eSPI OOB Message Channel.      |  |  |  |

| Chamiler Lilable                     |                                        | chasic, alsasic.                                                           | 1 – Enable eSPI OOB Message Channel.       |  |  |  |

| Flash Access                         | Davis markey for Floor access the area | FLASH_CHANNEL_ENABLE                                                       |                                            |  |  |  |

| Channel Enable                       | <b>0</b> , 1                           | Parameter for Flash access channel enable/disable.                         | 0 – Disable eSPI Flash Access Channel.     |  |  |  |

| Charmer Enable                       |                                        | Chable, disable.                                                           | 1 – Enable eSPI Flash Access Channel.      |  |  |  |

| eSPI Target                          |                                        | Davage star to configure if address 0.004 is                               | ESPI_TARGET_CONFIG_PROG                    |  |  |  |

| Configuration                        | <b>0</b> ,1                            | Parameter to configure if address 0x804 is programmable by User Interface. | 0 – Not Programmable.                      |  |  |  |

| Programmable                         |                                        | programmable by oser interface.                                            | 1 – Programmable.                          |  |  |  |

| PERIPHERAL_CHANNEL_ENABLE = 0 and    |                                        |                                                                            |                                            |  |  |  |

| OOB_MESSAGE_CHA                      | NNEL_ENABLE = 0 an                     | d                                                                          |                                            |  |  |  |

| FLASH_CHANNEL_EN                     | ABLE = 0                               |                                                                            |                                            |  |  |  |

| Enable eSPI Channel                  |                                        | Parameter of instantiating channel                                         | EN_ALL_REGISTERS                           |  |  |  |

| Configurations                       | <b>0</b> ,1                            | configuration registers when the eSPI                                      | 0 – Disabled.                              |  |  |  |

| Registers                            |                                        | channel is disabled.                                                       | 1 – Enabled.                               |  |  |  |

| PERIPHERAL_CHANN                     | EL_ENABLE = 0 or                       |                                                                            |                                            |  |  |  |

| VIRTUAL_WIRE_INTERFACE_SELECT = 0 or |                                        |                                                                            |                                            |  |  |  |

| OOB_MESSAGE_CHA                      | NNEL_ENABLE = 0 or                     |                                                                            |                                            |  |  |  |

| FLASH_CHANNEL_EN                     | ABLE = 0                               |                                                                            |                                            |  |  |  |

| 1                                    |                                        | The parameter to enable all the channel                                    |                                            |  |  |  |

|                                      |                                        | capabilities and configuration registers                                   |                                            |  |  |  |

| Enable eSPI                          |                                        | when their respective channels are                                         | EN_ALL_REGISTERS                           |  |  |  |

| Configuration                        | 0,1                                    | disabled in the IP Parameter GUI, General                                  | 0 – Disabled.                              |  |  |  |

| Registers                            |                                        | Attributes.                                                                | 1 – Enabled.                               |  |  |  |

|                                      |                                        | This allows the eSPI controller to read and                                |                                            |  |  |  |

|                                      |                                        | write in the eSPI Channel Configuration                                    |                                            |  |  |  |

| Attribute                           | Selectable Values                                  | Description                                                                                                                                                                                                                                                  | Parameter                                                                       |

|-------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

|                                     |                                                    | registers. However, if a channel is disabled in the IP instantiation parameters, the channel ready bit does not assert.                                                                                                                                      |                                                                                 |

| EN_CS_FILTER = 1                    |                                                    |                                                                                                                                                                                                                                                              |                                                                                 |

| Filtered Chip Select<br>Pulse Width | <b>50</b> –200                                     | Parameter for the filter width of chip select glitch filter. The value of this parameter is in nanosecond.                                                                                                                                                   | ECS_SPIKE_WIDTH = {50,200}                                                      |

| VIRTUAL WIRE CHAN                   | NEL ENABLE = 1                                     |                                                                                                                                                                                                                                                              |                                                                                 |

| Virtual Wire<br>Interface Select    | <b>GPIO Expander</b> ,<br>Simple<br>Implementation | Parameter for the virtual wire GPIO extender interface enable/disable.  If enabled, the virtual wire GPIO extender I/O is in the input/output port.  If disabled, 8-bit data I/O per virtual wire is implemented in the IP.                                  | VIRTUAL_WIRE_INTERFACE_SELECT<br>GPIO Extender – 0<br>Simple Implementation – 1 |

| VIRTUAL WIRE CHAN                   | NEL ENABLE = 1 , VIR                               | TUAL_WIRE_INTERFACE_SELECT = 0                                                                                                                                                                                                                               |                                                                                 |

| GPIO Input Count                    | 0–512                                              | Parameter for the count of GPIO input. One Virtual Wire Index is assigned per four GPIO. If the count is not divisible by four, the Most Significant bit which is less than four takes a VW Index. Current configuration exceeds the maximum of 128 indexes. | GPIO_IN_COUNT = {0-512}                                                         |

| GPIO Output Count                   | 0–(512–GPIO<br>Input Count)                        | Parameter for the count of GPIO output.                                                                                                                                                                                                                      | GPIO_OUT_COUNT = {0-(512-GPIO Input Count)}                                     |

| GPIO Index Order<br>Start           | GPIO Input First,<br>GPIO Output First             | Parameter to configure the order of the GPIO Input and Output in Virtual Wire Indexing.                                                                                                                                                                      | GPIO_INDEX_ORDER_START = {0,1}                                                  |

## 3.2. Capabilities and Configuration Register Default Values

**Table 3.2. Capabilities and Configuration Register Attributes**

| Attribute                                                 | Selectable Values                                                | Description                                                                                   | Parameter                                           |

|-----------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|

| I/O Mode Support                                          | Single, Single and Dual, Single and Quad, Single, Dual, and Quad | Parameter for the SPI mode supported by the target.                                           | IO_MODE_SUPPORT = {0,1,2,3}                         |

| Open Drain Alert<br>Supported                             | 0,1                                                              | Parameter that indicates the support of the Alert# pin as an open-drain output by the target. | OPEN_DRAIN_ALERT_SUPPORT = {0,1}                    |

| Maximum Frequency Supported                               | <b>20</b> , 25, 30, 50, 66 MHz                                   | Maximum frequency of operation supported by the target.                                       | MAX_FREQ_SUPPORT = {0,1,2,3,4}                      |

| Peripheral Channel<br>Maximum Payload<br>Size Supported   | <b>64</b> , 128, 256 Bytes                                       | The Maximum Payload Size supported by the target for the Peripheral channel.                  | PERIPHERAL_CHANNEL_MAX_SIZE = {64,128,256}          |

| Maximum Virtual Wire Count Supported                      | 0–63 Bytes                                                       | The maximum Virtual Wire count supported by the target.                                       | MAX_VW_COUNT_SUPPORT = {0-63}                       |

| OOB Message Channel<br>Maximum Payload<br>Size Supported  | <b>64</b> , 128, 256 Bytes                                       | The maximum payload size supported by the target for the OOB Message channel.                 | OOB_MSG_CH_MAX_PAYLOAD_SIZE = {64,128,256}          |

| Flash Access Channel<br>Maximum Payload<br>Size Supported | <b>64</b> , 128, 256 Bytes                                       | The maximum payload size supported by the target for the Flash Access channel.                | FLASH_ACCESS_CH_MAX_PAYLOAD_SIZ<br>E = {64,128,256} |

# 4. Signal Description

| Post Middle Birection Description |                       |           |                                                                 |  |  |  |

|-----------------------------------|-----------------------|-----------|-----------------------------------------------------------------|--|--|--|

| Port                              | Width                 | Direction | Description                                                     |  |  |  |

| System                            |                       |           | T                                                               |  |  |  |

| clk_i                             | 1                     | Input     | System clock                                                    |  |  |  |

| resetn_i                          | 1                     | Input     | Active-low system reset                                         |  |  |  |

| int_o                             | 1                     | Output    | Active-high interrupt output                                    |  |  |  |

| espi_rst_n_i                      | 1                     | Input     | Active-low eSPI reset                                           |  |  |  |

| espi_clk_i                        | 1                     | Input     | eSPI clock input driven by eSPI controller                      |  |  |  |

| espi_cs_n_i                       | 1                     | Input     | eSPI chip select input driven by eSPI controller                |  |  |  |

| OPEN_DRAIN_ALERT_SU               | PPORT = 0             |           |                                                                 |  |  |  |

| espi_alert_n_o                    | 1                     | Output    | eSPI target alert output                                        |  |  |  |

| OPEN_DRAIN_ALERT_SU               | PPORT = 1             |           |                                                                 |  |  |  |