# JESD204B IP

IP Version: v1.3.0

# **User Guide**

FPGA-IPUG-02259-1.3

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents | S                                           | 3  |

|----------|---------------------------------------------|----|

| Abbrevia | ations in This Document                     | 9  |

| 1. Intr  | roduction                                   | 10 |

| 1.1.     | Overview of the IP                          | 10 |

| 1.2.     | Quick Facts                                 | 10 |

| 1.3.     | IP Support Summary                          | 10 |

| 1.4.     | Features                                    |    |

| 1.5.     | Licensing and Ordering Information          | 11 |

| 1.5.     | .1. Ordering Part Number                    |    |

| 1.6.     | Hardware Support                            |    |

| 1.7.     | Minimum Device Requirements                 | 11 |

| 1.8.     | Naming Conventions                          |    |

| 1.8.     |                                             |    |

| 1.8.     | .2. Signal Names                            | 12 |

| 1.8.     | .3. Attribute Names                         | 12 |

| 2. Fun   | nctional Description                        | 13 |

| 2.1.     | IP Architecture Overview                    |    |

| 2.2.     | Rx Link Layer                               | 13 |

| 2.2.     | •                                           |    |

| 2.2.     | •                                           |    |

| 2.2.     | .3. ILA Detection                           | 15 |

| 2.2.     |                                             |    |

| 2.2.     | •                                           |    |

| 2.3.     |                                             |    |

| 2.3.     | •                                           |    |

| 2.3.     | •                                           |    |

| 2.3.     |                                             |    |

| 2.3.     |                                             |    |

| 2.4.     | Embedded Transport Layer                    |    |

| 2.5.     | JESD204B PHY Layer                          |    |

| 2.5.     | •                                           |    |

| 2.5.     |                                             |    |

| 2.6.     | Clocking Overview                           |    |

| 2.7.     | Reset                                       |    |

| 3. IP P  | Parameter Description                       |    |

| 3.1.     | General                                     |    |

| 3.2.     | PHY                                         |    |

| 3.3.     | Transport Layer Setup                       |    |

| 3.4.     | Test Mode Setup                             |    |

| 3.5.     | IP Parameter Settings for Example Use Cases |    |

| 3.5.     | ·                                           |    |

| 3.5.     | ,                                           |    |

| 3.5.     | • •                                         |    |

| 4. Sigr  | nal Description                             |    |

| 4.1.     | Signal Interface                            |    |

| 4.2.     | Clock Interface                             |    |

|          | gister Description                          |    |

| 5.1.     | Tx Register                                 |    |

| 5.1.     | G                                           |    |

| 5.1.     |                                             |    |

| 5.1.     | •                                           |    |

| 5.1.     | •                                           |    |

| J        |                                             |    |

| 5.1.5. Link Config Register                        | 46 |

|----------------------------------------------------|----|

| 5.2. Rx Register                                   | 50 |

| 5.2.1. Rx Register Map Overview.                   | 50 |

| 5.2.2. Control Register                            | 51 |

| 5.2.3. Status Register                             | 51 |

| 5.2.4. Error Status Register                       | 52 |

| 5.2.5. Link Config Register                        | 52 |

| 5.2.6. Error Counter Register                      | 57 |

| 5.2.7. Buffer Fill Level Register                  | 57 |

| 6. Example Design                                  | 58 |

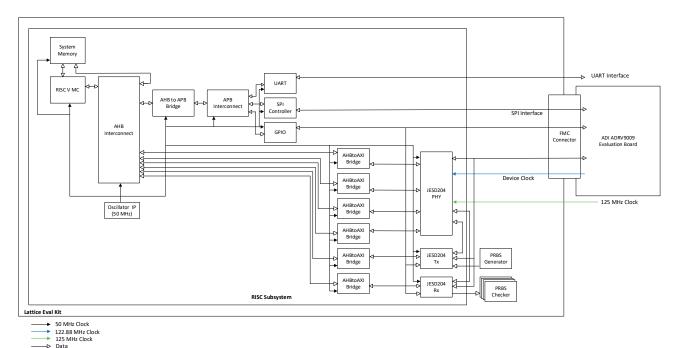

| 6.1. CertusPro-NX Device Example Design            | 58 |

| 6.1.1. Example Design Supported Configuration      | 58 |

| 6.1.2. Overview of the Example Design and Features | 59 |

| 6.1.3. Example Design Components                   | 59 |

| 6.1.4. Hardware Testing                            | 61 |

| 6.2. Avant-X Versa Board Rx Example Design         | 68 |

| 6.2.1. Example Design Supported Configuration      |    |

| 6.2.2. Overview of the Example Design and Features |    |

| 6.2.3. Example Design Components                   |    |

| 6.2.4. Hardware Testing                            |    |

| 6.3. Avant-X Versa Board Tx Example Design         |    |

| 6.3.1. Example Design Supported Configuration      |    |

| 6.3.2. Overview of the Example Design and Features | 72 |

| 6.3.3. Example Design Components                   | 73 |

| 6.3.4. Hardware Testing                            |    |

| 7. Designing with the IP                           |    |

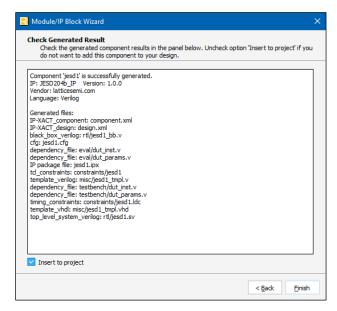

| 7.1. Generating and instantiating the IP           |    |

| 7.1.1. Generated Files and File Structure          |    |

| 7.2. Design Implementation                         |    |

| 7.3. Specifying the Strategy                       |    |

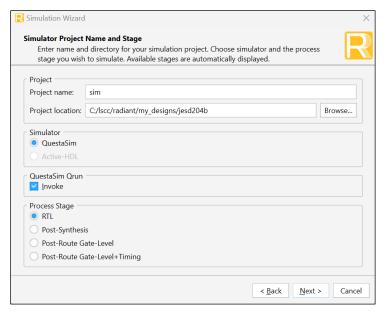

| 7.4. Running Functional Simulation                 |    |

| 7.4.1. Simulation Results                          |    |

| Appendix A. Resource Utilization                   |    |

| References                                         |    |

| Technical Support Assistance                       |    |

| Revision History                                   | 86 |

# **Figures**

| Figure 2.1. JESD204B IP Block Diagram                                                                     |    |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 2.2: JESD204B Rx Link Layer Block Diagram                                                          | 13 |

| Figure 2.3. Timing Diagram Illustration for LMFC and Rx Frames Interface                                  | 14 |

| Figure 2.4. Timing Diagram Illustration for Deterministic Latency Equal to Multiples of Multiframe Period | 15 |

| Figure 2.5. Serial Descrambling                                                                           | 16 |

| Figure 2.6. JESD204B Tx Link Layer Block Diagram                                                          | 16 |

| Figure 2.7. Tx LMFC Timing Diagram Correlation with tx_somf Signal                                        | 17 |

| Figure 2.8. Mapping of Link Configuration Fields to Octets                                                | 18 |

| Figure 2.9. User Data Format for Independent Lane with Oversampling                                       | 19 |

| Figure 2.10. Embedded Transport Layer Block Diagrams for Tx and Rx                                        | 20 |

| Figure 2.11. Timing Diagram with OCTET_PER_FRAME = 2 and TL_FRAME_PER_CLK = 2                             | 21 |

| Figure 2.12. Timing Diagram with OCTET_PER_FRAME = 2 and TL_FRAME_PER_CLK = 1                             |    |

| Figure 2.13. Timing Diagram with OCTET_PER_FRAME = 3 and TL_FRAME_PER_CLK = 1                             | 22 |

| Figure 2.14. Timing Diagram with OCTET_PER_FRAME = 3 and TL_FRAME_PER_CLK = 2                             |    |

| Figure 2.15. JESD204B PHY Layer Module                                                                    |    |

| Figure 2.16. CertusPro-NX PCS REFCLK Architecture                                                         | 24 |

| Figure 2.17. AXI4-Lite to LMMI Aligned Transfer on 8-bit, 16-bit, and 32-bit Buses                        | 24 |

| Figure 2.18. AXI4-Lite to LMMI Write Timing Diagram                                                       |    |

| Figure 2.19. AXI4-Lite to LMMI Read Timing Diagram                                                        |    |

| Figure 2.20. JESD204B IP Clock Domain Block Diagram                                                       |    |

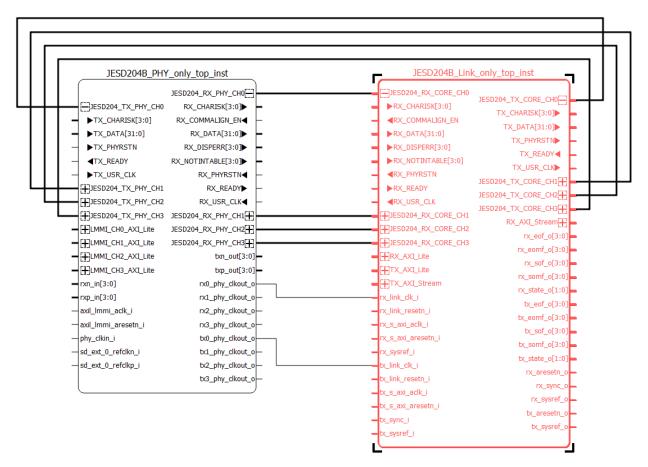

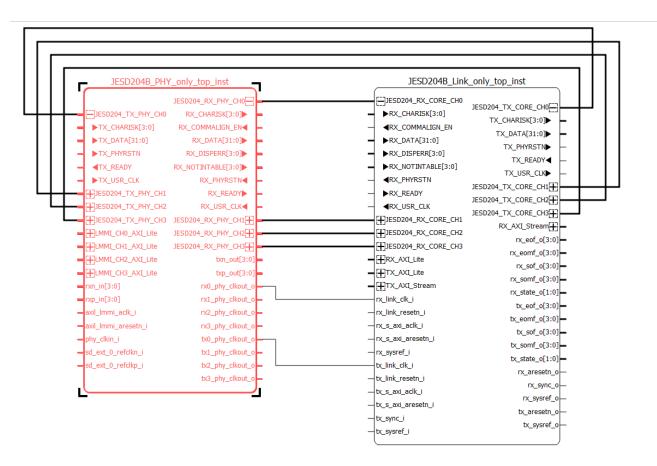

| Figure 3.1. JESD204B PHY to Link Connection Example with Main Channel (Channel 0)                         | 31 |

| Figure 3.2. JESD204B Link Only Mode Connection Example                                                    |    |

| Figure 3.3. JESD204B PHY Only Mode Connection Example                                                     |    |

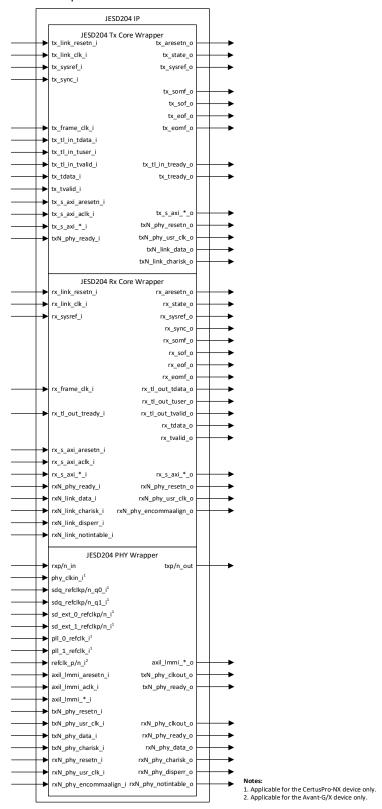

| Figure 4.1. JESD204B IP Port Interface Overview                                                           |    |

| Figure 6.1. JESD204B Example Design Block Diagram                                                         |    |

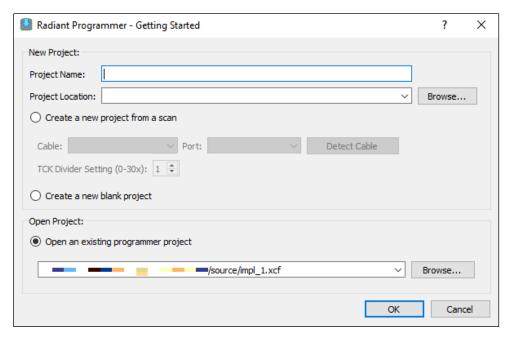

| Figure 6.2. Opening a Programmer Project                                                                  |    |

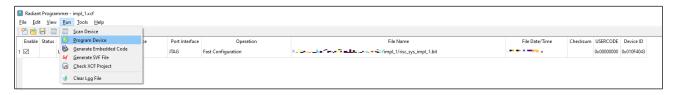

| Figure 6.3. Programming the Device through the Run Menu                                                   |    |

| Figure 6.4. Programming Log Messages                                                                      |    |

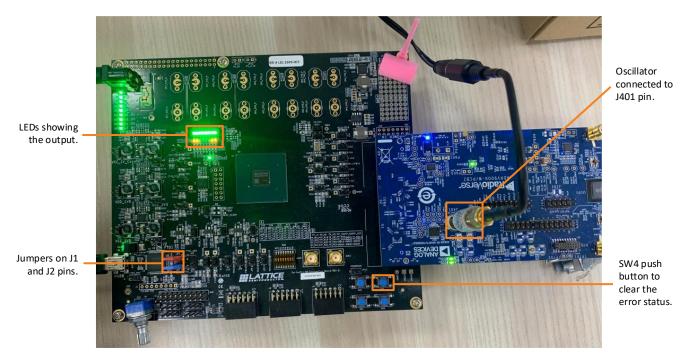

| Figure 6.5. CertusPro-NX Evaluation Board (Left) with ADI ADRV9009 Dual RF Evaluation Board (Right)       |    |

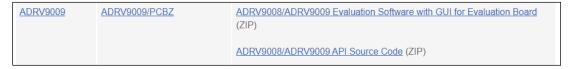

| Figure 6.6. ADI Software and Source Code to Download                                                      |    |

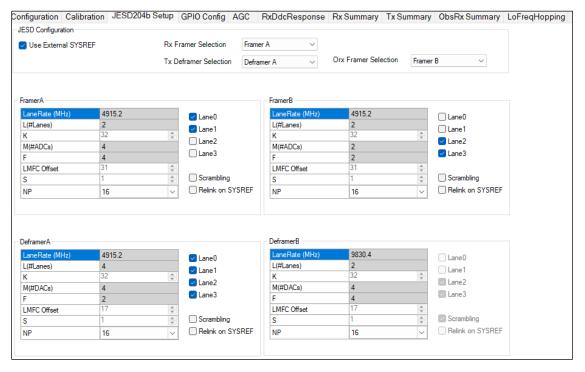

| Figure 6.7. JESD204B Setup Information                                                                    | 64 |

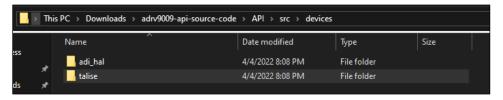

| Figure 6.8. Locating the Software Codes                                                                   |    |

| Figure 6.9. Project Explorer Import Window in Propel                                                      |    |

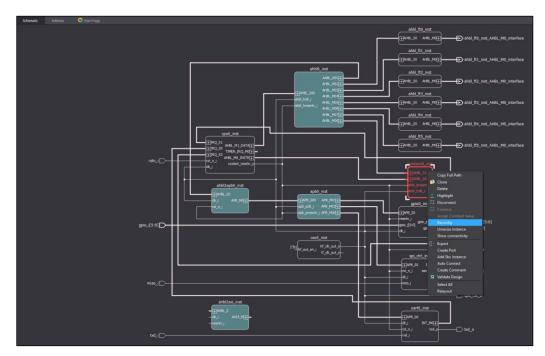

| Figure 6.10. Locating System Memory Module and Selecting Reconfig                                         |    |

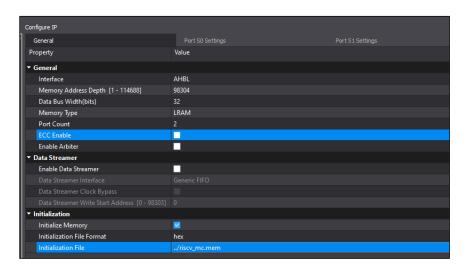

| Figure 6.11. Selecting the Initialization File                                                            |    |

| Figure 6.12. Regenerating the SoC Design RTL                                                              |    |

| Figure 6.13. JESD204B Example Design Block Diagram (with Avant-X and TI Evaluation Boards)                |    |

| Figure 6.14. Regenerating All IP Instances                                                                |    |

| Figure 6.15. Avant Versa Board (Bottom) with TI ADC32RF44EVM Evaluation Board (Top)                       |    |

| Figure 6.16. JESD204B Example Design Block Diagram (with Avant-X and TI Evaluation Boards)                |    |

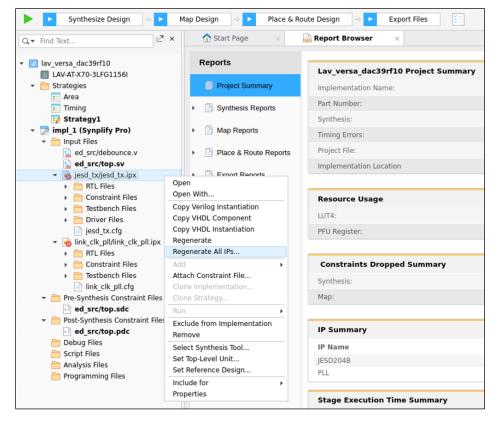

| Figure 6.17. Regenerating All IP Instances                                                                | 74 |

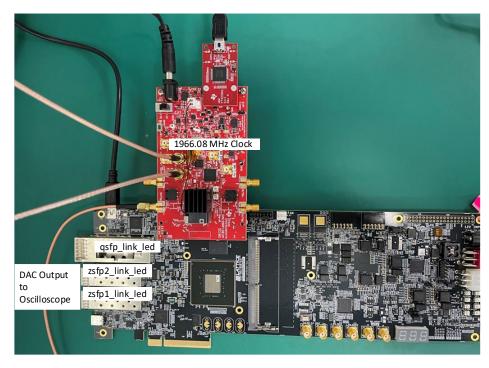

| Figure 6.18. Avant Versa Board (Top) with TI DAC39RF10EVM Evaluation Board (Bottom)                       |    |

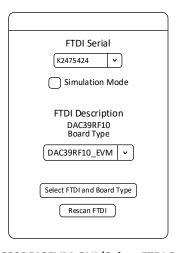

| Figure 6.19. DAC39RF10EVM GUI (Select FTDI Device Window)                                                 |    |

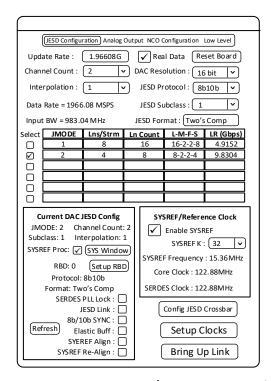

| Figure 6.20. DAC39RF10EVM GUI (DAC39RF1xEVM Window)                                                       |    |

| Figure 6.21. JESD Crossbar Configuration Window                                                           |    |

| Figure 6.22. Output Waveform on Oscilloscope                                                              |    |

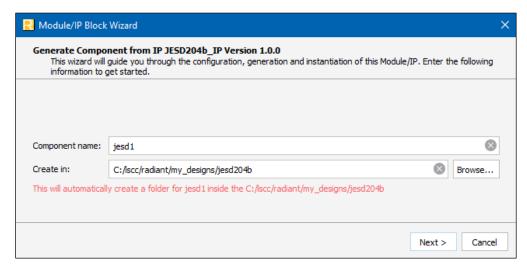

| Figure 7.1. Module/IP Block Wizard                                                                        |    |

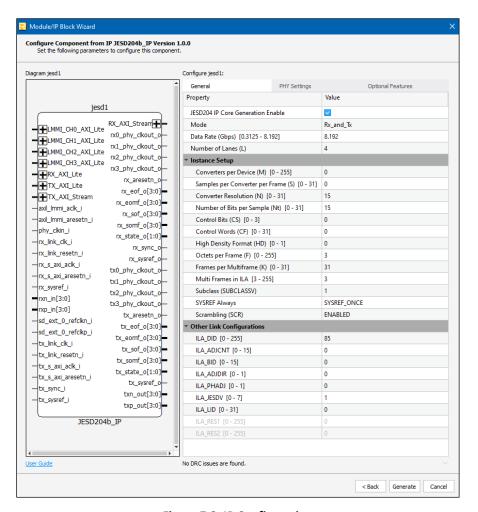

| Figure 7.2. IP Configuration                                                                              |    |

| Figure 7.3. Check Generated Result                                                                        |    |

| Figure 7.4. Simulation Wizard                                                                             |    |

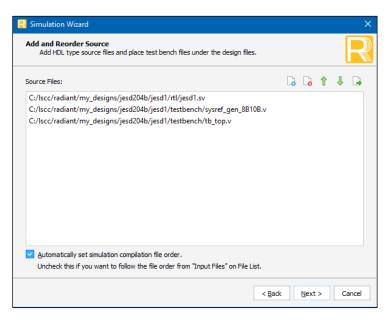

| Figure 7.5. Add and Reorder Source                                                                        |    |

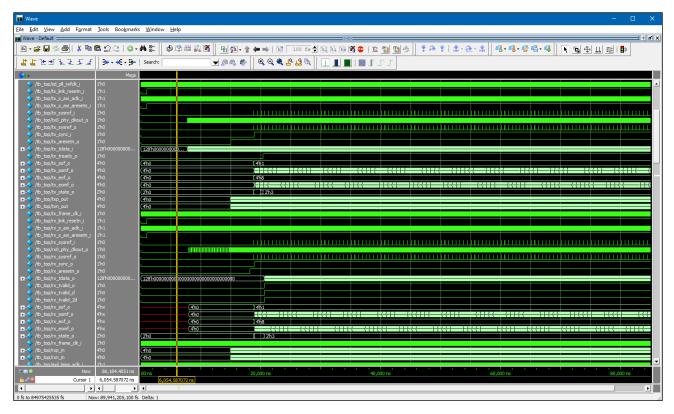

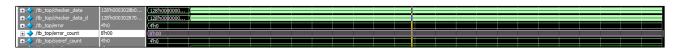

| Figure 7.6. Simulation Waveform                                                                           |    |

|                                                                                                           |    |

| Figure 7.7. | . Test Transcript Result              | 82 |

|-------------|---------------------------------------|----|

| Figure 7.8. | . Example Passing Simulation Waveform | 82 |

# **Tables**

| Table 1.1. Summary of the JESD204B IP                                                       |    |

|---------------------------------------------------------------------------------------------|----|

| Table 1.2. JESD204B IP Support Readiness                                                    |    |

| Table 1.3. Ordering Part Number                                                             |    |

| Table 1.4. Minimum Device Requirements for JESD204B IP                                      |    |

| Table 2.1. JESD204B Rx States                                                               |    |

| Table 2.2. JESD204B Tx States                                                               |    |

| Table 2.3. JESD204B IP Reset Input Overview                                                 |    |

| Table 2.4. JESD204B IP Reset Output Overview                                                |    |

| Table 3.1. General Attributes                                                               |    |

| Table 3.2. PHY Attributes                                                                   |    |

| Table 3.3. Transport Layer Setup Attributes                                                 |    |

| Table 3.4. Test Mode Setup Attributes                                                       |    |

| Table 3.5. Attributes to Enable JESD204B PHY and Link Layer Mode                            |    |

| Table 3.6. Attributes to Enable JESD204B Link Only Mode                                     |    |

| Table 3.7. Attributes to Enable JESD204B PHY Only Mode                                      |    |

| Table 4.1. Signal Ports                                                                     |    |

| Table 4.2. Clock Ports                                                                      |    |

| Table 5.1. Register Access Types                                                            |    |

| Table 5.2. Tx Register Map Overview                                                         | 44 |

| Table 5.3. Tx Control Register                                                              |    |

| Table 5.4. Tx Status Register                                                               |    |

| Table 5.5. Tx Test Mode Register                                                            |    |

| Table 5.6. Tx Link Config 0 Register                                                        |    |

| Table 5.7. Tx Link Config 1 Register                                                        |    |

| Table 5.8. Tx Link Config 2 Register                                                        | 47 |

| Table 5.9. Tx Link Config 3 Register                                                        |    |

| Table 5.10. Tx Link Config 4 Register                                                       |    |

| Table 5.11. Tx Link Config 5 Register                                                       |    |

| Table 5.12. Tx Link Config 6 Register [Offset 0x28 – 0x2B]                                  |    |

| Table 5.13. Tx Link Config 7 Register                                                       |    |

| Table 5.14. Rx Register Map Overview                                                        |    |

| Table 5.15. Rx Control Register                                                             |    |

| Table 5.16. Rx Status Register                                                              |    |

| Table 5.17. Rx Error Status Register                                                        |    |

| Table 5.18. Rx Link Config 0 Register                                                       |    |

| Table 5.19. Rx Link Config 1 Register                                                       |    |

| Table 5.20. Rx Link Config 2 Register                                                       |    |

| Table 5.21. Rx Link Config 3 Register                                                       |    |

| Table 5.22. Rx Link Config 4 Register                                                       |    |

| Table 5.23. Rx Link Config 5 Register                                                       |    |

| Table 5.24. Rx Link Config 6 Register                                                       |    |

| Table 5.25. Rx Link Config 7 Register                                                       |    |

| Table 5.26. Rx Error Counter Register                                                       |    |

| Table 5.27. Buffer Fill Level Register                                                      |    |

| Table 6.1. JESD204B IP Configuration Supported by the CertusPro-NX Device Example Design    |    |

| Table 6.2. Summary of LED Indicators on CPNX Evaluation Board                               |    |

| Table 6.3. JESD204B IP Configuration Supported by the Avant-X Versa Board Rx Example Design |    |

| Table 6.4. Summary of LED Indicators on Avant-X Versa Board (Rx Example Design)             |    |

| Table 6.5. JESD204B IP Configuration Supported by the Avant-X Versa Board Tx Example Design |    |

| Table 6.6. Summary of LED Indicators on Avant-X Versa Board (Tx Example Design)             |    |

| Table 7.1. Generated File List                                                              |    |

| Table A.1. Resource Utilization on LAV-AT-X70 LFG1156 Device                                | 83 |

7

Table A.2. Resource Utilization on LFCPNX-100 LFG672 Device......83

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                          |  |  |

|--------------|-----------------------------------------------------|--|--|

| ADC          | Analog-to-Digital Converter                         |  |  |

| AXI          | Advanced eXtensible Interface                       |  |  |

| CGS          | Code Group Synchronization                          |  |  |

| CMOS         | Complementary Metal Oxide Semiconductor             |  |  |

| CSR          | Control and Status Register                         |  |  |

| DAC          | Digital-to-Analog Converter                         |  |  |

| DUT          | Device Under Test                                   |  |  |

| DW           | Double Word                                         |  |  |

| EBR          | Embedded Block RAM                                  |  |  |

| EOF          | End of Frame                                        |  |  |

| EOMF         | End of Multiframe                                   |  |  |

| ES           | Engineering Sample                                  |  |  |

| FMC          | FPGA Mezzanine Card                                 |  |  |

| FPGA         | Field Programmable Gate Array                       |  |  |

| FSM          | Finite State Machine                                |  |  |

| FTDI         | Future Technology Devices International             |  |  |

| GUI          | Graphical User Interface                            |  |  |

| ILA          | Initial Lane Alignment                              |  |  |

| ILAS         | Initial Lane Alignment Sequence                     |  |  |

| IP           | Intellectual Property                               |  |  |

| IQ           | In-Phase (I) Component and Quadrature (Q) Component |  |  |

| LFC          | Local Frame Clock                                   |  |  |

| LMFC         | Local Multiframe Clock                              |  |  |

| LMMI         | Lattice Memory Mapped Interface                     |  |  |

| LUT4         | 4-bit Look-up Table                                 |  |  |

| LVDS         | Low-Voltage Differential Signaling                  |  |  |

| MPCS         | Multi-protocol Physical Coding Sublayer             |  |  |

| PFU          | Programmable Functional Unit                        |  |  |

| PHY          | Physical                                            |  |  |

| RBD          | Release Buffer Delay                                |  |  |

| Rx           | Receiver                                            |  |  |

| SERDES       | Serializer/Deserializer                             |  |  |

| SOF          | Start of Frame                                      |  |  |

| SOMF         | Start of Multiframe                                 |  |  |

| Tx           | Transmitter                                         |  |  |

| /A/          | Control character K28.3                             |  |  |

| /F/          | Control character K28.7                             |  |  |

| /K/          | Control character K28.5                             |  |  |

| /Q/          | Control character K28.4                             |  |  |

| /R/          | Control character K28.0                             |  |  |

# Introduction

JESD204B is a high-speed serial interface used between data converters, such as analog-to-digital converters (ADCs) and digital-to-analog converters (DACs), and the FPGA device to replace traditional interfaces, such as CMOS and LVDS. With converter sampling rates and data throughput increasing, the JESD204B interface offers advantages in terms of size, cost, and speed.

#### 1.1. Overview of the IP

The Lattice JESD204B IP supports both the Tx and Rx directions, with corresponding PHY, link, and embedded transport layers, on Lattice FPGA devices.

#### 1.2. **Quick Facts**

Table 1.1. Summary of the JESD204B IP

| IP Requirements              | Supported Devices        | CertusPro™-NX, Lattice Avant™-G¹, Avant-X¹,<br>Certus™-N2 (except LN2-CT-20ES)         |

|------------------------------|--------------------------|----------------------------------------------------------------------------------------|

|                              | IP Changes <sup>2</sup>  | Refer to the JESD204B IP Release Notes (FPGA-RN-02006).                                |

| Resource Utilization         | Supported User Interface | AXI4-Lite, AXI4-Stream                                                                 |

| Resource Offization          | Resources                | Refer to Appendix A for resource utilization samples.                                  |

|                              | Lattice Implementation   | IP Core v1.3.0 – Lattice Radiant™ Software 2025.2                                      |

|                              |                          | Lattice Propel™ Design Environment 2025.2                                              |

| Design Tool Support          | Synthesis                | Synopsys® Synplify Pro® for Lattice                                                    |

|                              | Simulation               | Refer to the Lattice Radiant Software User Guide for the list of supported simulators. |

| Driver Support API Reference |                          | Refer to the JESD204B Driver API Reference (FPGA-TN-02412).                            |

#### Notes:

- Excluding engineering sample (ES) devices.

- In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

#### 1.3. **IP Support Summary**

Table 1.2. JESD204B IP Support Readiness

| Device Family    | Simulation Provided | Radiant Timing Model | Hardware Validated |

|------------------|---------------------|----------------------|--------------------|

| CertusPro-NX     | Yes                 | Final                | Yes                |

| Avant-G, Avant-X | Yes                 | Preliminary          | Yes                |

| Certus-N2        | Yes                 | Preliminary          | No                 |

#### 1.4. **Features**

Key features of the JESD204B IP include:

- JESD204B subclass 0 and 1

- Lane rates up to:

- 8.192 Gb/s for CertusPro-NX devices

- 9.8304 Gb/s for Avant-G, Avant-X, and Certus-N2 devices

- Configurable lane counts of:

- 1, 2, or 4 lanes for CertusPro-NX and Certus-N2 devices

- 1, 2, 4, or 8 lanes for Avant-G and Avant-X devices

- Scrambler and descrambler support

- SYSREF modes: One-shot and periodic (always)

- Link layer and PHY layer separation modes

- Configurable embedded transport layer

# 1.5. Licensing and Ordering Information

An IP specific license string is required to enable full use of the JESD204B IP in a complete, top-level design.

The IP can be fully evaluated through functional simulation and implementation (synthesis, map, place and route) without an IP license string. This IP supports Lattice's IP hardware evaluation capabilities. You can create versions of the IP to operate in hardware for a limited time (approximately four hours) without requiring an IP license string. A license string is required to enable timing simulation and to generate a bitstream file that does not include the hardware evaluation timeout limitation.

For more information about pricing and availability of the JESD204B IP, contact your local Lattice Sales Office.

### 1.5.1. Ordering Part Number

**Table 1.3. Ordering Part Number**

| Device Family | Part Number                            |                   |  |

|---------------|----------------------------------------|-------------------|--|

|               | Single Seat Annual Single Seat Perpetu |                   |  |

| CertusPro-NX  | JESD-204B-CPNX-US                      | JESD-204B-CPNX-UT |  |

| Avant-G       | JESD-204B-AVG-US                       | JESD-204B-AVG-UT  |  |

| Avant-X       | JESD-204B-AVX-US                       | JESD-204B-AVX-UT  |  |

| Certus-N2     | JESD-204B-CN2-US                       | JESD-204B-CN2-UT  |  |

# 1.6. Hardware Support

Refer to the Example Design section for more information on the boards used.

# 1.7. Minimum Device Requirements

The minimum device requirements for the JESD204B IP with selected link speeds are as follows:

Table 1.4. Minimum Device Requirements for JESD204B IP

| Device Family    | Link Speed  | Speed Grades            |

|------------------|-------------|-------------------------|

| CertusPro-NX     | 8.192 Gb/s  | 9_High-Performance_1.0V |

|                  | 7 Gb/s      | 8_High-Performance_1.0V |

|                  | 6 Gb/s      | 7_High-Performance_1.0V |

|                  | 6 Gb/s      | 9_Low-Power_1.0V        |

|                  | 5 Gb/s      | 8_Low-Power_1.0V        |

|                  | 4 Gb/s      | 7_Low-Power_1.0V        |

| Avant-G, Avant-X | 9.8304 Gb/s | 2 and 3                 |

|                  | 8.5 Gb/s    | 1                       |

| Certus-N2        | 9.8304 Gb/s | 2 and 3                 |

|                  | 8.5 Gb/s    | 1                       |

## 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.8.2. Signal Names

Signal names that end with:

- \_n are active low signals (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

### 1.8.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

# 2. Functional Description

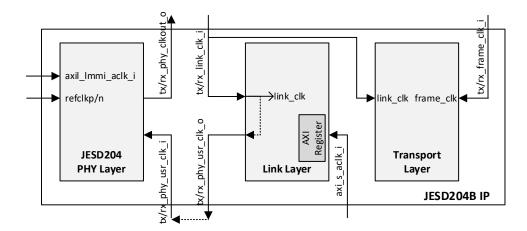

#### 2.1. IP Architecture Overview

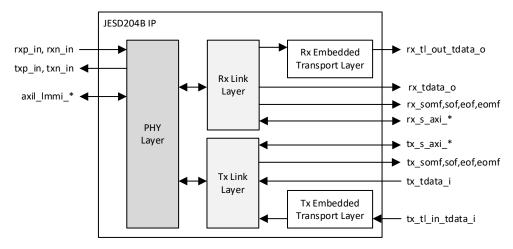

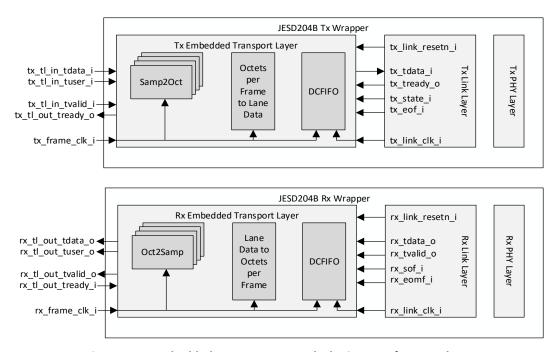

The JESD204B IP supports parameterizable PHY layer, link layer, and embedded transport layer, thus providing the capability for custom configuration based on application needs. Figure 2.1 shows the block diagram of the JESD204B IP.

Figure 2.1. JESD204B IP Block Diagram

# 2.2. Rx Link Layer

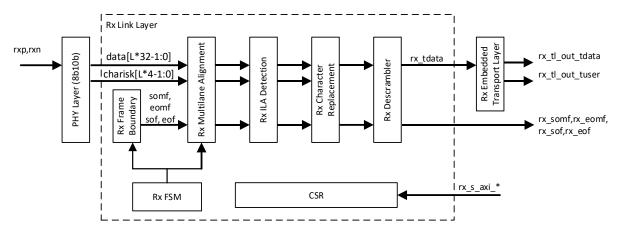

Figure 2.2 shows the JESD204B Rx link layer block diagram. An 8b10b decoder is implemented in the PHY layer, which outputs decoded parallel symbols to the Rx multilane alignment module in the Rx link layer.

Figure 2.2: JESD204B Rx Link Layer Block Diagram

#### 2.2.1. Frame Boundary and State Machine

The Rx frame boundary module regenerates the local frame clock (LFC) and local multiframe clock (LMFC) in the form of SOF-EOF and SOMF-EOMF close loops, respectively. For subclass 1, the module detects SYSREF assertion as a condition to generate the frame clock. For subclass 0, the module generates the frame clock upon exiting reset.

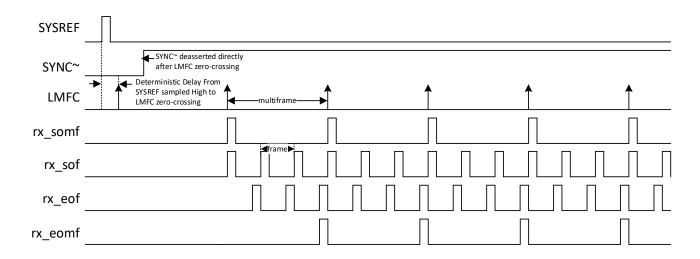

Figure 2.3 illustrates the LMFC correlation with Rx data frame. SOF to EOF indicates the number of octets per frame (F) while SOMF to EOMF indicates the number of frames per multiframe (K) and number of octets per multiframe (F  $\times$  K). SOMF is aligned with the LMFC arrow as illustrated in Figure 2.3.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2.3. Timing Diagram Illustration for LMFC and Rx Frames Interface

The Rx finite state machine (FSM) module indicates the current Rx state through rx\_state\_o. Table 2.1 shows the four JESD204B Rx states. The rx\_sync signal is generated when the link enters the ILA state.

Table 2.1. JESD204B Rx States

| Port       | Bit Setting | State | Description                                                                                                                                                                                                    |

|------------|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_state_o | 2'd0        | IDLE  | Default state. Link waits for Rx SYSREF detection before entering code group synchronization (CGS) state.                                                                                                      |

|            | 2'd1        | CGS   | SYSREF detected and link is detecting the CGS pattern. Once the CGS pattern for all lanes are detected, link enters ILA state.                                                                                 |

|            | 2'd2        | ILA   | Link is detecting the initial lane alignment sequence (ILAS) symbol and decoding the JESD204B ILA configuration. Link waits for all ILAS multiframes (default is four multiframes) before entering DATA state. |

|            | 2'd3        | DATA  | Rx link is receiving user data. Link enters IDLE state when:  Link reinitialization request is received through Rx register.  Link is reset.                                                                   |

## 2.2.2. Multilane Alignment

The Rx multilane alignment module has two main functions:

- CGS pattern detection Upon comma character (/K/) detection on each lane, this module asserts the respective cgs over signal to indicate that the CGS pattern has been detected.

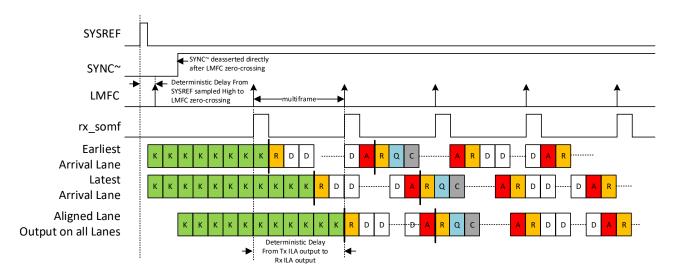

- Interlane symbol deskew During serial data transmission, interlane symbol skew may occur causing symbols across lanes to arrive at different times. This module detects the first ILA character (/R/) of the start of ILA multiframe symbol of each lane in order to later release the characters across lanes at the same time through the FIFO with a depth of 2X the number of octets per multiframe.

Note: Octets per multiframe can range from 1 to 8,192. Therefore, FIFO depth can go up to 16K.

Figure 2.4. Timing Diagram Illustration for Deterministic Latency Equal to Multiples of Multiframe Period

#### 2.2.3. ILA Detection

The Rx ILA detection module detects the ILA sequence and decodes the link configuration parameter. The minimum and default number of ILA multiframes is 4 but the JESD204B specification allows for more than 4 ILA multiframes. The ILA detection module supports an ILA multiframe range of 4 to 256. The Ila\_over signal, when asserted, indicates that all ILA multiframes have been detected.

### 2.2.4. Character Replacement

The JESD204B specification mandates character replacement during the DATA phase depending on whether the scrambler is enabled or disabled (refer to sections 5.3.3.4.2 and 5.3.3.4.3 of the JESD204B specification for more information).

The following are conditions for character replacement by the Rx character replacement module:

- Scrambler is enabled

- When the last scrambled octet in a frame (rx\_eof), but not at the end of multiframe (rx\_eomf), equals to control character /F/, Rx character replacement module will decode it as data 0xFC.

- When the last scrambled octet in a multiframe (rx\_eomf) equals control character /A/, Rx character replacement module will decode it as data 0x7C.

- Scrambler is disabled

- When the last octet in current frame (rx\_eof), not coinciding with the end of multiframe (rx\_eomf), equals to control character /F/, it will replace current character with the last octet in previous frame (rx\_eof).

- When the last octet in current frame at the end of multiframe (rx\_eomf) equals to control character /A/, it will replace current character with the last octet in the previous frame (rx\_eof).

- It is illegal to have two continuous /F/ in back-to-back frames but legal to have /F/ and /A/ in back-to-back frames (because /A/ is EOMF). It is legal to have /F/, /A/, and /F/ in three back-to-back frames.

- Error condition

- An error condition occurs when the link receives any control character apart from EOF and EOMF. This module passes the receive data through as legal data without fixing the error but increases the error counter.

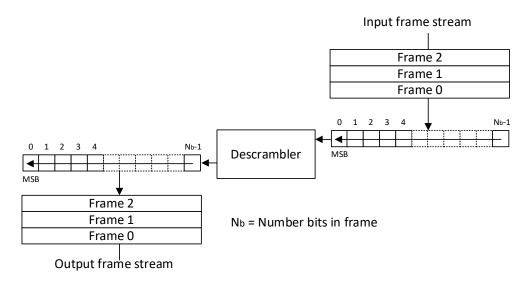

#### 2.2.5. Descrambler

The JESD204B scrambler is self-synchronous with a scrambler polynomial as follows:

$$1+x^{14}+x^{15}$$

The period of this polynomial is long enough (32,767 bits) to meet the spectral requirements of sensitive radio applications while allowing the descrambler to self-synchronize in two octets.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

The scrambler is disabled during the CGS and ILA phases and enabled during the Data phase after the last ILA EOMF character /A/ is detected.

The descrambler is defined via its serial implementation, processing the received data frame by frame. The left-most bit of the frame is shifted in first as illustrated in Figure 2.5. The actual implementation produces the same result as the serial definition.

Figure 2.5. Serial Descrambling

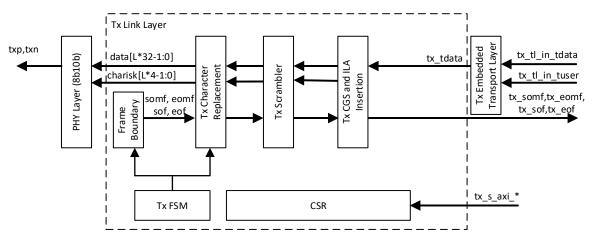

#### 2.3. Tx Link Layer

Figure 2.6 shows the JESD204B Tx link layer block diagram. The Tx link layer packetizes tx\_tdata from the transport layer with CGS and ILA sequences and transmits to the PHY layer. The Tx scrambler can be enabled or disabled before the ILA sequence.

Figure 2.6. JESD204B Tx Link Layer Block Diagram

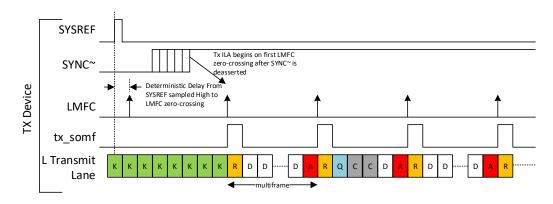

#### 2.3.1. Frame Boundary and State Machine

The Tx frame boundary module regenerates the LFC and LMFC in form of SOF-EOF and SOMF-EOMF. For subclass 1, the module detects SYSREF assertion as a condition to generate the frame clock. For subclass 0, the module generates the frame clock upon exiting reset.

The SOF-EOF period depends on the number of octets per frame (F). The SOMF-EOMF period depends on the number of octets per frame (F) and number of frames per multiframe (K).

Figure 2.7. Tx LMFC Timing Diagram Correlation with tx somf Signal

SOMF is aligned with the LMFC arrow as illustrated in Figure 2.7. SOMF and EOMF are aligned with SOF and EOF, respectively.

The Tx FSM module indicates the current Tx state through tx\_state\_o. Table 2.2 shows the four JESD204B Tx states. This module also detects any resynchronization request from Rx when SYNC~ is asserted (tx\_sync\_i==0) for at least four LMFC periods (refer to section 8.4 of the JESD204B specification for more information).

Table 2.2. JESD204B Tx States

| Port       | Bit Setting | State | Description                                                                                                                                                                                                                                                       |

|------------|-------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_state_o | 2'd0        | IDLE  | Default state. Link waits for Tx SYSREF detection before entering CGS state.                                                                                                                                                                                      |

|            | 2'd1        | CGS   | SYSREF detected and link is transmitting the CGS pattern. Link enters ILA state when SYNC (tx_sync_i==1) is detected.                                                                                                                                             |

|            | 2'd2        | ILA   | Link is transmitting the ILAS. Once the ILAS is transmitted for all multiframes (default is four multiframes), the link enters DATA state.                                                                                                                        |

|            | 2'd3        | DATA  | <ul> <li>Tx link is transmitting user data received from the transport layer.</li> <li>Link enters IDLE state when:</li> <li>Link reinitialization request is received – SYNC~ is asserted (tx_sync_i==0) for more than four consecutive LMFC periods.</li> </ul> |

|            |             |       | Link is reset.                                                                                                                                                                                                                                                    |

#### 2.3.2. CGS and ILA Insertion

The Tx CGS and ILA insertion module inserts CGS and ILA sequence depending on tx\_state\_o from the Tx FSM. During the CGS phase, the module transmits repeated /K/ symbols until the Rx asserts the SYNC signal. Upon detection of SYNC, the module transmits the ILA sequence that aligns with the LMFC period (tx\_somf\_i).

The ILA multiframe starts with /R/ and ends with /A/. The ILA sequence consists of at least four multiframes or up to 256 multiframes, configurable through the MULTI\_FRAME\_IN\_ILA parameter. The second multiframe contains the JESD204B link configuration information (refer to sections 8.2 and 8.3 of the JESD204B specification).

**Note:** A multiframe is defined as a group of K successive frames, where K is between 1 and 32, such that the number of octets per multiframe is between 17 and 1,024:

$$ceil(17/F) \le K \le min(32, floor(1024/F))$$

| Configuration | Bits                     |                  |         |     |        |          |       |     |

|---------------|--------------------------|------------------|---------|-----|--------|----------|-------|-----|

| octet no.     | MSB                      | 6                | 5       | 4   | 3      | 2        | 1     | LSB |

| 0             |                          |                  |         | DID | [7:0]  |          |       |     |

| 1             |                          | ADJCN            | NT[3:0] |     |        | BID      | [3:0] |     |

| 2             | Χ                        | ADJDIR           | PHADJ   |     |        | LID[4:0] |       |     |

| 3             | SCR                      | X                | Χ       |     |        | L[4:0]   |       |     |

| 4             |                          | F[7:0]           |         |     |        |          |       |     |

| 5             | Χ                        | X                | Χ       |     |        | K[4:0]   |       |     |

| 6             |                          |                  |         | M[7 | 7:0]   |          |       |     |

| 7             | CS[                      | CS[1:0] X N[4:0] |         |     |        |          |       |     |

| 8             | SU                       | BCLASSV[2        | 2:0]    |     |        | Np[4:0]  |       |     |

| 9             |                          | JESDV[2:0]       |         |     |        | S[4:0]   |       |     |

| 10            | HD                       | X                | X       |     |        | CF[4:0]  |       |     |

| 11            | RES1[7:0] - Set to all X |                  |         |     |        |          |       |     |

| 12            | RES2[7:0] - Set to all X |                  |         |     |        |          |       |     |

| 13            |                          |                  |         | FCH | ([7:0] |          |       |     |

Figure 2.8. Mapping of Link Configuration Fields to Octets

#### 2.3.3. Scrambler

The JESD204B scrambler is self-synchronous with a scrambler polynomial as follows:

$$1+x^{14}+x^{15}$$

The scrambler is disabled during the CGS and ILA phases and enabled during the Data phase.

The scrambler is defined via its serial implementation, processing the transmitted data frame by frame. The left-most bit of the frame is shifted in first as illustrated in Figure 2.5. The actual implementation produces the same result as the serial definition.

## 2.3.4. Character Replacement

The JESD204B specification mandates character replacement during the DATA phase depending on whether the scrambler is enabled or disabled (refer to sections 5.3.3.4.2 and 5.3.3.4.3 of the JESD204B specification for more information).

The following are conditions for character replacement by the Tx character replacement module:

- Scrambler is enabled

- When the last scrambled octet in a frame (tx\_eof), but not at the end of multiframe (tx\_eomf), equals 0xFC, Tx character replacement module will encode it as control character /F/.

- When the last scrambled octet in a multiframe (tx\_eomf) equals 0x7C, Tx character replacement module will encode it as control character /A/.

- Scrambler is disabled

- When the last octet in current frame (tx\_eof), not coinciding with the end of multiframe (tx\_eomf), equals to the last octet in previous frame (tx\_eof), it will be encoded as control character /F/.

- When the last octet in current frame at the end of multiframe (tx\_eomf) equals the last octet in the previous frame (tx\_eof), it will be encoded as control character /A/.

FPGA-IPUG-02259-1.3

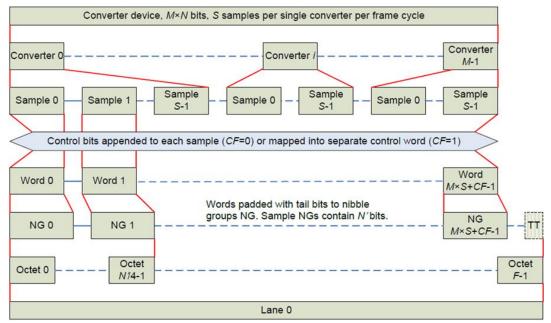

# 2.4. Embedded Transport Layer

The function of the transport layer is to map the data samples from the converter to a non-scrambled octet. In addition, since the input data width of the core is 32 bits per lane, the transport layer is also responsible to output octets that match the expected data width.

Figure 2.9 shows a simple example of how data is mapped from converter samples to octets and output in a lane. Refer to section 5.1 of the JESD204B specification for more examples.

#### Notes:

- 1. CF = Number of control words per frame clock period per link

- 2. F = Number of octets per frame

- 3. M = Number of converters per device

- 4. N = Converter resolution

- 5. N' = Total number of bits per sample

- 6. S = Number of samples per converter per frame cycle

- 7. T = Tail bit

Figure 2.9. User Data Format for Independent Lane with Oversampling

Figure 2.10 shows the embedded transport layer block diagrams for Tx and Rx. The transport layers can be enabled through the respective options in the IP GUI. Refer to the IP Parameter Description and Signal Description sections for the lists of parameters and signals, respectively.

Figure 2.10. Embedded Transport Layer Block Diagrams for Tx and Rx

To calculate the required frame clock frequency, it is important to know that the underlying core is operating at 32 bits per lane in every link clock cycle. These 32 bits are encoded/decoded with 8b10b encoding in the transceiver as required by the JESD204B specification. Hence, the actual link clock frequency can be calculated as follows:

Total Bits Transmitted per Lane per Link Clock Period =  $32b \times (10/8) = 40b$ Link Clock Frequency = Data Rate / 40b

Since the core is expecting 32 bits of data in every link clock cycle, the frame clock frequency required by the transport layer can be calculated using the JESD204B link parameter octets per frame (F), since F determines how many bits are transmitted per frame clock period (see the data mapping diagram in Figure 2.9), as follows:

Frame Clock Frequency  $\times$  (F  $\times$  8) = Link Clock Frequency  $\times$  32

In the scenario where F < 4, the required frame clock frequency may exceed the supported fabric speed depending on the data rate configuration. For example, when data rate = 8.1 Gb/s and F = 1, the required frame clock frequency is 810 MHz. A parameter TL\_FRAME\_PER\_CLK is added to allow multiple frames to be processed at the transport layer in one clock cycle which then lowers the required clock frequency. The updated calculation for the frame clock frequency is as follows:

Frame Clock Frequency × (F × 8) × TL FRAME PER CLK = Link Clock Frequency × 32

For TL\_FRAME\_PER\_CLK > 1, the samples from all converters for the first frame should be placed at LSB, then only followed by the samples for the second frame and so on. For example, if TL\_FRAME\_PER\_CLK = 4, the tdata bus data bit locations are assigned as follows: {Frame 3 samples, Frame 2 samples, Frame 1 samples, Frame 0 samples}. The transport layer tdata width is byte oriented (8, 16, 24, 32 ... bits). Any remaining MSB bits, after packing of all sample data, are padded with 0s.

Transport Layer Data Width =  $ceil((ILA\_M+1) \times (ILA\_S+1) \times (ILA\_N+1) \times TL\_FRAME\_PER\_CLK/8) \times 8$

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

**Note:** ILA\_M, ILA\_S, and ILA\_N are registers whose values are offset by minus one from the actual values the registers are representing. For example, ILA\_M = 0 indicates one converter, ILA\_S = 1 indicates 2 samples per converter, and ILA\_N = 2 indicates 3 bits per sample.

The following examples are simple illustrations for the timing diagrams of incoming samples from converter devices and the outgoing octet data to the JESD core.

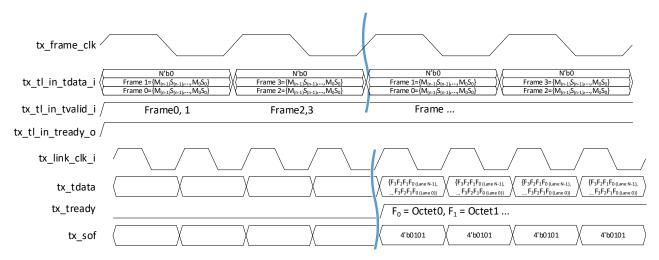

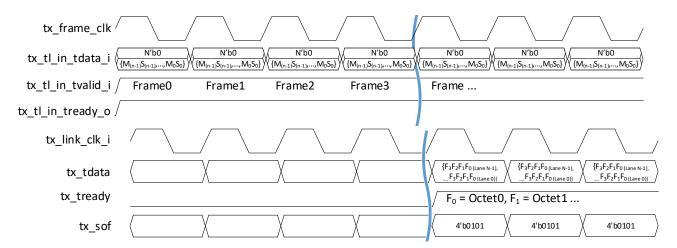

In the first example, the timing diagrams with the link parameter OCTET\_PER\_FRAME set to 2 and TL\_FRAME\_PER\_CLK set to 2 and 1 are shown in Figure 2.11 and Figure 2.12, respectively.

- 1. When tx\_tl\_in\_tready is asserted at cycle 0, this indicates that the Tx transport layer is ready to accept data. The first sample from the converter comes in at the same cycle as when tx\_tl\_in\_tvalid is asserted.

- 2. Later when the transport layer sees tx\_tready from the core is asserted, it starts to transmit the lane data to the core at the tx\_tdata bus. The data are the remapped samples in octet format where each lane is fixed to a 32-bit wide data bus.

The LSB of the data bus is usually Octet 0 of the frame and the subsequent byte is followed by Octet 1. Note that these data also need to be aligned with tx\_sof output from the core where a bit in tx\_sof indicates that a specific byte location in the tx\_tdata bus is the start of frame.

For instance, in the diagram, tx\_sof = 0101 indicates that the core is expecting the data at start of frame to be placed at byte locations 0 and 2 in the tx\_tdata bus. Hence, at the F0 and F2 positions in the tdata\_bus of every lane, the octet is expected to be the data at start of frame from the in\*\_tdata bus.

Figure 2.11. Timing Diagram with OCTET PER FRAME = 2 and TL FRAME PER CLK = 2

Figure 2.12. Timing Diagram with OCTET\_PER\_FRAME = 2 and TL\_FRAME\_PER\_CLK = 1

FPGA-IPUG-02259-1.3

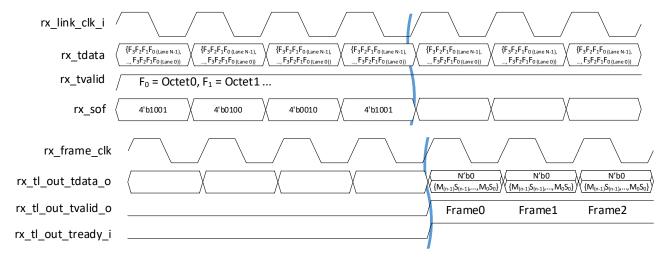

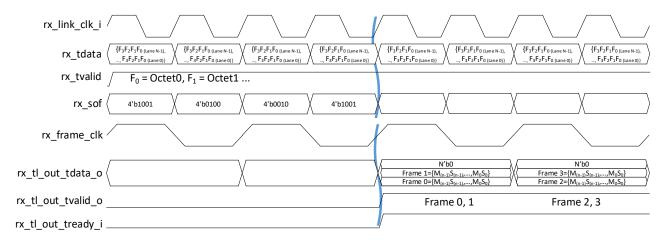

In the second example, the timing diagrams at the Rx transport layer with OCTET\_PER\_FRAME set to 3 and TL FRAME PER CLK set to 1 and 2 are shown in Figure 2.13 and Figure 2.14, respectively.

- 1. As the rx\_tvalid signal is asserted, the transport layer starts to accept data from Rx core. Note that at clock cycle 0, rx\_sof = 1001 indicates that byte locations 0 and 3 at rx\_tdata are the data at start of frame, which means that the data at the F0, F1, and F2 positions of every lane from rx\_tdata form the samples of the first frame to the converter while the data at the F3 position are part of the subsequent second frame.

- 2. At clock cycle 1, the value of rx\_sof changes to 0100 indicating that the data at start of frame has changed to byte location 2 at rx\_tdata. This means that the data at the F0 and F1 positions in this clock cycle form the samples of the second frame to the converter along with the data at the F3 position from the previous clock cycle. The data at the F2 and F3 positions in this clock cycle are part of the third frame with F2 at lane 0 forming the start of frame.

- 3. At clock cycle 2, the value of rx\_sof changes to 0010 indicating that the data at the F0 position of all lanes in this clock cycle form the last few missing data for the third frame. The data at the F1, F2, and F3 positions of rx\_tdata together form the samples of the fourth frame.

- 4. When the transport layer sees the rx\_tl\_in\_tready signal asserted, it starts outputting the remapped data to the application layer as well as asserting the rx\_tl\_out\_tvalid signal. Note that rx\_tl\_out\_tready and rx\_tl\_out\_tvalid have no dependency on each other and one may assert earlier than the other. Data transfer between manager and subordinate only occurs when both signals are asserted. The Rx\_tl\_out\_tready\_i signal is not expected toggle once it gets asserted as the incoming frame clock and link clock have the same ratio as the input and output data widths, and hence equal in throughput.

Figure 2.13. Timing Diagram with OCTET PER FRAME = 3 and TL FRAME PER CLK = 1

Figure 2.14. Timing Diagram with OCTET\_PER\_FRAME = 3 and TL\_FRAME\_PER\_CLK = 2

FPGA-IPUG-02259-1.3

## 2.5. JESD204B PHY Layer

The JESD204B PHY layer is enabled and preconfigured as part of the JESD204B IP. The IP also handles the reset sequence for the JESD204B PHY layer. You only need to configure the *Data Rate*, *Number of Lanes*, and *Ref Clk Freq* attributes as shown in the IP Parameter Description section.

The JESD204B IP offers the flexibility of enabling or disabling generation of the JESD204B PHY layer through the *JESD204 IP Core Generation Enable* attribute. The JESD204B IP also offers the flexibility of generating only the JESD204B PHY layer (JESD204B PHY layer separation mode). This is accomplished by setting the *JESD204B IP Core Generation Enable* attribute to unchecked and *JESD204 PHY Generation Enable* attribute to checked.

When the JESD204B PHY layer separation mode is enabled, only the JESD204B PHY wrapper and respective interfaces are generated. You need to connect the PHY layer to the link layer manually.

Figure 2.15 shows the JESD204B PHY layer module.

- ${\bf 1.}\ {\bf Applicable}\ {\bf for}\ {\bf the}\ {\bf CertusPro-NX}\ {\bf device}\ {\bf only}.$

- 2. Applicable for the Avant-G/X device only.

Figure 2.15. JESD204B PHY Layer Module

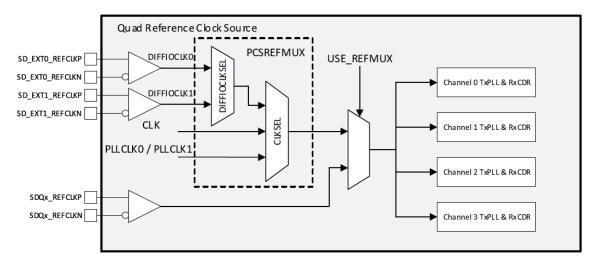

#### 2.5.1. PLL Reference Clock for CertusPro-NX Device

The JESD204B PHY layer supports reference clock selection through the *PMA Reference Clock* attribute. You can select one of six options (sd\_ext\_0\_refclk, sd\_ext\_1\_refclk, sdq0\_refclk, sdq1\_refclk, pclk0, pclk1) as the PMA reference clock source. The JESD204B PHY layer constrains mux select according to the selection internally so that the output is the selected reference clock. For PCS reference clock information, refer to CertusPro-NX SerDes/PCS User Guide (FPGA-TN-02245).

Figure 2.16. CertusPro-NX PCS REFCLK Architecture

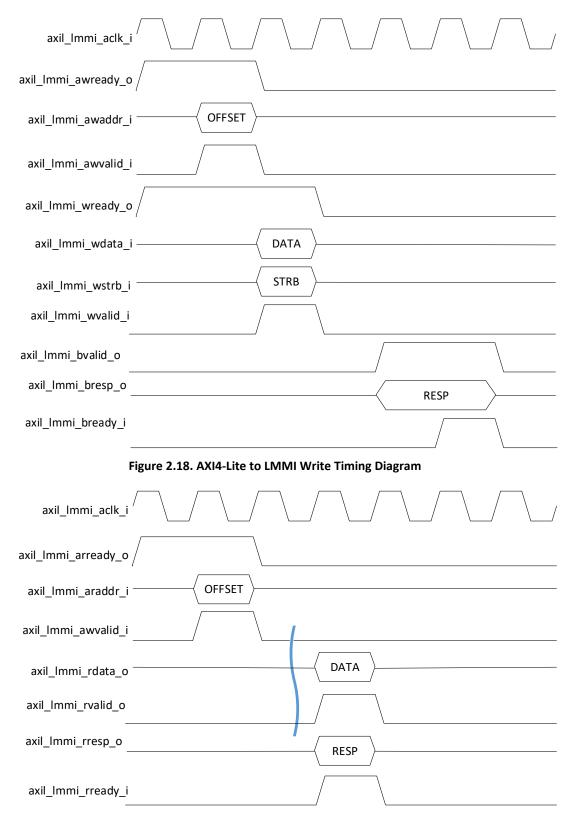

#### 2.5.2. AXI4-Lite to LMMI

The JESD204B PHY layer supports access to the PHY layer configuration register through the AXI4-Lite to LMMI interface. AXI4-Lite read and write data are double word (DW) aligned. For register information, refer to the following:

- Lattice Avant SERDES/PCS User Guide (FPGA-TN-02313)

- CertusPro-NX SerDes/PCS User Guide (FPGA-TN-02245)

- Lattice Nexus 2 SERDES/PCS User Guide (FPGA-TN-02395)

Figure 2.17 shows the supported AXI4-Lite aligned transfer with respect to 8-bit, 16-bit, or 32-bit transfer. JESD204B AXI4-Lite to LMMI does not support AXI4 unaligned transfer (refer to the AMBA AXI Protocol Specification document). Figure 2.18 and Figure 2.19 show the AXI4-Lite timing diagrams.

| Regist           | Register offset access |             | 23 16  | 15 8  | 7 0   |

|------------------|------------------------|-------------|--------|-------|-------|

| sfer             | Offset 0x0             |             |        |       | BYTE0 |

| 8-bits transfer  | Offset 0x1             |             |        | BYTE1 |       |

| oits t           | Offset 0x2             |             | BYTE2  |       |       |

| 3-8              | Offset 0x3             | BYTE3       |        |       |       |

| fer              | Offset 0x0             |             |        | BYTE1 | BYTE0 |

| rans             | Offset 0x1             |             | Not al | lowed |       |

| 16-bits transfer | Offset 0x2             | BYTE3       | BYTE2  |       |       |

| 16-k             | Offset 0x3             |             | Not al | lowed |       |

| ifer             | Offset 0x0             | BYTE3       | BYTE2  | BYTE1 | BYTE0 |

| rans             | Offset 0x1             |             | Not al | lowed |       |

| 32-bits transfer | Offset 0x2             | Not allowed |        |       |       |

| 32-k             | Offset 0x3             |             | Not al | lowed |       |

Figure 2.17. AXI4-Lite to LMMI Aligned Transfer on 8-bit, 16-bit, and 32-bit Buses

Figure 2.19. AXI4-Lite to LMMI Read Timing Diagram

# 2.6. Clocking Overview

This section describes the JESD204B IP clock architecture. Figure 2.20 shows an overview of the JESD204B IP clock domain. All clock domain crossings are handled in the IP.

Figure 2.20. JESD204B IP Clock Domain Block Diagram

Refer to the Clock Interface section for descriptions of the JESD204B IP clock signals.

### **2.7.** Reset

This section describes the JESD204B IP reset scheme.

Table 2.3. JESD204B IP Reset Input Overview

|                                           |      | Component to be Reset |    |                         |    |          |     |          |

|-------------------------------------------|------|-----------------------|----|-------------------------|----|----------|-----|----------|

| Reset                                     | Туре | CSR (AXI4-Lite)       |    | Link and Transport Core |    | РНҮ      |     |          |

|                                           |      | Tx                    | Rx | Tx                      | Rx | LMMI Reg | PCS | PMA      |

| Link Wrapper                              |      |                       |    |                         |    |          |     |          |

| tx_s_axi_aresetn_i                        | Pin  | ✓                     | _  | ✓                       | _  | _        | ✓   | ✓        |

| tx_link_resetn_i                          | Pin  | _                     | _  | ✓                       | _  | _        | ✓   | ✓        |

| Tx Core Reset (CSR offset 0x00 bit[0])    | Reg  | _                     | _  | <b>~</b>                | _  | _        | ✓   | <b>√</b> |

| rx_s_axi_aresetn_i                        | Pin  | _                     | ✓  | _                       | ✓  | _        | ✓   | ✓        |

| rx_link_resetn_i                          | Pin  | _                     | _  | _                       | ✓  | _        | ✓   | ✓        |

| Rx Core Reset<br>(CSR offset 0x00 bit[0]) | Reg  | _                     | _  | _                       | ✓  | _        | ✓   | <b>√</b> |

| PHY Wrapper                               |      |                       |    |                         |    |          |     |          |

| axil_lmmi_aresetn_i                       | Pin  | _                     | _  | _                       | _  | ✓        | ✓   | ✓        |

| txN_phy_resetn_i<br>(see note¹)           | Pin  | _                     | _  | _                       | _  | _        | ✓   | <b>√</b> |

| rxN_phy_resetn_i<br>(see note¹)           | Pin  | _                     | _  | _                       | _  | _        | √   | <b>√</b> |

#### Note:

1. When the PHY is in Rx\_only or Tx\_only mode, asserting the respective rxN/txN\_phy\_resetn\_i resets both PMA and PCS. When the PHY is in Rx\_and\_Tx mode, both txN\_phy\_resetn\_i and rxN\_phy\_resetn\_i must be asserted to reset the PMA and PCS. Otherwise, only the respective Tx PCS and Rx PCS are reset.

### Table 2.4. JESD204B IP Reset Output Overview

| Reset                             | Туре                       | Description                                                                                                                            |  |  |  |  |

|-----------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <b>Link and Transport Wrapper</b> | Link and Transport Wrapper |                                                                                                                                        |  |  |  |  |

| tx_aresetn_o                      | Pin                        | Output reset signal from Tx indicating that link is in reset when de-asserted.                                                         |  |  |  |  |

| rx_aresetn_o                      | Pin                        | Output reset signal from Rx indicating that link is in reset when de-asserted.                                                         |  |  |  |  |

| PHY Wrapper                       | PHY Wrapper                |                                                                                                                                        |  |  |  |  |

| txN_phy_ready_o                   | Pin                        | Output ready signal from PHY to indicate that Tx PHY is ready. Used as reset to link layer (excludes AXI register) when phy_ready = 0. |  |  |  |  |

| rxN_phy_ready_o                   | Pin                        | Output ready signal from PHY to indicate that Rx PHY is ready. Used as reset to link layer (excludes AXI register) when phy_ready = 0. |  |  |  |  |

# 3. IP Parameter Description

The configurable attributes of the JESD204B IP are shown in the following tables. You can configure the IP by setting the attributes accordingly in the IP Catalog Module/IP wizard of the Lattice Radiant software.

Wherever applicable, default values are in bold.

### 3.1. General

**Table 3.1. General Attributes**

| Attribute                            | Selectable Values                                     | Description                                                                                                                        |

|--------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| JESD204 IP Core Generation<br>Enable | Checked, Unchecked                                    | Enables JESD204B link layer IP generation.                                                                                         |

| Mode                                 | Rx_and_Tx, Rx_only, Tx_only                           | Selects the IP mode.                                                                                                               |

| Data Rate (Gbps)                     | CertusPro-NX: 0.7425 – 8.192 <sup>1</sup>             | For CertusPro-NX devices, enter the JESD204B data rate in the range from 0.7425 to 8.192 Gb/s.                                     |

|                                      | Avant-G/X, Certus-N2:<br>1.2288 – 9.8304 <sup>2</sup> | For Avant-G, Avant-X, and Certus-N2 devices, enter the JESD204B data rate in the range from 1.2288 to 9.8304 Gb/s.                 |

|                                      |                                                       | Note: Valid values or ranges are as follows:                                                                                       |

|                                      |                                                       | • 1.2288 Gbps                                                                                                                      |

|                                      |                                                       | • 1.25 – 1.289 Gbps                                                                                                                |

|                                      |                                                       | • 1.375 – 2.57812 Gbps                                                                                                             |

|                                      |                                                       | • 2.75 – 5.15625 Gbps                                                                                                              |

|                                      |                                                       | • 5.5 – 6.64062 Gbps                                                                                                               |

|                                      |                                                       | • 7.34 – 9.8304 Gbps                                                                                                               |

| Number of Lanes (L)                  | <b>1</b> , 2, 4, 8                                    | Number of lanes. Only Avant devices support 8 lanes.                                                                               |

| Converters per Device (M)            | 0-255                                                 | Sets the number of converters per device. The lowest selectable value corresponds with the lowest allowable setting.               |

| Samples per Converter per Frame (S)  | 0-31                                                  | Sets the number of samples per converter per frame. The lowest selectable value corresponds with the lowest allowable setting.     |

| Converter Resolution (N)             | 0-31                                                  | Sets the number of bits per converter sample. The lowest selectable value corresponds with the lowest allowable setting.           |

| Number of Bits per Sample (Nt)       | 0-31                                                  | Sets the number of bits per sample in user data format. The lowest selectable value corresponds with the lowest allowable setting. |

| Control Bits (CS)                    | 0-3                                                   | Sets the number of control bits per device.                                                                                        |

| Control Words (CF)                   | 0-31                                                  | Sets the number of control words per frame clock per link.                                                                         |

| High Density Format (HD)             | 0, 1                                                  | Enables or disables high density format.                                                                                           |

| , , ,                                |                                                       | 0 – Disable high density user data format                                                                                          |

|                                      |                                                       | 1 – Enable high density user data format                                                                                           |

| Octets per Frame (F)                 | 0-255                                                 | Sets the number of octets per frame. The lowest selectable value corresponds with the lowest allowable setting.                    |

| Frames per Multiframe (K)            | 0-31                                                  | Sets the number of frames per multiframe. The lowest selectable value corresponds with the lowest allowable setting.               |

|                                      |                                                       | <b>Note:</b> (Octets per Frame + 1) × (Frames per Multiframe + 1) must be a multiple of 4.                                         |

| Multi Frames in ILA                  | 3-255                                                 | Sets the number of multiframes required in ILAS phase.                                                                             |

| Subclass (SUBCLASSV)                 | 0, 1                                                  | Selects the JESD204B subclass mode.                                                                                                |

|                                      |                                                       | 0 – Subclass 0                                                                                                                     |

|                                      |                                                       | 1 – Subclass 1                                                                                                                     |

| SYSREF Always                        | SYSREF_ONCE,                                          | Selects the incoming SYSREF operating mode.                                                                                        |

|                                      | SYSREF_ALWAYS                                         | SYSREF_ONCE – One shot                                                                                                             |

|                                      |                                                       | SYSREF_ALWAYS – Periodic                                                                                                           |

| Attribute        | Selectable Values | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scrambling (SCR) | ENABLED, DISABLED | Enables or disables the scrambler/descrambler.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ILA_DID          | 0-255             | Device (= link) identification number.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ILA_ADJCNT       | 0-15              | Number of adjustment resolution steps to adjust DAC LMFC.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ILA_BID          | 0-15              | Bank ID – Extension to DID                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ILA_ADJDIR       | 0, 1              | Direction to adjust DAC LMFC 0 – Advance 1 – Delay                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ILA_PHADJ        | 0, 1              | Phase adjustment request to DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ILA_JESDV        | 0, 1              | JESD204 version<br>000 – JESD204A<br>001 – JESD204B                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ILA_LID          | 0-31              | Lane identification number (within link) for Lane 0. The LID of a subsequent lane is an increment of the LID of the previous lane. For example, for <i>Number of Lanes</i> =4 and <i>ILA_LID</i> =5, Lane0 LID=5, Lane1 LID=6, Lane2 LID=7, and Lane3 LID=8. The valid range is dependent on the number of lanes:  If <i>Number of Lanes</i> =1, the valid range is 0-31.  If <i>Number of Lanes</i> =2, the valid range is 0-30.  If <i>Number of Lanes</i> =4, the valid range is 0-28. |

#### Notes:

- 1. The CertusPro-NX device supports data rates up to 8.192 Gb/s.

- 2. The Avant-G, Avant-X, and Certus-N2 devices support multiple continuous data rate ranges up to 9.8304 Gb/s.

## 3.2. PHY

**Table 3.2. PHY Attributes**

| Attribute                        | Selectable Values                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

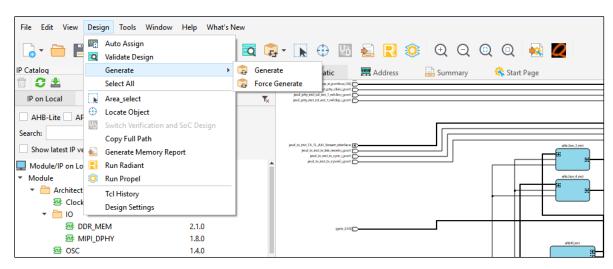

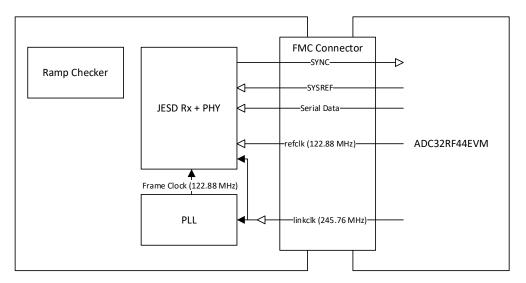

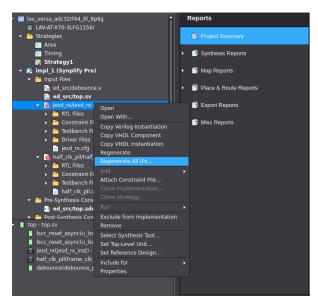

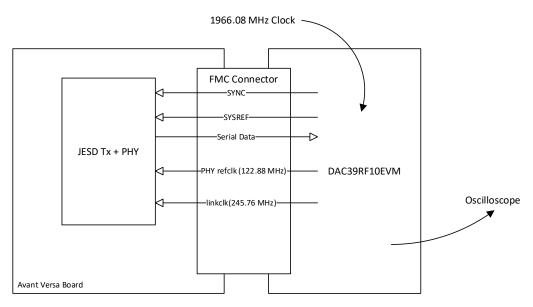

|----------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|