# **Lattice RISC-V Embedded Design Guidelines**

# **Application Note**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

|         | 5                                                                  |    |

|---------|--------------------------------------------------------------------|----|

| Acronym | ns in This Document                                                | 6  |

| 1. Intr | oduction                                                           | 7  |

| 1.1.    | Overview                                                           | 7  |

| 1.2.    | Purpose                                                            | 7  |

| 1.3.    | Audience                                                           | 7  |

| 2. Latt | ice RISC-V Processors Family                                       | 8  |

| 3. RISC | C-V Embedded Hardware Design Guidelines                            | 9  |

| 3.1.    | RISC-V Processor Reset and Exception Vector                        | 9  |

| 3.2.    | RISC-V Processor Memory Selection                                  | 9  |

| 3.2.    | 1. Cache                                                           | 9  |

| 3.2.    | 2. System Memory                                                   | 10 |

| 3.2.    | 3. Tightly Coupled Memory (TCM)                                    | 10 |

| 3.2.    | 4. External SDRAM Memory                                           | 10 |

| 3.2.    | 5. Flash Memory                                                    | 11 |

| 3.3.    | Interconnects and Bridges                                          | 11 |

| 3.3.    | 1. Using AXI4 Interconnect IP                                      | 11 |

| 3.3.    | 2. Using AHB-Lite Interconnect IP                                  | 15 |

| 3.3.    | 3. Using APB Interconnect IP                                       | 17 |

| 3.3.    | 4. Using Bridges IP                                                | 17 |

| 3.3.    | 5. Using Feedthrough IP                                            | 18 |

| 3.4.    | Assigning Address Map                                              | 19 |

| 4. RISC | C-V Embedded Software Design Guidelines                            | 21 |

| 4.1.    | Software Project Support                                           | 21 |

| 4.2.    | Board Support Package (BSP)                                        | 21 |

| 4.2.    |                                                                    |    |

| 4.3.    | Software Compiler Optimization Options                             | 22 |

| 4.3.    | 1. C/C++ Compiler Flow                                             | 23 |

| 4.3.    | 2. Compiler Architecture                                           | 23 |

| 4.3.    | 3. Optimization Levels                                             | 24 |

| 4.3.    | 4. C/C++ Compiler Optimization in the Lattice Propel Software      | 25 |

| 4.3.    | 5. Fine Grain Control of Optimization                              | 26 |

| 4.3.    | 6. Linker Relaxation                                               | 28 |

| 4.3.    | 7. Link Time Optimization                                          | 28 |

| 4.4.    | Linker Script                                                      | 28 |

| 4.4.    | ·                                                                  |    |

| 4.4.    | 2. Lattice Propel SDK Default Linker Script                        | 31 |

| 4.5.    | Interrupts                                                         | 40 |

| 4.5.    | 1. RISC-V Interrupt Architecture                                   | 40 |

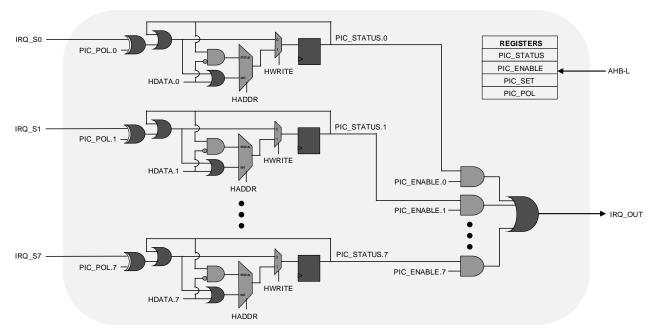

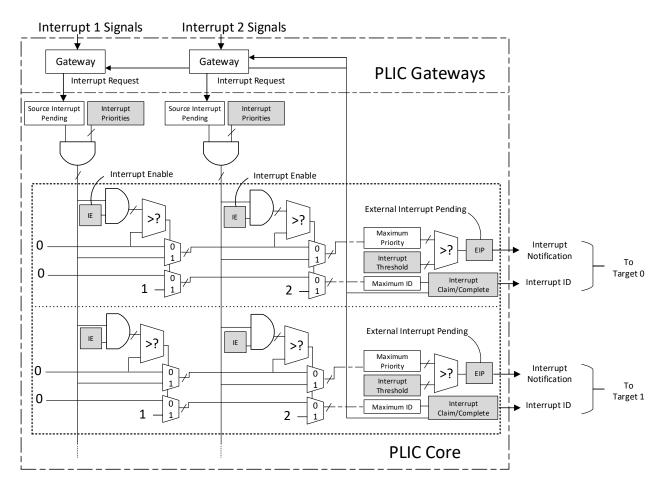

| 4.5.    | 2. Lattice RISC-V Interrupt Controller Hardware                    | 41 |

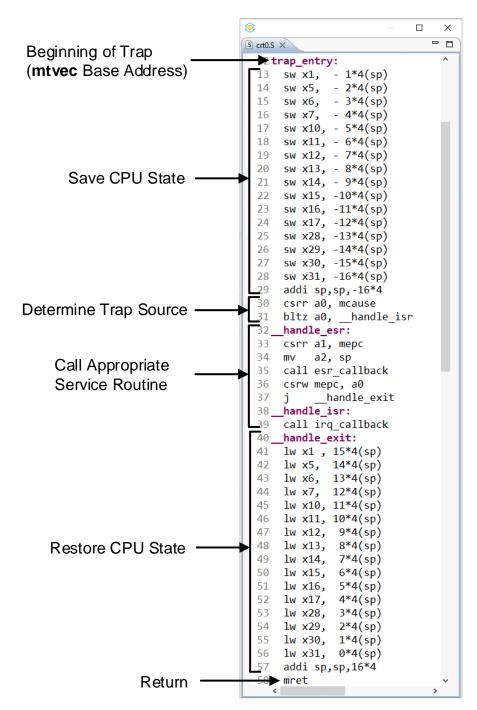

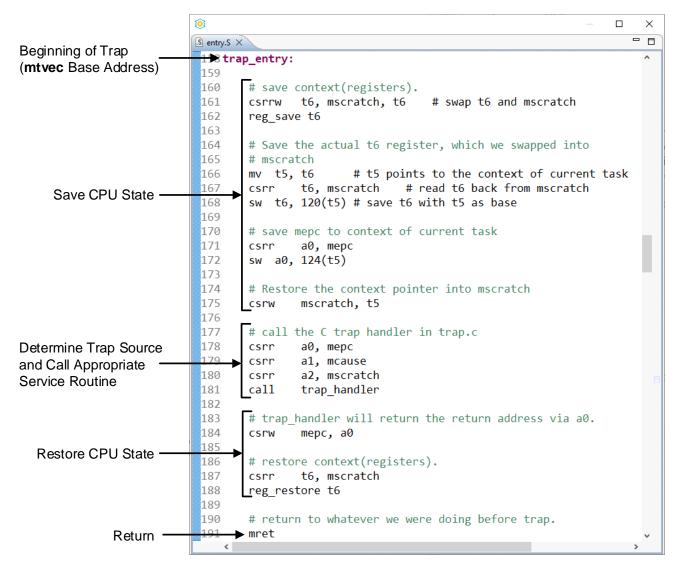

| 4.5.    | 3. Lattice RISC-V Trap Handlers                                    | 44 |

| 4.5.    | 4. Using the Lattice RISC-V BSP Interrupt Firmware                 | 49 |

| 5. RISC | C-V System Debugging                                               | 51 |

| 5.1.    | Using OpenOCD Debugger and Reveal Analyzer                         | 51 |

| 5.2.    | Using Breakpoints                                                  | 53 |

| 5.2.    | 1. Hardware Breakpoints                                            | 53 |

| 5.2.    | 2. Software Breakpoints                                            | 53 |

| 5.3.    | Using Semihosting                                                  | 53 |

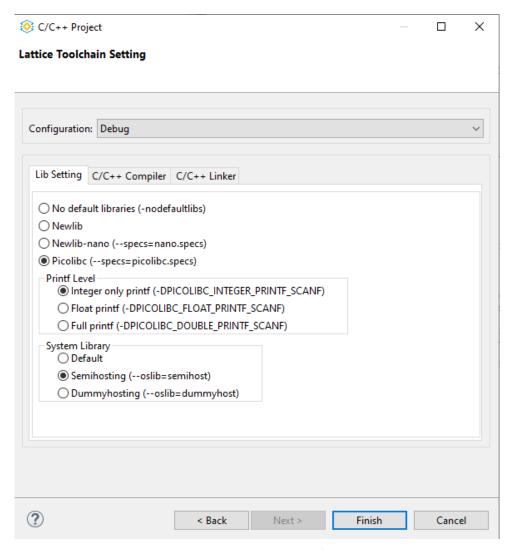

| 5.3.    | Enabling Semihosting During Project Creation in Lattice Propel SDK | 54 |

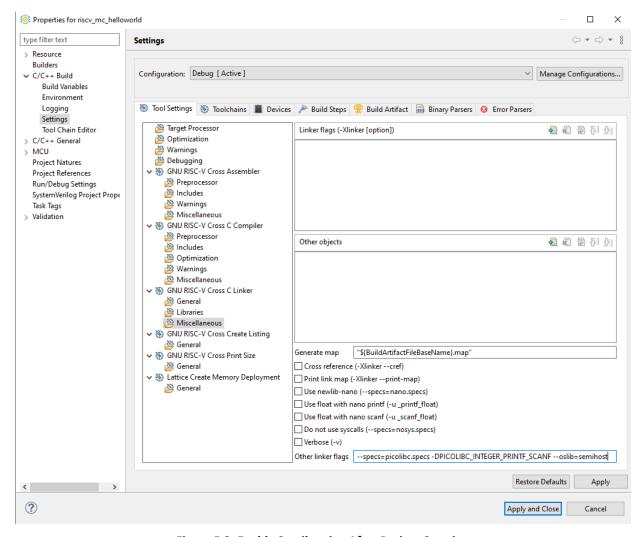

| 5.3.    |                                                                    |    |

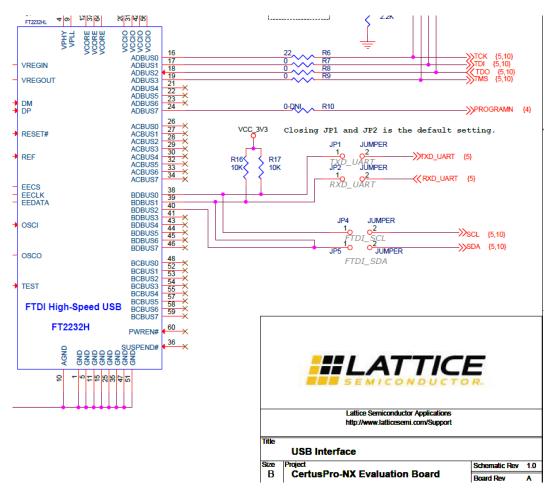

| 5.4.    | Setting UART Serial Interface                                      | 56 |

|         |                                                                    |    |

| References                   | 58 |

|------------------------------|----|

| Technical Support Assistance |    |

| Revision History             |    |

| xevision - notory            |    |

# **Figures**

| Figure 3.1. AXI4 Interconnect IP Parameters – General Tab                            | 11 |

|--------------------------------------------------------------------------------------|----|

| Figure 3.2. AXI4 Interconnect IP Parameters – External Manager Settings Tab          |    |

| Figure 3.3. AXI4 Interconnect IP Parameters – External Subordinate Settings Tab      |    |

| Figure 3.4. Example System with Different Clock Domains                              |    |

| Figure 3.5. AHB-Lite Interconnect IP Parameters – General Tab                        |    |

| Figure 3.6. System with APB Interconnect for Peripherals Access                      |    |

| Figure 3.7. Lattice Propel Builder System with Feedthrough IP                        |    |

| Figure 3.8. APB Feedthrough Module/IP Block Wizard                                   |    |

| Figure 3.9. Address Map of Feedthrough IP                                            |    |

| Figure 3.10. Address Map for Peripherals                                             |    |

| Figure 4.1. Update System and BSP Wizard                                             |    |

| Figure 4.2. Phases of Compilation                                                    |    |

| Figure 4.3. Generalized Compiler Architecture                                        |    |

| Figure 4.4. Optimization Setting during Project Creation                             |    |

| Figure 4.5. Changing Optimization Level from the Lattice Propel SDK Project Settings |    |

| Figure 4.6. Using the #pragma Directive to Control Optimization Level                |    |

| Figure 4.7. Applying an Optimize Attribute to a Function                             |    |

| Figure 4.8. Phases of Compilation                                                    |    |

| Figure 4.9. Lattice Propel SDK Linker Configuration GUI                              |    |

| Figure 4.10. Lattice Propel SDK Linker Script Text Editor                            |    |

| Figure 4.11. Autogenerated Linker Script for SoC System with Two Memory Regions      |    |

| Figure 4.12start Entry Point in RISC-V MC BSP                                        |    |

| Figure 4.13. MEMORY Command Defining Two Memory Regions                              |    |

| Figure 4.14. Autogenerated Linker Script .text Section                               |    |

| Figure 4.15. Definition for .ctors and .dtors Output Sections                        |    |

| Figure 4.16. Definition for .rodata Output Section                                   |    |

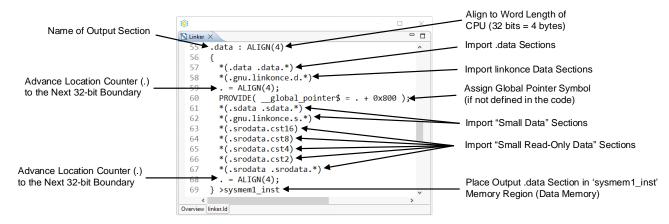

| Figure 4.17. Definition for .data Output Section                                     |    |

| Figure 4.18. RISC-V Load and Store Instruction Encodings                             |    |

| Figure 4.19. Startup Code Initializing gp (Global Pointer Register)                  |    |

| Figure 4.20. Configuration of the Small Data Limit in Lattice Propel SDK             |    |

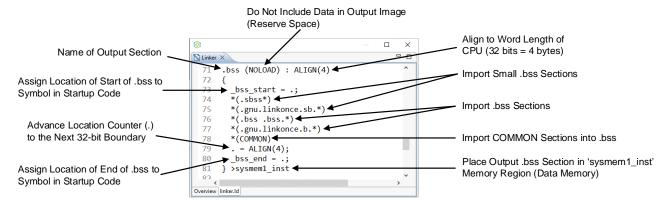

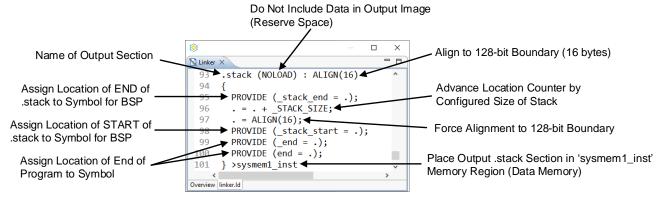

| Figure 4.21. Definition for .bss Output Section                                      |    |

| Figure 4.22bss Initialization Loop in crt0.S Source File                             |    |

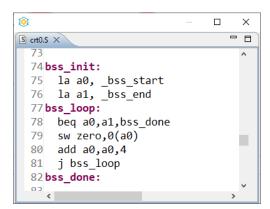

| Figure 4.23. Definition for .heap Output Section                                     |    |

| Figure 4.24. Defining Heap and Stack Size Symbol                                     |    |

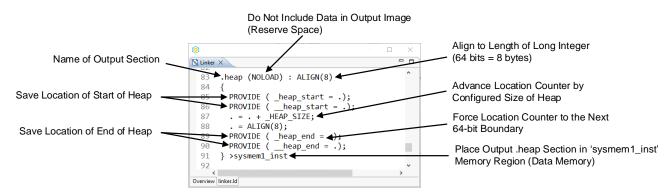

| Figure 4.25. Definition for .stack Output Section                                    |    |

| Figure 4.26. Programmable Interrupt Controller (PIC)                                 |    |

| Figure 4.27. Platform Level Interrupt Controller (PLIC) Block Diagram                |    |

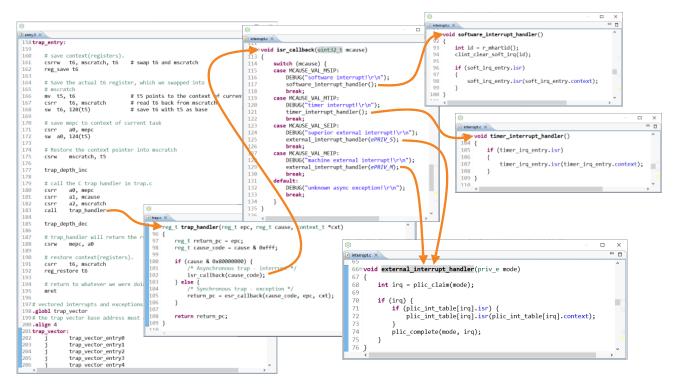

| Figure 4.28. Bare Metal Trap Handler for RISC-V MC and SM                            |    |

| Figure 4.29. Bare Metal BSP irg_callback()                                           | 46 |

| Figure 4.30. Trap Handler (Direct Mode) for Lattice Implementation of FreeRTOS       | 47 |

| Figure 4.31. C Language Portion of Trap Handler for FreeRTOS                         |    |

| Figure 4.32. Program Flow for Handling Interrupts                                    |    |

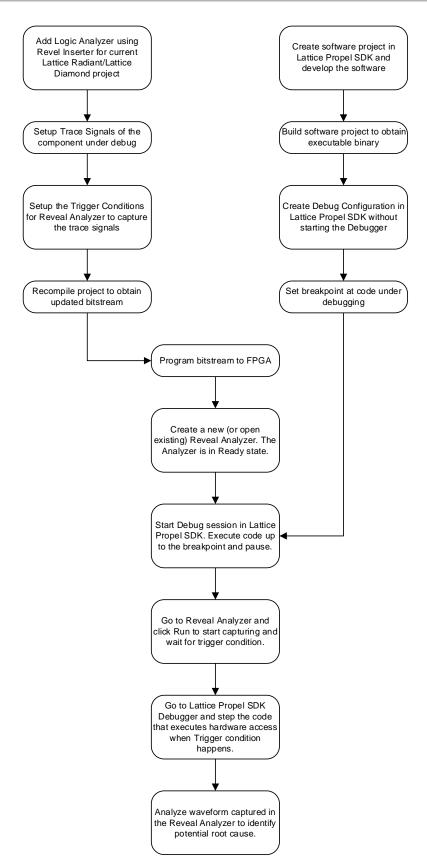

| Figure 5.1. Debugging Flow Using the OpenOCD Debugger and the Reveal Analyzer        |    |

| Figure 5.2. System Library Settings During C/C++ Project Creation                    |    |

| •                                                                                    |    |

| Figure 5.3. Enable Semihosting After Project Creation                  | 55 |

|------------------------------------------------------------------------|----|

| Figure 5.4. Changing Linker Script Heap Size                           | 56 |

| Figure 5.5. CertusPro-NX Evaluation Board UART Interface Schematic     | 57 |

|                                                                        |    |

|                                                                        |    |

|                                                                        |    |

| T. I. I                                                                |    |

| Tables                                                                 |    |

| Table 2.1. Lattice RISC-V Use Cases                                    |    |

| Table 2.2. Features Comparison of Lattice RISC-V Variants              | 8  |

| Table 3.1. RISC-V Processor Reset Vector                               | 9  |

| Table 3.2. Types of Memory Device                                      | 9  |

| Table 3.3. RISC-V Processor Caches                                     | 9  |

| Table 3.4. System Memory IP Features and Use Cases                     | 10 |

| Table 3.5. LPDDR4 SDRAM Memory Controller Parameters                   |    |

| Table 3.6. AXI4 Interconnect CDC Signals                               |    |

| Table 4.1. BSP Components and Hierarchy                                | 21 |

| Table 4.2. GNU Compiler Optimization Levels and Command Line Arguments |    |

| Table 4.3. Key RISC-V Trap Handling CSRs                               |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

|         | Definition                                   |  |  |  |

|---------|----------------------------------------------|--|--|--|

| AHB-L   | Advanced High-performance Bus-Lite           |  |  |  |

| APB     | Advanced Peripheral Bus                      |  |  |  |

| AXI     | Advanced eXtensible Interface                |  |  |  |

| BSP     | Board Support Package                        |  |  |  |

| CLINT   | Core Local Interrupter                       |  |  |  |

| DMA     | Direct Memory Access                         |  |  |  |

| EBR     | Embedded Block RAM                           |  |  |  |

| ELF     | Executable and Linkable Format               |  |  |  |

| GDB     | GNU Debugger                                 |  |  |  |

| GPIO    | General Purpose Input/Output                 |  |  |  |

| I2C     | Inter-Integrated Circuit                     |  |  |  |

| I3C     | Improved Inter-Integrated Circuit            |  |  |  |

| ISA     | Instruction Set Architecture                 |  |  |  |

| OpenOCD | Open On-Chip Debugger.                       |  |  |  |

| PLIC    | Platform Level Interrupt Controller          |  |  |  |

| RAM     | Random Access Memory                         |  |  |  |

| RISC-V  | Reduced Instruction Set Computer-V           |  |  |  |

| ROM     | Read Only Memory                             |  |  |  |

| RTOS    | Real-time Operating System                   |  |  |  |

| SDK     | Software Development Kit                     |  |  |  |

| SoC     | System-on-Chip                               |  |  |  |

| SPI     | Serial Peripheral Interface                  |  |  |  |

| SRAM    | Static Random Access Memory.                 |  |  |  |

| TCM     | Tightly Coupled Memory                       |  |  |  |

| UART    | Universal Asynchronous Receiver/Transmitter. |  |  |  |

| USB     | Universal Serial Bus                         |  |  |  |

# 1. Introduction

#### 1.1. Overview

Lattice embedded system solutions offer RISC-V processors Intellectual Property (IP), memory IP, communication IP (UART, I2C/I3C, SPI, and others), and design software such as Lattice Propel™ Builder, Lattice Propel Software Development Kit (SDK), Lattice Radiant™ software, and Lattice Diamond™ software.

The Lattice Propel Builder is a graphical design tool used to create system that comprises of various modules. These modules are IP that the Lattice Propel Builder offers or custom IP you created. Module can be easily instantiated and connected to other modules in the Lattice Propel Builder Schematic window. The Lattice Propel Builder provides address management for memory-mapped peripherals in the system. Once system building is completed, the Lattice Propel Builder generates the hardware code in RTL files and system environment XML file for building embedded software project.

The Lattice Propel SDK is a complete set of tools to create, compile, and debug embedded software project for processor systems. The Lattice Propel SDK generates the Board Support Package (BSP) for the corresponding system created in the Lattice Propel Builder. The BSP consists of processor start-up code, device drivers, and platform header file that aids application software development. The Lattice Propel SDK provides debugging tools such as OpenOCD and GNU GDB for debugging software on device.

The Lattice Radiant software and the Lattice Diamond software offer the synthesis, mapping, place-and-route, and bitstream generation capabilities. You can create FPGA bitstream using the software for the system created in the Lattice Propel Builder. FPGA pin assignment and timing constraints are performed in this stage. The software Programmer tool offers capability to program the bitstream onto FPGA devices.

The following list shows the documentations for above-mentioned software tools. Complete reading the following documents as a prerequisite to these guidelines:

- A Step-By-Step Approach to Lattice Propel

- Lattice Propel 2023.2 Builder User Guide (FPGA-UG-02196)

- Lattice Propel 2023.2 SDK User Guide (FPGA-UG-02195)

## 1.2. Purpose

This document provides guidance on designing with Lattice embedded solutions and information regarding various design options for Lattice RISC-V processors and IP. The document is organized into sections covering the entire design flow: selecting the RISC-V processor IP, hardware design, software design, and debugging.

#### 1.3. Audience

The intended audience for this document includes embedded system designers and embedded software developers using Lattice FPGA devices. The pre-requisite of this technical guidelines is the knowledge in digital design, FPGAs, and embedded systems.

# 2. Lattice RISC-V Processors Family

The Lattice Propel supports three versions of the RISC-V CPU: SM, MC, and RX. Table 2.1 shows an overview of the models and the basic use cases.

Table 2.1. Lattice RISC-V Use Cases

| Model | Class           | Supported Device Family                                        | Targeted Software Stack           | Typical Application                                                                                   |

|-------|-----------------|----------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------|

| RX    | RTOS Capable    | Lattice Avant™, Lattice Nexus™,<br>MachXO5™                    | RTOS (FreeRTOS™)     Bare metal   | Higher performance     Network connected                                                              |

|       |                 |                                                                | bare metal                        | External memory support                                                                               |

| MC    | Microcontroller | Lattice Avant, Lattice Nexus,<br>MachXO3™ (D, L, LF), MachXO2™ | Bare metal     RTOS (third party) | <ul><li>Mid-performance</li><li>Microcontroller replacement</li><li>External memory support</li></ul> |

| SM    | State Machine   | Lattice Avant, Lattice Nexus,<br>MachXO3 (D, L, LF), MachXO2   | Bare metal                        | <ul><li>Small footprint</li><li>Simple monitoring and configuration applications</li></ul>            |

The RISC-V SM is the "state machine" version and trades performance for reduced area size. This model is for simple monitoring and control tasks. With small size and area efficient AHB-Lite interconnect, this model is suitable for use in smaller device families such as MachXO2 and MachXO3.

The RISC-V MC is the "microcontroller" version. This model balances performance with area. As shown in Table 2.2, the MC model supports optional features for performance improvement, including the RISC-V 'M' extension (hardware-based integer multiply and divide) and instruction and data caches. This model also optionally supports the RISC-V 'C' extension that uses 16-bit compressed instructions to save code space. The MC model uses AHB-Lite as the native interconnect and is suitable for use in smaller device families such as MachXO2 and MachXO3.

The RISC-V RX is the highest performing model in the Lattice RISC-V family. This model is "RTOS" capable as it adds Supervisor and User modes from the Privileged Architecture portion of the RISC-V ISA. The RX model uses AXI-4 as the native interconnect for higher performance and more deterministic timing. This model also adds a Platform Level Interrupt Controller (PLIC) and a Core Local Interrupter (CLINT) for managing external interrupts and timers, respectively. A watchdog timer and optional UART are integrated into the RX IP. This IP also supports the custom instructions via the Composable Custom Extension, an emerging industry standard.

Table 2.2. Features Comparison of Lattice RISC-V Variants

| Model | Arch  | Extensions                   | System<br>Bus | Interrupt<br>Controller | System<br>Timer           | Cache                                      | Memory<br>Type(s) | Watchdog   | Privilege<br>Level(s)          | Custom<br>Instructions |

|-------|-------|------------------------------|---------------|-------------------------|---------------------------|--------------------------------------------|-------------------|------------|--------------------------------|------------------------|

| RX    | RV32I | MC<br>F (optional)           | AXI-4         | PLIC                    | CLINT                     | 2-Way Set<br>Associative<br>RR             | TCM<br>SysMem     | Integrated | Machine<br>Supervisor,<br>User | Yes                    |

| MC    | RV32I | M (optional)<br>C (optional) | AHBL          | PIC                     | Memory<br>Mapped<br>mtime | Optional<br>2-Way Set<br>Associative<br>RR | SysMem            | _          | Machine                        | No                     |

| SM    | RV32I | _                            | AHBL          | PIC                     | Memory<br>Mapped<br>mtime | No Cache                                   | SysMem            | 1          | Machine                        | No                     |

Refer to the respective IP User Guide for the latest resource and performance data for each RISC-V CPU.

# 3. RISC-V Embedded Hardware Design Guidelines

This section describes the options when designing RISC-V embedded hardware systems using the Lattice Propel Builder.

### 3.1. RISC-V Processor Reset and Exception Vector

RISC-V processor executes the memory address set by reset vector after released from reset. Table 3.1 shows the supported reset vectors for RISC-V SM, MC, and RX processors. Assign the memory that contains initial software to address matching the reset vector shown in the table.

Table 3.1. RISC-V Processor Reset Vector

| RISC-V Processor Variant | Supported Reset Vector <sup>1</sup> |

|--------------------------|-------------------------------------|

| SM                       | 0x0000_0000                         |

| MC                       | 0x0000_0000                         |

| RX                       | 0x0000_0000                         |

#### Note:

Exception vector is the memory address that contains the exception handler code. The **Machine Trap-Vector Base-Address** (mtvec) register in the RISC-V processor holds the exception vector. The vector is set by the RISC-V software driver during runtime. The driver is generated as part of the Board Support Package (BSP). Refer to the Interrupts Section for more information.

## 3.2. RISC-V Processor Memory Selection

Memory device is used to store RISC-V processor instructions and data of a software program. The types of memory devices are described in Table 3.2.

Table 3.2. Types of Memory Device

| Types of Memory Device | Example                                                | Description                                                                                                                                                                                      |  |  |

|------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Volatile memory        | Cache     Random Access Memory (RAM)                   | <ul> <li>Only retains the data while power is supplied to it. Data is lost when the memory power supply is turned off.</li> <li>Use as temporary storage and has faster access speed.</li> </ul> |  |  |

| Non-volatile memory    | <ul><li>Read Only Memory (ROM)</li><li>Flash</li></ul> | <ul> <li>Retains data even when power is turned off.</li> <li>Use for storing contents permanently and usually has slower access speed compared to volatile memory.</li> </ul>                   |  |  |

#### 3.2.1. Cache

Cache memory is a high-speed memory that integrates directly into the RISC-V processor. Cache acts as a temporary storage that processor can retrieve data faster. Table 3.3 shows the cache capabilities of the Lattice RISC-V processors.

**Table 3.3. RISC-V Processor Caches**

| RISC-V Processor<br>Variant | Instruction Cache<br>Size | Data Cache<br>Size | Option to Disable Cache | Cache Range                                                                       |  |

|-----------------------------|---------------------------|--------------------|-------------------------|-----------------------------------------------------------------------------------|--|

| SM                          | _                         | _                  | _                       | _                                                                                 |  |

| MC                          | 4 Kbytes                  | 4 Kbytes           | Yes                     | User Configurable                                                                 |  |

| RX                          | 4 Kbytes                  | 4 Kbytes           | No                      | Instruction: 0x00000000 to 0xFFFFFFFF Data: 0x00000000 to 0x0FFFFFFF <sup>1</sup> |  |

#### Note:

1. Based on Lattice Propel version 2023.2.

Based on Lattice Propel version 2023.2. Configurable reset vector is not supported.

Enabling the processor caches consumes FPGA memory resources for better CPU performance. It is recommended to enable cache for design with Lattice Avant, MachXO5-NX, CrossLink-NX, CertusPro-NX, and Certus-NX devices.

#### 3.2.2. System Memory

System memory provides easy use of Lattice FPGA memory resources (EBR, Distributed RAM, or Large RAM) as an IP available in Lattice Propel. System memory does not require connections to external devices from FPGA and can store RISC-V software and data using FPGA resources.

Table 3.4 shows the system memory IP features and use cases.

Table 3.4. System Memory IP Features and Use Cases

| Feature                                               | Use Case                                                                                                                                                                                                   |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHB-Lite interface Use as memory for RISC-V SM and MC |                                                                                                                                                                                                            |

| AXI4 interface                                        | Use as memory for RISC-V RX                                                                                                                                                                                |

| Configurable as single or dual port memory            | With dual port memory, the RISC-V Instruction port can be connected directly to one of the memory ports. The other memory port is for RISC-V data port.                                                    |

| Memory initialization enable                          | Memory is initialized with RISC-V software during FPGA configuration process. Processor executes instructions stored in memory when out of reset. Typically, use the bootloader software in this scenario. |

### 3.2.3. Tightly Coupled Memory (TCM)

Tightly Coupled Memory provides the processor low-latency predictable access for critical instruction and data. Lattice Propel provides TCM IP that can be used with RISC-V RX processor. The TCM IP supports Local Bus Interface which is connected directly to the RISC-V RX Local Instruction and Data ports. This direct connection provides the RISC-V RX low latency and predictable access to the memory. TCM uses FPGA memory resources like the system memory.

When using TCM, the first 128 Kbytes of processor address range (0x00000000 to 0x0001FFFF) is reserved for it. If system memory (or other types of memory) is used for the processor non-TCM instruction port (for example the AXI port), this memory must start from address 0x00020000.

#### 3.2.4. External SDRAM Memory

External SDRAM memory can be used in applications that require larger memory size. Large program and data can be stored and accessed on the external memory with increased latency. SDRAM memory requires a controller for refreshing the memory and handling memory accesses (such as switching between memory banks, rows, and columns).

Lattice Propel offers SDRAM memory controllers for CertusPro-NX and Avant devices. Both memory controllers support LPDDR4 SDRAM. The memory controller supports AXI4 interface for interfacing to the processor.

Table 3.5 shows the memory controller parameters that you can customize for RISC-V applications.

**Table 3.5. LPDDR4 SDRAM Memory Controller Parameters**

| Parameter                    | Description                                                                                                                                                                                       |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDR Command Frequency (MHz)  | Change the frequency to the desired value that matches your design. The maximum frequency is 800 MHz for Lattice Avant devices and 533 MHz for CertusPro-NX devices.                              |

| DDR Density                  | Change the density (in terms of Gb) per channel to match the SDRAM chip. This change affects the address bus width of the controller AXI4 interface.                                              |

| DDR Bus Width                | Change the bus width for DDR data bus to match the DRAM chip. This change affects the DQ, DQS, and DMI bus width, and requires update to FPGA pin assignments.                                    |

| Data Width on Local Data Bus | Change the data bus width (range from 32-bit to 256-bit) of the AXI4 interface. RISC-V processor has 32-bit data bus. To avoid width adaptation, set this parameter to match the processor width. |

#### 3.2.5. Flash Memory

Flash memory is a non-volatile memory that can store permanent data. Most embedded applications require flash memory to store the processor program (such as Bootloader) and data (such as media file and configuration file). Flash memory accesses are different from volatile memory (such as system memory or SDRAM). Writing data to the flash memory requires erasing the corresponding page before the write occurs. Flash memory controller is required for RISC-V processors to access the memory.

Lattice Propel offers SPI Flash Controller IP to provide interface from RISC-V processor to a SPI based flash device. This IP supports single-bit serial data interface to the flash device. The IP provides AHB-Lite based interface for data access and APB interface for control (registers) access. When connecting the RISC-V RX processor to the AHB-Lite port, a converter bridge is required.

The input delay of the MISO signal (read data from SPI Flash) requires proper timing constrains for the controller to capture the correct data. Use the timing constraint set\_input\_delay to define the delay contributed by the flash device (refer to flash vendor datasheet) and board traces. Refer to the following examples of input delay constraints for MISO:

- set input delay -clock [get clocks spi flash0 inst spi clk] -max 8 [get ports miso i]

- set\_input\_delay -clock [get\_clocks spi\_flash0\_inst\_spi\_clk] -min 7 [get\_ports miso\_i]

## 3.3. Interconnects and Bridges

Interconnects connect multiple managers to multiple subordinates in a system. Examples of managers include RISC-V instruction port, RISC-V data ports, and DMA. Subordinates include peripherals such as UART, SPI, and I2C controllers. Interconnect provides several functions to the system including the following:

- Decode the managers transaction address and route to the correct subordinate.

- Arbitrate concurrent transactions from multiple managers to a specific subordinate.

- Convert different data widths between managers and subordinates.

Lattice Propel provides Interconnect solutions that are in compliance with Arm Advanced Microcontroller Bus Architecture (AMBA) including AXI-4, AXI-4 Lite, AHB-Lite, and APB protocols. Select the appropriate Interconnect IP for your project. The following sub-sections describe each Interconnect solution in detail.

Bridges connect interfaces of different AMBA protocols, for example connecting an AXI-4 manager to an APB subordinate. The Bridges IP ease system building where you can use the manager or subordinate IP without changing the AMBA interface.

#### 3.3.1. Using AXI4 Interconnect IP

The AXI4 Interconnect IP connects multiple AXI4 based managers to AXI4 subordinates. This interconnect is useful for Lattice RISC-V RX processor-based system as both the instruction and data ports are AXI4 interfaces. The AXI4 Interconnect supports both AXI4 and AXI4-Lite protocols. The protocol type can be configured for individual manager and subordinate.

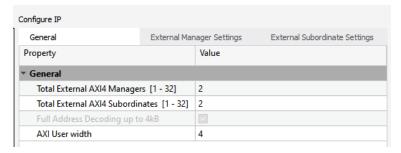

The AXI4 Interconnect IP is fully parameterizable for your application. Figure 3.1, Figure 3.2, and Figure 3.3 show the IP Wizard for the configurable parameters. The subsequent subsections discuss the guideline when configuring the AXI4 Interconnect IP.

Figure 3.1. AXI4 Interconnect IP Parameters - General Tab

| Configure IP                             |                                               |                 |                               |  |

|------------------------------------------|-----------------------------------------------|-----------------|-------------------------------|--|

| General                                  | External Manager Settings                     |                 | External Subordinate Settings |  |

| Property                                 |                                               | Value           |                               |  |

| ▼ General                                |                                               |                 |                               |  |

| External Manager AXI ID width            |                                               | 1               | 1                             |  |

| AXI Manager Max Address Width(bits)      |                                               | 32              |                               |  |

| AXI Manager Max Data Width(bits)         |                                               | 32              |                               |  |

| AXI Manager Max no.of ID supports        |                                               | 16              |                               |  |

| ▼ External Manager Access Typ            | e Settings                                    |                 |                               |  |

| INFO: Ext Manager Access type list       |                                               | {2'd2,2'd2}     | {2'd2,2'd2}                   |  |

| External Manager AXI Access Type 0       |                                               | WR              | WR                            |  |

| External Manager AXI Access Type 1       |                                               | WR              | WR                            |  |

| ▼ External Manager Protocol Se           | ettings                                       |                 |                               |  |

| INFO: Ext Manager Protocol               | type list                                     | {1'd0,1'd0}     | {1'd0,1'd0}                   |  |

| External Manager AXI protoc              | ol 0                                          | AXI4            |                               |  |

| External Manager AXI protoc              | ol 1                                          | AXI4            |                               |  |

| ▼ External Manager CDC Enable            | e Settings                                    |                 |                               |  |

| INFO: Ext Manager CDC Enal               | INFO: Ext Manager CDC Enable list {1'd0,1'd0} |                 |                               |  |

| External Manager CDC Enable 0            |                                               |                 |                               |  |

| External Manager CDC Enable 1            |                                               |                 |                               |  |

| ▼ External Manager Address So            | ettings                                       |                 |                               |  |

| INFO: Ext Manager actual ad              | dress list                                    | {7'd32,7'd32}   |                               |  |

| External Manager Address wi              | idth 0                                        | 32              |                               |  |

| External Manager Address wi              | idth 1                                        | 32              |                               |  |

| ▼ External Manager Data Settir           | ngs                                           |                 |                               |  |

| INFO: Ext Manager actual Data width list |                                               | {11'd32,11'd32} |                               |  |

| External Manager Data width 0            |                                               | 32              |                               |  |

| External Manager Data width 1            |                                               | 32              |                               |  |

| ▼ External Manager No.of IDs s           | supports Settings                             |                 |                               |  |

| INFO: Ext Manager ID supports list       |                                               | {7'd16,7'd16}   |                               |  |

| External Manager No.of IDs 0             |                                               | 16              |                               |  |

| External Manager No.of IDs 1             |                                               | 16              |                               |  |

Figure 3.2. AXI4 Interconnect IP Parameters – External Manager Settings Tab

Figure 3.3. AXI4 Interconnect IP Parameters – External Subordinate Settings Tab

#### 3.3.1.1. Total External Managers and Subordinates

The AXI4 Interconnect is configured based on the total number of external managers and subordinates in the system.

The **Total External AXI4 Managers** parameter is set to match with total Managers in the system. For example, RISC-V RX has 2 managers (instruction and data). If other Managers (such as DMA) is connected to the AXI4 Interconnect, increase this number accordingly.

The **Total External AXI4 Subordinates** parameter is set to match with total Subordinates in the system that need to connect with the Managers.

Total managers and total subordinates cannot have the values of 1 because one manager and one subordinate can be connected directly without an interconnect.

#### 3.3.1.2. AXI Address and Data

The AXI4 Interconnect supports configurable address and data widths to match with all external managers and the connected subordinates. Set the maximum allowable address and data width on both the manager and subordinate using the following parameters:

- AXI Manager Max Address Width

- AXI Manager Max Data Width

- AXI Subordinate Max Address Width

- AXI Subordinate Max Data width

For each external manager interface, set the actual **External Manager Address Width** and **Data Width** parameters to match with the manager properties. Similar approach applies when setting the **External Subordinate Address Width** and **Data**

**Width** parameters. For example, the RISC-V RX processor address width is 32 bit and data width is 32 bit. The width value should not exceed the values set in the maximum allowable parameters.

When the manager and subordinate data widths are not equal, the AXI4 Interconnect inserts width converter to handle the differences. For example, when connecting the RISC-V RX processor (data width is 32 bit) to LPDDR4 memory controller subordinate (data width is 256 bit), the interconnect applies width conversion. Note that width converter increases the logic utilization and may impact the timing performance of the achievable Fmax. For optimizing the interconnect usage, configure the managers and subordinates to the same width when possible.

#### 3.3.1.3. AXI USER

AXI User signal is for user-defined purposes. The AXI4 Interconnect IP supports configurable **AXI User Width** parameter that applies to all manager and subordinate interfaces in the IP. Set the AXI User signal (AxUSER, xUSER, and BUSER) width to match the application.

For AXI4 manager to AXI4-Lite subordinate, the AXI4 Interconnect IP ignores the AXI User signals when routing the transactions.

For AXI4 manager to AXI4 subordinate, the AXI4 Interconnect IP passes through the AXI User signals without changing the signals.

#### 3.3.1.4. AXI ID

The AXI ID signals are used for transaction identification and ordering. The AXI4 Interconnect supports configurable AXI ID Width for external managers and subordinates. The **External Manager AXI ID Width** and **External Subordinate AXI ID Width** parameters set the ID widths to match the following equation:

Subordinate ID width  $\geq$  Manager ID width  $+ \log 2$  (number of managers)

For example, on system with RISC-V RX processor where RISC- RX manager ID width = 1 and number of managers = 2, the subordinate ID width is set to 2 using the equation as follows:

Subordinate ID width = Manager ID width +

$$log2$$

(number of managers)

= 1 +  $log2$  (2)

= 2

The AXI Interconnect external subordinate ID width must set to match with the actual subordinate. For example, if the Interconnect ID width is 2, the subordinate on system memory IP must match. If the subordinate ID width does not match, the extra bits on ID signal are left undriven and may lead to unpredictable behavior.

The **AXI Manager Max no of ID Supports** parameter sets maximum allowable number of ID for external managers arriving at the Interconnect. The **External Manager No of ID** parameter is set for each manager interface to change the interconnect reordering depth for transactions ID tracking. The value set for this parameter should not be larger than the maximum allowable number of ID parameter.

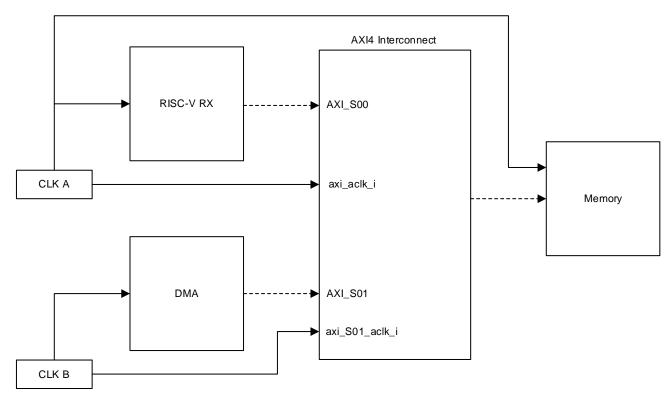

#### 3.3.1.5. Clock Domain Crossing

The AXI4 Interconnect operates at single clock domain which is driven by the **axi\_aclk\_i** clock input signal. For system with single clock domain, the axi\_aclk\_i is connected to the same clock as with the rest of the system.

However, some external managers or subordinates operate at different clock than the axi\_aclk\_i. The AXI4 Interconnect supports clock domain crossing that can be enabled on individual manager or subordinate interface. The **External Manager CDC Enable** and **External Subordinate CDC Enable** parameters is enabled according to the system clock crossing setup.

Figure 3.4 shows RISC-V RX, AXI4 Interconnect, and Memory operate in CLK A domain while DMA operates in CLK B domain. DMA is connected to the AXI Interconnect where the DMA accesses to the memory that operates in CLK A domain.

Figure 3.4. Example System with Different Clock Domains

DMA is connected to AXI\_S01 port of the AXI4 Interconnect. To turn on clock domain crossing for this port, enable the **External Manager CDC Enable 1** parameter. Additional clock and reset signals listed in Table 3.6 are exported when the CDC feature is enabled.

**Table 3.6. AXI4 Interconnect CDC Signals**

| CDC Signal        | Description                                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| axi_S01_aclk_i    | Clock input for AXI_S01 port. Connect this to the clock that external manager uses (CLK B).                                                                                            |

| axi_S01_aclken_i  | Clock enable input (active low) for AXI_S01 port. Connect to the clock source enable signal. For example, if the clock is from PLL, connect the PLL Lock output signal to this signal. |

| axi_S01_aresetn_i | Reset input (active low) for AXI_S01 port. This reset signal is de-asserted synchronously to axi_S01_aclk_i.                                                                           |

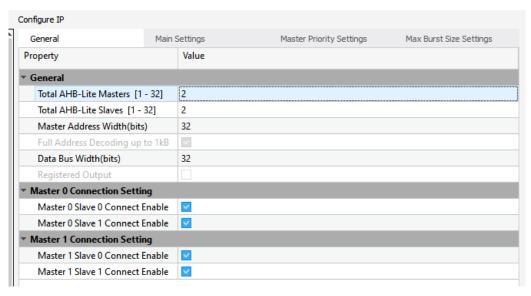

### 3.3.2. Using AHB-Lite Interconnect IP

The AHB-Lite Interconnect IP connects multiple AHB-Lite based managers to AHB-Lite subordinates. This Interconnect is useful for Lattice RISC-V MC and RISC-V SM processor-based systems as both the instruction and data ports are AHB-Lite interfaces.

The AHB-Lite Interconnect IP is fully parameterizable for your applications. Figure 3.5 shows the IP Wizard with the configurable parameters. The subsequent subsections discuss the guideline when configuring the AXI4-Lite Interconnect IP.

Figure 3.5. AHB-Lite Interconnect IP Parameters - General Tab

#### 3.3.2.1. General Settings

The **Total AHB-Lite Managers** and **Total AHB-Lite Subordinates** parameters set the numbers of managers/subordinates that are connected to the interconnect. The RISC-V MC or SM processor has 2 AHB-Lite manager ports (Instruction and Data). Only the Data port requires connection to multiple subordinates (peripherals). The Instruction port is usually connected directly to memory that stores the program. When the Instruction port require access to a shared memory, increase the value for **Total AHB-Lite Managers** and connect the Instruction port to the AHB-Lite interconnect that grants access to the shared memory.

When the AHB-Lite Interconnect is configured with multiple managers and subordinates, all connections between managers and subordinates are enabled by default. In the example showed in Figure 3.5, 2 managers and 2 subordinates results in 4 interconnection logics. If one of the managers does not require access to a specific subordinate, the **Connect Enable** checkbox can be disabled. For example, if Manager 0 does not access Subordinate 1, uncheck **Manager 0 Subordinate 1**Connect Enable to reduce the logic generated for the Interconnect and improve overall Fmax.

#### 3.3.2.2. Main Settings

The **Main Settings** tab lists the default base address and range for each subordinate that is enabled on the AHB-Lite Interconnect. The actual addresses are not set via parameters in this setting tab.

When creating RISC-V system with the Lattice Propel Builder, each subordinate base address and range are set up in the **Address** tab of the Lattice Propel Builder GUI. This address information is then propagated to the AHB-Lite Interconnect IP during system generation in the Lattice Propel Builder. The generated system (RTL code) parameterizes the AHB-Lite Interconnect IP with the addresses from the Lattice Propel GUI during IP instantiation.

#### 3.3.2.3. Master Priority Settings

The **Master Priority Settings** tab allows selection of the AHB-Lite subordinates arbitration scheme. Select **either Round Robin** or **Fixed Priority** scheme to match the application requirements.

#### 3.3.2.4. Max Burst Size Settings

The **Max Burst Size Settings** tab allows selection of the maximum burst size for each AHB-Lite subordinates in the interconnect. If the manager performs burst transaction on one subordinate and the transaction exceeds the said maximum burst size setting, the interconnect sends an error response to the manager. This prevents a manager from hogging the bus by generating very long bursts.

17

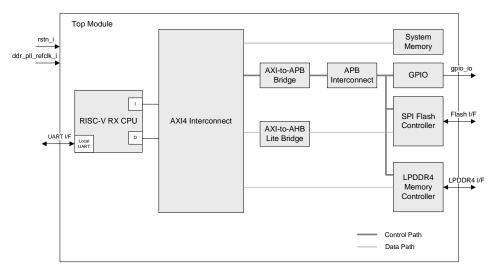

#### 3.3.3. Using APB Interconnect IP

The APB interface is commonly used for low bandwidth bus interface such as peripherals access. In a typical embedded system, the processor interfaces to multiple peripherals such as I2C controller, UART, and GPIO. These peripherals do not require high performance bus and typically uses the APB interface.

RISC-V RX has AXI4 interface and RISC-V SM or MC has AHB-Lite interface. The processors use conversion bridges such as AXI4-to-APB bridge to connect the processor interface to the APB-based peripherals. These bridges operate on per interface basis where a bridge is required for each peripheral. APB Interconnect allows a single manager to connect to multiple subordinates, eliminating the need for individual bridge.

Figure 3.6 shows the RISC-V RX data port accessing to GPIO, SPI flash controller, and LPDDR4 memory controller. All these peripherals have APB based subordinate interface. A single AXI-to-APB bridge converts the AXI interface from the AXI4 Interconnect to APB interface. Subsequently, the APB Interconnect connects the interface to multiple peripherals.

Figure 3.6. System with APB Interconnect for Peripherals Access

#### 3.3.4. Using Bridges IP

Bridges connect different types of AMBA interfaces in the Lattice Propel system. The following bridges are available in the Lattice Propel Builder:

- AXI4-to-AHB-Lite bridge

- AXI4-to-APB bridge

- AHB-Lite-to-APB bridge

#### 3.3.4.1. AXI4-to-AHB-Lite Bridge

This bridge connects RISC-V RX AXI4 interface to any AHB-Lite subordinate interface. As the RISC-V processor has 32-bit data width, the **AXI\_AHB Data Bus Width** parameter is set to 32.

The **AXI ID Width** parameter is set to the value that matches the upstream manager. For example, if the upstream manager is an AXI4 Interconnect with ID Width of 2, the bridge value is set to 2.

The AXI User Width parameter defines the AXI USER signal width and is set to a value that matches the upstream manager.

The AXI4-to-AHB-Lite bridge does not support clock domain crossing where the AXI4 and AHB-Lite interfaces operate at different clock domains. However, if AXI4 Interconnect is used as the upstream, you can enable clock domain crossing in the AXI4 Interconnect. Refer to the Using AXI4 Interconnect IP section for details.

#### 3.3.4.2. AXI4-to-APB Bridge

This bridge connects RISC-V RX AXI4 interface to any APB subordinate interface. As the RISC-V processor has 32-bit data width, the **AXI\_APB Data Bus Width** parameter is set to 32.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

The **AXI ID Width** parameter is set to the value that matches the upstream manager. For example, if the upstream manager is an AXI4 Interconnect with ID Width of 2, the bridge value is set to 2.

The AXI User Width parameter defines the AXI USER signal width and is set to a value that matches the upstream manager.

The AXI4-to-APB bridge does not support clock domain crossing where the AXI4 and APB interfaces operate at different clock domains. However, if AXI4 Interconnect is used as the upstream, you can enable clock domain crossing in the AXI4 Interconnect. Refer to the Using AXI4 Interconnect IP section for details.

#### 3.3.4.3. AHB-Lite-to-APB Bridge

This bridge connects RISC-V SM or MC AHB-Lite interface to any APB subordinate interface. Configure the bridge **Address Width** and **Data Bus Width** parameters to 32-bit when interfacing with RISC-V processors.

The bridge supports a separate APB clock domain from the AHB-Lite clock domain. This allows the slower peripherals to be decoupled from the system clock domain and may make it easier to reach timing objectives. Check the **APB Clock Enable** parameter to enable separate clock and reset signals for APB domain, namely pclk\_i and presetn\_i.

#### 3.3.5. Using Feedthrough IP

The Feedthrough IP allows you to export the specific AMBA bus out from the Lattice Propel Builder system to the higher-level module. This is useful when connecting IP that is not available in the Lattice Propel Builder. For example, you can connect the exported bus to an IP in the Lattice Radiant project. The Lattice Propel Builder offers AHB-Lite Feedthrough and APB Feedthrough IP that export the AHB-Lite and APB bus respectively.

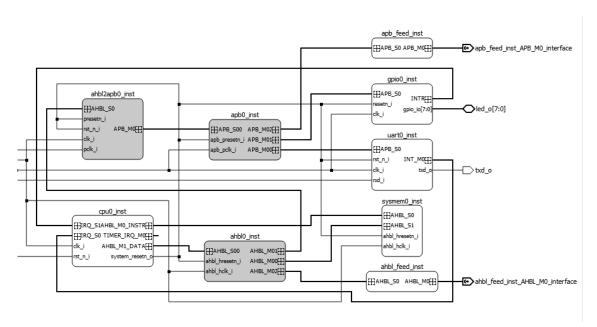

Figure 3.7 shows the Lattice Propel Builder system with the feedthrough IP. The AHB-Lite feedthrough (ahbl\_feed\_inst) is connected from the AHB-Lite Interconnect for the processor to access to external IP. Similarly, the APB feedthrough (apb\_feed\_inst) is connected to APB Interconnect located at the top right of Figure 3.7.

Figure 3.7. Lattice Propel Builder System with Feedthrough IP

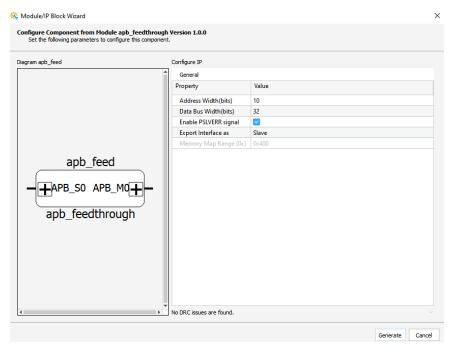

When connecting to the external subordinate, set **Export Interface As** to **Slave** in the Bridge Module/IP Block Wizard as shown in Figure 3.8.

Figure 3.8. APB Feedthrough Module/IP Block Wizard

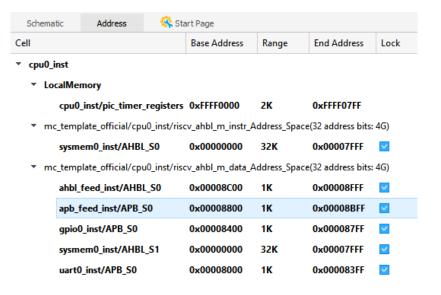

To create a memory-mapped address space for the feedthrough block, click **Generate** in the Bridge Module/IP Block Wizard in Figure 3.8. When interface to RISC-V processor, the software code accesses the block via the assigned address. Figure 3.9 shows the address space for the APB feedthrough in the **Address** tab in the Lattice Propel Builder.

Figure 3.9. Address Map of Feedthrough IP

## 3.4. Assigning Address Map

The Lattice Propel Builder supports assigning addresses to all memory-mapped peripherals in the embedded system. The address map is managed via the **Address** tab in the Lattice Propel Builder. The **Auto Assign** feature in the Lattice Propel Builder allows the tool to automatically assign non-overlapping addresses to all peripherals. However, there are situations where manual address assignments are required.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

Peripherals addresses must not be assigned to the processor cacheable range, so that the processor reads the peripheral registers value from the actual register value and not from the cache.

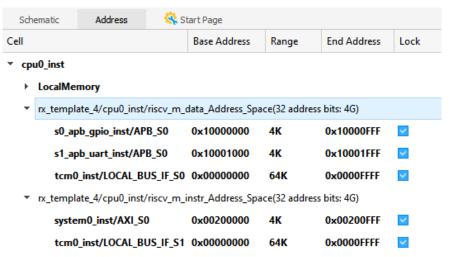

For RISC-V RX processor, the cache range is from address 0x0000\_0000 to 0x0FFF\_FFFF<sup>(1)</sup>. For peripherals that do not need caching, do not assign the addresses into this address range. Figure 3.10 shows the address map for GPIO and UART peripherals that are assigned to non-cacheable range of the RISC-V RX processor that starts from address 0x1000\_0000.

When the addresses are assigned correctly, check the **Lock** option to avoid unnecessary changes by you or the Auto Assign feature.

Figure 3.10. Address Map for Peripherals

When ICACHE and DCACHE features are turned on for RISC-V MC processor, the address assignment method must be applied for peripherals that do not need to be cached. The cacheable range is configured in the RISC-V MC IP Wizard via **DCACHE\_RANGE\_LOW** and **DCACHE\_RANGE\_HIGH** parameters.

#### Note:

1. Based on Lattice Propel 2023.2 and RISC-V RX 2.3.0. Refer to the RISC-V RX CPU IP Core User Guide (FPGA-IPUG-02241) for more information.

# 4. RISC-V Embedded Software Design Guidelines

This section describes the options when designing RISC-V embedded software systems using the Lattice Propel Software Development Kit (SDK).

# 4.1. Software Project Support

RISC-V SM, MC, and RX processors support bare metal software applications. The Board Support Package (BSP) provides drivers for processor startup initialization and accessing the IP in the system. When creating a new Lattice C/C++ Project in the Lattice Propel SDK, select **Hello World Project** for bare metal based applications.

The Lattice Propel SDK supports creating FreeRTOS based projects. FreeRTOS is available only when using the RISC-V RX processor. When creating a new Lattice C/C++ Project in the Lattice Propel SDK, select the **FreeRTOS Project**. For more information, refer to the **FreeRTOS** web page.

# 4.2. Board Support Package (BSP)

The Board Support Package (BSP) is generated when creating a Lattice C/C++ Project in the Lattice Propel SDK. The BSP provides the following:

- RISC-V processor start-up code and drivers for interrupt, exception, timer, cache, and watchdog

- Device drivers for IP in the system

- · Platform header file that defines memory-mapped addresses, IP parameters, and C Macro

Table 4.1 lists the BSP components and the corresponding file hierarchy in the Lattice Propel SDK project.

Table 4.1. BSP Components and Hierarchy

| Component                | Hierarchy                                                             |  |

|--------------------------|-----------------------------------------------------------------------|--|

| RISC-V processor drivers | For RISC-V RX: <project name="">/src/bsp/driver/riscv_rtos/</project> |  |

|                          | For RISC-V MC: <project name="">/src/bsp/driver/riscv_mc/</project>   |  |

|                          | For RISC-V SM: <project name="">/src/bsp/driver/riscv_sm/</project>   |  |

| Device drivers           | ivers <project name="">/src/bsp/<device name=""></device></project>   |  |

|                          | Example: <project name="">/src/bsp/driver/gpio/</project>             |  |

| Platform header file     | <project name="">/src/bsp/sys_platform.h</project>                    |  |

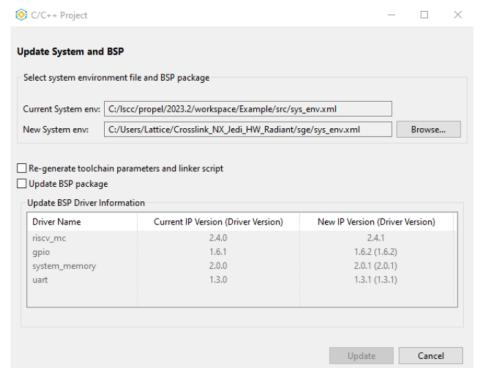

#### 4.2.1. Updating BSP

Update BSP when changes are made in the Lattice Propel Builder. This includes adding, removing, or upgrading IP, changing IP parameters, and changing the memory-mapped addresses. To update BSP, follow these steps:

- 1. Click **Design > Generate** in the Lattice Propel Builder to generate the latest system.

- 2. In the Lattice Propel SDK, under **Project Explorer** view, select the C/C++ project to update.

- 3. Click Project > Update Lattice C/C++ Project....

The **Update System and BSP** wizard opens as shown in Figure 4.1.

Figure 4.1. Update System and BSP Wizard

- 4. If your Lattice Propel Builder project has a different path as **Current System env**, click **Browse** to the latest Lattice Propel Builder project **sge/** directory and select the **sys env.xml** file.

- 5. If you change the processor system memory, check **Re-generate toolchain parameters and linker script**. For example, if you change the processor connection to the program memory, update the connection in the linker script. Do not check this option if there is no change to maintain the current linker script.

- 6. Check **Update BSP package** to update the device drivers. The wizard shows the new driver version (when available) that for the updated BSP.

- 7. Click **Update** to make changes.

# 4.3. Software Compiler Optimization Options

Compiler optimization is a tool to improve performance and reduce code size with any modern CPU. Optimization is particularly important when dealing with Reduced Instruction Set Computer (RISC) architectures. RISC architectures such as RISC-V implicitly assume that the compiler solves structural issues that other architectures handle at the hardware level. Furthermore, well optimized code can make efficient use of the deep register files associated with RISC architectures, minimizing potentially costly accesses to main memory.

Optimization can significantly reduce instruction count, decrease memory footprint, and increase performance.

During the development phase, optimization may be counterproductive. Aggressive optimization increases compile times and slows down development. Optimization may also remove or reorder instructions, complicating debugging. For example, when single stepping through optimized code, execution may not be consistent with the high-level source (even though the code logically produces the correct result).

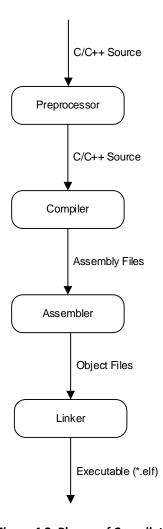

### 4.3.1. C/C++ Compiler Flow

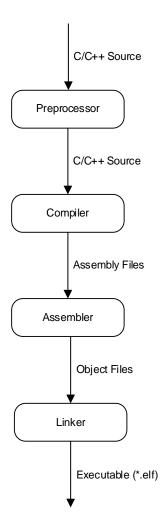

The conventional process of compiling C/C++ source code into an executable binary image consists of four phases, as shown in Figure 4.2:

- 1. Preprocessing

- 2. Compilation

- 3. Assembly

- 4. Linking

Figure 4.2. Phases of Compilation

Linking is the only phase that has a complete view of the entire program. Global optimizations across the whole program can only be performed by the linker.

Most optimizations are local optimizations performed by the compiler. Optimizations are performed on each source code module, one at a time.

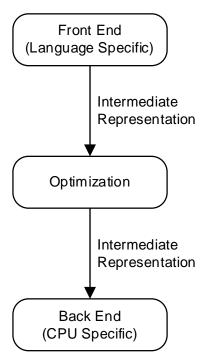

#### 4.3.2. Compiler Architecture

Compiling refers to converting high-level source into binary machine code. However, as shown in the C/C++ Compiler Flow section, the compiler performs only one part of the overall process.

The Lattice Propel SDK uses the GNU toolchain to build application images. The GNU compiler has three stages as shown in Figure 4.3.

Figure 4.3. Generalized Compiler Architecture

The first stage which is the front end, is specific to a high-level language. The front end parses and analyzes high-level source code and converts the source code into a language independent intermediate representation that is passed to the next stage.

The second stage optimizes the intermediate representation that was produced by the front end. The nature of the optimization (for example performance versus code size) and the degree of effort are controlled by command line arguments to the compiler. When the second stage has completed optimization, a new, language independent, intermediate representation is passed to the final stage which is the back end.

A back end is specific to a CPU architecture. The primary function is to convert the intermediate representation produced by the optimization phase into instructions that can execute on the target hardware. The output of the back end is assembly code that can be passed to the assembler, the next stage after the compiler in the build flow.

With this modular compiler architecture, the same optimization engine and target specific back end can support multiple high-level languages by using a different, language specific front end. Similarly, the same front-end and optimization engine can generate code for different variants of the same CPU architecture (for example 32-bit versus 64-bit) and different architectures (for example ARM versus RISC-V).

The front and back ends do little to optimize the code. If the compiler is invoked with optimization disabled, the output is a literal translation of the input source into assembly code. The output code has no logical reductions in instruction count and is not optimized for architectural features of the target CPU.

#### 4.3.3. Optimization Levels

The GNU compiler supports many optimization algorithms. For a complete list of these algorithms, refer to the GCC, the GNU Compiler Collection web page. Most optimizations reduce the number of instructions in the compiled code which increases performance and reduces the program size in memory. However, some optimization algorithms increase code space to enhance performance or vice-versa.

Some optimization routines are iterative and can significantly increase compilation time.

The GNU compiler allows individual optimization algorithms to be invoked at the command line. The compiler also groups commonly used algorithms into different levels based on the desired tradeoffs. The levels and the corresponding command line arguments are shown in Table 4.2.

**Table 4.2. GNU Compiler Optimization Levels and Command Line Arguments**

| gcc Command Line Argument | Description                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------------------------------|

| -00                       | Disables optimization                                                                                          |

| -01                       | Runs optimizations that increase performance without increasing memory size and compilation time               |

| -02                       | Runs optimizations in -O1 and optimizations that increase compilation time                                     |

| -03                       | Runs optimizations in -O2 and adds optimizations that sacrifice code space for improved performance            |

| -Ofast                    | Runs optimizations in -O3 and adds several optimizations that are not valid for C/C++ standards compliant code |

| -Os                       | Runs optimizations that reduce program size without impacting the performance                                  |

| -Og                       | Runs subset of optimizations that do not alter execution order that is useful for debugging                    |

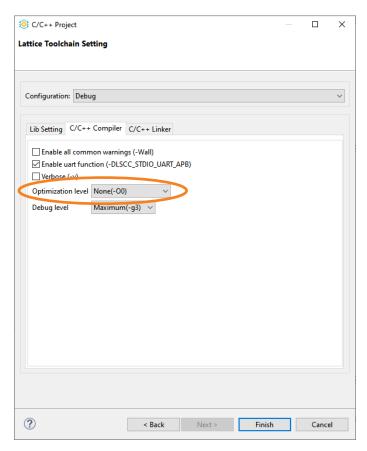

#### 4.3.4. C/C++ Compiler Optimization in the Lattice Propel Software

The Lattice Propel SDK invokes the GNU compiler to build applications. You can control the arguments that the Lattice Propel software sends to the compiler, including optimization level, via the GUI settings.

You can change the optimization level using the GUI in several ways. During project creation, you can change the optimization level in the C/C++ Compiler tab in the Lattice Toolchain Setting window, as shown in Figure 4.4.

Figure 4.4. Optimization Setting during Project Creation

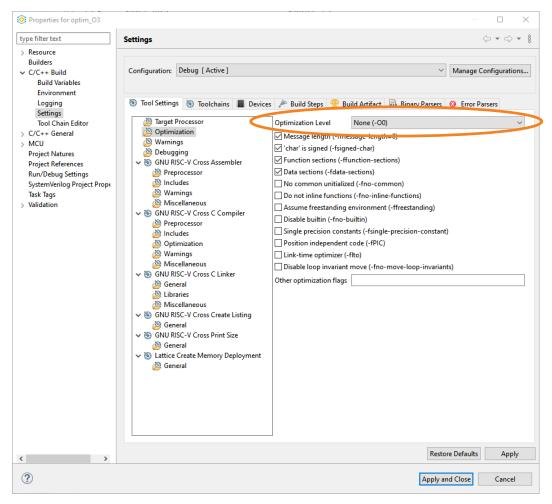

You can also change the optimization level after project creation in the Project Properties menu as shown in Figure 4.5.

Figure 4.5. Changing Optimization Level from the Lattice Propel SDK Project Settings

The default Optimization Level is -00 which turns off optimization. During the initial stages of a project, it is recommended to turn off optimization so that compile times remain short and instruction ordering matches that of the source code. For most applications, enable optimizations in the design cycle prior to the creation of a release candidate.

#### 4.3.5. Fine Grain Control of Optimization

You can apply different levels of optimization to different parts of an embedded program using the GNU C/C++ compiler. As shown in Figure 4.6, the #pragma GCC optimize command optimizes all subsequent code at the optimization level specified in the argument in double quotes.

```

®

×

c power.c ×

1

2

#pragma GCC optimize("03")

3

4

5⊖ int power(unsigned int x, unsigned int n)

6

unsigned prod = 1;

7

8

unsigned int i;

9

for (i=0; ikn; i=i+1)

10

prod = prod * x;

11

12

13

return prod

14

15

```

Figure 4.6. Using the #pragma Directive to Control Optimization Level

You can also apply optimization at the granularity of functions using the \_\_attribute\_\_ in the GNU compiler. Different attributes can apply useful properties to functions, variables, type definitions, and optimization level. Figure 4.7 demonstrates the syntax for applying level 3 optimization to a function. The \_\_attribute\_\_ keyword applies only to the specified function.

```

0

X

c *power.c ×

1

3

((optimize ("03"))) int power(unsigned int x, unsigned int n)

6

7

unsigned prod = 1;

8

unsigned int i;

9

10

for (i=0; i<n; i=i+1)

11

prod = prod * x;

12

13

return prod;

14

}

15

```

Figure 4.7. Applying an Optimize Attribute to a Function

#### 4.3.6. Linker Relaxation

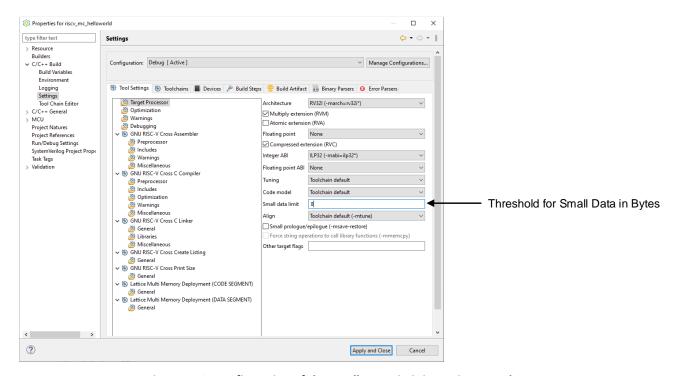

Some optimizations can only be applied globally. For RISC-V architecture, because of the design of the jump, load, and store instructions, linker relaxation optimization can only be performed once the whole program has been assembled and the locations of code and data are known.

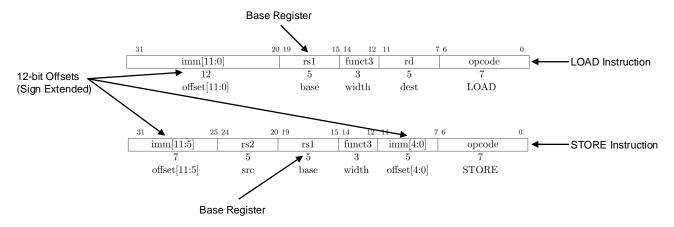

The width of RISC-V instructions is equal to or less than the width of the address bus (32 bits). A RISC-V instruction cannot contain an immediate value that spans across the entire addressable memory space. Instead, RISC-V instructions compute a target address by adding a smaller immediate offset to a value contained in a register.

Loads and stores add a twelve-bit immediate field in the instruction to the contents of a register in the CPU register file. Jump instructions compute the target address by adding an immediate offset to either a register in the register file or to the Program Counter.

If the target address of a jump or a memory access is unknown at the time the instructions are emitted by the compiler, the compiler assumes the target address is outside the range of the offset provided by the immediate field. To cover the full range of potential target addresses, the compiler includes an instruction to load the higher order address bits of the target address into a register.

Because of code locality, the extra instruction is typically not necessary for most load, store, and jump instructions. However, it can only be determined at the linking stage whether a given operation requires a register to be loaded with the high order bits of its target address.

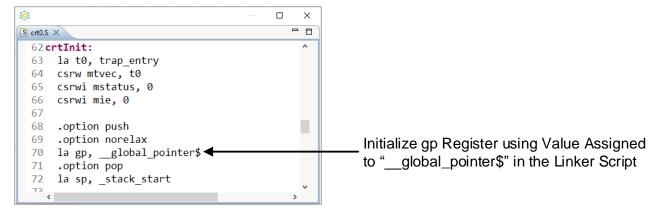

During linker relaxation, the linker scans the program as a whole and determines whether the target address of an operation is within the range of the immediate field from a register that holds a known value. The register for jump instructions can be the Program Counter. For load and store instructions, the register is in the register file and is designated as the Global Pointer. The Global Pointer is loaded during startup with an address that is near the location of most variables in memory.

If the linker detects that an operation can reach the target address without loading a new register value, the linker removes the extra register load instruction added by the compiler. This cuts in half, the number of instructions required for loads, stores and jumps. Linker relaxation results in significant gains in terms of both code size and performance.

Linker relaxation is enabled by default.

#### 4.3.7. Link Time Optimization

Link time optimization is an option provided by the GNU C/C++ compiler and is a global optimization. This optimization forwards extra information to the linker and causes the linker to run optimization on the program.

Link time optimization may marginally improve performance. Link time optimization may increase code size.

Refer to the GNU GCC documentation for additional information.

Link time optimization is disabled by default.

# 4.4. Linker Script

Linking is the final step in translating a set of source files and libraries into an executable binary. Prior stages in the build process, which are the pre-processor, compiler, and assembler, produce a set of object files that the linker combines to form the complete program. Figure 4.8 shows the phases of compilation.

Figure 4.8. Phases of Compilation

You can control the GNU linker utility, Id, via command line arguments. For simple, natively compiled applications, the default settings are sufficient. More complex embedded applications require more control over the linking process. Control via command line becomes cumbersome and it is common practice to place linker arguments into a linker script file.

#### 4.4.1. Linker Scripts in the Lattice Propel SDK

The Lattice Propel SDK automatically generates a linker script during the Lattice C/C++ Project creation. The autogenerated script is based on the memory configuration of the Lattice Propel Builder SoC design. This default script is suitable for simple designs. For more complex designs, add customizations to the default script.

The Lattice Propel SDK supports the following modifications to a linker script:

- GUI based linker script configuration

- Text based editing

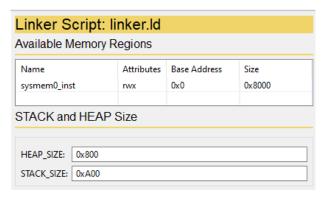

#### 4.4.1.1. GUI Based Linker Script Configuration

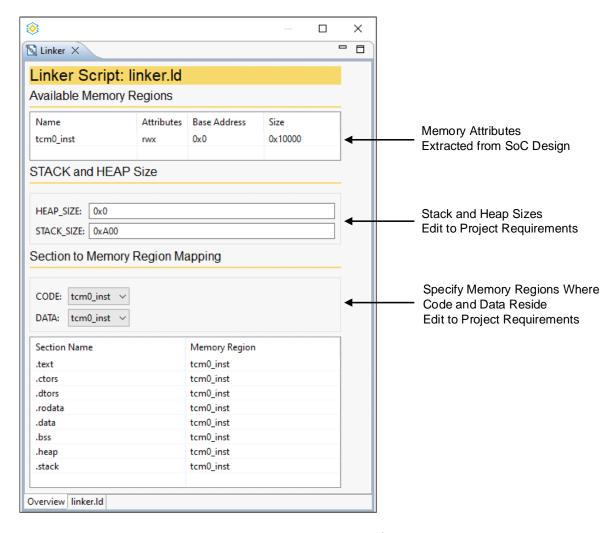

To open the GUI based linker script editor in the Lattice Propel SDK, double click the linker.ld file in the src directory of your Lattice C/C++ project. Figure 4.9 shows the Linker Configuration GUI.

Figure 4.9. Lattice Propel SDK Linker Configuration GUI

The GUI displays the memory regions that are available in the SoC design which the project is based. Modify stack and heap sizes by changing the values in the text boxes. For SoC designs that have multiple memory regions, you can partition the code and data into separate memory regions using the GUI.

You can only make limited changes to the linking process using the Linker Configuration GUI. For more complex designs requiring more customizations, edit the text of the default linker script directly.

#### 4.4.1.2. Text Based Linker Script Customization

To open the text based linker script editor, double click the linker.ld file in the src directory of your Lattice C/C++ project and click the linker.ld tab at the bottom of the pane as shown in Figure 4.10.

```

0

X

- -

Linker X

1/* Lattice Generated linker script, for normal executables */

3 ENTRY ( start)

4

5_HEAP_SIZE = DEFINED(_HEAP_SIZE) ? _HEAP_SIZE : 0x0;

6_STACK_SIZE = DEFINED(_STACK_SIZE) ? _STACK_SIZE : 0xA00;

8 MEMORY

9 {

sysmem0_inst (rwx) : org = 0x0, len = 0x8000

10

11 }

12

13 SECTIONS

14 {

15

/* CODE */

.text : ALIGN(4)

16

17

18

ftext = .;

KEEP (*(SORT(.crt*)))

19

20

*(.text .text.* .gnu.linkonce.t.*)

21

KEEP (*(.init))

KEEP (*(.fini))

22

23

\cdot = ALIGN(4);

24

etext = .;

} >sysmem0 inst

25

26

27

.ctors : ALIGN(4)

28

29

ctors start = .;

30

KEEP (*(.init_array*))

KEEP (*(SORT(.ctors.*)))

31

32

KEEP (*(.ctors))

33

. = ALIGN(4);

34

_ctors_end = .;

35

} >sysmem0_inst

Overview linker.ld

linker.ld Tab

```

Figure 4.10. Lattice Propel SDK Linker Script Text Editor

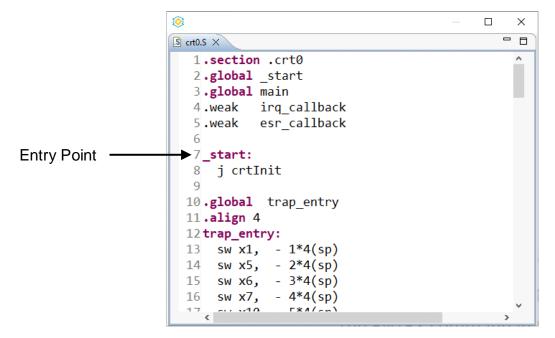

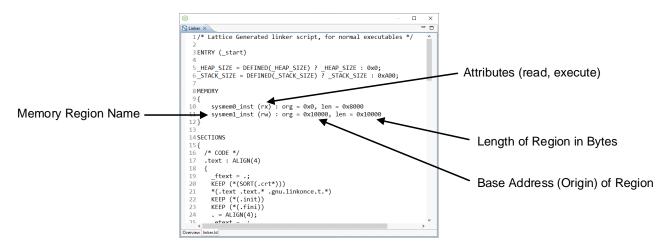

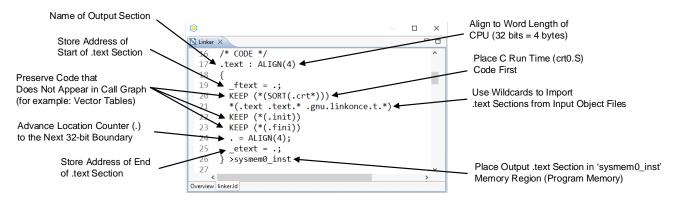

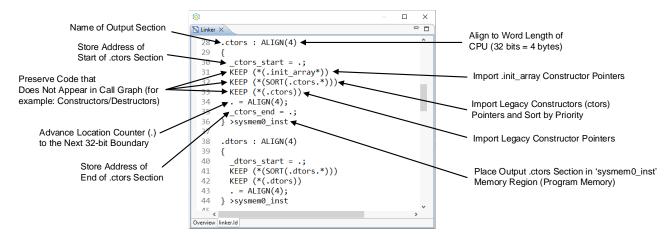

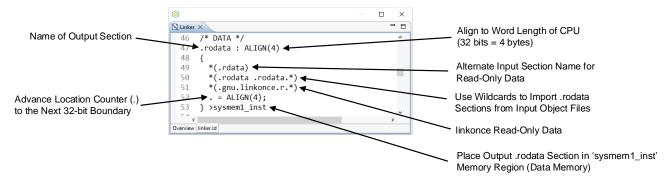

#### 4.4.2. Lattice Propel SDK Default Linker Script

GNU compatible linker scripts are written in the Linker Command Language. The default linker script provided by the Lattice Propel software consists of three commands in the following sequence:

- 1. ENTRY: Identifies the entry point, the first instruction to be executed in the program.

- 2. MEMORY: Specifies the different memory regions visible to the processor and the characteristics such as base address, size, and accessibility (read, write, execute).

- 3. SECTIONS: Specifies how the object file input sections are mapped to the ELF output sections.

Figure 4.11 shows the beginning of an autogenerated linker script for a system with two separate memories: one for storing instructions and one for storing data.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

```

- -

1/* Lattice Generated linker script, for normal executables

3 ENTRY (_start)

5_HEAP_SIZE = DEFINED(_HEAP_SIZE) ? _HEAP_SIZE : 0x0;

6_STACK_SIZE = DEFINED(_STACK_SIZE) ? _STACK_SIZE : 0xA00;

8 MEMORY

9 {

sysmem0_inst (rx) : org = 0x0, len = 0x8000

sysmem1_inst (rw) : org = 0x10000, len = 0x10000

11

12}

13

14 SECTIONS

15 {

/* CODE */

16

17

.text : ALIGN(4)

18

19

ftext = .;

20

KEEP (*(SORT(.crt*)))

21

*(.text .text.* .gnu.linkonce.t.*)

KEEP (*(.init))

KEEP (*(.fini))

22

23

24

. = ALIGN(4);

25