# Importing Platform Designer IP into MachXO3D Designs

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Contents**

| Acr                          | onyms in This Document                                                 | 4  |  |

|------------------------------|------------------------------------------------------------------------|----|--|

| 1.                           | Introduction                                                           |    |  |

| 2.                           | Exporting a Platform Manager 2 Design                                  |    |  |

| 3.                           | Excluding the EFB Module                                               |    |  |

| 4.                           | Building and Exporting                                                 |    |  |

| 5.                           | Importing the Platform Manager 2 IP into a MachXO3D Design             | 10 |  |

| 6.                           | Summary                                                                | 14 |  |

| Ref                          | erences                                                                | 15 |  |

| Technical Support Assistance |                                                                        |    |  |

| Rev                          | Revision History                                                       |    |  |

| Fig                          | gures                                                                  |    |  |

| Figi                         | re 1.1. Exporting Platform Manager 2 IP                                | 5  |  |

|                              | re 1.2. Platform Designer Exported IP within MachXO3D Top-Level Design |    |  |

|                              | re 2.1. Global Device Options – Export IP                              |    |  |

| Figu                         | rre 3.1. Disable the EFB Module                                        | 8  |  |

|                              | rre 4.1. Compile and Export                                            |    |  |

| _                            | re 5.1. Only MachXO3D Selected in Device Selector Window               |    |  |

|                              |                                                                        |    |  |

## **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                               |

|---------|------------------------------------------|

| ASC     | Analog Sense and Control                 |

| ASCVM   | Analog Sense and Control Virtual Machine |

| EFB     | Embedded Function Block                  |

| FPGA    | Field-Programmable Gate Array            |

| GPIO    | General Purpose Input/Output             |

| PFR     | Platform Firmware Resiliency             |

| PIO     | Programmed Input/Output                  |

| PTM2    | Platform Manager II                      |

| RTL     | Register-Transfer Level                  |

#### 1. Introduction

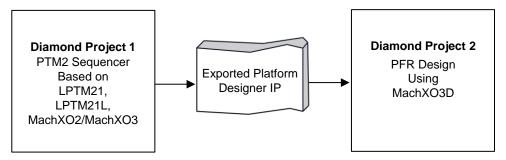

This user guide shows how to integrate power supply monitoring and sequencing into MachXO3D™ designs. While the Platform Designer tool in Lattice Diamond® does support MachXO3D based designs with L-ASC10 devices, similar to MachXO2 or MachXO3 based designs, the tool creates a top-level design based on the ASC interface and power sequence. This document describes modifications to the Platform Designer tool that supports exporting an IP package that can be easily instantiated in a separate MachXO3D top-level design, as shown Figure 1.1. For example, to provide a secure power sequencing to the Platform Firmware Resiliency (PFR) solution. The exported module could also be instantiated in other Lattice FPGA designs.

Figure 1.1. Exporting Platform Manager 2 IP

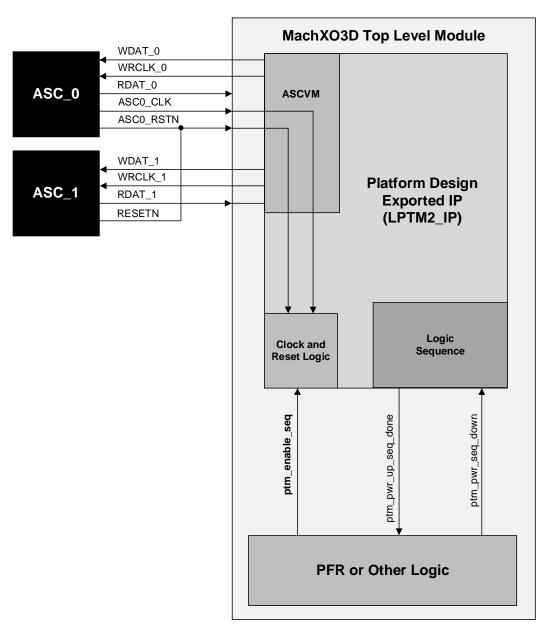

Figure 1.2 shows the following key components of the exported IP:

- The ASC virtual machine (ASCVM) that handles the three-wire interface between the FPGA and the various ASC devices.

- The Clock and Reset module that generates clocks and enables the start of the sequencer. Note that the signal ptm\_enable\_seq is automatically added to the IP as part of the export process and is used to enable the power sequence after the PFR decides that it is safe to do so.

- The Logic Sequence interfaces with other signals (not in bold) that are examples of user defined handshaking signals between the Platform Designer sequence and the PFR controller. One is to signal to the PFR that the power up sequence is complete and the other provides a means for the PFR to shut the power down. Both signals need to be designed into the Platform Designer and PFR logic by the user. Additional signals to handle fault conditions, or other situations, can easily be added by the user.

Figure 1.2. Platform Designer Exported IP within MachXO3D Top-Level Design

### 2. Exporting a Platform Manager 2 Design

A Platform Manager 2 design can be based on several FPGA devices and the exported module will be generic so that it can be included into a MachXO3D design. Thus, existing designs based on any of the following can be exported into the MachXO3D design: LPTM21, LPTM21L, MachXO2, MachXO3, and MachXO3D.

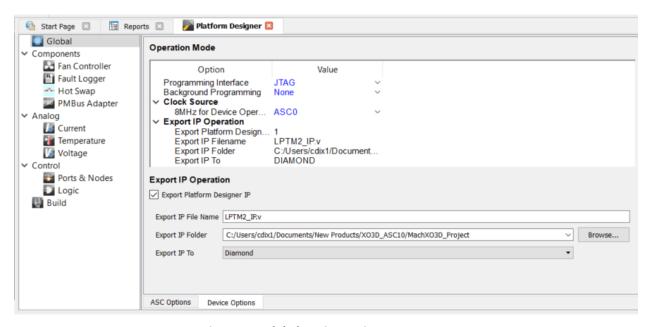

The export option is selected by checking *Export Platform Designer IP* in the *Global* view of the *Device Options* tab, as shown in Figure 2.1.

Figure 2.1. Global Device Options – Export IP

When Export Platform Designer IP is checked, the following fields are visible and editable:

- Export IP File Name

- By default, Platform Designer creates a top-level design file based on the project name with the added prefix of psb\_. This file is generated when the *Compile* button is clicked in the *Build* view. For example, a project named Power\_Sequence.ptm results in the file name psb\_Power\_Sequence.v as the default export file name. In Figure 2.1, the file name is changed to LPTM2\_IP.v and the exported IP module name reflects the file name (LPTM2\_IP).

- Export IP Folder

- This supports browsing to and creating a folder for the exported files to be written into. In addition to the exported IP design file, several other files and folders are written into this location. The other files and folders are described in a later section.

- Export To

- This drop down list allows the export function to target various Lattice devices. For the MachXO3D and other Diamond supported devices, the selection should be Diamond. The other options support exporting the Platform Designer IP to Lattice Radiant™ projects. This is covered in separate documents.

## 3. Excluding the EFB Module

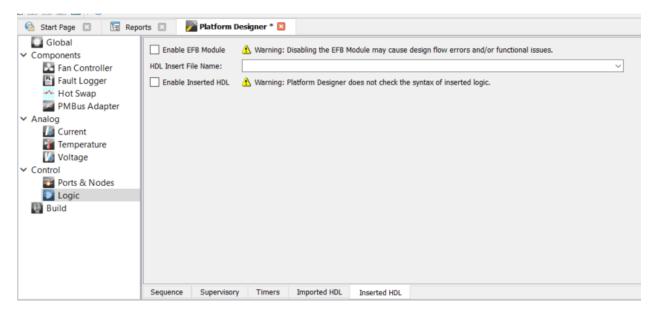

In many designs, the embedded function block (EFB) of the MachXO2 or MachXO3 device is needed for a user function. By default, Platform Designer instantiates the EFB and connects the primary I<sup>2</sup>C port to reserve the port for programming functions. However, when the FPGA is erased, the I<sup>2</sup>C port is available for programming regardless if the EFB is part of a design or not. In order to free up the EFB for user functions, *Enable EFB Module* should be unchecked in the *Inserted HDL* tab of the *Logic* view as shown in Figure 3.1.

Figure 3.1. Disable the EFB Module

## 4. Building and Exporting

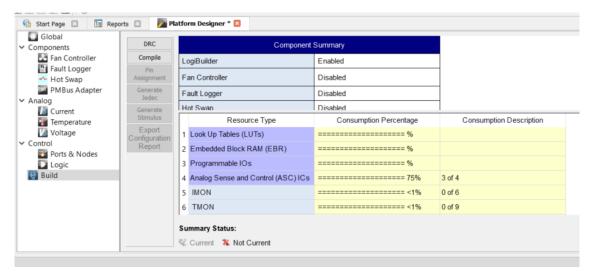

The *Compile* button, as shown in Figure 4.1, in the *Build* view generates the Platform Designer IP and writes it (and associated sub-modules) into the target folder that is specified in Figure 2.1.

Figure 4.1. Compile and Export

## 5. Importing the Platform Manager 2 IP into a MachXO3D Design

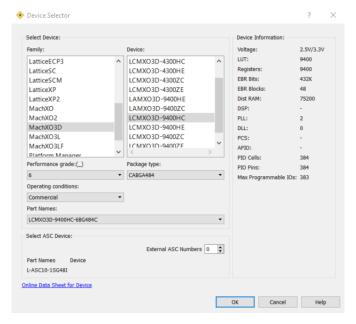

A separate or new MachXO3D design should be started, or modified, in the *Device Selector* window without any external ASC devices, as shown in Figure 5.1.

Figure 5.1. Only MachXO3D Selected in Device Selector Window

Right-click on Input Files and select Add > Existing File from the drop-down menu, as shown in Figure 5.2.

Figure 5.2. Adding Existing File - Popup Menu

Then select the following files (individually or in groups):

- LPTM2 IP.v

- LPTM2\_IP\_tmpl.v

- Power\_Sequencer\_lgb.v

- efb timer config.v

- RDAT.v

- WDAT.v

- CLKRST/src/rtl/Verilog/clkrst.v

- CLKRST/src/rtl/Verilog/clkrst\_core.v

- ASCVM/src/rtl/Verilog/ASCVM.v

- ASCVM/src/rtl/Verilog/ASCVM DATAPATH.v

- ASCVM/src/rtl/Verilog/ASCVM RAM EBR.v

- ASCVM/src/rtl/Verilog/ASCVM\_RAM\_DIST.v

Note that the first three file names depend on the original Platform Designer project name and the export IP file name. Right-click on the template file (PTM\_IP\_tmpl.v) and select *Exclude from Implementation* from the drop-down menu. The result should look similar to Figure 5.3.

Figure 5.3. MachXO3D Project with Platform Designer IP Added to Input Files

Open the template file (PTM\_IP\_tmpl.v) and copy all (CTRL-A, CTRL-C) and paste (CTRL-V) into the top-level module. Insert the module name before the instantiation and connect to the top-level inputs, outputs, and wires, as shown in Figure 5.4.

```

output o_LED_seg_g

vire w_enable_ptm_ip;

wire w_ptm_ip_sequence_done;

wire w_ptm_ip_pwr_down;

LPTM2 IP LPTM2 IP inst

ptm_enable_seq

(w_enable_ptm_ip),

.ASCO_RSTN

(mandatory_resetn_i),

(w_ptm_ip_pwr_down),

(ASC0_CLK_i),

.ptm pwr seq down

.ASCO CLK

.rdat_0

(i_rdat_0)

.rdat 1

(i_rdat_1)

.wrclk 0

(o_wrclk_0),

(o_wrclk_1),

.wrclk_1

(w ptm ip sequence done),

.ptm_pwr_up_seq_done

(o_LED_seg_a),

(o_LED_seg_b),

.LED_seg_a

.LED_seg_b

.LED_seg_c

(o_LED_seg_c),

.LED_seg_d

(o_LED_seg_d),

(o LED seg e),

.LED_seg_f

.LED_seg_g

(o_LED_seg_f),

(o_LED_seg_g),

.wdat_0

(o_wdat_0),

.wdat 1

(o wdat 1)

```

Figure 5.4. Platform Manager 2 IP Inserted into MachXO3D Top-Level Design

The signal .ptm\_enable\_seq is generated as part of the Export Platform Design IP process. The MachXO3D top-level module has the responsibility of setting this signal true and keeping it true. Either tie it true with 1'b1, and the Platform Design IP starts at the same time as the rest of the MachXO3D IP. Another option is to connect it to a wire or register that is driven true after the IP within the MachXO3D starts up. For example, after the PFR IP determines it is safe to start the power up sequence for the platform. This signal is connected to the ASCVM reset logic and should only transition from false to true. If this signal transitions from true to false (1 to 0), then power supplies on the platform assume the reset state without sequencing off and damage could occur to some components.

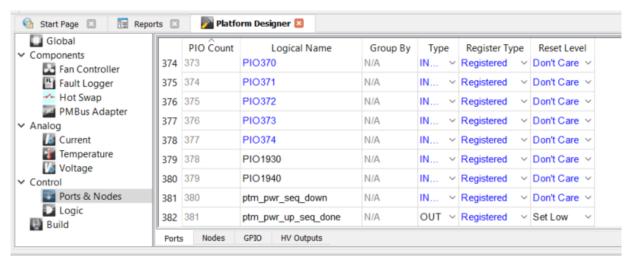

The signal .ptm\_pwr\_up\_seq\_done is a user created PIO port, in Platform Designer, just like the seven-segment LED outputs (.LED\_seg\_a - .LED\_seg\_g). It is up to the user to create the name of this output and to reset the signal at power up and set the signal when the sequence is complete in the Platform Designer Logic Sequence.

The signal ptm\_pwr\_seq\_down is also a user created PIO port in Platform Designer, as shown in Figure 5.5. It is up to the user to create the name of this input signal and to sequence off the power supplies in Platform Designer logic when the MachXO3D logic activates this signal.

The MachXO3D design can interface with these Platform Designer ports either directly in RTL or indirectly thru the GPIO interface of the PFR solution.

Figure 5.5. User Defined PIO Ports in Platform Designer

### 6. Summary

With the Platform Designer IP imported into the MachXO3D top-level module, both the Power Sequence design and the MachXO3D design can undergo the typical iterative design process. Changes to the Power Sequence are updated with the *Compile* button in the *Build* view (Figure 4.1) and the MachXO3D firmware or RTL can be updated and rebuilt using the standard Diamond interface without any hand-modifications to generated RTL.

#### References

- L-ASC10 Data Sheet (FPGA-DS-02038)

- Platform Manager 2 Data Sheet (FPGA-DS-02036)

- MachXO2 Family Data Sheet (FPGA-DS-02056)

- MachXO3 Family Data Sheet (FPGA-DS-02032)

- MachXO3D Family Data Sheet (FPGA-DS-02026)

- Lattice Sentry Root of Trust Demo Setup for MachXO3D User Guide (FPGA-UG-02114)

- Lattice Sentry PLD Interface IP Core Lattice Propel Builder User Guide (FPGA-IPUG-02106)

- MachXO3D Platform Firmware Resiliency Manifest and Log Management (FPGA-UG-02025)\*

- MachXO3D Platform Firmware Resiliency Out-of-Band I2C Command Protocol (FPGA-UG-02032)\*

<sup>\*</sup>Note: To access this document, contact your Lattice representative

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

# **Revision History**

#### Revision 1.0, October 2022

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

www.latticesemi.com