# **DisplayPort and Video Scaler Demonstration**

# **User Guide**

FPGA-UG-02201-1.0

December 2023

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ# 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                     | 3  |

|----------------------------------------------|----|

| Acronyms in This Document                    | 6  |

| 1. Introduction                              | 7  |

| 1.1. Demonstration Requirements              | 7  |

| 1.1.1. Hardware                              | 7  |

| 1.1.2. Software                              | 8  |

| 1.1.3. Cable                                 | 8  |

| 1.2. Configurations and Hardware Description | 8  |

| 1.2.1. Supported configurations              | 8  |

| 1.2.2. Hardware setup                        | 8  |

| 1.2.3. LEDs Description                      | 8  |

| 2. SoC Design Details                        | 11 |

| 2.1. Top-level design                        | 11 |

| 2.2. Top-level ports                         | 11 |

| 2.3. IP Description                          | 13 |

| 2.3.1. DisplayPort                           | 13 |

| 2.3.2. Video Scaler                          | 16 |

| 2.3.3. DP to VS Converter                    | 17 |

| 2.3.4. Clock Controller                      | 18 |

| 2.3.5. Oscillator                            | 20 |

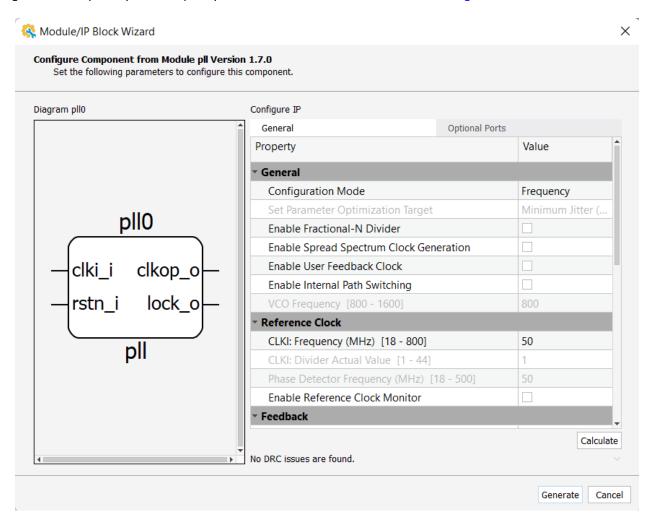

| 2.3.6. PLL                                   | 21 |

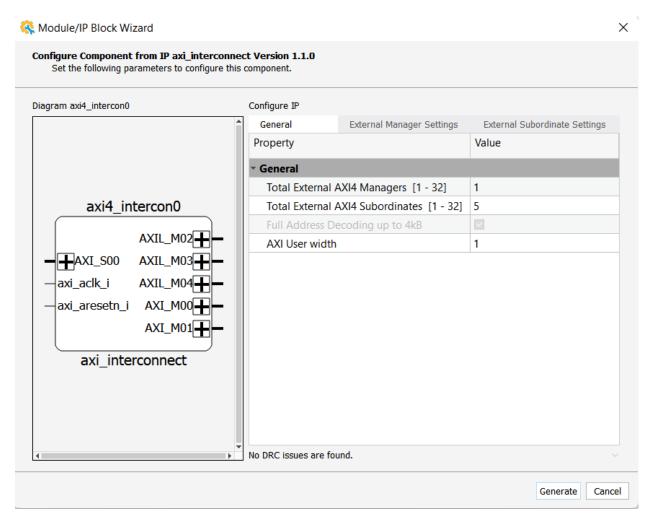

| 2.3.7. AXI Interconnect                      | 22 |

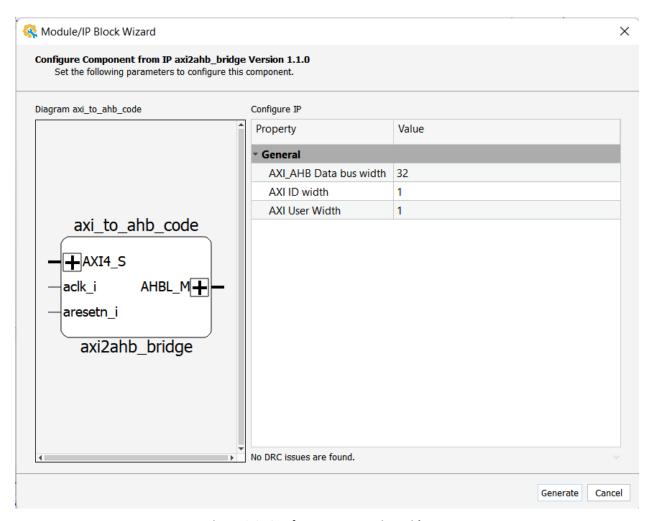

| 2.3.8. AXI to AHB-Lite Bridge                | 23 |

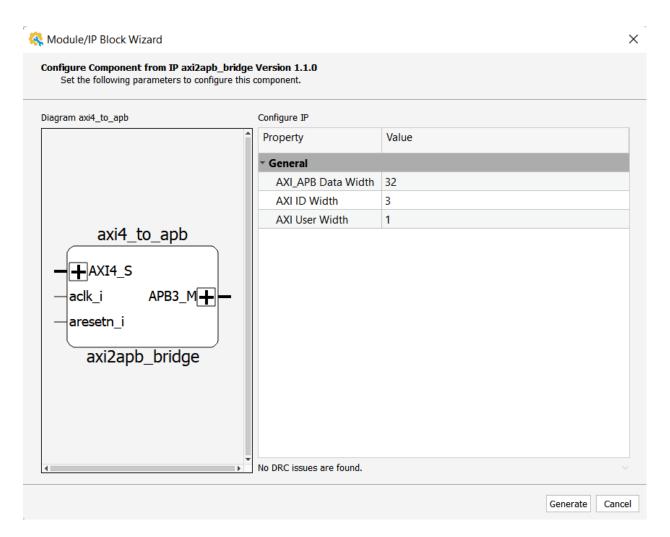

| 2.3.9. AXI to APB Bridge                     | 24 |

| 2.3.10. System memory                        | 25 |

| 2.3.11. RISC-V RX                            | 26 |

| 2.3.12. UART                                 | 27 |

| 3. Modifying and Implementing the SoC Design | 28 |

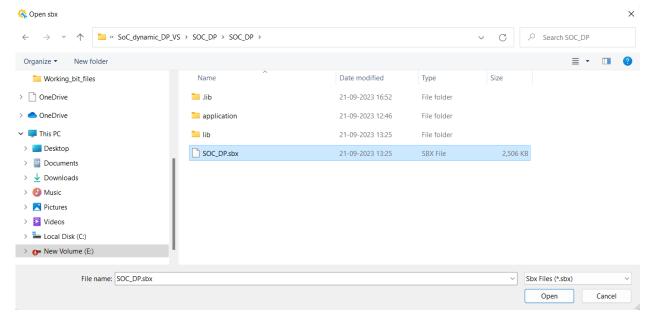

| 3.1. Opening the Sbx project                 | 28 |

| 3.2. Modifying the SoC                       | 31 |

| 3.2.1. DisplayPort                           | 31 |

| 3.2.2. Video Scaler                          | 32 |

| 3.2.3. DP to VS Converter                    | 32 |

| 3.3. Validating and generating the design    | 32 |

| 3.4. Opening Project in Radiant              | 33 |

| 3.5. Uploading the bit file to the FPGA      | 35 |

| 4. Demonstration                             | 37 |

| 5. Troubleshooting                           | 44 |

| 5.1. LED Troubleshooting Guide               |    |

| 5.2. Unresponsive board or terminal          |    |

| Appendix A: Resource Utilization             |    |

| References                                   |    |

| Technical Support Assistance                 |    |

| Revision History                             |    |

# **Figures**

| Figure 1.1. DP Video Scaler Hardware Top Level Diagram                     | 7  |

|----------------------------------------------------------------------------|----|

| Figure 1.2. Demonstration Hardware Setup                                   | 10 |

| Figure 2.1. Soc Design                                                     | 11 |

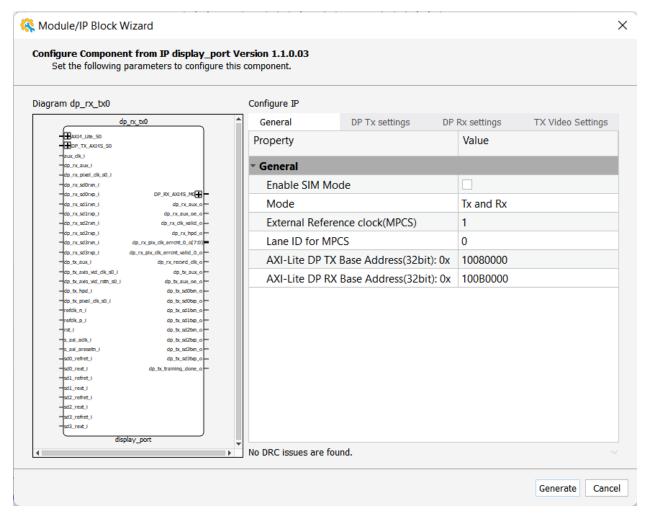

| Figure 2.2. GUI for DisplayPort IP                                         | 15 |

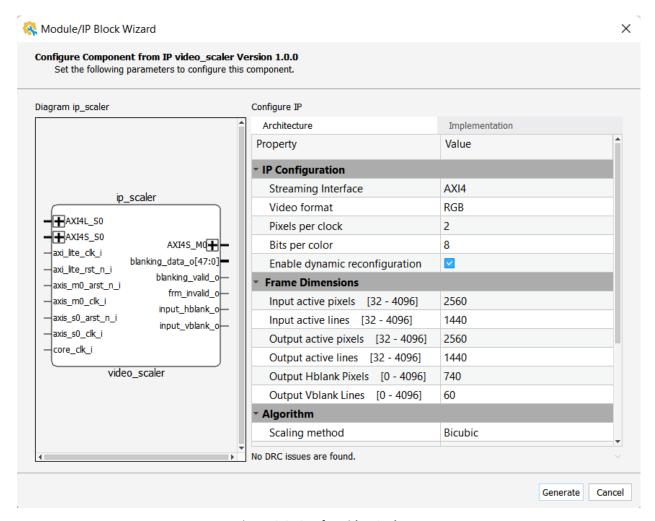

| Figure 2.3. GUI for Video Scaler IP                                        |    |

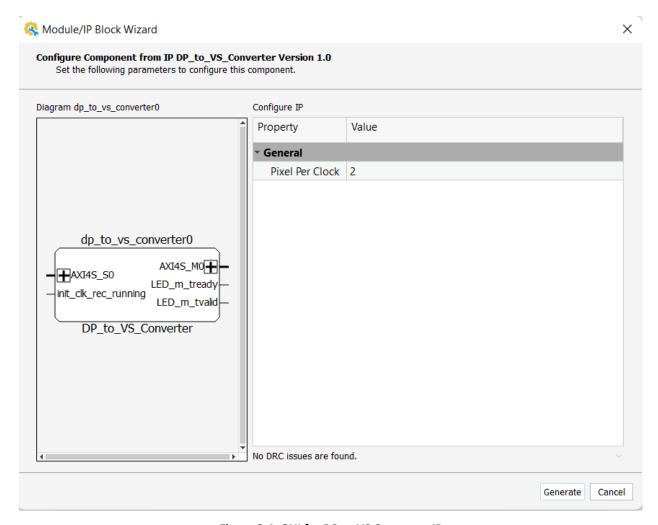

| Figure 2.4. GUI for DP to VS Converter IP                                  | 18 |

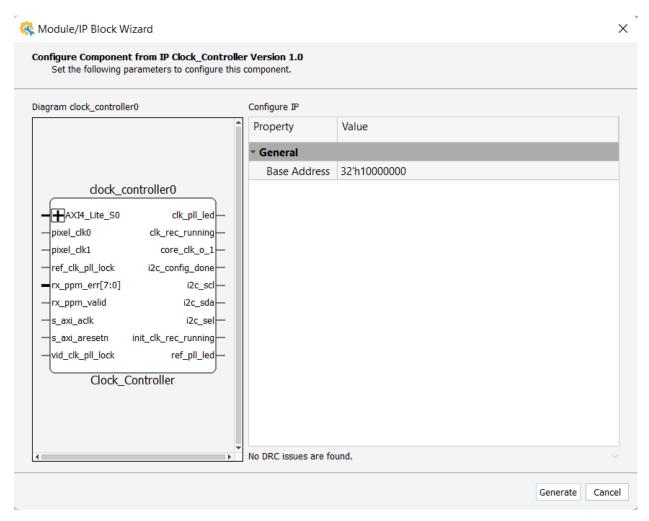

| Figure 2.5. GUI for Clock Controller IP                                    |    |

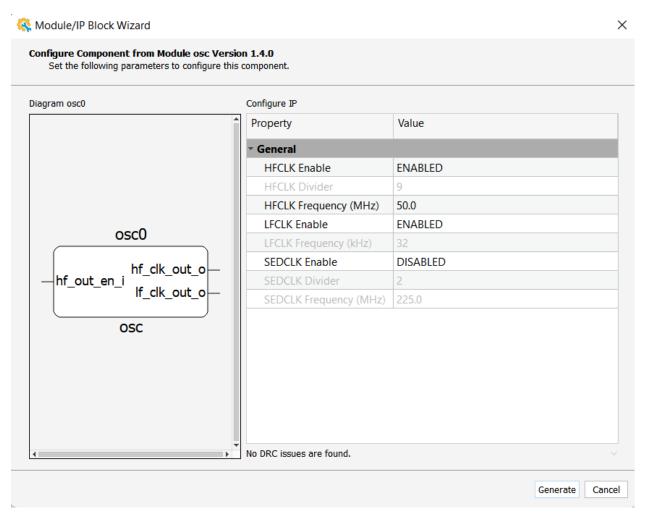

| Figure 2.6. GUI for Oscillator IP                                          |    |

| Figure 2.7. GUI for PLL IP                                                 |    |

| Figure 2.8. GUI for AXI Interconnect IP                                    |    |

| Figure 2.9. GUI for AXI to AHB-Lite Bridge IP                              |    |

| Figure 2.10. GUI for AXI to APB Bridge IP                                  |    |

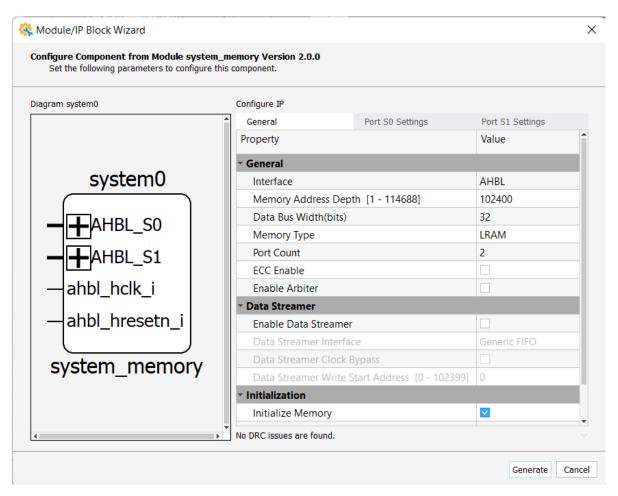

| Figure 2.11. GUI for System Memory IP                                      |    |

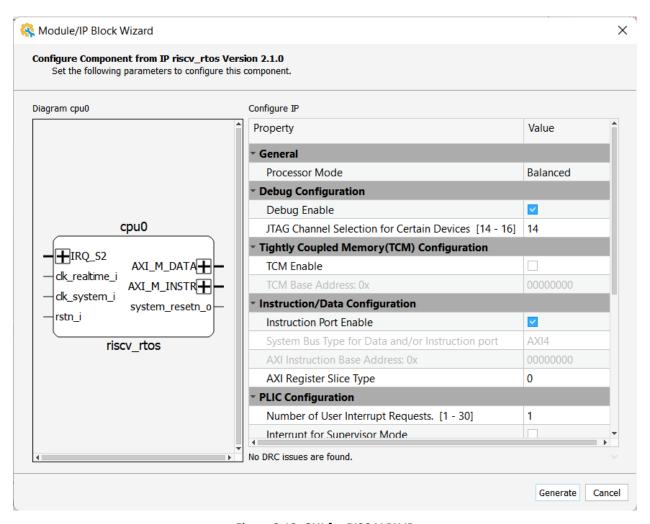

| Figure 2.12. GUI for RISC-V RX IP                                          |    |

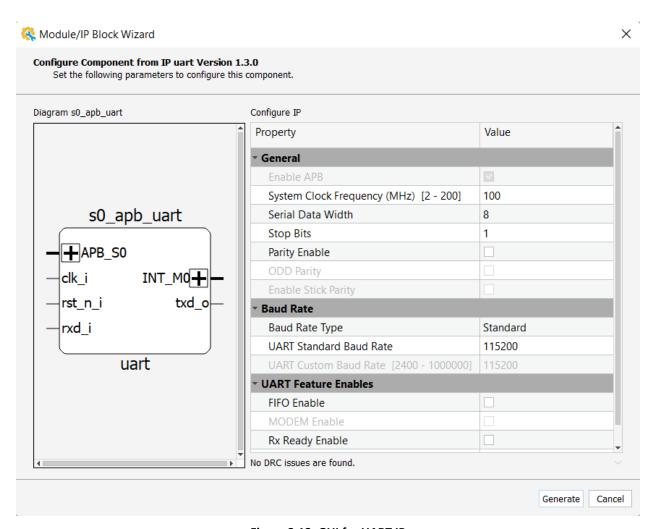

| Figure 2.13. GUI for UART IP                                               |    |

| Figure 3.1. Sbx Dialog Box                                                 |    |

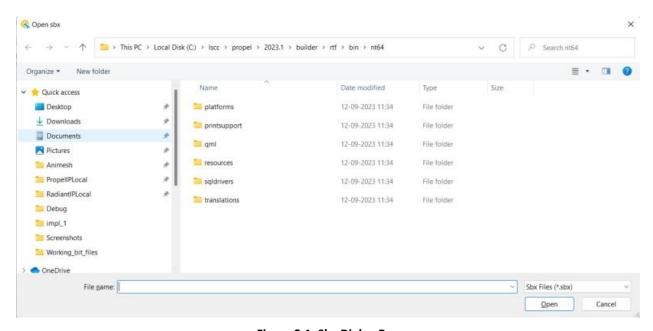

| Figure 3.2. Project Sbx file Dialog Box                                    |    |

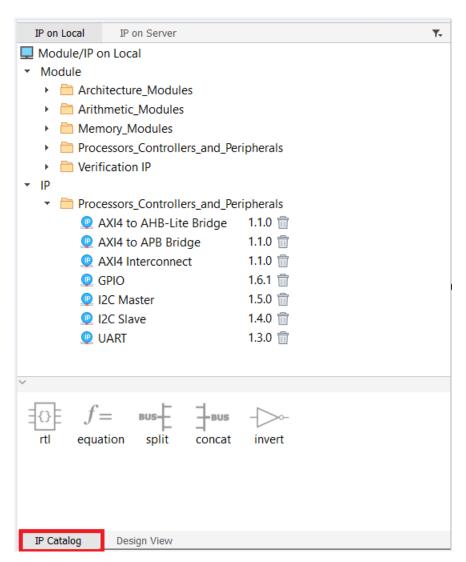

| Figure 3.3. IP Catalog tab                                                 |    |

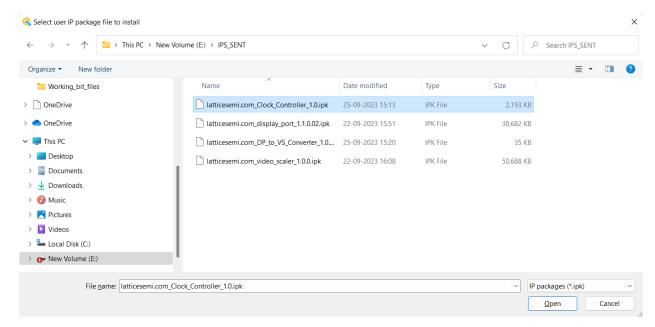

| Figure 3.4. IPK Dialog Box                                                 |    |

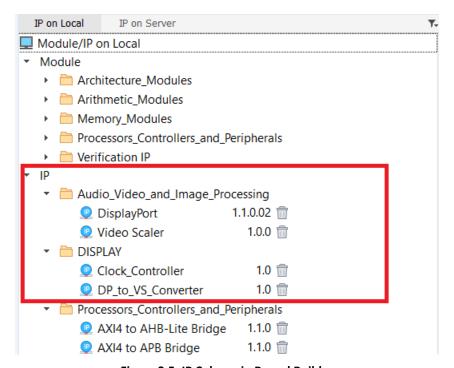

| Figure 3.5. IP Column in Propel Builder                                    |    |

| Figure 3.6. Generating IP in Builder                                       |    |

| Figure 3.7. GUI Icon in Propel Builder                                     |    |

| Figure 3.8. Radiant Icon in Propel Builder                                 |    |

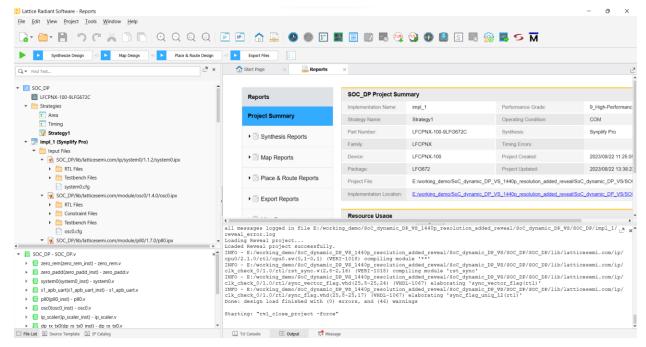

| Figure 3.9. Radiant Project                                                |    |

| Figure 3.10. Synthesize Design                                             |    |

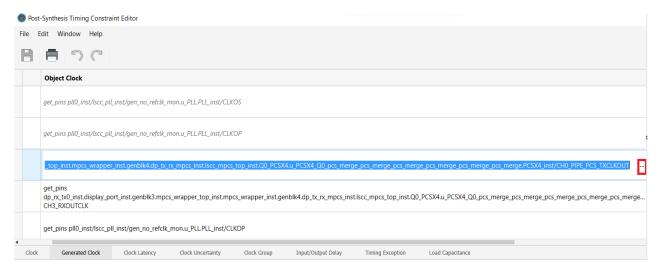

| Figure 3.11. Post Synthesis Timing Constraint Editor Dialog Box            |    |

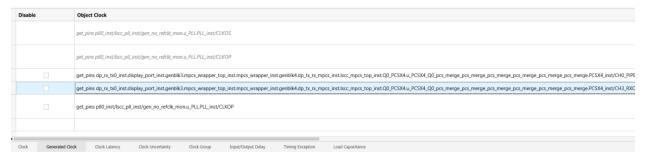

| Figure 3.12. Generated Clock Tab                                           |    |

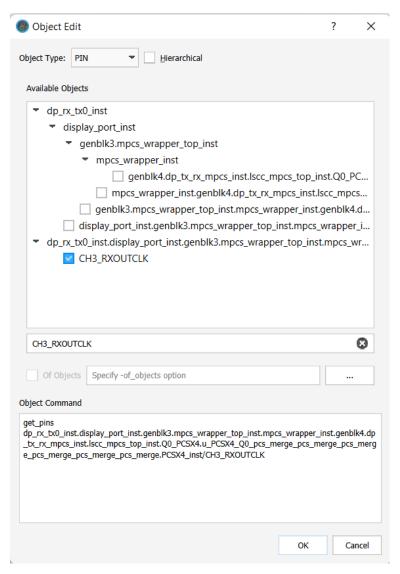

| Figure 3.13. Object Edit Dialog Box                                        |    |

| Figure 3.14. Saving the Post Synthesis Timing Constraint Editor Dialog Box |    |

| Figure 3.15. Export Files                                                  |    |

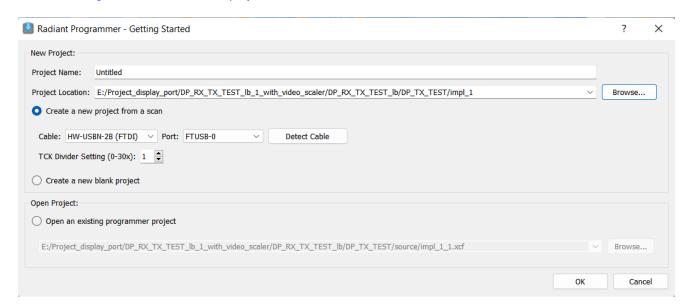

| Figure 3.16. Radiant Programmer Dialog Box                                 |    |

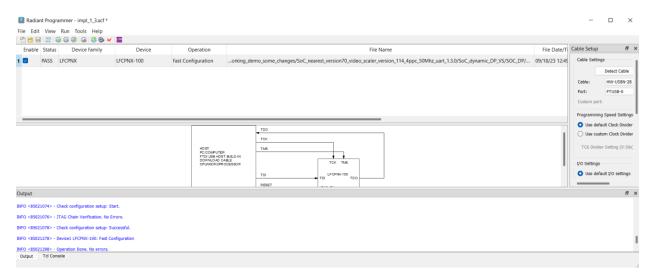

| Figure 3.17. Radiant Programmer Window                                     |    |

| Figure 3.18: Program Device Toolbar Icon                                   |    |

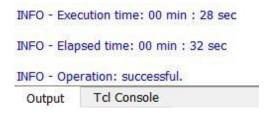

| Figure 3.19. Output Window                                                 |    |

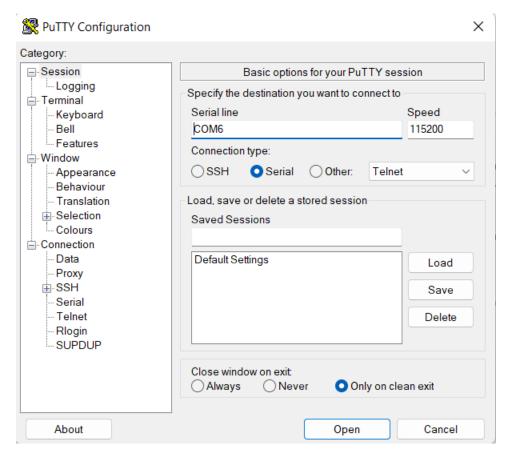

| Figure 4.1. PuTTY Configuration Window- Port Selection                     |    |

| Figure 4.2. PuTTY Window                                                   |    |

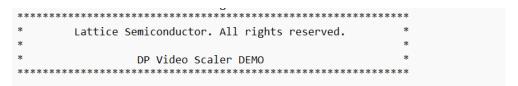

| Figure 4.3. Input and Output Configuration                                 |    |

| Figure 4.4. Pixel Clock Set Information                                    |    |

| Figure 4.5. Video Scaler Parameters                                        |    |

| Figure 4.6. Rx EDID Information                                            |    |

| Figure 4.7. DP Rx Training Unsuccessful                                    |    |

| Figure 4.8. The Demonstration - DP Rx Link Training                        |    |

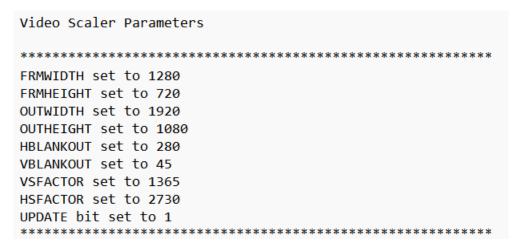

| Figure 4.9. MSA Detection and Main Video Streaming                         |    |

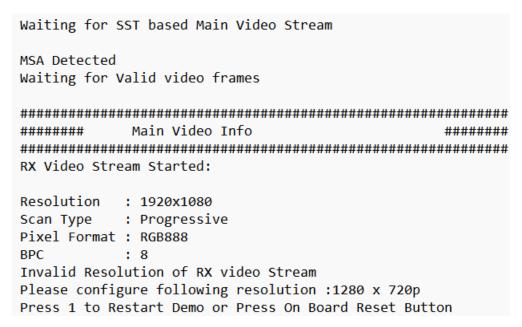

| Figure 4.10. MSA Detection and Incorrect Resolution Detected               |    |

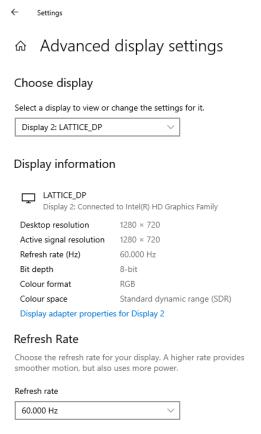

| Figure 4.11. Display Settings                                              |    |

| Figure 4.12. DP Tx Initialized (Sink Detected)                             |    |

| Figure 4.13. DP Tx Initialized (Sink not Detected)                         |    |

| Figure 4.14. DP Tx Max Capability                                          |    |

| Figure 4.15. DP Tx Training                                                |    |

| Figure 4.16. Video Enabled                                                 |    |

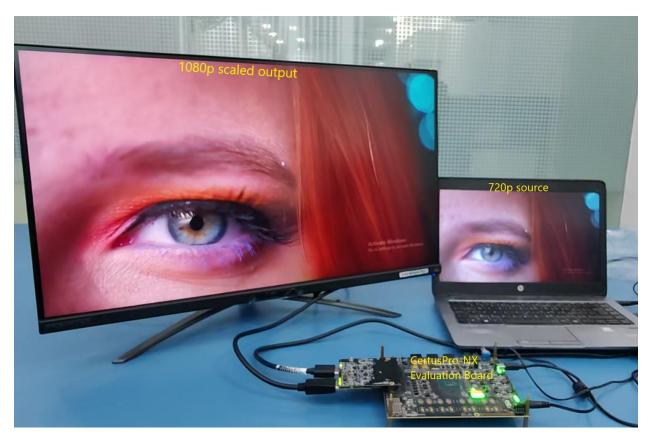

| Figure 4.17. 720p to 1080p Live Video Upscaling Dynamically                | 43 |

## **Tables**

| Table 1.1. Eval Board LEDs Description                   | <u>C</u> |

|----------------------------------------------------------|----------|

| Table 1.2. Modular FMC adapter LEDs Description          |          |

| Table 2.1. SoC Design Ports Description                  |          |

| Table 2.2. DP Attributes Description                     |          |

| Table 2.3. Video Scaler Attributes Description           |          |

| Table 2.4. DP to VS Converter Attribute Description      |          |

| Table 2.5. Clock Controller Attribute Description        |          |

| Table 3.1. DisplayPort IP Modified Parameters            |          |

| Table 3.2. Video Scaler IP Modified Parameters           |          |

| Table 3.3. DP to VS Converter IP modified Parameters     |          |

| Table 5.1. LED troubleshooting                           |          |

| Table A.1. Resource Utilization for DP Video Scalar Demo | /15      |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                                    |

|---------|-----------------------------------------------|

| AXI     | Advanced eXtensible Interface                 |

| BPC     | Bits Per Color                                |

| CLINT   | Core-local Interrupt Controller               |

| DP Rx   | DisplayPort Receiver                          |

| DP Tx   | DisplayPort Transmitter                       |

| EDID    | Extended Display Identification Data          |

| FMC     | FPGA Mezzanine Card                           |

| FPGA    | Field Programmable Gate Array                 |

| GUI     | Graphical User Interface                      |

| HBR     | High bit rate                                 |

| MPCS    | Multi-protocol physical coding sublayer       |

| MSA     | Main Stream Attribute                         |

| MST     | Multi-Stream Transport                        |

| PLIC    | Platform-level Interrupt Controller           |

| PLL     | Phase locked loop                             |

| PPC     | Pixels Per Clock                              |

| RISC-V  | Reduced instruction set computer version five |

| SERDES  | Serializer de-serializer                      |

| SST     | Single Stream Transport                       |

| UART    | Universal asynchronous receiver-transmitter   |

| VS      | Video Scaler                                  |

## 1. Introduction

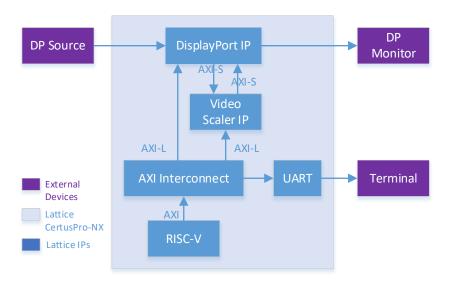

This demonstration illustrates the integration of the Lattice DisplayPort (DP) IP and Lattice Video Scaler IP. The Lattice Semiconductor CertusPro™-NX Evaluation Board allows designers to evaluate the features of the CertusPro-NX Field Programmable Gate Array (FPGA) and assists them with rapid prototyping of their designs. The DisplayPort and Video Scaler demonstration showcases an end-to-end Video Scaling system. It includes Lattice DP IP and Lattice Video Scaler IP as the primary components. The demonstration system is schematically shown in Figure 1.1. It takes in a video from a DisplayPort source, like a desktop, scales the resolution up or down and re-transmits the scaled video through a DisplayPort connector to a DisplayPort sink, like a computer monitor. As shown in the Figure 1.1, the DP input is received by the DisplayPort IP receiver (DP Rx), scaled by Video Scaler and sent to the DisplayPort IP transmitter (DP Tx) to be sent to the DP connector. There are additional components in the demonstration system, like a RISC-V processor, AXI interconnect and UART, which are used to read the status of DP IP and display that in an external terminal.

Figure 1.1. DP Video Scaler Hardware Top Level Diagram

The demonstration system is built on Lattice CertusPro-NX Evaluation board, along with the Lattice Modular FMC Adapter, Lattice DisplayPort Transmitter Daughter Card, and Lattice DisplayPort Receiver Daughter Card (collectively referred to as DP FMC Daughter Card Kit). The demonstration design is a SoC (System on a Chip) design created as a Lattice Propel™ project. The propel project can be opened, modified if necessary and implemented using Lattice Radiant. The final bitstreams are also provided which can be directly programmed on the board and tested out. The design supports an external UART terminal for controlling the demo and for status display. The details of the Propel design, the included bitstreams, and the bring-up procedure are given in the following chapters.

### 1.1. Demonstration Requirements

The hardware, software and cable requirements for this demonstration are provided in the following section.

#### 1.1.1. Hardware

This demonstration requires the following hardware components:

- CertusPro-NX Evaluation Board

- Lattice Modular FMC Adapter

- Lattice DisplayPort Transmitter Daughter Card

- Lattice DisplayPort Receiver Daughter card

- HBR2 (5.4 Gbps x4) capable DP source and sink devices

- Power supply for the evaluation board

8

#### 1.1.2. Software

This demonstration requires the following software components:

- Lattice Propel Builder Software version 2023.1 or higher

- Lattice Radiant Software version 2023.1 or higher

- Radiant Programmer System software for downloading the FPGA bitstream

- A terminal application like PuTTY

#### 1.1.3. Cable

Two DisplayPort cables supporting version 1.4 or higher

## 1.2. Configurations and Hardware Description

#### 1.2.1. Supported configurations

The included Propel project is built using 2 pixels per clock (PPC) data path for DP and Video Scaler IPs. The project can also be modified to support 4 PPC data path. Two bitstreams, one for 2 PPC data path and the other for 4 PPC data path are included in the demo package. Both versions support dynamic configuration of Video Scaler and input/output resolutions.

The bitstream for 2 PPC supports live video scaling for the following configurations (Bicubic algorithm):

- 720p to 1080p upscaling

- 1080p to 720p downscaling

- 1080p to 1080p pass through

- 720p to 1440p upscaling

- 1440p to 720p downscaling

- 720p to 720p pass through

- 1080p to 1440p upscaling

- 1440p to 1080p downscaling

- 1440p to 1440p pass through

The bitstream for 4 PPC supports live video scaling for the following configurations (Nearest neighbor algorithm):

- 1080p to 2160p upscaling

- 2160p to 1080p downscaling

- 2160p to 2160p pass through

- 1440p to 2160p upscaling

- 2160p to 1440p downscaling

- 1440p to 1440p pass through

- 1080p to 1440p upscaling

- 1440p to 1080p downscaling

- 1080p to 1080p pass through

#### 1.2.2. Hardware setup

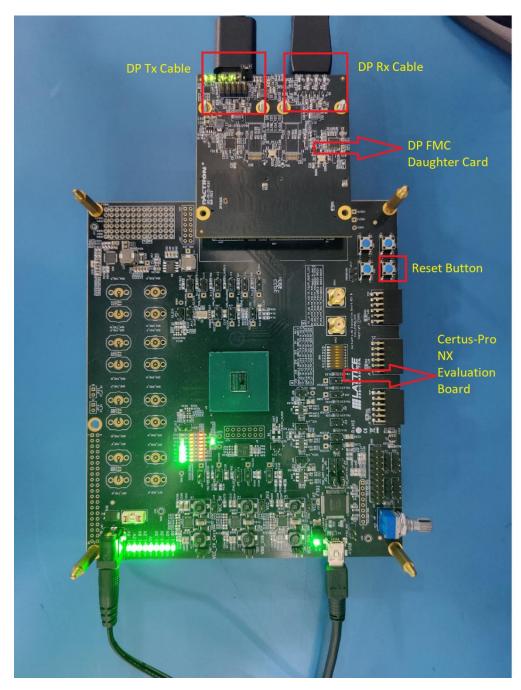

Figure 1.2 shows the hardware configuration used for this demonstration. This demonstration works on the CertusPro-NX Evaluation board with the DP FMC Daughter Card kit connected to it. The kit consists of Modular FMC Adapter, DisplayPort Transmitter Daughter Card, and DisplayPort Receiver Daughter Card. After mounting the DP FMC daughter board kit on to the CertusPro-NX evaluation board, connect DP source and sink through two different DP cables. A commonly used DP source is a desktop or Laptop PC with DP output and a common DP sink is a computer monitor supporting DP input.

#### 1.2.3. LEDs Description

The LEDs on the evaluation board and the Modular FMC adapter are used to indicate status of the demonstration system. All used LEDs must be glowing steadily (without blinking) to indicate proper running state of the demo. Please refer to the

LED Troubleshooting Guide section to interpret the status of the demonstration system based on LEDs. The eight green LEDs on the evaluation board are used as described in Table 1.1 and the four green LEDs used on the Modular FMC adapter are used as described in Table 1.2.

#### Table 1.1. Eval Board LEDs Description

| LED | Description                       |

|-----|-----------------------------------|

| D6  | SERDES reference clock PLL locked |

| D7  | System (RISC-V) clock PLL locked  |

| D8  | Not used                          |

| D9  | Pixel Clock PLL locked            |

| D10 | RX video stream valid             |

| D11 | Clock recovery running status     |

| D12 | Video Scaler IP ready             |

| D13 | Video Scaler IP frame valid       |

#### Table 1.2. Modular FMC adapter LEDs Description

| LED  | Description      |

|------|------------------|

| LED0 | Not used         |

| LED1 | Not used         |

| LED2 | Tx training done |

| LED3 | Not used         |

Figure 1.2. Demonstration Hardware Setup

## 2. SoC Design Details

An SoC design created using Lattice Propel™ Builder is provided for this demo. Users can take this working system and modify the design or the parameters of the building block IPs as necessary.

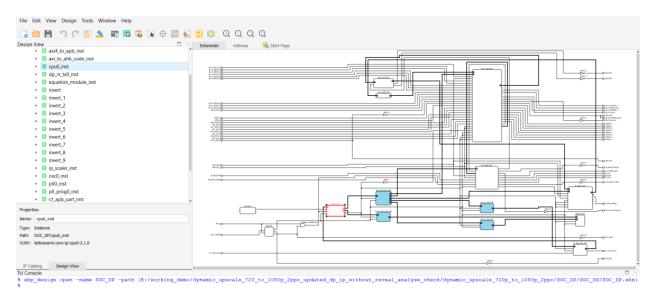

## 2.1. Top-level design

The top-level SoC design is shown in Figure 2.1.

Figure 2.1. Soc Design

## 2.2. Top-level ports

Table 2.1 shows the ports used in the SoC Design in the Lattice Propel Builder.

**Table 2.1. SoC Design Ports Description**

| Port Name           | Direction | Width | Description                                                                                                                                  |

|---------------------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| refclk_p            | In        | 1     | P port of 135 MHz differential reference clock.                                                                                              |

|                     |           |       | Note: This should be 108 MHz for 1.62Gbps Data Rate                                                                                          |

| refclk_n            | In        | 1     | N port of 135 MHz differential reference clock.                                                                                              |

|                     |           |       | Note: This should be 108 MHz for 1.62Gbps Data Rate                                                                                          |

| pixel_clk_0         | In        | 1     | Pixel clock input. The frequency depends on the video resolution.                                                                            |

| pixel_clk_1         | In        | 1     | Pixel clock input. The frequency depends on the resolution.                                                                                  |

| rstn_i              | In        | 1     | Active low asynchronous reset of minimum 100 us duration.                                                                                    |

| dp_tx_aux_o         | Out       | 1     | Output signal for AUX channel.                                                                                                               |

| dp_tx_aux_oe_o      | Out       | 1     | Tri-state control for AUX channel. If the value is '1', the AUX output is driven, otherwise it is undriven and held at high impedance state. |

| dp_tx_aux_i         | In        | 1     | Input signal from AUX channel                                                                                                                |

| dp_tx_hpd_i         | In        | 1     | Hot plug detect signal to inform DP source that DP sink is connected.                                                                        |

| dp_tx_training_done | Out       | 1     | Training done output signal to inform that training has been done at at DP Tx side.                                                          |

| dp_rx_sd0rxp_i      | In        | 1     | This is lane0 serial data_p signal of DP Rx main channel.                                                                                    |

| dp_rx_sd0rxn_i      | In        | 1     | This is lane0 serial data_n signal of DP Rx main channel.                                                                                    |

| dp_rx_sd1rxn_i   In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port Name           | Direction | Width | Description                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|-------|--------------------------------------------------------------------|

| top_rx_sd2rxp_i in 1 This is lane2 serial data_p signal of DP Rx main channel.  dp_rx_sd3rxp_i in 1 This is lane2 serial data_p signal of DP Rx main channel.  dp_rx_sd3rxp_i in 1 This is lane3 serial data_p signal of DP Rx main channel.  dp_rx_sd3rxp_i in 1 This is lane3 serial data_p signal of DP Rx main channel.  dp_rx_sd3rxp_i in 1 This is lane3 serial data_p signal of DP Rx main channel.  dp_rx_sd3rxn_i in 1 This is lane3 serial data_p signal of DP Rx main channel.  dp_rx_sd3rxn_i in 1 This is lane3 serial data_p signal of DP Rx main channel.  ddDtxp_o Out 1 This is lane1 serial data_p signal of DP Rx main channel.  dd1txp_o Out 1 This is lane1 serial data_p signal of DP Rx main channel.  dd1txp_o Out 1 This is lane1 serial data_p signal of DP Rx main channel.  dd1txp_o Out 1 This is lane2 serial data_p signal of DP Rx main channel.  dd2txp_o Out 1 This is lane2 serial data_p signal of DP Rx main channel.  dd2txp_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd2txp_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd2txp_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd_rx_aux_oe_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd_rx_aux_oe_o Out 1 This is lane3 serial data_p signal of DP Rx main channel.  dd_rx_aux_i In 1 AuX channel output. If the value is '1', the AUX output is driven, otherwise it is undriven and held at high impedance state.  dd_rx_aux_i In 1 AuX channel output.  dd_rx_aux_i In 1 External resistance for Lane 0  dd_rx_aux_i In 1 External resistance for Lane 0  dd_rx_aux_i In 1 External resistance for Lane 0  dd_refte_i In 1 Analog reference return for PMA PLL for Lane 1  dd_refte_i In 1 External resistance for Lane 1  dx_refte_i In 1 External resistance for Lane 1  dx_refte_i In 1 External resistance for Lane 1  dx_refte_i In 1 External resistance for L | dp_rx_sd1rxp_i      | In        | 1     | This is lane1 serial data_p signal of DP Rx main channel.          |

| dp_rx_sd2zn_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | dp_rx_sd1rxn_i      | In        | 1     | This is lane1 serial data_n signal of DP Rx main channel.          |

| dp_rx_sd3rxp_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | dp_rx_sd2rxp_i      | In        | 1     | This is lane2 serial data_p signal of DP Rx main channel.          |

| top m. sd3mm i In 1 This is lane3 serial data in signal of DP Rx main channel. sd0txp.o Out 1 This is lane0 serial data in signal of DP Tx main channel. sd0txp.o Out 1 This is lane0 serial data in signal of DP Tx main channel. sd1txp.o Out 1 This is lane1 serial data in signal of DP Tx main channel. sd1txp.o Out 1 This is lane1 serial data in signal of DP Tx main channel. sd1txp.o Out 1 This is lane1 serial data in signal of DP Tx main channel. sd2txp.o Out 1 This is lane2 serial data in signal of DP Tx main channel. sd2txp.o Out 1 This is lane2 serial data in signal of DP Tx main channel. sd2txp.o Out 1 This is lane2 serial data in signal of DP Tx main channel. sd3txp.o Out 1 This is lane3 serial data in signal of DP Tx main channel. sd3txp.o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 This is lane3 serial data in signal of DP Tx main channel. dip m. hpd_out_o Out 1 Aux hpd. dip m. hpd_out_o Out 1 Aux hpd. dip m. hpd. dip m. hpd. hpd. dip m.  | dp_rx_sd2rxn_i      | In        | 1     | This is lane2 serial data_n signal of DP Rx main channel.          |

| sd0tbp_o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | dp_rx_sd3rxp_i      | In        | 1     | This is lane3 serial data_p signal of DP Rx main channel.          |

| sd0tbm_o Out 1 This is lane0 serial data_n signal of DPTx main channel.  sd1txp_o Out 1 This is lane1 serial data_p signal of DPTx main channel.  sd2txp_o Out 1 This is lane1 serial data_p signal of DPTx main channel.  sd2txp_o Out 1 This is lane2 serial data_p signal of DPTx main channel.  sd2txp_o Out 1 This is lane2 serial data_p signal of DPTx main channel.  sd2txp_o Out 1 This is lane2 serial data_p signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_p signal of DPTx main channel.  sd3txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd3txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd3txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd3txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd3txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 This is lane3 serial data_n signal of DPTx main channel.  sd2txp_o Out 1 AuX channel output signal of DPTx main channel.  sd2txp_o Color of DTx main channel.  sd2txp_o Out 1 AuX channel output.  sd2txp_o Out 1 Output.  sd2txp_o Out 1 Output.  sd2txp_o Output.  sd2txp_o Output.  sd2tx | dp_rx_sd3rxn_i      | In        | 1     | This is lane3 serial data_n signal of DP Rx main channel.          |

| sd1txp_o         Out         1         This is lane1 serial data_p signal of DP Tx main channel.           sd1txn_o         Out         1         This is lane1 serial data_n signal of DP Tx main channel.           sd2txp_o         Out         1         This is lane2 serial data_n signal of DP Tx main channel.           sd2txn_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           sd3txp_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           sd3txp_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_help_out_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_help_out_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_help_out_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_help_out_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_help_out_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_help_out_o         Out         1         This is lane3 serial data_n signal of DP Tx main channel.           dp_rx_aux_o         Out         1 <td>sd0txp_o</td> <td>Out</td> <td>1</td> <td>This is lane0 serial data_p signal of DP Tx main channel.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | sd0txp_o            | Out       | 1     | This is lane0 serial data_p signal of DP Tx main channel.          |

| sd1txp_o Out 1 This is lane1 serial data_p signal of DP Tx main channel.  sd1txn_o Out 1 This is lane1 serial data_n signal of DP Tx main channel.  sd2txp_o Out 1 This is lane2 serial data_n signal of DP Tx main channel.  sd2txn_o Out 1 This is lane2 serial data_n signal of DP Tx main channel.  sd3txn_o Out 1 This is lane2 serial data_n signal of DP Tx main channel.  sd3txn_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  sd3txn_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_lnd_out_out_out_out_out_out_out_out_out_out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | sd0txn o            | Out       | 1     |                                                                    |

| sd1tm_o Out 1 This is lane1 serial data_n signal of DP Tx main channel.  sd2txp_o Out 1 This is lane2 serial data_p signal of DP Tx main channel.  sd3txp_o Out 1 This is lane2 serial data_p signal of DP Tx main channel.  sd3txp_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  sd3txp_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  sd3txp_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_aux_oo_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_aux_oo_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_aux_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | sd1txp o            | Out       | 1     |                                                                    |

| sd2txp_o Out 1 This is lane2 serial data_p signal of DP Tx main channel. sd2txn_o Out 1 This is lane2 serial data_p signal of DP Tx main channel. sd3txp_o Out 1 This is lane3 serial data_p signal of DP Tx main channel. sd3txn_o Out 1 This is lane3 serial data_p signal of DP Tx main channel. sd3txn_o Out 1 This is lane3 serial data_p signal of DP Tx main channel. dp_rx_hpd_out_o Out 1 Hot plug signal to inform DP source that DP sink is connected. (part of dp cable) dp_rx_aux_oe_o Out 1 Tri-state control for AUX channel output. If the value is '1', the AUX output is driven, otherwise it is undriven and held at high impedance state.  dp_rx_aux_o Out 1 AUX channel output.  dp_rx_aux_o Out 1 Aux channel output.  do_rx_fut_i In 1 External resistance for Lane 0  sd0_refret_i In 1 External resistance for Lane 0  sd1_refret_i In 1 External resistance for Lane 1  sd2_refret_i In 1 External resistance for Lane 2  sd3_refret_i In 1 External resistance for Lane 3  sd2_rext_i In 1 External resistance for Lane 3  sd2_rext_i In 1 External resistance for Lane 3  sd2_rext_i In 1 External resistance for Lane 3  clk_synth_locked  In 1 Video Clock PLL lock  s1_uart_rxd_i In 1 UART Rx pin to receive data  training_done_LED  Out 1 Video_coler ready_LED  dp_tx_valid_LED  Out 1 Video_coler ready_LED  dp_tx_valid_LED  Out 1 Video_coler ready_LED  Out 1 Video_coler frame invalid_LED to inform regarding frame invalid_LED  Out 1 Video_coler | sd1txn o            | Out       | 1     |                                                                    |

| sd2txn_o Out 1 This is lane2 serial data_n signal of DP Tx main channel. sd3txp_o Out 1 This is lane3 serial data_n signal of DP Tx main channel. sd3txn_o Out 1 This is lane3 serial data_n signal of DP Tx main channel. sd3txn_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal of DP Tx main channel.  This is lane3 serial data_n signal or DP Tx main channel.  This is lane3 serial data_n signal or DP Tx main channel.  This is lane3 serial | <del>-</del>        | Out       | 1     |                                                                    |

| sd3txp_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  sd3txn_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 This is lane3 serial data_p signal of DP Tx main channel.  dp_rx_hpd_out_o Out 1 Tri-state control for AUX channel output. If the value is '1', the AUX output is driven, otherwise it is undriven and held at high impedance state.  dp_rx_aux_o Out 1 AUX channel input.  dp_rx_aux_o Out 1 AUX channel input.  dp_rx_aux_o Out 1 ANAlog reference return for PMA PLL for Lane 0  sd0_rext_i In 1 External resistance for Lane 0  sd1_refret_i In 1 Analog reference return for PMA PLL for Lane 1  sd1_rext_i In 1 External resistance for Lane 1  sd2_rext_i In 1 External resistance for Lane 1  sd2_rext_i In 1 External resistance for Lane 2  sd2_rext_i In 1 External resistance for Lane 2  sd2_rext_i In 1 External resistance for Lane 2  sd3_refret_i In 1 Analog reference return for PMA PLL for Lane 2  sd3_rext_i In 1 External resistance for Lane 3  sd3_rext_i In 1 External resistance for Lane 3  sd3_rext_i In 1 External resistance for Lane 3  sd3_rext_i In 1 Uxideo Clock PLL lock  gt_clk_LOCK In 1 External resistance for Lane 3  clk_synth_locked In 1 Video Clock PLL lock  gt_clk_LOCK In 1 PX Reference Clock PLL lock  gt_clk_LOCK In 1 PX Reference Clock PLL lock  gt_clk_LOCK In 1 Uxideo_scaler ready_LED  Out 1 Video_scaler frame invalid LED to inform regarding frame invalidity.  clk_rec_running_led  Out 1 Clock running status_LED                                                                                   | · <del>-</del>      | Out       | 1     |                                                                    |

| sd3txn_o dp_rx_hpd_out_o dp_rx |                     |           | 1     |                                                                    |

| dp_rx_hpd_out_o  Out 1 Hot plug signal to inform DP source that DP sink is connected. (part of dp cable)  dp_rx_aux_oe_o  Out 1 Tri-state control for AUX channel output. If the value is '1', the AUX output is driven, otherwise it is undriven and held at high impedance state.  dp_rx_aux_i In 1 AUX channel input.  dp_rx_aux_o Out 1 AUX channel output.  sdo_refret_i In 1 Analog reference return for PMA PLL for Lane 0  sdo_rext_i In 1 External resistance for Lane 0  sdd_rext_i In 1 External resistance for Lane 0  sdd_rext_i In 1 External resistance for Lane 1  sdd_rext_i In 1 External resistance for Lane 1  sd2_refret_j In 1 Analog reference return for PMA PLL for Lane 1  sd2_refret_j In 1 External resistance for Lane 2  sd2_rext_i In 1 External resistance for Lane 2  sd3_refret_j In 1 External resistance for Lane 3  sd3_rext_j In 1 External resistance for Lane 3  sd4_rext_j In 1 External resistance for Lane 3  sd4_rext_j In 1 External resistance for Lane 3  sd4_rext_j In 1 External resistance for Lane 3  sd5_rext_j In 1 External resistance for Lane 3  sd6_rext_j In 1 External resistance for Lane 3  sd7_rext_j In 1 In 1 External resistance for Lane 3  sd7_rext_j In 1 In 1 External resistance for Lane 3  sd8_rext_j In 1 In 1 External resistance for Lane 3  sd7_rext_j In 1 In 1 External resistance for Lane 2  sd7_rext_j In 1 In 1 In 1 External resistance for Lane 2  sd8_rext_j In 1 In                                                                                                                              |                     |           | 1     |                                                                    |

| dp_rx_aux_oe_o  Out  1 Tri-state control for AUX channel output. If the value is '1', the AUX output is driven, otherwise it is undriven and held at high impedance state.  dp_rx_aux_i  In  1 AUX channel input.  dp_rx_aux_o  Out  1 AUX channel output.  do_rex_eux_o  out  1 External resistance for Lane 0  sd1_refret_i  In  1 Analog reference return for PMA PLL for Lane 1  sd1_rext_i  In  1 External resistance for Lane 1  sd2_rext_i  In  1 Analog reference return for PMA PLL for Lane 2  sd2_rext_i  In  1 External resistance for Lane 2  sd3_refret_i  In  1 Analog reference return for PMA PLL for Lane 2  sd3_refret_i  In  1 External resistance for Lane 2  sd3_refret_i  In  1 External resistance for Lane 3  clk_synth_locked  In  1 Video Clock PLL lock  st_uart_rxd_i  In  1 External resistance for Lane 3  clk_synth_locked  In  1 Video Clock PLL lock  st_uart_rxd_i  In  1 UART Rx pin to receive data  training_done_LED  Out  1 Video scaler ready_LED  Out  1 Video scaler ready_LED  Out  1 PTx valid LED  HPD_LED  Out  1 Video Clock PLL lock LED  clk_synth_lock_led  Out  1 Video Clock PLL lock LED  clk_synth_lock_led  Out  1 Video Clock PLL lock LED  clc_scd  Out  1 Video Scaler freame invalid LED to inform regarding frame invalid_lo  invalidity.  clk_rec_running_led  Out  1 Video Clock PLL lock LED  Clock running status LED  PLL_LOCK  Out  1 PLL locked LED                                                                                                                                                                                                                                                                                                                                                                                                  |                     |           |       |                                                                    |

| AUX output is driven, otherwise it is undriven and held at high impedance state.  dp_rx_aux_0  Out 1 AUX channel input. dp_rx_aux_0  Out 1 AUX channel output.  sd0_refret_i  In 1 External resistance for Lane 0  sd0_rest_i  In 1 Analog reference return for PMA PLL for Lane 0  sd0_rest_i  In 1 External resistance for Lane 0  sd1_rest_i  In 1 Analog reference return for PMA PLL for Lane 1  sd1_rest_i  In 1 External resistance for Lane 1  sd2_refret_i  In 1 Analog reference return for PMA PLL for Lane 1  sd2_refret_i  In 1 External resistance for Lane 2  sd3_rest_i  In 1 External resistance for Lane 2  sd3_rest_i  In 1 External resistance for Lane 2  sd3_rest_i  In 1 External resistance for Lane 3  sd3_rest_i  In 1 UART Rx pin to receive data  training done_LED  Out 1 This is to connect to an LED to indicate dp_tx_training_done  ip_scaler_ready_LED  Out 1 Video_scaler ready LED  Out 1 DP Tx valid LED  HPD_LED  Out 1 Hot plug detect LED  clk_synth_lock_led  Out 1 Video Clock PLL lock LED  i2c_scd1  Out 1 Video Clock PLL lock LED  i2c_scd2  Out 1 1 I2C serial data  i2c_sel  Out 1 1 I2C serial data  i2c_sel  Out 1 1 I2C serial data  i2c_sel  Out 1 Video Scaler frame invalid LED to inform regarding frame invalid_o  clk_rec_running_led  Out 1 Video Scaler frame invalid LED to inform regarding frame invalid_to.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | apnpa_oat_o         | Cut       | _     | , 5 5                                                              |

| AUX output is driven, otherwise it is undriven and held at high impedance state.  dp_rx_aux_0  Out 1 AUX channel input. dp_rx_aux_0  Out 1 AUX channel output.  sd0_refret_i  In 1 External resistance for Lane 0  sd0_rest_i  In 1 Analog reference return for PMA PLL for Lane 0  sd0_rest_i  In 1 External resistance for Lane 0  sd1_rest_i  In 1 Analog reference return for PMA PLL for Lane 1  sd1_rest_i  In 1 External resistance for Lane 1  sd2_refret_i  In 1 Analog reference return for PMA PLL for Lane 1  sd2_refret_i  In 1 External resistance for Lane 2  sd3_rest_i  In 1 External resistance for Lane 2  sd3_rest_i  In 1 External resistance for Lane 2  sd3_rest_i  In 1 External resistance for Lane 3  sd3_rest_i  In 1 UART Rx pin to receive data  training done_LED  Out 1 This is to connect to an LED to indicate dp_tx_training_done  ip_scaler_ready_LED  Out 1 Video_scaler ready LED  Out 1 DP Tx valid LED  HPD_LED  Out 1 Hot plug detect LED  clk_synth_lock_led  Out 1 Video Clock PLL lock LED  i2c_scd1  Out 1 Video Clock PLL lock LED  i2c_scd2  Out 1 1 I2C serial data  i2c_sel  Out 1 1 I2C serial data  i2c_sel  Out 1 1 I2C serial data  i2c_sel  Out 1 Video Scaler frame invalid LED to inform regarding frame invalid_o  clk_rec_running_led  Out 1 Video Scaler frame invalid LED to inform regarding frame invalid_to.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dp rx aux oe o      | Out       | 1     | Tri-state control for AUX channel output. If the value is '1', the |

| dp_rx_aux_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |           |       | · ·                                                                |

| dp_rx_aux_o  dq_refret_i  dp_rx_aux_o  dd_refret_i  dp_rx_aux_o  dd_rext_i  dp_rx_aux_o  dp_rx_ |                     |           |       | impedance state.                                                   |

| sd0_refret_i In 1 Analog reference return for PMA PLL for Lane 0 sd0_rext_i In 1 External resistance for Lane 0 sd1_refret_i In 1 Analog reference return for PMA PLL for Lane 1 sd1_refret_i In 1 Analog reference return for PMA PLL for Lane 1 sd2_rext_i In 1 Analog reference return for PMA PLL for Lane 2 sd2_rext_i In 1 Analog reference return for PMA PLL for Lane 2 sd3_refret_i In 1 External resistance for Lane 2 sd3_refret_i In 1 Analog reference return for PMA PLL for Lane 3 sd3_rext_i In 1 External resistance for Lane 3 cdk_synth_locked In 1 Video Clock PLL lock gt_clk_LOCK In 1 Reference Clock PLL lock s1_uart_rxd_i In 1 UART Rx pin to receive data training_done_LED Out 1 This is to connect to an LED to indicate dp_tx_training_done ip_scaler_ready_LED Out 1 Video_scaler ready_LED dp_tx_valid_LED Out 1 DP_Tx valid_LED HPD_LED Out 1 Video Clock PLL lock LED clk_synth_lock_led Out 1 Video Clock PLL lock LED clk_synth_lock_led Out 1 Video Clock PLL lock LED clk_synth_lock_led Out 1 Video Clock PLL lock LED clc_scal Out 1 Li2C serial data li2c_scal Out 1 Li2C serial data li2c_scal Out 1 Reference Clock PLL lock LED ref_clk_PLL_LOCK Out 1 Reference Clock PLL lock LED clk_serial clock LED clk_rec_running_led Out 1 Clock running status LED PLL_LOCK Out 1 PLL locked LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | dp_rx_aux_i         | In        | 1     | AUX channel input.                                                 |

| sdO_rext_i     In     1     External resistance for Lane 0       sd1_refret_i     In     1     Analog reference return for PMA PLL for Lane 1       sd1_rext_i     In     1     External resistance for Lane 1       sd2_refret_i     In     1     Analog reference return for PMA PLL for Lane 2       sd3_refret_i     In     1     External resistance for Lane 2       sd3_rext_i     In     1     External resistance for Lane 3       sd3_rext_i     In     1     External resistance for Lane 3       clk_synth_locked     In     1     Video Clock PLL lock       gt_clk_LOCK     In     1     Reference Clock PLL lock       s1_uart_rxd_i     In     1     UART Rx pin to receive data       training_done_LED     Out     1     This is to connect to an LED to indicate dp_tx_training_done       ip_scaler_ready_LED     Out     1     Video_scaler ready LED       dp_tx_valid_LED     Out     1     DP Tx valid LED       HPD_LED     Out     1     Hot plug detect LED       clk_synth_lock_led     Out     1     Video Clock PLL lock LED       cl2c_scl     Out     1     1/2C serial data       i2c_scl     Out     1     1/2C serial data       i2c_sel     Out     1     1/2C select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dp_rx_aux_o         | Out       | 1     | AUX channel output.                                                |

| sd1_refret_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sd0_refret_i        | In        | 1     | Analog reference return for PMA PLL for Lane 0                     |

| sd1_rext_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sd0_rext_i          | In        | 1     | External resistance for Lane 0                                     |

| sd2_refret_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sd1_refret_i        | In        | 1     | Analog reference return for PMA PLL for Lane 1                     |

| sd2_rext_i     In     1     External resistance for Lane 2       sd3_refret_i     In     1     Analog reference return for PMA PLL for Lane 3       sd3_rext_i     In     1     External resistance for Lane 3       clk_synth_locked     In     1     Video Clock PLL lock       gt_clk_LOCK     In     1     Reference Clock PLL lock       s1_uart_rxd_i     In     1     UART Rx pin to receive data       training_done_LED     Out     1     Video_scaler ready LED to indicate dp_tx_training_done       ip_scaler_ready_LED     Out     1     Video_scaler ready LED       dp_tx_valid_LED     Out     1     DP Tx valid LED       HPD_LED     Out     1     Hot plug detect LED       clk_synth_lock_led     Out     1     Video Clock PLL lock LED       i2c_config_done     Out     1     I2C serial clock       i2c_scl     Out     1     I2C serial clock       i2c_sel     Out     1     I2C select       ref_clk_PLL_LOCK     Out     1     Reference Clock PLL lock LED       frame_invalid_o     Out     1     Video Scaler frame invalid LED to inform regarding frame invalid/led.       clk_rec_running_led     Out     1     Clock running status LED       PLL_LOCK     Out     1     PLL l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | sd1_rext_i          | In        | 1     | External resistance for Lane 1                                     |

| sd3_refret_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sd2_refret_i        | In        | 1     | Analog reference return for PMA PLL for Lane 2                     |

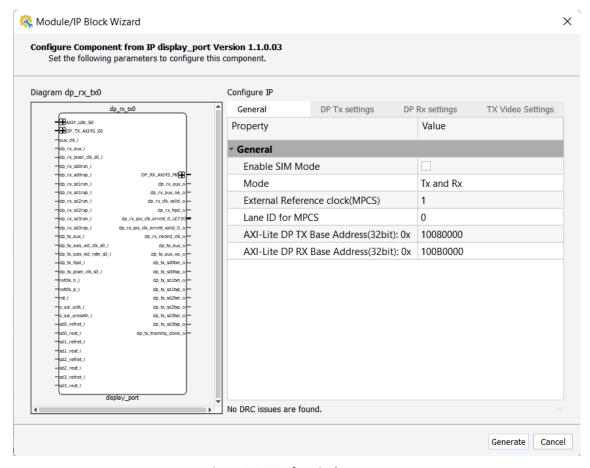

| sd3_rext_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sd2_rext_i          | In        | 1     | External resistance for Lane 2                                     |