# MachXO5-NX and L-ASC10 Platform Power Management Using RISC-V Demo

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Content  | TS                                                |    |

|----------|---------------------------------------------------|----|

| Acronyr  | ms in This Document                               | 7  |

| 1. Int   | troduction                                        | 8  |

| 1.1.     | Overview                                          | 8  |

| 2. De    | emo Setup                                         | 11 |

| 2.1.     | Software Requirements                             | 11 |

| 2.2.     | Compressed File Contents                          |    |

| 2.3.     | Hardware Requirements                             | 12 |

| 3. Ini   | tial Step by Step Design Flow                     | 14 |

| 3.1.     | Creating a new project in the Propel Builder      | 14 |

| 3.2.     | Adding I <sup>2</sup> C Master IP to the Design   | 16 |

| 3.3.     | Modifying the GPIO component                      | 22 |

| 3.4.     | Adding and Modifying the Clocks                   | 24 |

| 3.5.     | Updating the RISC-V IP                            |    |

| 3.6.     | Checking the Memory Map                           | 27 |

| 3.7.     | Generating the SOC RTL                            | 27 |

| 3.8.     | Creating the Platform Manager 2 IP                | 28 |

| 3.9.     | Building the MachXO5-NX Top Level Design          |    |

| 3.10.    | Starting the Propel SDK                           | 40 |

| 3.11.    |                                                   |    |

| 3.12.    | Writing Code to Interface with Platform Manager 2 | 45 |

| 3.13.    |                                                   |    |

| 3.14.    | Loading the Firmware into Memory                  | 49 |

| 3.15.    | Running the Demo                                  | 51 |

|          | mmary                                             |    |

|          | dix A                                             |    |

| Firmv    | ware APIs                                         | 56 |

|          | ternal Firmware APIs                              |    |

|          | ternal Firmware APIs                              |    |

|          | nces                                              |    |

| Technic  | cal Support Assistance                            | 62 |

| Revision | n History                                         | 63 |

# **Figures**

| Figure 1.1. MachXO5-NX and (3) L-ASC10s Project Flow Block Diagram       | 8  |

|--------------------------------------------------------------------------|----|

| Figure 1.2. MachXO5-NX and (3) L-ASC10s Demo Block Diagram               | 10 |

| Figure 2.1. MachXO5-NX and (3) L-ASC10s Demo Hardware                    | 13 |

| Figure 3.1. Propel Builder – Project Name                                | 14 |

| Figure 3.2. Propel Builder – Device and Template                         | 14 |

| Figure 3.3. Propel Builder – Summary                                     | 15 |

| Figure 3.4. Propel Builder – Initial Schematic                           | 15 |

| Figure 3.5. Propel Builder – I <sup>2</sup> C IP on Server               | 16 |

| Figure 3.6. Propel Builder – I <sup>2</sup> C IP License                 | 16 |

| Figure 3.7. Propel Builder – Instantiate I <sup>2</sup> C Block          | 17 |

| Figure 3.8. Propel Builder – Configure I <sup>2</sup> C IP               | 17 |

| Figure 3.9. Propel Builder – Finish                                      | 18 |

| Figure 3.10. Propel Builder – Instance Name                              | 18 |

| Figure 3.11. Propel Builder – I <sup>2</sup> C Master added to Schematic | 19 |

| Figure 3.12. Propel Builder – Adding Slave to APB                        | 20 |

| Figure 3.13. Propel Builder – Connecting I <sup>2</sup> C IP to APB      | 20 |

| Figure 3.14. Propel Builder – Adding a Port                              |    |

| Figure 3.15. Propel Builder – Adding ptm_scl Port                        | 21 |

| Figure 3.16. Propel Builder – I <sup>2</sup> C Ports Connected           |    |

| Figure 3.17. Propel Builder – GPIO IP Configuration                      |    |

| Figure 3.18. Propel Builder – GPIO Auto Connect                          |    |

| Figure 3.19. Propel Builder – Renaming GPIO Port                         |    |

| Figure 3.20. Propel Builder – Oscillator IP Configuration                |    |

| Figure 3.21. Propel Builder – PLL IP Configuration                       |    |

| Figure 3.22. Propel Builder – Clock Ports                                | 26 |

| Figure 3.23. Propel Builder – Update RISCV IP                            |    |

| Figure 3.24. Propel Builder – Memory Map                                 |    |

| Figure 3.25. Propel Builder – Generating the Design                      |    |

| Figure 3.26. Lattice Diamond – New Platform Designer Project             |    |

| Figure 3.27. Lattice Diamond – ASC Options                               |    |

| Figure 3.28. Lattice Diamond – Global Device Options                     |    |

| Figure 3.29. Lattice Diamond – Disable EFB Logic                         |    |

| Figure 3.30. Platform Designer – V, I, T Fault Logging Enabled           |    |

| Figure 3.31. Platform Designer – Fault Node Supervisory Equation         |    |

| Figure 3.32. Platform Designer – Compiling the IP                        |    |

| Figure 3.33. Radiant – MachXO5_ASC10_Demo Module                         |    |

| Figure 3.34. Radiant – Input Files, Add Existing File                    |    |

| Figure 3.35. Radiant – Input File List                                   | 37 |

| Figure 3.36. Radiant – Platform Manager 2 IP instantiation               |    |

| Figure 3.37. Radiant – SOC Instantiation                                 |    |

| Figure 3.38. Radiant – Top Level Ports                                   |    |

| Figure 3.39. Propel SDK – New Project Workspace                          |    |

| Figure 3.40. Propel SDK – New Project System and BSP                     | 40 |

| Figure 3.41. Propel SDK – New Project C++                                |    |

| Figure 3.42. Propel SDK – New Project Name                               |    |

| Figure 3.43. Propel SDK – New Project Tool Settings                      |    |

| Figure 3.44. Propel SDK – IDE main.c File                                |    |

| Figure 3.45. Propel SDK – Main DIP Switch Options                        |    |

| Figure 3.46. Propel SDK – Main Platform Manager 2 Start                  |    |

| Figure 3.47. Propel SDK – Main Loop                                      |    |

| Figure 3.48. Propel SDK – Main Print Faults                              |    |

| Figure 3.49. Propel SDK – ptm_asc.h, Defines PPL_IDE                     |    |

|                                                                          | _  |

| Figure 3.50. Propel SDK – ptm_asc.h, Structures                        | 46 |

|------------------------------------------------------------------------|----|

| Figure 3.50. Propel SDK – ptm_asc.h, Structures                        | 47 |

| Figure 3.52. Propel SDK – ptm_asc.c, Configuration includes            | 47 |

| Figure 3.53. Propel SDK – ptm_asc0_data.h                              | 48 |

| Figure 3.54. Command Prompt – ASC_Hex_Reader                           | 48 |

| Figure 3.55. Propel Builder – System Memory Initialization             | 49 |

| Figure 3.56. Radiant ECO Editor – Icon                                 |    |

| Figure 3.57. Radiant ECO Editor – Memory Initialization Tab            |    |

| Figure 3.58. Radiant ECO Editor – Choose File                          | 50 |

| Figure 3.59. Radiant ECO Editor – Settings                             |    |

| Figure 3.60. Radiant ECO Editor – Save                                 | 51 |

| Figure 3.61. Radiant ECO Editor – Exporting Files                      | 51 |

| Figure 3.62. Radiant ECO Editor – TCL Command                          | 51 |

| Figure 3.63. Propel SDK Terminal – Demo Running Power Sequence         | 52 |

| Figure 3.64. Propel SDK Terminal – Demo Running Configure and Sequence | 53 |

| Figure 3.65. Propel SDK Terminal – Demo Running Program and Sequence   | 54 |

## **Tables**

| Table 3.1. Platform Designer – VMON Trip Points                    | 31 |

|--------------------------------------------------------------------|----|

| Table 3.2. Platform Designer – SM1: ASC1 Power Sequence            |    |

| Table 3.3. Platform Designer – SM3: Fault Logger Sequence          | 34 |

| Table 3.4. Platform Designer – SM4: Fault Display on 7-segment LED | 34 |

| Table 3.5. Platform Designer – User Defined Ports and Nodes        | 35 |

| Table A.1. MachXO5-NX and L-ASC10 Demo Resource Utilization        | 55 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym   | Definition                                                          |

|-----------|---------------------------------------------------------------------|

| AHBL      | Advanced High Performance Bus Light                                 |

| APB       | Advanced Peripheral Bus                                             |

| API       | Application Programming Interface                                   |

| ASC       | Analog Sense and Control                                            |

| BSP       | Board Support Package                                               |

| СРИ       | Central Processing Unit                                             |

| DSP       | Digital Signal Processing                                           |

| EBR       | Embedded Block RAM                                                  |

| ECO       | Engineering Change Order                                            |

| EFB       | Embedded Function Block                                             |

| GPIO      | General Purpose Input / Output                                      |

| HDL       | Hardware Description Language                                       |

| HVOUT     | ASC10 High Voltage Output (Charge Pump Output)                      |

| IMON      | ASC10 Current Monitor                                               |

| IP        | Intellectual Property                                               |

| LED       | Light Emitting Diode                                                |

| LUT       | Look Up Table                                                       |

| LUT4      | LUT with by-4 Architecture                                          |

| PFU       | Programmable Function Unit                                          |

| PLL       | Phase Locked Loop                                                   |

| PTM       | Platform Manager                                                    |

| PTM2      | Platform Manager Version 2                                          |

| RAM       | Random Access Memory                                                |

| RISC-V    | Reduced Instruction Set Computer – Version 5                        |

| SM0 – SM4 | State Machine 0 – State Machine 4 (Logic view in Platform Designer) |

| SDK       | Software Development Kit                                            |

| SOC       | System On a Chip                                                    |

| TMON      | ASC10 Temperature Monitor                                           |

| VMON      | ASC10 Voltage Monitor                                               |

#### 1. Introduction

This Demo Design and User Guide shows how to combine Lattice's Analog Sense and Control (L-ASC10) devices with Lattice's MachXO5-NX FPGA. The Demo Design is a centralized Platform Management system using three L-ASC10 devices. The Demo Design has three separate power sequencers (one for each L-ASC10) that are cascaded in both powering-up and powering-down. The RISC-V in this Demo Design configures the L-ASC10 devices over an I<sup>2</sup>C bus at initial power up; this illustrates how multiple boot and remote updates can be supported. The firmware APIs interface with the centralized Platform Manager to enable both powering-up and powering-down along with fault monitoring.

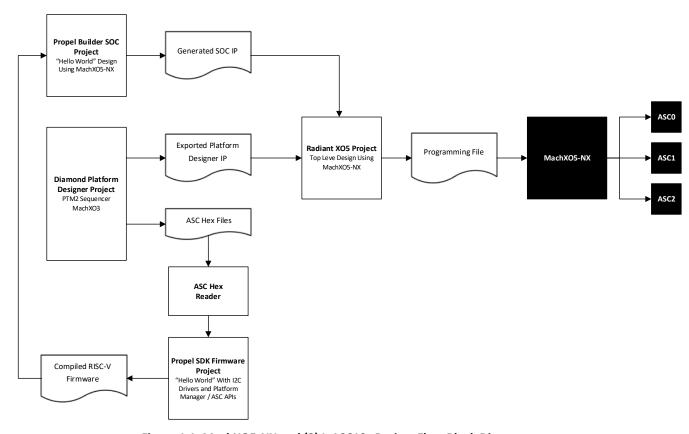

This User Guide steps thru the several software tools used in building the Demo Design, those tools include; Propel Builder, Propel SDK, Diamond's Platform Designer, Radiant, and ASC\_HEX\_Reader.exe. Propel Builder creates the RISC-V SOC for the MachXO5-NX device. Propel SDK builds the firmware for the RISC-V CPU. Platform Designer in Diamond builds the power sequences and generates the L-ASC10 HEX file with the analog settings; it also exports the RTL that embodies the three-wire interface for each L-ASC10 and the centralized power sequencer. Radiant combines the RTL generated from Propel Builder and Platform Designer along with the firmware from Propel SDK to generate a single programming file for the MachXO5-NX. The ASC\_HEX\_Reader.exe is a utility that converts the L-ASC10 HEX programming file into a C=type data array file for inclusion in the firmware.

#### 1.1. Overview

This User Guide describes the MachXO5-NX and (3) L-ASC10s demo project. Figure 1.1 illustrates both the project block diagram and a block diagram of the design flow. The design flow for a project like this one is not a linear flow; rather it can be a bouncing back and forth from several tools to achieve a final system design.

Figure 1.1. MachXO5-NX and (3) L-ASC10s Project Flow Block Diagram

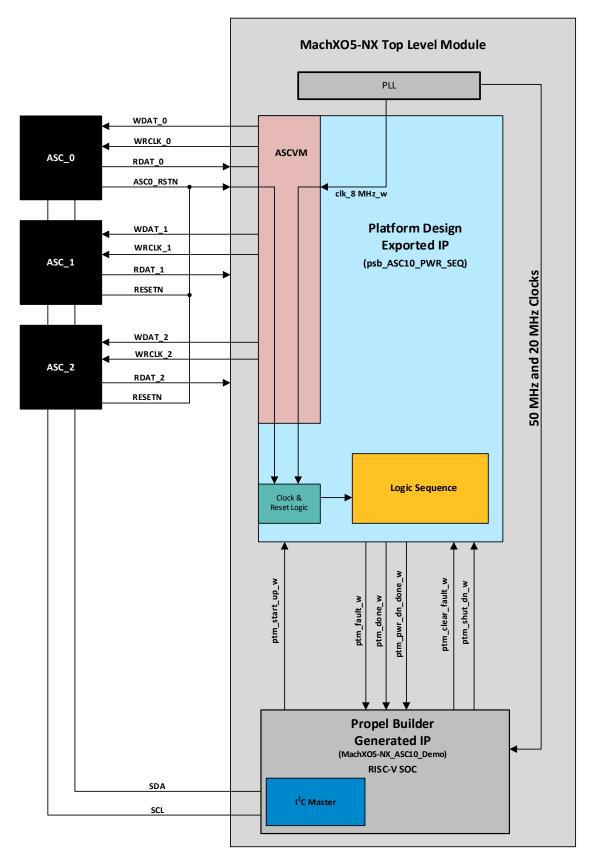

A more detailed diagram of the demo project is provided in Figure 1.2. Here we can see the handshaking connections between the Platform Manager 2 IP and the RISC-V system on a chip (SOC) design. It also shows the I<sup>2</sup>C bus connecting all three L-ASC10s to the I<sup>2</sup>C Master that is controlled by the RISC-V firmware. Three separate ASC-I/F are shown, one for each L-ASC10. However, the RESETN pins are tied together for a single mandatory reset input to the MachXO5-NX; so that the Platform Manager 2 logic cannot start until all three have powered up. This is a high-level block diagram, the details of which are provided in the sections that follow.

Figure 1.2. MachXO5-NX and (3) L-ASC10s Demo Block Diagram

## 2. Demo Setup

This section describes the demo setup.

#### 2.1. Software Requirements

- Lattice Propel Builder version 2.2.2207251517

- Is a graphical interface that is used to connect various IP modules to build a system on a chip (SOC). It generates logic and firmware files for subsequent tool use.

- Lattice Propel version 2.2.22075251517

- Is a software development kit (SDK) that is used to write and compile C-code firmware that will execute on the RISC-V part of the SOC. This tool also contains a terminal view to monitor output from the firmware thru the UART interface.

- Lattice Diamond version 3.12.1.454 with Patch Version 131140

- The Platform Designer tool within Diamond generates the Platform Manager 2 IP to sense and control the system thru the L-ASC10 devices. The Patch Version 131140 enables exporting the RTL and analog settings from the Platform Designer tool.

- Lattice L-ASC10 HEX File Reader version 2.0

- The executable named ASC\_Hex\_Reader.exe is run in a Command Prompt window to convert the L-ASC10 programming (.hex) file, generated from the Platform Designer tool, into a C-type unsigned char data array file that can be included into the RISC-V firmware.

- Lattice Radiant version 2.3

- This software tool combines all the RTL and firmware to generate a single programming file for the MaxhXO5-NX.

- Lattice Radiant Programmer version 2.3

- This software utility programs the MachXO5-NX evaluation board to verify and debug the demo design.

#### 2.2. Compressed File Contents

When the MachXO5\_ASC10\_Demo.zip file is unzipped to the root "C:" drive, many folders and files will be available. Here is a short list and description of the more significant folders and files:

The demo project root folder:

C:\MachXO5 ASC10 Demo

Diamond 3.12 Platform Manager 2 Project File:

C:\MachXO5 ASC10 Demo \ASC10 PWR SEQ.ldf

Diamond 3.12 Platform Manager 2 Project Folder:

C:\MachXO5 ASC10 Demo \Diamond

Exported Platform Manager 2 IP Folder:

C:\MachXO5\_ASC10\_Demo \ASC10\_PWR\_SEQ\_IP

ASC HEX Reader Executable file:

C:\MachXO5\_ASC10\_Demo \ASC10\_PWR\_SEQ\_IP\L\_ASC10\ASC\_HEX\_Reader.exe

Radiant 3.2 Project File:

C:\MachXO5\_ASC10\_Demo \MachXO5\_ASC10\_Demo.rdf

Radiant 3.2 Project Folder:

C:\MachXO5\_ASC10\_Demo\Radiant

Radiant 3.2 Programming File:

C:\MachXO5\_ASC10\_Demo\Radiant\MachXO5\_ASC10\_Demo\_Radiant.bit

Propel Builder 2.2 Project Folder:

C:\MachXO5\_ASC10\_Demo\Propel

Propel Builder 2.2 Project File:

C:\MachXO5 ASC10 Demo\Propel\MachXO5 ASC10 Demo\MachXO5 ASC10 Demo.sbx

Propel 2.2 SDK Workspace Folder:

C:\MachXO5\_ASC10\_Demo\PPL\_Workspace

Platform Manager 2 API Source Folder:

C:\MachXO5\_ASC10\_Demo\PPL\_Workspace/MachXO5\_ASC10\_Demo/src

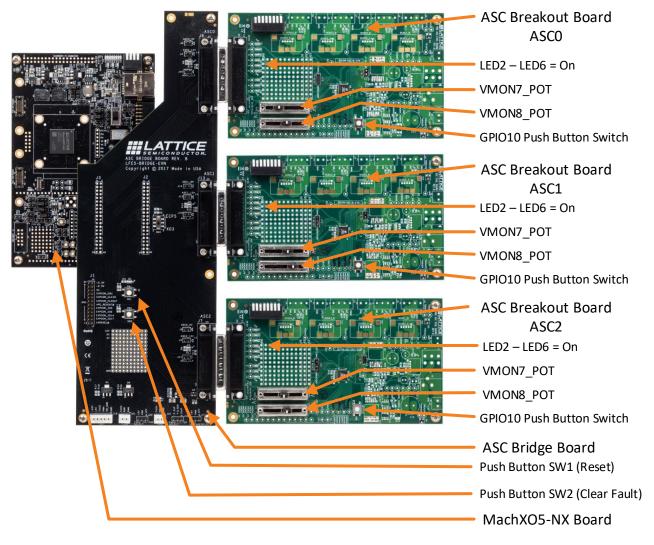

#### 2.3. Hardware Requirements

The following list of hardware is required to run this demo design and Figure 2.1 shows the actual hardware running the demo design. Note the VMON slider POTs in different locations; this will be discussed in more detail in later sections.

- MachXO5-NX Development Board

- ASC Bridge Board

- 3x ASC Breakout Boards

- 2x USB cables

- 12 V Wall wart (power supply)

Figure 2.1. MachXO5-NX and (3) L-ASC10s Demo Hardware

# 3. Initial Step by Step Design Flow

This is just one example of a flow to start this demo design. A project like this could also start from an existing Platform Manager 2 design, RISC-V firmware, or MachXO5-NX SOC design. Also, this step-by-step flow combines several iterations of the build, program, and test process that were part of the demo development. For example, after the whole project was initially built in Radiant, the number of GPIO lines in the Propel Builder component was increased from eight to ten, and later to 11 in separate build cycles.

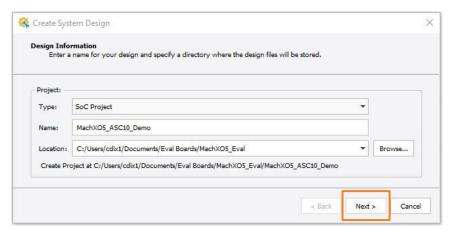

#### 3.1. Creating a new project in the Propel Builder

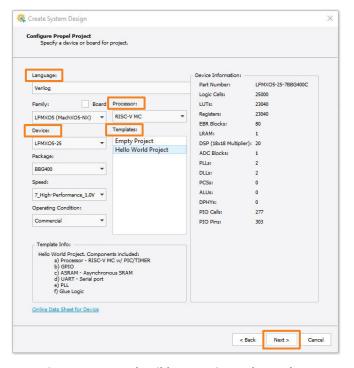

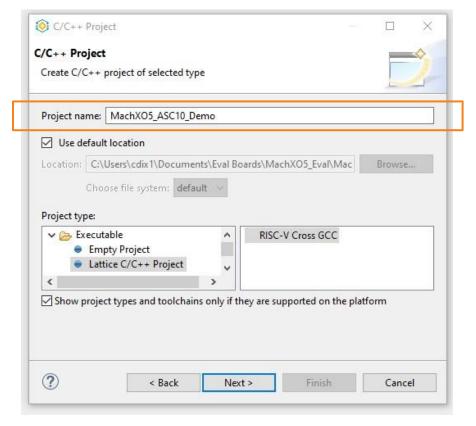

1. From the Propel Builder menu, click **File->New Design** the **Design Information** window will appear, as shown in Figure 3.1. Select the project type and fill in the name and path then click **Next**.

Figure 3.1. Propel Builder - Project Name

The Configure Propel Project window will be displayed, as shown in Figure 3.2. In this window, select the Language, Device, Processor, and Template then click Next.

Figure 3.2. Propel Builder – Device and Template

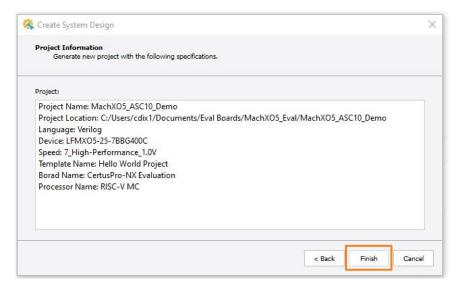

3. The **Project Information** window will appear, as shown in Figure 3.3. To summarize the project click **Finish** to generate the project.

Figure 3.3. Propel Builder - Summary

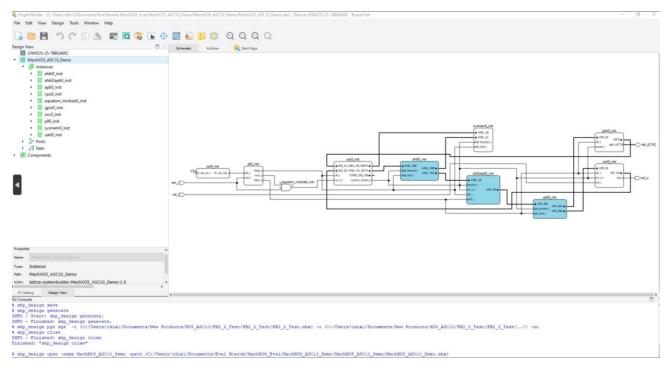

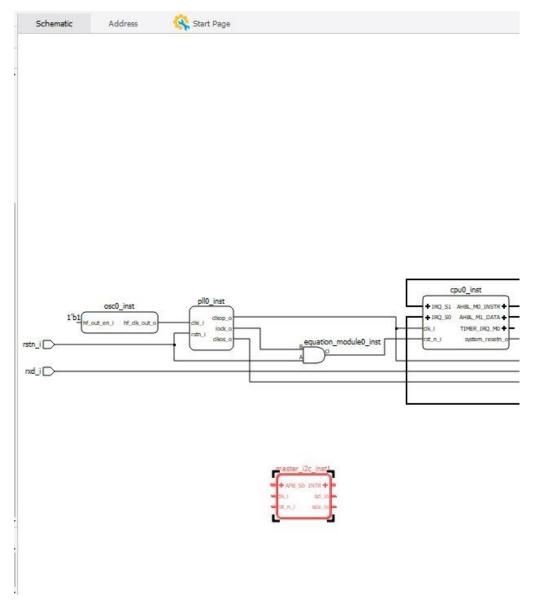

4. The Propel Builder will now display the SOC high-level schematic, as shown in Figure 3.4.

Figure 3.4. Propel Builder – Initial Schematic

#### 3.2. Adding I<sup>2</sup>C Master IP to the Design

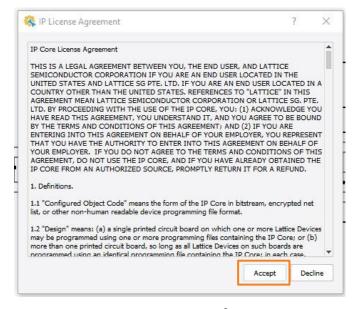

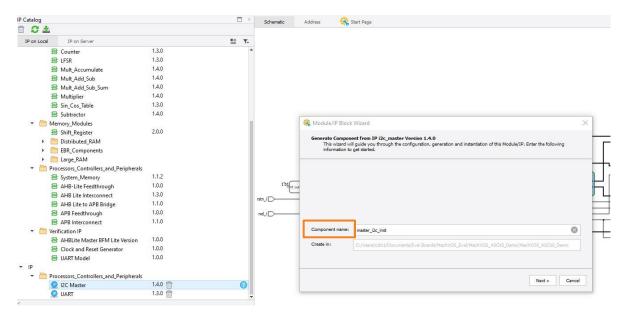

If you don't have the I<sup>2</sup>C Master IP in the IP on Local tab (under the IP Catalog), do the following steps:

1. Click on the IP on Server tab and find the I<sup>2</sup>C Master in the list, as shown in Figure 3.5. and click to download it.

Figure 3.5. Propel Builder – I<sup>2</sup>C IP on Server

A license agreement will be appear as shown in Figure 3.6. Click Accept to install the I<sup>2</sup>C Master IP.

Figure 3.6. Propel Builder – I<sup>2</sup>C IP License

© 2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

3. The Propel Builder will ask for a **Component Name** for the I<sup>2</sup>C Master, as shown in Figure 3.7.

Figure 3.7. Propel Builder – Instantiate I<sup>2</sup>C Block

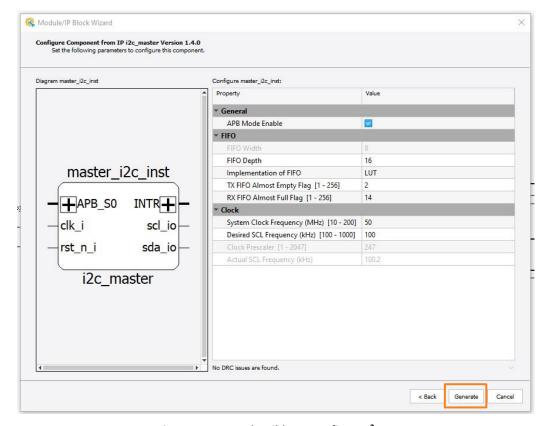

The IP configuration window will appear as shown Figure 3.8. Edit the settings and click Generate.

Figure 3.8. Propel Builder - Configure I<sup>2</sup>C IP

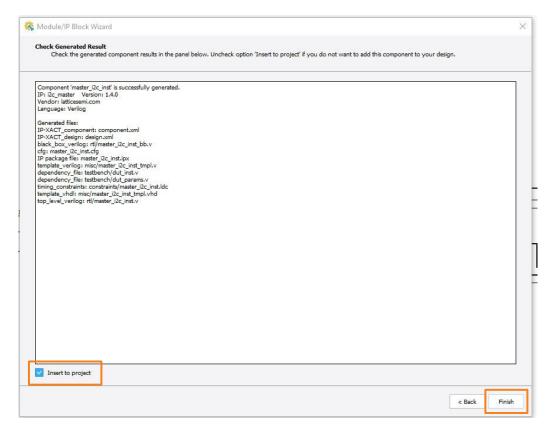

5. Click Finish and ensure the Insert to project checkbox is ticked, as shown in Figure 3.9.

Figure 3.9. Propel Builder - Finish

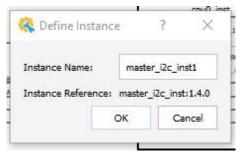

6. The Propel Builder will request a name for the instance of the I<sup>2</sup>C Master IP, as shown in Figure 3.10.

Figure 3.10. Propel Builder - Instance Name

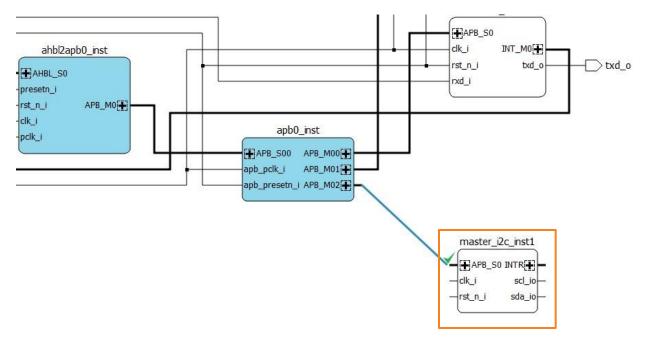

7. The Propel Builder will drop the unconnected I<sup>2</sup>C Master component on the schematic, as shown in Figure 3.11.

Figure 3.11. Propel Builder – I<sup>2</sup>C Master added to Schematic

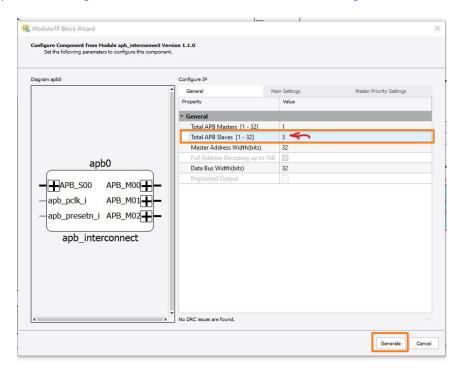

8. To connect the I<sup>2</sup>C Master to the SOC we need to add a slave connection to the APB Interconnect. Double-click on the APB component to change the Total APB Slaves from 2 to 3, as shown in Figure 3.12 then click **Generate**.

Figure 3.12. Propel Builder - Adding Slave to APB

9. Click and drag the I<sup>2</sup>C Master component to the right side of the schematic. Then click on the APB\_M02 port and drag a connection to the APB\_S0 port of the I<sup>2</sup>C Master component, as shown in Figure 3.13. Note the green checkmark indicates the width and direction of the ports match and is OK to connect the two.

Figure 3.13. Propel Builder - Connecting I<sup>2</sup>C IP to APB

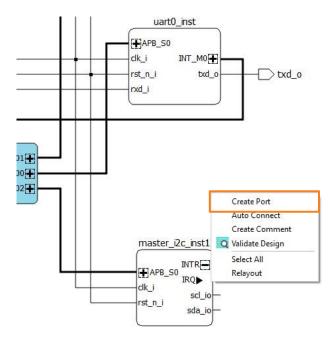

10. In a similar manner, connect the clk\_i and rst\_n\_i ports of the I<sup>2</sup>C Master to the existing nets. Next, right-click in a blank area of the schematic to open the pop-up menu, as shown in Figure 3.14, and select **Create Port.**

Figure 3.14. Propel Builder - Adding a Port

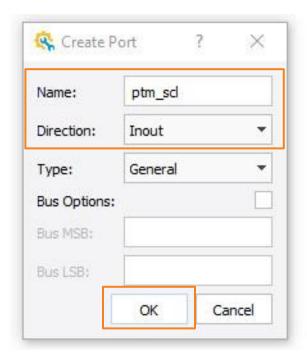

11. In the **Create Port** window, as shown in **Figure 3.15**, **Name** the port **ptm\_scl**, select the port **Direction** to **Inout**, and click **OK**. Repeat this process to create an **Inout** port named **psb\_sda**.

Figure 3.15. Propel Builder - Adding ptm\_scl Port

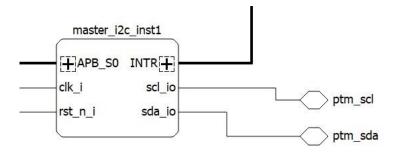

12. Connect the newly created ports to the respective ports of the I<sup>2</sup>C Master component, as shown in Figure 3.16.

Figure 3.16. Propel Builder - I<sup>2</sup>C Ports Connected

#### 3.3. Modifying the GPIO component

The GPIO component from the Propel Builder template only supports an eight-bit bi-directional port. In this demo design additional bits are needed to handshake between the RISC-V firmware and the Platform Manager 2 design.

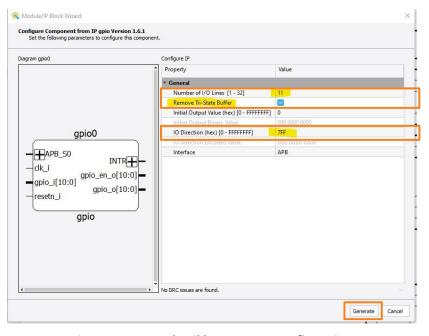

- 1. Double-click on the gpio0\_inst component to open the IP configuration window, as shown in Figure 3.17.

- 2. Tick the Remove Tri-State Buffer checkbox to create both an input and output port.

- 3. Change the **Number of I/O Lines** from 8 to **11**.

- 4. Set the I/O Direction to all outputs (7FF).

- 5. Click Generate.

Figure 3.17. Propel Builder - GPIO IP Configuration

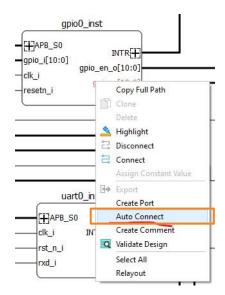

6. Right-click on the **gpio0\_inst** component to open the pop-up menu and select the **Auto Connect** as shown in Figure 3.18. The Propel Builder will generate and connect the input, output, and output enable ports.

Figure 3.18. Propel Builder - GPIO Auto Connect

7. The auto connect will generate port names that are verbose. Click on the port and edit the **Name** in the **Properties** box in the lower left of the screen as shown in Figure 3.19.

Figure 3.19. Propel Builder - Renaming GPIO Port

## 3.4. Adding and Modifying the Clocks

The primary clock for this design is the built in oscillator of the MachXO5-NX.

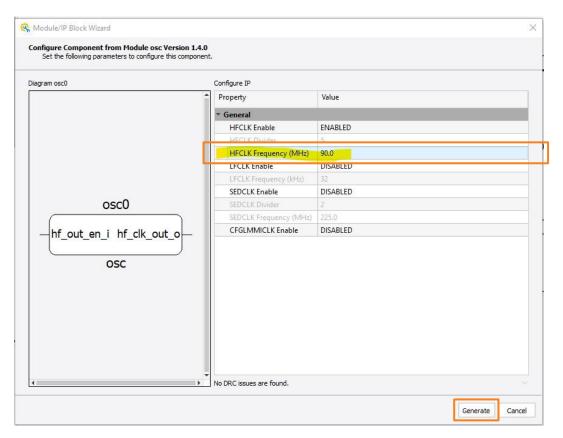

1. Double-click on the **osc0\_inst** component to open the IP configuration window as shown in Figure 3.20. Change the **HFCLK Frequency** to **90.0 MHz**. Then click **Generate**.

Figure 3.20. Propel Builder – Oscillator IP Configuration

24

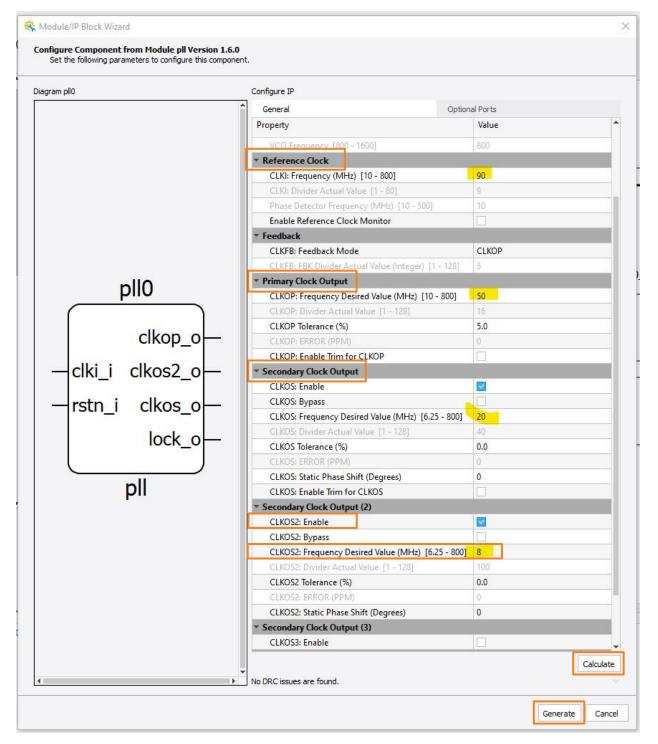

2. Double-click on the pllo\_inst component to open the IP configuration window as shown in Figure 3.21.

Figure 3.21. Propel Builder - PLL IP Configuration

- 3. Change the **Reference Clock** to match the oscillator output of **90.0 MHz**.

- 4. Change the **Primary Clock Output** to **50.0 MHz** with a **5.0 % CLKOP tolerance**; this is the RISC-V clock.

- 5. Change the **Secondary Clock Output** to **20.0 MHz**; this is the peripheral clock for UART, GPIO, and I<sup>2</sup>C components.

- 6. Tick the CLKOS2:Enable checkbox and set the frequency to 8.0 MHz; this is the Platform Manager 2 IP clock.

- 7. Click the Calculate button and then click Generate to update the PLL.

- 8. Add an output port named **CIk\_8MHz** and connect it to the **pll0\_inst clkos2\_o** port to enable connection to the Platform Manager 2 IP with the 8 MHz clock. This may be required because the **ASCO\_CLK**, that is normally the clock source for Platform Manager 2 designs, is not connected in the hardware to a MachXO5-NX primary clock pin. The Lattice LSE synthesis tool in Radiant generates an error when clocks are not connected to primary clock pins.

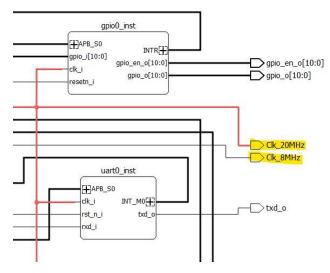

- 9. Add an output port named Clk\_20MHz and connect it to the clock bus that is connected to the peripheral clk\_i ports to drive additional logic in the top level design (described later in this document) as shown in Figure 3.22.

Figure 3.22. Propel Builder - Clock Ports

#### 3.5. Updating the RISC-V IP

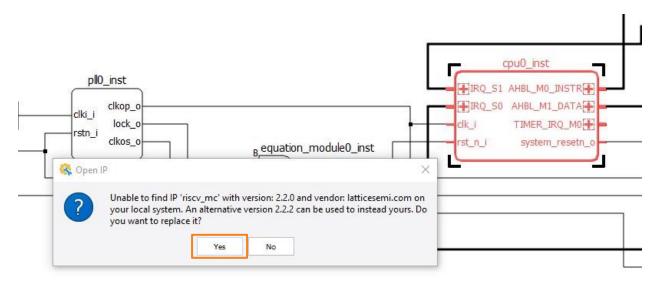

- 1. Double-click on the cpu0\_inst component and the Unable to find IP message may pop-up.

- 2. Click Yes to update to the later version of the RISC-V IP as shown in Figure 3.23.

Figure 3.23. Propel Builder - Update RISCV IP

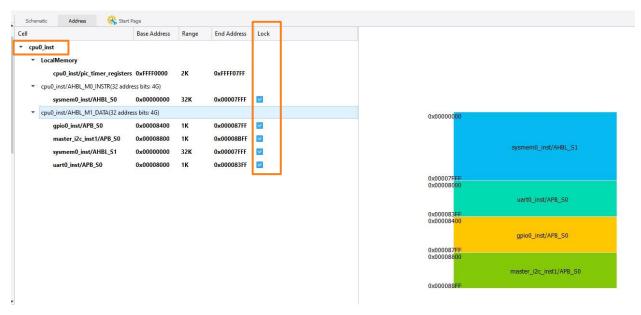

#### 3.6. Checking the Memory Map

- 1. Click on the Address tab to show the system memory map.

- 2. Click to expand the memory display and to show where the peripherals are mapped as shown in Figure 3.24.

- 3. Ensure the memory addresses do not overlap and the Lock checkboxes are ticked.

Figure 3.24. Propel Builder - Memory Map

#### 3.7. Generating the SOC RTL

The final step in creating the SOC RTL is to click on the **Generate** icon as shown in Figure 3.25, or click **Design-> Generate**. This will generate a top-level SOC module that can be instantiated in the overall top level module that also includes a top-level module for the Platform Manager 2 IP.

Figure 3.25. Propel Builder - Generating the Design

#### 3.8. Creating the Platform Manager 2 IP

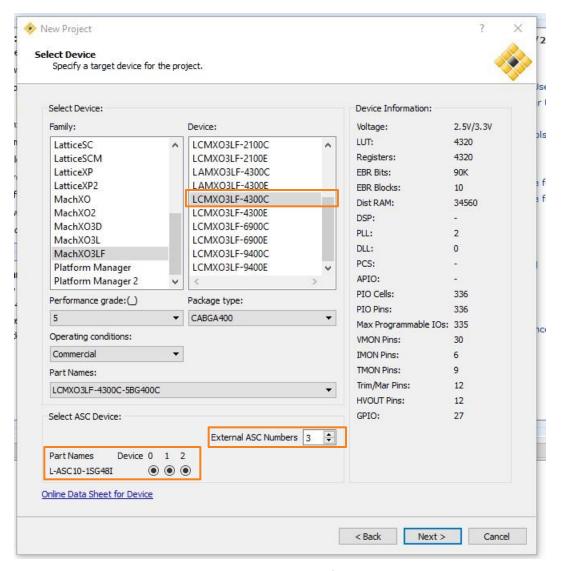

- 1. In the Lattice Diamond software, click File->New->Project to create a new project named ASC10\_PWR\_SEQ.

- 2. Select the MachXO3LF-4300C (or similar) device and add three L-ASC10 devices as shown in Figure 3.26.

Figure 3.26. Lattice Diamond - New Platform Designer Project

- 3. Click **Next** in the following windows until the project is generated.

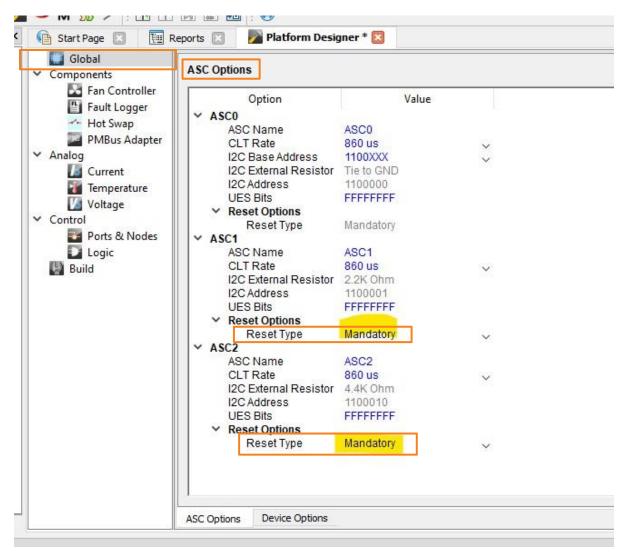

- 4. After the Platform Designer tool opens, select the Global view and the ASC Options tab.

- 5. Change the **Reset Type** for ASC1 and ASC2 to **Mandatory**, as shown in Figure 3.27. This will require all the L-ASC10 RESETb pins to be connected together (wire-OR'd), so that the sequence cannot start until all three L-ASC10s have completely powered up. The wire or'ing in hardware is done with jumper J12 on the ASC Breakout boards.

Figure 3.27. Lattice Diamond - ASC Options

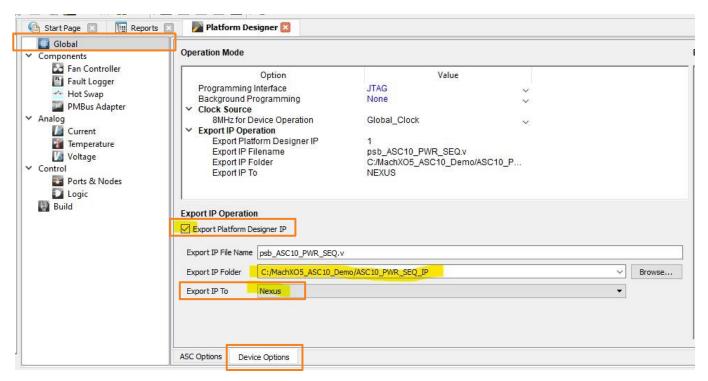

- 6. Click the **Device Options** of the **Global** view, and check the **Export Platform Designer IP** box, as shown in Figure 3.28. Note that the Clock Source is set to Global\_Clock to support connection to the PLL 8 Mhz output when using the Lattice LSE synthesis tool.

- 7. Select **Nexus** as the family to **Export To** and select the **Export IP Folder**. The name of top-level module for the exported IP defaults to a prefix of *psb\_* added to the project name. The **Export IP File Name** can be renamed by the user in this view.

Figure 3.28. Lattice Diamond – Global Device Options

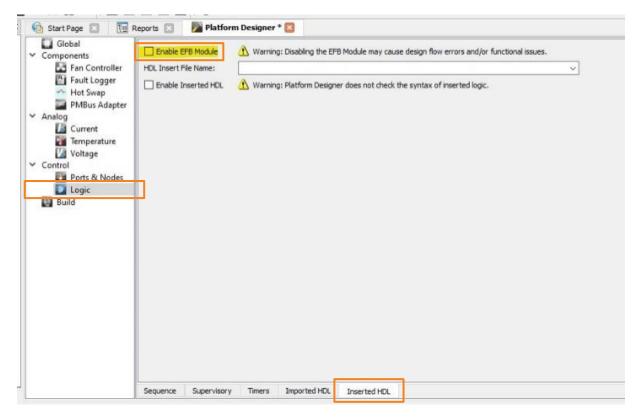

- 8. Select the **Logic** view and click the **Inserted HDL** tab.

- 9. Uncheck the Enable EFB Module because, the MachXO5-NX does not have an embedded function block (EFB).

Figure 3.29. Lattice Diamond – Disable EFB Logic

Now, the Platform Manager 2 design process can proceed just like any other Platform Manager 2 design by configuring the analog settings (VMON, IMON, TMON, and HVOUT) and building the sequencer logic.

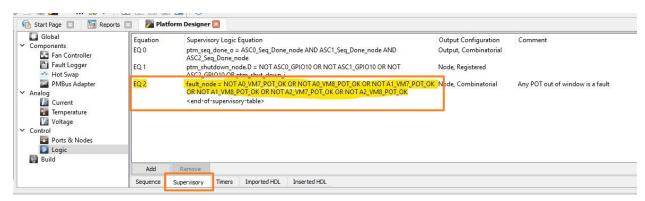

In this demo design, each ASC Breakout board has its own sequence (SM0 - SM2). There are two additional sequences to deal with Fault Logging (SM3 & SM4) for a total of five separate sequences. There is also three supervisory equations, shown in Figure 3.31, to support fault logging and sequencing.

Each ASC sequence is similar in that they enable pseudo power supplies (GPIO LEDs) and wait for the supply voltage (VMON7 and VMON8 slide POTs) to be within range before completing the sequence. The ASCs are cascaded so that after ASC0 has completed its sequence, then ASC1 starts and finally ASC2 starts its sequence when ASC1 is done. The entire sequence is initiated from the RISC-V firmware by setting a GPIO bit (more about this in the firmware and Radiant discussions).

Similarly, the power down sequence cascades in reverse order from ASC2, to ASC1, and finally ASC0 without waiting for the supply voltage (VMON7 and VMON8 slide POTs) to drop. The power down sequence can be triggered by any of the GPIO10 push-buttons on the ASC Breakout boards or from the RISC-V firmware by setting a GPIO bit (more about this in the firmware and Radiant discussions).

In this demo design the VMON trip points used different values to verify that each ASC was configured with its unique and correct programming pattern. The values used are shown in Table 3.1.

Table 3.1. Platform Designer - VMON Trip Points

| ASC | VMON  | Logical Name  | Lower Trip Point | Upper Trip Point |

|-----|-------|---------------|------------------|------------------|

| 0   | VMON7 | A0_VM7_POT_OK | 0.667 V          | 0.964 V          |

| 0   | VMON8 | A0_VM8_POT_OK | 1.205 V          | 1.805 V          |

| 1   | VMON7 | A1_VM7_POT_OK | 1.197 V          | 1.805 V          |

| 1   | VMON8 | A1_VM8_POT_OK | 1.592 V          | 2.401 V          |

| 2   | VMON7 | A2_VM7_POT_OK | 1.592 V          | 2.415 V          |

| 2   | VMON8 | A2_VM8_POT_OK | 1.999 V          | 2.999 V          |

The three ASC sequences are similar and follow the flow listed in Table 3.2.

Table 3.2. Platform Designer - SM1: ASC1 Power Sequence

| Step | Instruction                                   | Outputs                                                                           | Comment                                                                        |

|------|-----------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 0    | Begin Startup Sequence                        |                                                                                   |                                                                                |

| 1    | Wait for ASC1_AGOOD                           | ASC1_GPIO1 - ASC1_GPIO9 = 1<br>ASC1_Seq_Done_node = 0<br>ASC1_Seq_Pwr_Dn_node = 0 | Turn LEDs Off – Wait for AGOOD and reset Power Up and Power Down flags         |

| 2    | Wait for A1_VM7_POT_OK AND ASC0_Seq_Done_node | ASC1_GPIO2 = 0                                                                    | Turn LED2 On and wait for VMON7 voltage to be in window and ASC0 sequence done |

| 3    | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 4    | ASC1_GPIO3 = 0                                |                                                                                   | Sequence LED3 On                                                               |

| 5    | Wait for A1_VM8_POT_OK                        | ASC1_GPIO4 = 0                                                                    | Turn LED4 On and wait for VMON8 voltage to be in window                        |

| 6    | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 7    | ASC1_GPIO5 = 0                                |                                                                                   | Sequence LED5 On                                                               |

| 8    | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 9    | ASC1_GPIO6 = 0                                |                                                                                   | Sequence LED6 On                                                               |

| 10   | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 11   | ASC1_Seq_Done_node = 1                        |                                                                                   | Enable ASC2 to sequence up                                                     |

| 12   | Begin Shutdown Sequence                       |                                                                                   |                                                                                |

| 13   | Wait for ASC2_Seq_Pwr_Dn_node                 |                                                                                   | Wait for ASC2 to complete sequence down                                        |

| 14   | ASC1_GPIO6 = 1,<br>ASC1_Seq_Done_Node = 0     |                                                                                   | Sequence LED6 Off and reset Power Up Done                                      |

| 15   | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 16   | ASC1_GPIO5 = 1                                |                                                                                   | Sequence LED5 Off                                                              |

| 17   | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 18   | ASC1_GPIO4 = 1                                |                                                                                   | Sequence LED4 Off                                                              |

| 19   | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 20   | ASC1_GPIO3 = 1                                |                                                                                   | Sequence LED3 Off                                                              |

| 21   | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 22   | ASC1_GPIO2 = 1                                |                                                                                   | Sequence LED2 Off                                                              |

| 23   | Wait for 250ms using Timer                    |                                                                                   | Sequence Delay                                                                 |

| 24   | ASC1_Seq_Pwr_Dn_node = 1                      |                                                                                   | Enable ASC0 to sequence down                                                   |

| 25   | Halt (end-of-program)                         |                                                                                   |                                                                                |

#### Note:

1. Greyed out Steps 0, 12, and 25 are default steps included in every sequence.

One main difference in the ASCO sequence is that Step 2 in Table 3.2, does not wait for a previous ASC to complete its sequence. Instead, it only waits for AO\_VM7\_POT\_OK because, ASCO is the first L-ASC10 in the group.

Similarly, the ASC2 sequence does not wait for the next ASC to complete power down before starting the shutdown sequence. Instead, it waits for the ptm\_shutdown\_node in Step 12 in Table 3.2 . The ptm\_shutdown\_node is defined in Supervisory Equation EQ1 (see Figure 3.31); it is the OR of the three GPIO10 push button switches (on the three ASC Breakout boards) OR the input port ptm\_shut\_down\_i that is connected to a RISC-V GPIO bit.

In like fashion, Step 24 in Table 3.2 for ASCO does not set a node but rather the output port ptm\_pwr\_dn\_done\_o that is connected to a RISC-V bit.

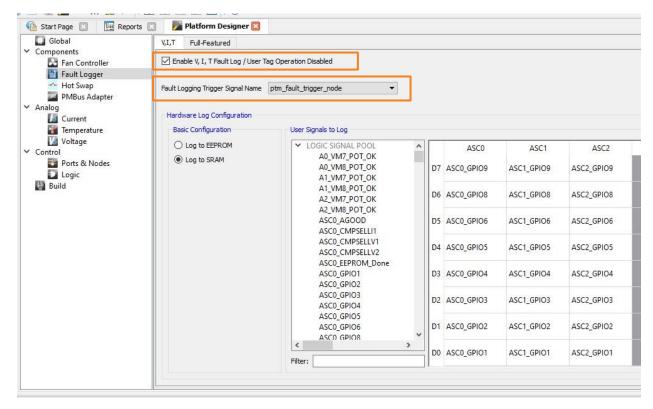

In this demo design, the Voltage, Current, and Temperature (V,I,T) fault logging is enabled as shown in Figure 3.30. The user created node ptm\_fault\_trigger\_node is used to trigger the storing of V,I,T and ASCx\_GPIO status within the L-ASC10's SRAM. The trigger signal is sent over the three-wire ASC/IF. The fault record is later read back via I<sup>2</sup>C.

Figure 3.30. Platform Designer - V, I, T Fault Logging Enabled

The logic to detect and trigger the fault log is a combination of a supervisory equation and a sequence. The supervisory equation EQ2 is the OR of any POT not OK as shown in Figure 3.31. Since the fault\_node will be true during the power up sequence, a separate Logic sequence is used to enable the ptm\_fault\_trigger\_node as listed in Table 3.3.

Figure 3.31. Platform Designer – Fault Node Supervisory Equation

Table 3.3. Platform Designer – SM3: Fault Logger Sequence

| Step | Instruction                                                                                       | Outputs                                               | Comment                                                                    |

|------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|

| 0    | Begin Startup Sequence                                                                            |                                                       |                                                                            |

| 1    | Wait for ASCO_Seq_Done_node AND ASC1_Seq_Done_node AND ASC2_Seq_Done_node AND NOT ptm_clr_fault_i | <pre>ptm_fault_o = 0 ptm_fault_trigger_node = 0</pre> | Wait for all sequences to be Done and RISC-V ready to clear the next fault |

| 2    | Wait for fault_node                                                                               |                                                       | Wait for any POT to be out of its window = FAULT                           |

| 3    | ptm_fault_trigger_node = 1                                                                        |                                                       | Trigger the ASCs to capture Fault Status in Volatile Register              |

| 4    | ptm_fault_o = 1 ptm_fault_trigger_node<br>= 0                                                     |                                                       | Tell RISC-V that fault occurred and clear the trigger signal to the ASCs   |

| 5    | Wait for NOT fault_node                                                                           |                                                       | Wait for faults to go away                                                 |

| 6    | Wait for 50ms using Timer                                                                         |                                                       |                                                                            |

| 7    | Wait for ptm_clr_fault_i                                                                          |                                                       | Wait for RISC-V to clear the fault                                         |

| 8    | Go to step 1                                                                                      |                                                       | Get ready for next fault                                                   |

| 9    | Begin Shutdown Sequence                                                                           |                                                       |                                                                            |

| 10   | Halt (end-of-sequence)                                                                            |                                                       |                                                                            |

#### Note:

1. Greyed out Steps 0, 9, and 10 are default steps included in every sequence.

The Fault Logger sequence manages both the trigger to log a fault and the handshaking between the RISC-V firmware and the Platform Manager 2 design. So that the RISC-V firmware has time to read out the faults before re-enabling the fault trigger.

The last sequence is state machine 4 (SM4) and it simply drives the seven-segment LED display on the MachXO5-NX development board. If any of the VMON POTs are outside their window then an "**F**" will be displayed otherwise the display LEDs are off (see Table 3.4). This visual feedback helps when running the demo to restore the slide POT within the lower and upper VMON trip points. This also demonstrates how the Platform Manager 2 design can directly control the MachXO5-NX Top-Level Ports without involving the RISC-V.

Table 3.4. Platform Designer – SM4: Fault Display on 7-segment LED

| Step | Instruction                                                               | Outputs | Comment                           |

|------|---------------------------------------------------------------------------|---------|-----------------------------------|

| 0    | Begin Startup Sequence                                                    |         |                                   |

| 1    | Wait for ASCO_Seq_Done_node AND ASC1_Seq_Done_node AND ASC2_Seq_Done_node |         | Wait for all sequences to be Done |

| 2    | If fault_node Then Goto 3 Else Goto 5                                     |         |                                   |

| 3    | Segment = 01110001                                                        |         | Display "F" on 7-sement LED       |

| 4    | Goto step 2                                                               |         |                                   |

| 5    | Segment = 11111111                                                        |         | 7-segment LEDs Off                |

| 6    | Go to step 2                                                              |         | Get ready for next fault          |

| 7    | Begin Shutdown Sequence                                                   |         |                                   |

| 8    | Halt (end-of-sequence)                                                    |         |                                   |

#### Note:

1. Greyed out Steps 0, 7, and 8 are default steps included in every sequence.

Throughout this discussion several Ports and Nodes have been mentioned. Table 3.5 provides a summary of the user defined Ports and Nodes in this demo design.

| Name                   | Direction   | Description                                                | RISC-V bit-map |

|------------------------|-------------|------------------------------------------------------------|----------------|

| segment_0              | From PTM2   | seg_dp_o                                                   | n/a            |

| segment_1              | From PTM2   | seg_g_o                                                    | n/a            |

| segment_2              | From PTM2   | seg_f_o                                                    | n/a            |

| segment_3              | From PTM2   | seg_e_o                                                    | n/a            |

| segment_4              | From PTM2   | seg_d_o                                                    | n/a            |

| segment_5              | From PTM2   | seg_c_o                                                    | n/a            |

| segment_6              | From PTM2   | seg_b_o                                                    | n/a            |

| segment_7              | From PTM2   | seg_a_o                                                    | n/a            |

| ptm_fault_o            | From PTM2   | Fault Flag                                                 | 0x400          |

| ptm_seq_done_o         | From PTM2   | Power Up sequence done                                     | 0x200          |

| ptm_pwr_dn_done_o      | From PTM2   | Power Down sequence done                                   | 0x100          |

| ptm_clr_fault_i        | From RISC-V | Clear the Fault Flag                                       | 0x400          |

| ptm_shut_down_i        | From RISC-V | Start Shutdown sequence                                    | 0x200          |

| fault_node             | n/a         | VMON POT = NOT OK                                          | n/a            |

| ptm_fault_trigger_node | n/a         | Trigger signal for Fault Log                               | n/a            |

| ptm_shutdown_node      | n/a         | OR of RISC-V signal or push buttons on ASC Breakout boards | n/a            |

The signal in the MachXO5-NX Top-Level Radiant design, ptm\_start\_up\_w, has the RISC-V bit map of 0x100. It does not connect to the Platform Manager 2 Ports or Nodes. It connects to the ptm\_enable\_seq port (see Figure 3.36) of the Platform Designer exported module and ultimately to the external reset port of the clock and reset module. The ptm\_enable\_seq port is not a user defined port, it is always included by the export function. Thus, once this signal is set it should not be cleared otherwise, the ASC outputs will immediately assume their safe state and the Powerdown Sequence will not be followed.

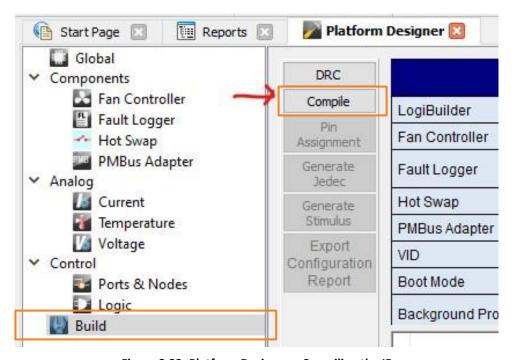

The final step in generating the Platform Manager 2 IP is to click the **Compile** button in the **Build** view, as shown in Figure 3.32. This will generate the IP and export the files to the folder specified in Figure 3.28.

Figure 3.32. Platform Designer – Compiling the IP

© 2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 3.9. Building the MachXO5-NX Top Level Design

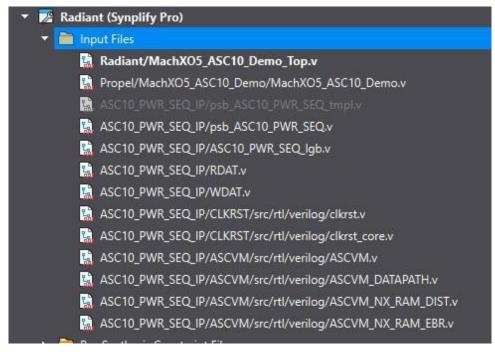

When Step 3.7 Generating the SOC RTL is completed, the Propel Builder placed a top-level RTL module and all the IP RTL library files in a folder for the Radiant software project as shown in Figure 3.33.

```

n Start Page

Reports

MachXO5_ASC10_Demo.v

include "./lib/latticesemi.com/ip/master_i2c_inst/1.4.0/rtl/master_i2c_inst.v"

include "./lib/latticesemi.com/ip/sysmem0/1.1.2/rtl/sysmem0.v"

include "./lib/latticesemi.com/ip/timer_counter/1.2.0/rtl/timer_counter.v"

include "./lib/latticesemi.com/ip/timer_counter/1.2.0/rtl/timer_counter.v"

`include "./lib/latticesemi.com/module/ahbl0/1.3.0/rtl/ahbl0.v"

`include "./lib/latticesemi.com/module/ahbl2apb0/1.1.0/rtl/ahbl2apb0.v"

'include "./lib/latticesemi.com/module/apb0/1.1.0/rtl/apb0.v"

'include "./lib/latticesemi.com/module/osc0/1.4.0/rtl/osc0.v"

'include "./lib/latticesemi.com/module/osc0/1.4.0/rtl/osc0.v"

module MachXO5_ASC10_Demo (gpio_en_o, gpio_i, gpio_o, Clk_20MHz, Clk_8MHz,

ptm_scl, ptm_sda, rstn_i, rxd_i, txd_o) /* synthesis sbp_module=true */;

output [10:0]gpio_en_o;

input [10:0]gpio i;

output [10:0]gpio_o;

output Clk_20MHz;

output Clk_8MHz;

inout ptm_scl;

inout ptm_sda;

input rstn_i;

input rxd i;

output txd_o;

```

Figure 3.33. Radiant - MachXO5 ASC10 Demo Module

The whole SOC design has ten ports to connect to the outside world and to the Platform Manager 2 IP. To include the Platform Manager 2 IP do the following:

Right-click on the Input Files from the File List view, as shown in Figure 3.34, and select Add -> Existing File.

Figure 3.34. Radiant - Input Files, Add Existing File

© 2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

- 2. Browse to the folder where the Platform Manager 2 IP was exported to and add the files listed below and shown in Figure 3.35.

- psb\_ASC10\_PWR\_SEQ\_tmpl.v

- psb\_ASC10\_PWR\_SEQ.v

- ASC10 PWR SEQ lgb.v

- RDAT.v

- WDAT.v

- CLKRST/src/rtl/verilog/clkrst.v

- CLKRST/src/rtl/verilog/clkrst core.v

- ASCVM/src/rtl/verilog/ASCVM.v

- ASCVM/src/rtl/verilog/ASCVM DATAPATH.v

- ASCVM/src/rtl/verilog/ASCVM\_NX\_RAM\_DIST.v

- ASCVM/src/rtl/verilog/ASCVM\_NX\_RAM\_EBR.v

- 3. Right-click on the **psb\_ASC10\_PWR\_SEQ\_tmpl.v** file and select **Exclude from Implementation** as this is only a template file; the contents of which can be copied and pasted into the Top-Level design file

- 4. To add the MachXO5\_ASC10\_Demo\_Top.v file, right-click on the Input Files and select Add -> New. This top level module will be used to connect the Platform Manager 2 IP with the Propel Builder SOC IP and both of them to the physical pins of the MachXO5-NX device. This is the only RTL file that the user has to code by hand.

Figure 3.35. Radiant - Input File List

The Platform Manager 2 IP module **psb\_ASC10\_PWR\_SEQ** is instantiated and connected in lines 159 to 196 of the Top-Level design file, as shown in Figure 3.36.

```

MachXO5_ASC10_Demo_Top.v

👚 Start Page

Reports

psb ASC10 PWR SEQ psb ASC10 PWR SEQ inst

// Platform Manager Sequence Interface

.ptm_enable_seq

(ptm_start_up_w),

.ptm_seq_done_o

(ptm done w),

.ptm pwr dn done o (ptm pwr dn done w),

.ptm shut down i

(ptm shut dn w),

// Platform Manager Fault Interface

.ptm_fault_o

(ptm fault w),

.ptm clr fault i

(ptm clr fault w),

// Platform Manager 7-Segment Interface

// Platform Designer reverses the bit order

.segment 0

() ,

.segment 1

(seg g o),

.segment 2

(seg_f_o),

.segment_3

(seg_e_o),

.segment 4

(seg_d_o),

.segment_5

(seg c o),

.segment 6

(seg_b_o),

.segment_7

(seg_a_o),

.ASCO RSTN (ascO reset i),

.Global Clock

(clk 8MHz w),

.ASCO CLK (clk 8MHz w),

.rdat 0

(asc0 rdat i),

.wdat 0

(asc0 wdat o),

.wrclk_0

(asc0_wrclk_o),

.rdat 1

(asc1 rdat i),

wdat_1

(asc1_wdat_o),

.wrclk 1

(asc1 wrclk o),

.rdat 2

(asc2 rdat i),

.wrclk 2

(asc2 wrclk o),

.wdat 2

(asc2 wdat o)

```

Figure 3.36. Radiant - Platform Manager 2 IP instantiation

The Propel Builder SOC IP module **MachXO5\_ASC10\_Demo** is instantiated and connected in lines 200 to 210 of the Top-Level design file, as shown in Figure 3.37.

```

MachXO5_ASC10_Demo_Top.v

👚 Start Page

Reports

- // Instantiate the RISC-V SOC

MachXO5_ASC10_Demo MachXO5_ASC10_Demo_Inst(

({ptm_clr_fault_w, ptm_shut_dn_w, ptm_start_up_w, led_o}),

.gpio_o

.gpio_i

({ptm_fault_w, ptm_done_w, ptm_pwr_dn_done_w, gpio_i_spare, bridg_bd_pb2_r, dipsw_i}),

.rstn_i

(resetn_i),

rxd_i

(rxd i),

.txd o

(txd_o),

(ptm_scl)

.ptm_scl

(ptm_sda),

(clk_20MHz_w),

.ptm_sda

.Clk_20MHz

.Clk_8MHz

(clk_8MHz_w)

```

Figure 3.37. Radiant - SOC Instantiation

Between these two Figures, it can be seen how the two IPs are connected with the **ptm\_xxx\_w** wires. The placement of the wires in the SOC GPIO input and output ports determines the bit map in the RISC-V firmware.

The Top-Level ports (the MachXO5-NX physical connections) are between line 42 and line 87 of the MachXO5\_ASC10\_Demo\_Top module as shown in Figure 3.38.

```

👚 Start Page

MachXO5_ASC10_Demo_Top.v

module MachXO5 ASC10 Demo Top (

// UART Connections

input rxd_i,

output txd_o,

ptm_sda

// MachXO5 Eval Board Connections

// Seven Segment Display

output seg_a_o,

output seg_b_o,

output seg_c_o,

output seg_d_o,

output seg_d_o,

output seg_f_o,

output seg_g_o,

output seg_g_o,

output seg_dp_o

// LEDs and DIP Switch

output [7:0] led_o, input [3:0] dipsw i

bridge_bd_pb2_i,

asc0_reset_i

asc0_rdat_i,

output asc0_wdat_o,

output asc0_wrclk_o,

input asc1_rdat_i,

output asc1_wdat_o,

output asc1_wrclk_o,

input asc2_rdat_i,

output asc2_wdat_o,

output asc2_wrclk_o,

output raspi_io2_test_o,

input resetn_i

```

Figure 3.38. Radiant - Top Level Ports

© 2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Radiant's device **Constraint Editor** is used to map the Top-Level ports to the MachXO5-NX physical pins based on the schematics of the evaluation boards.

Now, the design is set up for Synthesis, Map, Place & Route, and Export a programming file. If either the SOC design in Propel Builder or the Platform Manager 2 design in Diamond are modified, then Radiant will know the source files have been updated and a re-build is necessary. If changes in the number of ports, names of ports, or the size of the ports changes, then the Top-Level instantiations will need to be modified. However, the RISC-V still needs some firmware before we have a working demo.

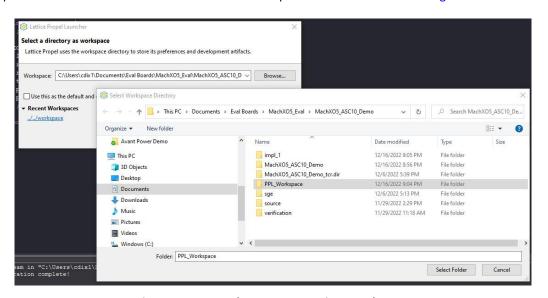

## 3.10. Starting the Propel SDK

In Step 3.7 Generating the SOC RTL, Propel Builder also generates system information files that are used in the Propel software development kit (SDK).

When Propel SDK is first launched for this demo a new workspace is created as shown in Figure 3.39.

Figure 3.39. Propel SDK - New Project Workspace

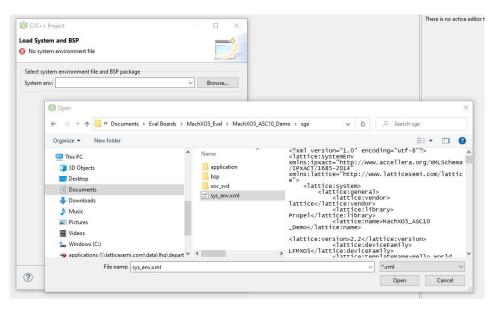

1. Browse the Propel Builder generated file sys\_env.xml as shown in Figure 3.40.

Figure 3.40. Propel SDK - New Project System and BSP

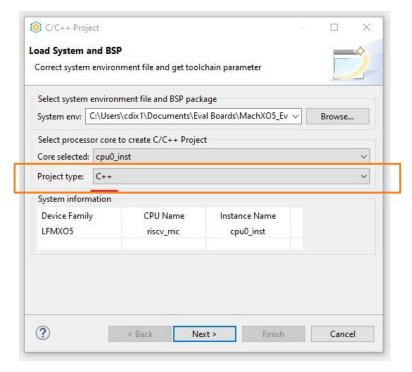

2. Select the **Project type** as "C++" as shown in Figure 3.41, and then provide a project name as shown in Figure 3.42.

Figure 3.41. Propel SDK - New Project C++

Figure 3.42. Propel SDK - New Project Name

3. Accept the default Toolchain Settings and click the Finish button as shown in Figure 3.43.

Figure 3.43. Propel SDK – New Project Tool Settings

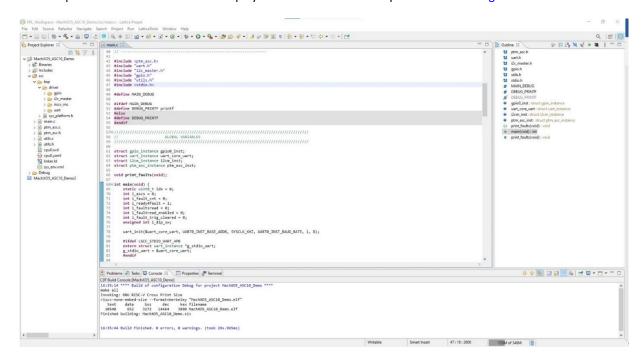

4. The Propel SDK environment will be displayed with the main.c file open as shown in Figure 3.44.

Figure 3.44. Propel SDK - IDE main.c File

42

# 3.11. Modifying main.c

Several edits to main.c were made for the demo design and are covered in this section.

1. Add global variable **ptm\_asc\_inst**:

This structure is used to hold pointers and data to support interface with the L-ASC10s. Details of the structure are covered in the next step.

2. Add several local variables:

Basic looping index, integers for number of ASCs and number of faults, and several flags to manage the Platform Manager 2 Fault detection.

- 3. DIP Switch:

- None: The L-ASC10s use the settings within their EECMOS no configuration is done from the RISC-V.

- SW1: The L-ASC10s will be configured by the erase, program, and verify algorithm (similar to Programmer).

- SW2: The L-ASC10s will be configured by writing to their SRAM and then verifying.

```

gpio_input_get(&gpio0_inst, 0, &i_dip_sw);

i_dip_sw &= 0x0F;

DEBUG PRINTF("DIP SW = %d\n\r", i dip sw);

111

112

113

if((i_dip_sw & 0x01) == 0) {

DEBUG_PRINTF("Programming ASC10s!\r\n");

114

115

i_ascs = ptm_asc_program_eeprom_config(&ptm_asc_inst);

if(i_ascs < PTM_ASC_I2C_ERROR_NAK)

116

DEBUG_PRINTF("Total of %d ASC10s Programmed!\r\n", i_ascs);

117

118

switch(i_ascs) {

119

case(PTM_ASC_I2C_ERROR_NAK) :

120

DEBUG_PRINTF("NAK Errors Ocurred - ASC10 Programming Failed!\n\r");

121

122

123

case (PTM_ASC_ERROR_PRG_MODE) :

124

DEBUG_PRINTF("Program Mode Errors Ocurred - ASC10 Programming Failed!\n\r");

125

break;

case (PTM_ASC_ERROR_VERIFY):

126

127

DEBUG_PRINTF("Verify Errors Ocurred - ASC10 Programming Failed!\n\r");

128

case (PTM_ASC_ERROR_ERASE):

129

130

DEBUG_PRINTF("Erase Errors Ocurred - ASC10 Programming Failed!\n\r");

131

132

DEBUG_PRINTF("Too many Errors Ocurred - ASC10 Programming Failed!\n\r");

break;

135

}

136

}

137

138

if((i_dip_sw & 0x02) == 0){

DEBUG PRINTF("Configuring ASC10s!\r\n");

139

140

i_ascs = ptm_asc_write_sram_config(&ptm_asc_inst);

if(i_ascs < PTM_ASC_I2C_ERROR_NAK)

DEBUG_PRINTF("Total of %d ASC10s Configured!\r\n", i_ascs);</pre>

141

142

143

144

switch(i_ascs) {

case(PTM_ASC_I2C_ERROR_NAK) :

145

146

DEBUG_PRINTF("NAK Errors Ocurred - ASC10 Config Failed!\n\r");

break;

147

case (PTM_ASC_ERROR_VERIFY):

148

149

DEBUG_PRINTF("Verify Errors Ocurred - ASC10 Config Failed!\n\r");

150

break;

151

default :

152

DEBUG_PRINTF("Too many Errors Ocurred - ASC10 Config Failed!\n\r");

153

154

155

}

156

```

Figure 3.45. Propel SDK - Main DIP Switch Options

#### 4. Platform Manager 2 Interface

This is the primary goal of this demo design.

One function call is made after decoding the DIP switch to enable the Platform Manager 2 sequence. Followed by a function to see if the Platform Manager 2 sequence is complete, as shown in Figure 3.46.

43

FPGA-IIG-02194-1 0

```

DEBUG_PRINTF("Starting ASC10 Power Up Sequence!\r\n");

ptm_asc_set_pwr_seq_start(&ptm_asc_inst);

while (ptm_asc_inst.i_seq_done_flag == 0) {

ptm_asc_get_pwr_up_seq_done(&ptm_asc_inst);

DEBUG_PRINTF("ASC10 Power Up Sequence Complete!\r\n");

164

```

Figure 3.46. Propel SDK – Main Platform Manager 2 Start

This is followed by a loop where several functions are called to interface with the Platform Manager 2 using the GPIO and I<sup>2</sup>C objects as shown in Figure 3.47.

```

167

while (true) {

ptm_asc_get_pwr_dn_seq_done(&ptm_asc_inst);

168

169

if(ptm_asc_inst.i_seq_off_flag) {

170

DEBUG_PRINTF("ASC10 Power Down Sequnce Complete!\r\n");

171

return 0;

172

173

if(i_fault_cnt == 5){

174

DEBUG PRINTF("Too Many Faults - Shutting Down!\r\n");

175

i_fault_cnt = 6;

176

ptm_asc_set_fault_trig(&ptm_asc_inst, PTM_ASC_FAULT_TRIG_ENABLE);

177

ptm_asc_set_pwr_seq_shutdown(&ptm_asc_inst);

178

179

ptm_asc_get_pwr_fault(&ptm_asc_inst);

180

if((ptm_asc_inst.i_seq_fault_flag) && (i_ready4fault)){

181

i_ready4fault = 0;

182

i_faultsread = 0;

183

i fault cnt++;

DEBUG PRINTF("Total ASC10 Faults = %d\r\n", i_fault_cnt);

184

185

186

if(!(ptm_asc_inst.i_seq_fault_flag) && !(i_ready4fault)){

187

i_ready4fault = 1;

188

i faultread enabled = 0;

189

i faultsread = 0;

190

i fault trig cleared = 0;

191

ptm_asc_set_fault_trig(&ptm_asc_inst, PTM_ASC_FAULT_TRIG_ENABLE);

192

DEBUG PRINTF("ASC10 Ready for Faults\r\n");

193

194

if((ptm_asc_inst.i_seq_fault_flag) && !(i_faultread_enabled)){

195

ptm asc get fault read enabled(&ptm asc inst);

196 //

DEBUG_PRINTF("Enabling the Reading of ASC10 Faults\r\n");

197

i faultread enabled = 1;

198

199

if((ptm_asc_inst.i_seq_fault_flag) && !(i_faultsread)){

200

if(ptm asc inst.i read fault en flag){

201

DEBUG_PRINTF("Reading ASC10 Faults

202

ptm_asc_get_faults(&ptm_asc_inst);

print_faults();

203

i faultsread = 1;

204

205

206

207

// Check if PB2 on ASC Bridge Board is pressed

208

gpio_input_get(&gpio0_inst, 0, &i_dip_sw);

209

if((i_dip_sw & 0x10) && !(i_fault_trig_cleared)){

210

DEBUG_PRINTF("Clearing ASC10 Fault Trigger\r\n");

ptm_asc_set_fault_trig(&ptm_asc_inst, PTM_ASC_FAULT_TRIG_CLEAR);

211

212

i_fault_trig_cleared = 1;

213

}

```

Figure 3.47. Propel SDK – Main Loop

44

#### 5. Platform Manager 2 Fault Decoder:

This local function **print\_faults()**, listed in Figure 3.48, decodes the fault record for the VMONs monitored in this design and sends a message over the UART to indicate which ASC had the fault and if the fault was an over-voltage or under-voltage. When running the demo, these messages correspond to actions taken on the VMON slider POTs.

```

230@ void print faults(void){

if((ptm_asc_inst.asc[0].fault[4] & FAULT_MASK_VMON7A) == 0){

231

232

if((ptm_asc_inst.asc[0].fault[4] & FAULT_MASK_VMON7B) == 0){

233

DEBUG_PRINTF("ASCO VMON7 Under Voltage\r\n");

234

} else {

235

DEBUG_PRINTF("ASC0 VMON7 Over Voltage\r\n");

}

236

237

if((ptm_asc_inst.asc[0].fault[4] & FAULT_MASK_VMON8A) == 0){

238

239

if((ptm_asc_inst.asc[0].fault[3] & FAULT_MASK_VMON8B) == 0){

DEBUG_PRINTF("ASCO VMON8 Under Voltage\r\n");

240

241

} else {

DEBUG_PRINTF("ASCO VMON8 Over Voltage\r\n");

242

243

244

245

if((ptm_asc_inst.asc[1].fault[4] & FAULT_MASK_VMON7A) == 0){

if((ptm_asc_inst.asc[1].fault[4] & FAULT_MASK_VMON7B) == 0){

246

247

DEBUG_PRINTF("ASC1 VMON7 Under Voltage\r\n");

248

} else {

249

DEBUG PRINTF("ASC1 VMON7 Over Voltage\r\n");

}

250

251

if((ptm_asc_inst.asc[1].fault[4] & FAULT_MASK_VMON8A) == 0){

252

if((ptm_asc_inst.asc[1].fault[3] & FAULT_MASK_VMON8B) == 0){

253

254

DEBUG_PRINTF("ASC1 VMON8 Under Voltage\r\n");

255

DEBUG_PRINTF("ASC1 VMON8 Over Voltage\r\n");

256

}

257

258

259

if((ptm_asc_inst.asc[2].fault[4] & FAULT_MASK_VMON7A) == 0){

if((ptm_asc_inst.asc[2].fault[4] & FAULT_MASK_VMON7B) == 0){

260

DEBUG_PRINTF("ASC2 VMON7 Under Voltage\r\n");

261

262

} else {

263

DEBUG_PRINTF("ASC2 VMON7 Over Voltage\r\n");

264

265

if((ptm_asc_inst.asc[2].fault[4] & FAULT_MASK_VMON8A) == 0){

266

267

if((ptm_asc_inst.asc[2].fault[3] & FAULT_MASK_VMON8B) == 0){

268

DEBUG_PRINTF("ASC2_VMON8_Under_Voltage\r\n");

269

} else -

270

DEBUG_PRINTF("ASC2 VMON8 Over Voltage\r\n");

271

272

}

273 }

```

Figure 3.48. Propel SDK – Main Print Faults

# 3.12. Writing Code to Interface with Platform Manager 2

In this section we will highlight some of the code written to interface with the Platform Manager 2 IP. All of the code is contained in the header file (ptm\_asc.h) and source file (ptm\_asc.c). A complete description of all of the functions within the source file (ptm\_asc.c) is provided in Appendix A.

The header file (ptm\_asc.h) can be divided into three major sections;

- #defines

- Structures

- function prototypes.

Most of the #defines are derived directly from the L-ASC10 Data Sheet. A few of the #defines at the very top of the file, listed in Figure 3.49, represents the connection made in the Radiant design (see Figure 3.37 and Table 3.5).

45

```

45 // PTM Control Bits

46 #define GPIO PTM PWR CLR FAULT 10

47 #define GPIO PTM PWR SHUTDOWN 9

48 #define GPIO PTM PWR ENABLE 8

49

50 // PTM Control Masks

51 #define PTM_PWR_CLEAR_FAULT 0x400

52 #define PTM PWR SHUTDOWN 0x200

53 #define PTM PWR ENABLE 0x100

54

55 // PTM Status Bits

56 #define GPIO PTM PWR FAULT 10

57 #define GPIO_PTM_PWR_DONE 9

58 #define GPIO_PTM_PWR_DN_DONE 8

59

60 // PTM Status Masks

61 #define PTM PWR FAULT 0x400

62 #define PTM PWR SEQ DONE 0x200

63 #define PTM_PWR_DN_DONE 0x100

64

```

Figure 3.49. Propel SDK – ptm\_asc.h, Defines PPL\_IDE

The **ptm\_asc\_instance** structure, listed in Figure 3.50, holds pointers to both the GPIO and I<sup>2</sup>C interfaces, various fault related flags, and an array of eight **asc\_device** structures.

```

135@ struct asc_device {

unsigned char *

137

unsigned char fault[7];

138 };

139

140@ struct ptm_asc_instance {

const char *instance name;

142

struct i2cm instance * i2cm;

143

struct gpio_instance * gpio;

144

int i_total_asc;

int i_seq_done_flag;

145

146

int i_seq_fault_flag;

147

int i_seq_off_flag;

148

int i_read_fault_en_flag;

149

struct asc device asc[8];

150 };

151

152@ enum ptm_asc_fault_trigger {

PTM_ASC_FAULT_TRIG_CLEAR,

153

154

PTM_ASC_FAULT_TRIG_ENABLE

155 };

```

Figure 3.50. Propel SDK - ptm\_asc.h, Structures

The asc\_device structure holds a pointer to the configuration data for the respective L-ASC10 device and the fault array contains the full fault record for the same device. The data pointer is set when the ptm\_asc\_init function is called and the fault array is populated by the ptm\_asc\_get\_faults function (both are described in the API section).

The source file (ptm\_asc.c) contains commands, listed in Figure 3.51, that are based on the L-ASC10 Data Sheet and Programming Specification.

46

```

73 // ASC I2C Commands

74 unsigned char ptm_asc_cmd_read_id[] = { 0x02};

75 unsigned char ptm_asc_cmd_read_status[] = {0x03};

76 unsigned char ptm_asc_cmd_write_config[] = { 0x31, 0x00};

77 unsigned char ptm_asc_cmd_read_config[] = { 0x33, 0x00};

78 unsigned char ptm_asc_cmd_load_config[] = {0x35};

79

80 unsigned char ptm asc cmd read fault enable[] = {0x74, 0xAC};

81 unsigned char ptm asc cmd read fault disable[] = {0x74, 0x00}; //

82 unsigned char ptm_asc_cmd_read_volatile_fault_reg[] = {0x73};

83 unsigned char ptm_asc_cmd_read_user_tag_cfg_reg[] = {0x33, 0x66};

84 unsigned char ptm_asc_cmd_enprog[] = {0x04, 0x3D, 0xE5};

85 unsigned char ptm_asc_cmd_usermode[] = {0x05};

86 unsigned char ptm_asc_cmd_becfg[] = {0x21};

87 unsigned char ptm_asc_cmd_writecfg[] = {0x22};

88 unsigned char ptm_asc_cmd_progcfg[] = {0x24, 0x00};

89 unsigned char ptm_asc_cmd_vercfg[] = {0x25, 0x00};

90 unsigned char ptm_asc_cmd_progdone[] = {0x27};

91 unsigned char ptm_asc_cmd_ldshdw[] = {0x28};

```

Figure 3.51. Propel SDK – ptm\_asc.c, I<sup>2</sup>C Commands

The configuration data arrays are #included in the source file (ptm\_asc.c), as listed in Figure 3.52, instead of having to copy-and-paste every time the L-ASC10 configuration changes. Also, the configuration header files for each L-ASC10 is added to the list of Project Includes.

Figure 3.52. Propel SDK - ptm\_asc.c, Configuration includes

# 3.13. Converting the L-ASC10 Programming Files

The L-ASC10 configuration header files (ASC0 is shown in Figure 3.53) are generated from the ASC\_Hex\_Reader.exe utility that converts the .hex programming file into the unsigned char array that can be #included into the design.

```

□ 🕏 🖓 🖇 🗆 🗖 📵 main.c

🦰 Project Explorer 🛭

h ptm_asc.h

ptm_asc.c

ntm_asc0_data.h ≅

1⊖//ASC Programming Data from ASC10_PWR_SEQ_ASC0.hex

✓

MachXO5_ASC10_Demo

MachXO5_ASC10_Dem

//Generated from Diamond tool Platform Designer

> 🚜 Binaries

//Converted to C++ array using Lattice L-ASC10 HEX File Reader

✓

Millington

Includes

Inclu

//Copyright 2022, Version 2.0 Dec 30, 2022

C:/Documents/Eval Boards/MachXO5_Eval/MachXO5_AS

//Converted on Tue Jan 10, 2023 at 16:39:12

> h ASCO_data.h

> In ASC10 PWR SEO ASC0.h

unsigned char ptm_asc0_data[] =

0xFF, 0x4E, 0x11, 0x4E, 0x11,

> h ptm_asc0_data.h

// ROW 0 -> FFFFFFFFFFFFF

// Row 1 -> FFFFFFFF4E114E11

> h ptm_asc1_data.h

0x4E, 0x11, 0x4E, 0x11, 0xFC, 0x00, 0x9C,

2 -> 4E114E11FC009CC7

0xC7,

h ptm_asc2_data.h

0x00, 0x9C, 0xC7, 0x00, 0x9C,

0x9C,

3 -> 009CC7009CC7009C

0xC7,

0x00,

// Row

> Le C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/lib/gcc/ris

12

0xC7, 0x00, 0x9C, 0xC7, 0x00, 0x9C, 0xC7,

9x99.

// Row 4 -> C7009CC7009CC700

Row 5 -> 1DD72092D2539CC7

13

0x1D, 0xD7, 0x20, 0x92, 0xD2, 0x53, 0x9C, 0xC7,

> LB C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/lib/gcc/ris

0x00, 0x9C, 0xC7, 0x00, 0x00,

0x00, 0x04,

> 🕒 C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/riscv-none

0x47, 0x70, 0x00, 0x00, 0x00,

0xC0, 0x00, 0xFF,

7 -> 47700000000C000FF

Row

> Le C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/riscv-none

Row 8 -> 814770000000000000

0x81, 0x47, 0x70, 0x00, 0x00, 0x00, 0xC0, 0x00,

> C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/riscv-none

17

0xFF, 0x81, 0x47, 0x6F, 0x00, 0x00, 0x00, 0xE0,

Row

9 -> FF81476F000000E0

> Le C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/riscv-none

0x00, 0xFF, 0x81, 0x40, 0x1C, 0x40, 0x1C, 0x40,

> 🕒 C:/lscc/propel/2.2/sdk/riscv-none-embed-gcc/riscv-none

19

0x1C, 0x40, 0x1C, 0x00, 0x00, 0x00, 0xFF, 0xFF,

// Row 11 -> 1C401C000000FFFF

// Row 12 -> 80FFAAAAFEFFF8FF

20

0x80, 0xFF, 0xAA, 0xAA, 0xFE, 0xFF, 0xF8, 0xFF,

MachXO5_ASC10_Demo/src

0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF

// Row 13 -> FFFFFFFFFFFFF

MachXO5 ASC10 Demo/src/bsp

MachXO5_ASC10_Demo/src/bsp/driver

```

Figure 3.53. Propel SDK - ptm\_asc0\_data.h

The ASC\_Hex\_Reader.exe utility is copied into the L\_ASC10 subfolder, where Platform Designer exports the ASC .hex files. By running the utility in the same folder, the command line does not have to include the full path, as shown in Figure 3.53. For this demo design, the "up" arrow was used with the "left" arrow to edit the "0" to "1" and later to "2" followed by the "enter" key to generate the header files for ASC1 and ASC2. This reduced the amount of typing. This utility could be ported into a graphical user interface, in the future, to simplify this step.

Figure 3.54. Command Prompt - ASC\_Hex\_Reader

# 3.14. Loading the Firmware into Memory

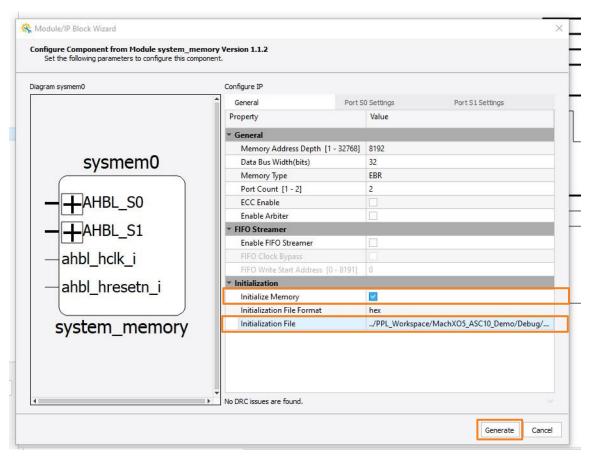

After the Propel SDK tool is used to successfully compile the firmware, we need to go back to Propel Builder and initialize the system memory with the firmware.

- 1. Double-click on the system0\_inst to open the memory IP configuration dialog, shown in Figure 3.55.

- 2. Tick the Initialize Memory checkbox and browse to the Initialization File MachXO5\_ASC10\_Demo.mem

- 3. Click the Generate button.

- 4. Click the **Generate** tool to update the SOC IP RTL.

- 5. Return to Radiant to build the entire project so that it can be programmed into the evaluation board.

Figure 3.55. Propel Builder - System Memory Initialization

There is a shortcut in Radiant for updating the firmware without rebuilding all the SOC and Platform Manager 2 IP. This is useful when developing or modifying the firmware.

1. Click on the ECO Editor tool icon, shown in Figure 3.56, or click Tools -> ECO Editor to open the tool.

Figure 3.56. Radiant ECO Editor - Icon

© 2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

2. When the tool opens, click on the **Memory Initialization** tab, shown in Figure 3.57, near the bottom of the screen.

Figure 3.57. Radiant ECO Editor – Memory Initialization Tab

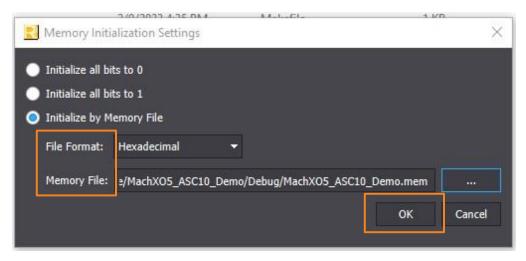

3. Double-click the **Choose File** as shown in Figure 3.58, and the **Memory Initialization Settings** window will open, shown in Figure 3.59.

Figure 3.58. Radiant ECO Editor - Choose File

In the Settings window, select Hexadecimal for the File Format and browse to the MachXO5\_ASC10\_Demo.mem file, then click OK.

Figure 3.59. Radiant ECO Editor - Settings

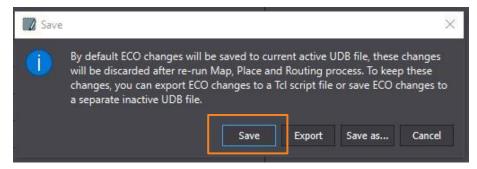

5. After clicking the **OK** button, double-click on the **Export Files** and the **Save** dialog box will open as shown in Figure 3.60. Click the **Save** button and Radiant will include the latest firmware into the programming file without having to repeat the synthesis, map, and P&R processes as shown in Figure 3.61.

© 2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.60. Radiant ECO Editor - Save

Figure 3.61. Radiant ECO Editor - Exporting Files

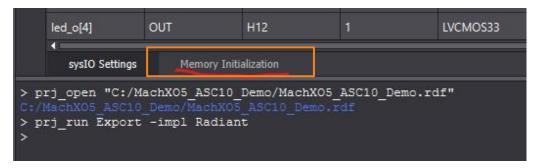

6. With the ECO Editor tool left open, the shortcut gets even shorter by using the Tcl Console to rerun the command. Use the "up" arrow (on the keyboard) to bring the command to the cursor and press the "Enter" key, as shown in Figure 3.62. Repeat the Save and Export Files operations and a new programming file is ready for testing.

```

> prj open "C:/MachXO5 ASC10 Demo/MachXO5 ASC10 Demo.rdf"

prj_run Export -impl Radiant

eco_config_memory -mem_ld {1.1.2} -init_file {C:/MachXO5_ASC10_Demo/PPL_Workspace/MachXO5_ASC10_Demo/Debug/MachXO5_ASC10_Demo.mem} -format HEX

prj_run Export -impl Radiant

eco_config_memory -mem_id {1.1.2} -init_file {C:/MachXOS_ASC10_Demo/PPL_Workspace/MachXOS_ASC10_Demo/Debug/MachXOS_ASC10_Demo.mem} -format HEX

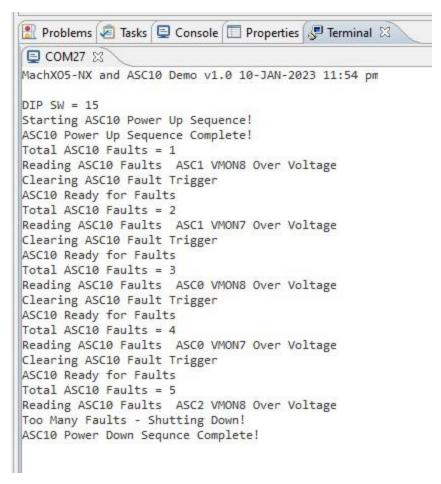

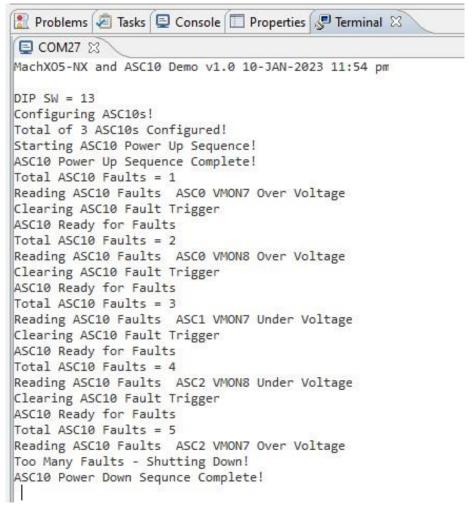

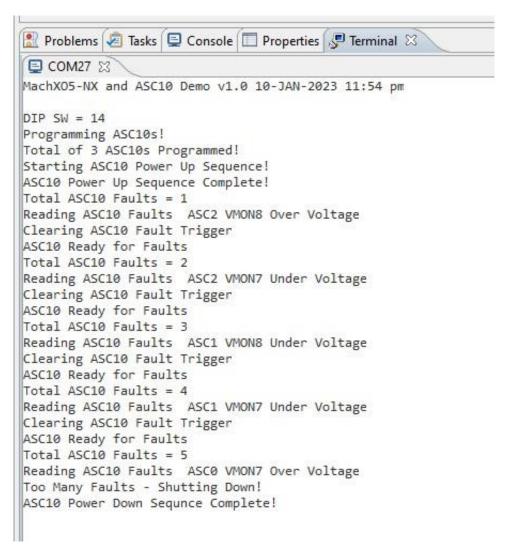

```