# **RISC-V RX and LPDDR4 Memory Controller**

# **Reference Design**

FPGA-RD-02278-1.1

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## **Contents**

| Contents                                                                         |    |

|----------------------------------------------------------------------------------|----|

| Abbreviations in This Document                                                   |    |

| 1. Introduction                                                                  |    |

| 1.1. Quick Facts                                                                 |    |

| 1.2. Features                                                                    |    |

| 1.3. Naming Conventions                                                          |    |

| 1.3.1. Nomenclature                                                              |    |

| 1.3.2. Signal Names                                                              |    |

| 2. Directory Structure and Files                                                 |    |

| 3. Functional Description                                                        | 11 |

| 3.1. Design Block Diagram                                                        | 11 |

| 3.2. Clocking Scheme                                                             |    |

| 3.2.1. Clocking Scheme Overview – CertusPro-NX Devices                           |    |

| 3.2.2. Clocking Scheme Overview - Lattice Avant Devices                          |    |

| 3.3. Reset Scheme                                                                | 14 |

| 4. IP Configuration and Parameter Description                                    | 15 |

| 4.1. RISC-V RX CPU                                                               | 15 |

| 4.2. LPDDR4 Memory Controller                                                    |    |

| 4.2.1. LPDDR4 Memory Controller for CertusPro-NX Devices                         |    |

| 4.2.2. DDR Memory Controller                                                     | 19 |

| 4.3. SPI Flash Memory Controller                                                 | 23 |

| 4.4. Tightly Coupled Memory                                                      | 25 |

| 4.5. AXI4 Interconnect                                                           | 27 |

| 5. Signal Description                                                            | 30 |

| 6. RISC-V RX Software Flow                                                       | 32 |

| 6.1. RISC-V RX Boot up Sequence                                                  | 32 |

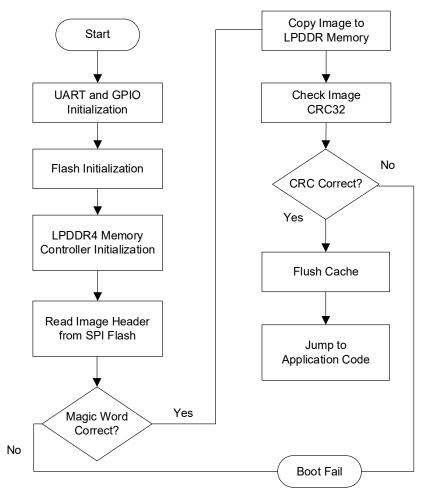

| 6.2. Bootloader Software Flow Chart                                              | 32 |

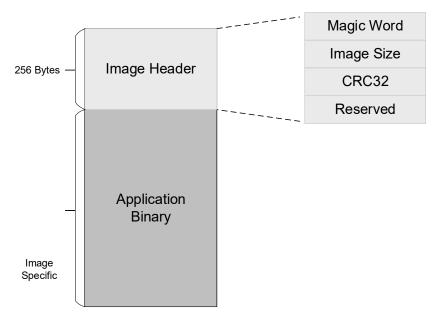

| 6.3. Application Image Format                                                    |    |

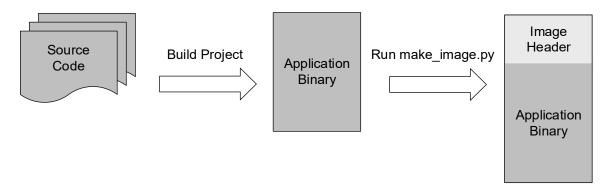

| 6.4. Application Image Generation                                                |    |

| 7. Implementing the Reference Design on the Board                                |    |

| 7.1. Extracting the Reference Design Files                                       |    |

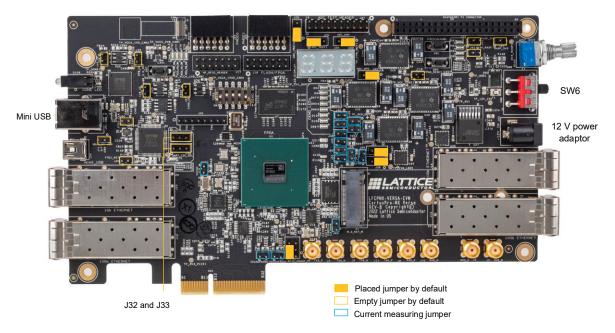

| 7.2. Setting up the CertusPro-NX Versa Board                                     |    |

| 7.3. Setting up the Lattice Avant-E Evaluation Board                             |    |

| 7.4. Setting up the UART Terminal                                                |    |

| 7.5. Programming the Application Image to SPI Flash                              |    |

| 7.6. Programming the FPGA Bitstream                                              |    |

| 7.7. Verifying the Results                                                       |    |

| 8. Compiling the Reference Design                                                |    |

| 8.1. Building and Generating the RISC-V CPU using the Lattice Propel Builder     |    |

| 8.2. Synthesizing RTL Files and Generating the Bitstream using the Lattice Radio |    |

| 8.3. Building the Software Project using Lattice Propel SDK                      |    |

| 8.3.1. Setting Up a New Lattice Propel SDK Workspace                             |    |

| 8.3.2. Building Bootloader and Application Software                              |    |

| 8.4. Pre-initializing Tightly Coupled Memory                                     |    |

| 8.5. Generating the Flash Image                                                  |    |

| 9. Customizing the Reference Design                                              |    |

| 9.1. Changing LPDDR4 Memory Controller Parameters                                |    |

| 9.2. Adding New Component to the Lattice Propel Builder System                   |    |

| 9.2.1. Hardware Flow                                                             |    |

| 9.2.2. Software Flow                                                             |    |

| 9.3. Changing the Application Image Load Address                                 |    |

| 9.4. Updating Linker Script to LPDDR4 Memory Address                             | 51 |

| 10. Debugging the Design                                         | 53 |

|------------------------------------------------------------------|----|

| 10.1. SPI Flash Programming Fail                                 |    |

| 10.1.1. Check Flash Device for CertusPro-NX Devices              | 53 |

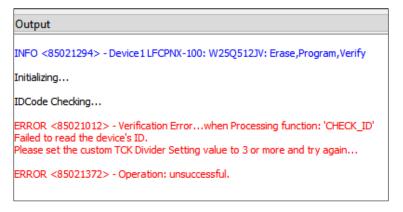

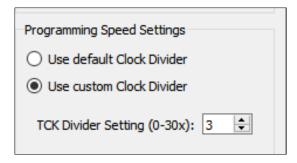

| 10.1.2. Check TCK Divider Setting                                | 54 |

| 10.1.3. Check Cable Settings                                     |    |

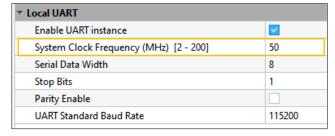

| 10.2. UART Serial Terminal Prints Incorrect Characters           |    |

| 11. Known Issues                                                 | 56 |

| 11.1. Avant LPDDR4 Link Training Failure                         | 56 |

| 11.1.1. Avant DDR Memory Controller IP Constraints Update        | 56 |

| 11.1.2. Avant DDR Memory Controller IP Driver Header File Update | 56 |

| 12. Resource Utilization                                         | 57 |

| References                                                       | 58 |

| Technical Support Assistance                                     | 59 |

| Revision History                                                 |    |

|                                                                  |    |

## **Figures**

| Figure 2.1. Directory Structure                                                                     | 10 |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 3.1. Reference Design Top Level Block Diagram                                                | 11 |

| Figure 3.2. Clocking Block Diagram – CertusPro-NX Devices                                           | 12 |

| Figure 3.3. Clocking Block Diagram - Lattice Avant Devices                                          | 13 |

| Figure 3.4. Reset Scheme Block Diagram                                                              | 14 |

| Figure 4.1. RISC-V RX CPU IP Configuration                                                          | 15 |

| Figure 4.2. LPDDR4 Memory Controller IP Configuration for CertusPro-NX Devices                      | 17 |

| Figure 4.3. LPDDR4 Memory Controller IP Configuration for Lattice Avant Devices – General Tab       | 19 |

| Figure 4.4. LPDDR4 Memory Controller IP Configuration for Lattice Avant Devices – Training Settings | 20 |

| Figure 4.5. SPI Flash Memory Controller IP Configuration                                            | 23 |

| Figure 4.6. Tightly Coupled Memory IP Configuration                                                 | 25 |

| Figure 4.7. AXI4 Interconnect IP Configuration                                                      | 27 |

| Figure 6.1. Boot up Sequence                                                                        | 31 |

| Figure 6.2. Bootloader Software Flow                                                                | 32 |

| Figure 6.3. Application Image Format                                                                | 33 |

| Figure 6.4. Application Image Generation                                                            | 34 |

| Figure 7.1. CertusPro-NX Versa Board                                                                | 35 |

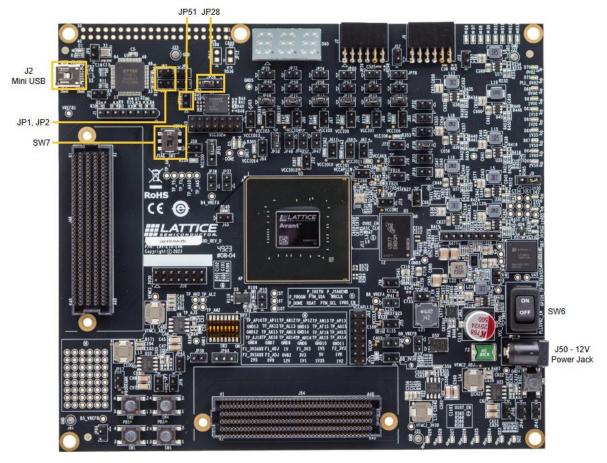

| Figure 7.2. Lattice Avant-E Evaluation Board                                                        |    |

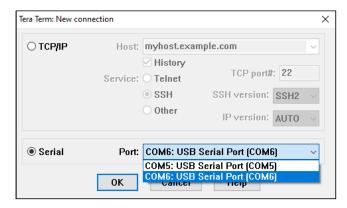

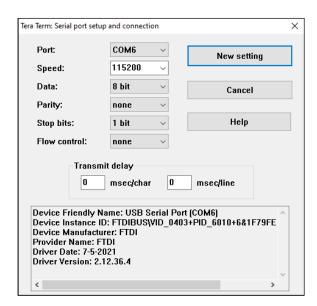

| Figure 7.3. Tera Term New Connection                                                                |    |

| Figure 7.4. Tera Term Serial Port Setup and Connection                                              | 37 |

| Figure 7.5. Windows Start Menu > Radiant Programmer                                                 |    |

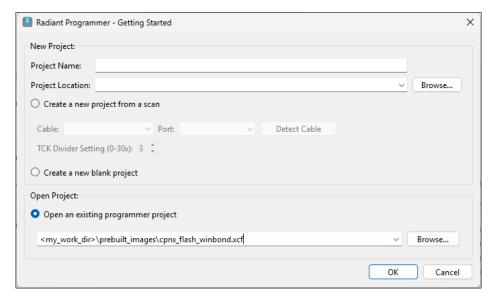

| Figure 7.6. Radiant Programmer - Getting Started Dialog Box                                         |    |

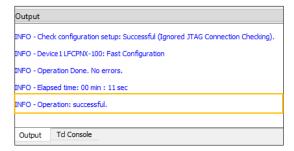

| Figure 7.7. Output Console                                                                          |    |

| Figure 7.8. Output Console                                                                          |    |

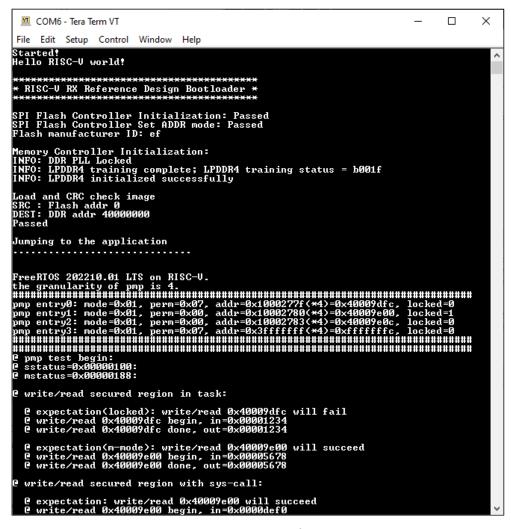

| Figure 7.9. RISC-V RX and LPDDR4 Reference Design Results                                           |    |

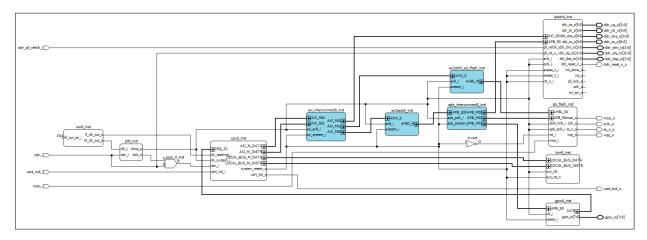

| Figure 8.1. Lattice Propel Builder Schematic view                                                   |    |

| Figure 8.2. Windows Start Menu > Lattice Propel Builder                                             |    |

| Figure 8.3. TCL Console – No Error for Validate                                                     |    |

| Figure 8.4. TCL Console – No Error for Generate                                                     |    |

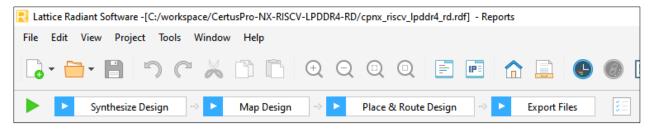

| Figure 8.5. Windows Start Menu > Radiant Software                                                   |    |

| Figure 8.6. Export Files                                                                            |    |

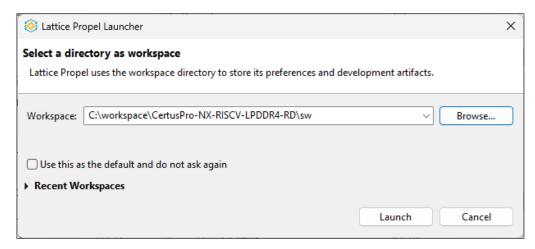

| Figure 8.7. Windows Start Menu > Lattice Propel 2025.1                                              |    |

| Figure 8.8. Propel SDK Workspace Setup                                                              |    |

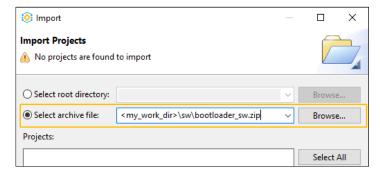

| Figure 8.9. Select Existing Projects                                                                |    |

| Figure 8.10. Import Projects                                                                        |    |

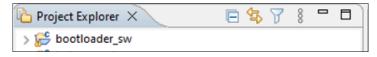

| Figure 8.11. Project Explorer                                                                       |    |

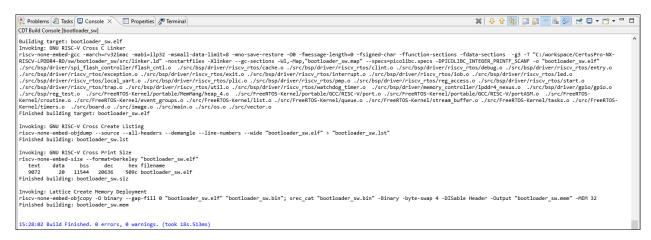

| Figure 8.12. Console                                                                                |    |

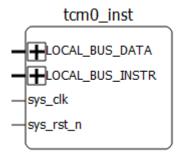

| Figure 8.13. systemO_inst Block                                                                     |    |

| Figure 8.14. Tightly Coupled Memory IP Setting to Pre-initialize with Bootloader Software           |    |

| Figure 8.15. Python Verification                                                                    |    |

| Figure 9.1. lpddr4_inst Block                                                                       |    |

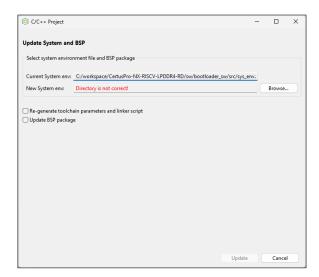

| Figure 9.2. New System Error                                                                        |    |

| Figure 10.1. Flash Device Properties for Macronix                                                   |    |

| Figure 10.2. Flash Device Properties for Winbond                                                    |    |

| Figure 10.3. TCK Divider Error                                                                      |    |

| Figure 10.4. Programming Speed Settings                                                             |    |

| Figure 10.5. UART Settings                                                                          | 55 |

## **Tables**

| Table 1.1. Reference Design Summary                                            | 8  |

|--------------------------------------------------------------------------------|----|

| Table 2.1. Directory List                                                      | 10 |

| Table 3.1. Clock Description – CertusPro-NX Target Device                      | 12 |

| Table 3.2. Clock Signal Description – Lattice Avant Target Device              | 13 |

| Table 3.3. Reset Signal Description                                            | 14 |

| Table 4.1. RISC-V RX IP Configuration                                          | 16 |

| Table 4.2. LPDDR4 Memory Controller IP Configuration for CertusPro-NX Devices  |    |

| Table 4.3. LPDDR4 Memory Controller IP Configuration for Lattice Avant Devices | 20 |

| Table 4.4. SPI Flash Memory Controller IP Configuration                        | 23 |

| Table 4.5.Tightly Coupled Memory IP Configuration                              | 26 |

| Table 5.1. Primary I/O                                                         |    |

| Table 6.1. Application Image Header                                            | 33 |

| Table 7.1. Programming Files Selection                                         | 38 |

| Table 9.1. LPDDR4 Memory Controller IP Parameters Customization                | 49 |

| Table 12.1. Resource Utilization for CertusPro-NX Devices                      |    |

| Table 12.2. Resource Utilization for Lattice Avant Devices                     | 57 |

## **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation        | Definition                                                    |

|---------------------|---------------------------------------------------------------|

| AHB                 | Advanced High-Performance Bus                                 |

| APB                 | Advanced Peripheral Bus                                       |

| API                 | Application Programming Interface                             |

| AXI4                | Advanced eXtensible Interface 4                               |

| BSP                 | Board Support Package                                         |

| CLINT               | Core Local Interrupt controller                               |

| CPU                 | Central Processing Unit                                       |

| PLIC                | Platform Level Interrupt Controller                           |

| RTOS                | Real Time Operating System                                    |

| SoC                 | System on Chip                                                |

| IP                  | Intellectual Property (core)                                  |

| HDL                 | Hardware Description Language                                 |

| JTAG                | Joint Test Action Group (IEEE 1149.1)                         |

| PLL                 | Phase-Locked Loop                                             |

| SDRAM               | Synchronous Dynamic Randon-Access Memory                      |

| SPI                 | Serial Peripheral Interface                                   |

| UART                | Universal Asynchronous Receiver-Transmitter                   |

| GPIO                | General Purpose Input/Output                                  |

| TCK                 | Test Clock (JTAG)                                             |

| CRC                 | Cyclic Redundancy Check                                       |

| SDK                 | Software Development Kit                                      |

| TCL                 | Tool Command Language                                         |

| EBR                 | Embedded Block RAM                                            |

| DDR                 | Double Data Rate (memory)                                     |

| LVSTL_I / LVSTL11_I | Low Voltage Sub Series Terminated Logic (I/O standard)        |

| RX                  | Receive (or RISC-V RX core)                                   |

| TXD / RXD           | Transmit Data / Receive Data                                  |

| MSB                 | Most Significant Bit                                          |

| TDM                 | Time Division Multiplexing (implied in memory access context) |

| R/W                 | Read/Write                                                    |

| TCM                 | Tightly Coupled Memory                                        |

## 1. Introduction

The RISC-V RX CPU and LPDDR4 Memory Controller Reference Design demonstrates how to use the RISC-V RX soft IP and LPDDR4 memory controller in Lattice Avant™ and CertusPro™-NX FPGA devices.

In this design, the CPU connects to the LPDDR4 memory controller IP to interface with external LPDDR4 SDRAM. The design shows how the CPU executes software stored in external SDRAM, which is useful for applications that require more memory than the FPGA's on-chip memory can provide. It includes a sample bootloader program that loads software from an SPI Flash device into the LPDDR4 SDRAM. The RISC-V RX CPU accesses all system peripherals through the AXI Interconnect and bridges.

The Lattice Semiconductor RISC-V RX CPU integrates a 32-bit RISC-V CPU core and several submodules, including the Platform-Level Interrupt Controller (PLIC), Core Local Interrupter (CLINT), and Watchdog. The latest RISC-V RX supports RV32IMACF instruction set and includes a JTAG-compliant debug feature (IEEE 1149.1). The CPU core accesses external modules through either AXI or Local Bus Interface.

The Lattice Semiconductor LPDDR4 Memory Controller IP Core offers a complete solution for interfacing with LPDDR4 SDRAM. Lattice provides a turnkey package that includes the controller, DDR PHY, and the necessary clocking and training logic. The LPDDR4 Memory Controller IP Core simplifies integration with user application designs by supporting the AXI4 interface which reduces the need to manage LPDDR4 SDRAM signals directly.

#### 1.1. Quick Facts

You can download the reference design files for the RISC-V RX and LPDDR4 Memory Controller from the Lattice Semiconductor website.

**Table 1.1. Reference Design Summary**

|                       | Target device             | CertusPro-NX devices                              |  |

|-----------------------|---------------------------|---------------------------------------------------|--|

| General               | Target device             | Lattice Avant-E devices                           |  |

|                       | Source code format        | Verilog, C                                        |  |

|                       | Functional simulation     | Not supported                                     |  |

| Simulation            | Timing simulation         | Not performed                                     |  |

|                       | Test bench                | Not available                                     |  |

|                       |                           | Lattice Propel™ Design Environment 2025.1         |  |

|                       | Software tool and version | Lattice Radiant™ software version 2025.1          |  |

|                       |                           | Python 3.11.x or later                            |  |

|                       |                           | RISC-V RX v2.6.0                                  |  |

|                       |                           | LPDDR4 Memory Controller for Nexus Devices v2.6.0 |  |

|                       |                           | DDR Memory Controller v2.6.0 (For Avant devices)  |  |

| Software Requirements |                           | SPI Flash Memory Controller v2.0.0                |  |

|                       | ID version                | Tightly Coupled Memory v1.5.2                     |  |

|                       | IP version                | AXI4 Interconnect v2.2.0                          |  |

|                       |                           | AXI4 to APB Bridge v1.4.0                         |  |

|                       |                           | AXI4 to AHB-Lite Bridge v1.4.0                    |  |

|                       |                           | APB Interconnect v1.3.0                           |  |

|                       |                           | GPIO v1.8.0                                       |  |

|                       | Doord                     | CertusPro-NX Versa Board                          |  |

| Hardware Requirements | Board                     | Lattice Avant-E Evaluation Board                  |  |

|                       | Cable                     | USB-A to Mini-B cable                             |  |

#### 1.2. Features

The key features of the reference design include:

- RISC-V RX soft IP features described in RISC-V RX CPU IP-Lattice Propel Builder 2025.1 (FPGA-IPUG-02280)

- LPDDR4 Memory Controller Interface IP Core for CertusPro-NX device features described in LPDDR4 Memory Controller IP Core for Nexus Devices (FPGA-IPUG-02127)

- LPDDR4 Memory Controller Interface IP Core for Lattice Avant device features described in DDR Memory Controller IP Core (FPGA-IPUG-02208)

- AXI4 Interconnect features described in AXI4 Interconnect IP Core User Guide (FPGA-IPUG-02196)

- SPI Flash memory controller features described in SPI Flash Memory Controller IP Core User Guide (FPGA-IPUG-02134)

- Bootloader software example to copy (with CRC check) application software from flash to SDRAM

- FreeRTOS<sup>TM</sup> demo as application software that runs on SDRAM

### 1.3. Naming Conventions

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.3.2. Signal Names

- n are active low (asserted when value is logic 0)

- \_i are input signals

- <u>o</u> are output signals

- \_io are bi-directional signals

## 2. Directory Structure and Files

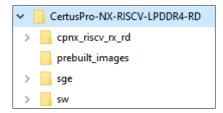

Figure 2.1 shows the directory structure.

Figure 2.1. Directory Structure

Table 2.1 shows the list of directories included in the reference design package.

**Note:** In the reference design targeting the Lattice Avant device, folder and file name uses *avant* in place of *cpnx*.

#### Table 2.1. Directory List

| Directory/File   | Description                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| cpnx_riscv_rx_rd | Contains the Lattice Propel Builder project and generated HDL files for IP.                                   |

| prebuilt_images  | Contains the bitstream file, software image file, Lattice Radiant Programmer scripts, and miscellaneous files |

| sge              | Contains the software handoff file from the Lattice Propel Builder project.                                   |

| SW               | Contains the software project and source code used in this reference design.                                  |

## 3. Functional Description

## 3.1. Design Block Diagram

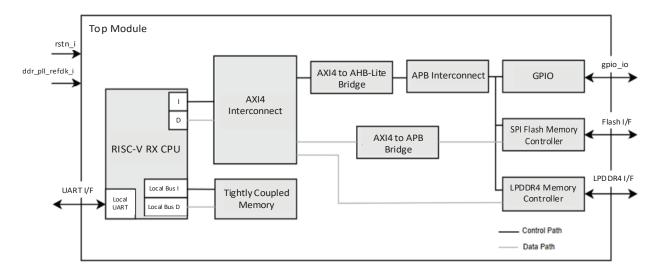

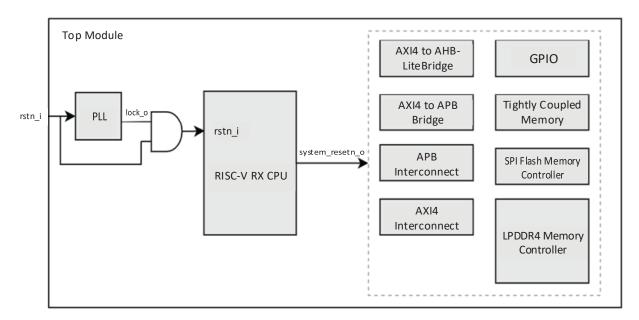

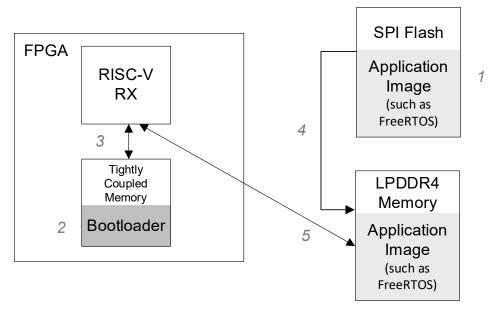

The reference design demonstrates a complete and functional RISC-V CPU system built using Lattice Propel Builder. All system components are available within Lattice Propel Builder, where they are instantiated, connected and used to generate the corresponding RTL design files.

Figure 3.1 illustrates the top-level block diagram and interconnections of the reference design.

Figure 3.1. Reference Design Top Level Block Diagram

The design includes the following components:

- RISC-V RX CPU with local UART

- LPDDR4 Memory Controller

- SPI Flash Controller

- Tightly Coupled Memory

- AXI4 Interconnect

- AXI4 to APB ridge

- AXI4 to AHB-Lite Bridge

- APB Interconnect

- General Purpose I/O (GPIO)

Each component in the block diagram is instantiated using IP available in Lattice Propel Builder. The features and parameters of each IP are detailed in the IP Configuration and Parameter Description section.

Figure 3.1 shows the multiple interfaces present at the top level of the design. The Signal Description section provides details on the signals associated with each interface.

### 3.2. Clocking Scheme

This section describes the clocking scheme used in the reference design. While the overall structure remains similar, there are minor differences between the clocking scheme for Certus Pro-NX and Lattice Avant devices. For more details refer to the Clocking Scheme Overview – Certus Pro-NX Devices section or to the Clocking Scheme Overview - Lattice Avant Devices section.

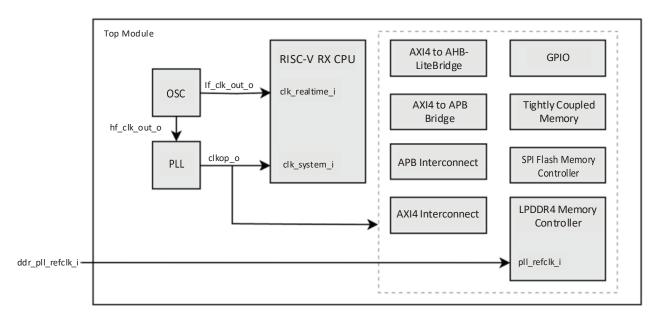

#### 3.2.1. Clocking Scheme Overview – CertusPro-NX Devices

Figure 3.2 illustrates the clocking scheme of the reference design when targeting the CertusPro-NX device. Table 3.1 lists the details of each clock signal used in the design.

Figure 3.2. Clocking Block Diagram - CertusPro-NX Devices

Table 3.1. Clock Description - CertusPro-NX Target Device

| Clock Signal     | Source                        | Destination                                | Clock<br>Frequency  | Description                                                                                                            |

|------------------|-------------------------------|--------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|

| lf_clk           | FPGA Oscillator               | RISC-V RX CPU                              | 32 kHz              | Low-speed real-time clock input to RISC-V RX CPU                                                                       |

| hf_clk           | FPGA Oscillator               | PLL                                        | 50 MHz              | Reference clock input to the PLL                                                                                       |

| clkop            | PLL                           | RISC-V RX CPU,<br>all IPs in the<br>system | 50 MHz <sup>1</sup> | PLL primary clock output drives the high-speed clock input of the RISC-V RX CPU and all other components in the system |

| ddr_pll_refclk_i | Oscillator on development kit | LPDDR4 Memory<br>Controller                | 100 MHz             | Reference clock input to the LPDDR4 Memory Controller's PLL                                                            |

#### Note:

The PLL clkop output frequency is adjustable and can be set higher than 50 MHz to increase the clock frequency of the RISC-V RX CPU and the overall system. However, the current reference design achieves timing closure at 50 MHz, so the PLL clkop is configured to operate at that frequency.

12

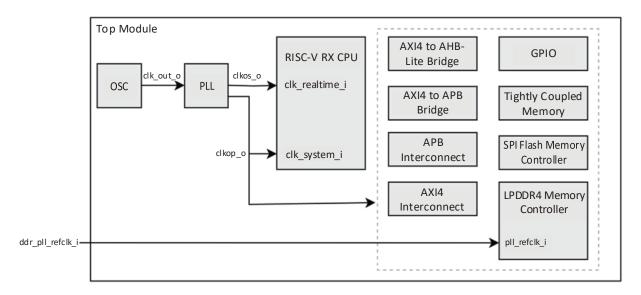

#### 3.2.2. Clocking Scheme Overview - Lattice Avant Devices

Figure 3.2 illustrates the clocking scheme of the reference design when targeting the Lattice Avant device. Table 3.1 provides detailed information about each clock signal used in the design.

Figure 3.3. Clocking Block Diagram - Lattice Avant Devices

Table 3.2. Clock Signal Description – Lattice Avant Target Device

| Clock Signal     | Source                        | Destination                                | Clock Frequency         | Description                                                                             |

|------------------|-------------------------------|--------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------|

| clk_out          | FPGA Oscillator               | PLL                                        | 50 MHz                  | Reference clock input to the PLL                                                        |

| clkop            | PLL                           | RISC-V RX CPU,<br>all IPs in the<br>system | 100 MHz <sup>1</sup>    | PLL's primary clock output for RISC-V RX high-<br>speed input and all system components |

| clkos            | PLL                           | RISC-V RX CPU                              | 16.384 MHz <sup>2</sup> | PLL's secondary clock output for RISC-V RX low-speed real-time clock input              |

| ddr_pll_refclk_i | Oscillator on development kit | LPDDR4 memory controller                   | 100 MHz                 | Reference clock input to the LPDDR4 memory controller PLL                               |

#### Notes:

- The PLL clkop output frequency is adjustable and can be set higher than 100 MHz to increase the clock frequency of the RISC-V RX and the overall system. However, the current reference design achieves timing closure at 100 MHz, so the PLL clkop is configured to operate at that frequency.

- For Lattice Avant family devices, the 32 kHz output cannot be directly obtained from the OSC and PLL. Therefore, a 512-clock divider is implemented for the real-time clock port of the RX core, clk realtime i. It is recommended to use a 16.384 MHz clock signal as the input to this port, which will then generate a 32 kHz clock signal for the mtimecmp and mtime registers. For more detailed information, refer to RISC-V RX CPU IP-Lattice Propel Builder 2025.1 (FPGA-IPUG-02280).

#### **Reset Scheme** 3.3.

This section describes the reset scheme used in the reference design for both CertusPro-NX and Lattice Avant target devices. Figure 3.4 illustrates the reset block diagram, while Table 3.3 provides detailed information about each reset signal.

Figure 3.4. Reset Scheme Block Diagram

**Table 3.3. Reset Signal Description**

| Reset Signal                 | Source                 | Destination               | Description                                                                                                                                                            |

|------------------------------|------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rstn_i                       | Push button on dev kit | PLL reset input           | Reset the PLL                                                                                                                                                          |

| rstn_i<br>(RISC-V RX<br>CPU) | PLL lock and rstn_i    | RISC-V RX CPU reset input | Release RISC-V RX CPU from reset once rstn_i is not asserted AND PLL is locked                                                                                         |

| system_rstn                  | RISC-V RX CPU          | All components in system  | RISC-V RX CPU output reset is used to reset all components in the system. This trigger resets during CPU debugging mode and is synchronous to the system clock domain. |

## 4. IP Configuration and Parameter Description

The reference design is developed using Lattice Propel Builder. Lattice Propel Builder generates the top-level HDL file, which serves as the top module of the design. Design parameterization is performed by configuring the IP blocks within Lattice Propel Builder. This section describes the following IPs and their configurable parameters. The screenshots provided are for reference only. The details may vary depending on the version of the IP or software being used.

- RISC-V RX CPU

- LPDDR4 Memory Controller for Nexus Devices

- DDR Memory Controller (for Avant Devices)

- SPI Flash Memory Controller

- Tightly Coupled Memory

- AXI4 Interconnect

- AXI4 to APB Bridge

- AXI4 to AHB-Lite Bridge

- APB Interconnect

- GPIO

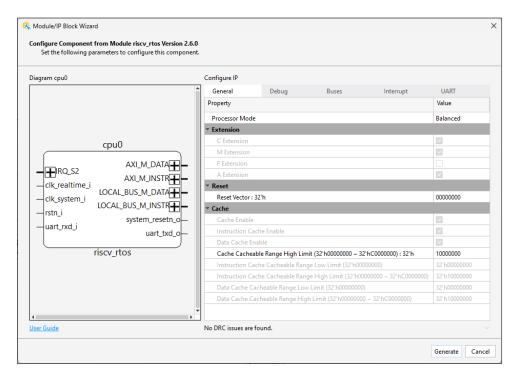

#### 4.1. RISC-V RX CPU

The RISC-V RX CPU IP features AXI-based instruction and data ports. The instruction port connects to memory that stores the software code executed by the CPU, while the data port connects to memory and peripherals for control operations. The design enables the local UART feature to support communication over a serial protocol. Figure 4.1 shows the configuration of the RISC-V RX CPU IP.

Figure 4.1. RISC-V RX CPU IP Configuration

Table 4.1 provides the configuration details of the RISC-V RX IP.

**Table 4.1. RISC-V RX IP Configuration**

| Property                                      | Value    | Description                                                                                                                           |  |

|-----------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| General Tab                                   |          |                                                                                                                                       |  |

| CPU Mode                                      | Balanced | Specifies the CPU mode. The default value is used to balance performance and resource utilization.                                    |  |

| Reset Vector                                  | 00000000 | Reset vector initial value.                                                                                                           |  |

| Cache Cacheable Range High Limit              | 10000000 | Specifies the higher limit of the cache's cacheable range.                                                                            |  |

| Debug Tab                                     |          |                                                                                                                                       |  |

| Enable Debug                                  | True     | Enable the JTAG interface for CPU debug capability.                                                                                   |  |

| Enable Debug On Off Control Port              | False    | Enables the presence of the Debug On Off Control port on the generated IP. The port is disabled in this design.                       |  |

| JTAG Type                                     | Hard     | Specifies the JTAG Type.                                                                                                              |  |

| Extend JTAG Channel                           | False    | Enables the JTAG channel's range extension.                                                                                           |  |

| JTAG Channel                                  | 14       | Specifies the channel of RX JTAG block which is used by the debugger.                                                                 |  |

| Bus Tab                                       | ,        |                                                                                                                                       |  |

| Enable Local Bus                              | True     | Enables the presence of the local bus on the generated IP. In this design, tightly coupled memory is connected to the local bus port. |  |

| Enable AXI Instruction Ports                  | True     | Enables the presence of AXI instructions ports on the generated IP.                                                                   |  |

| AXI Instruction Interface Register Slice Type | 0        | Type of AXI instruction ports channel register slice. The default is used in this design, which is bypass register slice.             |  |

| AXI Data Interface Register Slice Type        | 0        | Type of AXI data ports channel register slice. The default is used in this design, which bypasses register slice.                     |  |

| AXI ID Width                                  | 4        | Specifies the AXI ID signal width.                                                                                                    |  |

| AXI Data Ports ID Number                      | 0        | Specifies the value of RX AXI data ports ID signals.                                                                                  |  |

| AXI Instruction Ports ID Number               | 0        | Specifies the value of RX AXI instructions ports ID signals.                                                                          |  |

| Enable CXU Ports                              | False    | CXU ports are disabled in this design.                                                                                                |  |

| Enable RVFI                                   | False    | RVFI interface is disabled in this design.                                                                                            |  |

| Interrupt Tab                                 |          |                                                                                                                                       |  |

| Enable CLINT                                  | True     | Enable CLINT is selectable when RX is not in Fmax mode.                                                                               |  |

|                                               | _        | Enable CLINT is fixed as disabled when RX is in Fmax mode.                                                                            |  |

| Enable PLIC                                   | True     | Enable PLIC is selectable when RX is not in Fmax mode.  Enable PLIC is fixed as disabled when RX is in Fmax mode.                     |  |

| Enable Non-maskable Interrupt                 | False    | Non-maskable interrupt is disabled in this design.                                                                                    |  |

| Enable Non maskable intellupt                 | i aise   | Interrupt for supervisor mode is disabled; all external interrupts go                                                                 |  |

| Enable Interrupt for Supervisor Mode          | False    | to the Machine mode only.                                                                                                             |  |

| Width of Interrupt Priority Register          | 3        | Specifies the data width of PLIC priority register. The default is 3-bit.                                                             |  |

| Number of User Interrupt Request              | 1        | Specifies the supported number of interrupts for peripherals.  There is only interrupt from GPIO for this design.                     |  |

| Enable CDC Register for IRQ_S2                | False    | The ports for 2-stage synchronizer on enabled IRQ_S interface are disabled in this design.                                            |  |

| UART Tab                                      |          |                                                                                                                                       |  |

| Enable UART Instance                          | True     | Enable local UART within the RISC-V RX CPU. There is no need to add extra UART IP to the system.                                      |  |

| System Clock Frequency [2 – 200 MHz]          | 100 MHz  | Specify the clock frequency for RISC-V RX CPU clk_system_i to match with the actual clock frequency.                                  |  |

| Serial Data Width                             | 8        | 8-bit of serial data                                                                                                                  |  |

| Stop Bits                                     | 1        | 1 bit of stop                                                                                                                         |  |

| Property                | Value  | Description                                                                                                                                                           |

|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Parity           | False  | Parity is not enabled                                                                                                                                                 |

| UART Standard Baud Rate | 115200 | Baud rate of 115,200. Needs matching with terminal setting.                                                                                                           |

| Enable UART SIM         | False  | UART SIM is disabled in this design. The RX core does not drive uart_txd_o to output the character signal. Strings are not printed inside simulation tool transcript. |

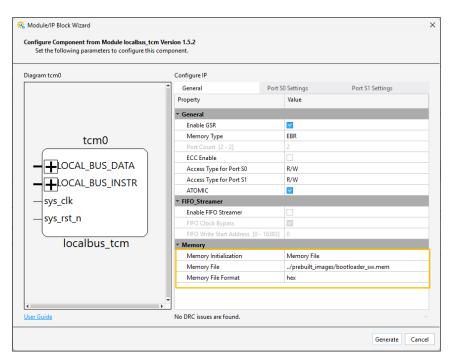

### 4.2. LPDDR4 Memory Controller

The LPDDR4 Memory Controller IP enables access to external LPDDR4 memory modules, which can store both CPU software code and data. The memory controller IP differs between CertusPro-NX and Lattice Avant devices. The following subsections describe the IP configuration for each device family.

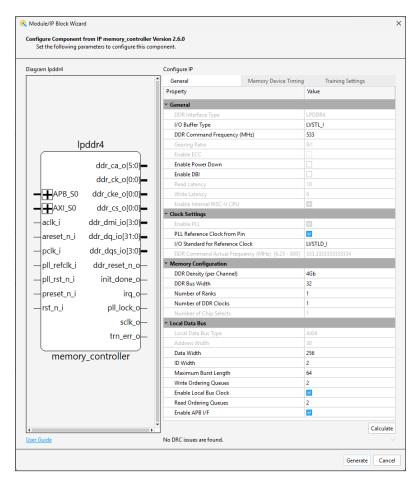

#### 4.2.1. LPDDR4 Memory Controller for CertusPro-NX Devices

Figure 4.2 shows the LPDDR4 Memory Controller IP configuration for the CertusPro-NX devices.

Figure 4.2. LPDDR4 Memory Controller IP Configuration for CertusPro-NX Devices

Table 4.2 provides the configuration details of the LPDDR4 Memory Controller IP for the CertusPro-NX device.

Table 4.2. LPDDR4 Memory Controller IP Configuration for CertusPro-NX Devices

| Property                     | Value   | Description                                                                                                                                                                                                                                                                         |  |

|------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General Tab                  |         |                                                                                                                                                                                                                                                                                     |  |

| I/O Buffer Type              | LVSTL_I | Set the I/O buffer type standard to LVSTL_I for better performance.                                                                                                                                                                                                                 |  |

| DDR Command Frequency        | 533 MHz | Maximum supported frequency on CertusPro-NX devices.                                                                                                                                                                                                                                |  |

| Enable Power Down            | False   | Not used in this reference design                                                                                                                                                                                                                                                   |  |

| Enable DBI                   | False   | Not used in this reference design                                                                                                                                                                                                                                                   |  |

| PLL Reference Clock from Pin | True    | Export the PLL reference clock input to be connected from the top module. Refer to the Clocking Scheme Overview – CertusPro-NX Devices section for details.                                                                                                                         |  |

| DDR Density (per Channel)    | 4 Gb    | Configure the DDR DRAM density based on the memory module on the development kit.                                                                                                                                                                                                   |  |

| DDR Bus Width                | 32      | Configure the DDR DRAM bus width based on the memory module on the development kit.                                                                                                                                                                                                 |  |

| Number of Ranks              | 1       | Configure the number of ranks based on the memory module on the development kit.                                                                                                                                                                                                    |  |

| Number of DDR Clocks         | 1       | Configure the number of CK/CK# clock pairs to be driven to DDR DRAM based on the memory module on development kit. There is only 1 DDR clock channel available for CertusPro-NX Versa Board.                                                                                        |  |

| Data Width                   | 256     | Data width on the AXI interface of the memory controller.                                                                                                                                                                                                                           |  |

| ID Width                     | 2       | ID width on the AXI interface of the memory controller. This value must match with the AXI Manager in the interconnect IP. Refer to the AXI4 Interconnect section for details.                                                                                                      |  |

| Write Ordering Queues        | 2       | Set the ordering queues that process the write and read data requests. More queues mean better ordering of access to the DDR bus. This minimizes the gaps between accesses but consumes more resources. T default value is used to balance performance and resource utilization.    |  |

| Enable Local Bus Clock       | True    | Enable the clock domain crossing logic for the local data bus.                                                                                                                                                                                                                      |  |

| Read Ordering Queues         | 2       | Set the ordering queues that process the write and read data requests.  More queues mean better ordering of access to the DDR bus. This minimizes the gaps between accesses but consumes more resources. The default value is used to balance performance and resource utilization. |  |

| Enable APB I/F               | True    | Enable APB interface, which allows the CPU to access the memory controller registers.                                                                                                                                                                                               |  |

Note: Default settings are used for properties in the Memory Device Timing and the Training Settings tabs.

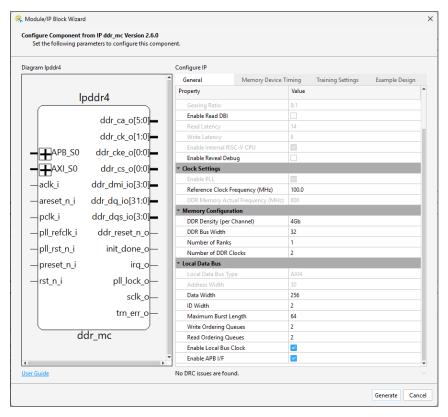

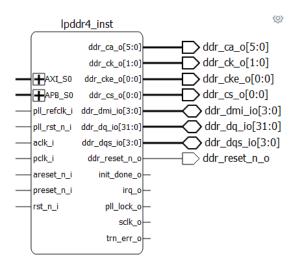

#### 4.2.2. DDR Memory Controller

Figure 4.3 and Figure 4.4 show the DDR4 Memory Controller IP configuration for Lattice Avant devices.

Figure 4.3. LPDDR4 Memory Controller IP Configuration for Lattice Avant Devices - General Tab

Figure 4.4. LPDDR4 Memory Controller IP Configuration for Lattice Avant Devices – Training Settings

Table 4.3 provides the configuration details of the LPDDR4 Memory Controller IP for the Lattice Avant device.

Table 4.3. LPDDR4 Memory Controller IP Configuration for Lattice Avant Devices

| Property                        | Value     | Description                                                                                                                                                             |  |  |

|---------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General Tab                     |           |                                                                                                                                                                         |  |  |

| Interface Type                  | LPDDR4    | Configure the interface type based on the memory module used in the development kit.                                                                                    |  |  |

| I/O Buffer Type                 | LVSTL11_I | Set the I/O buffer to LVSTL_II standard.                                                                                                                                |  |  |

| DDR Command Frequency (MHz)     | 800       | Maximum supported frequency for Lattice Avant devices.                                                                                                                  |  |  |

| Enable DBI                      | False     | Not used in this Reference design.                                                                                                                                      |  |  |

| Reference Clock Frequency (MHz) | 100       | PLL reference clock input connected from the top module. Refer to the Clocking Scheme Overview - Lattice Avant Devices section for details.                             |  |  |

| DDR Density (per Channel)       | 4 Gb      | Configure based on the DDR DRAM density of the memory module on the development kit.                                                                                    |  |  |

| DDR Bus Width                   | 32        | Set according to the DDR DRAM bus width of the memory module on the development kit.                                                                                    |  |  |

| Number of Ranks                 | 1         | Configure based on the number of ranks in the memory module on the development kit.                                                                                     |  |  |

| Number of DDR Clocks            | 2         | Set the number of CK/CK# clock pairs to be driven to DDR DRAM based on the memory module on the development kit. Lattice Avant-E boards support two DDR clock channels. |  |  |

FPGA-RD-02278-1.1

| Property                                 | Value | Description                                                                                                                                                                                                                                                                         |

|------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Width                               | 256   | Specifies the data width on the AXI interface of the memory controller.                                                                                                                                                                                                             |

| ID Width                                 | 2     | Defines the ID width on the AXI interface of the memory controller. Must match the AXI Manager in the Interconnect IP.  Refer to the AXI4 Interconnect section for details.                                                                                                         |

| Maximum Burst Length                     | 64    | Sets the maximum AXI4 burst length. Recommended to adjust based on the system requirements to optimize EBR resource usage. The default value is used to balance performance and resource utilization.                                                                               |

| Write Ordering Queues                    | 2     | Set the ordering queues that process the write and read data requests. More queues mean better ordering of access to the DDR bus. This minimizes the gaps between accesses but consumes more resources. The default value is used to balance performance and resource utilization.  |

| Read Ordering Queues                     | 2     | Set the ordering queues that process the write and read data requests. More queues mean better ordering of access to the DDR bus. This minimizes the gaps between accesses but consumes more resources. The default value is used to balance performance and resource utilization.  |

| Enable Local Bus Clock                   | True  | Enables the clock domain crossing logic for the local data bus.                                                                                                                                                                                                                     |

| Enable APB I/F                           | True  | Enables the APB interface, allowing CPU to access memory controller registers.                                                                                                                                                                                                      |

| Training Settings Tab                    |       |                                                                                                                                                                                                                                                                                     |

| DDR Clock Delay Value                    | 4     | Specifies the DDR clock delay so that the first DQS toggle is at CK = 0 during write leveling. It is recommended to increase this value if write leveling fails                                                                                                                     |

| DDR Clock Delay Value Incr/Decr          | True  | Specifies the adjustment direction Checked: DDR Clock Delay Value is added to the ddr_ck_o signal Unchecked: DDR Clock Delay Value is subtracted from the ddr_ck_o signal                                                                                                           |

| CS Delay Value                           | 0     | Specifies the DDR CS delay value                                                                                                                                                                                                                                                    |

| CS Delay Value Incr/Decr                 | False | Specifies the adjustment direction Checked: CS Delay Value is added to the ddr_cs_o signal Unchecked: CS Delay Value is subtracted from the ddr_cs_o signal                                                                                                                         |

| Address Control Delay Value              | 0     | Specifies the DDR address/control signals delay. It is recommended to increase this value if command bus training fails                                                                                                                                                             |

| Address Control Delay Value<br>Incr/Decr | True  | Specifies the adjustment direction Checked: Address Control Delay Value is added to the DDR address/control signals Unchecked: Address Control Delay Value is subtracted from the DDR address/control signals                                                                       |

| Memory CA_Vref Value for Rank 0          | 25    | Specifies the DRAM CA_Vref Value to be written to LPDDR4 DRAM's MR12 VR-CA and VREF(CA) for Rank0/Rank1. This should be set based on SI/PI simulation for the target board design. Please refer to LPDDR4 JEDEC Standard for allowed values in MR12                                 |

| Memory DQ_Vref Value for Rank 0          | 25    | Specifies the DRAM DQ_Vref Value to be written to LPDDR4 DRAM's MR14 VR(DQ) and VREF(DQ) for Rank0/Rank1. When the register field TRN_OP_REG.mem_vref_training_en=0, this will be used as the final DRAM DQ Vref. Please refer to LPDDR4 JEDEC Standard for allowed values in MR14. |

| Property                  | Value | Description                                                                                                                                                                            |

|---------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC DQS Grp0 Vref Value    | 40    | Specifies the MC DQ_Vref Value for each DQS group when DQ_Vref training is disabled by setting TRN_OP_REG.mc_vref_training_en=0. The theoretical mV value is: Vref decimal value × 5mV |

| MC DQS Grp1 Vref Value    | 40    | Specifies the MC DQ_Vref Value for each DQS group when DQ_Vref training is disabled by setting TRN_OP_REG.mc_vref_training_en=0. The theoretical mV value is: Vref decimal value × 5mV |

| MC DQS Grp2 Vref Value    | 40    | Specifies the MC DQ_Vref Value for each DQS group when DQ_Vref training is disabled by setting TRN_OP_REG.mc_vref_training_en=0. The theoretical mV value is: Vref decimal value × 5mV |

| MC DQS Grp3 Vref Value    | 40    | Specifies the MC DQ_Vref Value for each DQS group when DQ_Vref training is disabled by setting TRN_OP_REG.mc_vref_training_en=0. The theoretical mV value is: Vref decimal value × 5mV |

| CK/CS Slew Rate           | SLOW  | Specifies the CK/CS driver strength                                                                                                                                                    |

| Command Address Slew Rate | SLOW  | Specifies the CA driver strength                                                                                                                                                       |

| DQS Slew Rate             | SLOW  | Specifies the DQS driver strength                                                                                                                                                      |

| DQ/DMI Slew Rate          | SLOW  | Specifies the DQ/DMI driver strength                                                                                                                                                   |

| MC CA Output Impedance    | 34 Ω  | Memory controller CA I/O impedance to reach VDDQ threshold                                                                                                                             |

| MC DQ Output Impedance    | 34 Ω  | Memory controller DQ I/O impedance to reach VDDQ threshold                                                                                                                             |

| MC ODT Value              | 60 Ω  | Memory controller termination resistance value at FPGA                                                                                                                                 |

| CA_ODT Value              | RZQ/4 | Memory side CA ODT resistance value                                                                                                                                                    |

| DQ_ODT Value              | RZQ/4 | Memory side DQ ODT resistance value                                                                                                                                                    |

| SoC_ODT Value             | RZQ/6 | Memory controller ODT resistance value correlating to ZQ calibration                                                                                                                   |

| CK_ODT Override Enable    | False | Overrides the default CK ODT value for the non-terminating rank when option is checked.  Refer to MR22 in LPDDR4 device datasheet for more details                                     |

| CS_ODT Override Enable    | False | Overrides the default CS ODT value for the non-terminating rank when option is checked.  Refer to MR22 in LPDDR4 device datasheet for more details                                     |

| CA_ODT Override Enable    | False | Disable termination for CA when option is checked.  Refer to MR22 in LPDDR4 device datasheet for more details                                                                          |

| ODT-CS/CA/CLK Disable     | False | Disable ODT for CS/CA/CLK when option is checked                                                                                                                                       |

| Pull-Down Drive Strength  | RZQ/6 | Memory side pull-down drive strength value                                                                                                                                             |

#### Notes:

- Default settings are used for all properties in Memory Device Timing.

- Refer to the Known Issues section for details about issues affecting Avant DDR Memory Controller IP version 2.6.0.

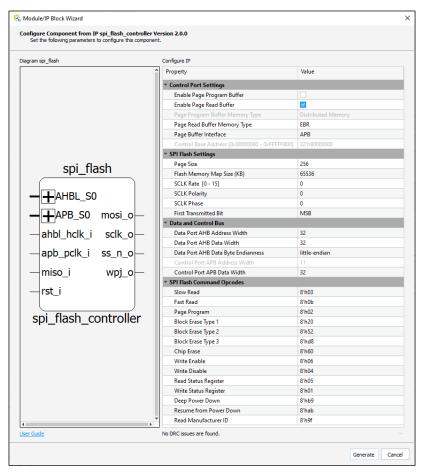

## 4.3. SPI Flash Memory Controller

Figure 4.5 shows the SPI Flash Memory Controller IP configuration

Figure 4.5. SPI Flash Memory Controller IP Configuration

Table 4.4 provides the configuration details of the SPI Flash Memory Controller IP.

**Table 4.4. SPI Flash Memory Controller IP Configuration**

| Property                     | Value  | Description                                                                                                             |

|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| Enable Page Program Buffer   | False  | When enabled, page write data is locally stored before writing the entire page to SPI Flash.  Disabled in this design.  |

| Enable Page Read Buffer      | True   | Speeds up page reads by reading an entire page from SPI Flash and locally storing it. Buffer size equals the page size. |

| Page Read Buffer Memory Type | EBR    | Specifies whether EBR or Distributed RAM is used for the Page Read Buffer.                                              |

| Page Buffer Interface        | APB    | Indicates the interface used for data buffer configuration.                                                             |

| Page Size                    | 256    | Defines the size of each page in SPI Flash. Refer to the SPI Flash data sheet to obtain this value.                     |

| Flash Memory Map Size (KB)   | 65,536 | The size of the memory mapped in KB. Available options must be a power of 2. Example: 1, 2, 4, 8 up to 2,097,152.       |

| Property                              | Value         | Description                                                                                                                                                                                                                                                                                                               |

|---------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK Rate [0 – 15]                    | 0             | Specifies the factor for deriving sclk_o from the 0 – 15 component input clock (apb_pclk_i).  sclk_o is derived from the following equation:  sclk_o = apb_pclk_i/(2 x SCLK_Rate) when SCLK_RATE is greater than 0. If SCLK_RATE is equal to 0 sclk_o = apb_pclk_i.  For example:For SCLK Rate = 1, sclk_o = apb_pclk_i/2 |

| SCLK Polarity                         | 0             | Note: This is configured in the bootloader software code.  Sets the idle state polarity of the sclk_o.  Default value is used in this design.                                                                                                                                                                             |

| SCLK Phase                            | 0             | Determines whether data is sampled and shifted on the rising or falling edge of the clock.  Default value is used in this design.                                                                                                                                                                                         |

| First Transmitted Bit                 | MSB           | Specifies bit-shifting direction in the SPI Interface.  Default value is used in this design.                                                                                                                                                                                                                             |

| Data Port AHB Address Width           | 32            | Width of the AHB-Lite address bus.                                                                                                                                                                                                                                                                                        |

| Data Port AHB Data Width              | 32            | Width of the AHB-Lite data bus.                                                                                                                                                                                                                                                                                           |

| Data Port AHB Data Byte<br>Endianness | Little-endian | Endianness of AHB-Lite data bus. Default value is used in this design.                                                                                                                                                                                                                                                    |

| Control Port APB Data Width           | 32            | Width of the APB data bus.                                                                                                                                                                                                                                                                                                |

| Slow Read                             | 8'h03         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.<br>Default value is used in this design.                                                                                                                                                                                  |

| Fast Read                             | 8'h0b         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Page Program                          | 8'h02         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.<br>Default value is used in this design.                                                                                                                                                                                  |

| Block Erase Type 1                    | 8'h20         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Block Erase Type 2                    | 8'h52         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Block Erase Type 3                    | 8'hd8         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Chip Erase                            | 8'h60         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.<br>Default value is used in this design.                                                                                                                                                                                  |

| Write Enable                          | 8'h06         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.<br>Default value is used in this design.                                                                                                                                                                                  |

| Write Disable                         | 8'h04         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Read Status Register                  | 8'h05         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Write Status Register                 | 8'h01         | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.  Default value is used in this design.                                                                                                                                                                                    |

| Property               | Value | Description                                                                                                                              |

|------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| Deep Power Down        | 8'hb9 | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.                                          |

|                        |       | Default value is used in this design.                                                                                                    |

| Resume from Power Down | 8'hab | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.<br>Default value is used in this design. |

| Read Manufacturer ID   | 8'h9f | Specifies the equivalent opcode of a flash command of the off-<br>chip SPI flash memory device.<br>Default value is used in this design. |

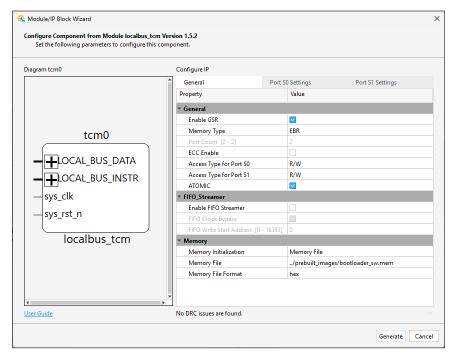

### 4.4. Tightly Coupled Memory

The Tightly Coupled Memory IP is used to store the initial software code executed by the RISC-V RX CPU immediately after resetting. Since the LPDDR4 external memory is not available until memory training is completed, this initial software ensures that the LPDDR4 memory is ready before any access by the RISC-V RX CPU.

By using the Tightly Coupled Memory IP, the initial software can be pre-compiled directly into the FPGA bitstream. Once device configuration is complete, the tightly coupled memory contains the valid initial software. Refer to the RISC-V RX Software Flow section for more details.

Figure 4.6 shows the configuration of the Tightly Coupled Memory IP in the General tab.

Figure 4.6. Tightly Coupled Memory IP Configuration

Table 4.5 provides the configuration details of the Tightly Coupled Memory IP.

### **Table 4.5.Tightly Coupled Memory IP Configuration**

| Property                     | Value                | Description                                                                                               |

|------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|

| General Tab                  |                      |                                                                                                           |

| Enable GSR                   | True                 | Enables global set/reset functionality.                                                                   |

| Memory Type                  | EBR                  | Specifies the types of memory used for this TCM instance.                                                 |

| 500 5 11                     | - 1                  | Determines whether the Error Correction Code (ECC) is enabled.                                            |

| ECC Enable                   | False                | Default value is used in this design.                                                                     |

| A T f D + CO                 | D ///                | Sets read/write access for the INSTR port.                                                                |

| Access Type for Port SO      | R/W                  | Default value is used in this design.                                                                     |

| Access Type for \$1          | R/W                  | Sets read/write access for the DATA port.                                                                 |

| Access Type for S1           | r, vv                | Default value is used in this design.                                                                     |

| ATOMIC                       | True                 | Indicate that TCM supports atomic instructions.                                                           |

| Enable FIFO Streamer         | False                | Enables the FIFO Streamer interface. If port count = 2, the streamer                                      |

| Lilable i ii O Streamei      | 1 0136               | shares the DATA port; otherwise, it uses a dedicated port.                                                |

| Memory Initialization        | Memory File          | Enable this option to specify the software memory initialization file                                     |

| Memory File                  | Path to the mem file | .mem. This file allows the software to be compiled into the FPGA                                          |

| Memory File Format           | hex                  | bitstream during the Lattice Radiant compilation process.                                                 |

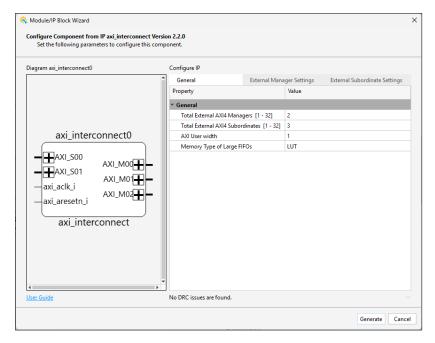

| Port SO Settings Tab         |                      |                                                                                                           |