**USB 2.0/3.2 IP**

IP Version: v3.2.0

# **User Guide**

FPGA-IPUG-02237-1.5

October 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents | 5                                                              | 3  |

|----------|----------------------------------------------------------------|----|

|          | ations in This Document                                        |    |

| 1. Intr  | oduction                                                       |    |

| 1.1.     | Overview of the IP                                             |    |

| 1.2.     | Quick Facts                                                    |    |

| 1.3.     | IP Support Summary                                             |    |

| 1.4.     | Features                                                       |    |

| 1.5.     | Licensing and Ordering Information                             | 9  |

| 1.6.     | Hardware Support                                               | 9  |

| 1.7.     | Minimum Device Requirements                                    | 9  |

| 1.8.     | Naming Conventions                                             | 10 |

| 1.8.     | 1. Nomenclature                                                | 10 |

| 1.8.     | 2. Signal Names                                                | 10 |

| 2. Fun   | ctional Description                                            | 11 |

| 2.1.     | IP Architecture Overview                                       | 11 |

| 2.2.     | Clocking                                                       | 12 |

| 2.2.     | 1. Clocking Overview                                           | 12 |

| 2.1      | User Interfaces                                                | 12 |

| 2.2      | Internal IP Blocks                                             | 12 |

| 2.2.     | 1 USB 2.0/3.2                                                  | 12 |

| 2.2.     | 2 AHBL-to-LMMI Converter                                       | 12 |

| 3. IP P  | arameter Description                                           | 13 |

| 4. Sign  | nal Description                                                | 14 |

| 4.1.     | Clock Interface                                                | 14 |

| 4.2.     | Reset Interface                                                | 14 |

| 4.3.     | USB Interface                                                  | 14 |

| 4.4.     | LMMI/AHBL Interface – Configuration Path                       | 14 |

| 4.5.     | AXI Interface – Data Path                                      | 15 |

| 4.6.     | Other Signals                                                  | 18 |

| 5. Reg   | ister Description                                              | 19 |

| 5.1.     | USB IP Controller Register Information                         | 19 |

| 5.1.     | 1 Global Core Control Register (GCTL)                          | 20 |

| 5.1.     | 2 Global ID Register (GSNPSID)                                 | 25 |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     | 6 Global Event Buffer Address (High) Register (GEVNTADRHI(#n)) | 33 |

| 5.1.     |                                                                |    |

| 5.1.     | 8 Global Event Buffer Count Register (GEVNTCOUNT(#n))          | 34 |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.1.     |                                                                |    |

| 5.2.     | USB IP 2/3 PHY Control Status Register Information             |    |

|          | ,                                                              |    |

| 6. Operation Details                                                                                                                                                                                            | 54  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1. Enumeration Sequence                                                                                                                                                                                       | 54  |

| 6.1.1. Power-On or Soft Reset                                                                                                                                                                                   | 54  |

| 6.1.2. USB Reset                                                                                                                                                                                                | 54  |

| 6.1.3. Connect Done                                                                                                                                                                                             | 54  |

| 6.1.4. SetAddress Device Request                                                                                                                                                                                | 55  |

| 6.2. Transfer Flow                                                                                                                                                                                              | 55  |

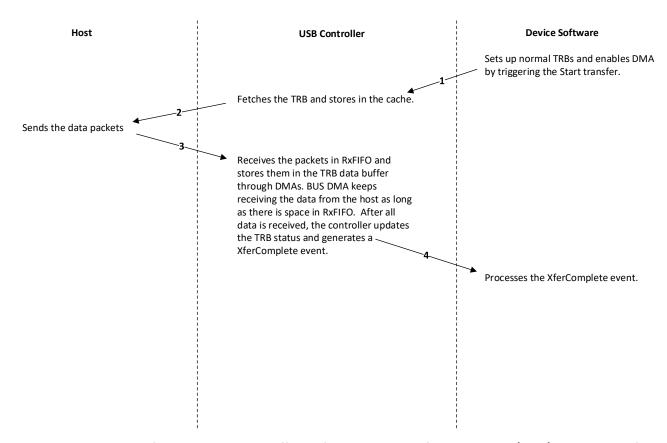

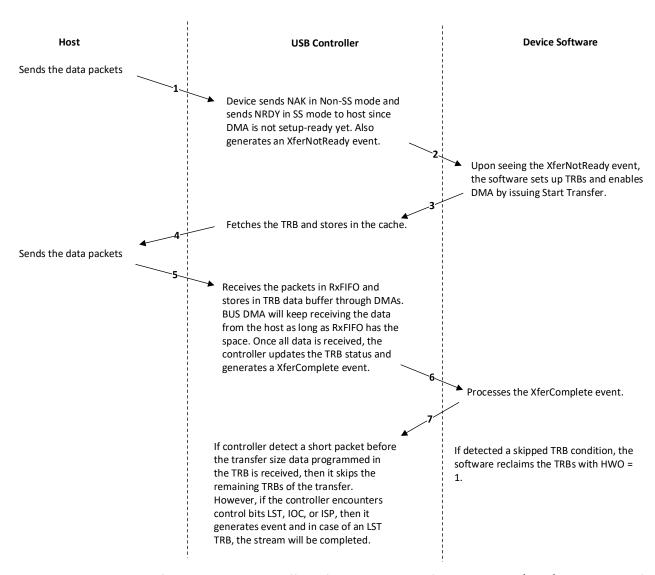

| 6.2.1. Control-data/Bulk/Interrupt OUT Transfer Flow                                                                                                                                                            | 55  |

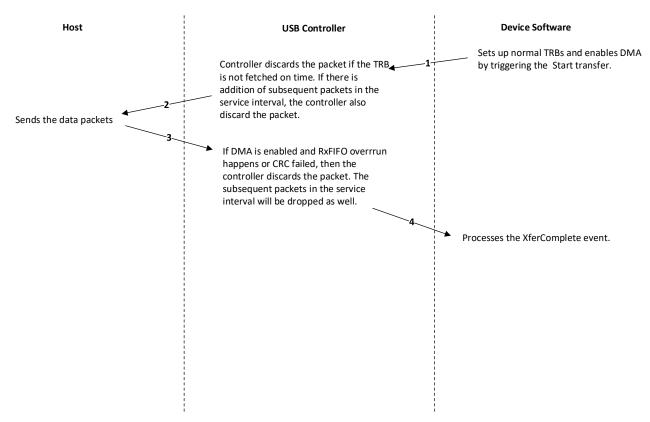

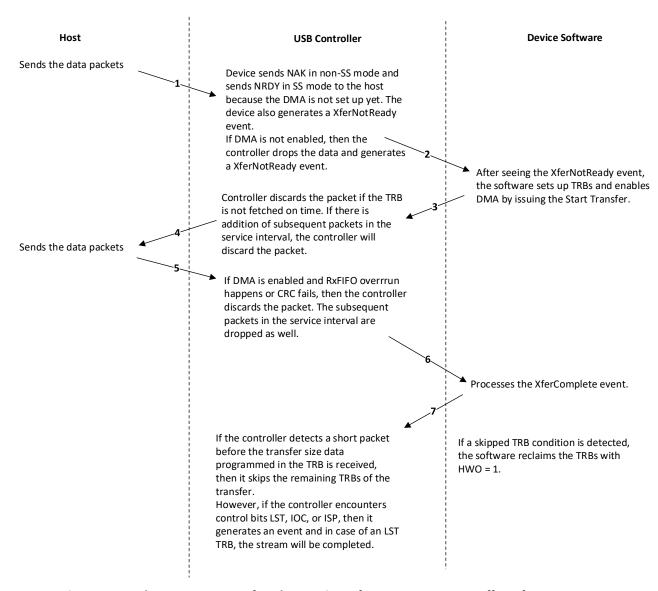

| 6.2.2. Isochronous OUT Transfer Flow                                                                                                                                                                            | 56  |

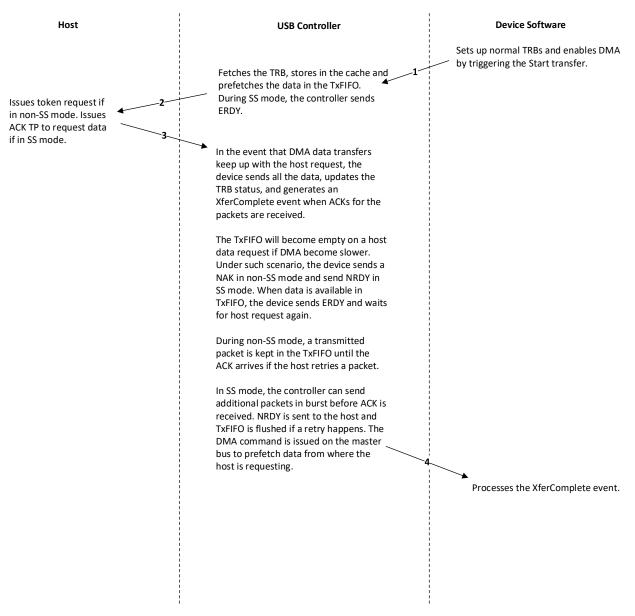

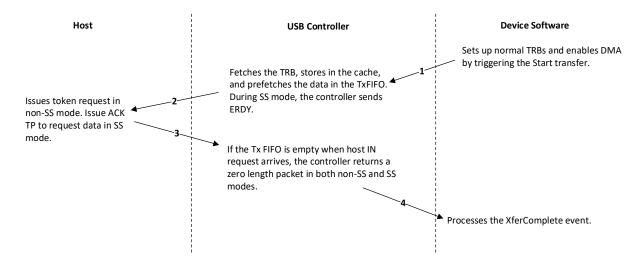

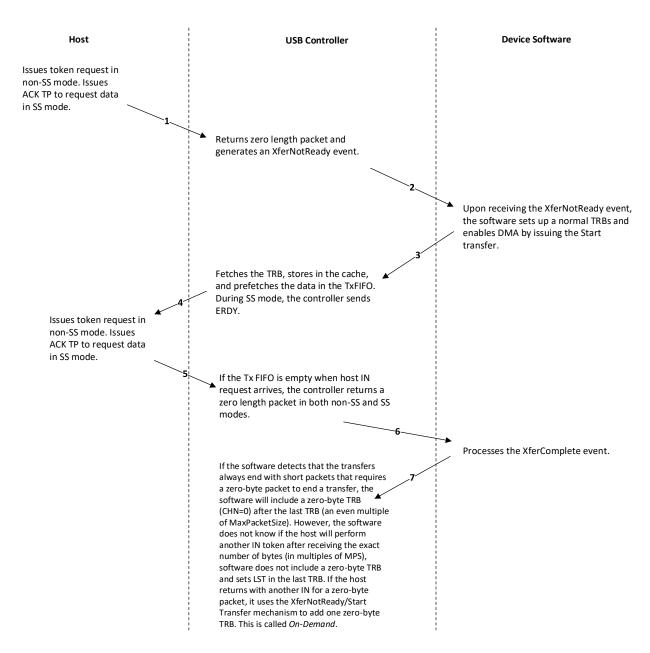

| 6.2.3. Control-data/ Bulk/Interrupt IN Transfer Flow                                                                                                                                                            | 58  |

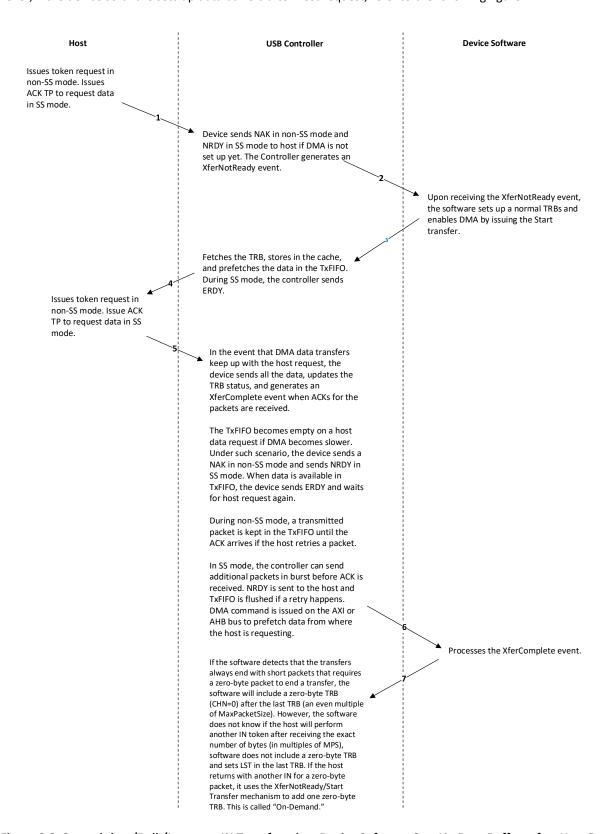

| 6.2.4. Isochronous IN Transfer Flow                                                                                                                                                                             | 61  |

| 7. Designing with the IP                                                                                                                                                                                        | 63  |

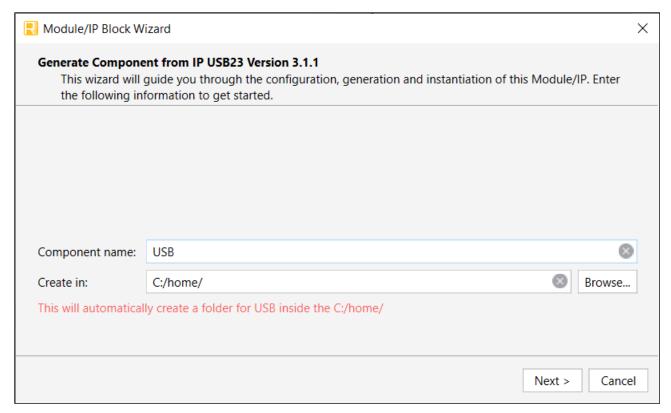

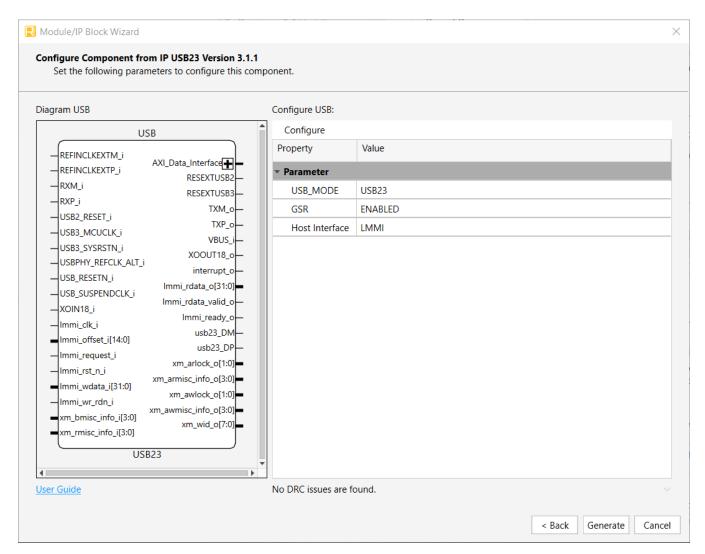

| 7.1. Generating and Instantiating the IP                                                                                                                                                                        | 63  |

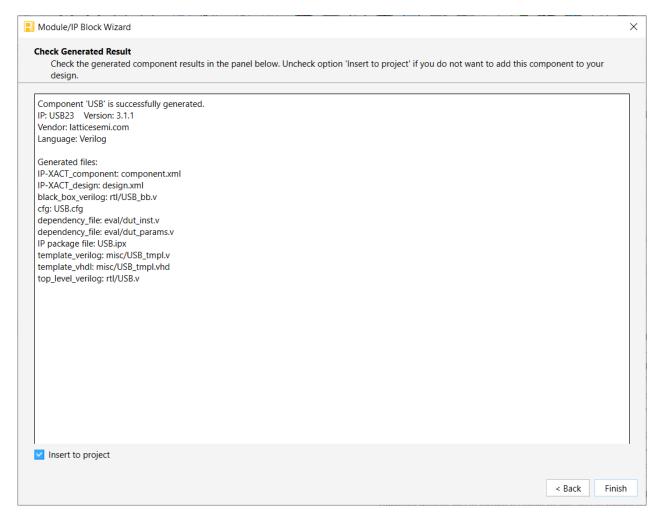

| 7.1.1. Generated Files and File Structure                                                                                                                                                                       | 65  |

| 7.1.2. Design Implementation                                                                                                                                                                                    | 66  |

| 7.1.3. Timing Constraints                                                                                                                                                                                       | 66  |

| 8. Example Design                                                                                                                                                                                               | 67  |

| 8.1. Overview of the Example Design and Features                                                                                                                                                                | 67  |

| 8.2. Example Design Components                                                                                                                                                                                  | 67  |

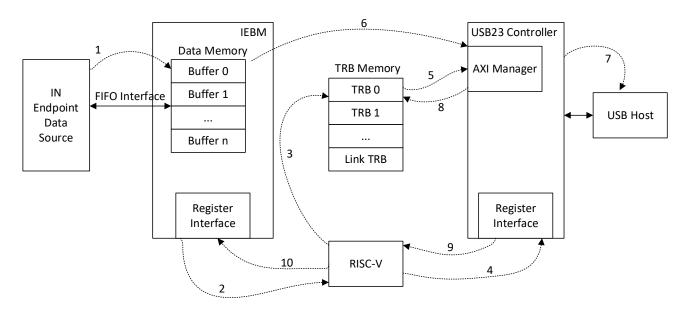

| 8.2.1. Description on Data Flow from USB Device to Host                                                                                                                                                         | 70  |

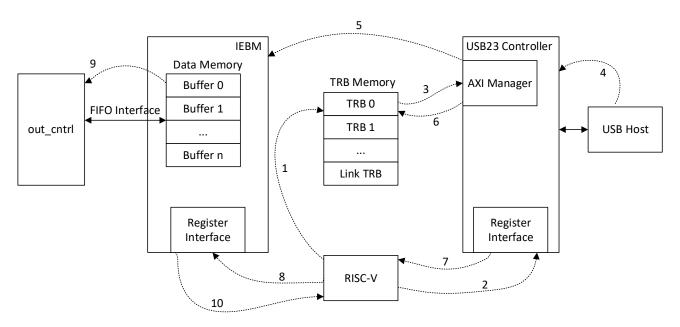

| 8.2.2. Description on Data Flow from USB Host to Device                                                                                                                                                         | 71  |

| 8.2.3. USB 2.0/3.2 Primitive                                                                                                                                                                                    | 71  |

| 8.2.4. USB23_ED                                                                                                                                                                                                 | 71  |

| 8.3. Running the Example Design                                                                                                                                                                                 | 85  |

| 8.3.1. Generating the USB23 Benchmark Example Design                                                                                                                                                            | 86  |

| 8.3.2. HAL Driver Compilation                                                                                                                                                                                   | 86  |

| 8.3.3. Radiant Software Compilation for Bitstream                                                                                                                                                               | 101 |

| 8.3.4. Trim the Memory File                                                                                                                                                                                     | 105 |

| 8.3.5. Merging .mem with Bitstream File                                                                                                                                                                         | 106 |

| 8.3.6. Hardware Testing                                                                                                                                                                                         | 108 |

| 8.3.7. FPGA Bitstream Programming                                                                                                                                                                               |     |

| 8.3.8. Performing Streaming Operations                                                                                                                                                                          | 112 |

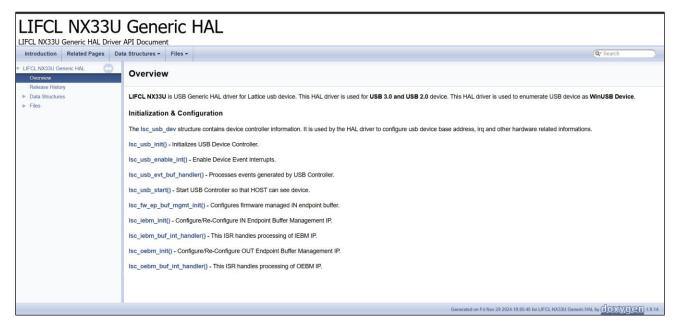

| 8.4. Example Software API                                                                                                                                                                                       | 128 |

| 8.4.1. USB Enumeration API                                                                                                                                                                                      | 128 |

| Appendix A. Resource Utilization                                                                                                                                                                                | 129 |

| References                                                                                                                                                                                                      | 130 |

| Technical Support Assistance                                                                                                                                                                                    | 131 |

| Revision History                                                                                                                                                                                                | 132 |

| Figures                                                                                                                                                                                                         |     |

| _                                                                                                                                                                                                               | 11  |

| Figure 2.1. USB 2.0/3.2 IP Block Diagram                                                                                                                                                                        |     |

| Figure 2.2. USB 2.0/3.2 IP Clock Domain Block Diagram<br>Figure 6.1. Device Software Sets Up Data Buffers Before Host Request for Control-data/Bulk/Interrupt T                                                 |     |

| Figure 6.1. Device Software Sets up Data Buffers Before Host Requests for Control-data/Bulk/Interrupt 1 Figure 6.2. Device Software Sets Up Data Buffers After Host Requests for Control-data/Bulk/Interrupt Ti |     |

| Figure 6.2. Device Software Sets up Data Buffers After Host Requests for Control-data/Bulk/Interrupt 11 Figure 6.3. Isochronous OUT Transfer when Device Software Sets Up Data Buffers Before Host Request .    |     |

| Figure 6.4. Isochronous OUT Transfer when Device Software Sets Up Data Buffers after Host Request                                                                                                               |     |

| Figure 6.5. Control-data/Bulk/Interrupt IN Transfer when Device Software Sets Up Data Buffers before F                                                                                                          |     |

| Figure 6.6. Control-data/Bulk/Interrupt IN Transfer when Device Software Sets Up Data Buffers after Ho                                                                                                          | -   |

| Figure 6.5. Isochronous IN Transfer when Device Software Sets Up Data Buffers before Host Request                                                                                                               | •   |

| Figure 6.8. Isochronous IN Transfer when Device Software Sets Up Data Buffers after Host Request                                                                                                                |     |

| Figure 7.1. Module/IP Block Wizard                                                                                                                                                                              |     |

| 1.84.6 / 121 11.044.6/ 11 DIOCK WIEGIA                                                                                                                                                                          |     |

| Figure 7.2. IP Configuration                                         |     |

|----------------------------------------------------------------------|-----|

| Figure 7.3. Check Generated Result                                   |     |

| Figure 8.1. USB2.0/3.2 IP Example Design Block Diagram               | 68  |

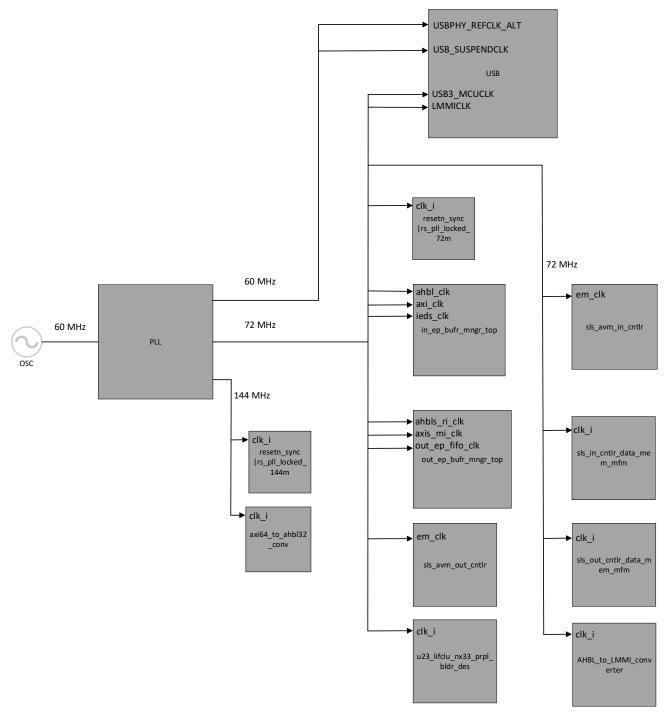

| Figure 8.2. Clocking Diagram of the Example Design                   |     |

| Figure 8.3. IN Data Flow from USB Device to Host                     |     |

| Figure 8.4. OUT Data Flow from USB Host to Device                    |     |

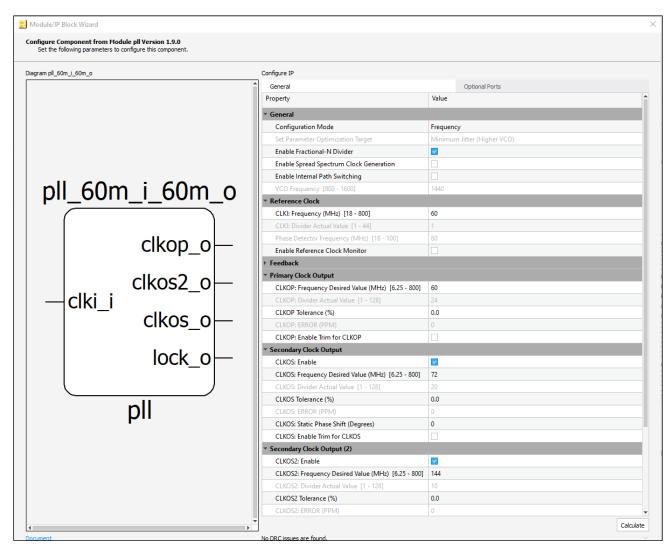

| Figure 8.5. PLL Configuration                                        |     |

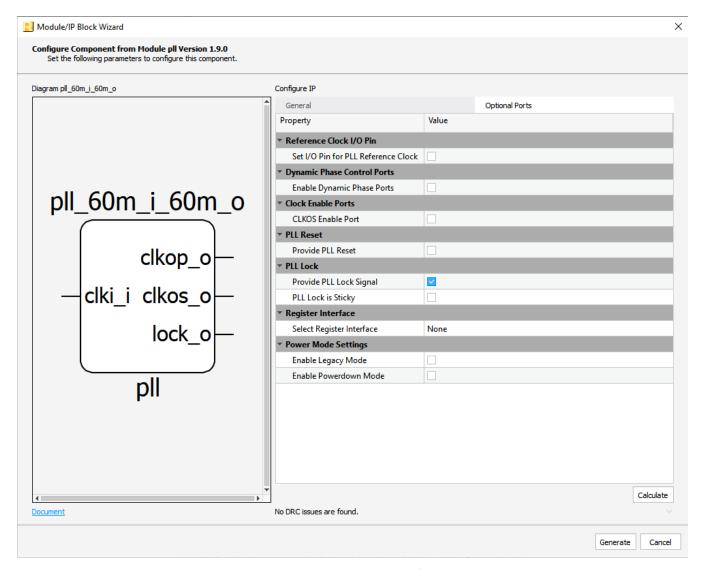

| Figure 8.6. PLL Optional Port Configuration                          |     |

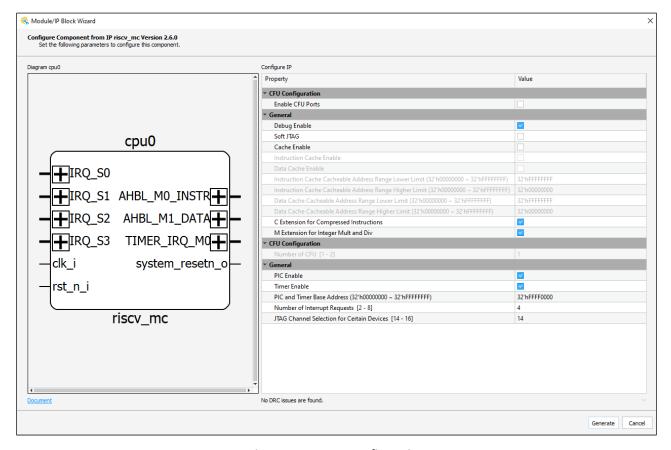

| Figure 8.7. RISC-V Configuration                                     |     |

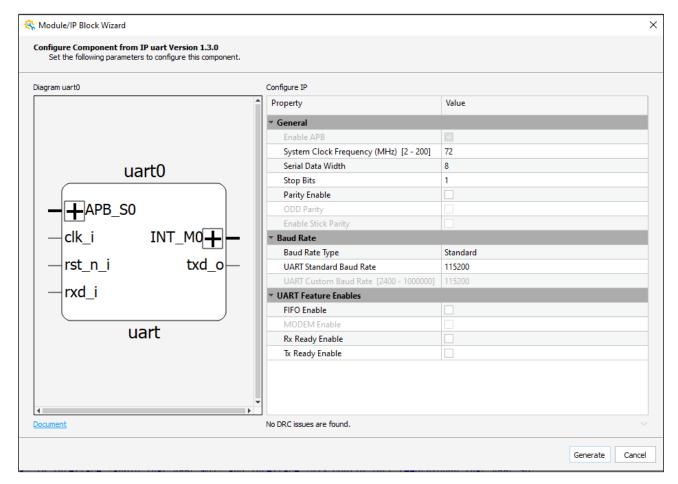

| Figure 8.8. UART Configuration                                       | 75  |

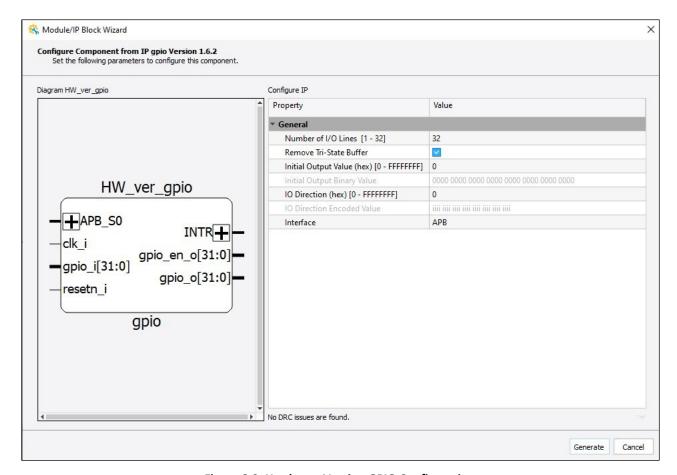

| Figure 8.9. Hardware Version GPIO Configuration                      | 76  |

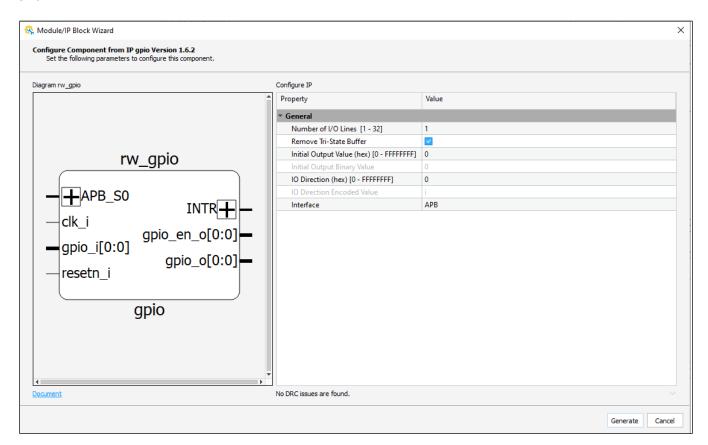

| Figure 8.10. Remote Wakeup GPIO Configuration                        | 77  |

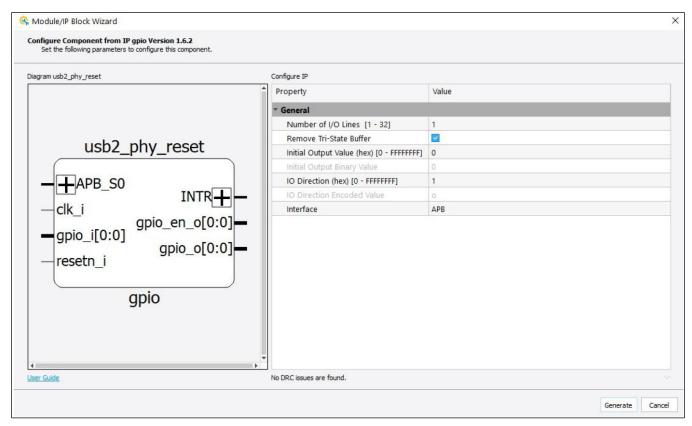

| Figure 8.11. USB2 PHY Reset GPIO Configuration                       | 78  |

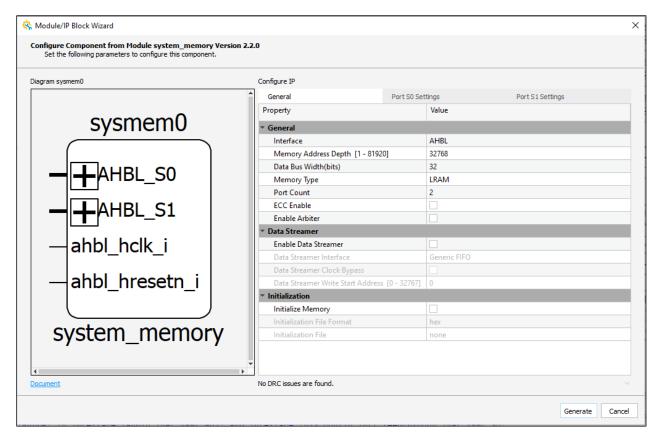

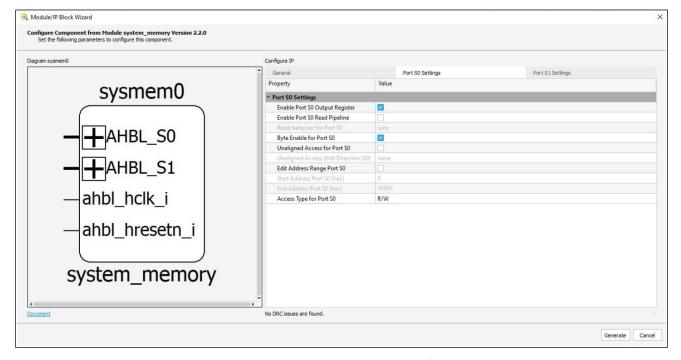

| Figure 8.12. System Memory Configuration                             | 79  |

| Figure 8.13. System Memory Port SO Configuration                     | 79  |

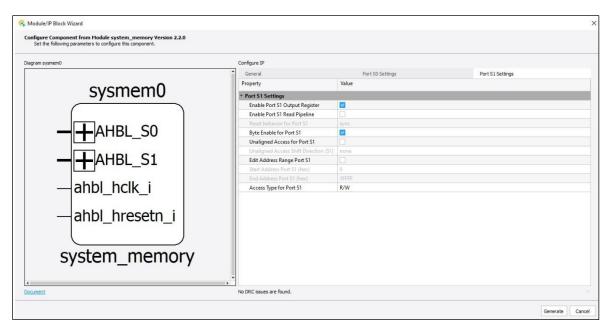

| Figure 8.14. System Memory Port S1 Configuration                     | 80  |

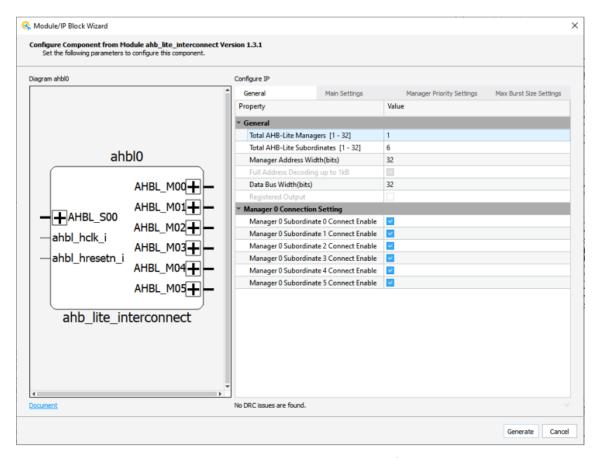

| Figure 8.15. AHBL Interconnect General Configuration                 | 80  |

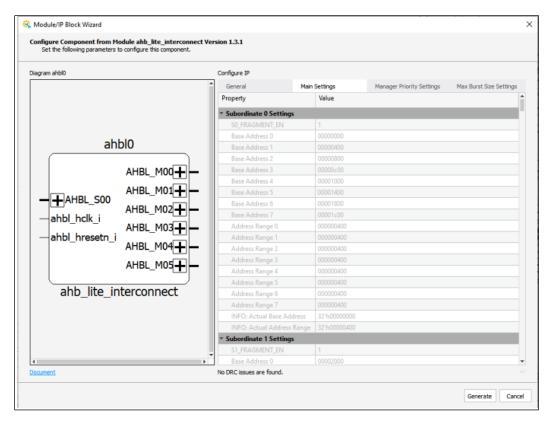

| Figure 8.16. AHBL Interconnect Main Configuration                    | 81  |

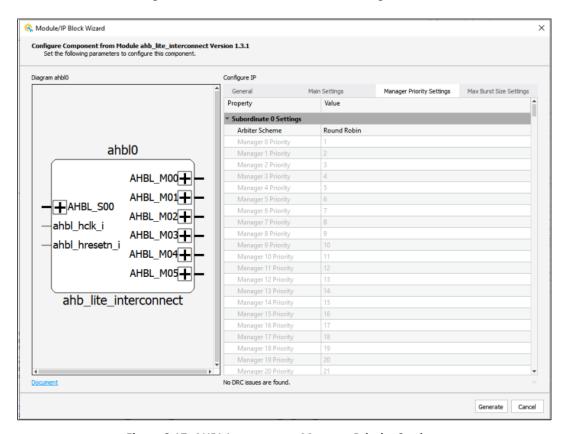

| Figure 8.17. AHBL Interconnect Manager Priority Settings             | 81  |

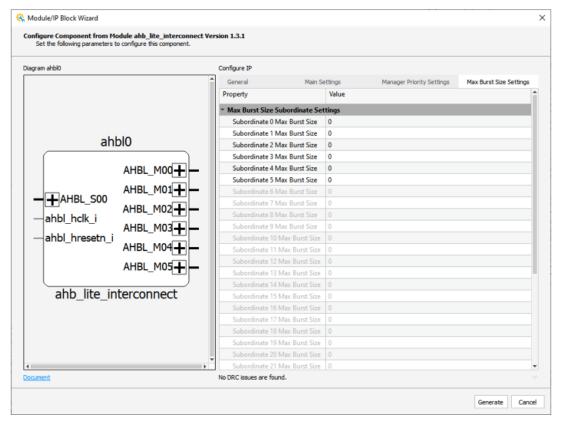

| Figure 8.18. AHBL Interconnect Max Burst Settings                    | 82  |

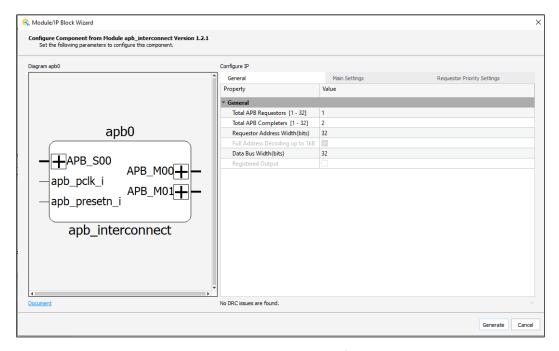

| Figure 8.19. APB Interconnect Configuration 1                        | 82  |

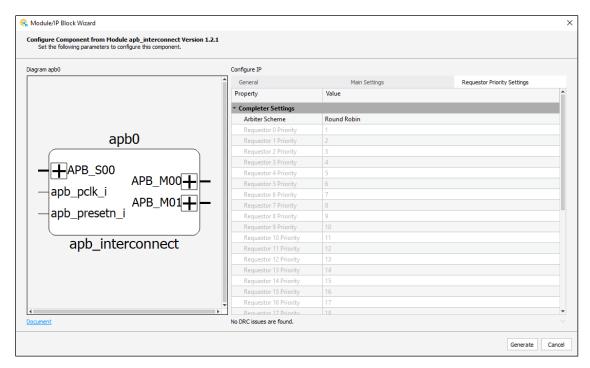

| Figure 8.20. APB Interconnect Configuration 2                        | 83  |

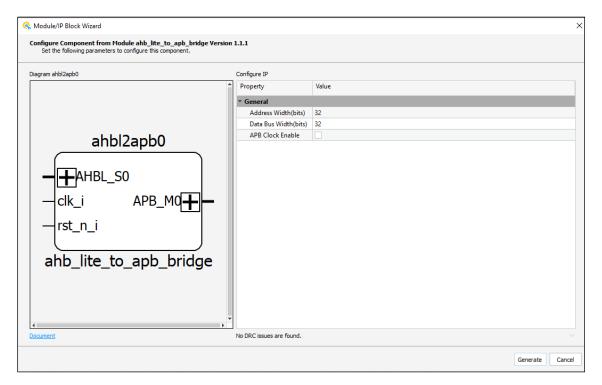

| Figure 8.21. AHB-Lite to APB Configuration                           | 83  |

| Figure 8.22. Lattice CrosslinkU-NX33 Evaluation Board (Rev B)        | 85  |

| Figure 8.23. nx33u_cmp_revb_evn_bd_rd_des.zip File                   |     |

| Figure 8.24. Create a Propel Project                                 | 86  |

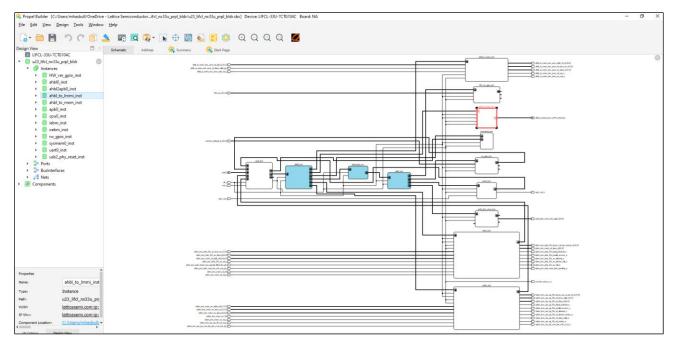

| Figure 8.25. Regenerate the Sub-Modules in the Propel Software       | 87  |

| Figure 8.26. Generate Button in the Propel Software                  |     |

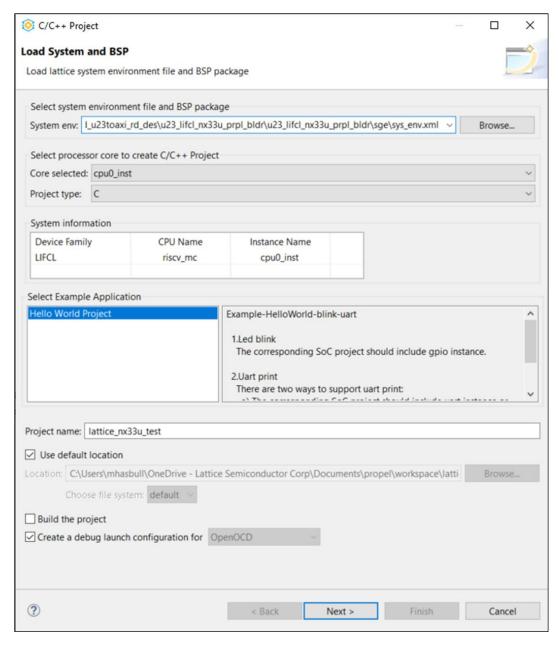

| Figure 8.27. Create a Project                                        | 88  |

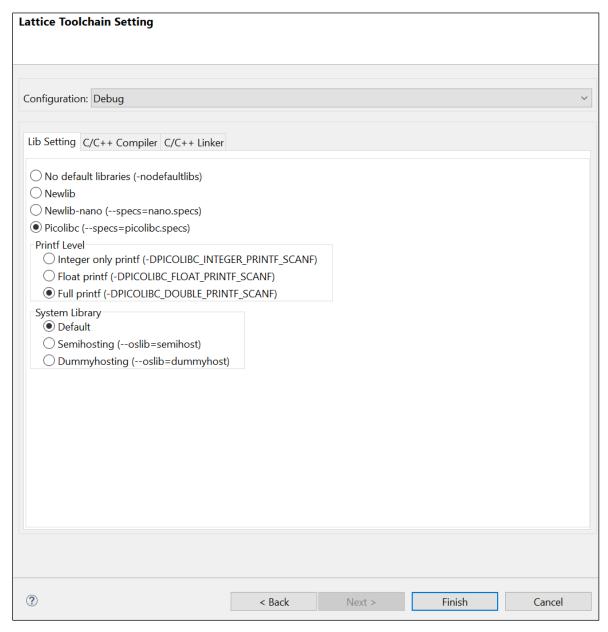

| Figure 8.28. Toolchain Setting                                       |     |

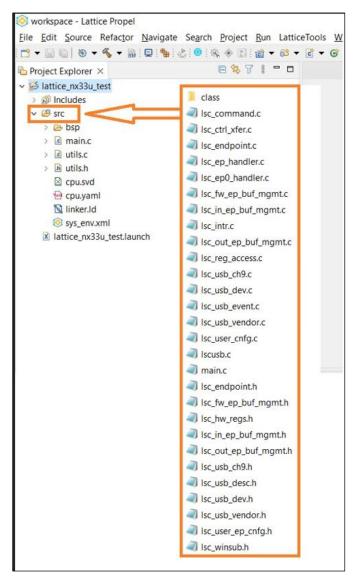

| Figure 8.29. Copy all C and H Files to the src Folder                | 90  |

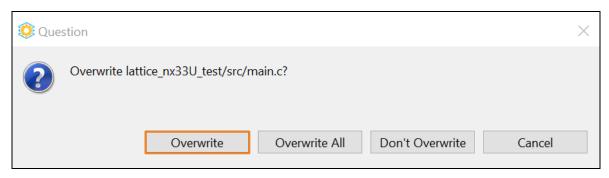

| Figure 8.30. Overwrite File                                          |     |

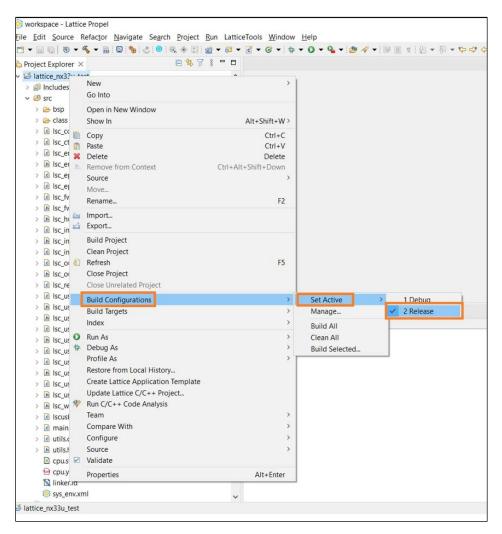

| Figure 8.31. Set Build Configuration to Release Mode                 |     |

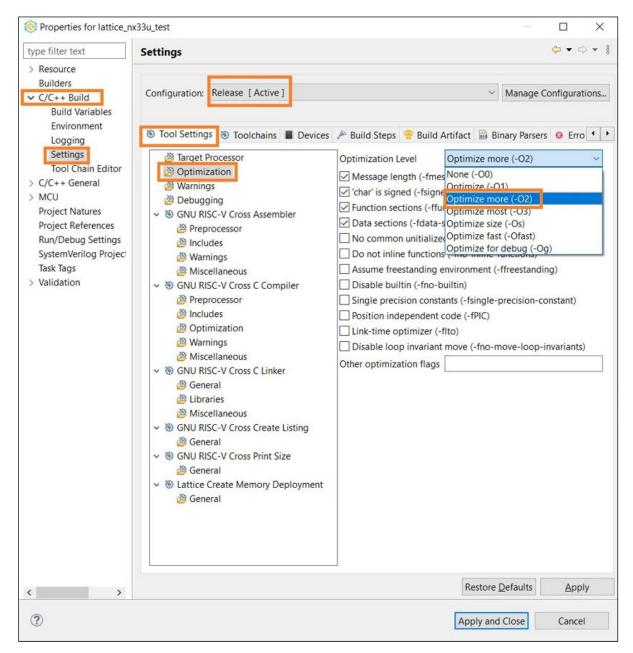

| Figure 8.32. Set Optimization Level                                  |     |

| Figure 8.33. Linker ID File                                          |     |

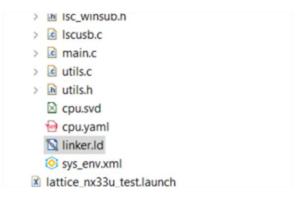

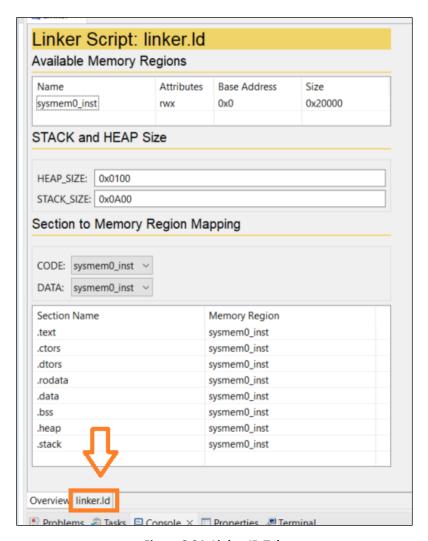

| Figure 8.34. Linker ID Tab                                           | 93  |

| Figure 8.35. Base Address Update                                     | 94  |

| Figure 8.36. System Memory Instance                                  | 95  |

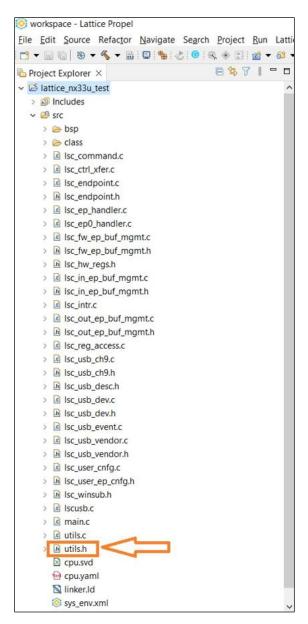

| Figure 8.37. utils.h File                                            | 96  |

| Figure 8.38. CPU_M_Frequency Update                                  | 97  |

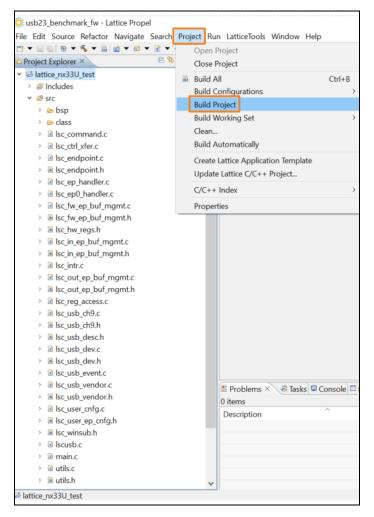

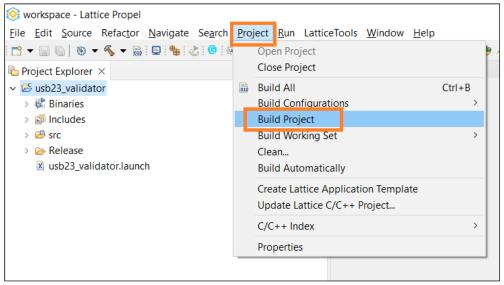

| Figure 8.39. Build a Project                                         | 97  |

| Figure 8.40. Console Message                                         |     |

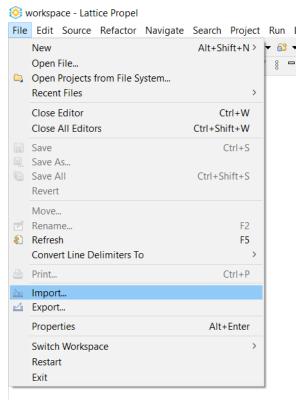

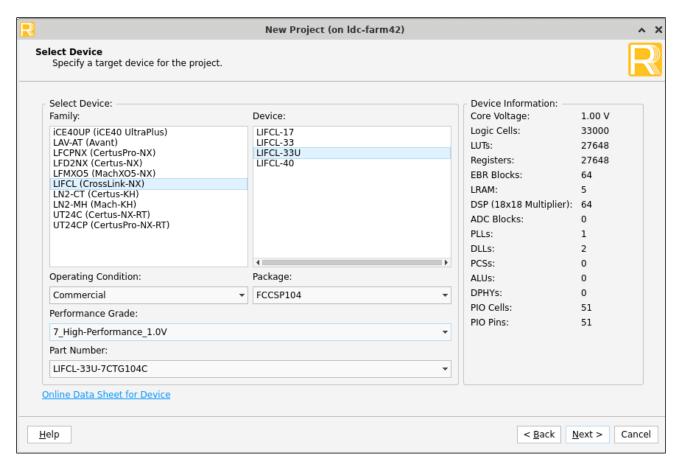

| Figure 8.41. Import Project                                          |     |

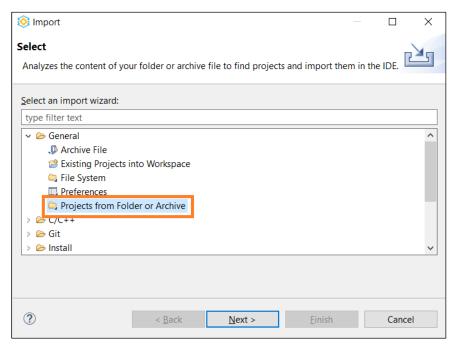

| Figure 8.42. Project from Folder or Archive                          |     |

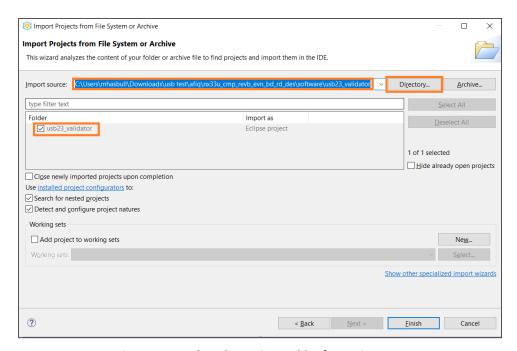

| Figure 8.43. Select the Project Folder from Directory                | 99  |

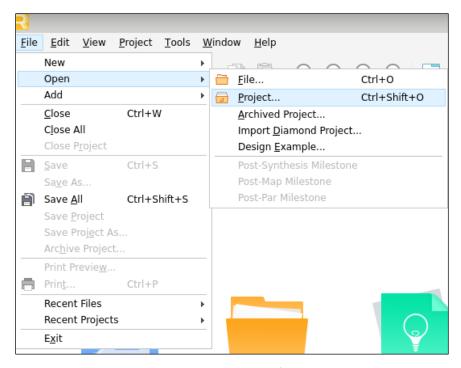

| Figure 8.44 Project Exploration Tab                                  |     |

| Figure 8.45 Build Project                                            |     |

| Figure 8.46 Console Message                                          |     |

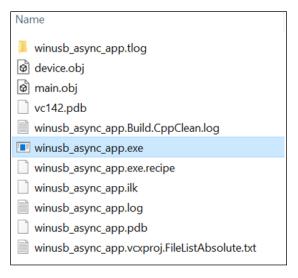

| Figure 8.47 Eval Folder                                              |     |

| Figure 8.48 nx33u_cmp_revb_evn_bd_rd_des Sub Folder                  |     |

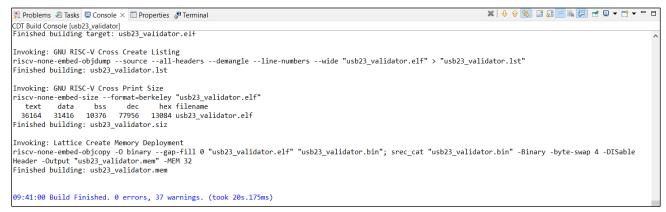

| Figure 8.49. Radiant Device Setup                                    |     |

| Figure 8.50. USB IP GUI Option                                       |     |

| Figure 8.51. Open a Radiant Software Project                         |     |

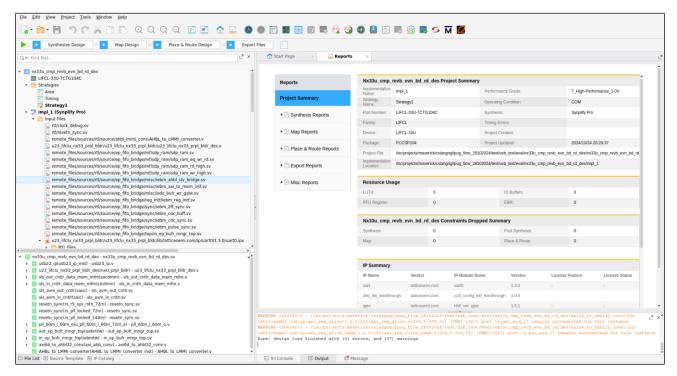

| Figure 8.52. USB23 Benchmark Example Design Radiant Software Project | 103 |

| Figure 8.53. Bitstream Generation                                       | 104 |

|-------------------------------------------------------------------------|-----|

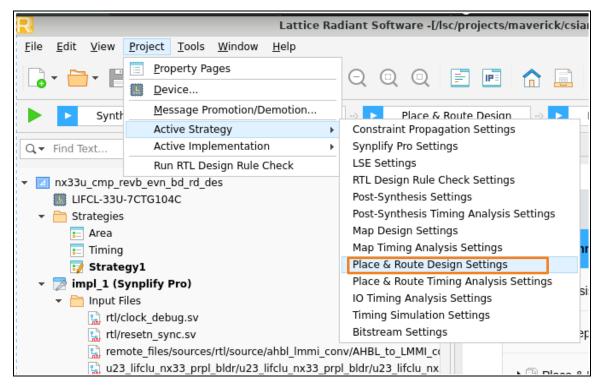

| Figure 8.54. Place & Route Design Settings                              | 104 |

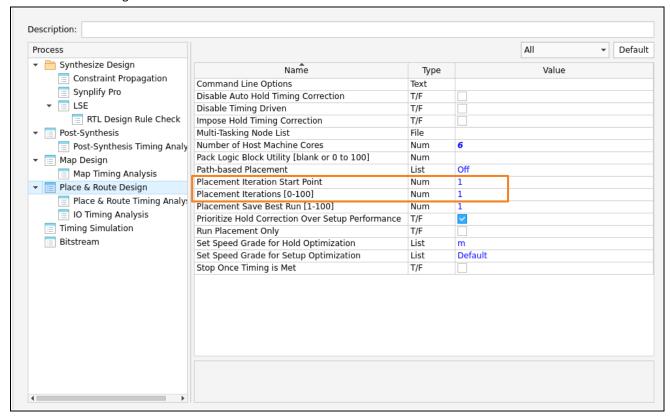

| Figure 8.55. Placement Iteration                                        | 105 |

| Figure 8.56. Trim the Memory File                                       | 106 |

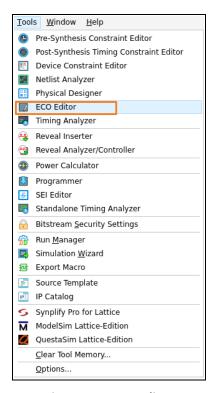

| Figure 8.57. ECO Editor                                                 | 106 |

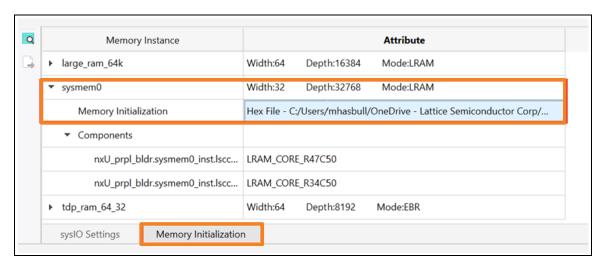

| Figure 8.58. Memory Initialization                                      | 107 |

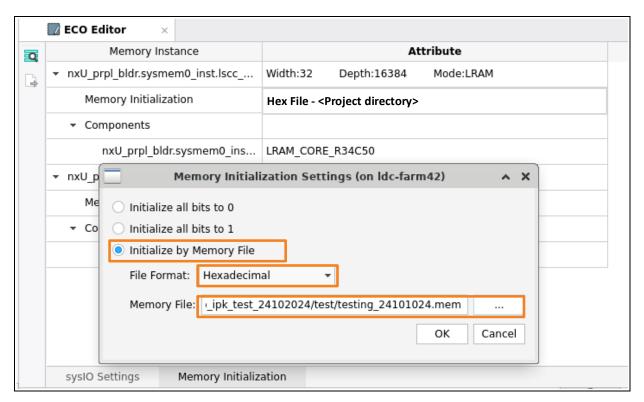

| Figure 8.59. Memory Initialization Settings                             | 107 |

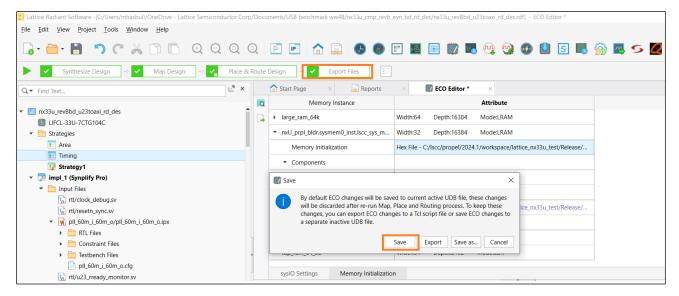

| Figure 8.60. Save the Settings in the ECO Editor and Generate Bitstream | 108 |

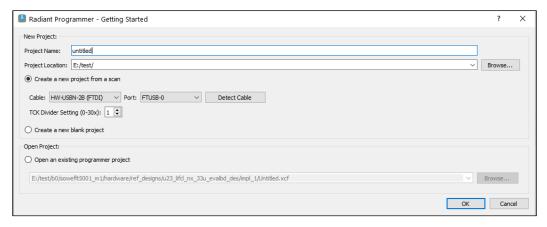

| Figure 8.61. Radiant Programmer Getting Started Window                  | 109 |

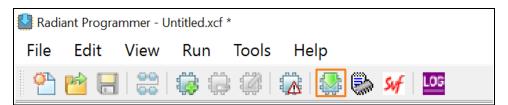

| Figure 8.62. Program Button                                             | 109 |

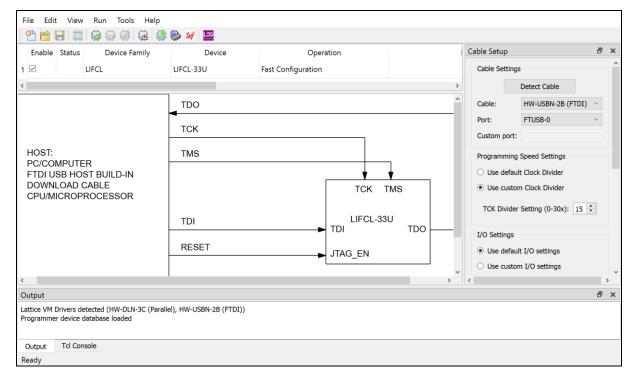

| Figure 8.63. Select Programming Mode                                    | 110 |

| Figure 8.64. SPI Flash Programmer Settings                              | 111 |

| Figure 8.65. USB Enumeration                                            | 112 |

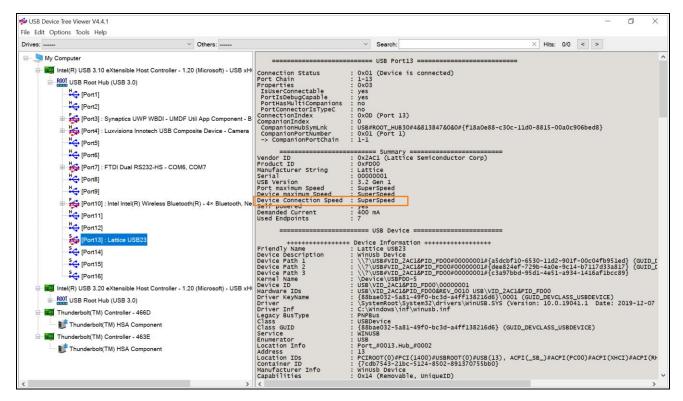

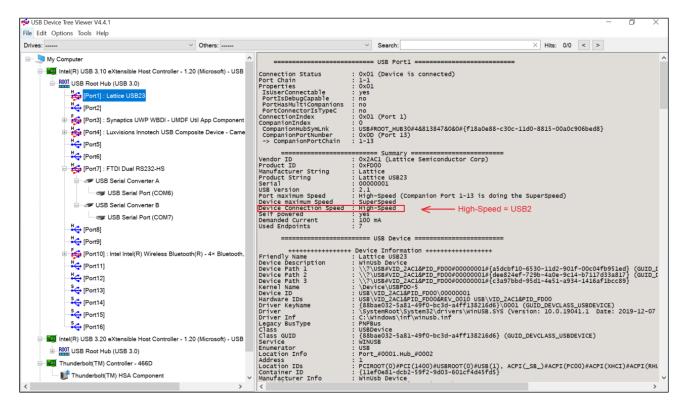

| Figure 8.66. USB Device Tree Viewer                                     | 113 |

| Figure 8.67. WinUSB Asynchronous CLI Application                        | 113 |

| Figure 8.68. Obtaining Device Information through WinUSB API            | 114 |

| Figure 8.69. Bulk IN Test                                               | 115 |

| Figure 8.70. Bulk OUT Test                                              | 116 |

| Figure 8.71. Interrupt IN Test                                          | 117 |

| Figure 8.72. Interrupt OUT Test                                         | 118 |

| Figure 8.73. Isochronous IN Test                                        | 119 |

| Figure 8.74. Isochronous OUT Test                                       | 120 |

| Figure 8.75. USB2 Connection Speed                                      | 121 |

| Figure 8.76. USB2 Bulk IN Test Result                                   | 122 |

| Figure 8.77. USB2 Bulk OUT Test Result                                  | 123 |

| Figure 8.78. USB2 Interrupt IN Test Result                              | 124 |

| Figure 8.79. USB2 Interrupt OUT Test                                    | 125 |

| Figure 8.80. USB2 Isochronous IN Test Result                            | 126 |

| Figure 8.81. USB2 Isochronous OUT Test Result                           | 127 |

| Figure 8.82. HAL Driver API Document                                    | 128 |

|                                                                         |     |

| Tables                                                                  |     |

|                                                                         |     |

| Table 1.1. Summary of the USB2.0/3.2 IP Core                       | 9  |

|--------------------------------------------------------------------|----|

| Table 1.1. Summary of the USB2.0/3.2 IP Core                       | 9  |

| Table 1.3. Minimum Device Requirements for the USB 2.0/3.2 IP Core | 10 |

| Table 3.1. General Attributes of the USB 2.0/3.2 IP Core           | 13 |

| Table 4.1. Clock Ports                                             | 14 |

| Table 4.2. Reset Interface                                         | 14 |

| Table 4.3. USB Interface                                           | 14 |

| Table 4.4. LMMI Interface - Configuration Path                     |    |

| Table 4.5. AHBL Interface - Configuration Path                     | 15 |

| Table 4.6. AXI Interface - Data Path                               |    |

| Table 4.7. Other Signals                                           | 18 |

| Table 5.1. USB IP Controller Register Information                  | 19 |

| Table 5.2. GLOBAL_CTL                                              | 20 |

| Table 5.3. GLOBAL_ID                                               | 25 |

| Table 5.4. GLOBAL_USB2_PHY_CFG(#n) (for n = 0)                     | 25 |

| Table 5.5. GLOBAL_USB3_PIPE_CTL(#n) (for n = 0)                    |    |

| Table 5.6. GLOBAL_EVNT_ADR(#n) (for n = 0)                         |    |

| Table 5.7. GLOBAL_EVNT_ADRI(#n) (for n=0)                          | 33 |

|                                                                    |    |

| Table 5.8. GLOBAL EVNT SIZ(#n) (for n=0)                                               | 33  |

|----------------------------------------------------------------------------------------|-----|

| Table 5.8. GLOBAL_EVNT_SIZ(#n) (for n=0)<br>Table 5.9. GLOBAL_EVNT_COUNT(#n) (for n=0) | 34  |

| Table 5.10. DEVICE CFG (DCFG)                                                          | 34  |

| Table 5.11. DEVICE CTI (DCTI)                                                          | 36  |

| Table 5.12. DEVICE_EVNT_EN                                                             | 41  |

| Table 5.13. DEVICE_STS(DSTS)                                                           | 42  |

| Table 5.14. DEVICE_ACT_EP_EN (DALEPENA)                                                | 44  |

| Table 5.15. DEPCMDPAR2[0:7]                                                            | 45  |

| Table 5.16. DEPCMDPAR1[0:7]                                                            | 45  |

| Table 5.17. DEPCMDPAR0[0:7]                                                            |     |

| Table 5.18. DEPCMD[0:7]                                                                | 45  |

| Table 5.19. GLOBAL_TX_FIFO_SIZE                                                        | 46  |

| Table 5.20. GLOBAL_RX_FIFO_SIZE                                                        | 47  |

| Table 5.21. USB IP 2/3 PHY Control Status Register Information                         |     |

| Table 6.1. Maximum Packet Size Based on the Configured Speed                           | 54  |

| Table 7.1. Generated Files                                                             | 65  |

| Table A.1. Resource Utilization Using LIFCL-33U-7CTG104C                               | 129 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                   |  |  |

|--------------|----------------------------------------------|--|--|

| AHB          | Advanced High-Performance Bus                |  |  |

| AHB-Lite     | Advanced High-Performance Bus Lite version   |  |  |

| APB          | Advanced Peripheral Bus                      |  |  |

| API          | Application Programming Interface            |  |  |

| AXI          | Advanced Extensible Interface                |  |  |

| CPU          | Central Processing Unit                      |  |  |

| ECC          | Error Correction Code                        |  |  |

| FIFO         | First In First Out                           |  |  |

| FPGA         | Field Programmable Gate Array                |  |  |

| HAL          | Hardware Abstraction Layer                   |  |  |

| IP           | Intellectual Property                        |  |  |

| LED          | Light Emitting Diode                         |  |  |

| LMMI         | Lattice Memory Mapped Interface              |  |  |

| MUX          | Multiplexer                                  |  |  |

| PRBS         | Pseudorandom Binary Sequence                 |  |  |

| RISC         | Reduced Instruction Set Computer             |  |  |

| TRB          | Transfer Request Block                       |  |  |

| UART         | Universal Asynchronous Receiver/ Transmitter |  |  |

| USB          | Universal Serial Bus                         |  |  |

### 1. Introduction

#### 1.1. Overview of the IP

The Lattice Semiconductor USB 2.0/3.2 intellectual property (IP) core provides a solution to interface with the USB host. The design is implemented using Verilog HDL. The IP core is targeted for Lattice CrossLinkU™-NX FPGAs. The IP core is implemented using the Lattice Radiant™ software integrated with the Synopsys® Synplify Pro® synthesis tool.

The Lattice USB 2.0/3.2 IP core supports the USB-IF compliant USB standard.

#### 1.2. Quick Facts

Table 1.1. Summary of the USB2.0/3.2 IP Core

| IP Requirements                        | Supported FPGA Family  | CrossLinkU-NX (LIFCL-33U )                                                                  |

|----------------------------------------|------------------------|---------------------------------------------------------------------------------------------|

|                                        | IP Changes             | For a list of changes to the IP, refer to the USB 2.0/3.2 IP Release Notes (FPGA-RN-02037). |

| Resource Utilization Performance Grade |                        | <b>-7</b> , <b>-8</b> , <b>-9</b>                                                           |

|                                        | Lattice Implementation | IP core v3.2.0—Lattice Radiant software 2025.1.1                                            |

| Design Tool Support                    | Synthesis              | Synopsys Synplify Pro software for Lattice                                                  |

|                                        | Simulation             | Not supported                                                                               |

### 1.3. IP Support Summary

Table 1.2. USB2.0/3.2 IP Support Readiness

| Device Family | e Family Radiant Timing Model Hardware Validated |     |

|---------------|--------------------------------------------------|-----|

| CrossLinkU-NX | Final                                            | Yes |

#### 1.4. Features

The following lists the key features of the USB 2.0/3.2 IP core:

- Supports High Speed and Full Speed USB 2.0 specification and Super Speed USB 3.2 specification.

- Supports high-speed, high-bandwidth isochronous transactions.

- Supports two control endpoints at EPO/1 (1 IN 1 OUT) and eight individually reconfigurable logical endpoints. Each

logical endpoint reflects two physical endpoints: one IN and one OUT. For more information, refer to the CrossLink-NX33 and CrossLinkU-NX Data Sheet (FPGA-DS-02104).

- Includes an example design as a reference usage model.

# 1.5. Licensing and Ordering Information

The USB 2.0/3.2 IP is provided at no additional cost with the Lattice Radiant software.

### 1.6. Hardware Support

Refer to the Example Design section for more information on the boards used.

### 1.7. Minimum Device Requirements

The minimum device requirements for the USB 2.0/3.2 IP core are as follows:

#### Table 1.3. Minimum Device Requirements for the USB 2.0/3.2 IP Core

| Devices       | Speed Grades |

|---------------|--------------|

| CrossLinkU-NX | -7           |

# 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

# 1.8.2. Signal Names

Signals name having extension as:

- \_n are active low signals (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

- \_io are bidirectional signals

# 2. Functional Description

#### 2.1. IP Architecture Overview

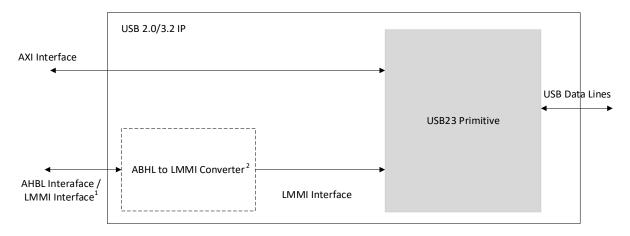

The USB 2.0/3.2 IP core includes the following components:

- USB23 primitive

- Lattice Memory Mapped Interface (LMMI)

- AHBL to LMMI converter (Optional)

- Advanced Extensible Interface (AXI)

- USB data lines

Figure 2.1. USB 2.0/3.2 IP Block Diagram

#### Notes:

- 1. The LMMI interface is available if the AHBL interface is not enabled.

- 2. The AHBL to LMMI converter is optional and can be enabled through the GUI. The default mode is LMMI interface.

### 2.2. Clocking

#### 2.2.1. Clocking Overview

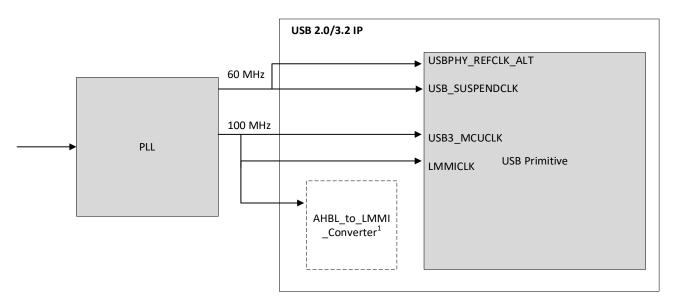

Figure 2.2. USB 2.0/3.2 IP Clock Domain Block Diagram

#### Note:

The AHBL\_to\_LMMI\_Converter is enabled through the GUI by selecting HOST\_IF = AHBL. The AHBL clock and LMMI clock must share the same clock source.

#### 2.1 User Interfaces

The LMMI configuration interface and the AXI data interface are available for the user application to connect with the USB 2.0/3.2 IP and perform the transfers. These interfaces use usb23\_reference\_clk.

#### 2.2 Internal IP Blocks

#### 2.2.1 USB 2.0/3.2

The USB 2.0/3.2 is the hard IP block for the USB device. It is compliant to the USB-IF standards and provides all the functionality.

#### 2.2.2 AHBL-to-LMMI Converter

The AHBL-to-LMMI converter is used to convert the AHBL interface to the LMMI interface. This block is optional and can be enabled through the GUI selection. The default mode is LMMI interface.

# 3. IP Parameter Description

The configurable attributes of the USB 2.0/3.2 IP core are shown in Table 3.1. You can configure the IP core by setting the attributes accordingly in the IP Catalog's Module/IP wizard of the Lattice Radiant software.

Table 3.1. General Attributes of the USB 2.0/3.2 IP Core

| Attribute | Default Value | Description                                                               |

|-----------|---------------|---------------------------------------------------------------------------|

| USB Mode  | USB23         | USB mode of operation options:                                            |

|           |               | USB2: Supports USB2 mode only                                             |

|           |               | USB3: Supports USB3 mode only                                             |

|           |               | <ul> <li>USB23: Supports both USB2 and USB3 mode (recommended)</li> </ul> |

| GSR       | Enabled       | Global set reset:                                                         |

|           |               | Enabled                                                                   |

|           |               | Disabled                                                                  |

| Host_IF   | LMMI          | CSR interface:                                                            |

|           |               | • LMMI                                                                    |

|           |               | • AHBL                                                                    |

# 4. Signal Description

This section describes the USB 2.0/3.2 IP ports.

#### 4.1. Clock Interface

**Table 4.1. Clock Ports**

| Port                | Туре   | Width | Description                                                                                                                        |

|---------------------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| USB3_MCUCLK_i       | Input  | 1     | Clock for the USB Hard IP and other modules. The frequency is 100 MHz.                                                             |

| USBPHY_REFCLK_ALT_i | Input  | 1     | Internal clock for the USB 2.0 and USB 3.0 (60 MHz).                                                                               |

| REFINCLKEXTP_i      | Input  | 1     | USB 3.0 PHY external positive differential clock.                                                                                  |

| REFINCLKEXTM_i      | Input  | 1     | USB 3.0 PHY external negative differential clock.                                                                                  |

| USB_SUSPENDCLK_i    | Input  | 1     | To achieve low power during suspend state, the PIPE3/MAC3/MAC2/MAC clock is switched to a lower frequency variable clock (60 MHz). |

| XOIN18_i            | Input  | 1     | 24 MHz or 12 MHz crystal input pad.                                                                                                |

| XOOUT18_o           | Output | 1     | 24 MHz or 12 MHz crystal output pad.                                                                                               |

#### 4.2. Reset Interface

**Table 4.2. Reset Interface**

| Port           | Туре  | Width | Description                                                                                                                  |

|----------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------|

| USB_RESETN_i   | Input | 1     | Asynchronous, active low reset signal.                                                                                       |

| USB2_RESET_i   | Input | 1     | Synchronous reset for USB 2.0 PHY. Resets all blocks in the transceiver. The RESET signal should retain no less than 300 ns. |

| USB3_SYSRSTN_i | Input | 1     | Active low reset signal for USB 3.0 PHY.                                                                                     |

#### 4.3. USB Interface

Table 4.3. USB Interface

| Port     | Туре   | Width | Description                                                  |

|----------|--------|-------|--------------------------------------------------------------|

| usb23_DP | Inout  | 1     | USB 2.0 positive data line.                                  |

| usb23_DM | Inout  | 1     | USB 2.0 negative data line.                                  |

| RXM_i    | Input  | 1     | USB 3.0 negative differential data line for the receiver.    |

| RXP_i    | Input  | 1     | USB 3.0 positive differential data line for the receiver.    |

| TXM_o    | Output | 1     | USB 3.0 negative differential data line for the transmitter. |

| TXP_o    | Output | 1     | USB 3.0 positive differential data line for the transmitter. |

# 4.4. LMMI/AHBL Interface – Configuration Path

**Table 4.4. LMMI Interface - Configuration Path**

| Port           | Туре  | Width | Description                                                                 |

|----------------|-------|-------|-----------------------------------------------------------------------------|

| lmmi_clk_i     | Input | 1     | Clock signal for the LMMI interface. The clock frequency is 100 MHz.        |

| lmmi_rst_n_i   | Input | 1     | Active low reset signal for the LMMI interface.                             |

| lmmi_request_i | Input | 1     | Start transaction. Asserted during read or write cycle.                     |

| Immi_offset_i  | Input | 15    | LMMI address bus.                                                           |

| lmmi_wr_rdn_i  | Input | 1     | Indicates the direction of the transfer. Indicates a write access when high |

| Port               | Туре   | Width | Description                                                                                             |

|--------------------|--------|-------|---------------------------------------------------------------------------------------------------------|

|                    |        |       | and a read access when low.                                                                             |

| Immi_wdata_i       | Input  | 32    | LMMI write data bus.                                                                                    |

| lmmi_rdata_o       | Output | 32    | LMMI read data bus.                                                                                     |

| lmmi_rdata_valid_o | Output | 1     | Indicates that the read transaction is complete and Immi_rdata_o contains valid data.                   |

| lmmi_ready_o       | Output | 1     | Indicates that the previous transaction is complete and the target is ready to start a new transaction. |

**Table 4.5. AHBL Interface - Configuration Path**

| Port             | Туре   | Width | Description                                                                           |

|------------------|--------|-------|---------------------------------------------------------------------------------------|

| ahbl_clk         | Input  | 1     | Clock signal for the AHBL interface. The clock frequency is 100 MHz.                  |

| ahbl_rst_n       | Input  | 1     | Active low reset signal for the AHBL interface.                                       |

| ahbl_haddr_i     | Input  | 32    | Write address.                                                                        |

| ahbl_hburst_i    | Input  | 3     | Unused.                                                                               |

| ahbl_hprot_i     | Input  | 4     | Unused.                                                                               |

| ahbl_hmastlock_i | Input  | 1     | Unused.                                                                               |

| ahbl_hsize_i     | Input  | 1     | Unused.                                                                               |

| ahbl_hready_i    | Input  | 1     | Indicates transfer completion.                                                        |

| ahbl_hsel_i      | Input  | 1     | Subordinate select.                                                                   |

| ahbl_hwdata_i    | Input  | 32    | AHBL write data bus.                                                                  |

| ahbl_htrans_i    | Input  | 2     | Transfer type of the current transfer (IDLE/BUSY/NSEQ/SEQ).                           |

| ahbl_hwrite_i    | Input  | 1     | Write = 1, Read = 0.                                                                  |

| ahbl_hrdata_o    | Output | 32    | AHBL read data bus.                                                                   |

| ahbl_hreadyout_o | Output | 1     | Indicates that the read transaction is complete and Immi_rdata_o contains valid data. |

| ahbl_hresp_o     | output | 1     | Subordinate response (OKAY/ERROR) .                                                   |

# 4.5. AXI Interface - Data Path

#### Table 4.6. AXI Interface - Data Path

| Port         | Туре   | Width | Description                                                                                                                                                                                                                 |

|--------------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xm_awaddr_o  | Output | 32    | AXI write address. Specifies the address of the first transfer in the write burst transaction. Associated control signals determine the address of the remaining transfers in a burst.                                      |

| xm_awid_o    | Output | 8     | AXI write address ID. Gives identification tag for write address signals.                                                                                                                                                   |

| xm_awvalid_o | Output | 1     | AXI write address valid. This signal indicates that the channel is signaling valid write address and control information when it is high. Address and control information remains stable until xm_awready_i signal is high. |

| xm_awsize_o  | Output | 3     | AXI write burst size. Indicates the size of each transfer in a burst. Byte lane strobes indicate exactly which byte lanes to update.                                                                                        |

| xm_awlen_o   | Output | 8     | AXI write burst length. Specifies the exact number of transfers in burst, determines the number of data transfers associated with the address.                                                                              |

| xm_awburst_o | Output | 2     | AXI write burst type. Combined with the size information and shows how the address for each transfer within a burst is calculated.  01 – INCR  10 – WRAP  11 – RESERVED  00 – FIXED                                         |

| Port             | Туре   | Width | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xm_awcache_o     | Output | 4     | AXI write memory type. This signal indicates how transactions are required to progress through a system.  [0] – Bufferable  [1] – Cacheable  [2] – Write through  [3] – Write back                                                                                                                                                                                                          |

| xm_awprot_o      | Output | 3     | AXI write protection type. This signal indicates the privilege and security level of the transaction and whether the transaction is for data access or instruction access.  [0] – Privileged or unprivileged  [1] – Secure or non-secure  [2] – Instruction or data access                                                                                                                  |

| xm_awready_i     | Input  | 1     | AXI write address ready. When the signal is high it indicates that the subordinate is ready to accept the address and associated control signals.                                                                                                                                                                                                                                           |

| xm_awmisc_info_o | Output | 4     | AXI write request miscellaneous information. Currently not used so leave it unconnected.                                                                                                                                                                                                                                                                                                    |

| xm_awlock_o      | Output | 2     | AXI write lock type. Provides additional information about atomic characteristics of the transfer.  00 – Normal  01 – Exclusive  10 – Locked  11 – Reserved.                                                                                                                                                                                                                                |

| xm_wdata_o       | Output | 64    | AXI write data.                                                                                                                                                                                                                                                                                                                                                                             |

| xm_wstrb_o       | Output | 8     | AXI write strobes. This signal indicates which byte lanes hold valid data.  There is one write strobe bit for every 8 bits of the write data bus.                                                                                                                                                                                                                                           |

| xm_wvalid_o      | Output | 1     | AXI write valid. This signal indicates that valid write data and strobes are available when it is high.                                                                                                                                                                                                                                                                                     |

| xm_wlast_o       | Output | 1     | AXI write last. This signal indicates the last transfer in a write burst.                                                                                                                                                                                                                                                                                                                   |

| xm_wid_o         | Output | 8     | AXI write data ID. Gives identification tag for write data transfer signals.                                                                                                                                                                                                                                                                                                                |

| xm_wready_i      | Input  | 1     | AXI write ready. When this signal is high, it indicates that the subordinate can accept write data.                                                                                                                                                                                                                                                                                         |

| xm_bid_i         | Input  | 8     | AXI response ID tag. Gives identification tag for write response signals.                                                                                                                                                                                                                                                                                                                   |

| xm_bvalid_i      | Input  | 1     | AXI write response valid. When this signal is high, it indicates that the valid write response is available.                                                                                                                                                                                                                                                                                |

| xm_bmisc_info_i  | Input  | 4     | AXI write response miscellaneous information. This signal is currently not in use, tie to '0'.                                                                                                                                                                                                                                                                                              |

| xm_bresp_i       | Input  | 2     | AXI write response. Indicates the status of the write transaction. This signal indicates an error if the data phase ID does not match the address phase ID. For example, if xm_awid_o = 0 and xm_wid_o != 0, the controller responds with bresp error.  00 – OKAY (Normal access success)  01 – EXOKAY (Exclusive access okay)  10 – SLVERR (Subordinate error)  11 – DECERR (Decode error) |

| xm_bready_o      | Output | 1     | AXI response ready. This signal indicates that the manager can accept a write response when it is high.                                                                                                                                                                                                                                                                                     |

| xm_araddr_o      | Output | 32    | AXI read address. Gives the initial address of the read burst transaction.  The control signals issued alongside the address show how the address is calculated for the remaining transfers in a burst.                                                                                                                                                                                     |

| xm_arvalid_o     | Output | 1     | AXI read address valid. When this signal is high, it indicates that the channel is signaling a valid read address and control information. Address and control information remains stable until xm_arready_i signal is high.                                                                                                                                                                |

| xm_arlen_o       | Output | 8     | AXI read burst length. Specifies the exact number of transfers in burst,                                                                                                                                                                                                                                                                                                                    |

| Port             | Туре   | Width | Description                                                                                                                                                                                                                                                                |

|------------------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |        |       | determines the number of data transfers associated with the address.                                                                                                                                                                                                       |

| xm_arsize_o      | Output | 3     | AXI read burst size. Indicates the size of each transfer in a burst.                                                                                                                                                                                                       |

| xm_arburst_o     | Output | 2     | AXI read burst type. Combined with the size information and shows how the address for each transfer within a burst is calculated.  01 – INCR  10 – WRAP  00 – FIXED  11 – RESERVED                                                                                         |

| xm_arid_o        | Output | 8     | AXI read address ID. Gives identification tag for read address signals.                                                                                                                                                                                                    |

| xm_arcache_o     | Output | 4     | AXI read memory type. This signal indicates how transactions are required to progress through a system.  [0] – Bufferable  [1] – Cacheable  [2] – Write through  [3] – Write back                                                                                          |

| xm_arprot_o      | Output | 3     | AXI read protection type. This signal indicates the privilege and security level of the transaction, and whether the transaction is for data access or instruction access.  [0] – privileged or Unprivileged  [1] – secure or non-secure  [2] – instruction or data access |

| xm_armisc_info_o | Output | 4     | AXI read request miscellaneous information. Currently not in use so leave it unconnected.                                                                                                                                                                                  |

| xm_arlock_o      | Output | 2     | AXI read lock type. Provides additional information about atomic characteristics of the transfer.  00 – Normal  01 – Exclusive  10 – Locked  11 Reserved                                                                                                                   |

| xm_arready_i     | Input  | 1     | AXI read address ready. When the signal is high, it indicates that the subordinate is ready to accept read address and associated control signals.                                                                                                                         |

| xm_rid_i         | Input  | 8     | AXI read ID tag. Gives the identification tag for read data transfer signals.                                                                                                                                                                                              |

| xm_rvalid_i      | Input  | 1     | AXI read valid. When this signal is high, it indicates that required read data is available and read transfer can complete.                                                                                                                                                |

| xm_rlast_i       | Input  | 1     | AXI read last. This signal indicates the last transfer in a read burst.                                                                                                                                                                                                    |

| xm_rdata_i       | Input  | 64    | AXI read data.                                                                                                                                                                                                                                                             |

| xm_rmisc_info_i  | Input  | 4     | AXI read response miscellaneous information. This signal is currently not used, tie it to '0'.                                                                                                                                                                             |

| xm_rresp_i       | Input  | 2     | AXI read response. Indicates the status of the read transaction.  00 – OKAY (Normal access success)  01 – EXOKAY (Exclusive access okay)  10 – SLVERR (Subordinate error)  11 – DECERR (Decode error)                                                                      |

| xm_rready_o      | Output | 1     | AXI read ready. This signal indicates that the manager can accept a read and response when it is high.                                                                                                                                                                     |

| interrupt_o      | Output | 1     | Interrupt output signal. This signal indicates that there is an interrupt request.                                                                                                                                                                                         |

18

# 4.6. Other Signals

#### Table 4.7. Other Signals

| Port       | Туре  | Width | Description                                                             |

|------------|-------|-------|-------------------------------------------------------------------------|

| VBUS_i     | Input | 1     | Power signal.                                                           |

| RESEXTUSB2 | Inout | 1     | This is a pad to connect an extra 300 ohm (±1%) resistor to the ground. |

| RESEXTUSB3 | Inout | 1     | This is a pad to connect an extra 300 ohm (±1%) resistor to the ground. |

# 5. Register Description

This section describes the USB IP register information. The USB IP has the following three types of register interfaces:

- USB IP Controller Register Information

- USB IP Controller Control Status Register Information

- USB IP 2.0 PHY Control Status Register Information

The USB IP register address is in 17-bit format ([0:16] bits) as follows:

• USB IP 2.0 PHY Control Status Register Information: 16th bit = 1 and [15:12] = 2

# 5.1. USB IP Controller Register Information

Table 5.1 lists the USB IP Controller Register Information.

**Table 5.1. USB IP Controller Register Information**

| Offset              | Register Name                        | Description                                    |

|---------------------|--------------------------------------|------------------------------------------------|

| 0xc110              | GLOBAL_CTL                           | Global Core Control Register.                  |

| 0xc120              | GLOBAL_ID                            | Global ID Register.                            |

| 0xc200 +            | GLOBAL_USB2_PHY_CFG(#n) (for n = 0)  | Global USB2 PHY Configuration Register.        |

| (i * 0x4)           |                                      |                                                |

| 0xc2c0 + (i * 0x4)  | GLOBAL_USB3_PIPE_CTL(#n) (for n = 0) | Global USB 3.0 PIPE Control Register.          |

| 0xc400 +            | GLOBAL_EVNT_ADR(#n) (for n = 0)      | Global Event Buffer Address Register.          |

| (i * 0x10)          |                                      |                                                |

| 0xc404 +            | GLOBAL_EVNT_ADRHI(#n) (for n = 0)    | Global Event Buffer Address (High) Register.   |

| (i * 0x10)          |                                      |                                                |

| 0xc408 +            | GLOBAL_EVNT_SIZ(#n) (for n = 0)      | Global Event Buffer Size Register.             |

| (i * 0x10)          |                                      |                                                |

| 0xc40c + (i * 0x10) | GLOBAL_EVNT_COUNT(#n) (for n = 0)    | Global Event Buffer Count Register.            |

| 0xc700              | DEVICE_CFG                           | Device Configuration Register.                 |

| 0xc704              | DEVICE_CTL                           | Device Control Register Note.                  |

| 0xc708              | DEVICE_EVNT_EN                       | Device Event Enable Register.                  |

| 0xc70c              | DEVICE_STS                           | Device Status Register.                        |

| 0xc720              | DEVICE_ACT_EP_EN                     | Device Active USB Endpoint Enable Register.    |

| 0xc800 +            | DEVICE_EP_CMDPAR2[0:7]               | Device Physical Endpoint-n Command Parameter 2 |

| (i * 0x10)          |                                      | Register (DEPCMDPAR2n).                        |

| 0xc804 +            | DEVICE_EP_CMDPAR1[0:7]               | Device Physical Endpoint-n Command Parameter 1 |

| (i * 0x10)          |                                      | Register (DEPCMDPAR1n).                        |

| 0xc808 +            | DEVICE_EP_CMDPAR0[0:7]               | Device Physical Endpoint-n Command Parameter 0 |

| (i * 0x10)          |                                      | Register (DEPCMDPAR0n).                        |

| 0xc80c + (i * 0x10) | DEVICE_EP_CMD[0:7]                   | Device Physical Endpoint-n Command Register    |

|                     |                                      | (DEPCMD).                                      |

| 0xc300 + (i*0x4)    | GLOBAL_TX_FIFO_SIZE                  | Global Transmit FIFO Size Register.            |

| 0xc380 + (n*0x4)    | GLOBAL_RX_FIFO_SIZE                  | Global Receiver FIFO Size Register.            |

# 5.1.1 Global Core Control Register (GCTL)

The default value of the GLOBAL\_CTL Register is 0x30c12004.

Table 5.2. GLOBAL\_CTL

| Bit   | Label            | Access | Description                                                                                                                                                                                        |

|-------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:19 | PWRDNSCALE       | R/W    | Power Down Scale (PwrDnScale).                                                                                                                                                                     |

|       |                  |        | The USB3 suspend_clk input replaces pipe3_rx_pclk as a clock source to a small part of the USB3 controller that operates when the SS PHY is in its lowest power (P3) state, and therefore does not |

|       |                  |        | provide a clock.  The Power Down Scale field specifies how many suspend_clk periods fit into a 16 kHz clock period. When performing the division, round up the remainder.                          |

|       |                  |        | For example, when using an 8-bit/16-bit/32-bit PHY and 25 MHz Suspend clock,  Power Down Scale = 25000 kHz/16 kHz = 13'd1563 (rounded up)                                                          |

|       |                  |        | Note:                                                                                                                                                                                              |

|       |                  |        | Minimum suspend clock frequency is 32 kHz                                                                                                                                                          |

|       |                  |        | Maximum suspend clock frequency is 125 MHz                                                                                                                                                         |

|       |                  |        | The LTSSM uses the suspend clock for 12-ms and 100-ms timers during suspend mode. According to the USB 3.0 specification, the accuracy on these timers is 0% to +50%.                              |

| ı     |                  |        | • 12 ms + 0~+50% accuracy = 18 ms (Range is 12 ms – 18 ms)                                                                                                                                         |

|       |                  |        | • 100 ms + 0~+50% accuracy = 150 ms (Range is 100 ms - 150 ms).                                                                                                                                    |

|       |                  |        | The suspend clock accuracy requirement is:                                                                                                                                                         |

|       |                  |        | • (12,000/62.5) * (GLOBAL_CTL[31:19]) * actual                                                                                                                                                     |

|       |                  |        | suspend_clk_pe- riod must be between 12,000 and 18,000                                                                                                                                             |

|       |                  |        | • (100,0000/62.5) * (GLOBAL_CTL[31:19]) * actual                                                                                                                                                   |

|       |                  |        | suspend_clk_pe-riod must be between 100,000 and 150,000 For example, if suspend_clk frequency varies from 7.5 MHz to 10.5                                                                          |

|       |                  |        | MHz, then the value needs to be programmed is:                                                                                                                                                     |

|       |                  |        | Power Down Scale = 10500/16 = 657 (rounded up and fastest)                                                                                                                                         |

|       |                  |        | frequency used).                                                                                                                                                                                   |

| 18    | MASTERFILTBYPASS | R/W    | Controller Filter Bypass.                                                                                                                                                                          |

|       |                  |        | When this bit is set to 1'b1, irrespective of the parameter                                                                                                                                        |

|       |                  |        | `USB3_EN_BUS_FILTERS chosen, all the filters in the USB3_filter                                                                                                                                    |

|       |                  |        | module are bypassed.                                                                                                                                                                               |

|       |                  |        | The double synchronizers to mac_clk preceding the filters are also bypassed. For enabling the filters, this bit must be 1'b0.                                                                      |

| 17    | BYPSSETADDR      | R/W    | Bypass SetAddress in Device Mode.                                                                                                                                                                  |

| ı     |                  | '      | When BYPSSETADDR bit is set, the device controller uses the value                                                                                                                                  |

|       |                  |        | in the DCFG[DevAddr] bits directly for comparing the device                                                                                                                                        |

|       |                  |        | address in the tokens.                                                                                                                                                                             |

|       |                  |        | When the xHCl Debug capability is enabled and this bit is set, the                                                                                                                                 |

|       |                  |        | Debug Target immediately enters the configured state without                                                                                                                                       |

|       |                  |        | requiring the Debug Host to send a SetAddress or SetConfig request.                                                                                                                                |

|       |                  |        | <b>Note</b> : In the actual hardware, this bit must be set to 1'b0.                                                                                                                                |

| 16    | U2RSTECN         | R/W    | U2RSTECN                                                                                                                                                                                           |

|       |                  |        | If the SuperSpeed connection fails during POLL or LMP exchange,                                                                                                                                    |

|       |                  |        | the device connects at non-SS mode.                                                                                                                                                                |

|       |                  |        | If this bit is set, then device attempts three more times to connect                                                                                                                               |

| ı     |                  |        | at SS, even if it previously failed to operate in SS mode. For each                                                                                                                                |

| 1     |                  |        | attempt, the device checks receiver termination eight times.                                                                                                                                       |

|       |                  |        | From 2.60a release, this bit controls whether to check for                                                                                                                                         |

| Bit   | Label          | Access  | Description                                                                                                                                         |

|-------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                |         | Rx.Detect eight times or one time for every attempt. Device                                                                                         |

|       |                |         | controller on USB 2.0 reset checks for receiver termination eight                                                                                   |

| İ     |                |         | times per attempt, if this bit is set to zero, or only once per                                                                                     |

|       |                |         | attempt if the bit is set to one.  Note: This bit is applicable only in device mode.                                                                |

| 15.14 | EDNACCI DVA(NI | D/M     |                                                                                                                                                     |

| 15:14 | FRMSCLDWN      | R/W     | FRMSCLDWN  This field scales down device view of a SOF/USOF/ITB duration                                                                            |

| İ     |                |         | This field scales down device view of a <u>SOF/USOF/ITP</u> duration. For SS/HS mode:                                                               |

| Í     |                |         | Value of 2'h3 implements interval to be 15.625 us                                                                                                   |

| Í     |                |         | Value of 2'h2 implements interval to be 13:023 us                                                                                                   |