# **I3C Target IP**

IP Version: v3.7.0

# **User Guide**

FPGA-IPUG-02227-1.6

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Abbreviations in | This Document                         | 9  |

|------------------|---------------------------------------|----|

| 1. Introduction  | 1                                     | 11 |

| 1.1. Overv       | iew of the IP                         | 11 |

| 1.2. Quick       | Facts                                 | 11 |

| 1.3. IP Sup      | port Summary                          | 11 |

| 1.4. Featur      | res                                   | 12 |

| 1.5. Licens      | ing and Ordering Information          | 12 |

|                  | vare Support                          |    |

|                  | num Device Requirements               |    |

|                  | ng Conventions                        |    |

|                  | menclature                            |    |

|                  | nal Names                             |    |

| U                | ribute Names                          |    |

|                  | Description                           |    |

|                  | hitecture Overview                    |    |

|                  | ng                                    |    |

|                  | ris                                   |    |

|                  | CKING OVERVIEW                        |    |

|                  | nterfaces                             |    |

|                  | ansfers in SDR Mode                   | -  |

|                  | padcast CCC                           |    |

|                  | ect CCC                               |    |

|                  | vate Write                            |    |

|                  |                                       |    |

|                  | vate Read                             |    |

|                  | ode                                   |    |

|                  | Write                                 |    |

|                  | C Read                                |    |

|                  | non Command Codes                     |    |

|                  | ansfers in HDR-DDR Mode               |    |

|                  | pical HDR-DDR Mode Frame              |    |

|                  | R-DDR Write                           |    |

|                  | R-DDR Read                            |    |

|                  | R-DDR Broadcast CCC                   |    |

|                  | R-DDR Direct Set CCC                  |    |

|                  | R-DDR Direct Get CCC                  |    |

| 2.9. Hot-Jo      | oin Mechanism                         | 22 |

| 2.9.1. Gei       | nerating a Hot-Join Request           | 22 |

| 2.10. In-Ban     | nd Interrupt                          | 22 |

| 2.10.1. Ger      | nerating an In-band Interrupt         | 22 |

| 2.10.2. Ser      | nding the IBI Payload                 | 23 |

| 2.10.3. Per      | nding Read Notification               | 23 |

| 2.10.4. Lim      | nitation for IBI and Private Read     | 23 |

| 2.11. Target     | t Reset                               | 24 |

| 2.12. Secon      | dary Controller Support               | 24 |

|                  | nerating the Controller Role Request  |    |

|                  | C for Secondary Controller Support    |    |

|                  | DDR Support                           |    |

|                  | er Description                        |    |

|                  | ral                                   |    |

|                  | ameter Settings for Example Use Cases |    |

| J                |                                       |    |

| 4. | _     | nal Description                                   |    |

|----|-------|---------------------------------------------------|----|

| 5. | Reg   | gister Description                                | 31 |

| 5  | 5.1.  | Bus Characteristics Register 0x00                 | 33 |

| 5  | 5.2.  | Device Characteristics Register 0x01              |    |

| 5  | 5.3.  | Dynamic Address Register 0x02                     | 34 |

| 5  | 5.4.  | Events Command Enable Register 0x03               | 34 |

| 5  | 5.5.  | Events Command Device Configuration Register 0x04 | 35 |

| 5  | .6.   | Events Command Request Register 0x05              | 35 |

| 5  | .7.   | Hot-Join/IBI Retry Register 0x06                  | 35 |

| 5  | .8.   | Maximum Write Length (MSB) Register 0x07          | 35 |

| 5  | .9.   | Maximum Write Length (LSB) Register 0x08          | 36 |

| 5  | .10.  | Maximum Read Length (MSB) Register 0x09           |    |

| 5  | .11.  | Maximum Read Length (LSB) Register 0x0A           | 36 |

| 5  | .12.  | Maximum IBI Payload Size Register 0x0B            |    |

| 5  | .13.  | Maximum Write Data Speed (MaxWr) Register 0x0C    | 37 |

| 5  | .14.  | Maximum Read Data Speed (MaxRd) Register 0x0D     |    |

| 5  | .15.  | Maximum Read Turnaround Time Byte2 Register 0x0E  | 38 |

| 5  | .16.  | Maximum Read Turnaround Time Byte1 Register 0x0F  |    |

| 5  | .17.  | Maximum Read Turnaround Time Byte0 Register 0x10  | 38 |

| 5  | .18.  | Device Provisioned ID Byte6 Register 0x11         |    |

| 5  | .19.  | Device Provisioned ID Byte5 Register 0x12         |    |

| 5  | .20.  | Device Provisioned ID Byte4 Register 0x13         |    |

| 5  | .21.  | Device Provisioned ID Byte3 Register 0x14         |    |

| 5  | .22.  | Device Provisioned ID Byte2 Register 0x15         |    |

| 5  | .23.  | Device Provisioned ID Byte1 Register 0x16         |    |

| 5  | .24.  | Static Address Register 0x17                      |    |

| 5  | .25.  | Device Capabilities Byte1 Register 0x18           | 40 |

| 5  | .26.  | Device Capabilities Byte2 Register 0x19           |    |

| 5  | .27.  | Device Capabilities Byte3 Register 0x1A           |    |

| 5  | .28.  | Oscillator Inaccuracy Register 0x1C               |    |

| 5  | .29.  | Receive FIFO Register 0x20                        |    |

| 5  | .30.  | Transmit FIFO Register 0x22                       |    |

| 5  | .31.  | Soft Reset Register 0x28                          |    |

| 5  | .32.  | Target Response Register 0x29                     |    |

| 5  | .33.  | Get Status MSB Register 0x2A                      |    |

| 5  | .34.  | Get Status LSB Register 0x2B                      |    |

| 5  | .35.  | Bus Activity State Register 0x2C                  |    |

| 5  | .36.  | Target Reset Action 1 Register 0x2D               |    |

|    | .37.  | Target Reset Action 2 Register 0x2E               |    |

|    | .38.  | Target Reset Action 3 Register 0x2F               |    |

|    | .39.  | Interrupt Status 1 Register 0x30                  |    |

|    | .40.  | Interrupt Enable 1 Register 0x31                  |    |

|    | .41.  | Interrupt Set 1 Register 0x32                     |    |

|    | .42.  | Interrupt Status 2 Register 0x33                  |    |

|    | .43.  | Interrupt Enable 2 Register 0x34                  |    |

|    | .44.  | Interrupt Set 2 Register 0x35                     |    |

|    | .45.  | Interrupt Status 3 Register 0x36                  |    |

|    | .46.  | Interrupt Enable 3 Register 0x37                  |    |

|    | .47.  | Interrupt Set 3 Register 0x38                     |    |

|    | .48.  | Interrupt Status 5 Register 0x3C                  |    |

|    | .49.  | Interrupt Enable 5 Register 0x3D                  |    |

|    | 5.50. | Interrupt Set 5 Register 0x3E                     |    |

|    | 5.51. | Bus Information Register 0x50                     |    |

| 5  | .52.  | HDR-DDR Target Configuration Register 0x51        | 50 |

| 5.53.    | HDR-DDR Abort Configuration Register 0x54                   | 50 |

|----------|-------------------------------------------------------------|----|

| 5.54.    | Secondary Controller Registers                              | 51 |

| 5.54     | 4.1. Bus Characteristics Register 0x80                      | 53 |

| 5.54     | 4.2. Dynamic Address Register 0x82                          | 54 |

| 5.54     | 4.3. Events Command Enable Register 0x83                    | 55 |

| 5.54     | 4.4. Events Command Device Configuration Register 0x84      | 55 |

|          | 4.5. Events Command Request Register 0x85                   |    |

| 5.54     | 4.6. Maximum Write Data Speed (MaxWr) Register 0x8C         |    |

| 5.54     | 4.7. Device Capabilities Byte 3 Register 0x9A               |    |

|          | 4.8. Interrupt Status 4 Register 0xB9                       |    |

|          | 4.9. Interrupt Enable 4 Register 0xBA                       |    |

|          | 4.10. Interrupt Set 4 Register 0xBB                         |    |

|          | 4.11. DEFTGTS Count Register 0xC0                           |    |

|          | 4.12. DEFTGTS Rx FIFO Start Register 0xC1                   |    |

|          | 4.13. DEFTGTS Rx FIFO Count Register 0xC2                   |    |

|          | 4.14. Controller Role Handoff Register 0xC3                 |    |

|          | 4.15. GETMXDS Controller Capable Device Register 0xC4       |    |

|          | 4.16. GETSTATUS Controller Capable Device LSB Register 0xC5 |    |

|          | 4.17. GETCAPS Controller Capable Device 1 Register 0xC6     |    |

|          | 4.18. GETCAPS Controller Capable Device 2 Register 0xC7     |    |

|          | 4.19. Set Device Role Register 0xC8                         |    |

|          | mple Design                                                 |    |

| 6.1.     | Example Design Supported Configuration                      |    |

| 6.2.     | Overview of the Example Design and Features                 |    |

| 6.3.     | Example Design Components                                   |    |

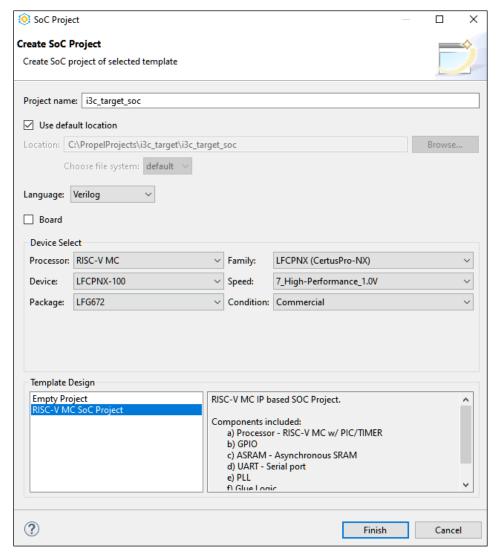

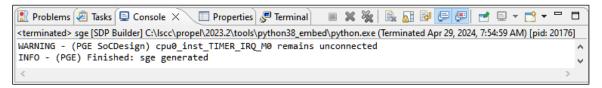

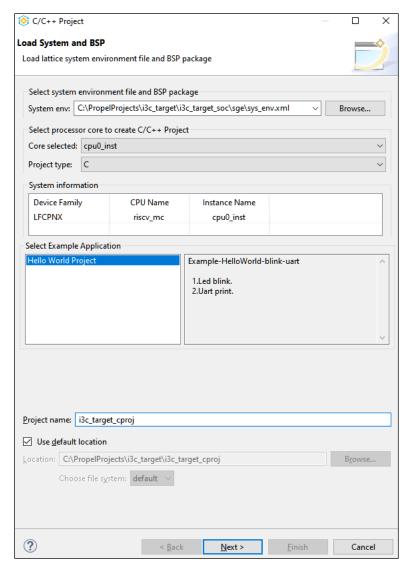

| 6.4.     | Generating the Example Design                               |    |

| 6.5.     | Hardware Testing                                            |    |

| 6.5.     | ···· · · · · · · · · · · · · · · · ·                        |    |

| 6.5.     | ·                                                           |    |

|          | igning with the IP                                          |    |

| 7.1.     | Generating and Instantiating the IP                         |    |

| 7.1.     |                                                             |    |

| 7.2.     | Design Implementation                                       |    |

| 7.3.     | Timing Constraints                                          |    |

| 7.4.     | Physical Constraints                                        |    |

| 7.5.     | Running Functional Simulation                               |    |

|          | x A. Resource Utilization                                   |    |

|          | ces                                                         |    |

|          | l Support Assistance                                        |    |

| Revision | History                                                     | 82 |

# **Figures**

| Figure 2.1. I3C Target IP Core Block Diagram                          | 14 |

|-----------------------------------------------------------------------|----|

| Figure 2.2. I3C Target IP Clock Domain Block Diagram                  | 15 |

| Figure 2.3. Broadcast CCC                                             |    |

| Figure 2.4. Direct CCC                                                |    |

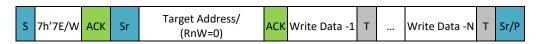

| Figure 2.5. I3C Private Write Initiated with START Condition          |    |

| Figure 2.6. I3C Private Write Initiated with Repeated START Condition |    |

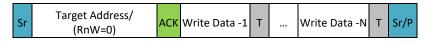

| Figure 2.7. I3C Private Read Initiated with START Condition           | 17 |

| Figure 2.8. I3C Private Read Initiated with Repeated START Condition  | 17 |

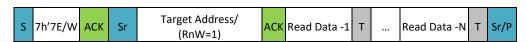

| Figure 2.9. I2C Write                                                 | 18 |

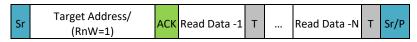

| Figure 2.10. I2C Read                                                 | 18 |

| Figure 2.11. Typical HDR-DDR Mode Frame                               | 20 |

| Figure 2.12. HDR-DDR Write                                            | 20 |

| Figure 2.13. HDR-DDR Read                                             |    |

| Figure 2.14. HDR-DDR Broadcast CCC                                    |    |

| Figure 2.15. HDR-DDR Direct Set CCC                                   |    |

| Figure 2.16. HDR-DDR Direct Get CCC                                   |    |

| Figure 6.1. I3C Target IP in Propel SoC Project                       | 65 |

| Figure 6.2. Sample C Code Test Routine                                |    |

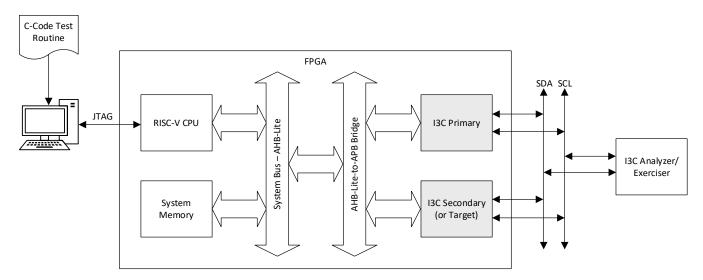

| Figure 6.3. I3C Target Example Design Block Diagram                   | 66 |

| Figure 6.4. Create SoC Project                                        |    |

| Figure 6.5. Define Instance                                           |    |

| Figure 6.6. Build SOC Project Result                                  |    |

| Figure 6.7. Lattice C/C++ Design Project                              | 69 |

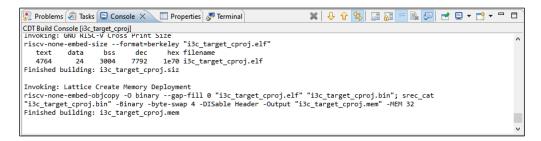

| Figure 6.8. Build C/C++ Project Result                                |    |

| Figure 6.9. Sample ENTDAA Sequence Response by I3C Target             |    |

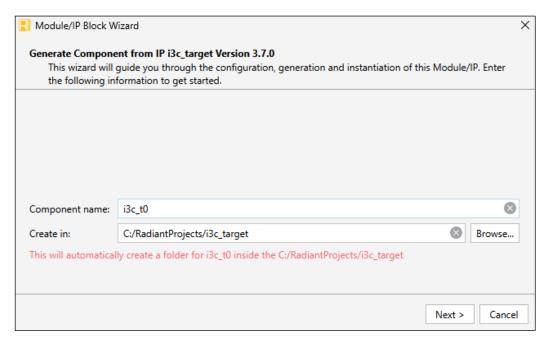

| Figure 7.1. Module/IP Block Wizard                                    |    |

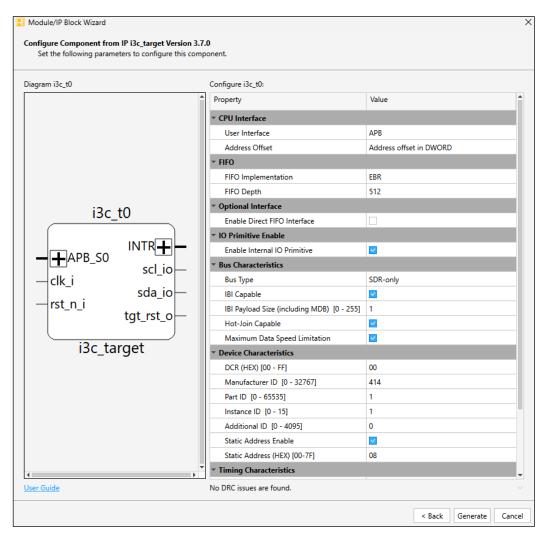

| Figure 7.2. IP Configuration                                          |    |

| Figure 7.3. Check Generated Result                                    | 73 |

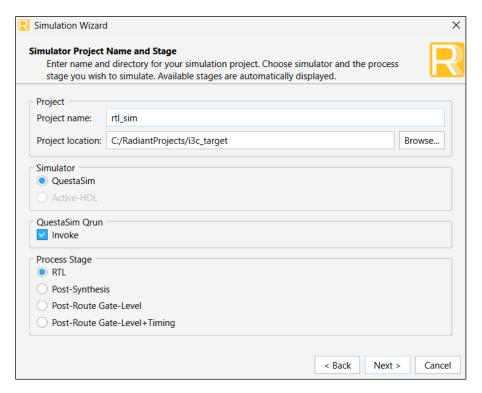

| Figure 7.4. Simulation Wizard                                         | 75 |

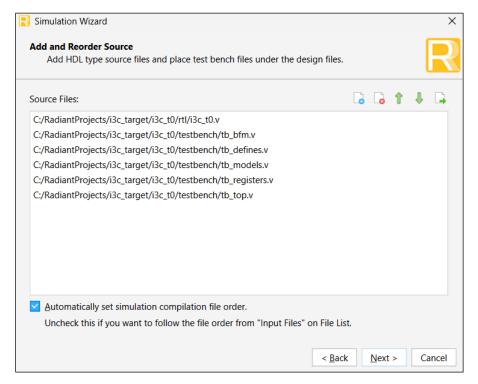

| Figure 7.5. Add and Reorder Source                                    |    |

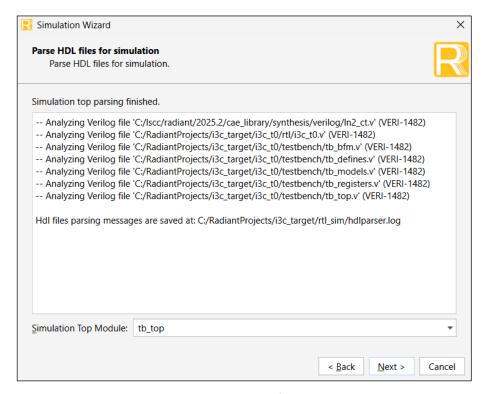

| Figure 7.6. Parse HDL Files for Simulation                            | 76 |

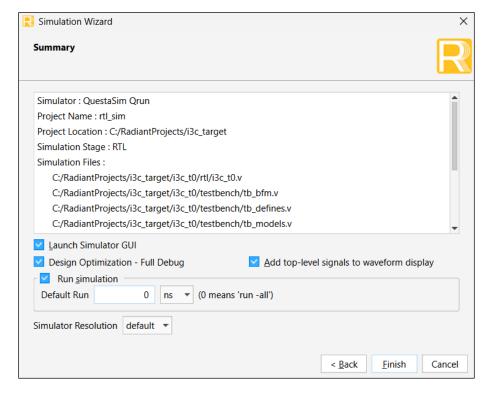

| Figure 7.7. Summary                                                   | 76 |

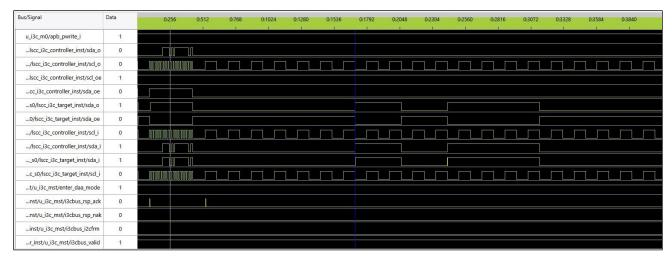

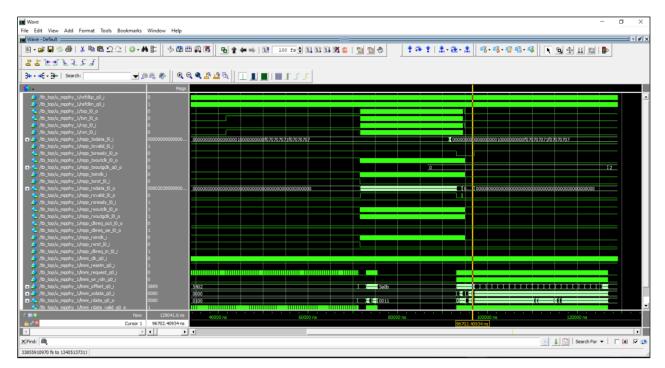

| Figure 7.8. Simulation Waveform                                       | 77 |

# **Tables**

| Table 1.1. Summary of the I3C Target IP                      |    |

|--------------------------------------------------------------|----|

| Table 1.2. I3C Target IP Support Readiness                   | 11 |

| Table 2.1. User Interfaces and Supported Protocols           | 16 |

| Table 2.2. I3C Target IP Supported CCC                       | 19 |

| Table 2.3. Target Reset                                      | 24 |

| Table 2.4. CCCs for Secondary Controller Support             | 24 |

| Table 2.5. CCCs Supported in HDR-DDR Mode                    | 25 |

| Table 3.1. General Attributes                                | 26 |

| Table 3.2. IP Parameter Settings for Example Use Cases       | 27 |

| Table 4.1. Ports Description                                 | 29 |

| Table 5.1. Register Access Types                             |    |

| Table 5.2. I3C Target IP Register Summary                    |    |

| Table 5.3. Bus Characteristics Register 0x00                 |    |

| Table 5.4. Device Characteristics Register 0x01              |    |

| Table 5.5. Dynamic Address Register 0x02                     |    |

| Table 5.6. Events Command Enable Register 0x03               |    |

| Table 5.7. Events Command Device Configuration Register 0x04 |    |

| Table 5.8. Events Command Request Register 0x05              |    |

| Table 5.9. Hot-Join/IBI Retry Register 0x06                  |    |

| Table 5.10. Maximum Write Length (MSB) Register 0x07         |    |

| Table 5.11. Maximum Write Length (LSB) Register 0x08         |    |

| Table 5.12. Maximum Read Length (MSB) Register 0x09          |    |

| Table 5.13. Maximum Read Length (LSB) Register 0x0A          |    |

| Table 5.14. Maximum IBI Payload Size Register 0x0B           |    |

| Table 5.15. Maximum Write Data Speed (MaxWr) Register 0x0C   |    |

| Table 5.16. Maximum Read Data Speed (MaxRd) Register 0x0D    |    |

| Table 5.17. Maximum Read Turnaround Time Byte2 Register 0x0E |    |

| Table 5.18. Maximum Read Turnaround Time Byte1 Register 0x0F |    |

| Table 5.19. Maximum Read Turnaround Time Byte0 Register 0x10 |    |

| Table 5.20. Device Provisioned ID Byte6 Register 0x11        |    |

| Table 5.21. Device Provisioned ID Byte5 Register 0x12        |    |

| Table 5.22. Device Provisioned ID Byte4 Register 0x13        |    |

| Table 5.23. Device Provisioned ID Byte3 Register 0x14        |    |

| Table 5.24. Device Provisioned ID Byte2 Register 0x15        |    |

| Table 5.25. Device Provisioned ID Byte1 Register 0x16        |    |

| Table 5.26. Static Address Register 0x17                     |    |

| Table 5.27. Device Capabilities Byte1 Register 0x18          |    |

| Table 5.28. Device Capabilities Byte2 Register 0x19          |    |

| Table 5.29. Device Capabilities Byte3 Register 0x1A          |    |

| Table 5.30. Oscillator Inaccuracy Register 0x1C              |    |

| Table 5.31. Receive FIFO Register 0x20                       |    |

| Table 5.32. Transmit FIFO Register 0x22                      |    |

| Table 5.33. Soft Reset Register 0x28                         |    |

| Table 5.34. Target Response Register 0x29                    |    |

| Table 5.35. Get Status MSB Register 0x2A                     |    |

| Table 5.36. Get Status LSB Register 0x2B                     |    |

| Table 5.37. Bus Activity State Register 0x2C                 |    |

| Table 5.38. Target Reset Action 1 Register 0x2D              |    |

| Table 5.39. Target Reset Action 2 Register 0x2E              |    |

| Table 5.40. Target Reset Action 3 Register 0x2F              |    |

| Table 5.41. Interrupt Status 1 Register 0x30                 |    |

| Table 5.42. Interrupt Enable 1 Register 0x31                 |    |

| . a.c. o                                                     |    |

| Table 5.43. Interrupt Set 1 Register 0x32                                                |    |

|------------------------------------------------------------------------------------------|----|

| Table 5.44. Interrupt Status 2 Register 0x33                                             |    |

| Table 5.45. Interrupt Enable 2 Register 0x34                                             | 47 |

| Table 5.46. Interrupt Set 2 Register 0x35                                                | 48 |

| Table 5.47. Interrupt Status 3 Register 0x36                                             | 48 |

| Table 5.48. Interrupt Enable 3 Register 0x37                                             | 48 |

| Table 5.49. Interrupt Set 3 Register 0x38                                                | 49 |

| Table 5.50. Interrupt Status 5 Register 0x3C                                             | 49 |

| Table 5.51. Interrupt Enable 5 Register 0x3D                                             | 49 |

| Table 5.52. Interrupt Set 5 Register 0x3E                                                | 49 |

| Table 5.53. Bus Information Register 0x50                                                | 50 |

| Table 5.54. HDR-DDR Target Configuration Register 0x51                                   | 50 |

| Table 5.55. HDR-DDR Abort Configuration Register 0x54                                    | 50 |

| Table 5.56. Secondary I3C Controller Register Summary                                    | 51 |

| Table 5.57. Bus Characteristics Register 0x80                                            | 53 |

| Table 5.58. Dynamic Address Register 0x82                                                | 54 |

| Table 5.59. Events Command Enable Register 0x83                                          | 55 |

| Table 5.60. Events Command Device Configuration Register 0x84                            | 55 |

| Table 5.61. Events Command Request Register 0x85                                         | 56 |

| Table 5.62. Maximum Write Data Speed (MaxWr) Register 0x8C                               | 56 |

| Table 5.63. Device Capabilities Byte 3 Register 0x9A                                     | 56 |

| Table 5.64. Interrupt Status 4 Register 0xB9                                             | 57 |

| Table 5.65. Interrupt Enable 4 Register 0xBA                                             | 58 |

| Table 5.66. Interrupt Set 4 Register 0xBB                                                | 58 |

| Table 5.67. DEFTGTS Count Register 0xC0                                                  | 58 |

| Table 5.68. DEFTGTS Rx FIFO Start Register 0xC1                                          | 59 |

| Table 5.69. DEFTGTS Rx FIFO Count Register 0xC2                                          | 59 |

| Table 5.70. Controller Role Handoff Register 0xC3                                        | 59 |

| Table 5.71. GETMXDS Controller Capable Device Register 0xC4                              | 59 |

| Table 5.72. GETSTATUS Controller Capable Device LSB Register 0xC5                        | 60 |

| Table 5.73. GETCAPS Controller Capable Device 1 Register 0xC6                            | 60 |

| Table 5.74. GETCAPS Controller Capable Device 2 Register 0xC7                            | 61 |

| Table 5.75. Set Device Role Register 0xC8                                                | 62 |

| Table 6.1. I3C Target IP Configuration Supported by the Example Design                   | 63 |

| Table 6.2. I3C Controller IP Version 3.3.0 Configuration Supported by the Example Design | 64 |

| Table 7.1. Generated File List                                                           | 73 |

| Table A.1. Resource Utilization for LFCPNX-100-7ASG256C                                  | 78 |

| Table A.2. Resource Utilization for LIFCL-40-7BG256I                                     | 78 |

| Table A.3. Resource Utilization for LAV-AT-E70-1LFG676I                                  | 79 |

| Table A.4. Pesource Utilization for LN2-CT-20-1CRG/18/1                                  | 70 |

9

# **Abbreviations in This Document**

| Abbreviation | Definition                                |  |  |

|--------------|-------------------------------------------|--|--|

| ACK          | Acknowledgement                           |  |  |

| AHB          | Advanced High-Performance Bus             |  |  |

| AMBA         | Advanced Microcontroller Bus Architecture |  |  |

| APB          | Advanced Peripheral Bus                   |  |  |

| BCR          | Bus Characteristics Register              |  |  |

| CCC          | Common Command Code                       |  |  |

| CPU          | Central Processing Unit                   |  |  |

| CRC          | Cyclic Redundancy Check                   |  |  |

| D2D          | Device to Device                          |  |  |

| DA           | Dynamic Address                           |  |  |

| DAA          | Dynamic Address Assignment                |  |  |

| DCR          | Device Characteristics Register           |  |  |

| DDR          | Double Data Rate                          |  |  |

| DWORD        | Double Word                               |  |  |

| EBR          | Embedded Block RAM                        |  |  |

| FIFO         | First In First Out                        |  |  |

| FPGA         | Field Programmable Gate Array             |  |  |

| GPIO         | General Purpose Input/Output              |  |  |

| GUI          | Graphical User Interface                  |  |  |

| HDL          | Hardware Description Language             |  |  |

| HDR          | High Data Rate                            |  |  |

| НЈ           | Hot-Join                                  |  |  |

| 1/0          | nput/Output                               |  |  |

| I2C          | nter-Integrated Circuit                   |  |  |

| I3C          | mproved Inter Integrated Circuit          |  |  |

| IBI          | In-Band Interrupt                         |  |  |

| IP           | ntellectual Property                      |  |  |

| LMMI         | Lattice Memory Mapped Interface           |  |  |

| LSE          | Lattice Synthesis Engine                  |  |  |

| MC           | Microcontroller                           |  |  |

| MIPI         | Mobile Industry Processor Interface       |  |  |

| MDB          | Mandatory Data Byte                       |  |  |

| MWL          | Maximum Write Length                      |  |  |

| NACK/NAK     | Negative Acknowledgement                  |  |  |

| PIC          | Programmable Interrupt Controller         |  |  |

| PID          | Provisioned Identification                |  |  |

| PLL          | Phase-Locked Loop                         |  |  |

| RAM          | Random Access Memory                      |  |  |

| RISC-V       | Reduced Instruction Set Computer Five     |  |  |

| RO           | Read-Only access                          |  |  |

| RTL          | Register Transfer Level                   |  |  |

| RW           | Read-Write access                         |  |  |

| RW1C         | Read and Write 1 to Clear                 |  |  |

| Rx           | Receiver                                  |  |  |

| Abbreviation | Definition                                  |  |

|--------------|---------------------------------------------|--|

| SA           | Static Address                              |  |

| SCL          | Serial Clock                                |  |

| SDA          | Serial Data                                 |  |

| SDR          | Single Data Rate                            |  |

| SoC          | System on Chip                              |  |

| SRAM         | Static Random Access Memory                 |  |

| Tx           | Transmitter                                 |  |

| UART         | Universal Asynchronous Receiver/Transmitter |  |

| WO           | Write-Only access                           |  |

# 1. Introduction

#### 1.1. Overview of the IP

The Lattice I3C IP is designed to comply with the MIPI I3C specification.

The MIPI I3C interface eases sensor system design architectures in mobile wireless products by providing a fast, low-cost, low-power, two-wire digital interface for sensors. I3C protocol is a single scalable, cost effective, and a power efficient protocol. Implementing the I3C specification greatly increases the implementation flexibility for an ever-expanding sensor subsystem as efficiently and at as low cost as possible.

The I3C protocol is backward compatible with many Legacy I2C devices. The I3C protocol offers greater than 10× speed improvements, more efficient bus power management, new communication modes, and new device roles which includes an ability to change device roles over time. For example, the initial Controller can cooperatively pass the Controller Role to another I3C Device on the Bus, if the requesting I3C Device supports Secondary Controller feature.

## 1.2. Quick Facts

Table 1.1. Summary of the I3C Target IP

| IP Requirements      | Supported Devices        | iCE40 UltraPlus™, MachXO3D™, CrossLink™-NX, Certus™-NX, Certus-NX-RT, CertusPro™-NX, CertusPro-NX-RT, Mach™-NX, MachXO5™-NX, Lattice Avant™, and Certus-N2. |  |

|----------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | IP Changes <sup>1</sup>  | For a list of changes to the IP, refer to the I3C Target IP Release Notes (FPGA-RN-02018).                                                                  |  |

| Resource Utilization | Supported User Interface | Lattice Memory Mapped Interface (LMMI), Advanced Peripheral<br>Bus (APB), Advanced High-Performance Bus-Lite (AHB-Lite)                                     |  |

|                      | Resources                | Refer to Appendix A. Resource Utilization                                                                                                                   |  |

|                      | Lattice Implementation   | IP Core v3.7.0 – Lattice Radiant™ Software 2025.2 and Lattice Propel™ Builder Software 2025.2                                                               |  |

| Design Tool Support  | Synthesis                | Lattice Synthesis Engine (LSE) Synopsys Synplify Pro® for Lattice                                                                                           |  |

|                      | Simulation               | For the list of supported simulators, see the Lattice Radiant Software User Guide.                                                                          |  |

#### Note:

## 1.3. IP Support Summary

Table 1.2. I3C Target IP Support Readiness

| Device Family | System Clock<br>Frequency (MHz) <sup>1</sup> | Supported Feature          | Radiant Timing<br>Model | Hardware<br>Validated |

|---------------|----------------------------------------------|----------------------------|-------------------------|-----------------------|

| Crosslink     | 25                                           | Dynamic Address Assignment | Final                   | Yes                   |

|               |                                              | IBI                        | Final                   | Yes                   |

|               |                                              | Hot-Join                   | Final                   | Yes                   |

|               |                                              | HDR-DDR                    | Final                   | No                    |

|               |                                              | I3C Write/Read             | Final                   | Yes                   |

|               |                                              | I2C Write/Read             | Final                   | Yes                   |

| CertusPro-NX  | 25                                           | Dynamic Address Assignment | Final                   | Yes                   |

|               |                                              | IBI                        | Final                   | Yes                   |

|               |                                              | Hot-Join                   | Final                   | Yes                   |

|               |                                              | HDR-DDR                    | Final                   | Yes                   |

<sup>1.</sup> In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

| Device Family | System Clock<br>Frequency (MHz) <sup>1</sup> | Supported Feature          | Radiant Timing<br>Model | Hardware<br>Validated |

|---------------|----------------------------------------------|----------------------------|-------------------------|-----------------------|

|               |                                              | I3C Write/Read             | Final                   | Yes                   |

|               |                                              | I2C Write/Read             | Final                   | Yes                   |

| MachXO5-NX    | 25                                           | Dynamic Address Assignment | Final                   | Yes                   |

|               |                                              | IBI                        | Final                   | Yes                   |

|               |                                              | Hot-Join                   | Final                   | Yes                   |

|               |                                              | HDR-DDR                    | Final                   | Yes                   |

|               |                                              | I3C Write/Read             | Final                   | Yes                   |

|               |                                              | I2C Write/Read             | Final                   | Yes                   |

| Avant         | 25                                           | Dynamic Address Assignment | Preliminary             | Yes                   |

|               |                                              | IBI                        | Preliminary             | Yes                   |

|               |                                              | Hot-Join                   | Preliminary             | Yes                   |

|               |                                              | HDR-DDR                    | Preliminary             | Yes                   |

|               |                                              | I3C Write/Read             | Preliminary             | Yes                   |

|               |                                              | I2C Write/Read             | Preliminary             | Yes                   |

#### Note:

#### 1.4. Features

The maximum number of devices that an I3C bus supports depends on trace length, capacitive load per device, and the types of devices (I2C versus I3C) present on the bus, because these factors affect clock frequency requirements. The Lattice I3C Target IP supports the following features:

- Compatible with MIPI I3C Specification v1.1.1

- Two-wire serial interface up to 12.5 MHz using Push-Pull

- Legacy I2C device co-existence on the same bus (with some limitations)

- Dynamic Addressing with optional Static Addressing for I3C Target acting as I2C Target

- I2C -like SDR messaging

- HDR-DDR mode support

- In-Band Interrupt support

- Hot-Join support

- Asynchronous Time Stamping (Mode 0)

- Target Reset without additional wires

- Configurable receive and transmit FIFO depth and implementation

The Lattice I3C Target IP does not support the following features:

- HDR-TSL for Ternary Symbol Legacy-inclusive-Bus (I2C Devices allowed)

- HDR-TSP for Ternary Symbol for Pure Bus (no I2C Devices allowed)

- HDR-BT for Bulk Transport

- Virtual target

- Synchronous Timing and Asynchronous Time Stamping (Except Mode 0)

- Group Addressing

- Monitoring Device Early Termination

- D2D Tunneling

- Multi-Lane Data Transfer

# 1.5. Licensing and Ordering Information

The I3C Target IP is provided at no additional cost with the Lattice Radiant software.

<sup>1.</sup> This is the system clock frequency used during hardware validation. For the actual frequency supported by the IP, refer to Appendix A. Resource Utilization.

# 1.6. Hardware Support

Refer to the Example Design section for more information on the boards used.

## 1.7. Minimum Device Requirements

There is no limitation in device speed grade for I3C Target IP. See Appendix A. Resource Utilization for minimum required resources to instantiate this IP and maximum clock frequency supported.

## 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.8.2. Signal Names

- \_n are active low (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

- \_oe are output enable signals

- \_io are bidirectional signals

#### 1.8.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

# 2. Functional Description

#### 2.1. IP Architecture Overview

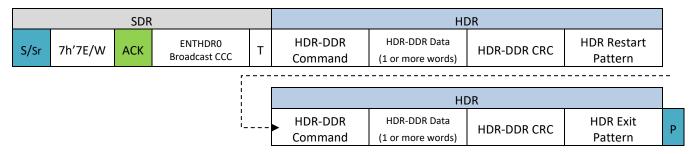

I3C Target IP supports several communication formats, all sharing a two-wire interface: SDA bidirectional data line and SCL bidirectional clock.

The Lattice I3C Target IP supports the following modes:

- SDR mode

- HDR-DDR mode

The I3C Target IP monitors the I3C bus for relevant I3C commands sent by the I3C Controller and responds accordingly. This includes commands that address all targets devices (Broadcast CCCs) and commands addressed specifically to that I3C Target device (Directed CCCs), provided these commands are supported by the I3C Target device.

Optionally, the I3C Target can perform the following operations:

- Request In-Band Interrupts

- Generate Hot-Join events

The I3C Target IP accepts commands from LMMI or from the optional APB/AHB-Lite interface. These commands are decoded into the following:

- Configurations for the I3C Target that may be requested by the Controller through CCC

- I3C signals that the Target device may transmit to the I3C bus

Furthermore, the I3C Target can operate in interrupt or polling mode. This means that you can choose to poll the I3C Target for a change in status at periodic intervals or wait to be interrupted by the I3C Target when data needs to be read or written.

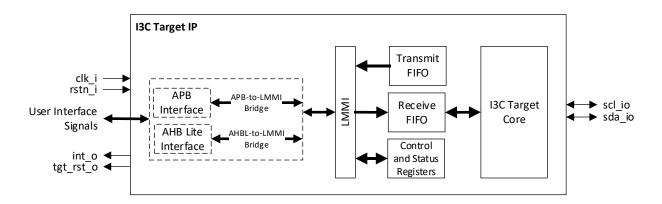

Figure 2.1 shows the functional diagram of the IP Core with Secondary Controller Capability.

Figure 2.1. I3C Target IP Core Block Diagram

#### **Clocking** 2.2.

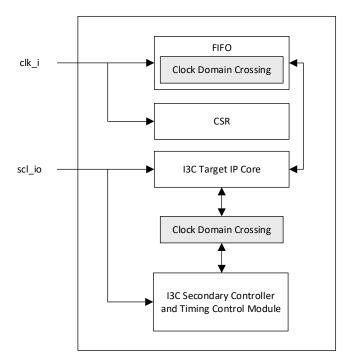

Figure 2.2. I3C Target IP Clock Domain Block Diagram

## 2.2.1. Clocking Overview

The I3C Target IP has the following clocks:

- clk i

- System clock Can be set in the range of 0.8 MHz 50 MHz. Used to clock internal FIFO, register access, and I3C Timing Control and Secondary Controller support logic.

- scl io Serial clock – Can support up to 12.5 MHz (based on I3C specification). Clock for I3C Target IP core.

#### 2.3. Reset

This IP has one asynchronous active low reset rst\_n\_i.

To ensure that reset has been properly propagated inside the IP, wait for at least 20 system clock (clk i) cycles after system reset (rst\_n\_i) de-assertion before doing any IP operation.

16

#### 2.4. User Interfaces

Table 2.1 shows the user interfaces and supported protocols. The memory-mapped interface of I3C Target IP Core is selected by the Interface attribute. It can be LMMI interface, AHB-Lite interface, or APB interface.

**Table 2.1. User Interfaces and Supported Protocols**

| User Interface                           | Supported Protocols | Description                                                                                                                                                                                                           |

|------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Selectable Memory-Mapped<br>Interface    | LMMI                | For LMMI interface, refer to the Lattice Memory Mapped Interface and Lattice Interrupt Interface (FPGA-UG-02039) document for information and timing diagram of the LMMI.                                             |

|                                          | AHB-Lite            | For AHB-Lite interface, refer to the AMBA 3 AHB-Lite Protocol v1.0  Specification for information and timing diagram of the APB interface.                                                                            |

|                                          | APB                 | For APB interface, refer to the AMBA 3 APB Protocol v1.0 Specification for information and timing diagram of the APB interface.                                                                                       |

| Device Receiver/Transmitter<br>Interface | 13C                 | The I3C Interface can complete the communication between the Lattice I3C Target IP core and external I3C controller and target devices. Refer to the MIPI I3C Specification for more information on the I3C protocol. |

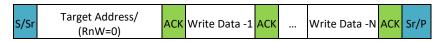

#### 2.5. I3C Transfers in SDR Mode

The following section describes the I3C Target response for different I3C transactions from the Controller in SDR mode.

#### 2.5.1. Broadcast CCC

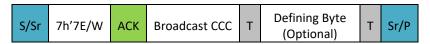

Figure 2.3. Broadcast CCC

When I3C Controller sends a broadcast CCC using the above format, the Target will ACK the I3C Broadcast Address 7'h7E/W. Depending on the received CCC and optional defining byte, the Target will process the command and respond accordingly.

#### 2.5.2. Direct CCC

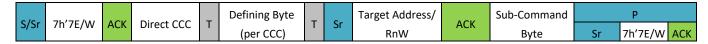

Figure 2.4. Direct CCC

When I3C Controller sends a direct CCC to the Target using the above format, the Target will ACK the I3C Broadcast Address 7'h7E/W. When the Target Address is transmitted in the bus at the address header, it will either:

- ACK if the CCC and the optional defining byte are both supported and the CCC T-bit is correct.

- NACK if CCC is not supported or CCC T-bit is incorrect.

Depending on the received CCC, the Target will process the command and respond accordingly.

#### 2.5.3. Private Write

Figure 2.5. I3C Private Write Initiated with START Condition

Figure 2.6. I3C Private Write Initiated with Repeated START Condition

When I3C Controller initiates a Private Write to Target, the Target will ACK if it receives the I3C Broadcast Address 7'h7E/W or its own Address followed by a Write bit.

Data written by the Controller will be stored in the Rx FIFO of Target. If enabled in Target, interrupt rxfifo\_not\_empty will be asserted to notify that Rx FIFO has data for reading.

#### 2.5.4. Private Read

Write data to the Tx FIFO of Target first before the I3C Controller initiates a Private Read.

Figure 2.7. I3C Private Read Initiated with START Condition

Figure 2.8. I3C Private Read Initiated with Repeated START Condition

When I3C Controller initiates a Private Read from Target, the Target will ACK if it receives the I3C Broadcast Address 7'h7E/W then its own Address followed by a Read bit. It will then proceed to transmit data that is stored in the Tx FIFO. Target will continue sending the Read data until Read is aborted by one of the following scenarios:

- Controller stops the Read by pulling SDA Low in the T-bit of data

- All content of Tx FIFO has been transmitted. Target will signal end of Message by pulling SDA Low while SCL is Low in the T-bit of the last data then releasing SDA when it sees SCL positive edge. The Controller shall then take over SDA and generate a STOP or a Repeated START.

If Tx FIFO is empty when Controller initiates Private Read, Target will respond depending on txfifo\_empty\_rd\_nak register:

- If txfifo\_empty\_rd\_nak is set to 0 (Default), Target will ACK its Address and return 0xFF Read Data then pull SDA Low at T-bit to signal end-of-message by default. If enabled, read\_txfifo\_empty interrupt will be set to notify the Private Read attempt by the Controller.

- If txfifo empty rd nak is set to 1, Target will NACK its Address.

#### 2.6. I2C Mode

When Target is not yet assigned a Dynamic Address, it may act as an I2C Target given that it is assigned a Static Address. To assign a Static Address to the I3C Target IP, check the Static Address Enable attribute and input a valid Static Address (must not use reserved I3C addresses).

If Target is already assigned a Dynamic Address, it will no longer ACK when its Static Address is transmitted in the I3C bus.

#### 2.6.1. I2C Write

In I2C Write, Target will ACK when its Static Address is transmitted in the I3C bus. The Controller then proceeds to send the 8-bit write data, then Target will pull down ACK at 9<sup>th</sup> bit to accept data.

Figure 2.9. I2C Write

#### 2.6.2. I2C Read

In I2C Read, Target will ACK when its Static Address is transmitted in the I3C bus. It will then proceed to transmit read data in Open Drain mode then Controller will either: (1) ACK and continue reading the data or (2) NACK to end reading of data.

Figure 2.10. I2C Read

If Tx FIFO is empty when Controller initiates I2C Read, Target will respond depending on the txfifo empty rd nak register.

- If txfifo\_empty\_rd\_nak is set to 0 (Default), Target will ACK its Address and return 0xFF Read Data then wait for Controller to end I2C read by sending NACK. If enabled, read\_txfifo\_empty interrupt will be set to notify the Private Read attempt by the Controller.

- If txfifo\_empty\_rd\_nak is set to 1, Target will NACK its Address.

# 2.7. Common Command Codes

Table 2.2 lists the supported CCC of this IP.

**Table 2.2. I3C Target IP Supported CCC**

| CCC  | Туре      | Required <sup>1</sup> | Command               |

|------|-----------|-----------------------|-----------------------|

| 0x00 | Broadcast | R                     | ENEC                  |

| 0x01 | Broadcast | R                     | DISEC                 |

| 0x06 | Broadcast | R                     | RSTDAA                |

| 0x07 | Broadcast | R                     | ENTDAA                |

| 0x09 | Broadcast | R                     | SETMWL                |

| 0x0A | Broadcast | R                     | SETMRL                |

| 0x2A | Broadcast | R                     | RSTACT                |

| 0x80 | Direct    | R                     | ENEC                  |

| 0x81 | Direct    | R                     | DISEC                 |

| 0x89 | Direct    | R                     | SETMWL                |

| 0x8A | Direct    | R                     | SETMRL                |

| 0x8B | Direct    | R                     | GETMWL                |

| 0x8C | Direct    | R                     | GETMRL                |

| 0x90 | Direct    | R                     | GETSTATUS             |

| 0x9A | Direct    | R                     | RSTACT                |

| 0x02 | Broadcast | С                     | ENTAS0                |

| 0x03 | Broadcast | 0                     | ENTAS1                |

| 0x04 | Broadcast | 0                     | ENTAS2                |

| 0x05 | Broadcast | 0                     | ENTAS3                |

| 0x28 | Broadcast | С                     | SETXTIME <sup>2</sup> |

| 0x29 | Broadcast | 0                     | SETAASA               |

| 0x82 | Direct    | С                     | ENTAS0                |

| 0x83 | Direct    | 0                     | ENTAS1                |

| 0x84 | Direct    | 0                     | ENTAS2                |

| 0x85 | Direct    | 0                     | ENTAS3                |

| 0x87 | Direct    | 0                     | SETDASA               |

| 0x88 | Direct    | С                     | SETNEWDA              |

| 0x8D | Direct    | С                     | GETPID                |

| 0x8E | Direct    | С                     | GETBCR                |

| 0x8F | Direct    | С                     | GETDCR                |

| 0x94 | Direct    | С                     | GETMXDS               |

| 0x95 | Direct    | С                     | GETCAPS               |

| 0x98 | Direct    | С                     | SETXTIME <sup>2</sup> |

| 0x99 | Direct    | С                     | GETXTIME              |

#### Notes:

- 1. R Required, O Optional, and C Conditional.

- 2. Supported Defining Bytes for SETXTIME CCC: 0xDF and 0xFF.

20

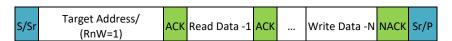

## 2.8. I3C Transfers in HDR-DDR Mode

An HDR-DDR Mode period in the I3C bus involves five steps:

- 1. The Controller sends a Broadcast Enter HDR-DDR Mode Broadcast CCC indicating which HDR-DDR Mode to enter.

- 2. The I3C bus switches from SDR Mode to the requested HDR-DDR Mode.

- 3. The Controller issues the first structured protocol per the HDR-DDR Mode framing, typically a Command or Header followed by optional Data sent by the Controller or the Target.

- 4. The Controller sends an HDR Restart Pattern or Exit Pattern.

- 5. If an HDR Restart Pattern is sent, then the Controller issues another structured protocol element for the New HDR-DDR Mode transfer. The Controller may repeat this process to remain in HDR-DDR Mode or send an HDR Exit Pattern to exit the HDR-DDR Mode.

- 6. If the Controller sends an HDR Exit Pattern, then it is always followed by an I3C STOP, which ends in the Bus Free Condition.

### 2.8.1. Typical HDR-DDR Mode Frame

Figure 2.11. Typical HDR-DDR Mode Frame

#### 2.8.2. HDR-DDR Write

|                                   | HDR-DDR Command                          |                                                     |     | HDR-DDR Write Data (N)              |                                    | HDR-DDR CRC          |                                      |

|-----------------------------------|------------------------------------------|-----------------------------------------------------|-----|-------------------------------------|------------------------------------|----------------------|--------------------------------------|

| Enter<br>HDR or<br>HDR<br>Restart | [15] <b>1'b0</b> (Write) [14:8] Reserved | [7:1] Target Address<br>[0] Parity Adj. (P0 = 1'b1) | ACK | [15:8] 1 <sup>st</sup><br>Data Byte | [7:0] 2 <sup>nd</sup><br>Data Byte | CRC5 for all<br>Data | HDR<br>Restart<br>or Exit<br>Pattern |

Figure 2.12. HDR-DDR Write

#### 2.8.3. HDR-DDR Read

|                                   | HDR-DDR Command                         |                                                     | HDR-DDR Command HDR- |                                     | HDR-DDR R                          | ead Data (N)         | HDR-DDR CRC                          |  |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------|----------------------|-------------------------------------|------------------------------------|----------------------|--------------------------------------|--|

| Enter<br>HDR or<br>HDR<br>Restart | [15] <b>1'b1</b> (Read) [14:8] Reserved | [7:1] Target Address<br>[0] Parity Adj. (P0 = 1'b1) | ACK                  | [15:8] 1 <sup>st</sup><br>Data Byte | [7:0] 2 <sup>nd</sup><br>Data Byte | CRC5 for all<br>Data | HDR<br>Restart<br>or Exit<br>Pattern |  |

Figure 2.13. HDR-DDR Read

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

## 2.8.4. HDR-DDR Broadcast CCC

|              | HDR-DDR CCC Indicator    |                             |                                 | HDR-DDR CC           | C Command            |

|--------------|--------------------------|-----------------------------|---------------------------------|----------------------|----------------------|

| Enter HDR or | [15] <b>1'b0</b> (Write) | [7:1] Broadcast Address     | ddress ACK [45.0] Broadcast CCC |                      | [7:0] Defining Byte, |

| HDR Restart  | [14:8] Reserved          | [0] Parity Adj. (P0 = 1'b1) | ACK                             | [15:8] Broadcast CCC | 0x0 if unused        |

| HDR-DDR CO           | CC Data (Optional)              | HDR-DDR CCC CRC  | HDR-DDR CCC End |

|----------------------|---------------------------------|------------------|-----------------|

| [15:8] 1st Data Byte | [7:0] 2 <sup>nd</sup> Data Byte | CRC for all Data | Procedure       |

Figure 2.14. HDR-DDR Broadcast CCC

#### 2.8.5. HDR-DDR Direct Set CCC

|                             | HDR-DDR CCC Indicator                    |                                                     |     | HDR-DDR CCC Command |                                       | HDR-DDR CCC<br>CRC     |

|-----------------------------|------------------------------------------|-----------------------------------------------------|-----|---------------------|---------------------------------------|------------------------|

| Enter HDR or<br>HDR Restart | [15] <b>1'b0</b> (Write) [14:8] Reserved | [7:1] Broadcast Address [0] Parity Adj. (P0 = 1'b1) | ACK | [15:8] Direct CCC   | [7:0] Defining Byte,<br>0x0 if unused | CRC for CCC<br>Command |

|                             |                                          |                                                     |     |                     |                                       | HDR-DDR CCC            |

|             | HDR-DDR CCC Selector                        |                                                  |     | HDR-DDR CCC Se                   | et Data (N times)               | HDR-DDR CCC<br>CRC  |

|-------------|---------------------------------------------|--------------------------------------------------|-----|----------------------------------|---------------------------------|---------------------|

| HDR Restart | [15] <b>1'b0</b> (Write)<br>[14:8] Reserved | [7:1] Target Address [0] Parity Adj. (P0 = 1'b1) | ACK | [15:8] 1 <sup>st</sup> Data Byte | [7:0] 2 <sup>nd</sup> Data Byte | CRC for all<br>Data |

HDR-DDR CCC End Procedure

Data

Figure 2.15. HDR-DDR Direct Set CCC

### 2.8.6. HDR-DDR Direct Get CCC

[14:8] Reserved

|                             | HDR-DDR CCC Indicator                    |                                                        |     | HDR-DDR CCC Command              |                                       | HDR-DDR CCC<br>CRC     |

|-----------------------------|------------------------------------------|--------------------------------------------------------|-----|----------------------------------|---------------------------------------|------------------------|

| Enter HDR or<br>HDR Restart | [15] <b>1'b0</b> (Write) [14:8] Reserved | [7:1] Broadcast Address<br>[0] Parity Adj. (P0 = 1'b1) | ACK | [15:8] Direct CCC                | [7:0] Defining Byte,<br>0x0 if unused | CRC for CCC<br>Command |

|                             | HDR-DDR CCC Selector                     |                                                        |     | HDR-DDR CCC G                    | et Data (N times)                     | HDR-DDR CCC<br>CRC     |

| HDR Restart                 | [15] <b>1'b1</b> (Read)                  | [7:1] Target Address                                   | ACK | [15:8] 1 <sup>st</sup> Data Byte | [7:0] 2 <sup>nd</sup> Data Byte       | CRC for all            |

| Target to Controller | HDR-DDR CCC   |

|----------------------|---------------|

| Handoff              | End Procedure |

Figure 2.16. HDR-DDR Direct Get CCC

[0] Parity Adj. (P0 = 1'b1)

#### 2.9. Hot-Join Mechanism

The I3C Target Device may issue a Hot-Join request to join the I3C bus after the bus is already configured. Target initiates Hot-Join Request by sending an IBI using the reserved address 7'h02 with Write bit after a START condition.

The Target may initiate Hot-Join by one of the following methods:

- Passive I3C Target may wait for a START condition transmitted in the I3C bus. It may then proceed to transmit the reserved address 7'h02 in the arbitrable address header.

- **Note**: I3C Target needs to know first if it is in an I3C bus before initiating Hot-Join passively. An I3C bus is determined by an SDR Frame with START followed by the Broadcast Address. See Errata 01 for MIPI I3C Basic Specification, Specification Version 1.1.1.

- Active If the I3C Target detects Bus Idle condition, it may generate a START by pulling the SDA line Low and waiting

for the I3C Controller to complete the start condition by pulling SCL low.

The Target will then proceed to send the reserved address 7'h02 in the arbitrable address header after the START condition.

#### 2.9.1. Generating a Hot-Join Request

The I3C Target IP supports Hot-Join when the Hot-Join Capable attribute is checked.

To initiate a Hot-Join request, confirm that Hot-Join is allowed by the Controller by reading the hj\_en\_ec register. If allowed (hj\_en\_ec is set to 1'b1), set the hj\_req register to 1'b1. I3C Target will attempt to transmit the Hot-Join request in the I3C bus by either active or passive method as described above. If the Target loses address arbitration, it will stop transmitting the Hot-Join address and wait for the next valid opportunity to retransmit the Hot-Join request depending on retry settings. When the Hot-Join request has been generated, hj\_req\_gen interrupt will be asserted.

If I3C Controller ACKs the request, I3C Target has successfully joined the I3C bus and hj\_done interrupt will be asserted to inform that Hot-Join was successful. The Target will then wait for Dynamic Address Assignment.

If the Hot-Join request is NACKed by I3C Controller, hj\_acnack interrupt will be asserted and I3C Target will then wait for the next valid condition to retry transmitting the Hot-Join request until the I3C Controller ACKs the request. If the Hot-Join request has been generated and NACKed by the Controller for hj\_ibi\_retry times, hj\_done and hj\_acknack interrupts will be asserted to inform that Hot-Join was not successful.

### 2.10. In-Band Interrupt

In-Band Interrupts may be issued by I3C Targets to signal pending action from the I3C Controller.

The I3C Target issues IBI by sending its own address in the Arbitrated Address Header with a Read bit after a START condition.

The Target may initiate IBI by one of the following methods:

- Passive I3C Target may wait for a START condition transmitted in the I3C bus. It may then proceed to transmit its own dynamic address in the arbitrable address header.

- Active If I3C bus Available condition is detected, I3C Target may generate a START by pulling the SDA line Low and

waiting for the I3C Controller to complete the start condition by pulling SCL low.

The Target will then proceed to transmit its address in the arbitrable address header after the START condition.

#### 2.10.1. Generating an In-band Interrupt

The I3C Target IP supports IBI when the IBI Capable attribute is checked.

To initiate an In-Band Interrupt, confirm that IBI is allowed by the Controller by reading the ibi\_en\_ec register. If allowed (ibi\_en\_ec is set to 1'b1), set the ibi\_req register to 1'b1. I3C Target will attempt to transmit its own Dynamic Address in the arbitrable Address Header after a START condition. If the Target loses address arbitration, it will stop sending the IBI and wait for the next valid opportunity to retry sending the IBI. If IBI has been successfully generated, ibi\_req\_gen interrupt will be asserted.

If IBI is ACKed by the Controller, I3C Controller shall read the payload following IBI depending on BCR[2] of I3C Target.

- If BCR[2] is set to 0: there is no data byte following the IBI. ibi done interrupt will be asserted.

- If BCR[2] is set to 1: the IBI has the following Mandatory Data Byte that shall be read by the Controller. The Target may also optionally send additional IBI data bytes (up to IBI Payload Size Limit by the Controller via the SETMRL CCC command). ibi\_done interrupt will be asserted when reading of the IBI payload is stopped either by the Target or the Controller.

If IBI is NACKed by the I3C Controller, ibi\_acknack interrupt will be asserted and I3C Target will then wait for the next valid condition to send the IBI until the I3C Controller ACKs the request. If IBI has been generated and NACKed by the Controller for hj ibi retry times, ibi done and ibi acknack interrupts will also be set to 1 to inform that IBI was not successful.

#### 2.10.2. Sending the IBI Payload

To send an IBI with mandatory data byte and optional additional payload (up to maximum IBI payload size), write the data bytes to Tx FIFO with MDB as the first data and the additional IBI payload as the succeeding data. When the IBI is generated by Target and ACKed by the Controller, the Target will proceed to send the MDB and the additional data bytes until the maximum IBI payload size.

When all IBI payload is transmitted, that is, maximum IBI payload size has been reached or Tx FIFO is empty, Target will end the transfer by pulling SDA Low at T-bit. ibi\_done interrupt will be asserted to notify that IBI is done, and all payload has been transmitted.

If the Controller chooses to end reading the additional IBI payload by pulling SDA Low during T-bit, ibi\_done and ibi\_payld\_terminated interrupts will be set to 1 to notify that IBI transfer is done but payload transfer is incomplete. When this interrupt is received, you may choose to reset the Tx FIFO by setting the txfifo\_rst register.

#### 2.10.3. Pending Read Notification

Pending Read Notification (MDB[7:5] = 3'b101) is supported by this IP.

If the I3C Controller accepts an IBI and reads the Pending Read Notification MDB from the Target, the Target considers Pending Read Notification as Active. Read Data associated with the MDB shall be available at the next Private Read.

For pending read notification, write the data bytes to the Tx FIFO in this order:

- 1. Pending Read Notification MDB

- 2. IBI Payload (equal to maximum IBI payload size)

- 3. Associated read data

Only one Pending Read Notification may be active at a time while the Target is waiting for the Controller to read data. This means that when a Pending Read Notification is active, the Target cannot send another IBI with MDB for Pending Read Notification.

#### 2.10.4. Limitation for IBI and Private Read

IBI Payload and read data are both stored in the Tx FIFO. If IBI Payload or Data for Private Read are written continuously to the Tx FIFO without being transmitted to the Controller (via IBI or Private Read), the intended data may not be sent correctly by the Target.

Ensure that all data corresponding to an intended IBI or Private Read has been transferred before initiating another IBI or Private Read. You may read the status registers ibi\_payld\_terminated (for IBI) and read\_aborted (for Private Read) to confirm if all contents of Tx FIFO have been transmitted. If the status registers are set, transfer of Tx FIFO contents is not completed. When this occurs, you have the option to reset the Tx FIFO before writing new data for the next IBI or Private Read to ensure correctness of data.

## 2.11. Target Reset

Target Reset Action is configured by the Controller via RSTACT CCC. This will be the action of Target when it receives the Target Reset Pattern following an RSTACT CCC in a single frame. Following are the supported Defining Bytes of this IP:

**Table 2.3. Target Reset**

| Defining Byte | Action                    | Description                                                                                                                             |

|---------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0x0           | No Action                 | No action                                                                                                                               |

| 0x1           | Reset I3C Peripheral only | Reset I3C states and FIFO. Equivalent to ip_core_rst soft reset                                                                         |

| 0x2           | Reset Whole Target        | Reset whole Target including DAA and previously configured settings via CCCs and register access. Equivalent to ip_main_rst soft reset. |

When the IP receives RSTACT CCC, it informs you by asserting rstact\_ccc\_rcvd interrupt. The configured reset action is stored in tgt\_rst\_act\_set register. Read this register to determine what action to do when the Target Reset Pattern is received. When Target detects the following Target Reset Pattern, it then asserts tgt\_rst\_ptrn\_rcvd interrupt. When you see this interruption, you may then perform the configured reset action or inaction. You may use the soft reset registers, or the system reset (for whole Target reset) to perform the configured reset action.

The behavior is different when Target receives Target Reset Pattern without RSTACT. When Target receives Target Reset Pattern without RSTACT for the first time, it automatically resets the I3C Peripheral. If this occurs a second time, tgt\_rst\_o output is asserted. This informs you to reset Whole Chip (Target Reset Escalation).

## 2.12. Secondary Controller Support

The I3C Target IP is instantiated when Secondary Controller feature is enabled in the I3C Controller IP. All the capabilities of the I3C Target will then be available to the Secondary Controller Capable device.

#### 2.12.1. Generating the Controller Role Request

To initiate a Controller Role request, confirm that Controller Role request is allowed by the Controller by reading the cr\_en\_ec register. If allowed (cr\_en\_ec is set to 1'b1), set the cr\_req register to 1'b1. I3C Target will attempt to transmit its own Dynamic Address in the arbitrable Address Header after a START condition. If Target loses address arbitration, it will stop sending the Controller Role request and wait for the next valid opportunity to retry sending the request. If the Controller Role request has been successfully generated, cr\_req\_gen interrupt will be asserted.

If the request is ACKed by the Controller, cr\_req\_done interrupt will be asserted.

If the request is NACKed by the I3C Controller, I3C Target will then wait for the next valid condition to send the request until the I3C Controller ACKs. If the Controller Role request has been generated and NACKed by the Controller for hj\_ibi\_retry times, cr\_req\_done and cr\_req\_acknack interrupts will also be set to 1 to inform that Controller Role request was not successful.

#### 2.12.2. CCC for Secondary Controller Support

Table 2.4 lists the additional CCCs supported when Secondary Controller feature is enabled.

**Table 2.4. CCCs for Secondary Controller Support**

| ССС  | Туре      | Command Name |

|------|-----------|--------------|

| 0x08 | Broadcast | DEFTGTS      |

| 0x91 | Direct    | GETACCCR     |

# 2.13. HDR-DDR Support

Table 2.5 lists CCCs supported by this IP in SDR mode and permitted in HDR-DDR mode, with notes and limitations.

Table 2.5. CCCs Supported in HDR-DDR Mode

| 0x00<br>0x01 | Broadcast<br>Broadcast | ENEC      |                                                                                                                                                                                                                                                     |     |

|--------------|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0x01         | Broadcast              |           | May not generally be useful in HDR-DDR Modes, as the Controller                                                                                                                                                                                     | Yes |

|              |                        | DISEC     | would need to exit HDR and return to SDR Mode for the Target to be able to raise any of the request types that are affected by these CCCs; see Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification.                                            | Yes |

| 0x02         | Broadcast              | ENTAS0    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x03         | Broadcast              | ENTAS1    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x04         | Broadcast              | ENTAS2    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x05         | Broadcast              | ENTAS3    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x08         | Broadcast              | DEFTGTS   | Not recommended for use in HDR-DDR Modes; generally only used for Secondary Controllers, to announce lists of known Targets, following changes to Target Dynamic Addresses or Hot-Join events, neither of which are permitted within HDR-DDR Modes. | No  |

| 0x09         | Broadcast              | SETMWL    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x0A         | Broadcast              | SETMRL    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x12         | Broadcast              | ENDXFER   | Not recommended for use in HDR-DDR Modes                                                                                                                                                                                                            | Yes |

| 0x28         | Broadcast              | SETXTIME  | No limitations                                                                                                                                                                                                                                      | Yes |

| 0x2A         | Broadcast              | RSTACT    | Not recommended for use in HDR-DDR Modes                                                                                                                                                                                                            | No  |

| 0x80         | Direct                 | ENEC      | May not generally be useful in HDR-DDR Modes, as the Controller                                                                                                                                                                                     | Yes |

| 0x81         | Direct                 | DISEC     | would need to exit HDR and return to SDR Mode for the Target to be able to raise any of the request types that are affected by these CCCs; see Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification.                                            | Yes |

| 0x82         | Direct                 | ENTAS0    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x83         | Direct                 | ENTAS1    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x84         | Direct                 | ENTAS2    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x85         | Direct                 | ENTAS3    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x89         | Direct                 | SETMWL    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x8A         | Direct                 | SETMRL    | See Section 5.2.1.2.4 of MIPI I3C Basic v1.1.1 specification                                                                                                                                                                                        | Yes |

| 0x8B         | Direct                 | GETMWL    | No limitations                                                                                                                                                                                                                                      | Yes |

| 0x8C         | Direct                 | GETMRL    | No limitations                                                                                                                                                                                                                                      | Yes |

| 0x8E         | Direct                 | GETBCR    | Not recommended for use in HDR-DDR Modes                                                                                                                                                                                                            | Yes |

| 0x8F         | Direct                 | GETDCR    | Not recommended for use in HDR-DDR Modes                                                                                                                                                                                                            | Yes |

| 0x90         | Direct                 | GETSTATUS | No limitations                                                                                                                                                                                                                                      | Yes |

| 0x92         | Direct                 | ENDXFER   | Not recommended for use in HDR-DDR Modes                                                                                                                                                                                                            | Yes |

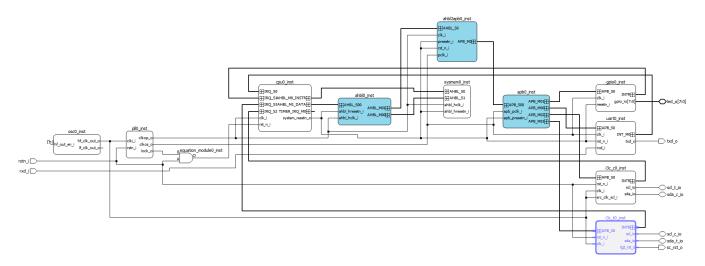

| 0x94         | Direct                 | GETMXDS   | No limitations                                                                                                                                                                                                                                      | Yes |