# **QuestaSim Lattice FPGA Edition Usage Guidelines and Tips**

# **Application Notes**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Abbreviations in This Document                                                   | 6  |

|----------------------------------------------------------------------------------|----|

| 1. Introduction                                                                  | 7  |

| 1.1. Purpose and Overview                                                        | 7  |

| 1.2. Audience                                                                    | 7  |

| 2. Overview of the Simulation Flow                                               |    |

| 2.1. General Simulation Flow                                                     | 8  |

| 2.2. Project vs Directory-Based Simulations                                      | 8  |

| 2.2.1. Advantages and Disadvantages for Each Flow                                | 8  |

| 2.2.2. Managing Libraries and Settings                                           |    |

| 2.3. Precompiled Device Libraries                                                |    |

| 2.4. Encrypted Files                                                             |    |

| 3. Recommended Simulation Flows                                                  |    |

| 3.1. Simulating a Project with QuestaSim User Interface                          |    |

| 3.1.1. Project-based Simulation Flow                                             |    |

| 3.1.2. Directory-based Simulation Flow                                           |    |

| 3.2. Simulating a Project with the Radiant or Diamond Software Simulation Wizard |    |

| 3.2.1. Initial Setup                                                             |    |

| 3.2.2. Simulation Flow 1 Using the QuestaSim User Interface                      |    |

| 3.2.3. Simulation Flow 2 Using the Radiant Software User Interface               |    |

| 3.3. Simulating a Project with Simulation Wizard and Custom Script               |    |

| 3.3.1. Simulation Flow Using the QuestaSim User Interface                        |    |

| 3.4. Simulating a Project with Simulation Script                                 |    |

| 3.4.1. Project-based Simulation Scripts                                          |    |

| · · · · · · · · · · · · · · · · · · ·                                            |    |

| 3.5. Simulating a Project with the Propel Software                               |    |

| 3.5.1. Initial Setup                                                             |    |

| 3.5.2. Simulation Flow Using the Propel Builder User Interface                   |    |

| 4. QuestaSim Software Usage Tips                                                 |    |

| 4.1. Tips for Script-Based Simulations                                           |    |

| 4.1.1. Do versus TCL Scripts                                                     |    |

| 4.1.2. Invoking Scripts                                                          |    |

| 4.1.3. Compiling Multiple Files                                                  |    |

| 4.2. Simulation Tips and Tricks                                                  |    |

| 4.2.1. Simulation Configurations                                                 |    |

| 4.2.2. Saving and Loading User Interface Layouts                                 |    |

| 4.2.3. Creating a Waveform Do Script                                             |    |

| 4.2.4. Creating and Using Custom Libraries                                       |    |

| 4.3. Simulating Different Process Stages                                         |    |

| 4.3.1. Generating Post-RTL Simulation Files                                      | 33 |

| 4.3.2. Using Post-RTL Simulation Netlists                                        | 34 |

| 4.3.3. Simulating Post-RTL with Timing                                           | 35 |

| 5. TCL Commands and Options                                                      | 37 |

| 5.1. Frequently Used TCL Commands and Options                                    | 37 |

| 5.1.1. add wave                                                                  | 37 |

| 5.1.2. cd                                                                        | 37 |

| 5.1.3. do                                                                        | 38 |

| 5.1.4. project                                                                   | 38 |

| 5.1.5. run                                                                       | 39 |

| 5.1.6. vcom                                                                      | 39 |

|                                                                                  |    |

| view                                  | 40                                                                                                                                                                                                                                                                                                             |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vlib                                  | 41                                                                                                                                                                                                                                                                                                             |

| vlog                                  | 41                                                                                                                                                                                                                                                                                                             |

| vmap                                  | 42                                                                                                                                                                                                                                                                                                             |

| vsim                                  | 43                                                                                                                                                                                                                                                                                                             |

| wave                                  | 44                                                                                                                                                                                                                                                                                                             |

| ther Useful TCL Commands and Options  | 44                                                                                                                                                                                                                                                                                                             |

| formatTime                            | 45                                                                                                                                                                                                                                                                                                             |

| layout load                           | 45                                                                                                                                                                                                                                                                                                             |

| onbreak                               | 45                                                                                                                                                                                                                                                                                                             |

| onelaberror                           | 45                                                                                                                                                                                                                                                                                                             |

| onerror                               | 46                                                                                                                                                                                                                                                                                                             |

| onfinish                              | 46                                                                                                                                                                                                                                                                                                             |

| precision                             | 46                                                                                                                                                                                                                                                                                                             |

| quietly                               | 47                                                                                                                                                                                                                                                                                                             |

| quit                                  | 47                                                                                                                                                                                                                                                                                                             |

| radix                                 | 47                                                                                                                                                                                                                                                                                                             |

| verror                                | 48                                                                                                                                                                                                                                                                                                             |

| where                                 | 48                                                                                                                                                                                                                                                                                                             |

| e Scripts                             | 49                                                                                                                                                                                                                                                                                                             |

| irectory-Based Simulation Script      | 49                                                                                                                                                                                                                                                                                                             |

| ost-MAP with Timing Simulation Script | 49                                                                                                                                                                                                                                                                                                             |

| /aveform Do Script                    | 50                                                                                                                                                                                                                                                                                                             |

| ompiling Files to a Custom Library    | 51                                                                                                                                                                                                                                                                                                             |

|                                       | 52                                                                                                                                                                                                                                                                                                             |

| pport Assistance                      | 53                                                                                                                                                                                                                                                                                                             |

| tory                                  |                                                                                                                                                                                                                                                                                                                |

|                                       | vlib vlog vmap vsim wave ther Useful TCL Commands and Options. formatTime layout load. onbreak. onelaberror. onerror onfinish precision quietly quit radix verror whereee Scripts irectory-Based Simulation Script ost-MAP with Timing Simulation Script /aveform Do Script ompiling Files to a Custom Library |

# **Figures**

| Figure 2.1. where TCL Command Output in QuestaSim Software Transcript View                            | 9  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2.2. Example of Session Key for a User Encrypted RTL File                                      | 11 |

| Figure 2.3. Public Key Example for Mentor from Radiant Software 3.2 key.txt File                      | 11 |

| Figure 2.4. Example of Additional IEEE Encrypted File Generated for Diamond IP in the Propel Software | 11 |

| Figure 3.1. Location of the New Project Option in the QuestaSim User Interface                        |    |

| Figure 3.2. Create a Project Window in the QuestaSim User Interface                                   | 13 |

| Figure 3.3. Add Item to Project Window from the QuestaSim User Interface                              | 13 |

| Figure 3.4. Initial Page of Simulation Wizard                                                         | 14 |

| Figure 3.5. Second Page of Simulation Wizard                                                          | 15 |

| Figure 3.6. Third Page of Simulation Wizard                                                           | 16 |

| Figure 3.7. Fourth Page of Simulation Wizard                                                          | 17 |

| Figure 3.8. Final Page of Simulation Wizard                                                           | 18 |

| Figure 3.9. Simulation Wizard Project File Location in the Radiant Software                           | 19 |

| Figure 3.10. Skip to End Button Location on the First Page of Simulation Wizard                       | 19 |

| Figure 3.11. Initialize Memory Setting Location for the System Memory IP, v1.1.2                      | 23 |

| Figure 4.1. Method for Invoking Scripts Using the QuestaSim User Interface                            | 24 |

| Figure 4.2. Adding a Simulation Configuration to a QuestaSim Project                                  | 26 |

| Figure 4.3. Simulation Configuration Setup Initial Page                                               | 27 |

| Figure 4.4. Simulation Configuration Added to Project                                                 | 28 |

| Figure 4.5. Location of the Save Layout As Option                                                     | 29 |

| Figure 4.6. Save Layout as Naming Option                                                              | 29 |

| Figure 4.7. Layout Setting in the QuestaSim User Interface                                            | 29 |

| Figure 4.8. QuestaSim Simulator Layout Configuration Window                                           | 30 |

| Figure 4.9. Save Waveform Display Format Window                                                       | 31 |

| Figure 4.10. Creating a Custom QuestaSim Library                                                      | 32 |

| Figure 4.11. Library Creation Window                                                                  | 32 |

| Figure 4.12. Example modelsim.ini Modification to Add Full Library PathPath                           | 33 |

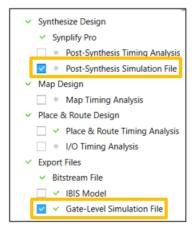

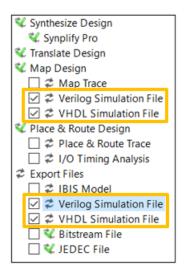

| Figure 4.13. Radiant Software Process Toolbar                                                         |    |

| Figure 4.14. Diamond Software Process Navigator Tab                                                   |    |

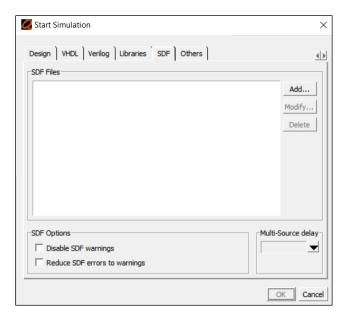

| Figure 4.15. SDF Tab View of the Start Simulation Window                                              |    |

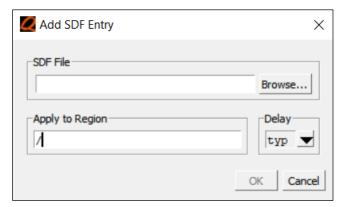

| Figure 4.16. Add SDF Entry Window                                                                     |    |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                      |

|--------------|---------------------------------|

| DUT          | Design Under Test               |

| HDL          | Hardware Description Language   |

| OEM          | Original Equipment Manufacturer |

| TCL          | Tool Command Language           |

# 1. Introduction

Siemens QuestaSim™ Latice FPGA Edition software is a multi-language simulation environment with support for languages such as VHDL, Verilog, System Verilog, and C. The version of QuestaSim software that is installed with the Lattice Diamond™, Lattice Radiant™, and Lattice Propel™ software is a licensed version that can be used to simulate projects as a standalone, or directly from each respective Lattice software tool.

# 1.1. Purpose and Overview

Project simulation plays a crucial role in the FPGA design process and is one of the main ways to ensure the functionality of a design is correct as it is being developed. Aside from RTL or functional simulations, both the Lattice Radiant and Lattice Diamond software also support various types of post-synthesis simulations.

The purpose of this document is to introduce the most important information that you need to know before using the QuestaSim software to simulate a project. Aside from that, this document also contains some recommended usage flows for simulating Lattice projects, as well as some additional usage guidelines and tips. The overall goal for the document is for its audience to know how to simulate their projects in the QuestaSim software, either using the user interface, TCL scripts, or any other methods directly supported in the Lattice Radiant, Lattice Diamond, and Lattice Propel software.

#### 1.2. Audience

The intended audience for this document includes design and verification engineers using Lattice FPGA devices. This document is specifically targeted to anyone using the Lattice Diamond, Lattice Radiant, or Lattice Propel software and does not require you to have any previous experience using simulation tools like QuestaSim or ModelSim. The technical guidelines for this document only assume that you have some expertise with digital design, FPGAs, and/or embedded systems.

# 2. Overview of the Simulation Flow

This section outlines important information about how projects can be simulated using the QuestaSim software. Aside from that, some basic information regarding Lattice FPGA device libraries and simulating encrypted files are also discussed in this section.

#### 2.1. General Simulation Flow

In general, the simulation flow is fairly simple and does not differ much from project to project. The high-level requirements to simulate a project includes the RTL, which consists of a design under test (DUT) and a testbench. Both the testbench and DUT are compiled to a library, usually called *work*, which is used to indicate the working files for the project.

The main difference between the two methods for simulation have to do with how files are organized. Directory-based simulations require more effort to set up, compile, and simulate, while project-based simulations are better integrated with the QuestaSim user interface and provide a few additional features. In general, a project-based approach is better when using the GUI for more detailed debugging while a directory-based approach works well in a script-based flow.

After the user RTL has been compiled to work, the next step is to invoke the QuestaSim VSIM simulator. This is done using the VSIM command, or by selecting **Simulate > Start Simulation** from the QuestaSim menu bar. The VSIM command requires user to specify the testbench you want to simulate. Alternatively, the QuestaSim software also provides a QRUN command, which bundles all this functionality into a single command as an alternative approach to using VLOG/VCOM, and VSIM. For more information on this command, refer to the Project vs Directory-Based Simulations section.

Additionally, libraries such as *work* or some of Lattice's pre-compiled device libraries are also often linked when invoking *VSIM*. This is because many Lattice IP contain device-specific primitives that are within these additional FPGA device libraries. One of the most commonly used libraries for both the Diamond, Radiant, and Propel software is *pmi\_work*, which contains modules for several Lattice primitives.

After VSIM has been invoked successfully, the final step is to advance the simulation for some amount of time. This is because using VSIM only invokes the QuestaSim software while the simulation remains at time = 0 until the simulation is advanced. Depending on the project, the next steps from this point onwards will vary depending on how you want to observe the simulation results. Generally, these next steps involve opening the waveform display and adding waveforms to observe various signals during the simulation.

# 2.2. Project vs Directory-Based Simulations

Ultimately, there are two main flows that you can follow to simulate your projects in the QuestaSim software, with the main difference being how files are organized for each method. For directory-based simulation flows, local directories are used to manage the user RTL files for a project. For project-based simulations, the QuestaSim user interface is used to manage the user RTL files for a simulation.

#### 2.2.1. Advantages and Disadvantages for Each Flow

In general, project-based simulations are better integrated with the QuestaSim software because everything can be managed within the QuestaSim user interface. The advantage of this is that this simulation flow requires little to no knowledge of QuestaSim TCL commands or options and enables you to easily manage and simulate your projects via the user interface. The main disadvantage of this flow is that not every TCL command has a corresponding setting in the QuestaSim user interface. What this means is that some functionality is lost when simulating with only the QuestaSim user interface. Similar to directory-based simulations, you can still automate project-based simulations using TCL scripts. However, this requires different TCL commands and is not as straightforward as it is for directory-based simulations.

The advantage of directory-based simulation flows is essentially the opposite of project-based simulations. Directory-based simulations can be more straightforward to set up but also require a better understanding of the various TCL commands used in the QuestaSim software and how they work. The QuestaSim user interface can also be used to simulate directory-based projects. However, this method is more complicated than it is for project-based simulations, as directory-based simulations require a few additional steps to run using only the QuestaSim user interface. Because of this,

TCL scripts are usually used to manage, compile, and simulate the files for directory-based simulations, although it is still possible to create a directory-based script.

#### 2.2.2. Managing Libraries and Settings

The first thing to know about the QuestaSim software settings is that they are stored in a primary file called *modelsim.ini*. Each of Lattice's software tools that has its own version of QuestaSim OEM software (Diamond, Radiant, and Propel software) will each come with their own *modelsim.ini* file, which contains the settings for the QuestaSim software version that is associated with that tool's installation. Each *modelsim.ini* may have different settings, and libraries linked so it is important that you are always certain you are using the correct version of the QuestaSim software, which corresponds to the tool version, and device family you are targeting in your simulations.

When setting or library changes are made within the QuestaSim user interface, those changes are saved to the active *modelsim.ini* file. Similarly, you can also directly modify these setting files to set some settings using a text editor. The second method for editing the setting file is useful and is worth checking out, as not all settings within the active *modelsim.ini* file can be modified directly from the QuestaSim user interface.

One of the main differences between project-based and directory-based simulation flows is the format for their respective *modelsim.ini* files. For directory-based simulations, *vmap -c* is often used to create a copy of the primary *modelsim.ini* file in the current directory. The reason for this is so any library or setting modifications made are specific for that simulation, and do not impact any other simulations. This local copy of the *modelsim.ini* file contains all the same settings as the active *modelsim.ini* file and references the library mappings from it as well.

For project-based simulations, the settings from the active modelsim.ini file are copied to the *<project name>.mpf* file that is generated when the project is created. The contents of this file are very similar to a local *modelsim.ini* file, and contain all the same settings and library mappings, and can also be modified in the same way by directly editing them with a text editor.

Depending on whether you are using a directory-based, or project-based simulation flow, the active *modelsim.ini* file may change. If a project is open, the *.mpf* file associated with that project will be the one that is active. If there is no project open, then the QuestaSim software defaults to the *modelsim.ini* file in the current directory. If there is no *modelsim.ini* file in the current directory, then the QuestaSim software resorts to the main *modelsim.ini* file as the active setting file.

Note: An easy way to tell the active setting file is to use the *where* TCL command as shown in Figure 2.1. Whichever file is listed here will always take precedence.

```

Questa Lattice OEM> where

# Current directory is: C:/Users

# Project is: C:/lscc/radiant/2024.lprod/questasim/win64/../modelsim.ini

#

```

Figure 2.1. where TCL Command Output in QuestaSim Software Transcript View

The following lists the order of precedence for an active *modelsim.ini* file:

- <project name>.mpf

- Local modelsim.ini

- Primary modelsim.ini

# 2.3. Precompiled Device Libraries

As mentioned before, each version of the QuestaSim software within each Lattice software tool installation will have its own unique library mappings within its respective main *modelsim.ini* file. These precompiled libraries are crucial, as they contain simulation models for many Lattice-specific primitives and hard IP blocks. Without these precompiled libraries, the QuestaSim software will be unable to resolve the references to various primitives within the design, which will cause simulations to error out.

The same is true for non-QuestaSim simulators, which also require these device specific Lattice simulation libraries as well to resolve undefined instances. Because of this, the *cmpl\_libs* TCL script needs to be used to compile Lattice's device

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

libraries for use in a separate third-party simulation tool since that tool does not have these crucial libraries installed by default. For more information about the cmpl\_libs TCL command, what simulators it supports library compilation for, and how it can be used to compile Lattice's device libraries for use in a third-party tool, refer to the Radiant or Diamond software web help pages.

One of the most commonly used types of precompiled libraries are device-specific libraries, like *lifcl* for CrossLink<sup>TM</sup>-NX device family, or *machxo3d* for the MachXO3D<sup>TM</sup> device family. These libraries are required when Lattice IP cores are involved in a design, as it contains the references to the primitives that are used within that IP. For the Diamond software, there are two types of device libraries: *Verilog* and *VHDL*. *Verilog* device libraries are denoted with the *ovi*\_ prefix (such as ovi\_machxo3d), while *VHDL* libraries do not have any prefix (such as machxo3d). Functionally, there are no difference between the two libraries so either can be used to the same effect.

Although the Radiant software also has *ovi* and *non-ovi* device libraries, both are compiled using Verilog source files. For example, this means there is no difference between libraries such as *lifcl* and *ovi\_lifcl* in the Radiant software other than their names. The Propel Builder software follows a similar naming format, but only contains the Verilog device libraries for both the Diamond and Radiant software.

Aside from device-specific libraries, two additional libraries you may need to use during your simulations are <code>pmi\_work</code> and <code>uaplatform</code>. Similar to the device libraries mentioned before, these two libraries also contain Lattice-specific primitives and parameterized modules. However, the main difference is that these primitives are common between multiple device families and are not necessarily unique to a single family. If a simulation is unable to resolve some instances despite linking the device libraries mentioned before, these two libraries are good options to try linking to resolve those missing instances.

For more information on how to create and compile to a custom library in the QuestaSim software, refer to the Compiling Files to a Custom Library section.

Each version of the QuestaSim software that is included with the Diamond, Radiant, or Propel software has an instance limit in place, which causes performance to degrade once the limit is passed. Because Lattice's precompiled device libraries are watermarked, the instances within these libraries do not count towards this instance limit. For this reason, it is important that you always use pre-compiled device libraries when applicable to prevent any performance degradation from happening.

# 2.4. Encrypted Files

This section describes how the QuestaSim software is used to simulate encrypted files, and not how to encrypt the user RTL itself. For more information about encrypting user RTL, refer to the Radiant software web help page for the *encrypt\_hdl* TCL command.

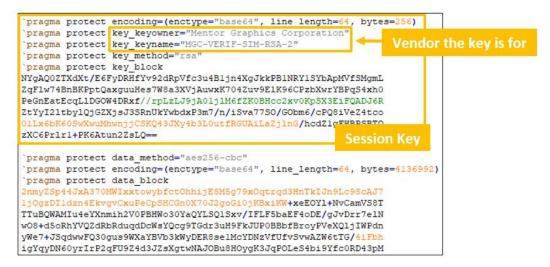

Two main keys are required for a third-party tool to be able to read user encrypted RTL. The first key is called the *session key*, and is located within the encrypted RTL file as shown in Figure 2.2. If a file was encrypted using the *encrypt\_hdl* command, there are several session keys in the encrypted RTL file. Each session key that is generated corresponds to a key that a different third-party vendor can use to decrypt the encrypted RTL.

Figure 2.2. Example of Session Key for a User Encrypted RTL File

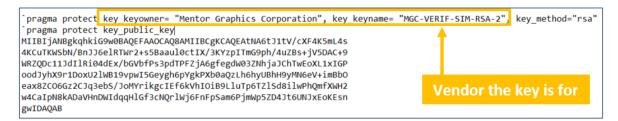

Aside from the session key, the other important key for third-party tools like the QuestaSim software to be able read encrypted RTL is the public key. Public keys are located in either the encrypted RTL itself, or in a separate key file. The public keys for Lattice's various supported third-party vendors can be found in a *key.txt* file within each tool's installation directory. Figure 2.3 shows the key owner and key name fields for each third-party vendor's public key that matches the session key. However, the key themselves are different.

Figure 2.3. Public Key Example for Mentor from Radiant Software 3.2 key.txt File

The following lists the *key.txt* file for various Lattice tools:

- Radiant software < Radiant software installation path > /ispfpga/data/key.txt

- Propel software— <Propel software installation path>/builder/rtf/ispfpga/data/key.txt

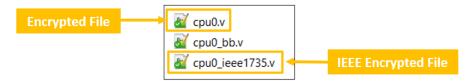

The Diamond software does not have a key.txt file like the Propel or Radiant software. This is because the Diamond software does not support IEEE1735 encryption. For encrypted IP that are generated in the Propel software, the default IEEE encryption is converted to blowfish encryption so the project can be synthesized in the Diamond software while still being encrypted.

A limitation of the Diamond software default encryption is that it is not supported by the QuestaSim software. Because of this, the Propel software generates an additional set of RTL files for each Diamond IP specifically for simulation. Figure 2.4 shows the IEEE encrypted version of the IP that is intended for simulation is denoted using \_ieee1735.

Figure 2.4. Example of Additional IEEE Encrypted File Generated for Diamond IP in the Propel Software

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

# 3. Recommended Simulation Flows

There are several different flows that you can follow to simulate a project. This section introduces some of the various simulation flows and explains the main advantages and disadvantages for each flow.

# 3.1. Simulating a Project with QuestaSim User Interface

For user interface-based simulations, there are two slightly different set of steps that are required to set up and simulate a project. This section covers the initial setup for project-based and directory-based simulations.

#### 3.1.1. Project-based Simulation Flow

To set up a simulation based on project flow, follow these steps:

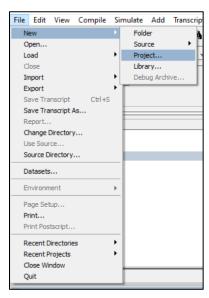

1. Go to File > New > Project to create a new project.

Figure 3.1. Location of the New Project Option in the QuestaSim User Interface

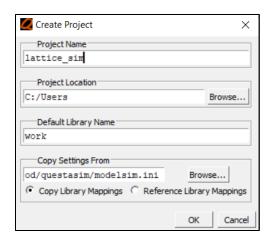

2. Define a Project Name and select a Project Location.

(Optional) Choose a different Default Library Name than work.

(Optional) Select a different modelsim.ini file to copy from using the Copy Settings From field.

- Copy Library Mappings Copies the library mappings from the selected *modelsim.ini* file directly into the cproject name>.mpf that is created.

- Reference Library Mappings References the library mappings from the selected modelsim.ini file. This causes

the library mappings to be synchronous so changes to the original modelsim.ini file library mappings also

affect the new project.

Figure 3.2. Create a Project Window in the QuestaSim User Interface

- 3. Click **OK** to create the new project.

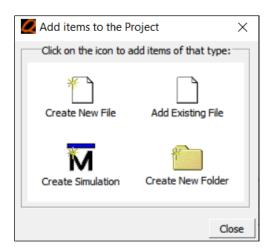

- 4. Add user RTL and testbenches to the project using the **Add Existing File** option from the popup window. If the popup disappears, right-click anywhere in the **Project Tab > Add to Project > Existing file**.

Figure 3.3. Add Item to Project Window from the QuestaSim User Interface

- 5. Compile the files in the project using the following options:

- Right-click anywhere in the Project tab, select Compile > Compile All or Compile Out-of-date.

- From the menu bar, select Compile > Compile All or Compile Out-of-date.

If compilation fails, try setting the Compilation Order so that files with dependencies are compiled after the files they are dependent on. Files at the top of the list are compiled first.

- 6. From the menu bar, select Simulate > Start Simulation.

- 7. In the **Design** tab, expand the work library using the plus icon next to its name. Select the testbench for the project. The **Design Unit(s)** field should update to reflect the testbench module selection.

- 8. In the **Libraries** tab, use the **-L** field and **Add**... button to specify which libraries to link. Typically, this is work, *<device library>*, pmi\_work, and uaplatform.

- 9. Click **OK** to begin simulation.

#### 3.1.2. Directory-based Simulation Flow

To set up based on directory, follow these steps:

- Switch to the directory where the work library is created in.

Select File > Change Directory ... or type cd < directory path > to switch to the correct directory.

- 2. From the menu bar, select **Simulate > Start Simulation**.

- In the **Design** tab, expand the work library using the plus icon next to its name.

Select the testbench for the project. The Design Unit(s) field should update to reflect the testbench module selection.

- 4. In the Libraries tab, use the -L field and Add... button to specify which libraries to link. Typically, this is work, <device library> and pmi work.

- 5. Click **OK** to begin simulation.

# 3.2. Simulating a Project with the Radiant or Diamond Software Simulation Wizard

This section describes the initial setup and setup for general simulations using the Simulation Wizard flow. Although the screen captures are from the Radiant software version of the Simulation Wizard, the Simulation Wizard for both the Diamond and Radiant software work the same and are very similar.

The main difference between the two software tools are the process stages that each Simulation Wizard can generate a .mdo simulation script for. Refer to the Simulating Different Process Stages section for information about simulating Diamond and Radiant software projects at various process stages.

#### 3.2.1. Initial Setup

To start initial setup, follow these steps:

- 1. Launch the Simulation Wizard through the following options:

- Select the Simulation Wizard icon

from the tool bar.

- Select **Tools > Simulation Wizard** from the menu bar.

- 2. Click **Next** when the Simulation Wizard opens.

The initial page describes how the Simulation Wizard works.

Figure 3.4. Initial Page of Simulation Wizard

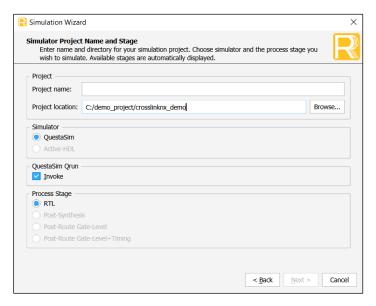

3. Select a name and location for the project using the **Project Name** and **Project Location** fields. A new directory called *<Project name>* is created wherever the selected project location is.

Figure 3.5. Second Page of Simulation Wizard

4. Select a **Process Stage** to simulate the project at.

These selections are only available after the required simulation files for each respective process stage have been generated.

- Click Next.

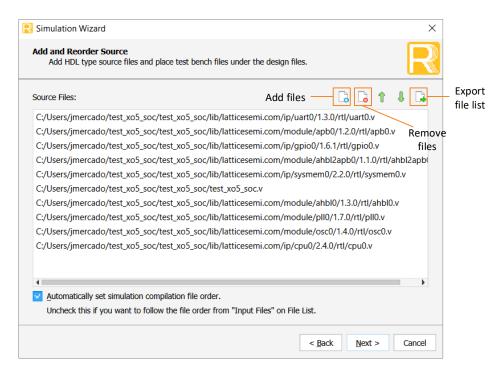

- 6. Select the files required for the simulation.

By default, all files in the project that are set for Synthesis and Simulation or Simulation are included.

Use the Add or Remove icons to add or remove files.

The Export source file list icon generates a file containing the full paths of the listed RTL files.

If **Automatically set simulation compilation file order** is enabled, the order of compilation is automatically determined by the Simulation Wizard. Otherwise, use the **Up** and **Down** green arrow icons to manually set the order of compilation. Files at the top are compiled first and should have no dependencies in the files compiled after them.

Figure 3.6. Third Page of Simulation Wizard

- 7. Click **Next** once all the required files for simulation have been added and the compilation order is correct.

- 8. Select the top testbench module from the **Simulation Top Module** drop-down list of options.

Simulation Wizard parses through all the included files to suggest valid simulation testbench modules.

Ensure the correct testbench module is selected before proceeding.

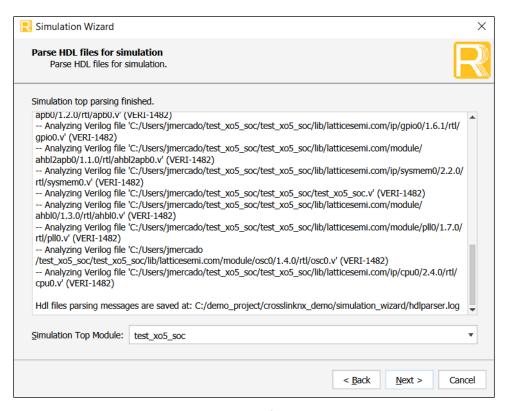

Figure 3.7. Fourth Page of Simulation Wizard

- 9. Click Next.

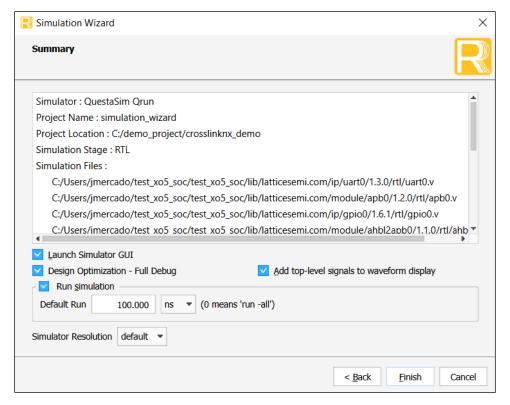

- 10. Review the settings in the top half of the final summary window to ensure the previous selections are correct.

Each option listed corresponds to a setting that was selected in the previous four pages of the Simulation Wizard.

Use the **Back** button to return to a previous page to correct any incorrect settings.

- 11. Select these last few settings according to how you want the script to be generated, and what to do afterwards:

- Run Simulator—Launches the QuestaSim software and invokes the generated .mdo script.

**Add top-level signals to waveform display**—Adds the *add wave* /\* command to the generated script, which means to add all the waveforms from the simulation testbench to the waveform display.

**Run Simulation**—Adds the *run* command to the final part of the simulation script and advancing it in time. Use the two boxes to the right to select how long to advance a simulation in time. The box on the left is the amount of time to advance, and the right box are the time units.

Figure 3.8. Final Page of Simulation Wizard

#### 12. Click Finish.

#### 3.2.2. Simulation Flow 1 Using the QuestaSim User Interface

The following lists two options to invoke the generated .mdo script:

- Type do <path of Simulation Wizard project>/<project name>.mdo in the Transcript window.

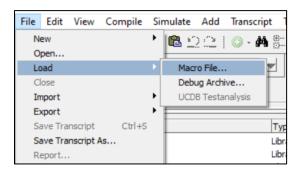

- Select File > Load > Macro File > and select the <project name>.mdo file located where the Simulation Wizard project

was generated. By default, only .do and .tcl files are displayed. Use the drop-down list on the bottom right to view all

files.

#### 3.2.3. Simulation Flow 2 Using the Radiant Software User Interface

To start initial setup, follow these steps:

- 1. Launch the Radiant software and open the project.

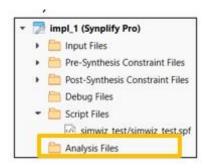

- 2. Double-click *<project name>.spf* from the list of files in the project under *Script Files*.

This is the Simulation Wizard project file and can be used to access existing projects.

Figure 3.9. Simulation Wizard Project File Location in the Radiant Software

Click Skip to End to skip to the final page of the Simulation Wizard window.

If you want to make changes to any selections for the Simulation Wizard project, click Next.

Figure 3.10. Skip to End Button Location on the First Page of Simulation Wizard

4. On the final page, ensure **Run Simulation** is enabled and then click **Finish**.

Doing this launches the QuestaSim software and invokes the generated simulation script automatically.

#### **Advantages**

- Requires little knowledge of QuestaSim TCL commands or TCL scripting.

- Can automatically generate a .mdo simulation script, invoke the QuestaSim software, and run a simulation.

#### Disadvantages

- Limited customization options via the user interface and generates a basic script.

- Generated simulation script is project-based and does not support directory-based script generation.

- Invoking the script through Simulation Wizard in the Diamond or Radiant software regenerates the script, making it difficult to keep changes that were made to the script itself.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

# 3.3. Simulating a Project with Simulation Wizard and Custom Script

For more information about the initial Simulation Wizard project setup, refer to the **Error! Reference source not found.** section. The initial flow is the same and only requires the Simulation Wizard to generate a .mdo as a starting point.

#### 3.3.1. Simulation Flow Using the QuestaSim User Interface

- 1. Launch the QuestaSim software.

- 2. The following lists the options to invoke the generated .mdo script:

Type do <path of Simulation Wizard project>/<project name>.mdo in the Transcript window.

Select **File > Load > Macro File** ... > and select the *<project name>.mdo* file located where the Simulation Wizard project was generated. By default, only .do and .tcl files are displayed. Use the dropdown on the bottom right to view all files.

Refer to the Invoking Scripts section for alternate methods of invoking simulation scripts.

#### **Advantages**

- Easily generate a simulation script as a starting point.

- Unlimited customizability with the baseline script.

#### Disadvantages

- Requires knowledge of QuestaSim TCL commands and TCL scripting basics.

- Generated script is project-based so changing it to directory-based requires additional effort.

# 3.4. Simulating a Project with Simulation Script

Depending on whether you are using a project-based or directory-based simulation approach, the commands that you use to simulate the project using scripts will vary. In this section, you will review the general structure for each type of script and the main considerations you must make to determine what options you can use with each command. For additional information about the most commonly used options for each of these commands, refer to the Error! Reference source not found. section. For more information about additional TCL commands, refer to the Other Useful TCL Commands and Options section, or the QuestaSim Command Reference Manual. For script examples, check out the Directory-Based Simulation Script section and the Post-MAP with Timing Simulation Script section.

#### 3.4.1. Project-based Simulation Scripts

The main TCL commands used for project-based simulation scripts are *project*, *vlog*, *vcom*, *vsim*, *view wave*, *add wave*, and *run*. Similar to any other simulation flow, project-based simulations can be broken down into four main parts:

Setting up a work library.

Compiling files to work.

Running the simulation.

Interpreting the results.

#### 3.4.1.1. Project-based Script Commands

The following is the list of project-based script commands:

- Setting up a work library:

- project new

- project open

- project addfile

- Compiling files:

- project compileall

- project compileoutofdate

- vlog

- vcom

- Running the simulation:

- vsim

- run

- Viewing results:

- view wave

- add wave

For project-based simulations, a work library is automatically created when a new project is created so only the *project new* TCL command is required to create a work library. After a project is created, it can be opened using the *project open* TCL command to avoid creating new projects each time a script is invoked.

One key difference for project-based simulations is that the *project addfile* command must be used to add files to the project. The advantage of this is that after the files have been added to a project, the *project compileall*, or *project compileoutofdate* commands can be used to automatically compile the files in the project without having to add separate compilation commands for each file. Aside from those two methods for compiling files, another way to compile files to work is to use the *vcom* or *vlog* TCL commands, depending on the language of the file you want to compile.

When all the design and testbench modules are compiled to work, the final step of the simulation flow is to run the simulation and view the results. For project-based simulation scripts, the *vsim* command is used to invoke the QuestaSim software. To view the results of the simulation graphically, use the *view wave* command to open QuestaSim waveform display window, and the *add wave* command to add the signals that you want to track to it. Lastly, the *run* command should be used to advance the simulation forward in time.

Refer to the Post-MAP with Timing Simulation Script section for an example simulation script that uses a project-based approach.

#### 3.4.2. Directory-based Simulation Scripts

The main TCL commands used for directory-based simulation scripts are *vlib*, *vmap*, *vlog*, *vcom*, *vsim*, *view wave*, *add wave*, and *run*. Similar to any other simulation flow, directory-based simulations can be broken down into four main parts: setting up a work library, compiling files to work, running the simulation, and interpreting results.

#### 3.4.2.1. Directory-based Script Commands

The following is the list of directory-based script commands:

- Setting up a work library:

- vlib

- vmap

- Compiling files:

- vlog

- vcom

- Running the simulation:

- vsim

- run

- Viewing results:

- view wave

- add wave

The main difference between directory-based, and project-based simulation scripts are the commands used to create a work library and compile files to it. Since the *project* command can only be used for project-based simulation scripts, the *vlib* command must instead be used to create a work library.

Aside from that, another frequently used command is *vmap*, which is used to map the logical library created by *vlib* to a physical directory. If a library is not mapped using *vmap*, its library mapping in the active *modelsim.ini* file uses a relative path instead of an absolute one. The disadvantage of using a relative path is that the QuestaSim software is not able to locate that library if you are in a different directory.

After the work library is correctly set up, the next few commands you must use for directory-based simulation scripts are *vlog* and *vcom*, which are used to compile Verilog or VHDL files to the work library. For directory-based simulation scripts, it is up to you to manage which files are compiled and when. Because of this, it is important to always keep track of the files that are required for the simulations.

Finally, after all the design and testbench modules are compiled to work, the last step of the simulation flow is to run the simulation and view the results. The commands used in this step are exactly the same as for project-based simulation scripts. These commands are *vsim*, which is used to invoke the QuestaSim software, *view wave* which opens the QuestaSim waveform display window, and *add wave* which adds the signals that user wants to track. Lastly, the *run* command is used to advance the simulation forward in time since invoking the QuestaSim software with *vsim* keeps the time at t=0.

Refer to the Directory-Based Simulation Script section for an example simulation script that uses a directory-based approach.

#### 3.4.2.2. Simulation Flow

- 1. Launch the QuestaSim software.

- 2. Invoke the simulation script.

Type *do <script location>* in the Transcript window or select **File > Load > Macro File >** select the <script location>. Refer to the Invoking Scripts section for alternate methods of invoking simulation scripts.

#### **Advantages**

- Unlimited customizability.

- Can use project-based or directory-based simulation flows.

#### **Disadvantages**

Requires knowledge of QuestaSim TCL commands and TCL scripting basics.

# 3.5. Simulating a Project with the Propel Software

#### 3.5.1. Initial Setup

To start initial setup, follow these steps:

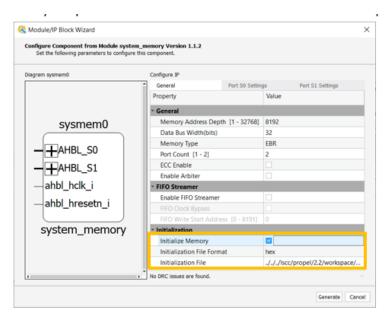

- 1. Edit the system memory component and initialize it with the .mem file from the Propel SDK C project.

- 2. Regenerate the SoC project using the **Generate** icon 4 from the toolbar.

- 3. Switch to the verification project using the **Switch Verification and Design** icon **I** from the toolbar.

- 4. Add, configure, and connect verification IP.

- The exact setup for this step varies from project to project.

- 5. Generate simulation environment using the **Generate** icon from the toolbar.

Doing this generates several additional files and folders for the simulation environment in *the <Builder project location>/verification/sim directory*:

flist.f - File list that contains the paths for all RTL files in the simulation environment.

<project name>\_v.sv — Basic simulation testbench to add stimulus to the SoC project. Generated according to the IP and connections in the Verification project schematic setup.

**msim.do** – Simulation do script that compiles all RTL for the SoC and verification project, invokes the QuestaSim software, and advances the simulation.

wave.do – Waveform do script that adds all signals from components in the SoC project.

work – Location of the work library generated by the simulation script.

6. Edit the generated testbench and simulation script.

msim.do, wave.do, and croject name>\_v.sv are good candidates to edit and add additional functionality to the simulation environment.

Figure 3.11. Initialize Memory Setting Location for the System Memory IP, v1.1.2

- 7. Launch the QuestaSim software using the **Launch Simulation** icon from the toolbar.

This launches the Propel software version of the QuestaSim software and invokes the generated simulation .do script.

- 8. Avoid regenerating the verification project to prevent files from being overwritten from step 4. Only regenerate to add verification IP or make changes to the verification project setup. Modifying the DUT does not require simulation environment regeneration. Because the DUT is instantiated in the testbench, any changes will synchronize due to the simulation script recompiling each file.

#### 3.5.2. Simulation Flow Using the QuestaSim User Interface

1. Launch the QuestaSim software from the Propel Builder.

This step is important so that the correct libraries are mapped.

- 2. Invoke the generated .mdo script through either of these methods:

- Type do <script location> in the Transcript window.

- Select File > Load > Macro File ... > select the <script location>.

Refer to the Invoking Scripts section for alternate methods of invoking simulation scripts.

#### 3.5.3. Simulation Flow Using the Propel Builder User Interface

- 1. Launch the Propel Builder and open the Verification project.

- 2. Select the **Launch Simulation** icon 📮 from the toolbar.

Doing this launches the Propel software version of the QuestaSim software and invokes the generated simulation .do script. Avoid regenerating the simulation environment beforehand if changes were made to the simulation script or testbench to prevent those files from being overwritten.

#### **Advantages**

- Requires little-to-no knowledge of TCL commands or scripting.

- Generates a basic simulation environment for you to perform a behavioral simulation for your Soc.

#### **Disadvantages**

- Only supports RTL simulation.

- No support for VHDL or mixed-language projects without editing the generated simulation script.

# 4. QuestaSim Software Usage Tips

This section describes the various tips and suggestions to simplify and enhance the usage of the QuestaSim software for simulations.

# 4.1. Tips for Script-Based Simulations

#### 4.1.1. Do versus TCL Scripts

The two main types of scripts that are used in the QuestaSim software are do (.do) and TCL (.tcl) scripts. Functionally, both script types are similar to each other and execute commands in a sequential order. One of the main differences between do and TCL scripts is that do scripts can use a few additional commands such as ONBREAK, ONELABERROR, ONERROR, and ONFINISH, which are useful for runtime condition handling and do not execute sequentially.

For example, placing ONERROR {resume;} at the top of a simulation script causes it to resume execution when it encounters an error, regardless of when or where the error is encountered. For more information and examples for these commands, refer to the onbreak, onelaberror, onerror, and onfinish sections.

#### 4.1.2. Invoking Scripts

The two main ways to invoke a script in the QuestaSim software are using either the *do* or *source* commands. Typically, the *do* command is used to invoke do scripts, while the *source* command is used to invoke TCL scripts. However, either can be used interchangeably in the QuestaSim software. This is because do is a superset of source, meaning there is no functional difference between using do or source to invoke a TCL script. One thing to consider is whether the script has any do specific commands like *onbreak* or *onerror*. For scripts containing these commands, the *do* command must be used.

As mentioned before, either the *do* or *source* commands can be used to invoke a script in the QuestaSim software. To invoke a script, simply type either *do* or *source* in the QuestaSim transcript area, followed by the location of the script you want to invoke. If the script is in the current directory, you can simply type the name of the script to invoke it. Similarly, a script can invoke another script using either of these commands.

Figure 4.1. Method for Invoking Scripts Using the QuestaSim User Interface

Aside from that, another way to invoke a script is to select **File > Load > Macro File** from the QuestaSim software menu bar as shown in **Figure 4.1**. If you are unable to select the macro file, try clicking the transcript area first. After **Macro File** has been selected, a new file explorer window opens and you can select the script to invoke. By default, this window only display .do and .tcl files so you must use the drop-down list at the bottom right of the window to select a different file type if the script uses some other extension. After you have located the script to invoke, select and then click the **Open** button to invoke it in the QuestaSim software. This method is the same as typing do <script name and location in the QuestaSim software transcript area.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

#### 4.1.3. Compiling Multiple Files

Depending on the language of the files you want to compile, there are three main ways to compile multiple files to a QuestaSim library. The *VCOM* command is used to compile VHDL modules and has a -f method, which can be used to compile multiple files from a master file list.

The VLOG command, which is used to compile Verilog and System Verilog files, also has a -f method as well as a +incdir+ method, and a -y method for compiling multiple files. The main limitation for these methods of compilation is that neither VCOM or VLOG support mixed language compilation. This means that you cannot compile VHDL and Verilog files with the same VCOM or VLOG commands and you must compile them separately.

The important thing to know about compiling multiple files with single TCL commands is that each module is treated as its own independent design unit. This means that using any method for compiling multiple files is functionally the same as typing multiple VLOG or VCOM to compile each individual file. Aside from that, the VLOG command also has a -mfcu option, which can be used to change this compilation behavior so that all compiled files are treated as a single design unit.

#### 4.1.3.1. -f Compilation Method

Requirements: Separate file list file with full or relative paths to additional files to compile.

Usage: vlog -work <library> -f <file list>

#### **Advantages**

- Command is simple to use and understand.

- Can be used by both VLOG or VCOM.

#### **Disadvantages**

- · Requires an additional file list file.

- Compiles all files in the file list, regardless of whether they are required or not.

#### 4.1.3.2. +incdir+ Compilation Method

**Requirements:** Include for additional files to compile in the top file being compiled first.

Usage: vlog +incdir+<search path> -work brary> <top file>

#### **Advantages**

Easiest command to set up if all `include RTL are in the same few directories.

#### Disadvantages:

- Cannot compile VHDL files that are include.

- Requires additional +incdir+ to search for files located in a different directory.

#### 4.1.3.3. -y Compilation Method

#### Requirements

- Top module with missing design units.

- -y option for various locations to search for design units to compile.

- +libext+ option to specify the file extensions to search for with the -y option.

Usage: vlog -work <library> <top file> -y <file search path> +libext+<file extension>

#### **Advantage**

- Can easily resolve missing instances to compile necessary files.

- Easy to manage which files to compile after the initial setup.

- Only compiles files that are necessary.

#### Disadvantage

- Complicated initial setup requires specific directory and file structure.

- Cannot compile VHDL files.

# 4.2. Simulation Tips and Tricks

This section introduces the various quality-of-life tips to improve the usage of the QuestaSim software. These tips can be used to simplify various portions of the simulation process. All these tips can be used interchangeably and are not mutually exclusive with each other. The only exception is for Simulation Configurations, which can only be used for project-based simulations and does not have an equivalent mechanic for directory-based simulations.

#### 4.2.1. Simulation Configurations

A simulation configuration is an easy way for project-based simulations to reinvoke the QuestaSim VSIM simulator with some specific settings. Functionally, using a simulation configuration is the same as typing a *VSIM* command to the QuestaSim transcript. The advantage of simulation configurations is that after they are set up, you only need to double click the configuration in their project tab to reinvoke the QuestaSim software with those specific settings.

This method is useful for projects with multiple testbenches or sets of options used to simulate a design in different ways. In situations like this, you can use multiple simulation configurations to easily reinvoke the QuestaSim software with a different set of VSIM command options to change the way the project is simulated.

#### 4.2.1.1. Creating a Simulation Configuration

To create a simulation configuration, follow these steps:

Select Project > Add to Project > Simulation Configuration. You can also right-click on the Project tab, select Add to Project > Simulation Configuration.

Figure 4.2. Adding a Simulation Configuration to a QuestaSim Project

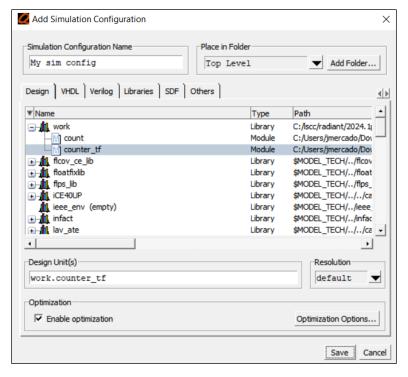

Figure 4.3. Simulation Configuration Setup Initial Page

- 2. Define a Simulation Configuration Name.

- 3. Select the folder to place the simulation configuration in using the **Place in Folder** drop-down option. By default, the configuration is added to the top-level project folder.

- 4. Select a top module to simulate from the **Design** tab.

- Select the dropdown next to **Work**, then select the module name corresponding to the testbench.

- The **Design Unit(s)** field should update to reflect the testbench selection.

- 5. Select which libraries to link for missing design instances in the **Libraries** tab.

- 6. Select settings in the VHDL, Verilog, SDF, or Others tabs according to the projects simulation requirements.

- 7. Click **Save** to add the configuration to the project.

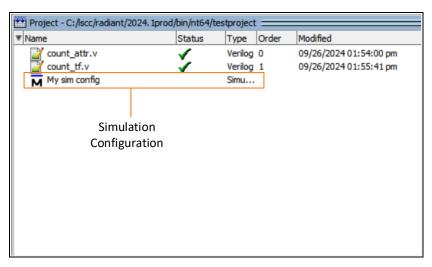

- The simulation configuration is visible in the **Projects** tab as shown in Figure 4.4.

Figure 4.4. Simulation Configuration Added to Project

#### 4.2.1.2. Launching a Simulation Configuration

Once a simulation configuration has been added to a QuestaSim project, it can be easily executed to reinvoke the QuestaSim VSIM simulator with the specified simulation settings. To invoke the QuestaSim software using a simulation configuration, double-click the name of the configuration from the **Projects** tab as shown in Figure 4.4.

#### 4.2.2. Saving and Loading User Interface Layouts

A useful aspect of the QuestaSim software is its user interface layout feature, which can be used to alternate between various user interface configurations. The user interface layout feature is used to create multiple different user interface layouts depending on which window you want to see, how you want them positioned, how they should be sized, and more.

The QuestaSim software comes with a few different user interface layouts by default, such as *NoDesign* and *Simulate*. These default layouts are used by the QuestaSim software during various parts of the QuestaSim software usage to automatically update the user interface layout and appearance. For example, when the VSIM simulator is invoked, the *Simulate* layout is loaded, which opens the waveform window as well as a few other debug views.

#### 4.2.2.1. Creating a Layout

Creating a user interface layout is simple. The first step in doing so is to modify the existing user interface layout and configuration according to the preference. This step does not require any active simulation to be running to include debugging views like the objects or waveform windows. Any layouts that are created are not project specific, and can be used regardless of the version of the QuestaSim software that you are using or the project that you are simulating.

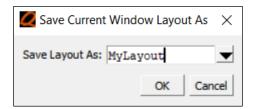

Figure 4.5. Location of the Save Layout As Option

**Note**: The **Delete** option is used to delete a custom user interface layout.

When you are satisfied with the configuration of the new user interface layout, select Layout from the QuestaSim menu bar, and then Save Layout As to create the new layout. From the popup window that appears, define a name for the new layout using the Save Layout As field. If an existing layout is selected instead of a new name, the existing layout is overwritten with the active layout settings.

Figure 4.6. Save Layout as Naming Option

#### 4.2.2.2. Loading a Layout

FPGA-AN-02053-1.1

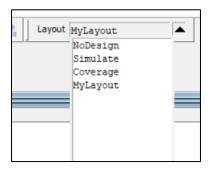

Depending on the intentions for the custom layout that was created, there are a few different ways to load a layout in the QuestaSim software. The first and most simple way to load a custom layout involves the QuestaSim user interface. To select a different layout to load, select the arrow next to the Layout option to expand the list of layouts to select from. From the drop-down list of layouts that appears, select the layout you want to load.

Figure 4.7. Layout Setting in the QuestaSim User Interface

Similarly, another way to load a user interface layout in the QuestaSim simulator involves the Layout tab drop-down list from the QuestaSim menu bar as shown in Figure 4.5. To load a different user interface layout this way, select the layout that you want to load from the list of layouts that appear at the bottom of the drop-down list.

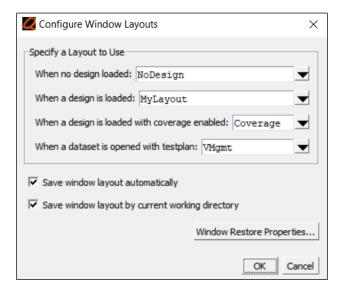

Aside from that, another way to select which layout to load is to set the default layout that the QuestaSim software automatically loads. To do this, select Layout > Configure from the QuestaSim menu bar. As shown in Figure 4.8, doing this opens the Configure Window Layouts window. Within this window, select a new layout to load automatically using the When no design loaded and When a design is loaded fields. The when no design is loaded selection is active whenever the QuestaSim software is opened, and the when design is loaded option only activates when the VSIM simulator is invoked.

Figure 4.8. QuestaSim Simulator Layout Configuration Window

The advantage of this method for selecting a QuestaSim layout is that the QuestaSim software automatically switches between these layouts as you simulate the project. The drawback of this method is that there are only two stages that can be set, which are when a design is loaded and when a design is not yet loaded.

Aside from the methods mentioned, one last way to load layouts involves the **layout load** TCL command. As the name implies, this TCL command can be used in scripts to automatically load a specific user interface layout during a scripts execution. For more information about this command, refer to the **layout load** section.

#### 4.2.3. Creating a Waveform Do Script

The Waveform scripts are a useful way to load a specific waveform configuration with signals and settings without having to manually add or modify any signals. An example waveform do script is shown in the Post-MAP with Timing Simulation Script section.

Typically, there are two main commands used in a waveform do script. The first command is *add wave*, which is used to add signals to the waveform display. This command has several additional options, which correspond to various settings for that signal. For more information about the *add wave* TCL command, refer to the <u>add wave</u> section.

Aside from that, another command that is typically used with waveform do scripts is *onerror*. Adding *onerror* {resume} to the top of user waveform do script allows the script to continue executing if it encounters an error. This is particularly useful for designs that are a work in progress and are frequently changing. The reason for this is because the *onerror* command allows the script to continue running if there are some signals that have been renamed or removed from the design. For more information about the *onerror* TCL command, refer to the *onerror* section.

#### 4.2.3.1. Saving a Waveform Format as a Script

A useful feature of the QuestaSim software is that its waveform display can be used to automatically generate a waveform do script. Depending on the modifications that were made to the waveform display, a do script containing the equivalent add wave TCL commands are generated. This do script can be invoked to repopulate a waveform display with the exact same settings as before.

#### 4.2.3.2. Saving a Waveform Configuration

To save a waveform configuration, follow these steps:

- 1. Configure the waveform as shown in Figure 4.9.

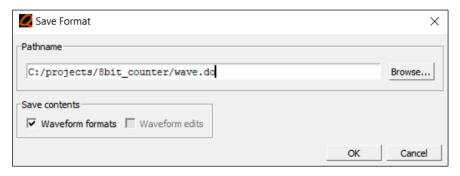

- 2. Select File > Save Format from the menu bar.

**CTRL + S** is another way to save the waveform configuration.

Figure 4.9. Save Waveform Display Format Window

- Define a name and location to save the waveform do script.

By default, the script is called wave.do and saved to the current QuestaSim directory.

- Enable Waveform formats.

This setting saves all the changes that were made to the waveform display to a script.

- 5 Click OK

After the waveform format is saved as a script, it can easily be invoked like any other script in the QuestaSim software. The only requirement is that the waveform window is already open. A useful way to invoke this script from a separate script is using the do *TCL* command, or the -do *VSIM* option.

#### 4.2.4. Creating and Using Custom Libraries

Custom libraries are a useful method for storing design or verification modules that are commonly used in other testbenches or designs. Custom libraries are particularly useful for modules that do not change frequently, as you can compile that file to a custom library knowing that you do not need to recompile it like other design or testbench files associated with the project.

There are two main ways to create a custom library. In this section, you focus on how to do so using the QuestaSim user interface. For more information on creating a custom library using TCL scripts, refer to the example script in the Compiling Files to a Custom Library section.

#### 4.2.4.1. Creating a Custom Library

To create a custom library, follow these steps:

- Switch to the directory you want to create the library in.

Use the CD TCL command, or select File > Change Directory from the menu bar.

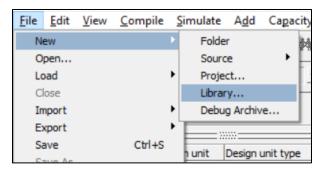

- Select File > New > Library from the menu bar.

Figure 4.10. Creating a Custom QuestaSim Library

#### 3. Select a new library and a logical mapping to it.

This creates a new QuestaSim library and maps it in the active *modelsim.ini* file.

#### 4. Define a Library Name.

The **Library Physical Name** option automatically updates to match.

The Library Physical Name is the name of the folder that is created

Figure 4.11. Library Creation Window

#### 5. Click OK.

A new library is created and mapped relative to the current directory.

Edit the modelsim.ini file to add the full library mapping.

By default, the mapping added to the active *modelsim.ini* file is relative to the current directory causing it to be inaccessible for projects/simulations in other directories.

The modelsim.ini file the full mapping is added to controls which projects can use the library.

**Local modelsim.ini** – only simulations from the current directory can access the library.

**Primary** *modelsim.ini* – library is accessible for all local *modelsim.ini* and *<project name>.mpf* files that reference the primary *modelsim.ini* file (recommended).

```

[Library]

custom lib = libdir

custom_lib = C:/demo_lib/lifcl/verilog/libdir

std = $MODEL TECH/../std

std = $MODEL TECH/../std

ieee = $MODEL TECH/../ieee

ieee = $MODEL_TECH/../ieee

vital2000 = $MODEL TECH/../vital2000

vital2000 = $MODEL TECH/../vital2000

verilog = $MODEL TECH/../verilog

verilog = $MODEL TECH/../verilog

std_developerskit = $MODEL_TECH/../std_developerskit std_developerskit = $MODEL_TECH/../std_developerskit

synopsys = $MODEL TECH/../synopsys

synopsys = $MODEL TECH/../synopsys

modelsim_lib = $MODEL_TECH/../modelsim_lib

modelsim lib = $MODEL TECH/../modelsim lib

sv std = $MODEL TECH/../sv

Default relative path OALTINID

floatfixlib = $MODEL TECH/.

Correct full path

```

Figure 4.12. Example modelsim.ini Modification to Add Full Library Path

# 4.3. Simulating Different Process Stages