# **DDR Memory PHY Module**

IP Version: v2.5.0

# **User Guide**

FPGA-IPUG-02195-1.4

December 2025

### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents                                    | 3  |

|---------------------------------------------|----|

| Figures                                     |    |

| Tables                                      | 6  |

| Abbreviations in This Document              | 8  |

| 1. Introduction                             | 9  |

| 1.1. Quick Facts                            |    |

| 1.2. Features                               |    |

| 1.2.1. DDR4                                 |    |

| 1.2.2. LPDDR4                               | 10 |

| 1.3. IP Validation Summary                  | 11 |

| 1.4. Licensing and Ordering Information     | 12 |

| 1.5. Minimum Device Requirements            |    |

| 1.6. Naming Conventions                     | 13 |

| 1.6.1. Nomenclature                         | 13 |

| 1.6.2. Signal Names                         | 13 |

| 2. Functional Description                   | 14 |

| 2.1. IP Architecture                        | 14 |

| 2.1.1. Hardened DDRPHY Software Primitive   | 14 |

| 2.1.2. Hardened DDRPHY IP                   | 15 |

| 2.1.3. Soft Training Engine                 | 15 |

| 2.2. Clocking                               | 15 |

| 2.3. Reset                                  | 15 |

| 2.4. User Interfaces                        | 16 |

| 2.4.1. DFI 4.0 PHY Interface                |    |

| 2.4.2. APB Configuration Interface          | 16 |

| 2.5. Calibration                            | 16 |

| 2.5.1. Command Bus Training (CBT)           |    |

| 2.5.2. Write Leveling                       | 17 |

| 2.5.3. Read Training (Read Bit-Leveling)    |    |

| 2.5.4. Write Training (Write Bit-Leveling)  |    |

| 2.5.5. VREF Training                        |    |

| 2.5.6. Self-Calibrating Logic (SCL)         |    |

| 2.5.7. Bit-Level Trim Sweep (BLTS)          |    |

| 2.5.8. 2-D Vref Training                    |    |

| 2.6. Operation Descriptions                 |    |

| 2.7. Bit Swizzle                            |    |

| 2.7.1. DQ Bit Swizzle Example               |    |

| 3. IP Parameter Description                 |    |

| 3.1. DDR4 Parameters                        |    |

| 3.1.1. DDR4 General                         |    |

| 3.1.2. DDR4 Training Settings               |    |

| 3.2. LPDDR4 Parameters                      |    |

| 3.2.1. LPDDR4 General                       |    |

| 3.2.2. LPDDR4 Training Settings             |    |

| 3.2.3. Bit Swizzle Settings                 |    |

| 4. Signal Description                       |    |

| 4.1. Clock and Reset                        |    |

| 4.2. Interrupts and Initialization/Training |    |

| 4.3. APB Register Interface                 |    |

| 4.4. DFI 4.0 PHY Interface                  |    |

| 4.5. Memory Interface Signals               |    |

| 4.5.1. DDR4 Memory Interface                | 36 |

| 4.5.2. LPDDR4 Memory Interface                                          | 36 |

|-------------------------------------------------------------------------|----|

| 5. Register Description                                                 | 37 |

| 5.1. Feature Control Register (FEATURE_CTRL_REG) (0x200)                | 38 |

| 5.2. Reset Register (RESET_REG) (0x204)                                 | 39 |

| 5.3. Settings Register (SETTINGS_REG) (0x208)                           | 39 |

| 5.4. PHY Clock Register (PHY_CLOCK_REG) (0x20C)                         | 40 |

| 5.5. Interrupt Status Register (INT_STATUS_REG) (0x210)                 |    |

| 5.6. Interrupt Enable Register (INT_ENABLE_REG) (0x214)                 | 41 |

| 5.7. Interrupt Set Register (INT_SET_REG) (0x218)                       | 41 |

| 5.8. Training Operation Register (TRN_OP_REG) (0x220)                   |    |

| 5.9. Training Status Register (TRN_STATUS_REG) (0x224)                  | 43 |

| 5.10. Mode Register Write Control Register (MRW_CTRL_REG) (0x230)       | 45 |

| 5.11. Clock/Address/Control Trim Register (CK_ADRCTRL_TRIM_REG) (0x250) | 45 |

| 5.12. ODT Settings Register (ODT_SETTINGS_REG) (0x254)                  | 46 |

| 5.13. DRAM VREF Register (DRAM_VREF_REG) (0x25C)                        |    |

| 5.14. PHY VREF Register for DQS Groups 0-3 (PHY_VREF_0_3_REG) (0x260)   | 48 |

| 5.15. PHY VREF Register for DQS Groups 4-7 (PHY_VREF_4_7_REG) (0x264)   | 49 |

| 5.16. PHY VREF Register for DQS Group 8 (PHY_VREF_8_REG) (0x268)        | 49 |

| 6. DDRPHY Example Design                                                | 50 |

| 6.1. Synthesis Example Design                                           | 50 |

| 6.2. Simulation Example Design                                          | 50 |

| 7. Designing and Simulating the IP                                      | 51 |

| 7.1. Generating the IP                                                  | 51 |

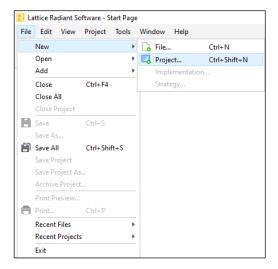

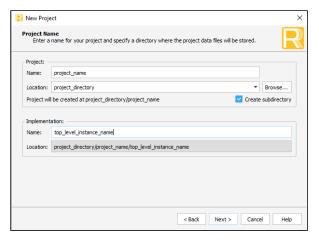

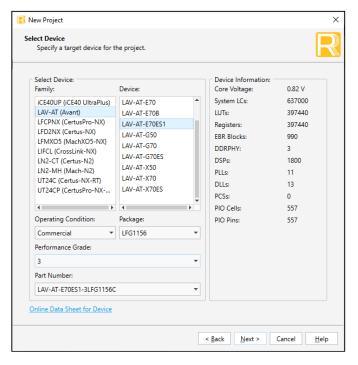

| 7.1.1. Creating a Radiant Project                                       | 51 |

| 7.1.2. Configuring and Generating the IP                                | 53 |

| 7.2. Design Implementation                                              | 54 |

| 7.2.1. Pin Placement                                                    | 54 |

| 7.2.2. Constraints                                                      | 55 |

| 7.3. Example Design Simulation                                          | 55 |

| Appendix A. Resource Utilization                                        | 60 |

| Appendix B. Known Issues                                                | 61 |

| References                                                              | 62 |

| Technical Support Assistance                                            | 63 |

| Revision History                                                        | 64 |

|                                                                         |    |

# **Figures**

| Figure 2.1. DDRPHY IP Module Functional Diagram                    | 14 |

|--------------------------------------------------------------------|----|

| Figure 2.2. Command Bus Training                                   | 17 |

| Figure 2.3. Write Leveling                                         | 18 |

| Figure 2.4. Read DQ-Bit Leveling                                   | 18 |

| Figure 2.5. Write DQ-Bit Leveling                                  | 19 |

| Figure 2.6. VREF Training                                          | 20 |

| Figure 2.7. Self-Calibrating Logic CDC Training Circuit            | 20 |

| Figure 2.8. Self-Calibrating Logic CDC Timing Diagram              | 21 |

| Figure 2.9. Self-Calibrating Logic Latency Training                | 21 |

| Figure 2.10. Bit Swizzle Feature Block Diagram                     | 23 |

| Figure 2.11. Example LPDDR4 DQ Bit Swizzle within DQS Group        | 24 |

| Figure 2.12. Example LPDDR4 Bit Swizzle Settings                   | 24 |

| Figure 6.1. DDR Memory PHY Module Synthesis Example Design Diagram | 50 |

| igure 7.1. Creating a New Radiant Project                          | 51 |

| igure 7.2. New Project Settings                                    | 51 |

| Figure 7.3. Project Device Settings                                | 52 |

| Figure 7.4. Project Synthesis Tool Selection                       | 52 |

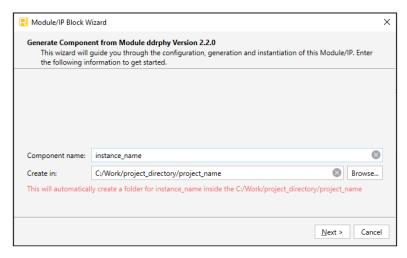

| Figure 7.5. IP Instance Settings                                   | 53 |

| igure 7.6. IP Generation Result                                    | 53 |

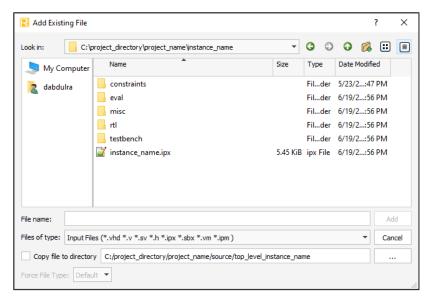

| Figure 7.7. Add Existing File Dialog Box                           | 56 |

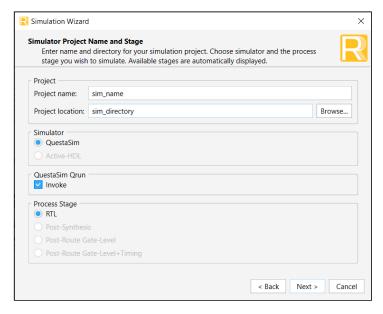

| igure 7.8. Simulation Wizard                                       | 57 |

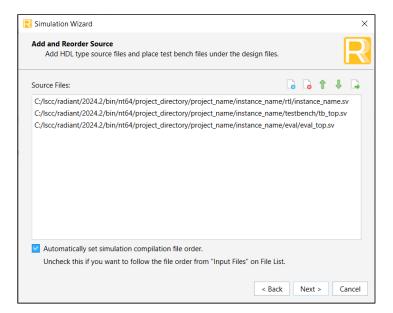

| Figure 7.9. Adding and Reordering Simulation Source Files          | 57 |

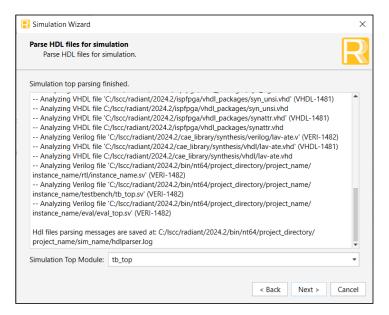

| Figure 7.10. Parsing Simulation HDL Files                          | 58 |

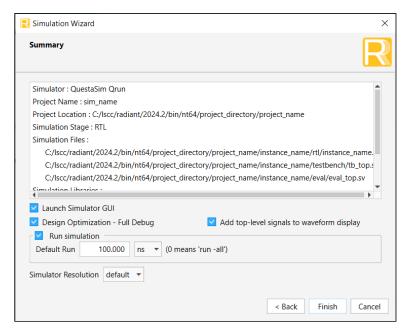

| Figure 7.11. Simulation Summary                                    | 58 |

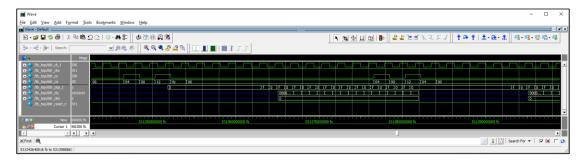

| Figure 7.12. Simulation Result Waveform                            | 59 |

# **Tables**

| Table 1.1. Quick Facts                                             | 9   |

|--------------------------------------------------------------------|-----|

| Table 1.2. DDR4 Features Overview                                  |     |

| Table 1.3. LPDDR4 Features Overview                                |     |

| Table 1.4. Avant IP Validation Summary                             |     |

| Table 1.5. Nexus 2 IP Validation Summary                           |     |

| Table 1.6. Avant Minimum Device Requirements                       |     |

| Table 1.7. Nexus 2 Minimum Device Requirements                     |     |

| Table 2.1. Calibration Summary                                     |     |

| Table 3.1. DDR4 General Attributes                                 |     |

| Table 3.2. DDR4 Clock Settings Attributes                          |     |

| Table 3.3. DDR4 Clock/Address/Command Attributes                   |     |

| Table 3.4. DDR4 General Definitions                                |     |

| Table 3.5. DDR4 Training Settings Attributes                       |     |

| Table 3.6. DDR4 PHY I/O Settings Attributes                        |     |

| Table 3.7. DDR4 Memory ODT Settings Attributes                     |     |

| Table 3.8. DDR4 Training Settings Definitions                      |     |

| Table 3.9. LPDDR4 General Attributes                               |     |

| Table 3.10. LPDDR4 Clock Settings Attributes                       | 29  |

| Table 3.11. LPDDR4 Clock/Address/Command Attributes                |     |

| Table 3.12. LPDDR4 General Definitions                             |     |

| Table 3.13. LPDDR4 Training Settings Attributes                    |     |

| Table 3.14. LPDDR4 PHY I/O Settings Attributes                     |     |

| Table 3.15. LPDDR4 Memory ODT Settings Attributes                  |     |

| Table 3.16. LPDDR4 Training Settings Definitions                   | .31 |

| Table 3.17. LPDDR4 Bit Swizzle Attributes                          |     |

| Table 3.18. LPDDR4 Bit Swizzle Attribute Definitions               | .33 |

| Table 4.1. Clock and Reset Port Definitions                        | .34 |

| Table 4.2. Interrupts and Initialization/Training Port Definitions | .34 |

| Table 4.3. APB Interface Port Definitions                          | .35 |

| Table 4.4. AXI4 Interface Port Definitions                         | .35 |

| Table 4.5. DDR4 Interface Port Definitions                         | .36 |

| Table 4.6. LPDDR4 Interface Port Definitions                       | .36 |

| Table 5.1. Summary of DDRPHY Module Registers                      | .37 |

| Table 5.2. Register Access Type Definitions                        | .38 |

| Table 5.3. Feature Control Register                                | .38 |

| Table 5.4. Reset Register                                          | .39 |

| Table 5.5. Settings Register                                       | 39  |

| Table 5.6. PHY Clock Register                                      | .40 |

| Table 5.7. Interrupt Status Register                               | .40 |

| Table 5.8. Interrupt Enable Register                               |     |

| Table 5.9. Interrupt Set Register                                  |     |

| Table 5.10. Training Operation Register                            |     |

| Table 5.11. Training Status Register                               |     |

| Table 5.12. Mode Register Write Control Register                   |     |

| Table 5.13. Clock/Address/Control Trim Settings Register           |     |

| Table 5.14. ODT Settings Register for LPDDR4                       |     |

| Table 5.15. ODT Settings Register for DDR4                         |     |

| Table 5.16. DRAM VREF Register                                     |     |

| Table 5.17. PHY VREF Register for DQS Groups 0-3                   |     |

| Table 5.18. PHY VREF Register for DQS Groups 4-7                   |     |

| Table 5.19. PHY VREF Register for DQS Group 8                      |     |

| Table 7.1. Generated File List                                     | .54 |

| Table 7.2. Project Constraints                            | 55 |

|-----------------------------------------------------------|----|

| Table A.1. DDR4 Resource Utilization for IP Core v2.5.0   |    |

| Table A.2. LPDDR4 Resource Utilization for IP Core v2.5.0 | 60 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                |  |  |

|--------------|-------------------------------------------|--|--|

| APB          | Advanced Peripheral Bus                   |  |  |

| AXI4         | Advanced eXtensible Interface 4           |  |  |

| BL           | Burst Length                              |  |  |

| BLTS         | Bit-Level Trim Sweep                      |  |  |

| CA           | Command and Address                       |  |  |

| CS           | Chip Select                               |  |  |

| CBT          | Command Bus Training                      |  |  |

| DBI          | Data Bus Inversion                        |  |  |

| DDR          | Double Data Rate                          |  |  |

| DDRPHY       | DDR Physical Layer                        |  |  |

| DFI          | DDR PHY Interface                         |  |  |

| DM           | Data Mask                                 |  |  |

| DQ           | Data                                      |  |  |

| DQS          | Data Strobe                               |  |  |

| ECC          | Error Correction Code                     |  |  |

| ECLK         | Edge Clock                                |  |  |

| FPGA         | Field Programmable Gate Array             |  |  |

| HPIO         | High Performance I/O                      |  |  |

| I/F          | Interface                                 |  |  |

| JEDEC        | Joint Electron Device Engineering Council |  |  |

| JTAG         | Joint Test Action Group                   |  |  |

| LPDDR4       | Low Power Double Data Rate Generation 4   |  |  |

| LVSTL        | Low Voltage Swing Terminated Logic        |  |  |

| MC           | Memory Controller                         |  |  |

| MR           | Mode Register                             |  |  |

| MRS          | Mode Register Set                         |  |  |

| ODT          | On-Die Termination                        |  |  |

| PRBS         | Pseudorandom Binary Sequence              |  |  |

| PVT          | Process, Voltage, and Temperature         |  |  |

| RTL          | Register Transfer Level                   |  |  |

| SCL          | Self-Calibration Logic                    |  |  |

| SCLK         | System Clock                              |  |  |

| SDR          | Single Data Rate                          |  |  |

| SDRAM        | Synchronous Dynamic Random Access Memory  |  |  |

| SSN          | Simultaneous Switching Noise              |  |  |

| TCL          | Tool Command Language                     |  |  |

| VREF         | Voltage Reference                         |  |  |

# 1. Introduction

The Lattice Semiconductor DDR Memory PHY Module for Avant and Nexus 2 Devices implements the DFI 4.0 Specification (© Cadence Design Systems, Inc.). The DDRPHY IP Module is a hardened block in Lattice Avant and Nexus 2 devices that describes the interoperation between a Memory Controller and Physical Interface (PHY). The DDRPHY IP Module provides training and clocking control for the following SDRAM protocols: DDR4 and LPDDR4. The IP Module is implemented in System Verilog HDL using the Lattice Radiant™ software integrated with the Lattice Synthesis Engine (LSE) and Synplify Pro® synthesis tools.

# 1.1. Quick Facts

Table 1.1 presents a summary of the DDRPHY IP Module.

Table 1.1. Quick Facts

| doi: 111 Quick 1 deb |                                     |                                                                                               |  |  |

|----------------------|-------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| ID Possilinoments    | Supported Devices                   | DDR4 mode – Lattice Avant, Certus-N2<br>LPDDR4 mode – Lattice Avant, Certus-N2                |  |  |

| IP Requirements      | IP Changes <sup>1</sup>             | For a list of changes to the IP, refer to the DDR Memory PHY IP Release Notes (FPGA-RN-02072) |  |  |

| Resource Utilization | Supported User Interfaces           | DFI for PHY access APB for configuration access                                               |  |  |

|                      | Resources                           | Refer to Appendix A. Resource Utilization Table A.1 and Table A.2                             |  |  |

|                      | Lattice Implementation <sup>2</sup> | IP Core v2.5.0 - Lattice Radiant software 2025.2                                              |  |  |

| Design Tool Support  | Synthesis                           | Lattice Synthesis Engine<br>Synopsys® Synplify Pro for Lattice                                |  |  |

|                      | Simulation                          | For a list of supported simulators, refer to the Lattice Radiant Software User Guide          |  |  |

### Notes:

- 1. In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

- Lattice Implementation indicates the IP version release coinciding with the software version release. Check the software for IP version compatibility with earlier or later software versions.

### 1.2. Features

The DDRPHY IP Module supports the following key features for DDR4 and LPDDR4 SDRAM.

### 1.2.1. DDR4

The DDRPHY Module, when configured in DDR4 mode, supports the following key features for Avant and Nexus 2 devices:

- DDR4 SDRAM protocol, compliant to DDR4 JEDEC Standard

- DDR4 SDRAM speeds ranging from 350 MHz to 1,200 MHz (700 Mbps to 2,400 Mbps)

- Memory Interface features:

- Interface data widths of x16, x32, and x64

- Interface data widths of x40 and x72 are also supported when Sideband ECC is enabled

- x8 and x16 DDR4 device support (8:1 DQ:DQS ratio)

- Configurable CAS latencies for Reads and Writes based on target interface speed

- 8:1 gearing mode (4:1 DDR4-to-FPGA clock frequency ratio)

- Supports component (DRAM soldered on the board) and UDIMM

- Memory Training features:

- Automatic DDR4 initialization

- Write Leveling

- Read Training

- Write Training

- Self-Calibrating Logic

- Includes dedicated PLL for clock generation

### **Table 1.2. DDR4 Features Overview**

| Key Features                | DDR4 Support Details                        |  |

|-----------------------------|---------------------------------------------|--|

| Device Format               | Component, DIMM not yet supported           |  |

| Data Widths                 | x16, x32, x40, x64, x72                     |  |

| PHY Interface               | DFI                                         |  |

| Configuration Interface     | APB                                         |  |

| Maximum Data Rate           | Refer to Table 1.6 and Table 1.7            |  |

| Other Features <sup>1</sup> |                                             |  |

| Error Correction Code (ECC) | Yes                                         |  |

| Dual-rank                   | Yes                                         |  |

| Data Bus Inversion (DBI)    | Not yet supported, for reads, No for writes |  |

| On-Die Termination (ODT)    | Yes, for DQ, No for CA                      |  |

| Bit Swizzle                 | Not yet supported                           |  |

| Training <sup>1</sup>       |                                             |  |

| Initialization              | Yes                                         |  |

| CS Training                 | Not yet supported                           |  |

| Write Leveling              | Yes                                         |  |

| Read Training               | Yes                                         |  |

| Write Training              | Yes                                         |  |

| Automatic VREF Training     | Not yet supported                           |  |

| Self-Calibrating Logic      | Yes                                         |  |

| Bit-Level Trim Sweep        | Not yet supported                           |  |

| 2-D Vref Training           | Not yet supported                           |  |

### Note:

# 1.2.2. LPDDR4

The DDRPHY Module, when configured in LPDDR4 mode, supports the following key features for Avant and Nexus 2 Devices:

- LPDDR4 SDRAM protocol, compliant to LPDDR4 JEDEC Standard

- LPDDR4 SDRAM speeds ranging from 350 MHz to 1,200 MHz (700 Mbps to 2,400 Mbps)

- Memory Interface features:

- Interface data widths of x16, x32, and x64

- 8:1 gearing mode (4:1 LPDDR4-to-FPGA clock frequency ratio)

- Memory Training features:

- Automatic LPDDR4 initialization

- Command Bus Training

- Write Leveling

- Read Training

- Write Training

- VREF Training

- Self-Calibrating Logic

- Bit-Level Trim Sweep

<sup>1.</sup> Yes implies that a configurable option exists to enable or disable the feature. No implies that the feature is currently not supported and will not be supported in the future.

- 2-D Vref Training

- Includes internal programmable VREF

- Includes dedicated PLL for clock generation

- Bit Swizzle (DQ bit swizzle within the DQS group)

### **Table 1.3. LPDDR4 Features Overview**

| Key Features                | LPDDR4 Support Details                             |

|-----------------------------|----------------------------------------------------|

| Device Format               | Component                                          |

| Data Widths                 | x16, x32, x64                                      |

| PHY Interface               | DFI                                                |

| Configuration Interface     | APB                                                |

| Maximum Data Rate           | Refer to Table 1.6 and Table 1.7                   |

| Other Features <sup>1</sup> |                                                    |

| Dual-rank                   | Yes                                                |

| Data Bus Inversion (DBI)    | Yes, for reads, No for writes                      |

| On-Die Termination (ODT)    | Yes for DQ and CA                                  |

| Bit Swizzle                 | Yes for DQ, Not yet supported for CA and DQS Group |

| Training <sup>1</sup>       |                                                    |

| Initialization              | Yes                                                |

| Command Bus Training        | Yes                                                |

| Write Leveling              | Yes                                                |

| Read Training               | Yes                                                |

| Write Training              | Yes                                                |

| Automatic VREF Training     | Yes                                                |

| Self-Calibrating Logic      | Yes                                                |

| Bit-Level Trim Sweep        | Yes                                                |

| 2-D Vref Training           | Yes                                                |

# Note:

# 1.3. IP Validation Summary

The DDRPHY IP Module supports Avant-AT-E, Avant-AT-G, Avant-AT-X, and Nexus 2 devices. Table 1.4 and Table 1.5 summarize the compilation, simulation, and hardware validation for the DDRPHY IP.

**Table 1.4. Avant IP Validation Summary**

| Table 1.4. Availt if Validation Summary |             |            |                        |  |  |

|-----------------------------------------|-------------|------------|------------------------|--|--|

| Device/Mode                             | Compilation | Simulation | Hardware               |  |  |

| DDR4                                    | DDR4        |            |                        |  |  |

| Avant-AT-E                              | Yes         | Yes        | No                     |  |  |

| Avant-AT-G                              | Yes         | Yes        | No                     |  |  |

| Avant-AT-X                              | Yes         | Yes        | No                     |  |  |

| LPDDR4                                  | LPDDR4      |            |                        |  |  |

| Avant-AT-E                              | Yes         | Yes        | Yes <sup>1, 3</sup>    |  |  |

| Avant-AT-G                              | Yes         | Yes        | Yes <sup>1, 2, 3</sup> |  |  |

| Avant-AT-X                              | Yes         | Yes        | Yes <sup>1, 2, 3</sup> |  |  |

### Notes:

- 1. Supports x16 and x32 data widths only. The data width of x64 is not hardware validated.

- 2. Supports up to 1,066 MHz only. 1,200 MHz is not yet hardware validated.

- 3. Supports single rank only. Dual rank is not yet hardware validated.

© 2023-2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02195-1.4

<sup>1.</sup> Yes implies that a configurable option exists to enable or disable the feature. No implies that the feature is currently not supported and will not be supported in the future.

**Table 1.5. Nexus 2 IP Validation Summary**

| Device/Mode <sup>1</sup> | Compilation | Simulation | Hardware |  |

|--------------------------|-------------|------------|----------|--|

| DDR4                     |             |            |          |  |

| Nexus 2                  | Yes         | Yes        | No       |  |

| LPDDR4                   |             |            |          |  |

| Nexus 2                  | Yes         | Yes        | No       |  |

### Note:

# 1.4. Licensing and Ordering Information

The DDRPHY IP is provided at no additional cost with the Lattice Radiant software.

# 1.5. Minimum Device Requirements

The DDRPHY IP Module supports Avant E/G/X and Nexus 2 devices. Table 1.6 and Table 1.7 summarize the minimum device requirements for the DDRPHY IP Module.

**Table 1.6. Avant Minimum Device Requirements**

| Device/Mode    | DDR Data Width          | DDR Ranks | Maximum Interface Speed | Supported Speed Grades |

|----------------|-------------------------|-----------|-------------------------|------------------------|

| DDR4           |                         |           |                         |                        |

| Avant-AT-E/G/X | x16, x32, x40, x64, x72 | 1         | 933 MHz (1,866 Mbps)    | 1, 2, 3                |

| Avant-AT-E/G/X | x16, x32, x40, x64, x72 | 1, 2      | 1,066 MHz (2,133 Mbps)  | 2, 3                   |

| Avant-AT-E/G/X | x16, x32, x40, x64, x72 | 1         | 1,200 MHz (2,400 Mbps)  | 3                      |

| LPDDR4         |                         |           |                         |                        |

| Avant-AT-E/G/X | x16, x32, x40, x64, x72 | 1         | 933 MHz (1,866 Mbps)    | 1, 2, 3                |

| Avant-AT-E/G/X | x16, x32, x40, x64, x72 | 1, 2      | 1,066 MHz (2,133 Mbps)  | 2, 3                   |

| Avant-AT-E/G/X | x16, x32, x40, x64, x72 | 1         | 1,200 MHz (2,400 Mbps)  | 3                      |

**Table 1.7. Nexus 2 Minimum Device Requirements**

| and 2177 Hoxas 2 minimum ported requirements |                |           |                         |                        |  |

|----------------------------------------------|----------------|-----------|-------------------------|------------------------|--|

| Device/Mode                                  | DDR Data Width | DDR Ranks | Maximum Interface Speed | Supported Speed Grades |  |

| DDR4                                         |                |           |                         |                        |  |

| Nexus 2                                      | x16, x32, x40  | 1         | 933 MHz (1,866 Mbps)    | 1, 2, 3                |  |

| Nexus 2                                      | x16, x32, x40  | 1, 2      | 1,066 MHz (2,133 Mbps)  | 2, 3                   |  |

| Nexus 2                                      | x16, x32, x40  | 1         | 1,200 MHz (2,400 Mbps)  | 3                      |  |

| LPDDR4                                       |                |           |                         |                        |  |

| Nexus 2                                      | x16, x32, x40  | 1         | 933 MHz (1,866 Mbps)    | 1, 2, 3                |  |

| Nexus 2                                      | x16, x32, x40  | 1, 2      | 1066 MHz (2,133 Mbps)   | 2, 3                   |  |

| Nexus 2                                      | x16, x32, x40  | 1         | 1200 MHz (2,400 Mbps)   | 3                      |  |

<sup>1.</sup> Nexus 2 supports only DDR4 and LPDDR4 interfaces.

# 1.6. Naming Conventions

This section provides information regarding terminology used within this document.

# 1.6.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

# 1.6.2. Signal Names

Signal Names that end with:

- \_n are active low

- \_i are input signals

- \_o are output signals

- \_io are bi-directional input/output signals

# 2. Functional Description

This section provides a detailed functional description of the DDRPHY IP Module, including information regarding clock and reset handling, available user data and configuration interfaces, the calibration sequence, and operation descriptions.

# 2.1. IP Architecture

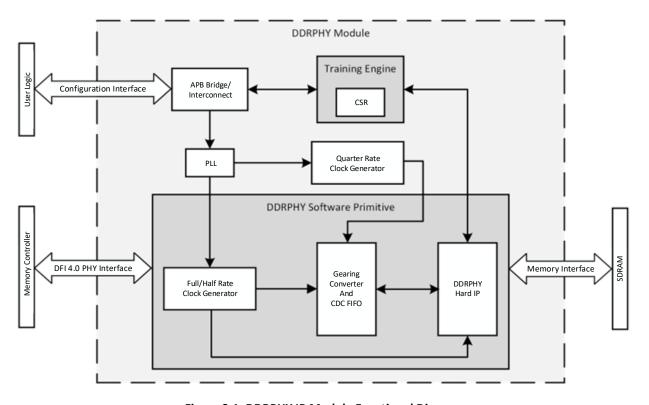

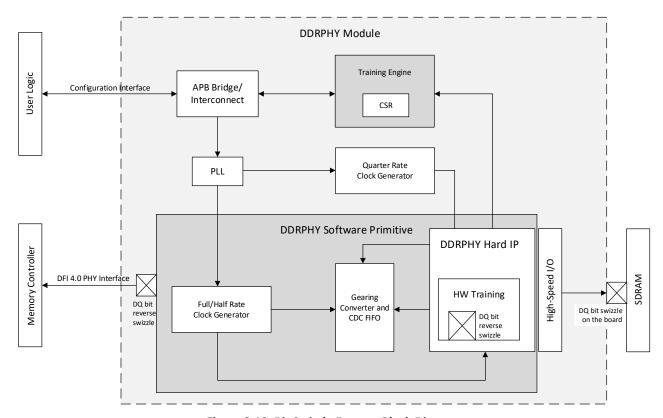

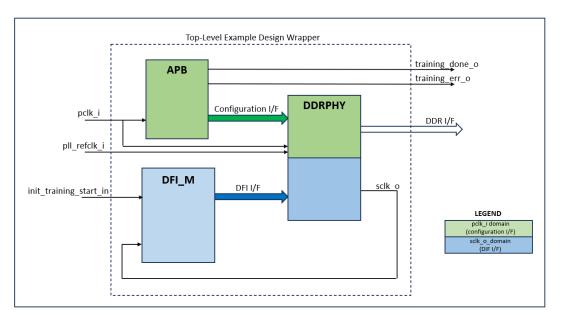

The DDRPHY Module consists of three main blocks: the DDRPHY Software Primitive, the DDRPHY Hard IP, and the Training Engine. Figure 2.1 shows the DDRPHY Module sub-blocks and their connectivity.

Figure 2.1. DDRPHY IP Module Functional Diagram

The configuration interface provides access to the Training Engine and the Configuration Set Registers (CSRs), which configure the DDRPHY and perform the DDR4 and LPDDR4 training sequences. The PHY interface allows users to initiate command, address, control, and read/write operations via a memory controller to the external DDR4/LPDDR4 SDRAM. The memory interface enables the selected Lattice FPGA to communicate with the external DDR4/LPDDR4 memory. For more information on the PHY and configuration interfaces, refer to the User Interfaces section of this User Guide.

# 2.1.1. Hardened DDRPHY Software Primitive

The Hardened DDRPHY consists of the following submodules:

- Full/Half Rate Clock Generator

- Gearing Converter and CDC FIFO

- DDRPHY Hard IP

### 2.1.1.1. Full/Half Rate Clock Generator

The DDRPHY Software Primitive contains a full-rate and half-rate clock generator, which utilizes dedicated PLLs and clock routing to enable high-frequency operation. The PLL provides a full-rate clock (ECLK) to the Hard IP and the half-rate clock (SCLK) to the Hard IP, and Gearing Converter, and CDC FIFO.

### 2.1.1.2. Gearing Converter and Clock Domain Crossing FIFO

The DDRPHY Hard IP implements a frequency ratio of 1:2 (4:1 gearing). The gearing converter and CDC FIFO convert this to a frequency ratio of 1:4 (8:1 gearing). The gearing converter implements 2:1 and 1:2 gearing to allow DFI signals to run at half-rate. The CDC FIFO ensures signal integrity when transferring data to and from FPGA fabric.

## 2.1.2. Hardened DDRPHY IP

The DDRPHY Hard IP implements the DFI 4.0 Standard. It connects to High Performance I/O (HPIO) to support high-frequency operation and allow reuse of FPGA I/O for other functions when the DDRPHY Hard IP is not utilizing the I/O. The DDRPHY Hard IP translates the PHY interface signals (DFI) from the fabric to memory interface signals for DDR4/LPDDR4 SDRAM.

# 2.1.3. Soft Training Engine

The Training Engine reads instructions from system memory and initializes and trains the external DDR4/LPDDR4 memory. It achieves this by accessing the Configuration Set Registers of the DDRPHY Module, PLL, and DDRPHY Hard IP. You issue commands to the Training Engine to perform reads and writes to these registers, allowing them to handle interrupts and obtain details during the memory training sequence.

# 2.2. Clocking

The DDRPHY IP Module, when configured for DDR4 and LPDDR4 interfaces, requires a differential input reference clock: pll\_refclk\_i. You need to provide this clock via an external source, an internal oscillator, or a dedicated PLL. This clock routes through a dedicated PLL within the DDRPHY IP to generate the Edge Clock (ECLK) and System Clock (SCLK). The ECLK signal clocks the I/O modules internally within the IP Core, and SCLK clocks the IP Core. The Primary Clock (PCLK) signal implements clock synchronization logic to synchronize SCLK and ECLK.

The DFI interface for the DDRPHY Module operates off the sclk\_o signal and resets via the dfi\_reset\_n\_i signal. The configuration interface for the DDRPHY IP Module operates off the pclk\_i signal and resets via the preset\_n\_i signal. The clock for the configuration interface is the same one that implements clock synchronization for SCLK and ECLK. Refer to the Clock and Reset Signal Description section of this user guide for information regarding the clocks and resets for DDR4 and LPDDR4 memory interfaces.

# 2.3. Reset

The DDRPHY IP Module contains an asynchronous active high reset: rst\_i. This signal requires a minimum pulse width of 2× the pclk\_i period. When asserted, the external SDRAM resets to its default value. The DDRPHY Module contains internal logic that synchronously de-asserts the internal reset once rst\_i is de-asserted, so you do not need to worry about implementing their own de-assertion logic.

The preset\_n\_i signal is an asynchronous active low reset, which you must ensure is synchronously de-asserted to pclk\_i. Refer to the Clock and Reset Signal Description section of this user guide for information regarding the clocks and resets for DDR4 and LPDDR4 memory interfaces.

# 2.4. User Interfaces

This section describes the supported protocols for data and configuration interfaces available to the user and supported by a DDR4/LPDDR4 Memory Controller.

### 2.4.1. DFI 4.0 PHY Interface

The DFI 4.0 I/F defines how control and data information communicate between a memory controller and PHY. For more information regarding the DFI 4.0 Interface, refer to the DFI 4.0 Specification. The DFI I/F operates off the sclk\_o signal and resets via the dfi\_reset\_n\_i signal. Refer to the Clock and Reset Signal Description section of this user guide for more details. For additional information on the available user DFI signals, refer to the DFI 4.0 Interface Signal Description section and the Operation Descriptions section of this user guide.

# 2.4.2. APB Configuration Interface

The configuration interface allows users to initialize and train the memory interface. The APB I/F is a low-power protocol intended for accessing programmable control registers. It is not pipelined and is a synchronous protocol with a single address bus and two data buses: write and read. The DDRPHY does not support APB write strobe commands. For more information regarding the APB protocol, refer to the AMBA APB Protocol Specification.

The DDRPHY IP Module leverages this protocol to initialize and train the interface between FPGA logic and external SDRAM. The APB I/F operates off the pclk\_i signal and resets via the preset\_n\_i signal. Refer to the Clock and Reset Signal Description section of this user guide for more details.

# 2.5. Calibration

To ensure proper device functionality, you must initialize and train the external memory. The DDRPHY Module consists of a soft RISC-V CPU located inside the Training Engine that executes the initialization and training routines for DDR4 and LPDDR4. Table 2.1 summarizes the calibration or training stages supported for each memory protocol by the DDRPHY IP.

**Table 2.1. Calibration Summary**

|        | Command<br>Bus Training | Write<br>Leveling | Read<br>Training | Write<br>Training | VREF<br>Training | Self-<br>Calibrating<br>Logic | Bit-Level<br>Trim Sweep | 2-D Vref<br>Training |

|--------|-------------------------|-------------------|------------------|-------------------|------------------|-------------------------------|-------------------------|----------------------|

| DDR4   | No                      | Yes               | Yes              | Yes               | Yes              | Yes                           | Not Yet<br>Supported    | Not Yet<br>Supported |

| LPDDR4 | Yes                     | Yes               | Yes              | Yes               | Yes              | Yes                           | Yes                     | Yes                  |

To start the initialization and training sequence for the SDRAM device, you should execute the following steps via the configuration interface:

- 1. Ensure that the DDRPHY Module's PLL is in the lock state by polling the PHY Clock Register (PHY\_CLOCK) until the pll\_lock signal asserts (PHY\_CLOCK[1]=1).

- 2. Enable initialization and training by writing to the Training Operation Register (TRN\_OP\_REG) as follows:

- For 1,333 Mbps and below, set TRN\_OP\_REG=0x0DF. This enables initialization, command-bus training, write leveling, read training, write training, and 1D Vref training sequences to run.

- For 1,600 Mbps and 1,866 Mbps, set TRN\_OP\_REG=0x1DF to perform bit-level trim sweep in addition to the above.

- For 2,133 Mbps and 2,400 Mbps, set TRN\_OP\_REG=0x3DF to perform bit-level trim sweep and 2D Vref training in addition to the above. This is necessary for the two highest data rates.

For simulation purposes, shorten the initialization and training sequences by writing 0x01C to TRN\_OP\_REG. For more information, refer to the Register Description section of this user guide.

Pull the CPU and Training Engine out of reset by writing 1'b1 to the Reset Register (RESET\_REG). This begins the initialization and training sequence.

- Wait until initialization and training completes using one of the following methods:

- Poll the Status Register (TRN STATUS REG) until the bit lvl trim sweep done signal asserts (TRN STATUS REG[16]=1). This indicates that the bit-level trim sweep has completed, which is the final stage in the initialization and training process.

- Wait for the trn\_done\_int signal (INT\_STATUS\_REG[0]=1) or the trn\_error\_int signal (INT\_STATUS\_REG[1]=1) to assert in the Interrupt Status Register (INT STATUS REG). This method requires the trn done en signal (INT\_ENABLE\_REG[0]=1) and the trn\_err\_en signal (INT\_ENABLE\_REG[1]=1) to be asserted in the Interrupt Enable Register (INT ENABLE REG).

After completing the above steps, the DDRPHY Module is ready for DFI access. Once init done o asserts, the RISC-V CPU and Training Engine enter reset to save power.

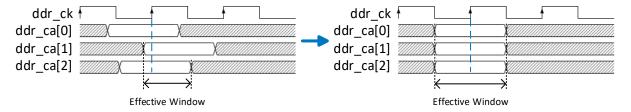

#### **Command Bus Training (CBT)** 2.5.1.

The goal of Command Bus Training (CBT) is to delay the command and address signals as necessary to optimize the CA window. When setting the cbt en signal high (TRN OP REG[1]=1), the Memory Controller performs CBT according to the DDR4 JEDEC Standard and LPDDR4 JEDEC Standard. This centers the entire CA bus relative to ddr ck o by aligning the rising edge of CK to the middle of the CA valid window. The DDR4/LPDDR4 memory then provides feedback to user through the DQ line, which the Memory Controller uses to determine if additional adjustment is required.

During this time, the DDR clock, ddr ck o, stops before and after CBT. This is expected as the clock is switches between low frequency (50 MHz) and high frequency (LPDDR4 interface speed) operation, as outlined in the DDR4 JEDEC Standard and LPDDR4 JEDEC Standard. Upon successful completion of CBT, ddr ca o centers to the eye of ddr ck o, ensuring correct behavior during high frequency operation.

Figure 2.2. Command Bus Training

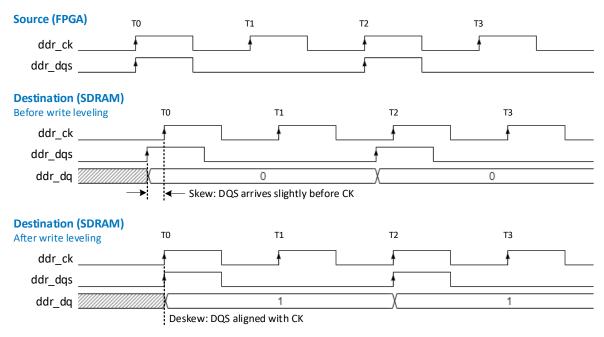

#### 2.5.2. Write Leveling

The purpose of write leveling is to delay each Data Strobe (DQS) relative to the DDR clock during write operations so they are edge-aligned. This addresses the CK to DQS timing skew introduced with the adoption of Fly-By Topology, which reduces Simultaneous Switching Noise (SSN) by allowing different memory components to receive write commands at different times. Setting the write IvI en signal high (TRN OP REG[2]=1) enables write leveling on all available ranks. During this process, the ddr dqs o signal is delay until a 0-to-1 transition on ddr ck o is captured by the dqs rising edge of the SDRAM device. The SDRAM memory then provides feedback of the captured clock signal value through the DQ line to determine if additional adjustment is required.

Figure 2.3. Write Leveling

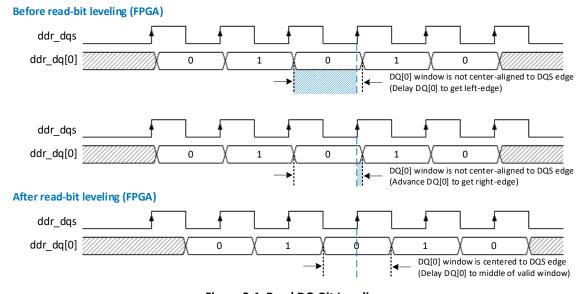

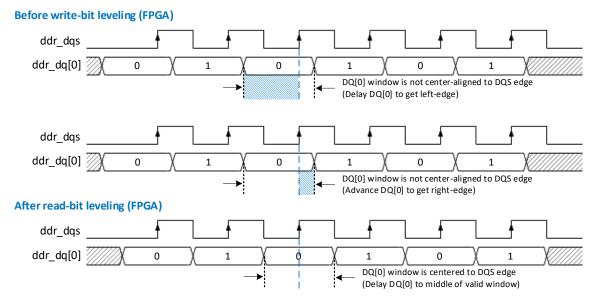

## 2.5.3. Read Training (Read Bit-Leveling)

The purpose of read training, or read DQ-bit leveling, is to center-align DQS relative to the DQ window. Setting the read\_trn\_en signal high (TRN\_OP\_REG[3]=1), enables read training. This compensates for unpredictable delays on DQ which can lead to skew between each input DQ and its respective DQS. During this process, a continuous 1-0-1-0 pattern is read from SDRAM on DQ, where DQS is delayed by 90 degrees. The DQ is then delayed and advanced to capture both edges of ddr\_dq\_io reading a 0, resulting in the DQ valid window. This indicates how far/close the rising edge of ddr\_dqs\_io is from ddr\_dq\_io to determine the amount of delay/advancement needed to align the rising edge of ddr\_dqs\_io to the ddr\_dq\_io valid window.

Figure 2.4. Read DQ-Bit Leveling

### 2.5.3.1. Read Training Limitation for LPDDR4 at 350MHz and 400MHz

Running Read Training at 350MHz and 400MHz (700Mbps and 800Mbps) will cause failure in the DDRPHY Hard IP because the adjustable read delay is less than the DQ period, and thus, the center of the DQ Valid window cannot be found. The Read DQS-DQ path is balanced in the DDRPHY Hard IP and thus, the default value delay value of 0 works at these speeds. The Self-Calibrating Logic (SCL) will confirm that the default read delay is okay. When the SCL passes, the data access will also pass. Because of this, the DDR Memory PHY Module cannot detect failure at Read Training (TRN\_STATUS\_REG.read\_training\_err=0) for these speeds even when you force the DQ bits to 0 during simulation. When the DDRPHY Hard IP detects Read Training error at these speeds, it will still be marked as pass (TRN\_STATUS\_REG.read\_training\_done=1). The read training error status can properly detect errors at 533MHz and up.

# 2.5.4. Write Training (Write Bit-Leveling)

The purpose of write training, or write DQ-bit leveling, is to center-align DQS relative to the DQ window. Setting the write\_trn\_en signal high (TRN\_OP\_REG[4]=1) enables write training. To achieve alignment, you must write a continuous 1-0-1-0 pattern to SDRAM and read it back to ensure successful writes. During this process, DQ delays and advances to capture both edges of ddr\_dq\_io successfully writing a 0, resulting in the DQ valid window. This indicates how far/close the rising edge of ddr\_dqs\_io is from ddr\_dq\_io to determine the amount of delay/advancement needed to align the rising edge of ddr\_dqs\_io to the ddr\_dq\_io valid window.

Figure 2.5. Write DQ-Bit Leveling

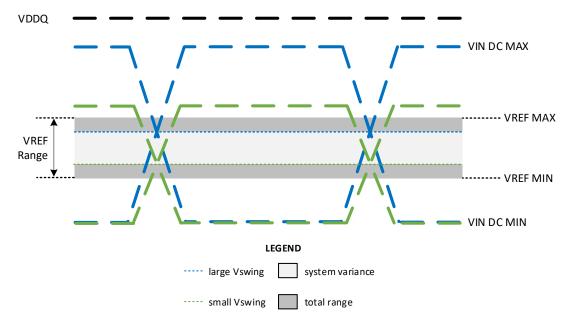

### 2.5.5. VREF Training

The goal of VREF training is to provide stable and robust memory access by maximizing margins on command, address, chip select, and data signals. VREF training occurs as part of CBT, read training, and write training. Setting the ca\_vref\_training\_en (TRN\_OP\_REG[5]=1), mc\_vref\_training\_en (TRN\_OP\_REG[6]=1), and mem\_vref\_training\_en (TRN\_OP\_REG[7]=1) signals high enables VREF training during CBT, reading training, and write training.

The voltage reference decides if a signal is registered as high (1) or low (0). Due to PVT variations and ODT drive/impedance matching, the internal voltage reference on DDR4/LPDDR4 can fluctuate, causing the center of the eye to move. VREF training consists of repeating the CBT, read training, and write training steps across different VREF values to find the center of the vertical valid window to maximize margins during operation.

Figure 2.6. VREF Training

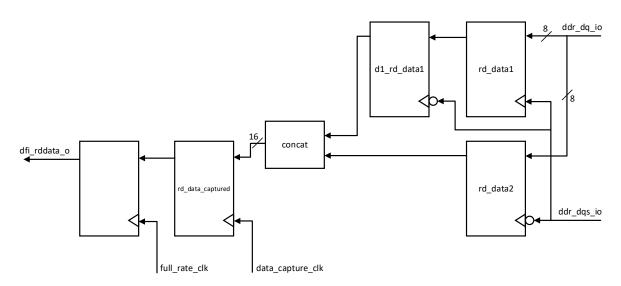

# 2.5.6. Self-Calibrating Logic (SCL)

The purpose of self-calibrating logic is to eliminate any DDR timing issues during DDR4/LPDDR4 read and write operations by performing the following:

- Clock Domain Crossing (CDC)

- Latency Calibration

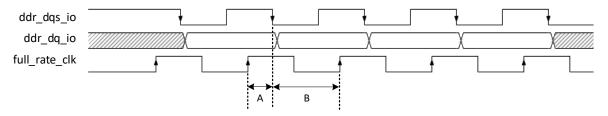

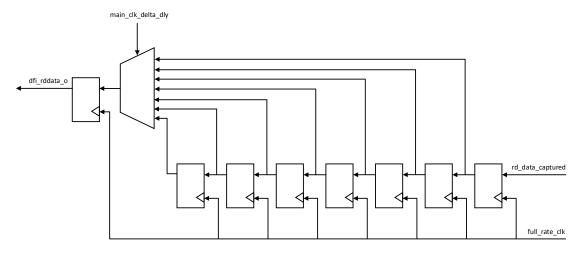

The goal of SCL CDC is to ensure sufficient margins during read operations by finding the center between the rising edge of ddr\_ck\_o and the falling edge of the next input ddr\_dqs\_io. This is achieved by performing 2 writes to SDRAM and then continuously reading data back while performing internal delay adjustments. Figure 2.7 shows the circuit for implementing the read capture logic, where the data\_capture\_clk is the variable delay clock, which SCL tunes to optimize setup and hold margins when clocking data from the input SDRAM DQS domain (ddr\_dqs\_io) to the DDRPHY clock domain represented as full rate clk.

Figure 2.7. Self-Calibrating Logic CDC Training Circuit

During the SCL routine, the DDRPHY searches for the falling edge of input DQS. Once found, the valid data following the DQS falling edge is captured in the rd\_data\_captured register and held for clocking into the PHY clock domain. SCL finds the center between the rising edge of the full rate clk and the falling edge of the next input DQS strobe, shown by points A and B in Figure 2.8. The point that gives the largest setup and hold margins (point B) is set as the active edge location for the captured read data.

Figure 2.8. Self-Calibrating Logic CDC Timing Diagram

In the latency calibration stage, you determine the best clock phase to capture the incoming data. The captured data from the rd data captured register is passed into the circuit shown in Figure 2.9, where SCL incrementally adjusts the multiplexer select signal (main clk delta dly) until the proper data (dfi rddata o) is received relative to full rate clk.

Figure 2.9. Self-Calibrating Logic Latency Training

#### 2.5.7. **Bit-Level Trim Sweep (BLTS)**

The purpose of bit-level trim sweep is to ensure proper alignment and sampling of the rising edge of DQS relative to DQ during DDR4/LPDDR4 write and read operations. Bit-level trim sweep helps to account for system SI/PI related variations/jitter introduced for high-speed applications running at 800 MHz – 1,200 MHz (1,600 Mbps – 2,400 Mbps). Setting the bit lvl trim sweep en (TRN OP REG[8]=1) signal high enables bit-level trim sweep.

Bit-level trim sweep is similar to read bit-leveling and write bit-leveling training stages. However, it helps to calibrate the DQS-DQ timing for complex and random transitions, compared to the simple 1-0-1-0 pattern completed in read bit-leveling and write bit-leveling training stages. Run bit-level trim sweep after SCL for frequencies greater than or egual to 800 MHz.

At high-level, the Bit-Level Trim Sweep performs the following:

- 1. Save the trained DQ delay values from the previous Read Training/Write Training.

- 2. Increase the delay of all DQ bits of the active DQS groups by 1 tap.

- 3. Perform DDR write and read with different aggressor-victim DQ patterns, capitalizing on the weakness of the I/O standard. This uses the worst-case DQ pattern to better find the data valid window.

- Check data integrity for all DQ and keep track of the maximum/minimum passing delay for each bit.

- 5. Repeat steps 2, 3, and 4 until all DQ bits has failed.

- 6. Revert the delay of all DQ bits to the saved values in step 1.

- 7. Repeat steps 2, 3, and 4 but use decrement instead of increment in step 2.

- 8. Get the average of the minimum passing delay and the maximum passing delay for each DQ bit and program it to the target DQ bit.

The DDRPHY Module performs read-side BLTS first, followed by the write-side BLTS.

## 2.5.8. 2-D Vref Training

At top speeds 2133Mbps and 2400Mbps, the actual eye opening is smaller as the high/low times are shorter. This requires more careful selection of the Vref. Each DQS Group has its own Vref setting which will be optimized for each of them. The 2D Vref training is only available for the DDRPHY-side Vref. This is not available for the DRAM side Vref because the DDRPHY has only 1 CS signal per rank and thus, it cannot set different Vref for each of the DRAM channel/chip in the same rank. This training step is only available for LPDDR4, it is not yet available for DDR4.

At the 2D At high Level, the 2-D Vref Training performs the following:

- 1. Set the Vref for each DQS group to the previous VREF Training value + 5.

- 2. Perform read-side BLTS.

- 3. Find the minimum DQ bit window for each DQS group and record them,

- 4. Decrement the Vref setting for each DQS group by 1 tap.

- 5. Repeat steps 2, 3 and 4 for 20x. Note that this training is lengthy so only 20-tap Vref sweep was performed. The sweep range was chosen based on the FPGA's I/O characteristics.

- 6. Find the optimal Vref setting for each DQS group based on the records from step 3 and use them as the trained Vref settings.

- 7. Run read-side BLTS again using the trained Vref settings.

# 2.6. Operation Descriptions

The DFI4.0 specifies several interfaces for training specific signals. The DDRPHY Module does not require these signals as it operates independently to fully perform the calibration sequence.

Note these special connectivity requirements:

- The dfi\_rddata\_en\_p0\_i and dfi\_rddata\_en\_p2\_i signals may be provided as a per byte lane output from the controller, with all bits having identical timing. The PHY requires only one dfi\_rddata\_en input. Connect the LSB (bit 0) of the controller's dfi\_rddata\_en to PHY dfi\_rddata\_en. The same connection applies to dfi\_wrdata\_en\_p0\_i and dfi\_wrdata\_en\_p2\_i.

- The turn\_off\_addr\_ctrl\_drv\_i signal is a special PHY input that the memory controller can use to dynamically turn off the DRAM clock and command/address outputs during self-refresh to save power. If the controller does not support this feature, you can turn off the DRAM clock and command/address outputs using a software-programmable register bit if required. During memory initialization, the DDRPHY module asserts the turn\_off\_addr\_ctrl\_drv\_i signal internally to turn off these DRAM clock and command/address outputs during reset and CKE wait periods.

When controlling the timing of the turn\_off\_addr\_ctrl\_drv\_i assertion (logic 1) after issuing a self-refresh entry command on the DFI bus via a memory controller, follow the JEDEC spec for clock shut off after entering self-refresh mode. Add an additional 5 sclk\_o margin to ensure that the DFI command propagation through the PHY is satisfied before the assertion.

When de-asserting turn\_off\_addr\_ctrl\_drv\_i (logic 0) before issuing a self-refresh exit command, you need an additional 5 sclk\_o margin to ensure that turn\_off\_addr\_ctrl\_drv\_i propagates to the I/Os and the clock output turns on and stabilizes before issuing the self-refresh exit command on the DFI bus.

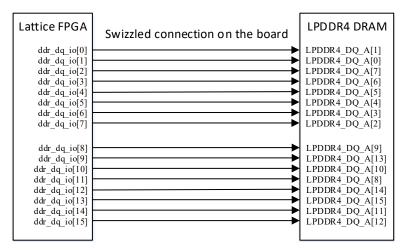

# 2.7. Bit Swizzle

The DDRPHY Foundation IP is hardened, the connection from the DDRPHY pins to the FPGA I/O are fixed. However, there are times that board routing can be improved significantly when the DQ bits can be swizzled or swapped around within the DQS group. For example, when using LPDDR4 device width of x16, you can swizzle each DQ bit within the lower byte and upper byte respectively, but you cannot swizzle the DQ bits from the lower byte to the upper byte and vice versa. Also, you cannot swizzle the lower byte DQS/DQ/DMI as a group to the upper byte DQS/DQ/DMI and vice versa because swizzling across the DQS group is not yet supported. This feature is currently only available for LPDDR4.

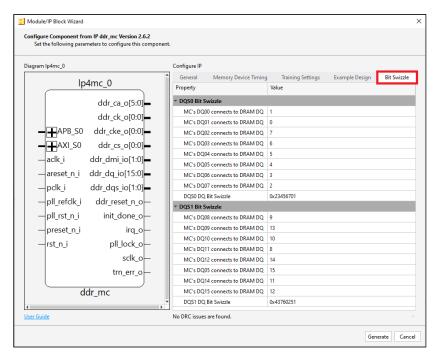

When you performed DQ bit swizzle on your board's FPGA to DRAM device connection, you should set the Bit Swizzle Settings accordingly so that the DDR Memory PHY module can perform the correct DQ reverse bit swizzle during training and during data access on the DFI I/F as shown in Figure 2.10. By implementing the DQ bit reverse swizzle, the Data on the DFI side will reach the DRAM device pins with the same data mapping as if no DQ bit swizzling happened.

Figure 2.10. Bit Swizzle Feature Block Diagram

# 2.7.1. DQ Bit Swizzle Example

An example DQ Bit Swizzled connection on the board is shown in Figure 2.11.

Figure 2.11. Example LPDDR4 DQ Bit Swizzle within DQS Group

You should set the corresponding settings in the IP GUI as shown in Figure 2.12. The Bit Swizzle Tab will appear when you check the option.

Figure 2.12. Example LPDDR4 Bit Swizzle Settings

# 3. IP Parameter Description

The following tables show and describe the configurable attributes of the DDRPHY IP Module. You can configure these attributes through the IP Catalog's Module/IP Block Wizard of the Lattice Radiant software. Refer to the Designing and Simulating the IP section of this user guide for information on how to configure and generate the DDRPHY Module.

# 3.1. DDR4 Parameters

This section describes the parameters available in the *General and Training Settings* tabs of the IP parameter editor for DDR4 interfaces.

# 3.1.1. DDR4 General

**Table 3.1. DDR4 General Attributes**

| Attribute            | Selectable Values  | Default   | Dependency on Other Attributes                                       |

|----------------------|--------------------|-----------|----------------------------------------------------------------------|

| Interface Type       | DDR4               | _         | -                                                                    |

| I/O Buffer Type      | POD12              | POD12     | Display only                                                         |

| Gearing Ratio        | 8:1                | 8:1       | Display only                                                         |

| Enable Side-Band ECC | Checked, Unchecked | Unchecked | -                                                                    |

|                      | 10                 | 10        | DDR Memory Frequency = 666 MHz                                       |

|                      | 10, 11, 12         | 12        | DDR Memory Frequency = 800 MHz                                       |

| Read Latency         | 12, 13, 14         | 12        | DDR Memory Frequency = 933 MHz                                       |

|                      | 14, 15, 16         | 14        | DDR Memory Frequency = 1,066 MHz                                     |

|                      | 15, 16, 17, 18     | 16        | DDR Memory Frequency = 1,200 MHz                                     |

|                      | 9                  | 9         | DDR Memory Frequency = 666 MHz                                       |

|                      | 9, 11              | 9         | DDR Memory Frequency = 800 MHz                                       |

| Write Latency        | 10, 12             | 10        | DDR Memory Frequency = 933 MHz                                       |

|                      | 11, 14             | 11        | DDR Memory Frequency = 1,066 MHz                                     |

|                      | 12, 16             | 12        | DDR Memory Frequency = 1,200 MHz                                     |

| Data Dua Midth       | 16, 32, 64         | 32        | _                                                                    |

| Data Bus Width       | 40, 72             | _         | If Enable Sideband ECC == Checked                                    |

| Enable Training CPU  | Checked            | Checked   | Display only Disabling the Internal RISC-V CPU is not yet supported. |

**Table 3.2. DDR4 Clock Settings Attributes**

| Attribute                            | Selectable Values         | Default | Dependency on Other Attributes                                           |

|--------------------------------------|---------------------------|---------|--------------------------------------------------------------------------|

| Enable PLL                           | Checked                   | Checked | Display only                                                             |

| DDR Memory Frequency (MHz)           | 666, 800, 933, 1066, 1200 | 800     | _                                                                        |

| System Clock Frequency (MHz)         | Calculated                | N/A     | Display only Calculated based on the selection for DDR Memory Frequency. |

| Reference Clock Frequency (MHz)      | 10-800                    | 100     | _                                                                        |

| DDR Memory Actual Frequency<br>(MHz) | Calculated                | N/A     | Display only Based on the selection for DDR Memory Frequency.            |

# Table 3.3. DDR4 Clock/Address/Command Attributes

| Attribute                     | Selectable Values | Default | Dependency on Other Attributes                            |

|-------------------------------|-------------------|---------|-----------------------------------------------------------|

| Number of Clocks              | 1, 2              | 1       | _                                                         |

| Number of Chip Selects (Rank) | 1, 2              | 1       | -                                                         |

| Address Width                 | 14                | 14      | Display only                                              |

| Number of Chip ODT            | 1, 2              | 1       | Based on the selection for <i>Number of Chip</i> Selects. |

| BA Width                      | 2                 | 2       | Display only                                              |

| BG Width                      | 2                 | 2       | Display only                                              |

# **Table 3.4. DDR4 General Definitions**

| Attribute                          | Description                                                                                                                                                                                      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Group                      |                                                                                                                                                                                                  |

| DDR Interface Type                 | Specifies the SDRAM Memory interface: DDR4.                                                                                                                                                      |

| I/O Buffer Type                    | I/O Standard for the memory interface signals. This is fixed to POD12 for DDR4 but the command/address/control signals should be terminated to VTT on the board. Please see note 2 of Table 4.5. |

| Gearing Ratio                      | Specifies the ratio relationship between the DDR data speed and the memory controller speed.                                                                                                     |

| Enable Sideband ECC                | Enables error-correction code (ECC) for single-bit error correction and double-bit error detection.                                                                                              |

| Enable DBI                         | Enables data bus inversion (DBI) for better signal integrity and read/write margins.                                                                                                             |

| Read Latency                       | Specifies the delay from issuing a read command to receiving of read data from SDRAM.  Set this based on the target DRAM's datasheet.                                                            |

| Write Latency                      | Specifies the delay from issuing a write command to providing of write data to SDRAM.  Set this based on the target DRAM's datasheet.                                                            |

| Data Bus Width                     | Specifies the total number of data pins in the memory interface.                                                                                                                                 |

| Enable Training CPU                | Enables RISC-V subsystem to support initialization and training of the memory device.  Disabling is not yet supported.                                                                           |

| Clock Settings Group               |                                                                                                                                                                                                  |

| Enable PLL                         | Enables PLL                                                                                                                                                                                      |

| DDR Memory Frequency (MHz)         | Speed at which the memory controller issues commands to the memory device.                                                                                                                       |

| System Clock Frequency (MHz)       | Speed to clock the memory controller.                                                                                                                                                            |

| Reference Clock Frequency (MHz)    | Indicates the PLL reference clock speed.                                                                                                                                                         |

| DDR Command Actual Frequency (MHz) | Specifies the actual operating frequency of the memory interface (calculated by the PLL – includes tolerance)                                                                                    |

| Clock/Address/Command Group        |                                                                                                                                                                                                  |

| Number of DDR Clocks               | Specifies the number of CK/CK# clock pairs to be driven to the SDRAM.                                                                                                                            |

| Number of Chip Selects             | Specifies the number of Chip Select (CS) signals to be driven to SDRAM.                                                                                                                          |

| Address Width                      | Specifies number of address pins in memory interface, dependent on the SDRAM density.                                                                                                            |

| Number of Chip ODT                 | Specifies the number of ODT bits.                                                                                                                                                                |

| BA Width                           | Specifies the row and column address of SDRAM.                                                                                                                                                   |

| BG Width                           | Specifies the bank group address of SDRAM.                                                                                                                                                       |

# 3.1.2. DDR4 Training Settings

**Table 3.5. DDR4 Training Settings Attributes**

| Attribute                              | Selectable Values | Default   | Dependency on Other Attributes  |

|----------------------------------------|-------------------|-----------|---------------------------------|

| DDR Clock Delay Value                  | 0-20              | 15        | _                               |

| DDR Clock Delay Value Incr/Decr        | Checked/Unchecked | Checked   | _                               |

| CS Delay Value                         | 0-20              | 15        | _                               |

| CS Delay Value Incr/Decr               | Checked/Unchecked | Checked   | _                               |

| Address Control Delay Value            | 0-20              | 4         | _                               |

| Address Clock Delay Value<br>Incr/Decr | Checked/Unchecked | Unchecked | _                               |

| Memory DQ_Vref Value for Rank0         | 0-114             | 25        | _                               |

| Memory DQ_Vref Value for Rank1         | 0-114             | 25        | Enabled when Number of Ranks==2 |

| MC DQS Grp<0,1> Vref Value             | 0-127             | 80        | _                               |

| MC DQS Grp<2,3> Vref Value             | 0-127             | 80        | Enabled when DDR Bus Width>=32  |

| MC DQS Grp<4,7> Vref Value             | 0-127             | 80        | Enabled when DDR Bus Width>=64  |

# Table 3.6. DDR4 PHY I/O Settings Attributes

| Attribute                 | Selectable Values                             | Default | Dependency on Other Attributes |

|---------------------------|-----------------------------------------------|---------|--------------------------------|

| CK/CS Slew Rate           | Slow, Fast                                    | Fast    | _                              |

| Command Address Slew Rate | Slow, Fast                                    | Fast    | _                              |

| DQS Slew Rate             | Slow, Fast                                    | Fast    | _                              |

| DQ/DMI Slew Rate          | Slow, Fast                                    | Fast    | _                              |

| MC CA Output Impedance    | 240 Ω, 120 Ω, 68 Ω, 60 Ω,<br>48 Ω, 40 Ω, 34 Ω | 34 Ω    | _                              |

| MC DQ Output Impedance    | 240 Ω, 120 Ω, 68 Ω, 60 Ω,<br>48 Ω, 40 Ω, 34 Ω | 34 Ω    | _                              |

| MC ODT Value              | 240 Ω, 120 Ω, 68 Ω, 60 Ω,<br>48 Ω, 40 Ω, 34 Ω | 60 Ω    | _                              |

# **Table 3.7. DDR4 Memory ODT Settings Attributes**

| Attribute      | Selectable Values                                              | Default            | Dependency on Other Attributes |

|----------------|----------------------------------------------------------------|--------------------|--------------------------------|

| RTT_WR Value   | Dynamic ODT OFF, RZQ/1,<br>RZQ/2, RZQ/3, Hi-Z                  | Dynamic ODT<br>OFF | _                              |

| RTT_NOM Value  | Disable, RZQ/1, RZQ/2,<br>RZQ/3, RZQ/4, RZQ/5,<br>RZQ/6, RZQ/7 | RZQ/5              | _                              |

| RTT_PARK Value | Disable, RZQ/1, RZQ/2,<br>RZQ/3, RZQ/4, RZQ/5,<br>RZQ/6, RZQ/7 | Disable            | _                              |

# **Table 3.8. DDR4 Training Settings Definitions**

| Attribute <sup>1</sup>          | Description                                                                                                                                                                  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Training Settings Group         |                                                                                                                                                                              |  |  |  |

| DDR Clock Delay Value           | Specifies the DDR clock delay so that the first DQS toggle is at CK = 0 during write leveling. It is recommended to increase this value if write leveling fails.             |  |  |  |

| DDR Clock Delay Value Incr/Decr | Specifies the adjustment direction. Checked: DDR Clock Delay Value is added to the ddr_ck_o signal. Unchecked: DDR Clock Delay Value is subtracted from the ddr_ck_o signal. |  |  |  |

| CS Delay Value                  | Specifies the DDR CS delay value.                                                                                                                                            |  |  |  |

© 2023-2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Attribute <sup>1</sup>                 | Description                                                                                                                                                                                                      |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CC Dalay Value Is as /Dags             | Specifies the adjustment direction.                                                                                                                                                                              |  |  |  |

| CS Delay Value Incr/Decr               | Checked: CS Delay Value is added to the ddr_cs_o signal.  Unchecked: CS Delay Value is subtracted from the ddr cs o signal.                                                                                      |  |  |  |

| Address Control Delay Value            | Specifies the DDR address/control signals delay. It is recommended to increase this value if the command bus training fails.                                                                                     |  |  |  |

| Address Clock Delay Value<br>Incr/Decr | Specifies the adjustment direction. Checked: Address Control Delay Value is added to the DDR address/control signals. Unchecked: Address Control Delay Value is subtracted from the DDR address/control signals. |  |  |  |

| Memory DQ_Vref Value for Rank<0,1>     | Specifies the DRAM DQ_Vref Value to be written to the DDR4 MR6 VR(DQ) and VREF(DQ) for Rank0/Rank1. When the register field TRN_OP_REG.mem_vref_training_en=0, this will be used as the final DRAM DQ Vref.      |  |  |  |

| MC DQS Grp<0,1> Vref Value             | Specifies the MC DQ_Vref Value for each DQS group when DQ_Vref training is disabled by setting TRN_OP_REG.mc_vref_training_en=0. The theoretical mV value is: Vref decimal value × 5 mV.                         |  |  |  |

| DDR4 MC I/O Settings                   |                                                                                                                                                                                                                  |  |  |  |

| CK/CS Slew Rate                        | Specifies the CK/CS driver strength.                                                                                                                                                                             |  |  |  |

| Command Address Slew Rate              | Specifies the CA driver strength.                                                                                                                                                                                |  |  |  |

| DQS Slew Rate                          | Specifies the DQS driver strength.                                                                                                                                                                               |  |  |  |

| DQ/DMI Slew Rate                       | Specifies the DQ/DMI driver strength.                                                                                                                                                                            |  |  |  |

| MC CA Output Impedance                 | Memory controller CA I/O impedance to reach VDDQ threshold.                                                                                                                                                      |  |  |  |

| MC DQ Output Impedance                 | Memory controller DQ I/O impedance to reach VDDQ threshold.                                                                                                                                                      |  |  |  |

| MC ODT Value                           | Memory controller termination resistance value at FPGA.                                                                                                                                                          |  |  |  |

| DDR4 Memory ODT Settings               |                                                                                                                                                                                                                  |  |  |  |

| RTT_WR Value                           | Specifies the RTT_WR value that is written to MR2 in DDR4 memory.                                                                                                                                                |  |  |  |

| RTT_NOM Value                          | Specifies the RTT_NOM value that is written to MR1 in DDR4 memory.                                                                                                                                               |  |  |  |