# LVDS Tunneling Protocol and Interface (LTPI) User Guide

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents.  |                                             | 3  |

|------------|---------------------------------------------|----|

| Figures    |                                             | 5  |

| Tables     |                                             | 7  |

| Abbreviati | ons in This Document                        | 8  |

| 1. Intro   | ductionduction                              | 9  |

| 1.1.       | Quick Facts                                 | 9  |

| 1.2.       | Features                                    | 9  |

| 1.3.       | Naming Conventions                          | 10 |

| 1.3.1      | . Nomenclature                              | 10 |

| 1.3.2      | . Signal Names                              | 10 |

| 2. Direc   | tory Structure and Files                    | 11 |

| 3. Funct   | tional Description                          | 12 |

| 3.1.       | Design Components                           | 15 |

| 3.1.1      | . LTPI                                      | 15 |

| 3.1.2      | . 25 MHz Generator                          | 19 |

| 3.1.3      | . Reset Timer                               | 20 |

| 3.1.4      |                                             |    |

| 3.1.5      | PLL Streamer Logic                          | 22 |

| 3.1.6      | 5                                           |    |

| 3.1.7      |                                             |    |

| 3.1.8      |                                             |    |

| 3.1.9      |                                             |    |

| 3.1.1      | O. APB Feedthrough (HPM Only)               |    |

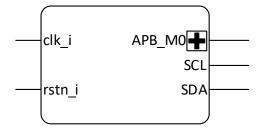

|            | 1. I2C-to-APB Bridge (SCM Only)             |    |

| 3.2.       | Clocking Scheme                             |    |

| 3.3.       | Reset Scheme                                |    |

| 3.4.       | DC-SCM LTPI IP Control and Status Registers |    |

| 3.5.       | GPIO Latency                                |    |

| 4. Signa   | l Description                               |    |

|            | g Constraints                               |    |

| 5.1.       | Clock Definitions                           |    |

| 5.2.       | Clocks, Resets, and False Paths             |    |

| 6. Modi    | fying the Reference Design                  |    |

| 6.1.       | Lattice Propel                              |    |

| 6.1.1      | '                                           |    |

| 6.1.2      |                                             |    |

| 6.1.3      | •                                           |    |

| 6.1.4      |                                             |    |

| 6.1.5      | •                                           |    |

| 6.2.       | Lattice Diamond                             |    |

| 6.2.1      |                                             |    |

| 6.2.2      | , •                                         |    |

| 6.2.3      |                                             |    |

| 6.2.4      |                                             |    |

| 6.2.5      |                                             |    |

| 6.3.       | Lattice Radiant                             |    |

| 6.3.1      |                                             |    |

| 6.3.2      | ·                                           |    |

| 6.3.3      |                                             |    |

| 6.3.4      | ·                                           |    |

|            | lating the Reference Design                 |    |

|            | · ·                                         |    |

| 7.1.       | Setting Up the Simulation                   | 6/ |

| 7.2.      | Simulation Details and Results  | 68 |

|-----------|---------------------------------|----|

| 7.2.      |                                 | 69 |

| 7.2.      |                                 |    |

| 7.2.      |                                 |    |

| 7.2.      | 4. I2C Test                     | 72 |

| 7.2.      |                                 |    |

| 8. Har    | dware Implementation            | 74 |

| 8.1.      | Requirements                    | 75 |

| 8.1.      | 1. DC-SCM 2.0 Requirements      | 75 |

| 8.1.      | 2. Lattice FPGA Requirements    | 76 |

| 9. Res    | ource Utilization               | 77 |

| 10. Con   | nmon Issues and Troubleshooting | 78 |

| 10.1.     | Link Not Reaching Active State  | 78 |

| 10.2.     | I2C Bus Hang                    | 79 |

| Reference | ces                             | 80 |

| Technica  | al Support Assistance           | 81 |

| Revision  | History                         | 82 |

# **Figures**

| Figure 2.1. Directory Structure                                       | 11 |

|-----------------------------------------------------------------------|----|

|                                                                       |    |

| Figure 3.1. LTPI State FlowFigure 3.2. SCM Block Diagram              |    |

|                                                                       |    |

| Figure 3.3. HPM Block Diagram                                         |    |

| Figure 3.4. LTPI (SCM) Block Diagram                                  |    |

| Figure 3.5. LTPI (HPM) Block Diagram                                  |    |

| Figure 3.6. 25 MHz Generator (MachXO3) Block Diagram                  |    |

| Figure 3.7. 25 MHz Generator (MachXO5-NX) Block Diagram               |    |

| Figure 3.8. Reset Timer Block Diagram                                 |    |

| Figure 3.9. Initialization Logic Block Diagram                        |    |

| Figure 3.10. PLL Streamer Logic (Wishbone) Block Diagram              |    |

| Figure 3.11. PLL Streamer Logic (APB) Block Diagram                   |    |

| Figure 3.12. EFB Block Diagram                                        |    |

| Figure 3.13. LTPI Clock Source (MachXO3/MachXO3D) Block Diagram       |    |

| Figure 3.14. LTPI Clock Source (MachXO5-NX) Block Diagram             |    |

| Figure 3.15. Clock Generator Block Diagram                            |    |

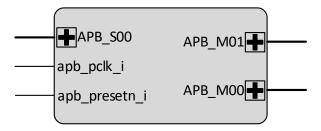

| Figure 3.16. APB Interconnect Block Diagram                           |    |

| Figure 3.17. APB Feedthrough Block Diagram                            |    |

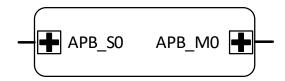

| Figure 3.18. I2C-to-APB Bridge Block Diagram                          |    |

| Figure 6.1. Open Design Button                                        |    |

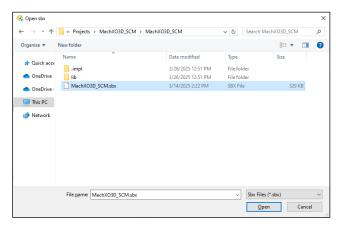

| Figure 6.2. Selecting the Lattice Propel™ Project                     |    |

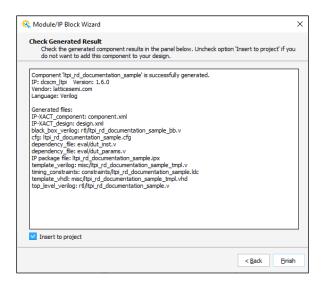

| Figure 6.3. Check Generated Result Window                             |    |

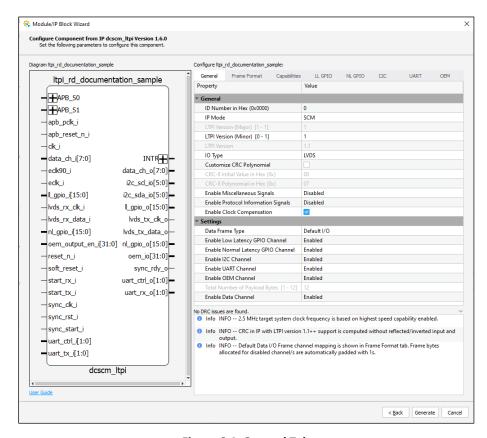

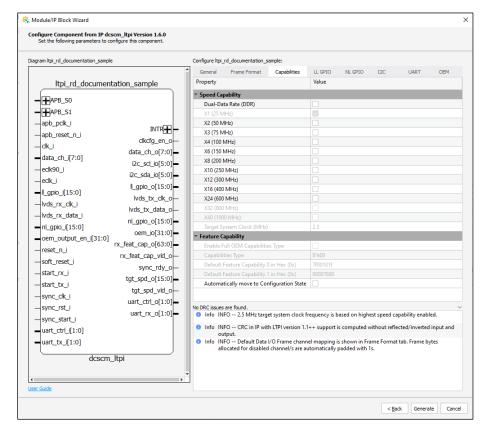

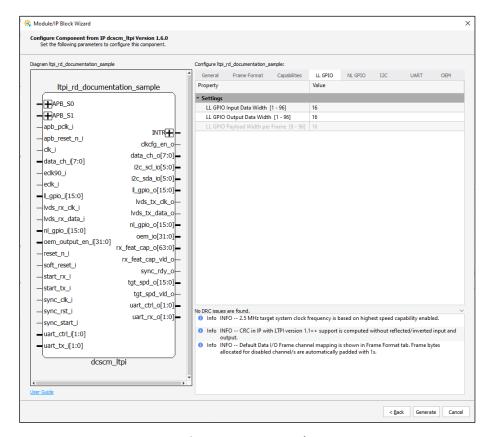

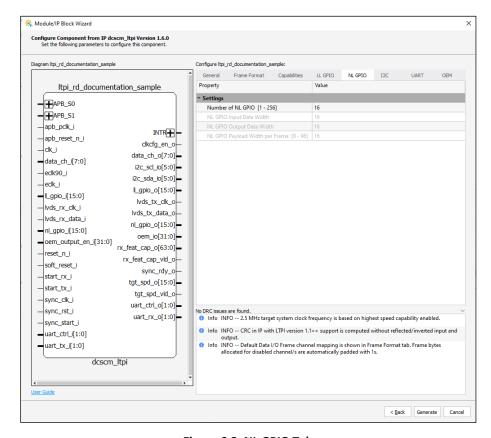

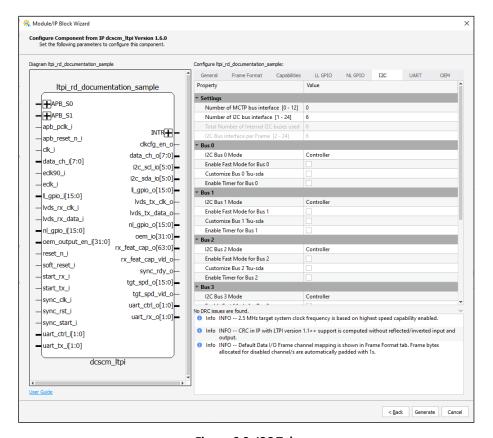

| Figure 6.4. General Tab                                               |    |

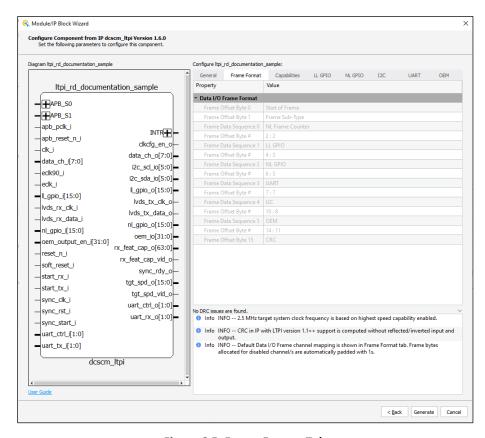

| Figure 6.5. Frame Format Tab                                          |    |

| Figure 6.6. Capabilities Tab                                          |    |

| Figure 6.7. LL GPIO Tab                                               |    |

| Figure 6.8. NL GPIO Tab                                               |    |

| Figure 6.9. I2C Tab                                                   |    |

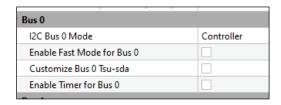

| Figure 6.10. Bus X Section for Controller                             | 50 |

| Figure 6.11. Bus X Section for Target                                 | 50 |

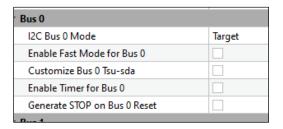

| Figure 6.12. Additional Bus X Section Options                         |    |

| Figure 6.13. I2C Timeout Formula and Sample Computation               |    |

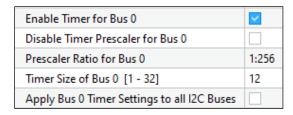

| Figure 6.14. UART Tab                                                 | 52 |

| Figure 6.15. UART Tab                                                 |    |

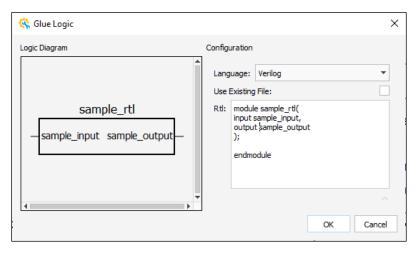

| Figure 6.16. RTL Glue Logic                                           | 54 |

| Figure 6.17. Using the RTL Box                                        |    |

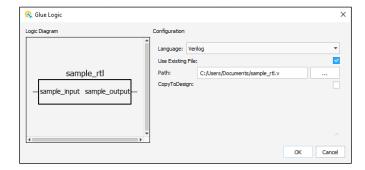

| Figure 6.18. Using an Existing RTL File                               | 54 |

| Figure 6.19. Connecting to Existing Modules                           | 55 |

| Figure 6.20. Selecting the Nets                                       | 55 |

| Figure 6.21. Connecting the Existing Nets of clk_o to External clk_i  | 55 |

| Figure 6.22. Connecting the Existing Net of lock_o to External rstn_i | 55 |

| Figure 6.23. Transferred Connections                                  | 56 |

| Figure 6.24. Selecting the Lattice Diamond Project                    | 56 |

| Figure 6.25. Selecting the Lattice Diamond Project                    | 57 |

| Figure 6.26. Device Selector Window                                   | 57 |

| Figure 6.27. Adding a Module via Drag and Drop                        |    |

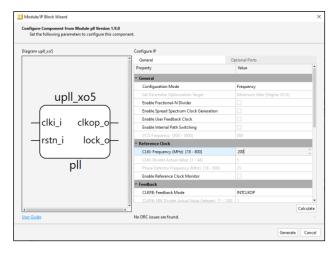

| Figure 6.28. Selecting the Lattice Diamond Project                    |    |

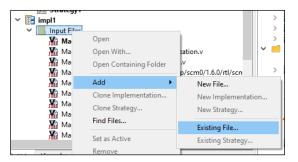

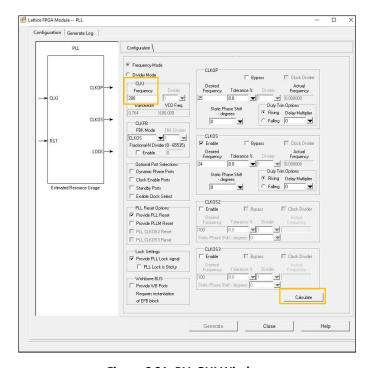

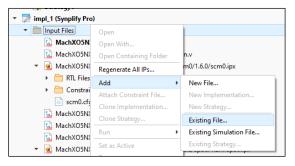

| Figure 6.29. Add Existing File Window                                 |    |

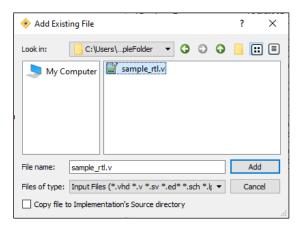

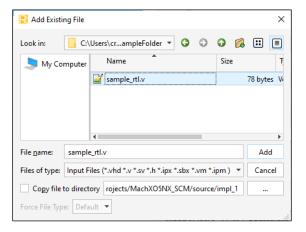

| Figure 6.30. UPLL File                                                |    |

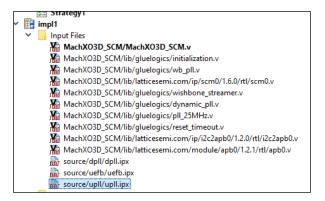

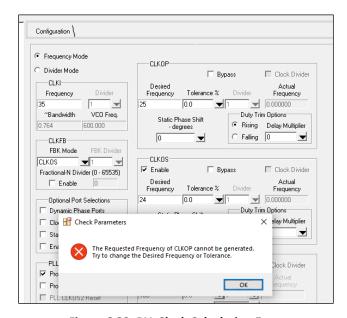

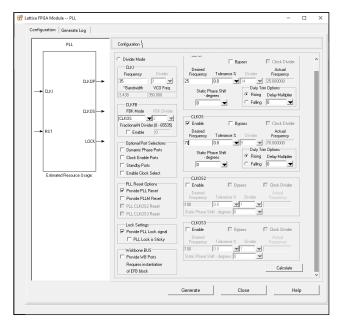

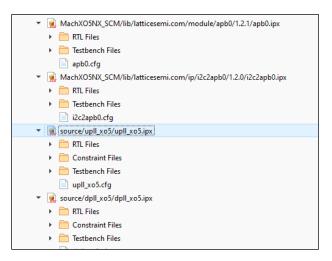

| Figure 6.31. PLL GUI Window                                           |    |

| Figure 6.32. PLL Clock Calculation Error                              |    |

| Figure 6.33. PLL Clock Calculation Done                               |    |

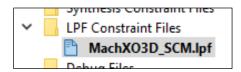

|                                                                       |    |

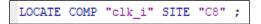

| Figure 6.34. Constraint File (*.lpf)                 |    |

|------------------------------------------------------|----|

| Figure 6.35. IO Properties Example                   | 61 |

| Figure 6.36. IO Location Example                     |    |

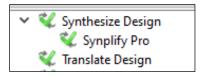

| Figure 6.37. Lattice Diamond Synthesis               |    |

| Figure 6.38. Open Spreadsheet View                   | 61 |

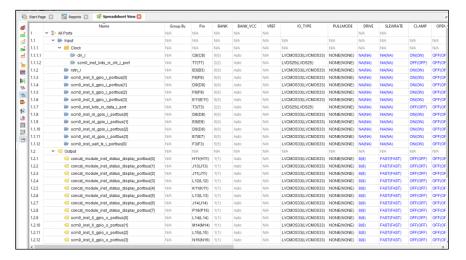

| Figure 6.39. Spreadsheet View                        | 62 |

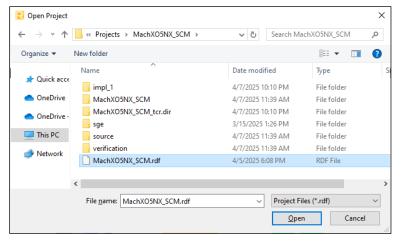

| Figure 6.40. Selecting the Lattice Radiant Project   | 62 |

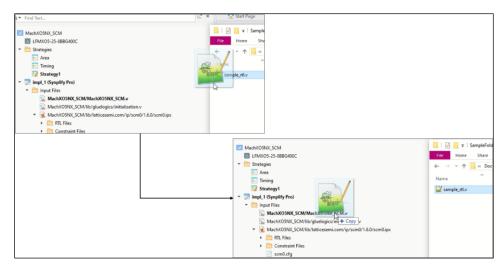

| Figure 6.41. Adding a Module via Drag and Drop       | 63 |

| Figure 6.42. Selecting the Lattice Diamond™ Project  |    |

| Figure 6.43. Add Existing File Window                |    |

| Figure 6.44. UPLL File                               |    |

| Figure 6.45. PLL GUI Window                          |    |

| Figure 6.46. PLL Clock Calculation Done              |    |

| Figure 6.47. Lattice Radiant Constraint File (*.pdc) | 65 |

| Figure 6.48. Lattice Radiant IO Properties Example   | 65 |

| Figure 6.49. Lattice Radiant™ IO Location Example    | 65 |

| Figure 6.50. Lattice Radiant Synthesis               | 65 |

| Figure 6.51. Open Device Constraint Editor           | 65 |

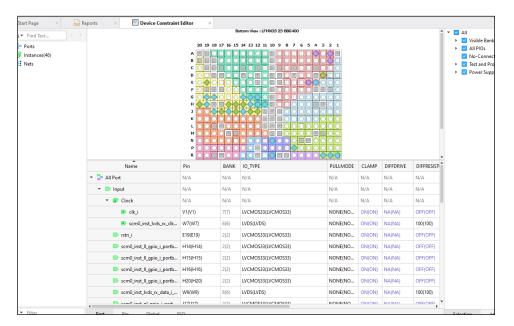

| Figure 6.52. Device Constraint Editor                | 66 |

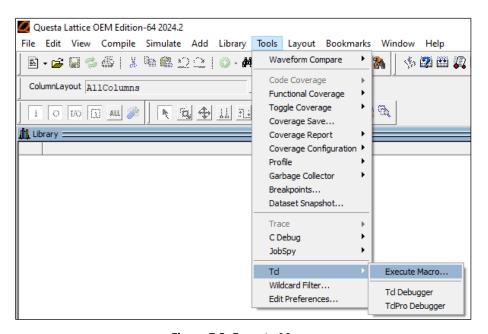

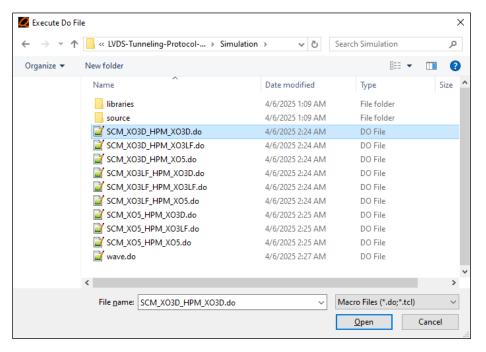

| Figure 7.1. Simulation Do File                       | 67 |

| Figure 7.2. Execute Macro                            | 67 |

| Figure 7.3. Execute Macro                            | 68 |

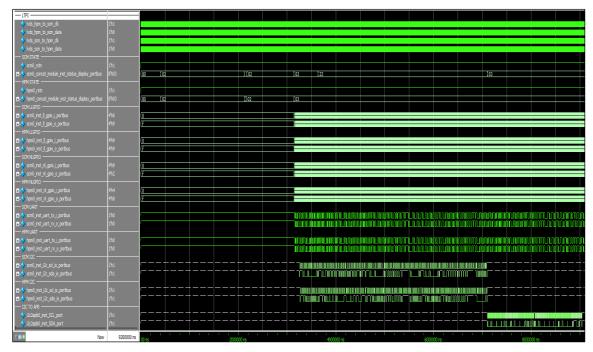

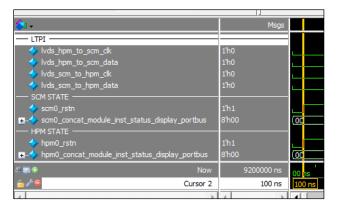

| Figure 7.4. Simulation Wave View                     | 68 |

| Figure 7.5. Reset Release                            | 69 |

| Figure 7.6. LTPI Base Speed                          | 69 |

| Figure 7.7. PHY Aligned                              | 69 |

| Figure 7.8. Base Speed to Target Speed Transition    | 70 |

| Figure 7.9. Link Training Done                       | 70 |

| Figure 7.10. Link Established Message                | 70 |

| Figure 7.11. GPIO Test Flow                          | 71 |

| Figure 7.12. GPIO Test Console Messages              | 71 |

| Figure 7.13. UART Test Flow                          | 72 |

| Figure 7.14. UART Test Console Messages              | 72 |

| Figure 7.15. I2C Test Flow                           | 72 |

| Figure 7.16. I2C Test Console Messages               | 72 |

| Figure 7.17. CSR Test Flow                           | 73 |

| Figure 7.18. CSR Test Console Messages               |    |

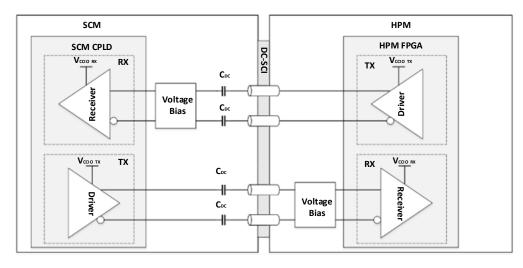

| Figure 8.1. LVDS Link                                | 75 |

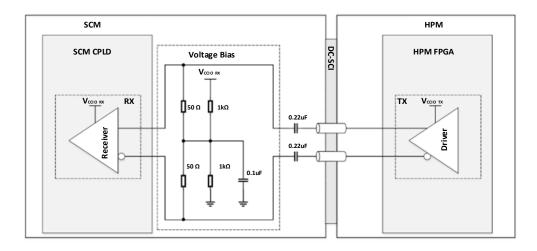

| Figure 8.2. LVDS Link                                | 76 |

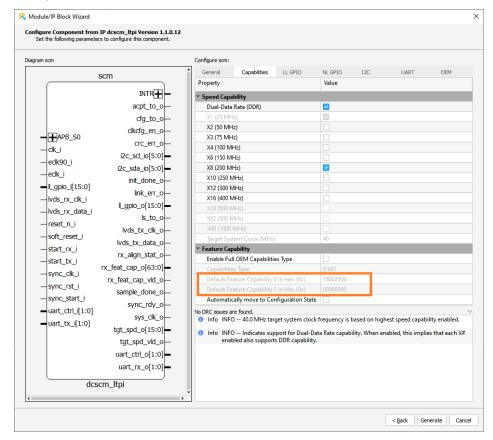

| Figure 10.1. Feature Capabilities                    |    |

| Figure 10.2. I2C_BUS_RST Register                    | 79 |

|                                                      |    |

# **Tables**

| Table 1.1. Summary of the Reference Design       | 9  |

|--------------------------------------------------|----|

| Table 2.1. File List                             |    |

| Table 3.1. LTPI Clock Source Signals             | 16 |

| Table 3.2. 25 MHz Generator Signals              | 20 |

| Table 3.3. 25 MHz Generator Implementation       | 20 |

| Table 3.4. Reset Timer Signals                   | 21 |

| Table 3.5. Initialization Logic Signals          | 21 |

| Table 3.6. PLL Streamer Logic Implementation     | 22 |

| Table 3.7. PLL Streamer Logic Signals            | 22 |

| Table 3.8. EFB Signals                           | 25 |

| Table 3.9. LTPI Clock Source Signals             | 26 |

| Table 3.10. LTPI Clock Source Implementation     | 27 |

| Table 3.11. Clock Generator Signals              | 27 |

| Table 3.12. APB Interconnect Signals             | 28 |

| Table 3.13. APB Feedthrough Signals              | 29 |

| Table 3.14. I2C-to-APB Bridge Signals            | 29 |

| Table 3.15. DC-SCM LTPI IP Registers             | 30 |

| Table 4.1. SCM Top Module Signals                | 37 |

| Table 4.2. HPM Top Module Signals                | 38 |

| Table 8.1. Pin Assignments                       |    |

| Table 8.2. LTPI Clock Source Implementation      | 75 |

| Table 8.3. LVDS Electrical Requirements          | 76 |

| Table 9.1. Resource Utilization for Demo Designs | 77 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviations    | Definition                                  |

|------------------|---------------------------------------------|

| APB              | Advanced Peripheral Bus                     |

| CDC              | Clock Domain Crossing                       |

| CRC              | Cycle Redundancy Check                      |

| CSR              | Control and Status Register                 |

| DC-SCI           | Datacenter-ready Secure Control Interface   |

| DC-SCM           | Datacenter-ready Secure Control Module      |

| DDR              | Double Data Rate                            |

| EFB              | Embedded Function Block                     |

| GPIO             | General Purpose Input/Output                |

| НРМ              | Host Processor Module                       |

| I/O              | Input/Output                                |

| I <sup>2</sup> C | Inter-Integrated Circuit                    |

| IP               | Intellectual Property                       |

| LED              | Light-Emitting Diode                        |

| LLGPIO           | Low Latency General Purpose Input/Output    |

| LTPI             | LVDS Tunneling Protocol and Interface       |

| LVDS             | Low Voltage Differential Signaling          |

| MCSI             | Multi-Channel Serial Interface              |

| MCTP             | Management Component Transport Protocol     |

| NLGPIO           | Normal Latency General Purpose Input/Output |

| OEM              | Original Equipment Manufacturer             |

| RTL              | Register Transfer Level                     |

| Rx               | Receiver                                    |

| SDR              | Single Data Rate                            |

| Tx               | Transmitter                                 |

| UART             | Universal Asynchronous Receiver/Transmitter |

# 1. Introduction

The DC-SCM 2.0 LTPI Reference Design offers multiple solution templates utilizing the current LVDS Tunneling Protocol Interface (LTPI) IP. This IP complies with Datacenter-ready Secure Control Module (DC-SCM) 2.0 LTPI specifications and features a standardized Datacenter-ready Secure Control Interface (DC-SCI). It aggregates multiple data channels, including I2C, GPIO, and UART to enhance flexibility in a customer's system and board design.

## 1.1. Quick Facts

You can download the reference design files in the LVDS Tunneling Protocol and Interface Reference Design web page.

Table 1.1. Summary of the Reference Design

| General               | Supported Devices          | MachXO3™, MachXO3D™, and MachXO5-NX™                                                                                                                                                                             |  |  |

|-----------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General               | Source code format         | Verilog                                                                                                                                                                                                          |  |  |

|                       | Functional simulation      | Performed                                                                                                                                                                                                        |  |  |

| Simulation            | Timing simulation          | Not performed                                                                                                                                                                                                    |  |  |

| Simulation            | Test bench                 | Available                                                                                                                                                                                                        |  |  |

|                       | Test bench format          | Verilog                                                                                                                                                                                                          |  |  |

| Software Requirements | Software tool and version  | Lattice Diamond™ version 3.14 for the MachXO3, MachXO3D devices  Lattice Radiant™ version 2024.2 for the MachXO5-NX devices  Lattice Propel™ version 2024.2  Synplify Pro®  Questa Lattice OEM Edition-64 2024.2 |  |  |

|                       | IP version (if applicable) | DC-SCM LTPI 1.6.0 APB Interconnect 1.2.1 APB Feedthrough 1.1.0 I2C to APB Bridge RD 1.2.0                                                                                                                        |  |  |

| Hardware Requirements | Board                      | MachXO3LF Starter Kit MachXO3D Breakout Board MachXO5-NX Development Board                                                                                                                                       |  |  |

|                       | Cable                      | USB Mini-B to USB-A Cable (provided for all boards except the LTPI board)                                                                                                                                        |  |  |

#### 1.2. Features

Key features of the LTPI reference design include:

- Support for DC-SCM 2.0 LTPI version 1.1 (Oct 2023)

- Link initialization, discovery, and negotiation

- Support for multi-channel serial interface

- Support for LVDS

- Aggregation/disaggregation of up to five channels in total

- Support for GPIO, I2C, UART, OEM, and data channel aggregation

- Configurable I2C interface as single-node (controller or target only) or multi-node (supports both external controller and target)

- Each multi-node I2C bus uses 1 payload byte, equivalent to two single-node I2C buses

- Support for up to 1,200 Mbps LVDS data rate (up to 800 Mbps on the MachXO3 and MachXO3D devices; up to 1,200 Mbps on the MachXO5-NX devices)

- Support for AMBA 3 APB Protocol version 1.0 for register access of the soft IP and data channel:

- PREADY signal indicates completion of an APB transfer

- PSLVERR signal indicates failure of a transfer, supported only in data channel-related access

# 1.3. Naming Conventions

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.3.2. Signal Names

Signal names that have:

- \_n are active low (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

# 2. Directory Structure and Files

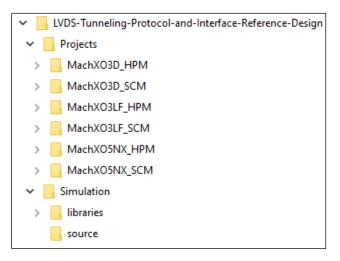

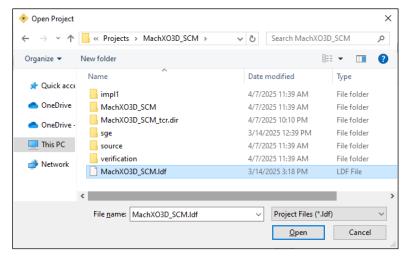

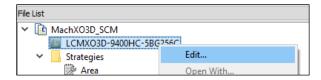

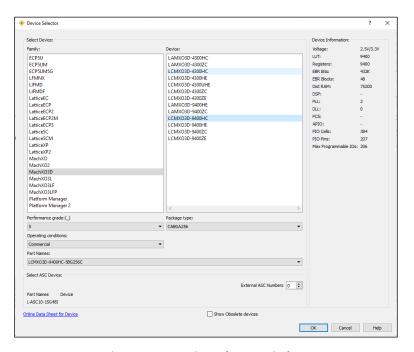

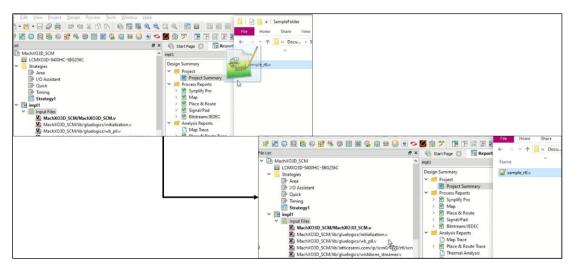

Figure 2.1 shows the directory structure.

Figure 2.1. Directory Structure

Table 2.1 shows the list of files included in the reference design package.

Table 2.1. File List

| Subfolder  | Description                                                                                           |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------|--|--|--|

|            | This subfolder contains pre-built projects, subcategorized by the function and the Lattice FPGA used. |  |  |  |

|            | MachXO3D HPM                                                                                          |  |  |  |

|            | MachXO3D SCM                                                                                          |  |  |  |

| Projects   | MachXO3LF HPM                                                                                         |  |  |  |

|            | MachXO3LF SCM                                                                                         |  |  |  |

|            | MachXO5NX HPM                                                                                         |  |  |  |

|            | MachXO5NX_SCM                                                                                         |  |  |  |

|            | Each project has been tested via simulation and on hardware.                                          |  |  |  |

|            | This subfolder contains the simulation files used for functional simulation.                          |  |  |  |

|            | Libraries: pre-built simulation libraries for the Lattice FPGA devices                                |  |  |  |

|            | Source: contains the test bench RTL and other submodules needed for simulation                        |  |  |  |

|            | Additionally, this subfolder *.do files used to run preset functional simulations. These              |  |  |  |

|            | files are named in this format:                                                                       |  |  |  |

|            | SCM_ <device_used_for_scm>_HPM_<device_used_for_hpm>.do</device_used_for_hpm></device_used_for_scm>   |  |  |  |

|            | SCM_XO3D_HPM_XO3D.do                                                                                  |  |  |  |

|            | SCM_XO3D_HPM_XO3LF.do                                                                                 |  |  |  |

| Simulation | SCM_XO3D_HPM_XO5.do                                                                                   |  |  |  |

|            | SCM_XO3LF_HPM_XO3D.do                                                                                 |  |  |  |

|            | SCM_XO3LF_HPM_XO3LF.do                                                                                |  |  |  |

|            | SCM_XO3LF_HPM_XO5.do                                                                                  |  |  |  |

|            | SCM_XO5_HPM_XO3D.do                                                                                   |  |  |  |

|            | SCM_XO5_HPM_XO3LF.do                                                                                  |  |  |  |

|            | SCM_XO5_HPM_XO5.do                                                                                    |  |  |  |

|            | wave.do – this is invoked by the other *.do files to add preset signals on the Wave                   |  |  |  |

|            | view of the simulator                                                                                 |  |  |  |

# 3. Functional Description

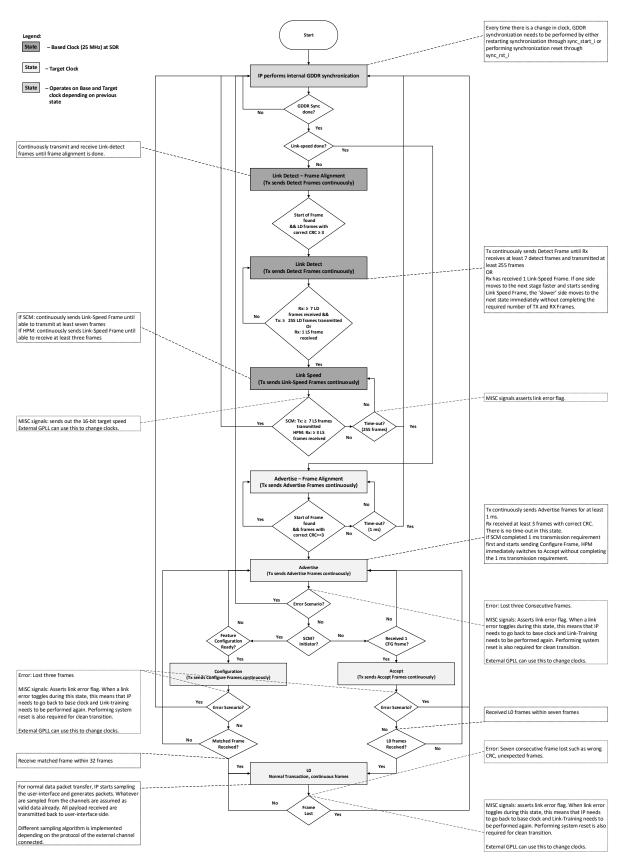

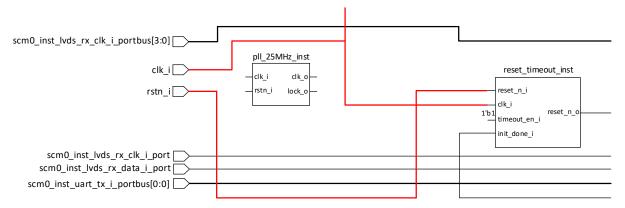

The reference design provides you with a ready-to-use LTPI template for both SCM and HPM. The design manages all initialization requirements for SCM and HPM to establish a working link, following the LTPI state flow internally, as shown in Figure 3.1. It also provides access to the LTPI IP's Control and Status Registers via the I2C interface.

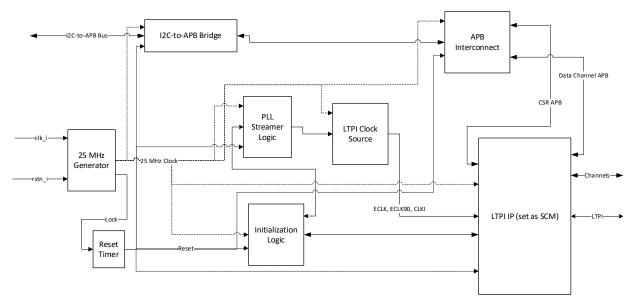

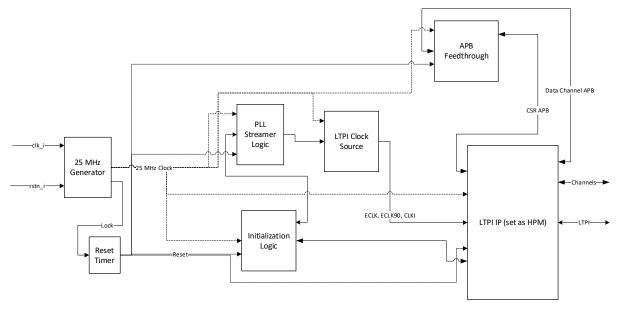

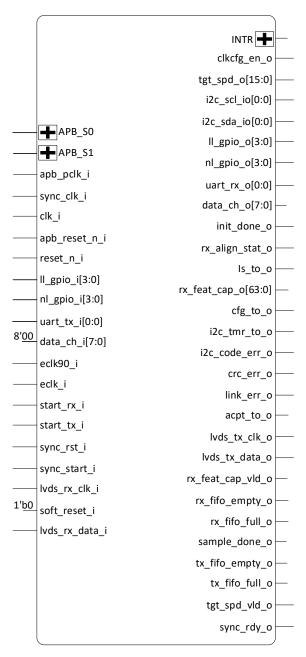

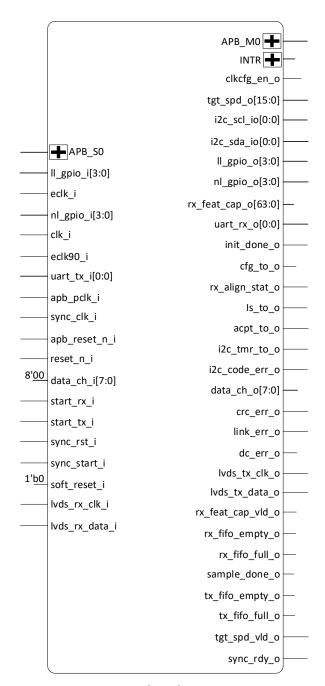

Figure 3.2 and Figure 3.3 illustrate the implementation of the DC-SCM LTPI IP within the reference design. Some modules differ between the HPM and SCM implementations based on their intended usage. Additionally, because the design supports multiple target devices, some modules vary for each device. These differences will be discussed in the subsection of each block.

The 25 MHz clock from the 25 MHz Generator module serves as the primary system clock unless specified otherwise. The reset from the Reset Timer is also used as the primary reset net unless specified otherwise.

Figure 3.1. LTPI State Flow

Figure 3.2. SCM Block Diagram

Figure 3.3. HPM Block Diagram

## 3.1. Design Components

This section outlines the module components of the top-level module in the reference design. For the signal description of the top-level module, refer to the Signal Description section.

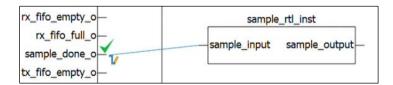

#### 3.1.1. LTPI

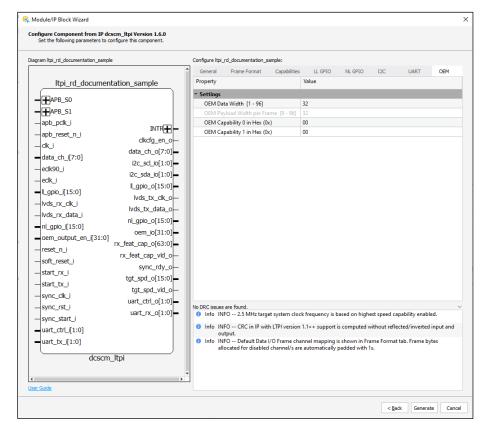

This module utilizes the DC-SCM LTPI IP from Lattice Propel. Depending on the configuration, it can be either an SCM or HPM instance.

Module Name: scm0 (for SCM instance) or hpm0 (for HPM instance).

Figure 3.4. LTPI (SCM) Block Diagram

Figure 3.5. LTPI (HPM) Block Diagram

**Table 3.1. LTPI Clock Source Signals**

| Table 3.1. Ell Telock Source Signals |              |       |               |                                                                                                     |  |  |

|--------------------------------------|--------------|-------|---------------|-----------------------------------------------------------------------------------------------------|--|--|

| Port Name                            | Input/Output | Width | Default Value | Description                                                                                         |  |  |

| System Signals                       |              |       |               |                                                                                                     |  |  |

| clk_i                                | Input        | 1     | N/A           | The LTPI main clock connects to either CLKOS2 of LTPI clock source or sys_clk_o of clock generator. |  |  |

| reset_n_i                            | Input        | 1     | N/A           | Active low reset.                                                                                   |  |  |

| soft_reset_i                         | Input        | 1     | 1'b0          | LTPI Active high soft reset.                                                                        |  |  |

| eclk_i                               | Input        | 1     | N/A           | The ECLK input connects to either CLKOP or clkop_o of the LTPI clock source.                        |  |  |

| Port Name            | Input/Output | Width | Default Value | Description                                                                                                  |

|----------------------|--------------|-------|---------------|--------------------------------------------------------------------------------------------------------------|

| eclk90_i             | Input        | 1     | N/A           | The ECLK90 input connects to either CLKOS or clkos_o of the LTPI clock source.                               |

| INTR                 | Interrupt    | N/A   | N/A           | Interrupt interface. Unused.                                                                                 |

| PHY Initialization S | Signals      |       |               |                                                                                                              |

| sync_clk_i           | Input        | 1     | N/A           | PHY synchronization clock. 25 MHz clock input.                                                               |

| start_rx_i           | Input        | 1     | N/A           | Initialize Rx PHY. Connects to start_rx_o of initialization logic.                                           |

| start_tx_i           | Input        | 1     | N/A           | Initialize Tx PHY. Connects to start_tx_o of initialization logic.                                           |

| sync_rst_i           | Input        | 1     | N/A           | PHY reset. Connects to sync_rst_o of initialization logic.                                                   |

| sync_start_i         | Input        | 1     | N/A           | The PHY synchronization start trigger connects to sync_start_o of the initialization logic.                  |

| sync_rdy_o           | Output       | 1     | 1'b0          | The PHY synchronization ready connects to sync_rdy_i of the initialization logic.                            |

| LTPI Signals         |              |       |               |                                                                                                              |

| lvds_rx_clk_i        | Input        | 1     | N/A           | LVDS Receive Clock. Connects to scm0_inst_lvds_rx_clk_i_port or hpm0_inst_lvds_rx_clk_i_port (Top Module).   |

| lvds_rx_data_i       | Input        | 1     | N/A           | LVDS Receive Data. Connects to scm0_inst_lvds_rx_data_i_port or hpm0_inst_lvds_rx_data_i_port (Top Module).  |

| lvds_tx_clk_o        | Output       | 1     | N/A           | LVDS Transmit Clock. Connects to scm0_inst_lvds_tx_clk_o_port or hpm0_inst_lvds_tx_clk_o_port (Top Module).  |

| lvds_tx_data_o       | Output       | 1     | N/A           | LVDS Transmit Data. Connects to scm0_inst_lvds_tx_data_o_port or hpm0_inst_lvds_tx_data_o_port (Top Module). |

| Low Latency GPIO     | Channel      |       |               |                                                                                                              |

| ll_gpio_i            | Input        | 4     | N/A           | Low Latency Input. Connect scm0_inst_Il_gpio_i_portbus or hpm0_inst_Il_gpio_i_portbus (Top Module).          |

| Il_gpio_o            | Output       | 4     | N/A           | Low Latency Output. Connect scm0_inst_ll_gpio_o_portbus or hpm0_inst_ll_gpio_o_portbus (Top Module).         |

| Normal Latency GI    | PIO Channel  |       |               |                                                                                                              |

| nl_gpio_i            | Input        | 4     | N/A           | Low Latency Input. Connect scm0_inst_nl_gpio_i_portbus or hpm0_inst_nl_gpio_i_portbus (Top Module).          |

| nl_gpio_o            | Output       | 4     | N/A           | Low Latency Output. Connect scm0_inst_nl_gpio_o_portbus or hpm0_inst_nl_gpio_o_portbus (Top Module).         |

| <b>UART Channel</b>  |              |       |               |                                                                                                              |

| uart_tx_i            | Input        | 1     | N/A           | UART Tx pin. Connect scm0_inst_uart_tx_i_portbus or hpm0_inst_uart_tx_i_portbus.                             |

| uart_rx_o            | Output       | 1     | N/A           | UART Rx pin. Connect scm0_inst_uart_rx_o_portbus or hpm0_inst_uart_rx_o_portbus (Top Module).                |

| I2C Channel          |              |       |               |                                                                                                              |

| i2c_scl_io           | Inout        | 1     | N/A           | I2C Clock pin. Connects to scm0_inst_i2c_scl_io_portbus or hpm0_inst_i2c_scl_io_portbus (Top Module).        |

| i2c_sda_io           | Inout        | 1     | N/A           | I2C Data pin. Connects to scm0_inst_i2c_sda_io_portbus or hpm0_inst_i2c_sda_io_portbus (Top Module).         |

| Data Channel         |              |       |               |                                                                                                              |

| data_ch_i            | Input        | 8     | 8'h00         | Data channel input tag. Unused.                                                                              |

| data_ch_o            | Output       | 8     | 8'h00         | Data channel output tag. Unused.                                                                             |

| APB_S1               | APB IF       | N/A   | N/A           | Data Channel Completer Interface (SCM only). Connects to APB_M00 of APB Interconnect.                        |

| APB_M0               | APB IF       | N/A   | N/A           | Data Channel APB Requester Interface. Connects to APB_SO of APB Feedthrough.                                 |

| Port Name          | Input/Output | Width | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|--------------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APB Interface      |              | •     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| apb_pclk_i         | Input        | 1     | N/A           | APB interface clock. 25 MHz clock input.                                                                                                                                                                                                                                                                                                                                                                                                         |

| apb_reset_n_i      | Input        | 1     | N/A           | Active-low reset.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| APB_S0             | APB IF       | N/A   | N/A           | CSR APB Completer Interface. Connects to APB_M01 of APB Interconnect (SCM only) or APB_M0 of APB Feedthrough (HPM only).                                                                                                                                                                                                                                                                                                                         |

| Miscellaneous Sign | nals         |       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| clkcfg_en_o        | Output       | 1     | N/A           | Clock Reconfiguration Enabled Flag. It indicates that the LTPI clocks can now change from Base Speed to Target Speed. It Connects to clkcfg_en_i of Initialization Logic and PLL Streamer Logic.                                                                                                                                                                                                                                                 |

| tgt_spd_o          | Output       | 32    | N/A           | Target Speed Status. It Indicates the highest common available frequency between SCM and HPM. Note that only one bit can be high for bits 0-9.  Bit 15: DDR if 1, SDR if 0  Bit 14-10: Reserved  Bit 9: 600 MHz  Bit 8: 400 MHz  Bit 7: 300 MHz  Bit 6: 250 MHz  Bit 6: 250 MHz  Bit 4: 150 MHz  Bit 4: 150 MHz  Bit 2: 75 MHz  Bit 1: 50 MHz  Bit 1: 50 MHz  Bit 0: 25 MHz  It Connects to tgt_spd_i of PLL Streamer Logic and Clock Generator. |

| rx_feat_cap_o      | Output       | 64    | N/A           | Received Feature Capabilities. Unconnected.                                                                                                                                                                                                                                                                                                                                                                                                      |

| init_done_o        | Output       | 1     | N/A           | Link Established Flag. Connects to concat_module_inst_status_display_portbus[0] (Top Module).                                                                                                                                                                                                                                                                                                                                                    |

| cfg_to_o           | Output       | 1     | N/A           | Configuration State Timeout. Only active for SCM. Connects to concat_module_inst_status_display_portbus[3] (Top Module, SCM only).                                                                                                                                                                                                                                                                                                               |

| rx_align_stat_o    | Output       | 1     | N/A           | PHY Rx Alignment Done Flag. Connects to concat_module_inst_status_display_portbus[1] (Top Module).                                                                                                                                                                                                                                                                                                                                               |

| ls_to_o            | Output       | 1     | N/A           | Link Speed State Timeout. Connects to concat_module_inst_status_display_portbus[2] (Top Module).                                                                                                                                                                                                                                                                                                                                                 |

| acpt_to_o          | Output       | 1     | N/A           | Accept State Timeout. Only active for HPM. Connects to concat_module_inst_status_display_portbus[3] (Top Module, HPM only).                                                                                                                                                                                                                                                                                                                      |

| Port Name         | Input/Output | Width | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|--------------|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i2c_tmr_to_o      | Output       | 1     | N/A           | <ul> <li>I2C Timer Timeout/Reset Flag. Inactive (low) when the I2C channel is disabled.</li> <li>When the I2C channel is enabled, this is only valid if any of the following is true:         <ul> <li>Enable Timer for Bus # option of any of the available I2C bus is checked; or</li> <li>Generate STOP on Bus # Reset option of any of the available Target I2C bus is checked.</li> </ul> </li> <li>This indicates that a timeout or bus reset occurred on any of the active I2C channels and that the bus recovery is successful. It Connects to concat_module_inst_status_display_portbus[4] (Top Module).</li> </ul> |

| i2c_code_err_o    | Output       | 1     | N/A           | Invalid I2C Event Received Flag. Connects to concat_module_inst_status_display_portbus[5] (Top Module).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| crc_err_o         | Output       | 1     | N/A           | Frame CRC Error. The following number of consecutive CRC Errors will result in a link error:  Advertise State – 3  Active State – 7  Connects to concat_module_inst_status_display_portbus[6] (Top Module).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| link_err_o        | Output       | 1     | N/A           | Link Error Flag. It indicates that the link between SCM and HPM is lost. It Connects to concat_module_inst_status_display_portbus[7] (Top Module).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| dc_err_o          | Output       | 1     | N/A           | Data Channel Error Flag. Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| rx_feat_cap_vld_o | Output       | 1     | N/A           | Received Feature Capability Valid Flag. Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rx_fifo_empty_o   | Output       | 1     | N/A           | Rx FIFO Empty Flag. Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| sample_done_o     | Output       | 1     | N/A           | Sample Done Flag. This indicates that the IP is done sampling a frame. Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| tx_fifo_empty_o   | Output       | 1     | N/A           | Tx FIFO Empty Flag. Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| tgt_spd_vld_o     | Output       | 1     | N/A           | Target Speed Valid Flag. Connects to tgt_spd_vld_i of PLL Streamer Logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

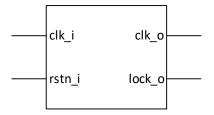

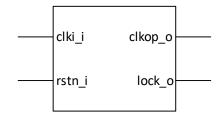

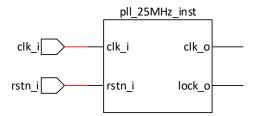

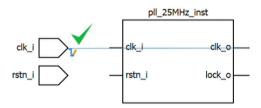

#### 3.1.2. 25 MHz Generator

This module serves as a wrapper for a PLL instance that accepts an external clock input and converts it into a 25 MHz clock. This module can be omitted if an external 25 MHz clock is available.

Table 3.3 for the difference in implementation across the three devices.

Figure 3.6. 25 MHz Generator (MachXO3) Block Diagram

Figure 3.7. 25 MHz Generator (MachXO5-NX) Block Diagram

Table 3.2. 25 MHz Generator Signals

| Port Name  | Input/Output     | Width | Default Value | Description                                                                                                     |  |  |  |  |

|------------|------------------|-------|---------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MachXO3/Ma | MachXO3/MachXO3D |       |               |                                                                                                                 |  |  |  |  |

| clk_i      | Input            | 1     | N/A           | External clock input. 12 MHz for MachXO3 and MachXO3D. 125 MHz for MachXO5-NX                                   |  |  |  |  |

|            |                  |       |               | Connects to clk_i (Top Module).                                                                                 |  |  |  |  |

| rstn_i     | Input            | 1     | N/A           | Active-low reset. Coonects to rstn_i (Top Module).                                                              |  |  |  |  |

| clk_o      | Output           | 1     | N/A           | 25 MHz clock output.                                                                                            |  |  |  |  |

| lock_o     | Output           | 1     | 1'b0          | PLL lock. Connects to reset_n_i input of the reset timer.                                                       |  |  |  |  |

| MachXO5-NX | ·                |       | ·             |                                                                                                                 |  |  |  |  |

| clki_i     | Input            | 1     | N/A           | External clock input. 12 MHz for MachXO3 and MachXO3D.  125 MHz for MachXO5-NX  Connects to clk i (Top Module). |  |  |  |  |

| rstn_i     | Input            | 1     | N/A           | Active-low reset. Coonects to rstn_i (Top Module).                                                              |  |  |  |  |

| clkop_o    | Output           | 1     | N/A           | 25 MHz clock output.                                                                                            |  |  |  |  |

| lock_o     | Output           | 1     | 1'b0          | PLL lock. Connects to reset_n_i input of the reset timer.                                                       |  |  |  |  |

Table 3.3. 25 MHz Generator Implementation

| Target Device | Module Name   | PLL Instance |

|---------------|---------------|--------------|

| MachXO3       | pll_25MHz     | upll         |

| MachXO3D      | pll_25MHz     | upll         |

| MachXO5-NX    | pll_25MHz_xo5 | upll_xo5     |

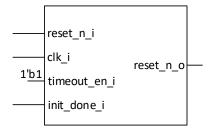

#### 3.1.3. Reset Timer

This module utilizes both the PLL lock from the 25 MHz Generator (or external reset if 25 MHz Generator is not used) and the output of an internal watchdog timer to generate the system's reset net. If the timer is disabled (timeout\_en\_i = 0), the output reset source is equal to the input reset.

Module Name: reset\_timeout

Figure 3.8. Reset Timer Block Diagram

© 2022-2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

**Table 3.4. Reset Timer Signals**

| Port Name    | Input/Output | Width | Default Value | Description                                                                                                                                                 |

|--------------|--------------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset_n_i    | Input        | 1     | N/A           | Active-low reset. It is connected to rstn_i (Top Module) if the 25 MHz generator is disabled. Otherwise, it is connected to lock_o of the 25 MHz generator. |

| clk_i        | Input        | 1     | N/A           | 25 MHz clock input.                                                                                                                                         |

| timeout_en_i | Input        | 1     | 1'b1          | Enables the timeout timer. The timer is active when timeout_en_i = 1 and init_done_i = 0.                                                                   |

| init_done_i  | Input        | 1     | N/A           | Connects to init_done_o of LTPI. The timer is active when timeout_en_i = 1 and init_done_i = 0.                                                             |

| reset_n_o    | Output       | 1     | 1'b0          | System reset source.                                                                                                                                        |

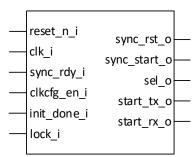

# 3.1.4. Initialization Logic

This module manages the PHY initialization of the LTPI and controls the signal to trigger the switch between Base Speed and Target Speed.

Figure 3.9. Initialization Logic Block Diagram

**Table 3.5. Initialization Logic Signals**

| Port Name    | Input/Output | Width | Default Value | Description                                                                                                                                           |

|--------------|--------------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset_n_i    | Input        | 1     | N/A           | Active-low reset.                                                                                                                                     |

| clk_i        | Input        | 1     | N/A           | 25 MHz clock input.                                                                                                                                   |

| sync_rdy_i   | Input        | 1     | N/A           | PHY synchronization ready. Connects to sync_rdy_o of LTPI.                                                                                            |

| clkcfg_en_i  | Input        | 1     | N/A           | Clock Reconfiguration Enable. Connects to clkcfg_en_o of LTPI.                                                                                        |

| init_done_i  | Input        | 1     | N/A           | Link Established Flag. Connects to init_done_o of LTPI.                                                                                               |

| lock_i       | Input        | 1     | N/A           | Dynamic PLL Lock. Connects to LOCK or lock_o of LTPI Clock Source.                                                                                    |

| sync_rst_o   | Output       | 1     | 1'b0          | PHY reset. Connects to sync_rst_i of LTPI.                                                                                                            |

| sync_start_o | Output       | 1     | 1'b0          | PHY synchronization start trigger. Connects to sync_start_i of LTPI.                                                                                  |

| sel_o        | Output       | 1     | 1'b0          | Control signal for frequency change:  1'b0 = Base Speed  1'b1 = Target Speed  Connects to sel_i of clock generator.  Unused for MachXO3 and MachXO3D. |

| start_tx_o   | Output       | 1     | 1'b0          | Initialize Tx PHY. Connects to start_tx_i of LTPI.                                                                                                    |

| start_rx_o   | Output       | 1     | 1'b0          | Initialize Rx PHY. Connects to start_rx_i of LTPI.                                                                                                    |

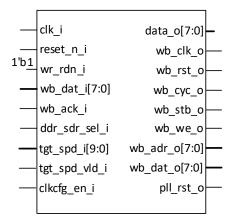

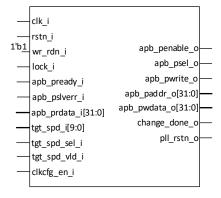

#### 3.1.5. PLL Streamer Logic

This module manages the process of changing the LTPI Clock Source frequency from Base Speed to Target Speed and vice versa. Table 3.7 outlines the difference in implementation for the three devices.

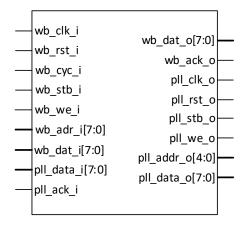

Figure 3.10. PLL Streamer Logic (Wishbone) Block Diagram

Figure 3.11. PLL Streamer Logic (APB) Block Diagram

**Table 3.6. PLL Streamer Logic Implementation**

| Target Device | Module Name       |

|---------------|-------------------|

| MachXO3       | wishbone_streamer |

| MachXO3D      | wishbone_streamer |

| MachXO5-NX    | apb_streamer      |

**Table 3.7. PLL Streamer Logic Signals**

| Port Name | Input/Output | Width | Default Value | Description                                      |  |

|-----------|--------------|-------|---------------|--------------------------------------------------|--|

| Wishbone  |              |       |               |                                                  |  |

| clk_i     | Input        | 1     | N/A           | 25 MHz clock input.                              |  |

| reset_n_i | Input        | 1     | N/A           | Active-low reset.                                |  |

| wr_rdn_i  | Input        | 1     | 1'b1          | Write (High) / Read (Low) Enable. DO NOT CHANGE. |  |

| wb_dat_i  | Input        | 8     | N/A           | Wishbone Data In. Connects to wb_dat_o of EFB.   |  |

| wb_ack_i  | Input        | 1     | N/A           | Wishbone Ack Bit. Connects to wb_ack_o of EFB.   |  |

© 2022-2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Port Name     | Input/Output | Width | Default Value | Description                                                     |

|---------------|--------------|-------|---------------|-----------------------------------------------------------------|

|               |              |       |               | Flag for SDR/DDR selection:                                     |

| ddr cdr col i | Innut        | 1     | N/A           | 1'b0 = SDR                                                      |

| ddr_sdr_sel_i | Input        | 1     | IN/A          | 1'b1 = DDR                                                      |

|               |              |       |               | Connects to tgt_spd_o[15] of LTPI.                              |

|               |              |       |               | Status flag for Target Speed Selection:                         |

|               |              |       |               | 10'h001 = 25 MHz                                                |

|               |              |       |               | 10'h002 = 50 MHz                                                |

|               |              |       |               | 10'h004 = 75 MHz                                                |

|               |              | 40    | 21/2          | 10'h008 = 100 MHz                                               |

| tgt_spd_i     | Input        | 10    | N/A           | 10'h010 = 150 MHz                                               |

|               |              |       |               | 10'h020 = 200 MHz<br>10'h040 = 250 MHz                          |

|               |              |       |               | 10 1040 - 250 MHz                                               |

|               |              |       |               | 10'h100 = 400 MHz                                               |

|               |              |       |               | Connects to tgt spd o[9:0] of LTPI.                             |

|               |              |       |               | It indicates that the value on the tgt_spd_o of LTPI is valid.  |

| tgt_spd_vld_i | Input        | 1     | N/A           | Connects to tgt_spd_vid_o of LTPI.                              |

| clkcfg_en_i   | Input        | 1     | N/A           | Clock Reconfiguration Enable. Connects to clkcfg_en_o of LTPI.  |

| data_o        | Output       | 8     | 8'h00         | Module debug port. Unused.                                      |

| wb_clk_o      | Output       | 1     | 1'b0          | Wishbone Clock. Connects to wb_clk_i of EFB.                    |

| wb_rst_o      | Output       | 1     | 1'b0          | Wishbone Reset. Connects to wb_rst_i of EFB.                    |

| wb_cyc_o      | Output       | 1     | 1'b0          | Wishbone Cycle. Connects to wb_cyc_i of EFB.                    |

| wb_stb_o      | Output       | 1     | 1'b0          | Wishbone Strobe. Connects to wb_stb_i of EFB.                   |

| wb_we_o       | Output       | 1     | 1'b0          | Wishbone Write Enable. Connects to wb_we_i of EFB.              |

| wb_adr_o      | Output       | 8     | 8'h00         | Wishbone Address. Connects to wb_adr_i of EFB.                  |

| wb_dat_o      | Output       | 8     | 8'h00         | Wishbone Data Out. Connects to wb_dat_i of EFB.                 |

| pll_rst_o     | Output       | 1     | 1'b0          | Dynamic PLL Reset Source. Connects to RST of LTPI Clock Source. |

| APB           |              |       |               |                                                                 |

| clk_i         | Input        | 1     | N/A           | 25 MHz clock input.                                             |

| rstn_i        | Input        | 1     | N/A           | Active-low reset.                                               |

| wr_rdn_i      | Input        | 1     | 1'b1          | Write (High) / Read (Low) Enable. <b>DO NOT CHANGE.</b>         |

| lock_i        | Input        | 1     | N/A           | Dynamic PLL Lock. Connects to lock_o of LTPI Clock Source.      |

| apb_pready_i  | Input        | 1     | N/A           | APB Ready. Connects to apb_pready_o of LTPI Clock Source.       |

|               | l t          | 4     | 21/2          | APB Slave Error. Connects to apb_pslverr_o of LTPI Clock        |

| apb_pslverr_i | Input        | 1     | N/A           | Source.                                                         |

| apb_prdata_i  | Input        | 32    | N/A           | APB Read Data. Connects to apb_prdata_o of LTPI Clock           |

| app_praata_r  | Прис         | 32    | 14/7          | Source.                                                         |

|               |              |       |               | Status flag for Target Speed Selection:                         |

|               |              |       |               | 10'h001 = 25 MHz                                                |

|               |              |       |               | 10'h002 = 50 MHz                                                |

|               |              |       |               | 10'h004 = 75 MHz                                                |

|               |              |       |               | 10'h008 = 100 MHz<br>10'h010 = 150 MHz                          |

| tgt_spd_i     | Input        | 10    | N/A           | 10 h010 = 150 MHz<br>10'h020 = 200 MHz                          |

|               |              |       |               | 10 h020 = 200 MHz                                               |

|               |              |       |               | 10'h080 = 300 MHz                                               |

|               |              |       |               | 10'h100 = 400 MHz                                               |

|               |              |       |               | 10'h200 = 800 MHz                                               |

|               |              |       |               | Connects to tgt_spd_o[9:0] of LTPI.                             |

| Port Name     | Input/Output | Width | Default Value | Description                                                                                                                            |

|---------------|--------------|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ddr_sdr_sel_i | Input        | 1     | N/A           | Flag for SDR/DDR selection:  1'b0 = SDR  1'b1 = DDR  Connects to tet, and of 1E1 of LTBI                                               |

| tgt_spd_vld_i | Input        | 1     | N/A           | Connects to tgt_spd_o[15] of LTPI.  It indicates that the value on the tgt_spd_o of LTPI is valid.  Connects to tgt_spd_vld_o of LTPI. |

| clkcfg_en_i   | Input        | 1     | N/A           | Clock Reconfiguration Enable. Connects to clkcfg_en_o of LTPI.                                                                         |

| apb_penable_o | Output       | 1     | 1'b0          | APB Enable. Connects to apb_penable_i of LTPI Clock Source.                                                                            |

| apb_psel_o    | Output       | 1     | 1'b0          | APB Select. Connects to apb_psel_i of LTPI Clock Source.                                                                               |

| apb_pwrite_o  | Output       | 1     | 1'b0          | APB Write Enable. Connects to apb_pwrite_i of LTPI Clock Source.                                                                       |

| apb_paddr_o   | Output       | 32    | 32'h00000000  | APB Address. Connects to apb_paddr_i of LTPI Clock Source.                                                                             |

| apb_pwdata_o  | Output       | 32    | 32'h00000000  | APB Write Data. Connects to apb_pwdata_i of LTPI Clock Source.                                                                         |

| change_done_o | Output       | 1     | 1'b0          | Frequency Change Done Flag. Connects to change_done_i of Clock Generator.                                                              |

| pll_rstn_o    | Output       | 1     | 1'b1          | Dynamic PLL Reset Source. Connects to rstn_i of LTPI Clock Source.                                                                     |

#### 3.1.6. EFB

This module serves as a wrapper for an EFB instance, providing access to the Wishbone interface of the LTPI Clock Source PLL. This module is used exclusively for MachXO3 and MachXO3D devices.

Module Name: wb\_pll

Figure 3.12. EFB Block Diagram

**Table 3.8. EFB Signals**

| Port Name  | Input/Output | Width | Default Value | Description                                                        |

|------------|--------------|-------|---------------|--------------------------------------------------------------------|

| wb_clk_i   | Input        | 1     | N/A           | Wishbone Clock. Connects to wb_clk_o of PLL Streamer Logic.        |

| wb_rst_i   | Input        | 1     | N/A           | Wishbone Reset. Connects to wb_rst_o of PLL Streamer Logic.        |

| wb_cyc_i   | Input        | 1     | N/A           | Wishbone Cycle. Connects to wb_cyc_o of PLL Streamer Logic.        |

| wb_stb_i   | Input        | 1     | N/A           | Wishbone Strobe. Connects to wb_stb_o of PLL Streamer Logic.       |

| wb_we_i    | Input        | 1     | N/A           | Wishbone Write Enable. Connects to wb_we_o of PLL Streamer Logic.  |

| wb_adr_i   | Input        | 8     | N/A           | Wishbone Address. Connects to wb_adr_o of PLL Streamer Logic.      |

| wb_dat_i   | Input        | 8     | N/A           | Wishbone Data In. Connects to wb_dat_o of PLL Streamer Logic.      |

| pll_dat_i  | Input        | 8     | N/A           | PLL Wishbone Data In. Connects to PLLDATO of LTPI Clock Source.    |

| pll_ack_i  | Input        | 1     | N/A           | PLL Wishbone Ack Bit. Connects to PLLACK of LTPI Clock Source.     |

| wb_dat_o   | Output       | 8     | 8'h00         | Wishbone Data Out. Connects to wb_dat_i of PLL Streamer Logic.     |

| wb_ack_o   | Output       | 1     | 1'b0          | Wishbone Ack Bit. Connects to wb_ack_i of PLL Streamer Logic.      |

| pll_clk_o  | Output       | 1     | N/A           | PLL Wishbone Clock. Connects to PLLCLK of LTPI Clock Source.       |

| pll_rst_o  | Output       | 1     | 1'b0          | PLL Wishbone Reset. Connects to PLLRST of LTPI Clock Source.       |

| pll_stb_o  | Output       | 1     | 1'b0          | PLL Wishbone Strobe. Connects to PLLSTB of LTPI Clock Source.      |

| pll_we_o   | Output       | 1     | 1'b0          | PLL Wishbone Write Enable. Connects to PLLWE of LTPI Clock Source. |

| pll_addr_o | Output       | 5     | 5′h00         | PLL Wishbone Address. Connects to PLLADDR of LTPI Clock Source.    |

| pll_data_o | Output       | 8     | 8'h00         | PLL Wishbone Data Out. Connects to PLLDATI of LTPI Clock Source.   |

## 3.1.7. LTPI Clock Source

This module serves as a wrapper for a PLL instance, providing the necessary clocks for the LTPI.

Table 3.3 outlines the difference in implementation for the three devices.

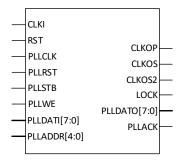

Figure 3.13. LTPI Clock Source (MachXO3/MachXO3D) Block Diagram

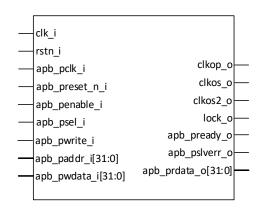

Figure 3.14. LTPI Clock Source (MachXO5-NX) Block Diagram

# **Table 3.9. LTPI Clock Source Signals**

| Port Name      | Input/Output | Width | Default Value | Description                                                           |

|----------------|--------------|-------|---------------|-----------------------------------------------------------------------|

| MachXO3/MachX  | (O3D         |       |               |                                                                       |

| CLKI           | Input        | 1     | N/A           | 25 MHz clock input.                                                   |

| RST            | Input        | 1     | N/A           | Active-high reset. Connects to pll_rst_o of PLL Streamer Logic.       |

| PLLCLK         | Input        | 1     | N/A           | PLL Wishbone Clock. Connects to pll_clk_o of LTPI Clock Source.       |

| PLLRST         | Input        | 1     | N/A           | PLL Wishbone Reset. Connects to pll_rst_o of LTPI Clock Source.       |

| PLLSTB         | Input        | 1     | N/A           | PLL Wishbone Strobe. Connects to pll_stb_o of LTPI Clock Source.      |

| PLLWE          | Input        | 1     | N/A           | PLL Wishbone Write Enable. Connects to pll_we_o of LTPI Clock Source. |

| PLLDATI        | Input        | 8     | N/A           | PLL Wishbone Data In. Connects to pll_data _o of LTPI Clock Source.   |

| PLLADDR        | Input        | 5     | N/A           | PLL Wishbone Address. Connects to pll_addr_o of LTPI Clock Source.    |

| CLKOP          | Output       | 1     | N/A           | LTPI ECLK source. Connects to eclk_i of LTPI.                         |

| CLKOS          | Output       | 1     | N/A           | LTPI ECLK 90 source. Connects to eclk90_i of LTPI.                    |

| CLKOS2         | Output       | 1     | N/A           | LTPI main clock source. Connects to clk_i of LTPI.                    |

| LOCK           | Output       | 1     | 1'b0          | Dynamic PLL Lock. Connects to lock_i of Initialization Logic.         |

| PLLDATO        | Output       | 8     | 8'h00         | PLL Wishbone Data Out. Connects to pll_dat_i of EFB.                  |

| PLLACK         | Output       | 1     | 1'b0          | PLL Wishbone Ack Bit. Connects to pll_ack_i of EFB.                   |

| MachXO5-NX     |              |       |               |                                                                       |

| clk_i          | Input        | 1     | N/A           | 25 MHz clock input.                                                   |

| rstn_i         | Input        | 1     | N/A           | Active-low reset. Connects to pll_rstn_o of PLL Streamer Logic.       |

| apb_pclk_i     | Input        | 1     | N/A           | 25 MHz clock input.                                                   |

| apb_preset_n_i | Input        | 1     | N/A           | Active-low reset.                                                     |

| apb_penable_i  | Input        | 1     | N/A           | APB Enable. Connects to apb_penable_o of PLL Streamer Logic.          |

| apb_psel_i     | Input        | 1     | N/A           | APB Select. Connects to apb_psel_o of PLL Streamer Logic.             |

| apb_pwrite_i   | Input        | 1     | N/A           | APB Write Enable. Connects to apb_pwrite_o of PLL Streamer Logic.     |

| apb_paddr_i    | Input        | 32    | N/A           | APB Address. Connects to apb_paddr_o of PLL Streamer Logic.           |

| Port Name     | Input/Output | Width | Default Value                                                       | Description                                                                                 |

|---------------|--------------|-------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| apb_pwdata_i  | Input        | 32    | N/A APB Write Data. Connects to apb_pwdata_o of PLL Streamer Logic. |                                                                                             |

| clkop_o       | Output       | 1     | N/A                                                                 | LTPI ECLK source. Connects to eclk_i of LTPI.                                               |

| clkos_o       | Output       | 1     | N/A                                                                 | LTPI ECLK 90 source. Connects to eclk90_i of LTPI.                                          |

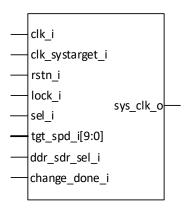

| clkos2_o      | Output       | 1     | N/A                                                                 | LTPI Target Speed System Clock. Connects to clk_systarget_i of Clock Generator.             |

| lock_o        | Output       | 1     | 1'b0                                                                | Dynamic PLL Lock. Connects to lock_i of Initialization Logic and lock_i of Clock Generator. |

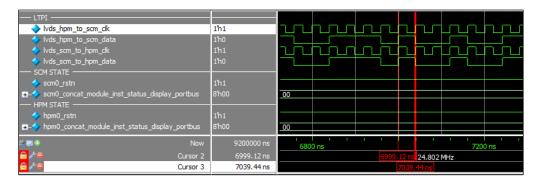

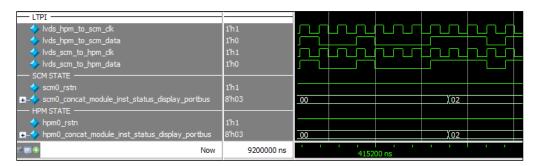

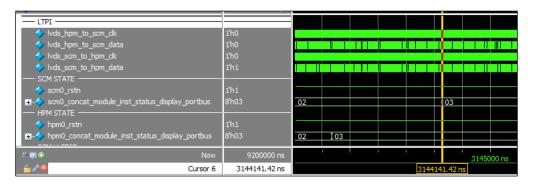

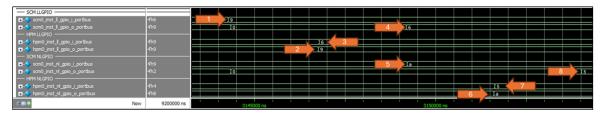

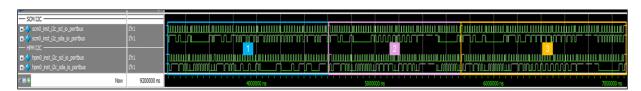

| apb_pready_o  | Output       | 1     | 1'b0                                                                | APB Ready. Connects to apb_pready_i of PLL Streamer Logic.                                  |