# Lattice Sentry SMBus Mailbox IP Core – Propel Builder

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ# 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

#### **Contents**

| Acronyms in This Document                                     | 5        |

|---------------------------------------------------------------|----------|

| 1. Introduction                                               | €        |

| 1.1. Features                                                 |          |

| 1.2. Conventions                                              |          |

| 2. Functional Descriptions                                    | 8        |

| 2.1. Overview                                                 | 8        |

| 2.2. Signals Description                                      | <u>ç</u> |

| 2.3. Attributes                                               | 10       |

| 2.4. Register Description                                     | 13       |

| 2.4.1. Target Core Register                                   | 16       |

| 2.4.2. Registers File                                         | 22       |

| 2.4.3. Controller Core Register                               | 22       |

| 2.5. SMBus Alert Signal                                       | 22       |

| 3. Program Flow                                               | 24       |

| 3.1. SMBus Target Core Initialization                         | 24       |

| 3.2. SMBus Controller Core Initialization                     | 24       |

| 3.3. SMBus Target Core Operation Flow                         | 24       |

| 3.3.1. Data Transfer in Response to External Controller Read  | 24       |

| 3.3.2. Data Transfer in Response to External Controller Write | 25       |

| 3.4. SMBus Controller Core Operation Flow                     | 25       |

| 3.4.1. Write Data to the SMBus Target                         | 26       |

| 3.4.2. Read Data from the SMBus Target                        | 27       |

| 3.5. C Code API                                               | 27       |

| 4. Generating the SMBus Mailbox IP                            | 28       |

| 5. Applicable Devices                                         | 30       |

| References                                                    | 31       |

| Technical Support Assistance                                  | 32       |

| Revision History                                              | 33       |

# **Figures**

| Figure 1.1. SMBus Mailbox Write Byte Message             | 6  |

|----------------------------------------------------------|----|

| Figure 1.2. SMBus Mailbox Read Byte Message              | 6  |

| Figure 1.3. MCTP over SMBus Packet Format                | 6  |

| Figure 2.1. SMBus IP Core Functional Diagram             | 9  |

| Figure 2.2. 7-bit Addressable Device Response            | 23 |

| Figure 3.1. SMBus Controller Program Flow Interrupt Mode | 26 |

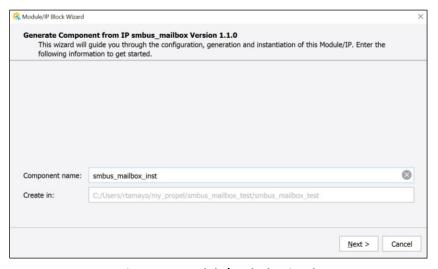

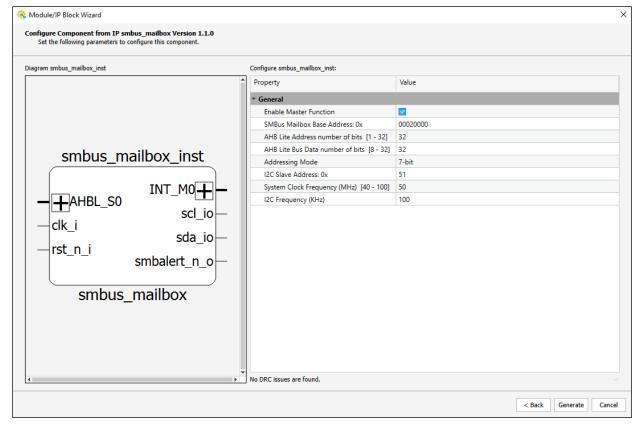

| Figure 4.1. Module/IP Block Wizard                       | 28 |

| Figure 4.2. Configuring Parameters                       |    |

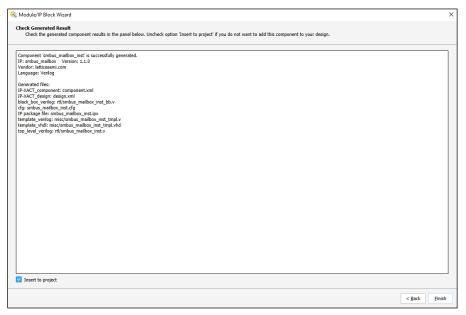

| Figure 4.3. Verifying Results                            | 29 |

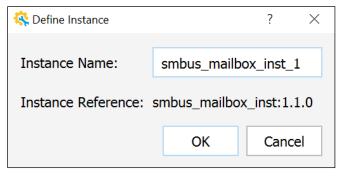

| Figure 4.4. Specifying Instance Name                     | 29 |

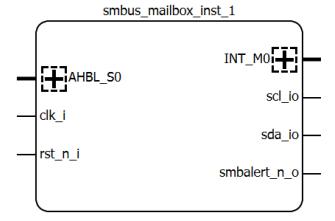

| Figure 4.5. Generated Instance                           | 29 |

|                                                          |    |

|                                                          |    |

| Tables                                                   |    |

| Table 2.1. Interface Signal Description                  | 9  |

| Table 2.2. Attributes Description                        | 11 |

| Table 2.3. Registers Address Map                         | 11 |

| Table 2.4. Access Type Definition                        | 15 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym  | Definition                              |  |  |  |

|----------|-----------------------------------------|--|--|--|

| AHB-Lite | Advanced High-performance Bus – Lite    |  |  |  |

| API      | Application Programming Interface       |  |  |  |

| CPU      | Central Processing Unit                 |  |  |  |

| FPGA     | Field Programmable Gate Array           |  |  |  |

| HDL      | Hardware Description Language           |  |  |  |

| I2C      | Inter-Integrated Circuit                |  |  |  |

| IP       | Intellectual Property                   |  |  |  |

| LMMI     | Lattice Memory Mapped Interface         |  |  |  |

| MCTP     | Management Component Transport Protocol |  |  |  |

| RoT      | Root of Trust                           |  |  |  |

| RTL      | Register Transfer Level                 |  |  |  |

| SMBus    | System Management Bus                   |  |  |  |

#### 1. Introduction

The System Management Bus (SMBus) is a two-wire interface through which simple system and power management devices can communicate with the rest of the system. The protocol is compatible with the I2C bus protocol and is often found in monitoring power conditions, temperature, and other sensors on a board. While the SMBus is derived from I2C, there are several major differences existing between the specifications of the two buses. The device that initiates the transmission on the SMBus is commonly known as the Controller, while the device being addressed is called the Target.

SMBus bus protocols support many kinds of formats, such as SMBus write byte, SMBus write word, SMBus read byte, SMBus read word, SMBus write block, SMBus read block and so on. See SMBus Specification for more information.

SMBus Mailbox is an SMBus target, which is designed to communicate with SMBus host mailbox. It responds to the standard SMBus Write Byte and Read Byte format messages, as shown in Figure 1.1 and Figure 1.2.

Figure 1.2. SMBus Mailbox Read Byte Message

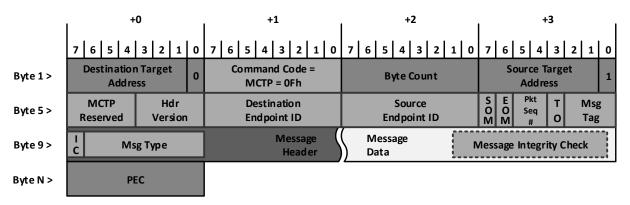

The MCTP over SMBus/I2C transport binding defines how the MCTP packets are delivered over a physical SMBus or I2C medium using SMBus transactions. All MCTP transactions are based on the SMBus Block Write bus protocol. The first eight bytes make up the packet header. The first three fields—Destination Target Address, Command Code, and Length—map directly to SMBus functional fields. The remaining header and payload fields map to SMBus Block Write Data Byte fields, as indicated in Figure 1.1. Hence, the inclusion of the Source Target Address in the header is specified by MCTP rather than SMBus. This is done to facilitate addressing required for establishing communications back to the message originator.

Figure 1.3. MCTP over SMBus Packet Format

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

#### 1.1. Features

The soft IP has the following features:

- Compatible with SMBus Specification

- Compatible with AHB-Lite Specification

- Supports SMBus controller

- Supports SMBus target

- Supports SMBus mailbox

- Supports MCTP over SMBus

- Supports 7-bit/10-bit addressing modes

- Supports Fairness arbitration SMBus arbitration mechanism

- Clock stretching and wait state generation

- · Timeout monitor for the Controller

- Interrupt flag generation

- Arbitration lost interrupt, with automatic transfer cancellation

- Bus busy detection

- Integrated glitch filter

#### 1.2. Conventions

The nomenclature used in this document is based on Verilog HDL.

## 2. Functional Descriptions

#### 2.1. Overview

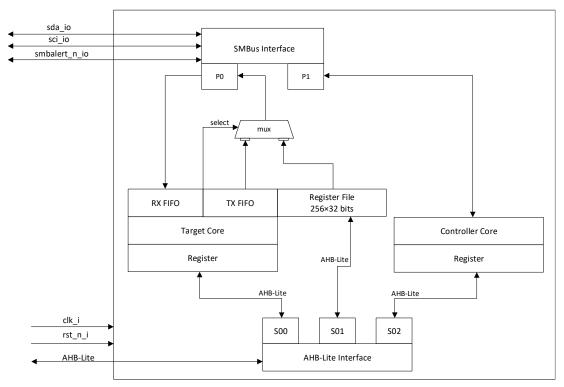

The functional diagram of this IP is shown in Figure 2.1, which contains two main blocks: one is the Target Core and the other is the Controller Core.

The Target Core performs two operations:

- Normal SMBus transfer as a target

- Register file transfer as SMBus Mailbox

The Controller Core can initiate SMBus transfer as an SMBus Controller.

The SMBus interface is connected to the external bus through SDA/SCL signals. The Controller Core connects through the P1 interface and the Target Core connects through the P0 interface. Therefore, a switch/mux is needed between Controller and Target Cores. The switch is implemented in SMBus interface by the following method:

- If the Controller Core does not initiate a transfer, P0 is routed to the SMBus interface and P1 is switched off. The SMBus target core can then exchange data using the SDA/SCL signals.

- If the Controller Core initiates a transfer, P1 is routed to the SMBus interface and P0 is switched off. The SMBus Controller Core can then exchange data using the SDA/SCL signals.

The Controller Core can initiate SMBus transfer to access other SMBus Targets. The MCTP transfer is also controlled by the Controller Core logic. The Controller Core supports multi-controller on one bus simultaneously. All the controllers obey fairness arbitration rules to avoid any bus conflicts.

The Target Core makes sure the IP serves as an SMBus target device on the bus. The external controller writing messages are routed to RX\_FIFO. Reading messages may come from two data sources, TX\_FIFO and Register File according to register configuration. The Register File can only be updated by the external host writing through the AHB-Lite port S01. The IP responds to two target addresses: the configured I2C Target Address from IP attributes, which can also be changed dynamically by the host, and the SMBus Device Default Address (7'b1100-001) as specified by the SMBus Specification.

The host accesses the IP through the AHB-Lite port. From the system level, it only has one AHB-Lite subordinate port, which can be connected to the host or another AHB-Lite Interconnect. The host can access Controller Core Register, Target Core Register, and Register File by the different addresses.

Figure 2.1. SMBus IP Core Functional Diagram

## 2.2. Signals Description

**Table 2.1. Interface Signal Description**

| Signal Name       | Width | Direction | Reset | Description                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Reset   | •     |           |       |                                                                                                                                                                                                                                                                                                                                   |

| clk_i             | 1     | input     | _     | System Clock                                                                                                                                                                                                                                                                                                                      |

| rst_n_i           | 1     | input     | _     | System Reset. The reset assertion can be asynchronous but reset negation should be synchronous. This is an active low signal. When asserted, output ports and registers are forced to their reset values.                                                                                                                         |

| AHB-Lite Bus      |       |           |       |                                                                                                                                                                                                                                                                                                                                   |

| ahbl_hsel_slv_i   | 1     | input     | _     | AHB-Lite Select Signal Indicates that the subordinate device is selected and a data transfer is required.                                                                                                                                                                                                                         |

| ahbl_haddr_slv_i  | 32    | input     | _     | The System Address Bus                                                                                                                                                                                                                                                                                                            |

| ahbl_hburst_slv_i | 3     | input     | _     | 3'b000: SINGLE Single Burst 3'b001: INCR Incrementing burst of undefined length (NOT supported) 3'b010: WRAP4 4-bit wrapping burst 3'b011: INCR4 4-bit incrementing burst 4'b100: WRAP8 8-bit wrapping burst 3'b101: INCR8 8-bit incrementing burst 8'b110: WRAP16 16-bit wrapping burst 3'b111: INCR16 16-bit incrementing burst |

| Signal Name          | Width | Direction | Reset                               | Description                                                                                                                                                                                                                                                              |

|----------------------|-------|-----------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ahbl_hprot_slv_i     | 4     | input     | _                                   | ahbl_hprot_slv_i [0]:  1'b0 – opcode fetch.  1'b1 – data access. ahbl_hprot_slv_i [1]:  1'b0 – user access.  1'b1 – privileged access. ahbl_hprot_slv_i [2]:  1'b0 – non-bufferable.  1'b1 – bufferable. ahbl_hprot_slv_i [3]:  1'b0 – non-cacheable;  1'b1 – cacheable. |

| ahbl_hsize_slv_i     | 3     | input     | _                                   | 3'b000: 1 byte<br>3'b001: 2 bytes<br>3'b010: 4 bytes                                                                                                                                                                                                                     |

| ahbl_htrans_slv_i    | 2     | input     | _                                   | Indicates the transfer type of the current transfer. This can be: 2'b00: IDLE 2'b01: BUSY 2'b10: NONSEQUENTIAL 2'b11: SEQUENTIAL                                                                                                                                         |

| ahbl_hwdata_slv_i    | 32    | input     | _                                   | The write data bus.                                                                                                                                                                                                                                                      |

| ahbl_hwrite_slv_i    | 1     | input     | _                                   | When this signal is HIGH, it indicates a write transfer and when it is LOW, it indicates a read transfer.                                                                                                                                                                |

| ahbl_hready_slv_i    | 1     | input     | 0                                   | This signal should come from AHB-Lite Interconnect. When it is set to 1, it indicates the previous transfer is complete.                                                                                                                                                 |

| ahbl_hrdata_slv_o    | 32    | output    | 0                                   | The read data bus                                                                                                                                                                                                                                                        |

| ahbl_hreadyout_slv_o | 1     | output    | 0                                   | When this signal is HIGH, it indicates that a transfer has finished on the bus. This signal can be driven LOW to extend a transfer.                                                                                                                                      |

| ahbl_hresp_slv_o     | 1     | output    | 0                                   | When this signal is LOW, it indicates that the transfer status is OKAY. When it is HIGH, it indicates that the transfer status is ERROR.                                                                                                                                 |

| Interrupt Signal     |       |           |                                     |                                                                                                                                                                                                                                                                          |

| int_o                | 1     | output    | 0                                   | Interrupt to host (CPU). The reset value is 1'b0.                                                                                                                                                                                                                        |

| SMBus Signal         |       |           |                                     |                                                                                                                                                                                                                                                                          |

| scl_io               | 1     | inout     | Reset value is weak high (pull-up). | SMBus Serial Clock                                                                                                                                                                                                                                                       |

| sda_io               | 1     | inout     | Reset value is weak high (pull-up). | SMBus data signal                                                                                                                                                                                                                                                        |

| smbalert_n_o         | 1     | output    | 0                                   | SMBus alert (active low)                                                                                                                                                                                                                                                 |

#### 2.3. Attributes

The configurable attributes of the IP Core are shown in Table 2.2. The attributes can be configured through the IP Catalog's Module/IP wizard of the Lattice Propel™ Builder.

**Table 2.2. Attributes Description**

| Parameter                           | Value Range                                 | Description                                                                                                                   |

|-------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Enable Controller Function          | Checkbox:<br>check, uncheck                 | Switch on/off controller function. Check: enable the Controller Core; Uncheck: disable the Controller Core. Target-only mode. |

| SMBus Mailbox Base Address          | 0–{AHB Lite Address assignment designation} | Specify IP base address on AHB-Lite bus.                                                                                      |

| AHB-Lite Address bus number of bits | [1–32]                                      | AHB-Lite bus address width                                                                                                    |

| AHB-Lite Data Bus number of bits    | [8–32]                                      | AHB-Lite bus data width                                                                                                       |

| Addressing Mode                     | 7-bit, 10-bit                               | 7-bit or 10-bit addressing selection                                                                                          |

| I2C Target Address: 0x              | 7-bit: 0x0–0x7f,<br>10-bit: 0x0–3ff         | As a target device, it is the target address for external controller to address.                                              |

| Device Architecture                 | ['LFMNX', 'MachXO3D']                       | FPGA Architecture                                                                                                             |

| System Clock Frequency (MHz)        | [40–100]                                    | System Clock Frequency                                                                                                        |

| I2C Frequency (kHz)                 | [100, 400, 1000]                            | I2C bus frequency                                                                                                             |

## 2.4. Register Description

The register address map, shown in Table 2.3, specifies the available IP Core registers. The offset of each register increments by four to allow easy interfacing with the Processor and System Buses. In this case, each register is 32-bit wide.

Table 2.3. Registers Address Map

| Offset   | Register Name              | Access     | Reset                                          | Description                                                                 |                |            |

|----------|----------------------------|------------|------------------------------------------------|-----------------------------------------------------------------------------|----------------|------------|

| AHB-Lite | S00: Each register is 32-b | it wide wh | •                                              |                                                                             | sed.           |            |

| 0x00     | RD_DATA_REG                | RO         | Not guaranteed.                                | Read Data F                                                                 | legister       |            |

| 0x00     | WR_DATA_REG                | wo         | Not guaranteed.                                | Write Data                                                                  | Register       |            |

| 0x04     | SLVADR_L_REG               | R/W        | [7] RSVD<br>[6:0] I2C Target<br>Address[6:0]   | Target Address Lower Register, same as the IZ<br>Target Address attribute.  |                | as the I2C |

| 0x08     | SLVADR_H_REG               | R/W        | [7:3] RSVD<br>[2:0] I2C Target<br>Address[9:7] | Target Address Higher Register, same as the I2<br>Target Address attribute. |                | as the I2C |

|          |                            |            |                                                | Control Register                                                            |                |            |

|          |                            | R/W        | [7:6] RSVD                                     | Field                                                                       | Name           | Access     |

|          |                            |            |                                                | [7:6]                                                                       | RSVD           | RSVD       |

|          |                            |            |                                                | [5]                                                                         | dat_src_sw     | R/W        |

| 0x0C     | CONTROL_REG                |            | [5:1] 0                                        | [4]                                                                         | nack_data      | R/W        |

|          |                            |            | [0] See Addressing Mode in Table 2.2.          | [3]                                                                         | nack_addr      | R/W        |

|          |                            |            | Table 2.2.                                     | [2]                                                                         | reset          | WO         |

|          |                            |            |                                                | [1]                                                                         | clk_stretch_en | R/W        |

|          |                            |            |                                                | [0]                                                                         | addr_10bit_en  | R/W        |

| 0x10     | TGT_BYTE_CNT_REG           | R/W        | 8'h00                                          | Target Byte                                                                 | Count Register |            |

| Offset | Register Name        | Access | Reset | Description                            |                                                          |                                              |

|--------|----------------------|--------|-------|----------------------------------------|----------------------------------------------------------|----------------------------------------------|

|        |                      |        |       | Interrunt St                           | atus First Register                                      |                                              |

|        |                      |        |       | Field                                  | Name                                                     | Access                                       |

|        |                      |        |       | [7]                                    | tr_cmp_int                                               | RW1C                                         |

|        |                      |        |       | [6]                                    | stop_det_int                                             | RW1C                                         |

|        | 0x14 INT_STATUS1_REG |        |       | [5]                                    | tx_fifo_full_int                                         | RW1C                                         |

| 0x14   |                      | RW1C   | 8'h00 | [4]                                    | tx_fifo_aempty_int                                       | RW1C                                         |

|        |                      |        |       | [3]                                    | tx_fifo_empty_int                                        | RW1C                                         |

|        |                      |        |       | [2]                                    | rx_fifo_full_int                                         | RW1C                                         |

|        |                      |        |       | [1]                                    | rx_fifo_afull_int                                        | RW1C                                         |

|        |                      |        |       | [0]                                    | rx_fifo_ready_int                                        | RW1C                                         |

|        |                      |        |       |                                        |                                                          |                                              |

|        |                      |        |       |                                        | nable First Register                                     |                                              |

|        |                      |        |       | Field                                  | Name                                                     | Access                                       |

|        |                      |        |       | [7]                                    | tr_cmp_en                                                | R/W                                          |

|        |                      |        |       | [6]                                    | stop_det_en                                              | R/W                                          |

| 0x18   | INT_ENABLE1_REG      | R/W    | 8'h00 | [5]                                    | tx_fifo_full_en                                          | R/W                                          |

| OXIO   | UNIT_LINABLLI_NLG    | IN/ VV |       | [4]                                    | tx_fifo_aempty_en                                        | R/W                                          |

|        |                      |        |       | [3]                                    | tx_fifo_empty_en                                         | R/W                                          |

|        |                      |        |       | [2]                                    | rx_fifo_full_en                                          | R/W                                          |

|        |                      |        |       | [1]                                    | rx_fifo_afull_en                                         | R/W                                          |

|        |                      |        |       | [0]                                    | rx_fifo_ready_en                                         | R/W                                          |

|        |                      |        |       | Interrupt Set First Register           |                                                          |                                              |

|        |                      |        |       | Field                                  | Name                                                     | Access                                       |

|        |                      |        |       | [7]                                    | tr_cmp_set                                               | wo                                           |

|        |                      |        |       | [6]                                    | stop_det_set                                             | WO                                           |

|        |                      |        |       | [5]                                    | tx_fifo_full_set                                         | WO                                           |

| 0x1C   | INT_SET1_REG         | wo     | 8'h00 | [4]                                    | tx_fifo_aempty_set                                       | wo                                           |

|        |                      |        |       | [3]                                    | tx_fifo_empty_set                                        | WO                                           |

|        |                      |        |       | [2]                                    | rx_fifo_full_set                                         | WO                                           |

|        |                      |        |       | [1]                                    | rx_fifo_afull_set                                        | WO                                           |

|        |                      |        |       | [0]                                    | rx_fifo_ready_set                                        | WO                                           |

|        |                      |        |       |                                        |                                                          |                                              |

|        |                      |        |       | Interrupt St                           | atus Second Register                                     |                                              |

|        |                      |        |       |                                        |                                                          |                                              |

|        |                      |        |       | Field                                  | Name                                                     | Access                                       |

|        |                      |        |       | [7]                                    | Name<br>reserved                                         | Access<br>RSVD                               |

|        |                      |        |       | [7]<br>[6]                             | reserved scl_h_to                                        | RSVD<br>RW1C                                 |

| 0x20   | INT STATUS? PEG      | RW1C   | 8'h00 | [7]<br>[6]<br>[5]                      | reserved scl_h_to scl_l_to                               | RSVD<br>RW1C<br>RW1C                         |

| 0x20   | INT_STATUS2_REG      | RW1C   | 8'h00 | [7]<br>[6]<br>[5]<br>[4]               | reserved scl_h_to scl_l_to SR_check_value                | RSVD<br>RW1C<br>RW1C<br>RW1C                 |

| 0x20   | INT_STATUS2_REG      | RW1C   | 8'h00 | [7]<br>[6]<br>[5]<br>[4]<br>[3]        | reserved scl_h_to scl_l_to SR_check_value SR_check_valid | RSVD<br>RW1C<br>RW1C<br>RW1C<br>RW1C         |

| 0x20   | INT_STATUS2_REG      | RW1C   | 8'h00 | [7]<br>[6]<br>[5]<br>[4]<br>[3]<br>[2] | reserved scl_h_to scl_l_to SR_check_value                | RSVD<br>RW1C<br>RW1C<br>RW1C<br>RW1C<br>RW1C |

| 0x20   | INT_STATUS2_REG      | RW1C   | 8'h00 | [7]<br>[6]<br>[5]<br>[4]<br>[3]        | reserved scl_h_to scl_l_to SR_check_value SR_check_valid | RSVD<br>RW1C<br>RW1C<br>RW1C<br>RW1C         |

| Offset        | Register Name   | Access | Reset                  | Description                                        | 1                                          |                  |

|---------------|-----------------|--------|------------------------|----------------------------------------------------|--------------------------------------------|------------------|

|               |                 |        |                        | Interrupt E                                        | nable Second Registe                       | er               |

|               |                 |        |                        | Field                                              | Name                                       | Access           |

|               |                 |        |                        | [7]                                                | reserved                                   | RSVD             |

|               |                 |        |                        | [6]                                                | scl_h_to_en                                | R/W              |

| 0.24          |                 | D /\A/ | [7:2] RSVD             | [5]                                                | scl_l_to_en                                | R/W              |

| 0x24          | INT_ENABLE2_REG | R/W    | [1:0] 2'b00            | [4]                                                | reserved                                   | RSVD             |

|               |                 |        |                        | [3]                                                | SR_valid_en                                | R/W              |

|               |                 |        |                        | [2]                                                | arp_cmd_en                                 | R/W              |

|               |                 |        |                        | [1]                                                | stop_err_en                                | R/W              |

|               |                 |        |                        | [0]                                                | start_err_en                               | R/W              |

|               |                 |        |                        | Interrupt Se                                       | et Second Register                         |                  |

|               |                 |        |                        | Field                                              | Name                                       | Access           |

|               |                 |        |                        | [7]                                                | reserved                                   | RSVD             |

|               |                 |        |                        | [6]                                                | sch_h_to_set                               | WO               |

|               |                 |        | [7:2] RSVD             | [5]                                                | sch_l_to_set                               | WO               |

| 0x28          | INT_SET2_REG    | WO     | [1:0] 2'b00            | [4]                                                | reserved                                   | RSVD             |

|               |                 |        | [=10] = 200            | [3]                                                | SR_valid_set                               | WO               |

|               |                 |        |                        | [2]                                                | arp_cmd_set                                | WO               |

|               |                 |        |                        | [1]                                                | stop_err_set                               | wo               |

|               |                 |        |                        |                                                    |                                            | _                |

|               |                 |        |                        | [0]                                                | start_err_set                              | WO               |

|               |                 |        |                        | FIFO Status                                        | Register                                   |                  |

|               |                 |        |                        | Field                                              | Name                                       | Access           |

|               |                 |        |                        | [7:6]                                              | RSVD                                       | RSVD             |

|               |                 |        |                        | [5]                                                | tx_fifo_full                               | RO               |

| 0x2C          | FIFO_STATUS_REG | RO     | [7:6] RSVD             | [4]                                                | tx_fifo_aempty                             | RO               |

|               |                 |        | [5:0] 6'b011001        | [3]                                                | tx_fifo_empty                              | RO               |

|               |                 |        |                        | [2]                                                | rx_fifo_full                               | RO               |

|               |                 |        |                        | [1]                                                | rx_fifo_afull                              | RO               |

|               |                 |        |                        | [0]                                                | rx_fifo_empty                              | RO               |

|               |                 | +      |                        | [0]                                                | TX_IIIO_CITIPLY                            | I NO             |

|               |                 |        |                        |                                                    | nable Second Registe                       |                  |

|               |                 |        | [7:2] RSVD             | Field                                              | Name                                       | Access           |

| 0x2C          | FLUSH_FIFO      | WO     | [1:0] 2'b0             | [7:2]                                              | reserved                                   | RSVD             |

|               |                 |        | [1.0] 2.00             | [1]                                                | rxfifo_flush                               | WO               |

|               |                 |        |                        | [0]                                                | txfifo_flush                               | WO               |

| 0x30          | SMB_CONTROL_REG | R/W    | [7:1] RSVD<br>[0] 1'b0 | [7:1] RSVD<br>[0] smb_ale<br>SMBus Con<br>• 1'b0 – | No interrupt to Cont<br>SMBus target sends | rt interrupt to  |

| 0x34-<br>0x3C | Reserved        | RSVD   | RSVD                   | Reserved<br>Write access                           | ss is ignored and 0 is                     | returned on read |

| Offset            | Register Name           | Access         | Reset                                   | Description                           | on                                                               |  |  |

|-------------------|-------------------------|----------------|-----------------------------------------|---------------------------------------|------------------------------------------------------------------|--|--|

| AHB-Lite          |                         |                | 1 10000                                 |                                       | <del></del>                                                      |  |  |

| 72 2.00           |                         |                |                                         |                                       | Registers File 256x32bits, SMBus Mailbox<br>Registers File.      |  |  |

|                   |                         |                |                                         | Offset                                | Dword Number                                                     |  |  |

| 0x2000-           |                         |                |                                         | 0x00                                  | 0                                                                |  |  |

| 0x2000-<br>0x23ff | Registers File          | R/W            | All '0's                                | 0x04                                  | 1                                                                |  |  |

|                   |                         |                |                                         | 0x08                                  | 2                                                                |  |  |

|                   |                         |                |                                         | <u></u>                               |                                                                  |  |  |

|                   |                         |                |                                         | 0x3fc                                 | 255                                                              |  |  |

| A115 13           |                         | 21: :1 1       | 1 11 12 12 12                           |                                       |                                                                  |  |  |

| AHB-Lite          | SU2: each register is 3 | 32-bit wide wr |                                         |                                       | the lower 8 bits [7:0] are used.                                 |  |  |

| 0x400             | PRERIO                  | R/W            | [31:8] RSVD<br>[7:0] 8'hff              |                                       | scale register low-byte<br>quency = clk_i / (PRERhi<<8 + PRERIo) |  |  |

|                   |                         |                | [31:8] RSVD                             | -                                     | scale register high-byte                                         |  |  |

| 0x404             | PRERhi                  | R/W            | [7:0] 8'hff                             | · · · · · · · · · · · · · · · · · · · | quency = clk_i / (PRERhi<<8 + PRERIo)                            |  |  |

|                   |                         |                | [,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                       |                                                                  |  |  |

|                   |                         |                |                                         | Control Re                            | Description                                                      |  |  |

|                   |                         |                |                                         |                                       | EN –Controller Core enable bit.                                  |  |  |

|                   |                         |                | [31:8] RSVD<br>[7:6] 2'h00              | [7]                                   | 1 = Core is enabled                                              |  |  |

| 0x408             | CTR                     | R/W            |                                         |                                       | 0 = Core is disabled                                             |  |  |

|                   |                         |                | [5:0] RSVD                              | [6]                                   | IEN – interrupt enable bit.                                      |  |  |

|                   |                         |                |                                         |                                       | 1 = Interrupt is enabled                                         |  |  |

|                   |                         |                |                                         |                                       | 0 = Interrupt is disabled                                        |  |  |

|                   |                         |                |                                         | Transmit                              | Pagistar                                                         |  |  |

|                   |                         |                |                                         | Transmit   Field                      | Description                                                      |  |  |

|                   |                         |                |                                         |                                       | Next byte to be transmitted via                                  |  |  |

|                   |                         |                |                                         | [7:1]                                 | SMBus Controller Core                                            |  |  |

| 0x40c             | TXR                     | wo             | [31:8] RSVD                             |                                       | a) The byte's LSB.                                               |  |  |

|                   |                         |                | [7:0] 8'h00                             |                                       | b) RW bit during target address                                  |  |  |

|                   |                         |                |                                         | [0]                                   | transfer                                                         |  |  |

|                   |                         |                |                                         |                                       | 1 = Reading from target                                          |  |  |

|                   |                         |                |                                         |                                       | 0 = Writing to target                                            |  |  |

|                   |                         |                | [31:8] RSVD                             | Receive R                             | _                                                                |  |  |

| 0x40c             | RXR                     | RO             | [7:0] 8'h00                             |                                       | received through the SMBus Controller                            |  |  |

|                   |                         |                |                                         | Core.                                 | N Dogistor                                                       |  |  |

|                   |                         |                |                                         | Command                               | Name                                                             |  |  |

|                   |                         |                |                                         | [7]                                   | STA – Generate (repeated) start                                  |  |  |

|                   |                         |                |                                         |                                       | condition                                                        |  |  |

|                   |                         |                |                                         | [6]                                   | STO – Generate stop condition                                    |  |  |

|                   |                         |                |                                         | [5]                                   | RD – Read from target                                            |  |  |

| 0x410             | CB                      | wo             | [31:8] RSVD                             | [4]                                   | WR – Write to target                                             |  |  |

| 07410             | CR                      | VVO            | [7:0] 8'h00                             | [3]                                   | ACK, when a receiver sends ACK (ACK = 0) or NACK (ACK = 1).      |  |  |

|                   |                         |                |                                         | [2]                                   | When set, clears the timeout status                              |  |  |

|                   |                         |                |                                         | [1]                                   | Reserved                                                         |  |  |

|                   |                         |                |                                         | [0]                                   | IACK – Interrupt acknowledge.                                    |  |  |

|                   |                         |                |                                         |                                       | When set, clears a pending                                       |  |  |

|                   |                         | 1              |                                         |                                       | interrupt.                                                       |  |  |

| Offset | Register Name | Access | Reset                      | Description  |                                                                                                                                                                                                                                |             |     |                                                                  |

|--------|---------------|--------|----------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|------------------------------------------------------------------|

|        |               |        |                            | Status F     | Register                                                                                                                                                                                                                       |             |     |                                                                  |

|        |               |        |                            | Field        | Name                                                                                                                                                                                                                           |             |     |                                                                  |

|        |               |        |                            | [7]          | RxACK – Received acknowledge<br>from addressed target.<br>1 = No acknowledge received.<br>0 = Acknowledge received.<br>Busy – Indicates that the SMBus bus                                                                     |             |     |                                                                  |

|        |               |        |                            |              | is busy.  1 = bus is busy.  0 = bus is idle.                                                                                                                                                                                   |             |     |                                                                  |

|        |               |        |                            | [5]          | <ul> <li>AL – Arbitration lost. This bit is set when the core loses arbitration.</li> <li>Arbitration is lost when:</li> <li>A STOP signal is detected, but not requested.</li> <li>A START signal is detected, but</li> </ul> |             |     |                                                                  |

| 0x410  | SR            | RO     | [31:8] RSVD<br>[7:0] 8'h00 |              | not requested.  The controller drives SDA high, but SDA is low.  Controller drive SCL high, but SCL is low. Not clock stretch.                                                                                                 |             |     |                                                                  |

|        |               |        | [7:0] 8 NOO                | [7.0] 8 1100 | [7.0] 8 1100                                                                                                                                                                                                                   | [7:0] 8 800 | [4] | Reserved. Timeout 1 = SCL and SDA line have been high for 50 us. |

|        |               |        |                            | [2]          | Timeout 1 = SCL line has been low for 25 ms.                                                                                                                                                                                   |             |     |                                                                  |

|        |               |        |                            | [1]          | TIP – Transfer in Progress  1 = Transferring data.  0 = Transfer is complete.                                                                                                                                                  |             |     |                                                                  |

|        |               |        |                            | [0]          | IF – Interrupt Flag. This bit is set when an interrupt is pending. The int_o signal is asserted if the IEN bit is set. The Interrupt Flag is set when:                                                                         |             |     |                                                                  |

|        |               |        |                            |              | <ul><li>One byte transfer has been completed.</li><li>Target NACK.</li></ul>                                                                                                                                                   |             |     |                                                                  |

|        |               |        |                            |              | <ul><li>Arbitration is lost.</li><li>Controller changes from busy to idle.</li></ul>                                                                                                                                           |             |     |                                                                  |

#### **Table 2.4. Access Type Definition**

| Table 2.4. Access 1 ype Definition |                          |                                                                                               |  |  |  |  |

|------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Access Type                        | Behaviour on Read Access | Behaviour on Write Access                                                                     |  |  |  |  |

| RO                                 | Returns register value.  | Ignores write access.                                                                         |  |  |  |  |

| WO                                 | Returns 0.               | Updates register value.                                                                       |  |  |  |  |

| RW                                 | Returns register value.  | Updates register value.                                                                       |  |  |  |  |

| RW1C                               | Returns register value.  | Writing 1'b1 on register bit clears the bit to 1'b0. Writing 1'b0 on register bit is ignored. |  |  |  |  |

| RSVD                               | Returns 0.               | Ignores write access.                                                                         |  |  |  |  |

#### 2.4.1. Target Core Register

AHB-Lite S00 is the port to access Target Core Register. The offset address is 0. The detail description for every register is shown below.

The RD\_DATA\_REG and WR\_DATA\_REG share the same offset. The Write access to this offset goes to WR\_DATA\_REG, while the Read access goes to RD\_DATA\_REG. Write Data Register is the interface to Transmit FIFO (TX\_FIFO). Writing to WR\_DATA\_REG pushes a word to Transmit FIFO (TX\_FIFO). When writing to WR\_DATA\_REG, the host should ensure that Transmit FIFO (TX\_FIFO) is not full. This can be done by reading FIFO\_STATUS\_REG. Data is popped from WR\_DATA\_REG during I2C read transaction. When reset is performed, the contents of Transmit FIFO (TX\_FIFO) are not reset but the FIFO control logic is reset. Thus, the content is not guaranteed after reset. The Read Data register is the interface to Receive FIFO (RX\_FIFO). After a data is received from I2C bus during I2C write transaction, the received data is pushed to Receive FIFO (RX\_FIFO). Reading from RD\_DATA\_REG pops a word from Receive FIFO (RX\_FIFO). The host should ensure that Receive FIFO (RX\_FIFO) has data before reading RD\_DATA\_REG, data is not guaranteed when this register is read during Receive FIFO (RX\_FIFO) empty condition. On the other hand, if Receive FIFO (RX\_FIFO) is full but I2C target continues to receive data, new data is lost. The Read FIFO\_STATUS\_REG to determine the status of Receive FIFO (RX\_FIFO). Similar to Transmit FIFO (TX\_FIFO), the reset value of Receive FIFO (RX\_FIFO) is also not guaranteed after reset.

The Target Address Lower Register (TARGET\_ADDRL\_REG) is a 7-bit Target address. This is used for 7-bit and 10-bit addressing mode as follows: for 7-bit Addressing Mode, it is the target address; for 10-bit Addressing Mode, it is the lower seven bits of the Target address. The Target Address Higher Register (TARGET\_ADDRH\_REG) is the upper three bits of 10-bit target address. This is not used in 7-bit addressing mode. The reset values of TARGET\_ADDRL\_REG and TARGET\_ADDRH\_REG is set by the I2C Target Address attribute, as shown in Table 2.2.

Each bit of the Control Register (CONTROL\_REG) controls the behavior of the Target Core.

dat\_src\_sw

Data source switch. Select data source when external controller read routine.

- 1'b0 selects register file for mailbox.

- 1'b1 selects tx fifo for normal external read.

- nack\_data

NACK on Data Phase. Specifies ACK/NACK response on I2C data phase.

- 1'b0 Sends ACK to received data.

- 1'b1 Sends NACK to received data.

- nack addr

NACK on Address Phase. Specifies ACK/NACK response on I2C address phase.

- 1'b0 Sends ACK to received address if it matches the programmed target address.

- 1'b1 Sends NACK to received address.

- reset

Reset. Resets I2C Target IP Core for one clock cycle. The registers and LMMI interface are not affected by this reset. This is write-only bit because it has auto-clear feature. It is cleared to 1'b0 after one clock cycle.

- 1'b0 No action.

- 1'b1 Resets I2C Target IP Core.

- clk\_stretch\_en

Clock Stretch Enable. Enables clock stretching on ACK bit of data.

- 1'b0 I2C Target IP Core releases SCL signal.

- 1'b1 I2C Target IP Core pulls down SCL signal on the next ACK bit of data phase and keeps pulling-down until the host writes 1'b0 on this bit.

- addr 10bit en

10-bit Address Mode Enable. Enables the reception of 10-bit I2C address.

- 1'b0 I2C Target IP Core rejects the 10-bit I2C address. It sends NACK.

- 1'b1 I2C Target IP Core responds to 10-bit I2C address. If TARGET\_ADDRH\_REG is 3'h0, it also responds to the 7-bit address.

The desired number of bytes to transfer (read/write) in I2C bus should be written to this Target Byte Count Register (TGT\_BYTE\_CNT\_REG). This is used for Transfer Complete interrupt generation which asserts when the target byte count is achieved.

The Interrupt Status Register (INT\_STATUS1\_REG and INT\_STATUS2\_REG) contains all the interrupts currently pending in the Target Core. When an interrupt bit asserts, it remains asserted until it is cleared by the host by writing 1'b1 to the corresponding bit.

The interrupt status bits are independent of the interrupt enable bits. In other words, status bits may indicate pending interrupts, even though those interrupts are disabled in the Interrupt Enable Register, see the description of Interrupt Enable Registers (INT\_ENABLE1\_REG, INT\_ENABLE2\_REG) below for details. The logic which handles interrupts should mask (bitwise and logic) the contents of INT\_STATUS1\_REG and INT\_ENABLE1\_REG registers as well as INT\_STATUS2\_REG and INT\_ENABLE2\_REG to determine the interrupts to service. The int\_o interrupt signal is asserted whenever both an interrupt status bit and the corresponding interrupt enable bits are set.

The corresponding bits of INT STATUS1 REG are shown below:

tr\_cmp\_int

Transfer Complete Interrupt Status. This interrupt status bit asserts when the number of bytes transferred in I2C interface is equal to TGT BYTE CNT REG.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- stop\_det\_int

STOP Condition Detected Interrupt Status. This interrupt status bit asserts when STOP condition is detected after an ACK/NACK bit.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- tx fifo full int

Transmit FIFO (TX\_FIFO) Full Interrupt Status. This interrupt status bit asserts when Transmit FIFO (TX\_FIFO) changes from not full state to full state.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- tx\_fifo\_aempty\_int

Transmit FIFO (TX\_FIFO) Almost Empty Interrupt Status. This interrupt status bit asserts when the amount of data words in Transmit FIFO (TX\_FIFO) changes from 'TX FIFO Almost Empty Flag' – 1 to 'TX FIFO Almost Empty Flag'.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- tx fifo empty int

Transmit FIFO (TX\_FIFO) Empty Interrupt Status. This interrupt status bit asserts when the last data in Transmit FIFO (TX\_FIFO) is popped-out, causing the FIFO to become empty.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- rx\_fifo\_full\_int

Receive FIFO (RX\_FIFO) Full Interrupt Status. This interrupt status bit asserts when RX FIFO full status changes from not full to full state.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- rx\_fifo\_afull\_int

Receive FIFO (RX\_FIFO) Almost Full Interrupt Status. This interrupt status bit asserts when the amount of data words in Receive FIFO (RX\_FIFO) changes from 'RX FIFO Almost Full Flag' – 1 to 'RX FIFO Almost Full Flag'.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

rx fifo ready int

Receive FIFO (RX\_FIFO) Ready Interrupt Status. This interrupt status bit asserts when Receive FIFO (RX\_FIFO) is empty and receives a data word from I2C interface.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

The corresponding bit of INT\_STATUS2\_REG is shown below:

scl h to

Timeout flag when SCL and SDA line have been high for 50 us in transfer mode.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- scl\_l\_to

Timeout flag when SCL line has been low for 25 ms.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- arp cmd det

Flag when 7'h61 is addressed.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- SR\_check\_valid: repeat start check valid.

- SR check value: repeat start value.

When SR\_check\_valid is valid (=1), then you know whether repeat start happens or not according to SR check value (=1, happen; =0 not happen).

stop\_err\_int

STOP Condition Error Interrupt Status. This interrupt status bit asserts after detecting a STOP condition when it is not expected. STOP condition is expected to occur only after the ACK/NACK bit. The stop\_err\_int and stop\_det\_int do not assert at the same time.

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

- start\_err\_int

START Condition Error Interrupt Status. This interrupt status bit asserts after detecting a START condition when it is not expected. START condition is expected to occur only when I2C bus is idle and after receiving an ACK or a NACK (repeated START condition).

- 1'b0 No interrupt.

- 1'b1 Interrupt pending.

INT\_ENABLE1\_REG/INT\_ENABLE2\_REG corresponds to interrupts status bits in INT\_STATUS1\_REG and INT\_STATUS2\_REG. They do not affect the contents of the INT\_STATUS1\_REG and INT\_STATUS2\_REG. If one of the INT\_STATUS1\_REG/INT\_STATUS2\_REG bits assert and the corresponding bit of INT\_ENABLE1\_REG/ INT\_ENABLE2\_REG is 1'b1, the interrupt signal int\_o asserts.

The corresponding bits of INT\_ENABLE1\_REG are shown below:

tr\_cmp\_en

Transfer Complete Interrupt Enable. Interrupt enable bit corresponds to Transfer Complete Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- stop\_det\_en

STOP Condition Detected Interrupt Enable. Interrupt enable bit corresponds to STOP Condition Detected Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

18

tx fifo full en

Transmit FIFO Full Interrupt Enable. Interrupt enable bit corresponds to Transmit FIFO Full Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- tx\_fifo\_aempty\_en

Transmit FIFO Almost Empty Interrupt Enable. Interrupt enable bit corresponds to Transmit FIFO Almost Empty Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- tx\_fifo\_empty\_en

Transmit FIFO Empty Interrupt Enable. Interrupt enable bit corresponds to Transmit FIFO Empty Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- rx\_fifo\_full\_en

Receive FIFO Full Interrupt Enable. Interrupt enable bit corresponds to Receive FIFO Full Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- rx\_fifo\_afull\_en

Receive FIFO Almost Full Interrupt Enable. Interrupt enable bit corresponds to Receive FIFO Almost Full Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- rx\_fifo\_ready\_en

Receive FIFO Ready Interrupt Enable. Interrupt enable bit corresponds to Receive FIFO Ready Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

The corresponding bits of INT ENABLE2 REG are shown below:

scl\_h\_to\_en

Enable interrupt when SCL and SDA line have been high for 50 us in transfer mode.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- scl I to en

Enable interrupt when SCL line has been low for 25 ms.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- SR valid en

Enable interrupt when repeat start check finish.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- arp\_cmd\_en

Enable interrupt when 7'h61 is addressed.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

- stop\_err\_en

STOP Condition Error Interrupt Enable. Interrupt enable bit corresponds to STOP Condition Error Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

start err en

START Condition Error Interrupt Enable. Interrupt enable bit corresponds to START Condition Error Interrupt Status.

- 1'b0 Interrupt disabled.

- 1'b1 Interrupt enabled.

INT\_SET1\_REG/INT\_SET2\_REG corresponds to interrupts status bits in INT\_STATUS1\_REG and INT\_STATUS2\_REG. Writing 1'b1 to a register bit in INT\_SET1\_REG or INT\_SET2\_REG asserts the corresponding interrupts status bit in INT\_STATUS1\_REG or INT\_STATUS2\_REG while writing 1'b0 is ignored. This is intended for testing purposes only.

The corresponding bit of INT SET1 REG shows below:

tr\_cmp\_set

Transfer Complete Interrupt Set. Interrupt set bit corresponds to Transfer Complete Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT STATUS1 REG.tr cmp int.

- stop\_det\_set

STOP Condition Detected Interrupt Set. Interrupt set bit corresponds to STOP Condition Detected Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.stop\_det\_int.

- tx fifo full set

Transmit FIFO Full Interrupt Set. Interrupt set bit corresponds to Transmit FIFO Full Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.tx\_fifo\_full\_int.

- tx fifo aempty set

Transmit FIFO Almost Empty Interrupt Set. Interrupt set bit corresponds to Transmit FIFO Almost Empty Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.tx\_fifo\_aempty\_int.

- tx\_fifo\_empty\_set

Transmit FIFO Empty Interrupt Set. Interrupt set bit corresponds to Transmit FIFO Empty Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.tx\_fifo\_empty\_int.

- rx\_fifo\_full\_set

Receive FIFO Full Interrupt Set. Interrupt set bit corresponds to Receive FIFO Full Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.rx\_fifo\_full\_int.

- rx\_fifo\_afull\_set

Receive FIFO Almost Full Interrupt Set. Interrupt set bit corresponds to Receive FIFO Almost Full Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.rx\_fifo\_afull\_int.

- rx\_fifo\_ready\_set

Receive FIFO Ready Interrupt Set. Interrupt set bit corresponds to Receive FIFO Ready Interrupt Status.

- 1'b0 No action.

- 1'b1 Asserts INT\_STATUS1\_REG.rx\_fifo\_ready\_int.

20

The corresponding bits of INT SET2 REG are shown below:

scl h to set

SCL and SDA line high timeout interrupt set. Interrupt set bit corresponds to scl h to bit in INT STATUS2 REG.

- 0 No action.

- 1 Asserts INT STATUS2 REG. scl h to.

- scl I to set

SCL line low timeout interrupt set. Interrupt set bit corresponds to scl\_l\_to bit in INT\_STATUS2\_REG.

- 0 No action.

- 1 Asserts INT\_STATUS2\_REG. scl\_l\_to.

- arp\_cmd\_det

7'h61 is addressed interrupt set. Interrupt set bit corresponds to arp\_cmd\_det bit in INT\_STATUS2\_REG.

- 0 No action.

- 1 Asserts INT\_STATUS2\_REG. arp\_cmd\_det.

- stop\_err\_set

STOP Condition Error Interrupt Set. Interrupt set bit corresponds to STOP Condition Error Interrupt Status.

- 0 No action.

- 1 Asserts INT\_STATUS2\_REG.stop\_err\_set.

- start\_err\_set

START Condition Error Interrupt Set. Interrupt set bit corresponds to START Condition Error Interrupt Status.

- 0 No action.

- 1 Asserts INT\_STATUS2\_REG.start\_err\_set.

FIFO Status Register reflects the status of Transmit FIFO and Receive FIFO as shown blow.

tx\_fifo\_full

Transmit FIFO Full. This bit reflects the full condition of Transmit FIFO.

- 1'b0 Transmit FIFO is not full.

- 1'b1 Transmit FIFO is full.

- tx\_fifo\_aempty

Transmit FIFO Almost Empty. This bit reflects the almost empty condition of Transmit FIFO.

- 1'b0 Data words in Transmit FIFO is greater than the TX FIFO Almost Empty Flag attribute.

- 1'b1 Data words in Transmit FIFO is less than or equal to the TX FIFO Almost Empty Flag attribute.

- tx fifo empty

Transmit FIFO Empty. This bit reflects the empty condition of Transmit FIFO.

- 1'b0 Transmit FIFO is not empty has at least one data word.

- 1'b1 Transmit FIFO is empty.

- rx\_fifo\_full

Receive FIFO Full. This bit reflects the full condition of Receive FIFO.

- 1'b0 Receive FIFO is not full.

- 1'b1 Receive FIFO is full.

- rx fifo afull

Receive FIFO Full. This bit reflects the almost full condition of Receive FIFO.

- 1'b0 Data words in Receive FIFO is less than the RX FIFO Almost Full Flag attribute.

- 1'b1 Data words in Receive FIFO is greater than or equal to the RX FIFO Almost Full Flag attribute.

- rx\_fifo\_empty

Receive FIFO Full. This bit reflects the empty condition of Receive FIFO.

- 1'b0 Receive FIFO is not empty has at least one data word.

- 1'b1 Receive FIFO is empty.

The corresponding bits of FLUSH FIFO are shown below:

rxfifo flush

Flush RX FIFO data.

- 0 No action.

- 1 Flush RX FIFO data to empty.

- txfifo flush

Flush TX FIFO data.

- 0 No action.

- 1 Flushes TX FIFO data to empty.

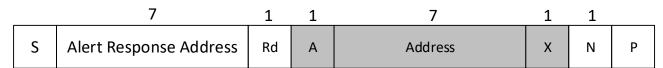

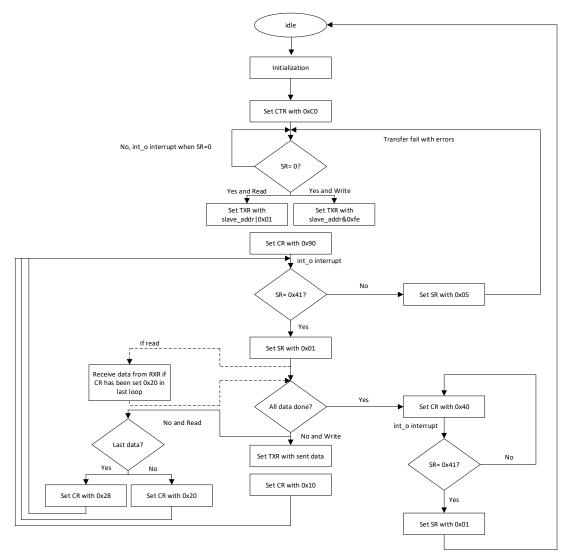

#### 2.4.2. Registers File