# CrossLink-NX QVGA MobileNet Human Identification Using VVML Board

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| Contents                                                                                 | 3  |

|------------------------------------------------------------------------------------------|----|

| Acronyms in This Document                                                                | 8  |

| 1. Introduction                                                                          |    |

| 1.1. Design Process Overview                                                             | Ç  |

| 2. Setting Up the Basic Environment                                                      | 10 |

| 2.1. Tools and Hardware Requirements                                                     | 10 |

| 2.1.1. Lattice Tools                                                                     | 10 |

| 2.1.2. Hardware                                                                          | 10 |

| 2.2. Setting Up the Linux Environment for Machine Training                               | 11 |

| 2.2.1. Installing the NVIDIA CUDA and cuDNN Library for Machine Learning Training on GPU |    |

| 2.2.1.1. Installing the CUDA Toolkit                                                     |    |

| 2.2.1.2. Installing the cuDNN                                                            |    |

| 2.2.2. Setting Up the Environment for Training and Model Freezing Scripts                |    |

| 2.2.2.1. Installing the Anaconda Python                                                  |    |

| 2.2.3. Installing the TensorFlow version 2.1.0                                           |    |

| 2.2.4. Installing the Python Package                                                     |    |

| 3. Dataset Preparation                                                                   |    |

| 3.1. Dataset Information                                                                 |    |

| 3.1.1. Training Set                                                                      |    |

| 3.1.2. Validation set                                                                    |    |

| 3.1.3. Test Set                                                                          |    |

| 4. Training Code Preparation                                                             |    |

| 4.1. Training Code Structure                                                             |    |

| 4.2. Neural Network Architecture                                                         |    |

| 4.2.1. Neural Network Architecture                                                       |    |

| 4.2.2. Face Identification Network Output                                                |    |

| 4.2.3. Training Code Overview                                                            |    |

| 4.2.3.1. Model Configuration                                                             |    |

| 4.2.3.2. Model Building                                                                  |    |

| 4.2.3.3. Training                                                                        |    |

| 4.3. Training from Scratch and/or Transfer Learning                                      |    |

| 5. Evaluating the Model                                                                  |    |

| 5.1. Running Inference on Test Set                                                       |    |

| 6. Creating Binary File with Lattice sensAl                                              |    |

| 7. Hardware Implementation                                                               |    |

| 7.1. Top Level Information                                                               |    |

| 7.1.1. Block Diagram                                                                     |    |

|                                                                                          |    |

| 7.1.2. Push Buttons for Face ID Demo                                                     |    |

| ·                                                                                        |    |

|                                                                                          |    |

|                                                                                          |    |

| 7.2.1. SPI Flash Operation                                                               |    |

| 7.2.2. Pre-processing CNN                                                                |    |

| 7.2.2.1. Masking and Downscaling flow                                                    |    |

| 7.2.2.2. Push Button Control                                                             |    |

| 7.2.3. HyperRAM Operations                                                               |    |

| 7.2.4. Post-Processing CNN                                                               |    |

| 7.2.4.1. REG MODE                                                                        |    |

| 7.2.4.2. CHECK MODE                                                                      |    |

| 7.2.4.3. CLEAR MODE                                                                      |    |

| 7.2.5. Output Screen Display                                                             |    |

| 7.2.5.1. USB Wrapper                                                                     | 43 |

| 7.2.5.2. Inference Time Calculation                                          | 43 |

|------------------------------------------------------------------------------|----|

| 7.2.5.3. Inference Time Display Management                                   | 45 |

| 8. Creating FPGA Bitstream File                                              |    |

| 8.1. Bitstream Generation Using Lattice Radiant Software                     |    |

| 9. Programming the Demo                                                      |    |

| 9.1. Package Folder Structure                                                |    |

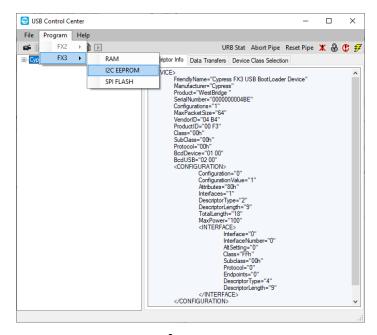

| 9.2. Load Firmware in FX3 I <sup>2</sup> C EEPROM                            |    |

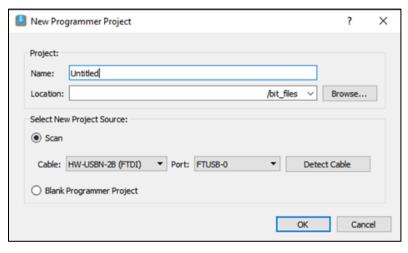

| 9.3. Programming the CrossLink-NX Voice and Vision SPI Flash                 |    |

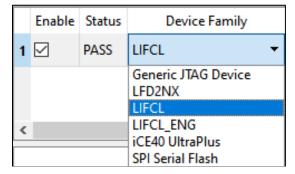

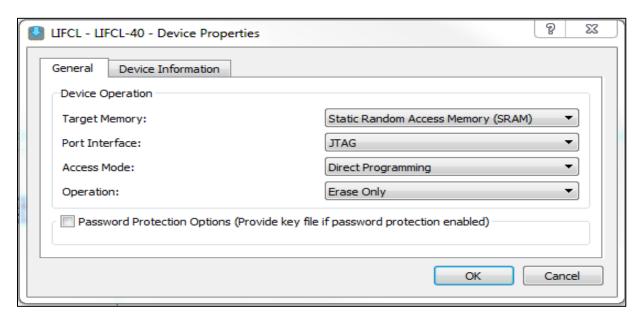

| 9.3.1. Erasing the CrossLink-NX Voice and Vision SRAM Prior to Reprogramming |    |

| 9.3.2. Programming the CrossLink-NX VVML Board                               |    |

| 9.3.3. Programming sensAl Firmware Binary to the CrossLink-NX SPI Flash      |    |

| 10. Running the Demo                                                         |    |

| 10.1. Ideal Conditions for Testing the Demo                                  |    |

| Appendix A. Other Labeling Tools                                             |    |

| References                                                                   |    |

| Technical Support Assistance                                                 | 61 |

| Revision History                                                             | 62 |

# **Figures**

| Figure 1.1. Lattice Machine Learning Design Flow                                       |    |

|----------------------------------------------------------------------------------------|----|

| Figure 2.1. Lattice CrossLink-NX Voice and Vision Machine Learning (VVML) Board, Rev B | 10 |

| Figure 2.2. Download CUDA Repo                                                         |    |

| Figure 2.3. Install CUDA Repo                                                          | 11 |

| Figure 2.4. Fetch Keys                                                                 | 11 |

| Figure 2.5. Update Ubuntu Packages Repositories                                        | 11 |

| Figure 2.6. CUDA Installation                                                          | 12 |

| Figure 2.7. cuDNN Library Installation                                                 | 12 |

| Figure 2.8. Anaconda Installation                                                      | 13 |

| Figure 2.9. Accept License Terms                                                       | 13 |

| Figure 2.10. Confirm/Edit Installation Location                                        |    |

| Figure 2.11. Launch/Initialize Anaconda Environment on Installation Completion         | 13 |

| Figure 2.12. Anaconda Environment Activation                                           | 14 |

| Figure 2.13. TensorFlow Installation                                                   | 14 |

| Figure 2.14. TensorFlow Installation Confirmation                                      | 14 |

| Figure 2.15. TensorFlow Installation Completion                                        | 14 |

| Figure 2.16. Easydict Installation                                                     | 15 |

| Figure 2.17. Opency Installation                                                       | 15 |

| Figure 2.18. Bcolz Installation                                                        | 15 |

| Figure 2.19. Tensorflow-addons Installation                                            | 16 |

| Figure 2.20. Scikit-learn Installation                                                 | 16 |

| Figure 2.21. Tqdm Installation                                                         | 16 |

| Figure 2.22. Albumentations Installation                                               | 16 |

| Figure 3.1. Dataset Format                                                             |    |

| Figure 4.1. Training Code Directory Structure                                          | 18 |

| Figure 4.2. Training Code Flow Diagram                                                 | 22 |

| Figure 4.3. Code Snippet – Input Dataset Path Configuration                            | 22 |

| Figure 4.4. Code Snippet – Model Name and Log Directory                                | 23 |

| Figure 4.5. Code Snippet – Input Image Size Configuration                              | 23 |

| Figure 4.6. Code Snippet – Model Features and Depth Configuration                      | 23 |

| Figure 4.7. Code Snippet – Training Parameters                                         | 23 |

| Figure 4.8. Code Snippet – Pooling Structure                                           | 24 |

| Figure 4.9. Code Snippet – Forward Graph Fire Layer                                    | 25 |

| Figure 4.10. Code Snippet – Forward Graph Output Layer                                 | 25 |

| Figure 4.11. Code Snippet – Forward Graph Triplet Loss                                 | 25 |

| Figure 4.12. Code Snippet: Training                                                    | 26 |

| Figure 4.13. Training Code Snippet for Mean and Scale                                  | 26 |

| Figure 4.14. Training Code Snippet for Identity Shuffling on Epoch End                 | 27 |

| Figure 4.15. Training Code Snippet for On the Fly Augmentation                         | 27 |

| Figure 4.16. Execute Run Script                                                        | 28 |

| Figure 4.17. TensorBoard – Generated Link                                              |    |

| Figure 4.18. TensorBoard                                                               |    |

| Figure 4.19. Model Graph on TensorBoard                                                | 29 |

| Figure 4.20. Example of Checkpoint Data Files at Log Folder                            |    |

| Figure 4.21. Set Pretrained Model Path to init Variable for Transfer Learning          | 30 |

| Figure 5.1. Run Testing                                                                |    |

| Figure 6.1. sensAl – Home Screen                                                       |    |

| Figure 6.2. sensAl – Framework, Device, and Network File Selection                     | 33 |

| Figure 6.3. sensAI – Image Data File Selection                                         | 33 |

| Figure 6.4. sensAl – Update Project Settings                                           | 34 |

| Figure 6.5. Analyze Project                                                            | 34 |

| Figure 6.6. Q Format Settings for Each Laver                                           | 35 |

| Figure 6.7. Compile Project                                                                            | 35 |

|--------------------------------------------------------------------------------------------------------|----|

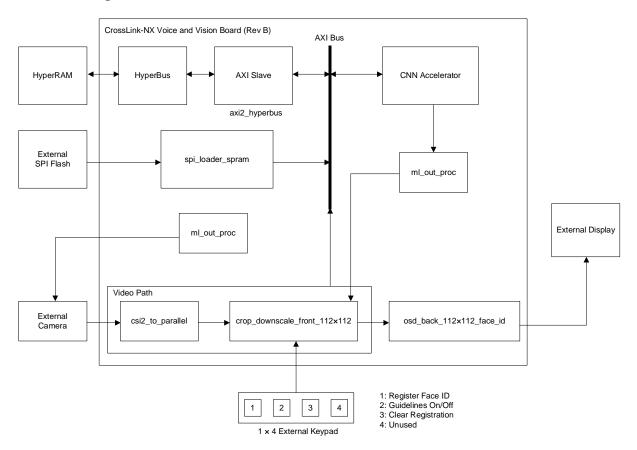

| Figure 7.1. RTL Top Level Block Diagram                                                                | 36 |

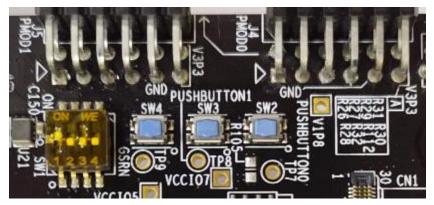

| Figure 7.2. Push Buttons on CrossLink-NX VVML Board for Face ID Demo                                   | 36 |

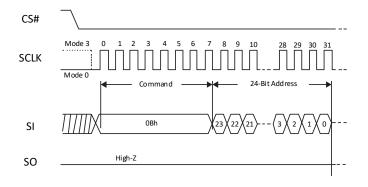

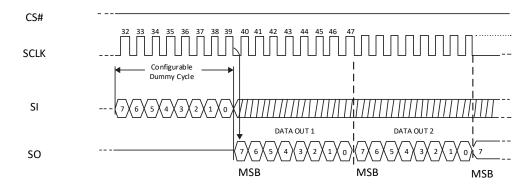

| Figure 7.3. SPI Read Command Sequence                                                                  | 39 |

| Figure 7.4. Masking                                                                                    | 40 |

| Figure 7.5. Downscaling                                                                                |    |

| Figure 7.6. HyperRAM Access Block Diagram                                                              | 42 |

| Figure 7.7. CNN Counter Design                                                                         | 43 |

| Figure 7.8. Frame Counter Design for 16 CNN Frames Average                                             |    |

| Figure 7.9. Average Inference Time Calculation                                                         |    |

| Figure 7.10. Inference Time in Millisecond                                                             |    |

| Figure 7.11. Average Inference Time Value to ASCII Conversion                                          | 45 |

| Figure 7.12. CNN Count Values to ASCII Conversion                                                      |    |

| Figure 7.13. Inference Time in Millisecond Values to ASCII Conversion                                  |    |

| Figure 7.14. Text Address Positions to Display Input Values                                            |    |

| Figure 7.15. Address Locations to Display Individual Frame Time and Inference Time with String in PC   |    |

| Figure 7.16. Bitmap Extraction from Font ROM                                                           |    |

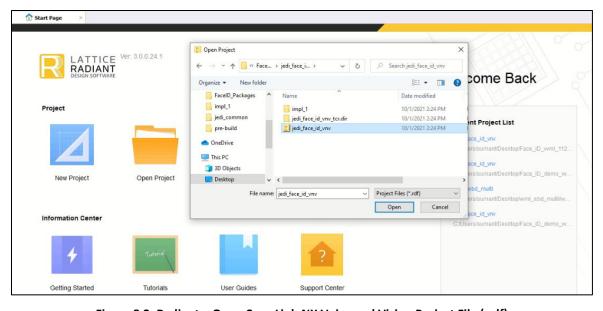

| Figure 8.1. Radiant – Default Screen                                                                   |    |

| Figure 8.2. Radiant – Open CrossLink-NX Voice and Vision Project File (.rdf)                           |    |

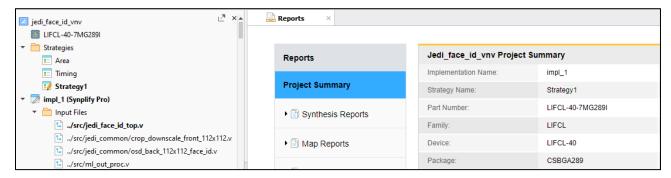

| Figure 8.3. Radiant – Design Load Check After Opening the Project File                                 |    |

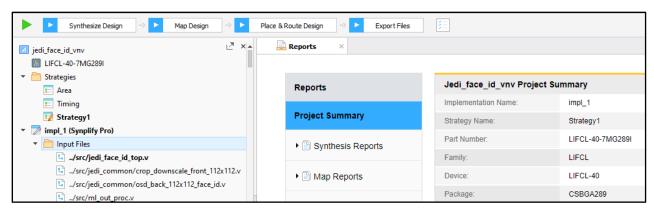

| Figure 8.4. Radiant – Trigger Bitstream Generation                                                     |    |

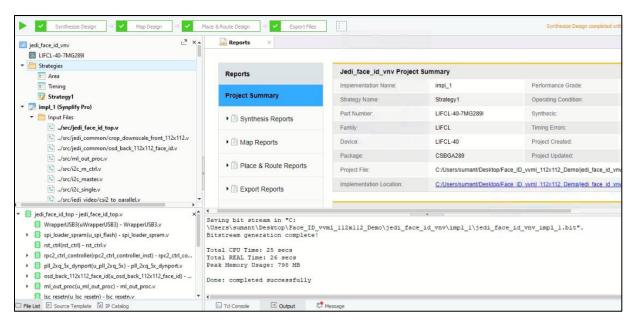

| Figure 8.5. Radiant – Bit File Generation Report Window                                                |    |

| Figure 9.1. Demo Package Folder Structure                                                              |    |

| Figure 9.2. Selecting FX3 I <sup>2</sup> C EEPROM in USB Control Centre                                |    |

| Figure 9.3. Lattice Radiant Programmer Default Screen                                                  |    |

| Figure 9.4. Lattice Radiant Programmer- Device Selection                                               |    |

| Figure 9.5. Lattice Radiant Programmer – Device Operation                                              |    |

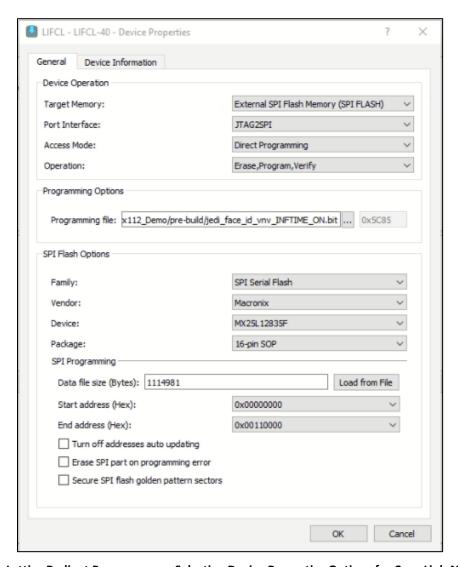

| Figure 9.6. Lattice Radiant Programmer – Selecting Device Properties Options for CrossLink-NX Flashing |    |

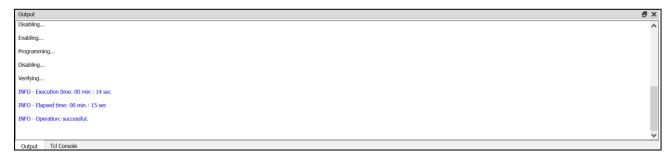

| Figure 9.7. Lattice Radiant Programmer – Output Console                                                |    |

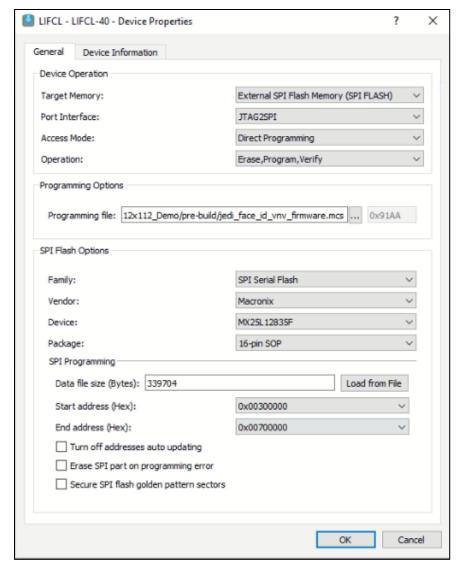

| Figure 9.8. Lattice Radiant Programmer – Selecting Device Properties Options for CrossLink-NX Flashing |    |

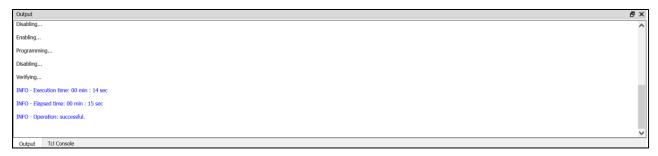

| Figure 9.9. Lattice Radiant Programmer – Output Console                                                |    |

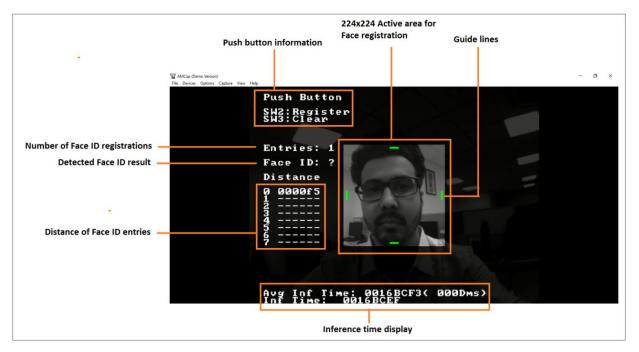

| Figure 10.1. Demo Camera Image                                                                         | 58 |

# **Tables**

| Table 4.1. Face Identification Training Network Topology | 19 |

|----------------------------------------------------------|----|

| Table 7.1. Core Parameter                                | 37 |

| Table 7.2. Push Button Modes                             | 41 |

| Table 7.3. Post-Processing Parameters                    | 42 |

| Table 7.4. Signal Values to ASCII Conversion             |    |

| Table A.1. Other Labeling Tools                          |    |

|                                                          |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym          | Definition                                          |

|------------------|-----------------------------------------------------|

| CNN              | Convolutional Neural Network                        |

| EEPROM           | Electrically Erasable Programmable Read-Only Memory |

| FPGA             | Field-Programmable Gate Array                       |

| I <sup>2</sup> C | Inter-Integrated Circuit                            |

| ML               | Machine Learning                                    |

| MLE              | Machine Learning Engine                             |

| SPI              | Serial Peripheral Interface                         |

| SRAM             | Static Random Access Memory                         |

| USB              | Universal Serial Bus                                |

| VVML             | Voice and Vision Machine Learning                   |

# 1. Introduction

This reference design implements Convolutional Neural Network (CNN) based human face identification application on a low power Lattice FPGA using an image sensor. The training process is completed on a GPU-powered machine to sharpen the CNN to detect points of reference on a human face and measure them to distinguish the differences between people. This design can be used for identification of other objects by modifying the training database.

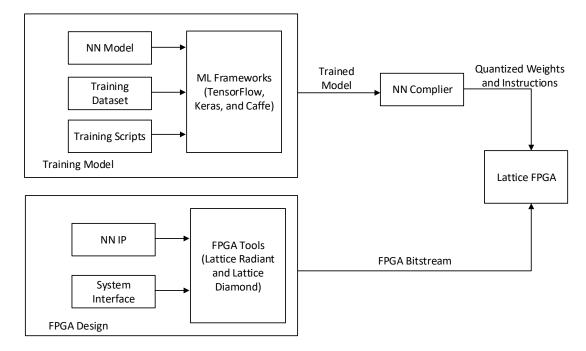

# 1.1. Design Process Overview

The design process involves the following steps:

- 1. Training the model

- Setting up the basic environment

- Preparing the dataset

- Training the machine

- Training the machine and creating the checkpoint data

- Creating the frozen file (\*. pb)

- 2. Compiling Neural Network

- Creating the filter and firmware binary files with Lattice sensAl™ 4.1 program

- 3. FPGA design

- Creating the FPGA Bitstream file

- 4. FPGA Bitstream and Quantized Weights and Instructions

- Flashing the binary and bitstream files to CrossLink™-NX Voice and Vision Machine Learning (VVML) hardware

Figure 1.1. Lattice Machine Learning Design Flow

# 2. Setting Up the Basic Environment

# 2.1. Tools and Hardware Requirements

This section describes the required tools and environment setup for training and model freezing.

#### 2.1.1. Lattice Tools

- Lattice Radiant™ Tool version 2.2 Refer to http://www.latticesemi.com/latticeradiant

- Lattice Radiant Programmer version 3.0 Refer to http://www.latticesemi.com/latticeradiant

- Lattice sensAl Compiler version 4.1 Refer to https://www.latticesemi.com/Products/DesignSoftwareAndIP/AIML/NeuralNetworkCompiler

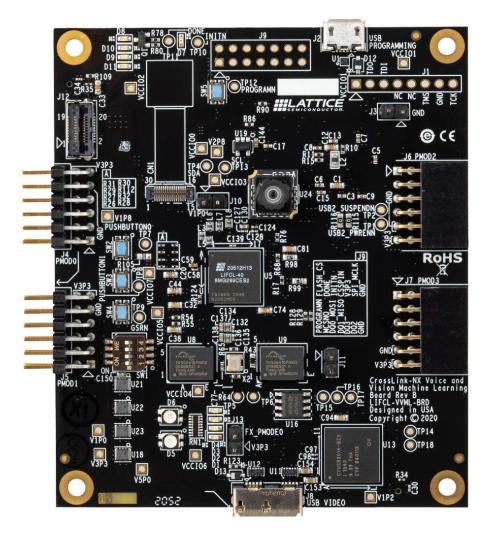

## 2.1.2. Hardware

This design uses the CrossLink-NX Voice and Vision board as shown in Figure 2.1.

• CrossLink-NX Voice and Vision Machine Learning (VVML) Board, Rev B Board.

Figure 2.1. Lattice CrossLink-NX Voice and Vision Machine Learning (VVML) Board, Rev B

# 2.2. Setting Up the Linux Environment for Machine Training

This section describes the steps for NVIDIA GPU drivers and/or libraries for 64-bit Ubuntu 16.04 OS. NVIDIA library and TensorFlow version is dependent on PC and Ubuntu/Windows version.

#### 2.2.1. Installing the NVIDIA CUDA and cuDNN Library for Machine Learning Training on GPU

#### 2.2.1.1. Installing the CUDA Toolkit

To install the CUDA toolkit, run the following commands in the order specified below:

```

$ curl -0

https://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64/cuda-

repo-ubuntu1604_10.1.105-1_amd64.deb

```

```

$ curl -0 https://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64/cuda-repo-ubuntu1604_10.1.105-1_amd64.deb

% Total % Received % Xferd Average Speed Time Time Time Current

Dload Upload Total Spent Left Speed

100 2832 100 2832 0 0 2204 0 0:00:01 0:00:01 --:--- 2205

```

Figure 2.2. Download CUDA Repo

```

$ sudo dpkg -I ./cuda-repo-ubuntu1604 10.1.105-1 amd64.deb

```

```

$ sudo dpkg -i ./cuda-repo-ubuntu1604_10.1.105-1_amd64.deb

Selecting previously unselected package cuda-repo-ubuntu1604.

(Reading database ... 5287 files and directories currently installed.)

Preparing to unpack .../cuda-repo-ubuntu1604_10.1.105-1_amd64.deb ...

Unpacking cuda-repo-ubuntu1604 (10.1.105-1) ...

Setting up cuda-repo-ubuntu1604 (10.1.105-1) ...

The public CUDA GPG key does not appear to be installed.

To install the key, run this command:

sudo apt-key adv --fetch-keys http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64/7fa2af80.pub

```

Figure 2.3. Install CUDA Repo

```

$ sudo apt-key adv --fetch-keys

http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64/7fa2af80.

pub

```

```

$ sudo apt-key adv --fetch-keys http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64/7fa2af80.pub

Executing: /tmp/tmp.a2QZZnTMUX/gpg.1.sh --fetch-keys

http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64/7fa2af80.pub

gpg: key 7FA2AF80: public key "cudatools <cudatools@nvidia.com>" imported

gpg: Total number processed: 1

gpg: imported: 1 (RSA: 1)

```

Figure 2.4. Fetch Keys

\$sudo apt-get update

```

$ sudo apt-get update

Ign:1 http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64 InRelease

Hit:2 http://archive.ubuntu.com/ubuntu xenial InRelease

Get:3 http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64 Release [697 B]

Get:4 http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64 Release [697 B]

Hit:5 http://archive.ubuntu.com/ubuntu xenial-updates InRelease

Hit:6 http://security.ubuntu.com/ubuntu xenial-security InRelease

Hit:7 http://archive.ubuntu.com/ubuntu xenial-backports InRelease

Ign:8 http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64 Packages

Get:8 http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1604/x86_64 Packages [428 kB]

Fetched 429 kB in 1s (386 kB/s)

Reading package lists... Done

```

Figure 2.5. Update Ubuntu Packages Repositories

\$ sudo apt-get install cuda-9-0

```

$ sudo apt-get install cuda-9-0

Reading package lists... Done

Building dependency tree

Reading state information... Done

```

Figure 2.6. CUDA Installation

#### 2.2.1.2. Installing the cuDNN

To install the cuDNN:

- 1. Create NVIDIA developer account: https://developer.nvidia.com.

- 2. Download cuDNN lib: https://developer.nvidia.com/compute/machine-learning/cudnn/secure/v7.1.4/prod/9.0\_20180516/cudnn-9.0-linux-x64-v7.1

- 3. Execute below commands to install cuDNN

```

$ tar xvfcudnn-9.0-linux-x64-v7.1.tgz

$ sudo cp cuda/include/cudnn.h/usr/local/cuda/include

$ sudo cp cuda/lib64/libcudnn* /usr/local/cuda/lib64

$ sudochmoda+r/usr/local/cuda/include/cudnn.h/usr/local/cuda/lib64/libcudnn*

```

```

$ tar xcf cudnn-9.0-linux-x64-v7.1.tgz

cuda/include/cudnn.h

cuda/NVIDIA_SLA_cuDNN_Support.txt

cuda/lib64/libcudnn.so

cuda/lib64/libcudnn.so.7

cuda/lib64/libcudnn.so.7.1.4

cuda/lib64/libcudnn_static.a

$ sudo cp cuda/include/cudnn.h /usr/local/cuda/include

$ sudo cp cuda/lib64/libcudnn* /usr/local/cuda/lib64

$ sudo chmod a+r /usr/local/cuda/include/cudnn.h /usr/local/cuda/lib64/libcudnn*

```

Figure 2.7. cuDNN Library Installation

## 2.2.2. Setting Up the Environment for Training and Model Freezing Scripts

This section describes the environment setup information for training and model freezing scripts for 64-bit Ubuntu 16.04. Anaconda provides one of the easiest ways to perform machine learning development and training on Linux.

## 2.2.2.1. Installing the Anaconda Python

To install the Anaconda and Python 3:

- 1. Go to https://www.anaconda.com/products/individual#download-section.

- 2. Download Python3 version of Anaconda for Linux.

- 3. Run the command below to install the Anaconda environment:

```

$ sh Anaconda3-2019.03-Linux-x86 64.sh

```

**Note:** Anaconda3-<version>-Linux-x86\_64.sh, version may vary based on the release.

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

```

(base) $ sh Anaconda3-2020.07-Linux-x86_64.sh

Welcome to Anaconda3 2020.07

In order to continue the installation process, please review the license agreement.

Please, press ENTER to continue

>>>

```

Figure 2.8. Anaconda Installation

4. Accept the license.

```

Do you accept the license terms? [yes|no] [no] >>> yes

```

Figure 2.9. Accept License Terms

5. Confirm the installation path. Follow the instruction on screen if you want to change the default path.

```

[no] >>> yes

Anaconda3 will now be installed into this location:

/home/user/anaconda3

- Press ENTER to confirm the location

- Press CTRL-C to abort the installation

- Or specify a different location below

[/home/user/anaconda3] >>> /home/user/anaconda3

```

Figure 2.10. Confirm/Edit Installation Location

6. After installation, enter No as shown in Figure 2.11.

```

Preparing transaction: done

Executing transaction: done

installation finished.

Do you wish the installer to initialize Anaconda3

by running conda init? [yes|no]

[no] >>> no

```

Figure 2.11. Launch/Initialize Anaconda Environment on Installation Completion

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 2.2.3. Installing the TensorFlow version 2.1.0

To install the TensorFlow version 2.1.0:

- 1. Activate the conda environment by running the command below:

- \$ source <conda directory>/bin/activate

```

$ source anaconda3/bin/activate

(base) ~$

```

Figure 2.12. Anaconda Environment Activation

2. Install the TensorFlow by running the command below:

```

$ conda install tensorflow-gpu==2.1.0

```

```

$ conda install tensorflow-gpu=2.1.0

Collecting package metadata (current_repodata.json): done

Solving environment: failed with initial frozen solve. Retrying with flexible solve.

Collecting package metadata (repodata.json): done

Solving environment: done

## Package Plan ##

environment location:

added / updated specs:

- tensorflow-gpu=2.1.0

```

Figure 2.13. TensorFlow Installation

3. After installation, enter **Y** as shown in Figure 2.14.

```

The following packages will be downloaded:

py37h7f8727e_2

541 KB

py37h06a4308_0

py37h400218f_0

cryptography-3.4.7

py37hd23ed53_0

904 KB

multidict-5.1.0

py37h27cfd23_2

66 KB

py37h06a4308_0

tensorflow-2.1.0

|gpu_py37h7a4bb67_0

|gpu_py37h6c5654b_0

tensorflow-base-2.1.0

h0d30ee6_0

tensorflow-gpu-2.1.0

157.0 MB

```

Figure 2.14. TensorFlow Installation Confirmation

Figure 2.15 shows TensorFlow installation is complete.

```

Preparing transaction: done Verifying transaction: done Executing transaction: done

```

Figure 2.15. TensorFlow Installation Completion

## 2.2.4. Installing the Python Package

To install the Python package:

- 1. Install Easydict by running the command below:

- \$ conda install -c conda-forge easydict

```

$ conda install -c conda-forge easydict

Collecting package metadata (current_repodata.json): done

Solving environment: done

## Package Plan ##

environment location:

added / updated specs:

- easydict

```

Figure 2.16. Easydict Installation

2. Install opency by running the command below:

\$ conda install -c menpo opencv

```

$ conda install -c menpo opencv

Collecting package metadata (current_repodata.json): done

Solving environment: failed with initial frozen solve. Retrying with flexible solve.

Solving environment: failed with repodata from current_repodata.json, will retry with next repodata source.

Collecting package metadata (repodata.json): done

Solving environment: done

## Package Plan ##

environment location:

added / updated specs:

- opencv

```

Figure 2.17. Opency Installation

3. Install boolz by running the command below:

\$ conda install bcolz

```

$ conda install bcolz

Collecting package metadata (current_repodata.json): done

Solving environment: failed with initial frozen solve. Retrying with flexible solve.

Solving environment: failed with repodata from current_repodata.json, will retry with next repodata source.

Collecting package metadata (repodata.json): done

Solving environment: done

## Package Plan ##

environment location:

added / updated specs:

- bcolz

```

Figure 2.18. Bcolz Installation

4. Install tensorflow-addons by running the command below:

```

$ python -m pip install tensorflow-addons==0.9.1

```

FPGA-RD-02244-1 1

Figure 2.19. Tensorflow-addons Installation

5. Install scikit-learn by running the command below:

```

$ conda install scikit-learn

```

```

$ conda install scikit-learn

Collecting package metadata (current_repodata.json): done

Solving environment: done

## Package Plan ##

environment location:

added / updated specs:

- scikit-learn

```

Figure 2.20. Scikit-learn Installation

6. Install tqdm by running the command below:

```

$ conda install tqdm

```

```

$ conda install tqdm

Collecting package metadata (current_repodata.json): done

Solving environment: done

## Package Plan ##

environment location:

added / updated specs:

- tqdm

```

Figure 2.21. Tqdm Installation

7. Install albumentations by running the command below:

```

$ pip install albumentations

```

Figure 2.22. Albumentations Installation

# 3. Dataset Preparation

This section describes the steps and guidelines used to prepare the dataset to train the Face ID Demo for CrossLink-NX Voice and Vision Machine Learning (VVML) board. Note that this section is for the example reference. The following sections provide the guidelines and/or example which can be used as reference for preparing dataset for given use cases but in no case, Lattice is recommending and/or endorsing any dataset(s). Lattice strongly recommends customers to gather and prepare their own datasets for their end applications.

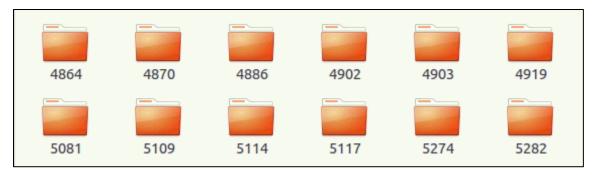

# 3.1. Dataset Information

For Face ID, use the dataset in directory format used in the image classification problem. Each folder in dataset denotes individual class which contains multiple images of that class.

Figure 3.1. Dataset Format

# 3.1.1. Training Set

- For the Face ID demo, use the MS-Celebs-1m dataset https://www.microsoft.com/en-us/research/project/ms-celeb-1m-challenge-recognizing-one-million-celebrities-real-world/ and https://github.com/EB-Dodo/C-MS-Celeb

- The original dataset does not have aligned faces. You can download the face aligned dataset in https://drive.google.com/file/d/1X202mvYe5tiXFhOx82z4rPiPogXD435i/view, or align faces using the custom scripts and cv2 operations.

#### 3.1.2. Validation set

• The subset of MS-celebs dataset is used as validation set which has 64 identities, with total of 4472 images.

## 3.1.3. Test Set

- As test set, use the subset from the LFW Face dataset (http://vis-www.cs.umass.edu/lfw/).

- The test set contains total of 6000 pairs of images, where 3000 pairs are of same person and another 3000 pairs of different persons.

# 4. Training Code Preparation

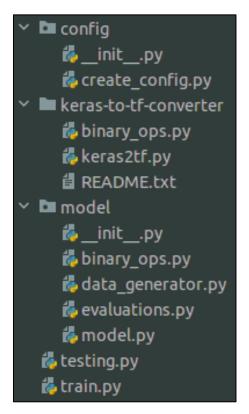

# 4.1. Training Code Structure

Download the Lattice Face ID demo training code. Figure 4.1 shows the directory structure of the Face ID demo:

Figure 4.1. Training Code Directory Structure

# 4.2. Neural Network Architecture

## 4.2.1. Neural Network Architecture

This section provides information on the Convolution Neural Network configuration of the Face Identification design.

**Table 4.1. Face Identification Training Network Topology**

|        | Image        | e Input (112 × 112 × 1)                                 |

|--------|--------------|---------------------------------------------------------|

| Fire 1 | DWConv3 – 40 | Conv3 - # where:                                        |

|        | BN           | Conv3 = 3 × 3 Convolution filter Kernel size            |

|        | ReLU         | # = The number of filter                                |

|        | Maxpool      | DWConv3 – 32- # where:                                  |

|        | Conv1 – 40   | DWConv3 = Depth wise convolution filter with 3 × 3 size |

|        | BN           | # = The number of filter                                |

|        | ReLU         | Conv1 – 32- # where:                                    |

| Fire 2 | DWConv3 – 40 | Conv1 = 1 × 1 Convolution filter Kernel size            |

|        | BN           | # = The number of filter                                |

|        | ReLU         |                                                         |

|        | Conv1 – 40   | For example, Conv3 – 16 = 16 3 × 3 convolution filters  |

|        | BN           |                                                         |

|        | ReLU         | BN – Batch Normalization                                |

| Fire 3 | DWConv3 – 60 |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

|        | Maxpool      |                                                         |

|        | Conv1 – 60   |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

| Fire 4 | DWConv3 – 60 |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

|        | Conv1 – 60   |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

| Fire 5 | DWConv3 – 80 |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

|        | Maxpool      |                                                         |

|        | Conv1 – 80   |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

| Fire 6 | DWConv3 – 80 |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

|        | Conv1 – 80   |                                                         |

|        | BN           |                                                         |

|        | ReLU         |                                                         |

|         | Image I       |

|---------|---------------|

| Fire 7  | DWConv3 – 100 |

|         | BN            |

|         | ReLU          |

|         | Maxpool       |

|         | Conv1 – 100   |

|         | BN            |

|         | ReLU          |

| Fire 8  | DWConv3 – 40  |

|         | BN            |

|         | ReLU          |

|         | Conv1 – 40    |

|         | BN            |

|         | ReLU          |

| Dropout | Dropout – 0.3 |

| E_Dense | Dense – 128   |

- In Table 4.1, the layer contains convolution (Conv), batch normalization (BN), ReLU, and pooling layers.

- Layer information

- Convolutional Layer

In general, the first layer in a CNN is always a convolutional layer. Each layer consists of number of filters (sometimes referred as kernels) which convolves with input layer/image and generates activation map (that is feature map). This filter is an array of numbers (the numbers are called weights or parameters). Each of these filters can be thought of as feature identifiers, like straight edges, simple colors, curves, and other high-level features. For example, the filters on the first layer convolve around the input image and "activate" (or compute high values) when the specific feature (say curve) it is looking for is in the input volume.

#### ReLU (Activation layer)

It is the convention to apply a nonlinear layer (or activation layer) immediately after each conv layer. The purpose of this layer is to introduce nonlinearity to a system that basically has just been computing linear operations during the conv layers (element wise multiplications and summations). In the past, nonlinear functions like tanh and sigmoid were used, but researchers found out that ReLU layers work far better because the network is able to train a lot faster (because of the computational efficiency) without making a significant difference in accuracy. The ReLU layer applies the function f(x) = max(0, x) to all of the values in the input volume. In basic terms, this layer just changes all the negative activations to 0. This layer increases the nonlinear properties of the model and the overall network without affecting the receptive fields of the conv layer.

#### Pooling Layer

After some ReLU layers, you may choose to apply a pooling layer. It is also referred to as a down sampling layer. In this category, there are also several layer options, with Maxpooling being the most popular. This basically takes a filter (normally of size  $2 \times 2$ ) and a stride of the same length. It then applies it to the input volume and outputs the maximum number in every sub region that the filter convolves around.

The intuitive reasoning behind this layer is that once we know that a specific feature is in the original input volume (there is a high activation value), its exact location is not as important as its relative location to the other features. As you can imagine, this layer drastically reduces the spatial dimension (the length and the width change but not the depth) of the input volume. This serves two main purposes. The first is that the number of parameters or weights is reduced by 75%, thus lessening the computation cost.

The second is that it controls over fitting. This term refers to when a model is so tuned to the training examples that it is not able to generalize well for the validation and test sets. A symptom of over fitting is having a model that gets 100% or 99% on the training set, but only 50% on the test data.

#### Batch Normalization Layer

Batch normalization layer reduces the internal covariance shift. To train a neural network, some preprocessing to the input data are performed. For example, you could normalize all data so that it resembles a normal distribution (that means, zero mean and a unitary variance). This prevents the early saturation of non-linear activation functions such as sigmoid, assures that all input data is in the same range of values, and others. An issue, however, appears in the intermediate layers because the distribution of the activations is constantly changing during training. This slows down the training process because each layer must learn to adapt them to a new distribution in every training step. This is known as internal covariate shift.

Batch normalization layer forces the input of every layer to have approximately the same distribution in every training step by following the process below during training:

- a. Calculate the mean and variance of the layers input.

- b. Normalize the layer inputs using the previously calculated batch statistics.

- c. Scales and shifts in order to obtain the output of the layer.

This makes the learning of layers in the network more independent of each other and allows you to be carefree about weight initialization, works as regularization in place of dropout and other regularization techniques.

#### Drop-out layer

Dropout layers have a very specific function in neural networks. After training, the weights of the network are so tuned to the training examples they are given that the network do not perform well when given new examples. The idea of dropout is simplistic in nature. This layer *drops out* a random set of activations in that layer by setting them to zero. It forces the network to be redundant. That means the network should be able to provide the right classification or output for a specific example even if some of the activations are dropped out. It makes sure that the network isn't getting too fitted to the training data and thus helps alleviate the over fitting problem. An important note is that this layer is only used during training, and not during test time.

#### Fully connected layer

This layer basically takes an input volume (whatever the output is of the conv or ReLU or pool layer preceding it) and outputs an N dimensional vector where N is the number of classes that the program must choose from.

#### Quantization

Quantization is a method to bring the neural network to a reasonable size, while also achieving high performance accuracy. This is especially important for on-device applications, where the memory size and number of computations are necessarily limited. Quantization for deep learning is the process of approximating a neural network that uses floating-point numbers by a neural network of low bit width numbers. This dramatically reduces both the memory requirement and computational cost of using neural networks.

The architecture above provides nonlinearities and preservation of dimension that help to improve the robustness of the network and control over fitting.

## 4.2.2. Face Identification Network Output

The Face Identification model gives an output of 128 embeddings.

# 4.2.3. Training Code Overview

Figure 4.2. Training Code Flow Diagram

Training code can be divided into below parts:

- Model Configuration

- Model Building

- Data Preparation

- Training for overall execution flow

The details of each part can be found in the subsequent sections.

# 4.2.3.1. Model Configuration

The following is a summary of the configurable parameters in the *config/create\_config.py* file:

Dataset Configuration

```

cfg.dataset_path = "FaceID-datasets/ms-celebs-1m/"

cfg.validation_set = "FaceID-datasets/validation-set/"

cfg.test_set = "FaceID-datasets/test-set/"

```

Figure 4.3. Code Snippet – Input Dataset Path Configuration

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

22

Model Properties

```

cfg.MODEL_NAME = 'Face_Identification'

cfg.LOG_PATH = "logs"

```

Figure 4.4. Code Snippet - Model Name and Log Directory

- Image Size

- Change cfg.IMAGE\_WIDTH and cfg.IMAGE\_HEIGHT to configure Image size (width and height) if required.

```

cfg.IMAGE_WIDTH = 112

cfg.IMAGE_HEIGHT = 112

cfg.N_CHANNELS = 1

```

Figure 4.5. Code Snippet - Input Image Size Configuration

• Model Configuration

```

cfg.FILTER_DEPTHS = [40, 40, 60, 60, 80, 80, 100, 40]

cfg.EARLY_POOLING = True

cfg.USE_CONV3 = True

```

Figure 4.6. Code Snippet – Model Features and Depth Configuration

```

cfg.EPOCHS = 120

cfg.QUANT_RANGE = (0, 2)

cfg.FEATURES = 128

cfg.BATCHSIZE = 256

cfg.GPUID = 0

cfg.LEARNING_RATE = 0.01

cfg.REDUCELRONPLATEAU = True

cfg.TEST_BATCHSIZE = 64

cfg.IS_CROP = False

```

Figure 4.7. Code Snippet – Training Parameters

- You can configure the number of layers by adding and removing the number of depth in FILTER\_DEPTHS.

- FEATURES denote how many values you need at embedding the layer.

- If you set S CROP to true, images are zoomed in and used for training.

- REDUCELRONPLATEAU configures auto-reducing learning rate if loss is not reducing at some point.

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 4.2.3.2. Model Building

SqueezeDet class constructor builds model, which is divided into the following sections:

## **Forward Graph**

- The CNN architecture consists of Convolution, Batch Normalization, ReLU, and Maxpool layers.

- Forward graph consists of eight fire layers as described in Table 4.1.

- You can set the pooling structure in *models/model.py* as per the depth you selected.

```

if config.EARLY_POOLING:

if depth_length == 6:

self.pooling = [True, True, True, False, True, False]

elif depth_length == 7:

self.pooling = [True, False, True, False, True, False, True]

elif depth_length == 8:

self.pooling = [True, False, True, False, True, False, True, False]

elif depth_length == 9:

self.pooling = [True, False, True, True, False, False, True, False, False, False]

elif depth_length == 12:

self.pooling = [True, False, False, True, False, True, False, True, False, False, False]

else:

if depth_length == 6:

self.pooling = [True, False, True, True, True, False]

elif depth_length == 7:

self.pooling = [True, False, True, False, True, False, True]

elif depth_length == 8:

self.pooling = [True, False, True, False, True, False, True, False]

elif depth_length == 9:

self.pooling = [True, False, True, False, True, False, True, False, False]

else:

self.pooling = [True, False, True, False, True, False, True, False, False]

else:

self.pooling = [True, False, False, True, False, True, False, True, False, False]

```

Figure 4.8. Code Snippet – Pooling Structure

You can mark the layer index True if you want pooling in that index.

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 4.9. Code Snippet – Forward Graph Fire Layer

• Figure 4.10 shows the generated model using the model configuration you provided in the config file.

Figure 4.10. Code Snippet – Forward Graph Output Layer

- The output layer has dropout, followed by the dense layer with the number of features you set in the *config* file. Note that the Dense layer is normalized by L2 normalization while training and it will be removed while freezing.

- The L2 Normalization calculates the distance of the vector coordinate from the origin of the vector space. The result is positive distance value.

#### Loss Graph and Optimizer

Figure 4.11. Code Snippet – Forward Graph Triplet Loss

- The Tensorflow's TrippletSemiHardLoss is used as loss to normalize embeddings.

- This block is responsible for training the model with the Adam optimizer to reduce all losses.

#### 4.2.3.3. Training

Figure 4.12. Code Snippet: Training

The Fit-generator feeds the data and labels batches to the Keras network and optimizes the weights and biases.

# 4.3. Training from Scratch and/or Transfer Learning

To train the machine:

1. Go to the top/root directory of the Lattice training code from command prompt.

The Model works on 112 × 112 images.

Current Face ID training code uses mean = 0 and scale = 1/128 (0.0078125) in pre-processing step with grayscale images. Mean and scale can be changed in training code @src/dataset/imdb.py as shown in Figure 4.13.

```

img = cv2.imread(self.paths[ID])

img = cv2.cvtColor(img, cv2.COLOR_BGR2GRAY)

img = cv2.resize(img, self.dim)

img = self.__augment(img)

img = img[:, :, None]

img = img / 128.

```

Figure 4.13. Training Code Snippet for Mean and Scale

The triplet data generator trains 10k identities on one epoch at a time and it shuffles the ids on each epoch end to train with next 10k random identities.

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

```

def on_epoch_end(self):

"""Updates indexes after each epoch"""

import random

random.shuffle(self.paths)

for path in self.paths[:self.num_person_per_epoch]:

self.paths1.extend(glob(path + "**"))

self.paths = self.paths1

self.classes = np.unique(np.asarray([path.split('/')[-2] for path in self.paths]))

self.index_mapping = {}

for i, class_id in enumerate(self.classes):

self.index_mapping[class_id] = i

self.n_classes = len(self.classes)

self.indexes = np.arange(len(self.paths))

if self.shuffle:

np.random.shuffle(self.indexes)

self.__len__()

```

Figure 4.14. Training Code Snippet for Identity Shuffling on Epoch End

The data generator performs on the Fly augmentation using the *Albumentation* library. You are basically performing contrast, brightness, and rotation (+-15') for augmentations.

Figure 4.15. Training Code Snippet for On the Fly Augmentation

2. Execute the train.py file to start training.

```

python train.py

Model: "model

Layer (type)

Output Shape

Param #

input (InputLayer)

fire1/expand3x3 (Conv2D)

360

batch_normalization (BatchNo (None, 112, 112, 40)

160

dropout (Dropout)

(None, 7, 7, 40)

(None, 1960)

E_flatten (Flatten)

0

_dense (Dense)

(None, 128)

251008

lambda_8 (Lambda)

(None, 128)

Total params: 530,568

Trainable params: 529,568

Non-trainable params: 1,000

None

Total 692715 with 10000 number of classes found.

Total 8944 with 64 number of classes found.

Train for 1352 steps, validate for 17 steps

Epoch 1/120

1351/1352 [=

Epoch 00001: loss improved from inf to 0.99629, saving model to logs/checkpoints/model.01-1.00.hdf5

```

Figure 4.16. Execute Run Script

3. Start TensorBoard.

```

$ tensorboard -logdir=<log directory of training>

```

For example: tensorboard -logdir='./logs/'.

4. Open the local host port on your web browser.

```

$ tensorboard --logdir logs/tensorboard/train/

Serving TensorBoard on localhost; to expose to the network, use a proxy or pass --bind_all

TensorBoard 2.4.0 at http://localhost:6006/ (Press CTRL+C to quit)

```

Figure 4.17. TensorBoard - Generated Link

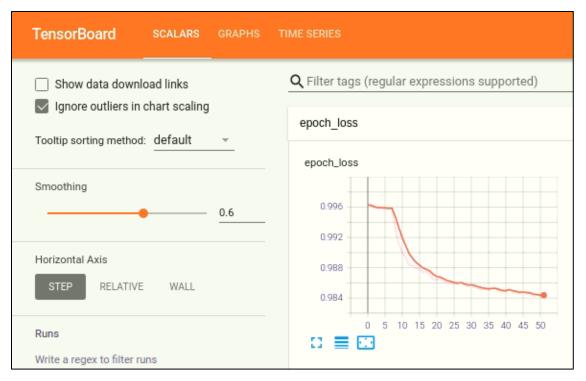

5. Check the training status on TensorBoard.

Figure 4.18. TensorBoard

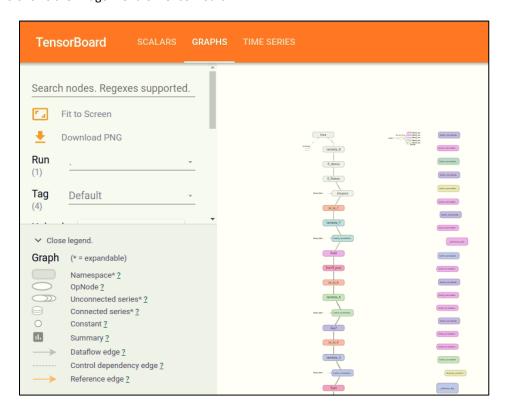

Figure 4.19 shows the image menu of TensorBoard.

Figure 4.19. Model Graph on TensorBoard

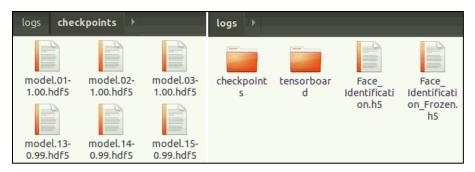

6. Checkpoints are saved at the end of each epoch. At the end of training, code also saves the frozen graph with original graph as shown in Figure 4.20.

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-RD-02244-1.1

29

Figure 4.20. Example of Checkpoint Data Files at Log Folder

7. If you start training with the existing log file, the training resumes from the latest checkpoint. Alternatively, you can specify the pretrained model in the *config* file. The model restores the weights from the pretrained model.

Note that while using the pretrained model for transfer learning, the learning-rate should be set low.

```

cfg.IMAGE_WIDTH = 112

cfg.IMAGE_HEIGHT = 112

cfg.N_CHANNELS = 1

cfg.init = None # "<Pretrained H5 file path>"

cfg.FILTER_DEPTHS = [40, 40, 60, 60, 80, 80, 100, 40]

```

Figure 4.21. Set Pretrained Model Path to init Variable for Transfer Learning

# 5. Evaluating the Model

This section describes the procedure on how to calculate the model performance in terms of correct detection percentage.

# 5.1. Running Inference on Test Set

The Face Identification code contains the *testing.py* script under root directory. It takes the input model and uses the configuration created for training to run the testing on the test set.

```

$ python testing -model <Model Path>

```

Figure 5.1. Run Testing

The testing results also suggest optimal threshold for deployment.

# Creating Binary File with Lattice sensAl

This chapter describes how to generate the binary file using the Lattice sensAl version 4.1 program.

Figure 6.1. sensAI - Home Screen

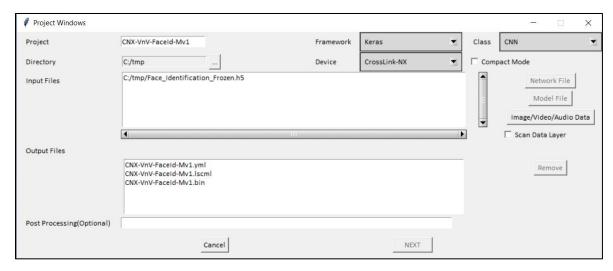

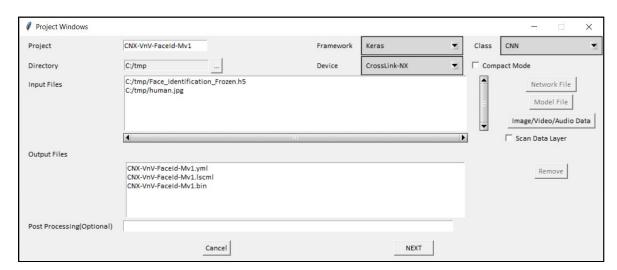

To create the project in the sensAl tool:

- Click File > New.

- 2. Enter the following settings:

- Project Name

- Framework Keras

- Class CNN

- Device CrossLink-NX

- 3. Click Network File and select the network (h5) file.

Figure 6.2. sensAl – Framework, Device, and Network File Selection

4. Click Image/Video/Audio Data and select the image input file.

Figure 6.3. sensAI - Image Data File Selection

- 5. Click Next.

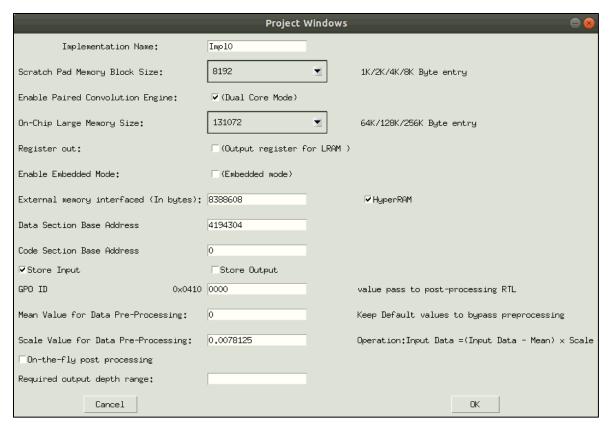

- 6. Configure your project settings as shown in Figure 6.4.

- Mean Value for Data Pre-Processing 0

- Scratch Pad Memory Block Size 8192

- On-Chip Memory Block Size 131072

- Scale Value for Data Pre-Processing **0.0078125**

- Data Selection Base Address 4194304

Figure 6.4. sensAI - Update Project Settings

- 7. Click **OK** to create the project.

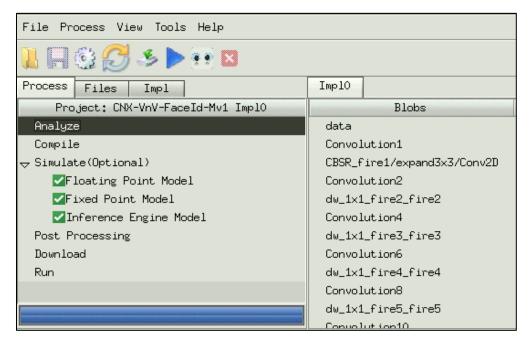

- 8. Double-click Analyze.

Figure 6.5. Analyze Project

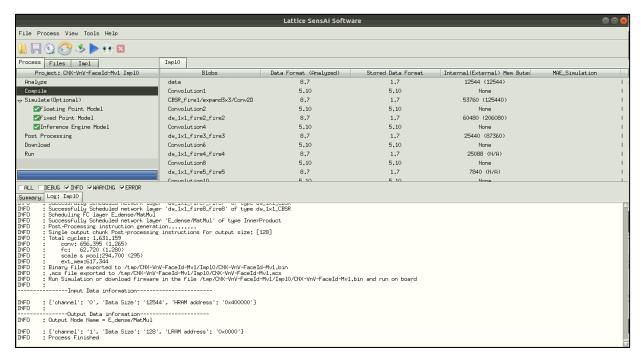

9. Confirm the Q format of each layer as shown in Figure 6.6.

| Imp10                       |                        |                    |                              |

|-----------------------------|------------------------|--------------------|------------------------------|

| Blobs                       | Data Format (Analyzed) | Stored Data Format | Internal(External) Mem Byte: |

| data                        | 8,7                    | 1.7                | 12544 (12544)                |

| Convolution1                | 5.10                   | 5,10               | None                         |

| CBSR_fire1/expand3x3/Conv2D | 8,7                    | 1.7                | 53760 (125440)               |

| Convolution2                | 5.10                   | 5,10               | None                         |

| dw_1x1_fire2_fire2          | 8,7                    | 1.7                | 60480 (206080)               |

| Convolution4                | 5.10                   | 5,10               | None                         |

| dw_1x1_fire3_fire3          | 8,7                    | 1.7                | 25440 (87360)                |

| Convolution6                | 5.10                   | 5,10               | None                         |

| dw_1x1_fire4_fire4          | 8,7                    | 1.7                | 25088 (N/A)                  |

| Convolution8                | 5.10                   | 5,10               | None                         |

| dw_1x1_fire5_fire5          | 8,7                    | 1.7                | 7840 (N/A)                   |

| Convolution10               | 5.10                   | 5,10               | None                         |

| dw_1x1_fire6_fire6          | 8,7                    | 1.7                | 7840 (N/A)                   |

| Convolution12               | 5.10                   | 5,10               | None                         |

| dw_1x1_fire7_fire7          | 8,7                    | 1.7                | 2548 (N/A)                   |

| Convolution14               | 5.10                   | 5,10               | None                         |

| dw_1×1_fire8_fire8          | 8,7                    | 1,7                | 980 (N/A)                    |

| E_dense/BiasAdd             | 8,7                    | 5.10               | 256 (N/A)                    |

Figure 6.6. Q Format Settings for Each Layer

10. Double-click **Compile** to generate the firmware and filter binary file.

Figure 6.7. Compile Project

The Firmware bin file location is displayed in the compilation log. Use the generated firmware bin on hardware for testing.

# 7. Hardware Implementation

# 7.1. Top Level Information

# 7.1.1. Block Diagram

Figure 7.1. RTL Top Level Block Diagram

#### 7.1.2. Push Buttons for Face ID Demo

Figure 7.2 shows the CrossLink-NX VVML board (Rev B). As shown in Figure 7.2, the SW2 push button is used for Registration and SW3 is used for clearing previously registered data. Refer to Push Button Control section for more information.

Figure 7.2. Push Buttons on CrossLink-NX VVML Board for Face ID Demo

## 7.1.3. Operational Flow

- The CNN module is configured with the help of a binary (mcs) sequence command code file, which is generated by the Lattice Machine Learning software tool.

- The command code is written to *spi\_loader\_spram*, which further stores it in HyperRAM through AXI before the execution of CNN Accelerator IP Core starts.

- The external camera configured using i2c\_single logic block captures the raw image and shares it to the csi2\_to\_parallel module. This module separates the R, G, and B pixels from the raw data.

- The RGB data from the *csi2\_to\_parallel* module is downscaled to 112 × 112 image resolution by the *crop\_downscale\_front\_112x112* module to match CNN's input resolution. This data is written into HyperRAM memory through *axi2\_hyperbus* through the *axi\_ws2m* AXI interface module.

- After the command code and input data are available to CNN Accelerator from HyperRAM, the IP Core starts inference at the rising edge of ML start signal.

- The push button control logic is managed by the *crop\_downscale\_front\_112x112* module. The registered Face IDs are stored by the *ml out proc* module.

- The output data of CNN is passed to *ml\_out\_proc* for post processing. ml\_out\_proc now compares the CNN results with initially stored face identifications and passes valid detected Face ID/index and distance to external display module *osd\_back\_112x112\_face\_id* through the *crop downscale* module. The output display can be observed in the video player AMCap software.

#### 7.1.4. Core Customization

### **Table 7.1. Core Parameter**

| Constant         | Default<br>(Decimal) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUM_FEAT         | 128                  | Number of features available in CNN output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| FRAC_POS         | 10                   | Fraction Part Width in Q-Format representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| DIST_THRESH      | 45                   | Indicates Distance Threshold value for Face ID detection output                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| EN_INF_TIME      | 0                    | Enable Timing measurement logic  By default, it is zero and the memory file used is face_id_dissplay.mem.  If assigned 1, timing measurement is enabled and the memory file used is face_id_display_INF.mem.  In order to configure the respective memory file, follow the below steps  1. Open dpram8192x8.ipx from the File List in Radiant.  2. Click Browse Memory File from the Initialization section.  3. Update mem file path:  • For 0 - /src/jedi_common/face_id_display.mem  • For 1 - /src/jedi_common/face_id_display_INF.mem |  |  |

| INF_MULT_FAC     | 19883                | Inference time multiplying factor calculated as per CNN clock frequency and using Q-Format (Q1.31).  CNN Clock Frequency = 108 MHz  Hence, CNN clock period  = $1/(108 \times 10^{-6}) \mu s$ = $0.000009259 ms$ Now, Q1.31 = $0.000009259 \times 2^{31} = \sim 19883$                                                                                                                                                                                                                                                                     |  |  |

| FLASH_START_ADDR | 24'h300000           | SPI Flash Read Start Address (keep the same address in Programmer while loading the firmware file) For example, for the current start address, programmer address should be: 0x00300000.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| FLASH_END_ADDR   | 24'h700000           | SPI Flash Read End Address (keep the same address in Programmer while loading the firmware file). The address must be in multiple of 512 bytes. For example, for the current end address, programmer address should be: 0x00700000.                                                                                                                                                                                                                                                                                                        |  |  |

| Constant          | Default<br>(Decimal) | Description                                                                                                                      |  |  |  |

|-------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | Cons                 | tant Parameters (Not to be modified)                                                                                             |  |  |  |

| PIC_WIDTH         | 112                  | Picture Pixel Width (CNN Input)                                                                                                  |  |  |  |

| PIC_HEIGHT        | 112                  | Picture Pixel Height (CNN Input)                                                                                                 |  |  |  |

| HYPERRAM_BASEADDR | 32'h400000           | Indicates HyperRAM starting Base address location value. This should match in the sensAl compiler while generating the firmware. |  |  |  |

## 7.2. Architecture Details

## 7.2.1. SPI Flash Operation

The RTL module *spi\_loader\_spram* provides SPI Flash read operation and writes that data into HyperRAM through the AXI interface. It reads from SPI Flash as soon as the board gets powered up, the .bit and .bin files are loaded in the expected addresses.

- Expected Address for .bit file (Programmer) 0x0000000 0x00110000

- Expected Address for Firmware file (Programmer) FLASH\_START\_ADDR to FLASH\_END\_ADDR

Typical sequence of SPI Read commands for SPI Flash MX25L12833F is implemented using FSM in RTL as per below flow of operation.

- After FPGA Reset, RELEASE FROM DEEP POWER DOWN command (0xAB) is passed to SPI Flash memory. RTL then

waits for 500 clock cycle for SPI flash to come into Stand By mode, if it is in Deep Power Down mode.

- RTL sends FAST READ command code (0x0B) on SPI MOSI signal for indication of Read Operation to SPI Flash.

- RTL sends three Bytes of Address on SPI MOSI channel which determines the location in SPI flash from the position the data needs to be read.

- This SPI Flash has eight Dummy cycles as wait duration before read data appears on MISO channel. After waiting for eight dummy cycles, the RTL code starts reading data.

- This read sequence is shown in Figure 7.3. The SPI Interface Signal Mapping with RTL signals are as follows

- CS (Chip Select) => SPI\_CSS

- SCLK (Clock) => SPI CLK

- SI (Slave In) => SPI MOSI

- SI (Slave Out) => SPI MISO

- The Read Data on MISO signal is stored in a FIFO in RTL, which then reads the data in multiple of 512 bytes. After 512 bytes chip select is deasserted, the AXI FSM state is activated.

Figure 7.3. SPI Read Command Sequence

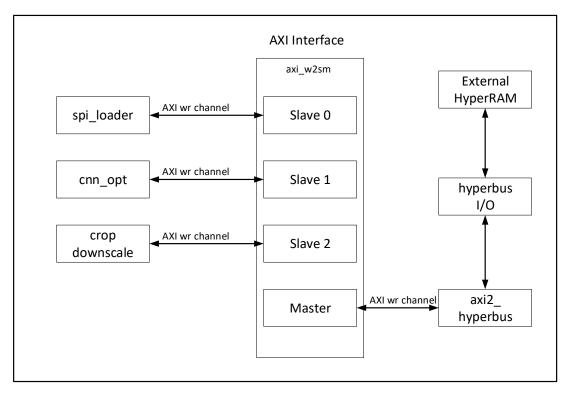

- AXI logic reads the data from FIFO in bursts of four on the AXI write channel, with each burst having 128 bytes.

- In accessing the HyperRAM, the axi\_ws2m module is used as a Muxing module among the multiple input slave AXI interfaces as shown in Figure 7.6. The spi\_loader\_spram module is considered as SLAVE 0 and given priority to write into HyperRAM. The MASTER Interface connects to the axi2\_hyperbus module, which provides output interface for accessing HyperRAM.

- After writing to HyperRAM is complete, the 512 bytes are fetched from the SPI Flash using the same command sequence as explained above until the FLASH\_END\_ADDR is reached.

#### 7.2.2. Pre-processing CNN

The pre-processing operations are mainly handled by the *crop\_downscale\_front\_112x112* module as mentioned below:

- This module mainly crops the incoming image to 224 × 224 image data and further generates downscaled input of 112 × 112 image data for the CNN IP input.

- Manages the control logic for SW2 and SW3 push buttons.

- Provides content for the output screen display to the osc back 112x112 face id module

- Calculates the inference time of theCNN IP

The output screen display and inference time management are explained in the Output Screen Display section.

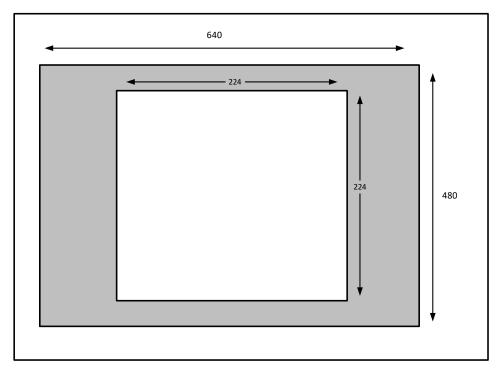

#### 7.2.2.1. Masking and Downscaling flow

- Image data values for each pixel are fed serially line by line for an image frame from csi2 to parallel block.

- These values are considered as valid only when horizontal and vertical masks are inactive. Mask parameters set to mask out boundary area of VGA resolution 640x480 to 224x224 are shown below.

- Left masking start = 208

- Right masking end = 432 (Obtained as 208+224)

- Top masking start = 128

- Bottom masking end = 352 (Obtained as 128+224)

© 2021-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-RD-02244-1.1

Figure 7.4 shows the image obtained after masking.

Figure 7.4. Masking

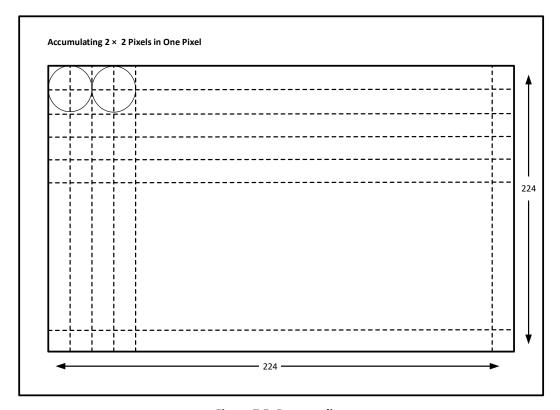

• This  $224 \times 224$  frame image is downscaled into a  $112 \times 112$  resolution image as shown in the **Figure 7.5** by accumulating  $2 \times 2$  pixels into single pixel. For example,  $224/2 \times 224/2 = 112 \times 112$ .

Figure 7.5. Downscaling

• The accumulated value is written in the Frame Buffer, which is a True Dual-Port RAM. The accumulated pixel values for the 2 × 2 grids are stored in the same memory location. When data is read from memory, each RGB value is divided by four (that is, the area of the 2 × 2 grid) to take the average of the 2 × 2 grid matrix.

The data from memory is read and stored in HyperRAM for CNN input through  $axi2\_hyperbus$ , through the  $axi\_w2sm$  module which acts as an AXI interface to write data from slave ( $crop\_downscale\_front\_112x112$ ) to the master HyperRAM. This process is described in the HyperRAM Operations section.

#### 7.2.2.2. Push Button Control

The information of the SW2 and SW3 push buttons connected on CrossLink-NX VVML board is passed into this module. Based on the button pressed, this module defines the following operational modes:

**Table 7.2. Push Button Modes**

| Push<br>Buttons | Mode  | Description                  |

|-----------------|-------|------------------------------|

| SW2             | REG   | Indicates Registration mode. |

| SW3             | CLEAR | Indicates Clear mode.        |

- The registration mode is used to register the user faces for identification purposes. A maximum eight user faces can be registered.

- The check mode is used by the demo to check/identity the new face by comparing with the previously registered face, by default, when no button is pressed.

- The green guide lines are always enabled in display. They mainly indicate the active area inside the 224 × 224 frame, where in you have to keep the face close to the camera for registration.

- The clear mode is used to clear all registrations and previous output results. Upon pressing the SW3 push button, the values displayed in Output also gets cleared and you can now initiate new registration process again.

This module manages the logic to Calculate Inference time of CNN IP as per parameter EN\_INF\_TIME passed from design top. It also collects the outputs from the post-processing module, inference time values, and shares the same with the output screen display block for display in the AMCap video software.

#### 7.2.3. HyperRAM Operations

The CrossLink-NX VVML board uses external HyperRAM for faster data transfer mechanism among the internal blocks and enhances the system performance. The *crop\_downscale\_front\_112x112* module uses HyperRAM to store the downscaled image data.

- The 640  $\times$  480 image is distributed into 224 horizontal and 224 vertical lines, and each block consists of 2  $\times$  2 pixels as shown in Figure 7.5. Thus, there are total 112  $\times$  112 pixel values for the downscaled image.

- Primarily, the *crop\_downscale\_front\_112x112* module stores 112 values into a local FIFO for all 112 horizontal blocks. Later, this stored data is written to HyperRAM through the AXI write data channel.

- When final data is written out, 112 × 112 pixels are initially stored into HyperRAM starting from the base address

- The 112 × 112 pixel values stored in HyperRAM are serially obtained by the CNN engine after getting command sequence through the AXI interface.

- In order for the *crop\_downscale\_front\_112x112* module to access HyperRAM for operations explained above, the *axi\_ws2m* module functions as a Muxing module for multiple input slave AXI interfaces as shown in Figure 7.6.

- For the internal blocks to access HyperRAM, the axi\_ws2m module considers the spi\_loader\_spram module as SLAVE 0, the cnn\_opt module as SLAVE 1, crop\_downscale\_front\_112x112 module as SLAVE2, and the MASTER connects these slaves to the axi2\_hyperbus module.

- The priority to select write channel is given, respectively, to the SPI loader slave, CNN slave, and crop-downscale slave. Whenever valid address is available from the respective Slave on its write address channel, that slave is given access of master channel if other priority slaves are not accessing it. Thus, when valid write address is obtained from the *crop\_downscale\_front\_112x112* module, access is given to Slave 2 to use HyperRAM.

FPGA-RD-02244-1 1

Figure 7.6. HyperRAM Access Block Diagram