# subLVDS to MIPI CSI-2 Image Sensor Bridge with CrossLink-NX

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| Acronyms in This Document                         | 5  |

|---------------------------------------------------|----|

| 1. Introduction                                   |    |

| 1.1. Supported Device, IP, and Software           | 6  |

| 1.2. Features                                     | 6  |

| 1.3. Block Diagram and Clock Distribution         | 6  |

| 1.4. RX and TX Permutations                       | 7  |

| 2. Parameters and Port List                       | 9  |

| 2.1. Synthesis Directives                         | 9  |

| 2.2. Simulation Directives                        | 11 |

| 2.3. Top-Level I/O                                | 12 |

| 3. Design and Module Description                  | 14 |

| 3.1. sensor_sync                                  | 14 |

| 3.2. rx_sublvds                                   | 14 |

| 3.3. trim_ctrl                                    | 17 |

| 3.4. pixel2byte                                   | 20 |

| 3.5. lane_ctrl                                    | 22 |

| 3.5.1. Communication Control                      |    |

| 3.5.2. LP-HS Control in Continuous Clock Mode     |    |

| 3.5.3. LP-HS Control in Non-Continuous Clock Mode | 23 |

| 3.5.4. Bus Width Conversion                       |    |

| 3.6. tx_dphy                                      | 26 |

| 3.7. int_gpll                                     |    |

| 3.8. i2c_slave                                    |    |

| 3.9. int_osc                                      | 32 |

| 4. Design and File Modification by User           | 33 |

| 4.1. Top-level RTL                                | 33 |

| 5. Design Simulation                              | 34 |

| 6. Design Debug on Hardware                       | 37 |

| 6.1. Top-Level                                    |    |

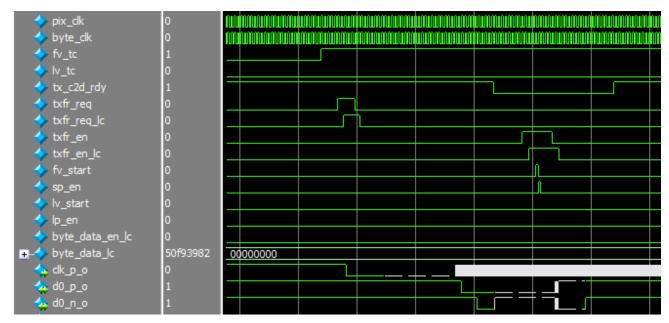

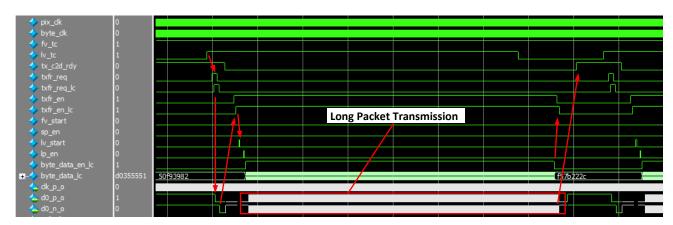

| 6.2. D-PHY TX Control                             | 37 |

| 7. Known Limitations                              |    |

| 8. Design Package and Project Setup               |    |

| 9. Resource Utilization                           | 41 |

| References                                        | 42 |

| Technical Support Assistance                      | 43 |

| Revision History                                  | 44 |

# **Figures**

| Figure 1.1. subLVDS to MIPI CSI-2 Image Sensor Bridge Block Diagram       | 7  |

|---------------------------------------------------------------------------|----|

| Figure 1.2. Bandwidth and Clock Frequency Calculator                      |    |

| Figure 3.1. rx sublvds IP Creation #1                                     |    |

| Figure 3.2. rx_sublvds IP Creation #2                                     |    |

| Figure 3.3. subLVDS Input Global Timing (RAW10, 10 Lanes)                 |    |

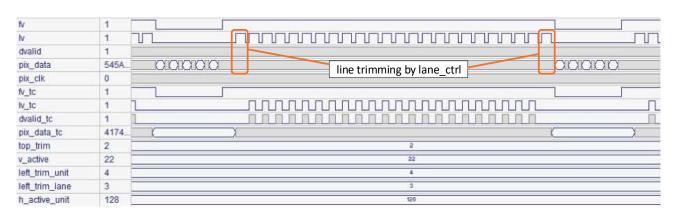

| Figure 3.4. trim_ctrl Global Timing (RAW10, 10 Lanes)                     |    |

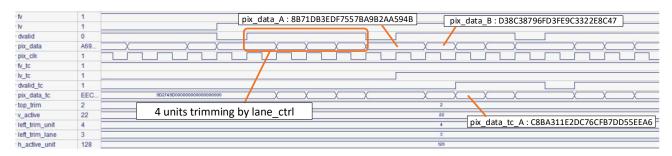

| Figure 3.5. Trimming in the Beginning of the Line (RAW10, 10 Lanes)       |    |

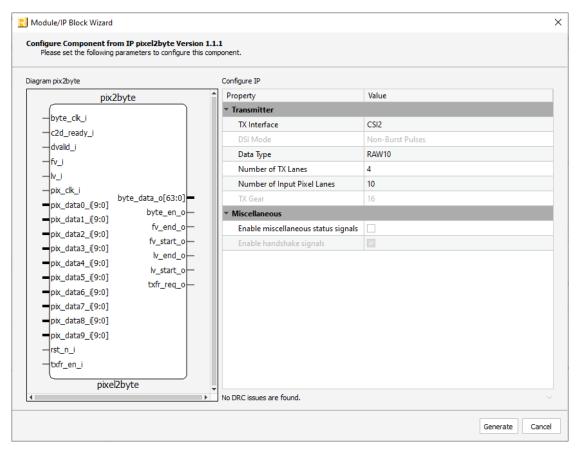

| Figure 3.6. pixel2byte IP Creation                                        | 20 |

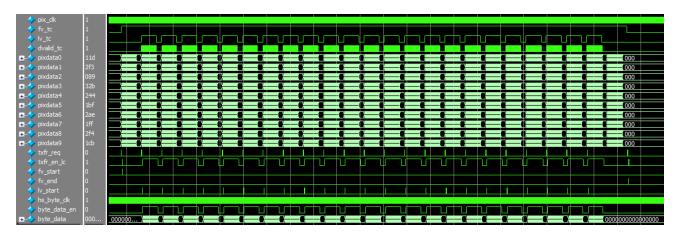

| Figure 3.7. Global Timing of pixel2byte                                   | 21 |

| Figure 3.8. Line Transactions of pixel2byte                               |    |

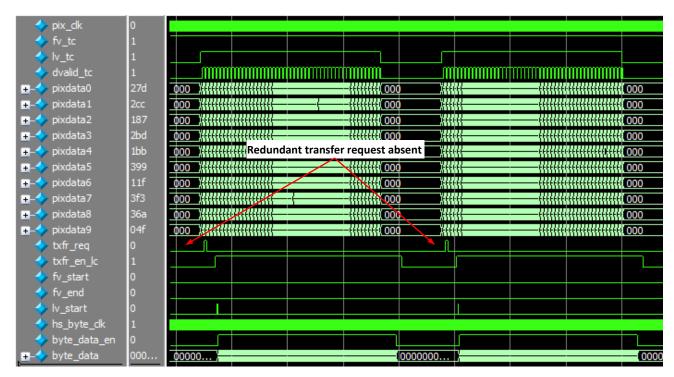

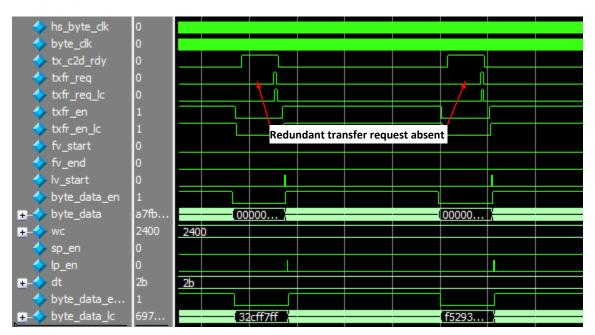

| Figure 3.9. Global Timing of lane_ctrl                                    | 22 |

| Figure 3.10. LP-HS Transition in Continuous clock mode (Short Packet)     | 23 |

| Figure 3.11. LP-HS Transition in Continuous clock mode (Long Packet)      | 23 |

| Figure 3.12. LP-HS Transition in Non-Continuous clock mode (Short Packet) | 24 |

| Figure 3.13. LP-HS Transition in Non-Continuous clock mode (Long Packet)  | 24 |

| Figure 3.14. LP-HS Transition in Non-Continuous clock mode with KEEP_HS   | 25 |

| Figure 3.15. Bus Width Conversion by lane_ctrl                            | 25 |

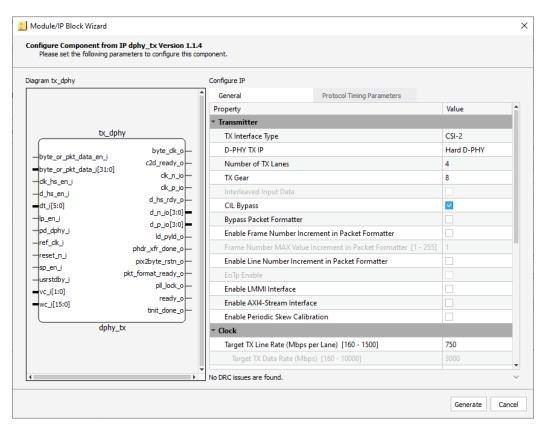

| Figure 3.16. tx_dphy IP Creation #1                                       | 26 |

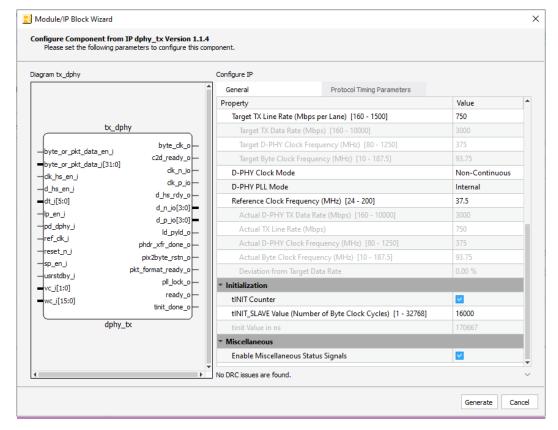

| Figure 3.17. tx_dphy IP Creation #2                                       | 27 |

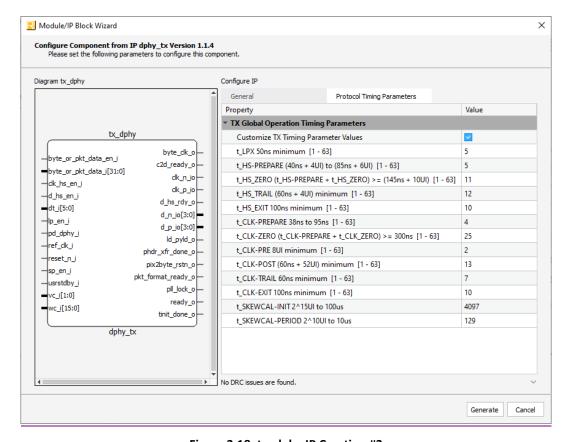

| Figure 3.18. tx_dphy IP Creation #3                                       |    |

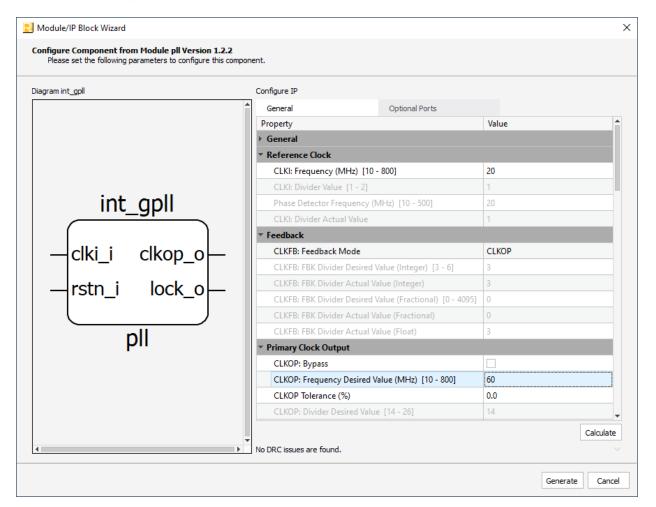

| Figure 3.19. GPLL IP Creation                                             | 29 |

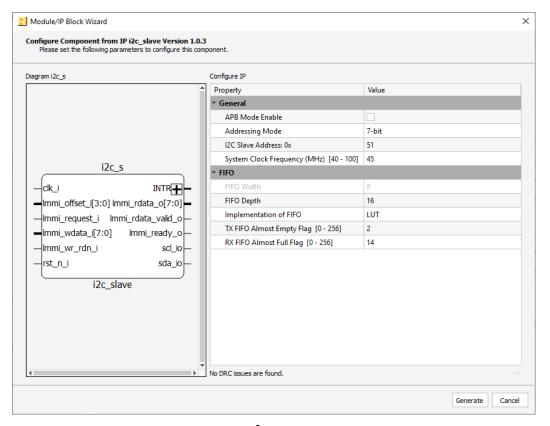

| Figure 3.20. I <sup>2</sup> C Slave IP Creation                           | 30 |

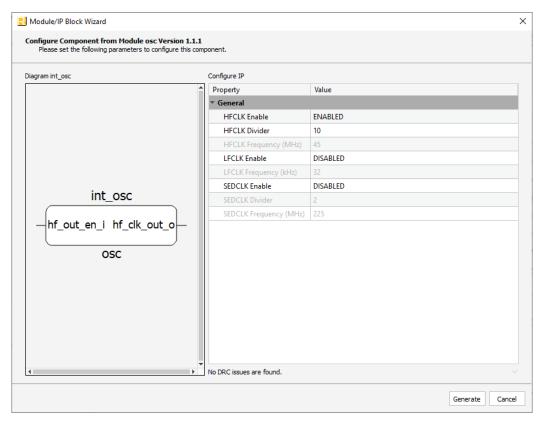

| Figure 3.21. OSC IP Creation                                              | 32 |

| Figure 5.1. Script File Modification                                      | 34 |

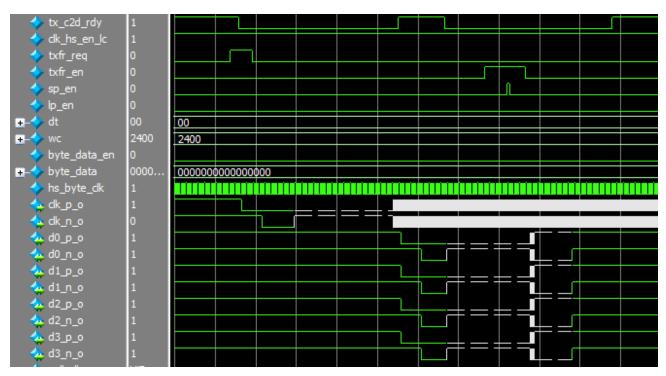

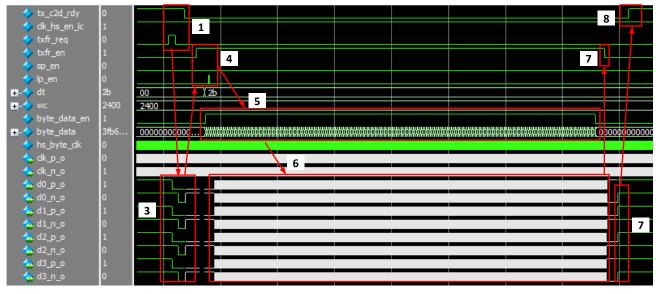

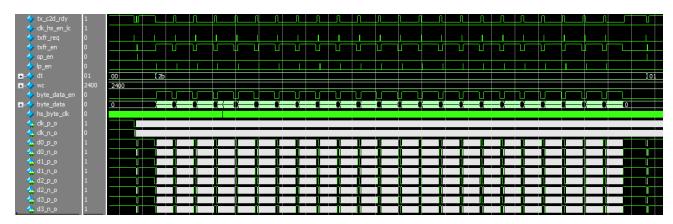

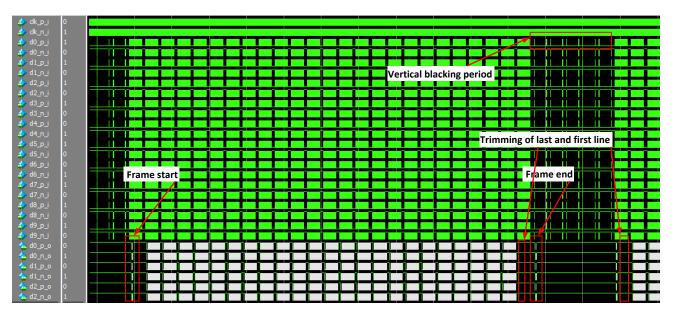

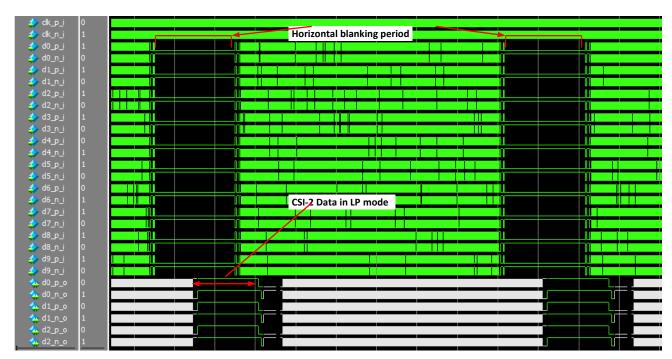

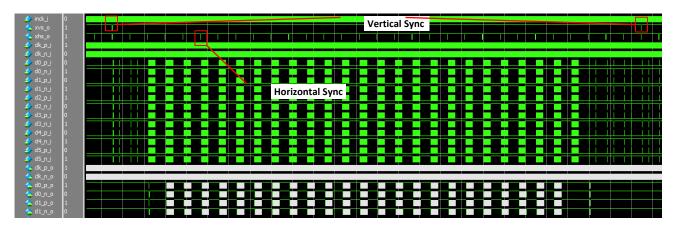

| Figure 5.2. Global Timing of 10-Lane RX and 4-Lane TX                     | 35 |

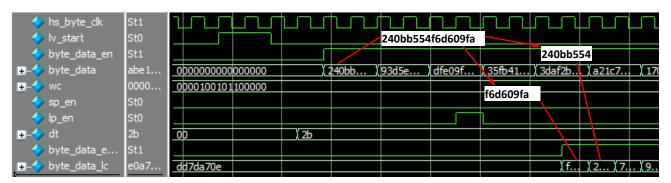

| Figure 5.3. CSI-2 LP/HS Mode Transitions                                  | 35 |

| Figure 5.4. Global Timing with Sensor Slave Mode                          | 36 |

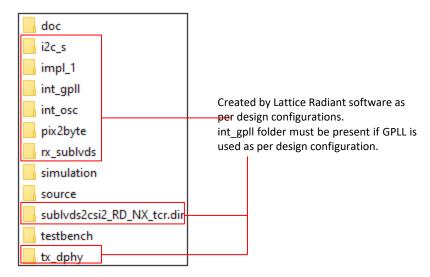

| Figure 8.1. Directory Structure                                           | 39 |

| Figure 8.2. Project Files                                                 | 40 |

| Tables                                                                    |    |

| Table 1.1. Supported Device, IP, and Software                             | 6  |

| Table 1.2. RX and TX Permutations                                         |    |

| Table 2.1. Synthesis Directives                                           |    |

| Table 2.2. Simulation Directives                                          |    |

| Table 2.3. SubLVDS to MIPI CSI2 Top-Level I/O                             |    |

| Table 3.1. Sync Code Details                                              |    |

| Table 3.2. Granularity of h_active_unit and WC                            |    |

| Table 3.3. I <sup>2</sup> C Slave Register Map                            |    |

| Table 9.1. Resource Utilization Examples                                  |    |

| · · · · · · · · · · · · · · · · · · ·                                     |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym          | Definition                              |

|------------------|-----------------------------------------|

| AP               | Application Processor                   |

| CMOS             | Complementary Metal Oxide Semiconductor |

| CSI-2            | Camera Serial Interface 2               |

| DDR              | Double Data Rate                        |

| EAV              | End of Active Video                     |

| FV               | Frame Valid                             |

| GPLL             | General Purpose PLL                     |

| HS               | High Speed                              |

| I <sup>2</sup> C | Inter-Integrated Circuit                |

| IP               | Intellectual Property                   |

| ISP              | Image Signal Processor                  |

| LP               | Low Power                               |

| LV               | Line Valid                              |

| LVDS             | Low Voltage Differential Signal         |

| MIPI             | Mobile Industry Processor Interface     |

| OSCI             | Internal Oscillator                     |

| PLL              | Phase Locked Loop                       |

| RD               | Reference Design                        |

| RX               | Receiver                                |

| SAV              | Start of Active Video                   |

| TX               | Transmitter                             |

| WC               | Word Count                              |

| XHS              | Horizontal Sync Pulse                   |

| XVS              | Vertical Sync Pulse                     |

# 1. Introduction

Many Image Signal Processors (ISP) or Application Processors (AP) use the Mobile Industry Processor Interface (MIPI®) Camera Serial Interface 2 (CSI-2) standard for image sensor inputs. However, some high-resolution CMOS image sensors use a proprietary subLVDS output format.

The Lattice Semiconductor subLVDS to MIPI CSI-2 Image Sensor Bridge reference design for CrossLink™-NX devices solves the mismatch between subLVDS output image sensor and an ISP/AP using CSI-2 interface.

# 1.1. Supported Device, IP, and Software

This reference design supports the CrossLink-NX device with IP and software versions shown below.

Table 1.1. Supported Device, IP, and Software

| Device Family              | Part Number  | Compatible IP                                                                                           | Lattice Radiant™ Version |

|----------------------------|--------------|---------------------------------------------------------------------------------------------------------|--------------------------|

| CrossLink-NX               | LIFCL-17 and | <ul> <li>subLVDS Receiver IP version 1.0.4</li> <li>Pixel-to-Byte Converter IP version 1.1.1</li> </ul> | 2.2.1                    |

| 5. 535 <u>2</u> 11110 1470 | LIFCL-40     | D-PHY Transmitter IP version 1.1.4                                                                      |                          |

#### 1.2. Features

- Supports 4-, 6-, 8-, or 10-lane subLVDS input to 1-, 2-, or 4-lane MIPI CSI-2 output

- Supports input lane bandwidth of up to 1.25 Gbps and output lane bandwidth of up to 2.5 Gbps

- Image cropping option

- VSYNC and HSYNC can be generated to control sensor timing

- Dynamic parameter setting through I<sup>2</sup>C

# 1.3. Block Diagram and Clock Distribution

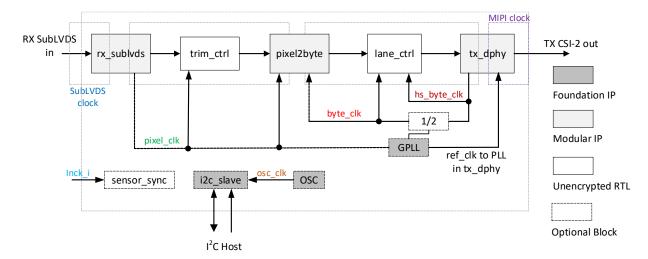

Figure 1.1 shows the block level diagram of the subLVDS to MIPI CSI-2 Image Sensor Bridge reference design. It contains three major IPs and interfacing modules between them. Image data from the sensor come in along with the subLVDS clock in double data rate (DDR) fashion. This clock is divided by 4 or 8 to generate pixel clock according to RX Gear. Pixel clock is fed to trim\_ctrl and Pixel-to-Byte IP modules. In addition, pixel clock is fed to TX D-PHY IP as a reference clock and the TX D-PHY IP creates the MIPI clock using its internal PLL. MIPI clock is divided by 8 or 16 to generate the byte clock and the byte clock is fed to Pixel-to-Byte IP and lane\_ctrl module. In some configurations, the data bus going to TX D-PHY is half of the data bus coming out from Pixel-to-Byte IP. In that case, the byte clock generated by TX D-PHY must be 2x of the byte clock used in Pixel-to-Byte IP and the original byte clock (hs\_byte\_clk) is divided by two and fed to Pixel-to-Byte IP and lane\_ctrl. The lane\_ctrl module takes care of bus width differences. When the image sensor is in slave mode, FPGA has to feed the sync signals to the sensor. In that case, the sensor\_sync module takes the clock from the sensor to generate sync signals. I<sup>2</sup>C slave module is optional to change the configurations on the fly.

Figure 1.1. subLVDS to MIPI CSI-2 Image Sensor Bridge Block Diagram

#### 1.4. RX and TX Permutations

Table 1.2 shows the available permutations of RX and TX configurations. Same permutations apply to both RAW10 and RAW12. In addition, Pixel-to-Byte IP supports only four lanes on TX. To overcome these limitations, a different TX Gear setting is applied in D-PHY TX IP to handle 1-lane or 2-lane outputs, which require faster byte clock (hs\_byte\_clk = 2x or 4x of byte\_clk). Currently, permutations that require 4x of byte\_clk (grayed out in Table 1.2) are not supported due to the unknown necessity.

Also, RX Gear 16 can be applied for RX lane count = 4. However, it does not provide any benefits against RX Gear 8. As such, this is excluded in the design even though the parameter itself remains available for potential future use.

| Table 1 | 2 R   | X and  | I TY P | ermii | tations  |

|---------|-------|--------|--------|-------|----------|

| Iable T | .Z. n | A allu | ΙΙΛΓ   | emmu  | Laliviis |

| Data<br>Type | RX Lane<br>Count | RX Gear     | RX Max. Lane<br>Bandwidth (Mbps) | TX Gear Setting in<br>Pixel-to-Byte IP | TX Lane<br>Count | TX<br>Gear | hs_byte_clk Ratio<br>Against byte_clk |    |

|--------------|------------------|-------------|----------------------------------|----------------------------------------|------------------|------------|---------------------------------------|----|

|              |                  |             | 1250                             |                                        | 4                | 8          | _                                     |    |

|              |                  | 8           | 1250                             | 8                                      | 2                | 16         | _                                     |    |

|              | 4                |             | 625                              |                                        | 1                | 16         | 2x                                    |    |

|              | 4                |             | 1250                             |                                        | 4                | 16         | 1                                     |    |

|              |                  | 16          | 1250                             |                                        | 2                | 16         | 2x                                    |    |

|              |                  |             | 625                              |                                        | 1                | 16         | 4x                                    |    |

| DANAGO       | RAW10<br>RAW12 6 | 6           |                                  | ~1000*                                 |                  | 4          | 8                                     | 1  |

|              |                  |             | 6 8                              | 8                                      | 833.3            | 8          | 2                                     | 16 |

| IVAVVIZ      |                  |             | 416.6                            |                                        | 1                | 16         | 2x                                    |    |

|              |                  |             | 1250                             |                                        | 4                | 16         | _                                     |    |

|              | 8                | 8           | 8 8                              | 625                                    | 16               | 2          | 16                                    | 2x |

|              |                  |             |                                  | 312.5                                  |                  | 1          | 16                                    | 4x |

|              |                  | 10 8 500 16 | 1000                             |                                        | 4                | 16         | _                                     |    |

|              | 10               |             | 2                                | 16                                     | 2x               |            |                                       |    |

|              |                  |             | 250                              |                                        | 1                | 16         | 4x                                    |    |

The Excel file (sublvds2csi2\_clock\_NX.xlsx) is provided to calculate the pixel clock, byte clock, and others, from RX bandwidth and other information. This sheet can be useful to configure IPs. A sample entry is shown in Figure 1.2. By setting four rows shown in the table, pixel clock, byte clock, and TX bandwidth are automatically calculated. Those can be used to configure D-PHY TX IP. In the following situations, the byte clock that comes out from D-PHY TX IP is hs\_byte\_clk and half of this clock is byte\_clk fed to Pixel-to-Byte IP (and lane\_ctrl):

2 x (TX Gear setting in Pixel-to-Byte IP) = (Number of TX Lanes in D-PHY TX) x (TX Gear in D-PHY TX).

| ibLVDS to N | AIPI CSI-2 Image Sensor Bridge RD v | vith Cross | Link-NX Fre | equency Calculat |

|-------------|-------------------------------------|------------|-------------|------------------|

|             | Data Type                           | RAW10      |             |                  |

|             | Number of RX Lanes                  | 4          |             |                  |

| SubLVDS     | RX Gear                             | 8          | fixed to 8  |                  |

| RX          | RX Line Rate (per lane)             | 1250       | Mbps        | (max 1250)       |

|             | SubLVDS Clock Frequency             | 625        | MHz         |                  |

|             | Pixel Clock Frequency               | 156.25     | MHz         | set by           |

| Pixel2Byte  | Number of TX Lanes                  | 4          | always 4    | user             |

|             | Number of Input Pixel Per Clock     | 4          |             | user             |

|             | TX Gear                             | 8          |             |                  |

|             | TX Line Rate (total)                | 5000       | Mbps        |                  |

|             | Number of TX Lanes                  | 2          | ľ           |                  |

| D-PHY TX    | TX Line Rate (per lane)             | 2500       | Mbps        | (max 2500)       |

| D-PHT IX    | TX Gear                             | 16         |             |                  |

|             | Byte Clock Frequency                | 156.25     | MHz         |                  |

|             | Reference Clock Frequency           | 156.25     | MHz         |                  |

|             | hs_byte_clk is not necessary        |            |             |                  |

Figure 1.2. Bandwidth and Clock Frequency Calculator

# 2. Parameters and Port List

There are two directive files for this reference design:

- synthesis\_directives.v used for design compilation by Lattice Radiant and for simulation.

- simulation directives.v used for simulation.

You can modify these directives according to your own configuration. The settings in these files must match subLVDS RX IP, Byte-to-Pixel IP, and TX D-PHY IP settings created in the Lattice Radiant software.

# 2.1. Synthesis Directives

Table 2.1 shows the synthesis directives that affect this reference design. These are used for both synthesis and simulation. Some parameter selections are restricted by other parameter settings.

**Table 2.1. Synthesis Directives**

| Category                                       | Directive                  | Remarks                                                                                                                                                     |  |  |  |

|------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Image Sensor                                   | SENSOR_MODE_MASTER         | Use SLAVE when sync signals (xvs_o/xhs_o) must be sent from FPGA                                                                                            |  |  |  |

| control <sup>1</sup>                           | SENSOR_MODE_SLAVE          | to the image sensor. Only one of these two directives must be defined.                                                                                      |  |  |  |

| Image Sensor Sync                              | SENSOR_SYNC_NEG            | Polarity setting for sync signals to the image sensor. Only effective                                                                                       |  |  |  |

| Polarity <sup>1</sup>                          | SENSOR_SYNC_POS            | when SENSOR_MODE_SLAVE is defined. Only one of these two directives must be defined.                                                                        |  |  |  |

| XVS (Vertical Sync)                            | XVS_LENGTH_XHS             | Select the active pulse length of xvs_o between xhs_o and one horizontal line. Only applicable in case of SENSOR_MODE_MASTER.                               |  |  |  |

| assertion period <sup>1</sup>                  | XVS_LENGTH_LINE            | Only one of these two directives must be defined.                                                                                                           |  |  |  |

| Total line count <sup>1</sup>                  | V_TOTAL {value}            | Total line count for one frame including blanking. Only effective when SENSOR_MODE_SLAVE is defined. Value must be 12'd10 – 12'd4095.                       |  |  |  |

| Total horizontal cycle <sup>1</sup>            | H_TOTAL {value}            | Total cycle count for one line including blanking in the unit of inck_i. Only effective when SENSOR_MODE_SLAVE is defined. Value must be 12'd10 – 12'd4095. |  |  |  |

| XHS (Horizontal Sync) pulse cycle <sup>1</sup> | XHS_LENGTH {value}         | Active pulse width of xhs_o. Only effective when SENSOR_MODE_SLAVE is defined. Value must be 8'd1 – 8'd255.                                                 |  |  |  |

| DV Data Tuna                                   | RAW10                      | Define the data type on RX channel. Only one of these                                                                                                       |  |  |  |

| RX Data Type                                   | RAW12                      | directives must be defined.                                                                                                                                 |  |  |  |

|                                                | NUM_RX_LANE_4              |                                                                                                                                                             |  |  |  |

| RX channel lane                                | NUM_RX_LANE_6              | Number of lanes in RX channel. Only one of these four direct must be defined.                                                                               |  |  |  |

| count                                          | NUM_RX_LANE_8              |                                                                                                                                                             |  |  |  |

|                                                | NUM_RX_LANE_10             |                                                                                                                                                             |  |  |  |

| RX subLVDS Clock<br>Gear                       | RX_GEAR_8                  | RX subLVDS Clock Gear. Use only Gear 8.                                                                                                                     |  |  |  |

| RX subLVDS Dropped<br>Line Mode                | RX_DATA_DROPPED_LINE_MODE  | Define only if the RX Dropped Line Mode is Dynamic.                                                                                                         |  |  |  |

| RX subLVDS Dropped<br>Pixel Mode               | RX_DATA_DROPPED_PIXEL_MODE | Define only if the RX Dropped Pixel Mode is Dynamic.                                                                                                        |  |  |  |

| RX subLVDS Word<br>Count Mode                  | RX_DATA_WORD_COUNT_MODE    | Define only if the RX Word Count Mode is Dynamic.                                                                                                           |  |  |  |

| TX D-PHY Clock                                 | TX_CLK_MODE_HS_LP          | TX D-PHY Clock mode. Only one of these two directives must be defined.                                                                                      |  |  |  |

| mode <sup>2</sup>                              | TX_CLK_MODE_HS_ONLY        | TX_CLK_MODE_HS_LP – Non-Continuous Clock Mode TX_CLK_MODE_HS_ONLY – Continuous Clock Mode                                                                   |  |  |  |

|                                                | NUM_TX_LANE_1              |                                                                                                                                                             |  |  |  |

| TX channel lane count                          | NUM_TX_LANE_2              | Number of lanes in TX channel. Only one of these three directives must be defined.                                                                          |  |  |  |

|                                                | NUM_TX_LANE_4              |                                                                                                                                                             |  |  |  |

|                                                |                            |                                                                                                                                                             |  |  |  |

| Category                                               | Directive              | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX D-PHY Clock Gear                                    | TX_GEAR_8              | Number of TX Clock Gear on RX channel. Only one of these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                        | TX_GEAR_16             | directives must be defined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Use GPLL <sup>10</sup>                                 | USE_GPLL               | Use GPLL to create a reference clock to be fed to PLL of TX DPHY IP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parameter set by I <sup>2</sup> C                      | USE_I2C                | Define this to use I <sup>2</sup> C I/F to configure the image sensor from FPGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Software Reset<br>Register <sup>3</sup>                | SW_RST_N {value}       | Default value of the software reset register of I <sup>2</sup> C Slave module. Value must be 1'b0 or 1'b1. Applicable only when USE_I2C is defined. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Top Line Trimming <sup>4, 5</sup>                      | TOP_TRIM {value}       | Define the number of lines to be trimmed before TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the $I^2$ C register when USE_I2C is defined. Value must be $6'd0-6'd63$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Vertical Active Lines<br>on TX <sup>5</sup>            | V_ACTIVE {value}       | Define the number of active lines to be sent on TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the $I^2$ C register when USE_I2C is defined. Value must be $I^2$ d = |

| Left Pixel Unit<br>Trimming <sup>6, 8</sup>            | LEFT_TRIM_UNIT {value} | Define the number of pixel units to be trimmed before TX. 1 pixel unit = number of RX lanes. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the $I^2C$ register when USE_I2C is defined. Value must be $6'd0 - 6'd63$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Left Pixel Trimming <sup>6, 8</sup>                    | LEFT_TRIM_LANE {value} | Define the number of pixels to be trimmed before TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the $I^2$ C register when USE_I2C is defined. Value must be $4'd0-4'd9$ and less than the RX lane count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Horizontal Active<br>Pixel units on TX <sup>7, 8</sup> | H_ACTIVE_UNIT {value}  | Define the number of active pixels to be sent on TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. Value must be 10'd1 – 10'd1023. The value must be even in case of TX_GEAR_16 or NUM_TX_CH_2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Active Word Count <sup>9</sup>                         | WC {value}             | Define the number of byte count of active pixels to be sent to TX. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the $I^2$ C register when USE_I2C is defined. Value must be $16'$ d5 – $16'$ d65535.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Virtual Channel ID                                     | VC {value}             | Define the virtual Channel ID. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the $I^2C$ register when USE_I2C is defined. Value must be $2'd0 - 2'd3$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| KEEP clock lane in HS<br>mode                          | KEEP_HS                | When defined, clock lane is kept in HS mode during active line periods even if TX clock lane is in non-continuous clock mode. This value is used as a fixed value when USE_I2C is not defined and used as the default value of the I <sup>2</sup> C register when USE_I2C is defined. The value is 1'b1 when defined and 1'b0 when not defined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Notes:

- 1. Refer to the image sensor data sheet for proper settings.

- 2. HS LP mode means non-continuous clock mode and HS ONLY means continuous clock mode.

- 3. Logical OR between this register and system reset (reset\_n\_i) is used to reset modules other than I<sup>2</sup>C slave module.

- 4. Value = 0 is not allowed when no line is trimmed by SubLVDS RX IP.

- 5. (TOP\_TRIM + V\_ACTIVE) cannot exceed the vertical active line count of the incoming RX data. It is your responsibility to manage this.

- 6. Number of pixels trimmed from the left edge is ((LEFT\_TRIM\_UNIT x number of RX lanes x (RX\_GEAR / 8)) + LEFT\_TRIM\_LANE).

- 7. Active pixel count sent to TX is (H\_ACTIVE\_UNIT x number of RX lanes x (RX\_GEAR / 8)).

- 8. ((LEFT\_TRIM\_UNIT + H\_ACTIVE\_UNIT) x number of RX lanes x (RX\_GEAR / 8) + LEFT\_TRIM\_LANE) cannot exceed the horizontal active pixel count of the incoming RX data. It is your responsibility to manage this.

- WC ≤ (H\_ACTIVE\_UNIT x number of RX lanes x (RX\_GEAR / 8)) x (RAW number (10 or 12)) / 8. Refer to the trim\_ctrl section for details.

- 10. Refer to the int\_gpll section for details.

# 2.2. Simulation Directives

Table 2.2 shows the simulation directives for this reference design. Some parameter selections are restricted by other parameter settings including Table 2.1.

**Table 2.2. Simulation Directives**

| Category                                               | Directive                  | Remarks                                                                                                                                                                        |

|--------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX subLVDS clock period                                | PIX_CLK {value}            | RX subLVDS clock period in ps.                                                                                                                                                 |

| INCK clock period                                      | INCK_PERIOD {value}        | INCK clock period in ps. Applicable only when SENSOR_MODE_SLAVE is defined.                                                                                                    |

| Number of frames to run                                | NUM_FRAMES {value}         | Number of video frames fed by testbench.                                                                                                                                       |

| Number of active lines <sup>1</sup>                    | NUM_LINES {value}          | Number of RX active video lines per frame.                                                                                                                                     |

| Number of active pixels <sup>2</sup>                   | NUM_PIXELS {value}         | Number of RX active video pixels per line.                                                                                                                                     |

| Vertical Blanking from XVS to active line <sup>1</sup> | VFRONT_BLNK {value}        | Number of blanking lines before the active video line.                                                                                                                         |

| Vertical Blanking after active line <sup>1</sup>       | VREAR_BLNK {value}         | Number of blanking lines after the active video line.                                                                                                                          |

| Horizontal Blanking period <sup>2</sup>                | HB_PERIOD {value}          | Horizontal Blanking period in SubLVDS clock cycles.                                                                                                                            |

| I <sup>2</sup> C Slave Address                         | I2C_SLAVE_ADR {value}      | Define 7-bit of I2C Slave Address. Value must match the one set for i2c_s module in Lattice Radiant. Applicable only when USE_I2C is defined.                                  |

| Software Reset Register <sup>3</sup>                   | I2C_SW_RST_N {value}       | Write value to the software reset register of I2C Slave module. Value must be 1'b0 or 1'b1. Applicable only when USE_I2C is defined. Active low.                               |

| Top Line Trimming <sup>4, 5</sup>                      | I2C_TOP_TRIM {value}       | Write value to the top trim register of I2C Slave module. Value must be 6'd0 – 6'd63. Applicable only when USE_I2C is defined.                                                 |

| Vertical Active Lines on TX <sup>5</sup>               | I2C_V_ACTIVE {value}       | Write value to the vertical active line register of I2C Slave module. Value must be 12'd1 – 12'd4095. Applicable only when USE_I2C is defined.                                 |

| Left Pixel Unit Trimming <sup>6, 8</sup>               | I2C_LEFT_TRIM_UNIT {value} | Write value to the pixel unit trim register of I2C Slave module. Value must be 6'd0 – 6'd63. Applicable only when USE_I2C is defined.                                          |

| Left Pixel Trimming <sup>6, 8</sup>                    | I2C_LEFT_TRIM_LANE {value} | Write value to the pixel trim register of I2C Slave module. Value must be 4'd0 – 4'd9 and less than the RX lane count. Applicable only when USE_I2C is defined.                |

| Horizontal Active Pixel units on TX <sup>7, 8</sup>    | I2C_H_ACTIVE_UNIT {value}  | Write value to the horizontal active pixel unit register of $I^2C$ Slave module. Value must be $10'd1-10'd1023$ . Applicable only when USE_I2C is defined.                     |

| Active Word Count <sup>9</sup>                         | I2C_WC {value}             | Write value to the word count register of I2C Slave module.  Value must be 16'd5 – 16'd65535. Applicable only when  USE_I2C is defined.                                        |

| Virtual Channel ID                                     | I2C_VC {value}             | Write value to the virtual channel ID register of I2C Slave module. Value must be 2'd0 – 2'd3. Applicable only when USE_I2C is defined.                                        |

| KEEP HS mode                                           | I2C_KEEP_HS {value}        | Write value to the keep HS mode register of I2C Slave module. Value must be 1'b0 or 1'b1. Applicable only when USE_I2C is defined.                                             |

| Total line count <sup>10</sup>                         | I2C_V_TOTAL {value}        | Write value to the total line count register of I2C Slave module.  Value must be 12'd10 – 12'd4095. Applicable only when  USE_I2C and SENSOR_MODE_SLAVE are defined.           |

| Total horizontal cycle <sup>10</sup>                   | I2C_H_TOTAL {value}        | Write value to the total horizontal cycle count register of I2C Slave module. Value must be 12'd10 – 12'd4095. Applicable only when USE_I2C and SENSOR_MODE_SLAVE are defined. |

| Category                                        | Directive              | Remarks                                                                                                                                                        |

|-------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XHS (Horizontal Sync) pulse cycle <sup>10</sup> | I2C_XHS_LENGTH {value} | Write value to the XHS pulse length register of I2C Slave module. Value must be 8'd1 – 8'd255. Applicable only when USE_I2C and SENSOR_MODE_SLAVE are defined. |

#### Notes:

- 1. Total number of lines per frame is (NUM\_LINES + VFRONT\_BLNK + VREAR\_BLNK).

- In the case of SENSOR\_MODE\_MASTER, total number of subLVDS clock cycles per line is (((NUM\_PIXELS/NUM\_RX\_LANE) + 8) x (RAW number (10 or 12)) / 2) + HB PERIOD).

- 3. Logical OR between this register and system reset (reset\_n\_i) is used to reset modules other than I<sup>2</sup>C slave module.

- 4. Value = 0 is not allowed when no line is trimmed by subLVDS RX IP.

- (I2C\_TOP\_TRIM + I2C\_V\_ACTIVE) cannot exceed the vertical active line count of the incoming RX data. It is your responsibility to manage this.

- 6. Number of pixels trimmed from the left edge is ((I2C\_LEFT\_TRIM\_UNIT x number of RX lanes x (RX\_GEAR / 8)) + I2C\_LEFT\_TRIM\_LANE).

- 7. Active pixel count sent to TX is (I2C H ACTIVE UNIT x number of RX lanes x (RX GEAR / 8)).

- 8. ((I2C\_LEFT\_TRIM\_UNIT + I2C\_H\_ACTIVE\_UNIT) x number of RX lanes x (RX\_GEAR / 8) + I2C\_LEFT\_TRIM\_LANE) cannot exceed the horizontal active pixel count of the incoming RX data. It is your responsibility to manage this.

- I2C\_WC ≤ (I2C\_H\_ACTIVE\_UNIT x number of RX lanes x (RX\_GEAR / 8)) x (RAW number (10 or 12)) / 8. Refer to the trim\_ctrl section for details.

- 10. Refer to the image sensor data sheet for proper settings.

### 2.3. Top-Level I/O

Table 2.3 shows the top level I/O of this reference design. Actual I/O depend on the customer's channel and lane configurations. All necessary I/O ports are automatically declared by compiler directives.

Table 2.3. SubLVDS to MIPI CSI2 Top-Level I/O

| Port Name      | Direction      | Description                                                                          |

|----------------|----------------|--------------------------------------------------------------------------------------|

| Reset          | •              |                                                                                      |

| reset_n_i      | I              | Asynchronous active low system reset                                                 |

| Control Interf | ace (condition | nal)                                                                                 |

| inck_i         | I              | Clock to control XVS and XHS. Only used in case of SENSOR_MODE_SLAVE.                |

| xvs_o          | 0              | Vertical Sync signal to the image sensor. Only used in case of SENSOR_MODE_SLAVE.    |

| xhs_o          | 0              | Horizontal Sync signal to the image sensor. Only used in case of SENSOR_MODE_SLAVE.  |

| Control Interf | ace (optional) |                                                                                      |

| scl            | I/O            | I <sup>2</sup> C clock. Only used in case of USE_I2C.                                |

| sda            | I/O            | I <sup>2</sup> C data Only used in case of USE_I2C.                                  |

| SubLVDS RX II  | nterface       |                                                                                      |

| clk_p_i        | I              | Positive differential RX subLVDS input clock                                         |

| clk_n_i        | I              | Negative differential RX subLVDS input clock                                         |

| d0_p_i         | I              | Positive differential RX subLVDS input data 0                                        |

| d0_n_i         | I              | Negative differential RX subLVDS input data 0                                        |

| d1_p_i         | I              | Positive differential RX subLVDS input data 1                                        |

| d1_n_i         | I              | Negative differential RX subLVDS input data 1                                        |

| d2_p_i         | I              | Positive differential RX subLVDS input data 2                                        |

| d2_n_i         | I              | Negative differential RX subLVDS input data 2                                        |

| d3_p_i         | I              | Positive differential RX subLVDS input data 3                                        |

| d3_n_i         | I              | Negative differential RX subLVDS input data 3                                        |

| d4_p_i         | I              | Positive differential RX subLVDS input data 4 (in case of 6/8/10-lane configuration) |

| d4_n_i         | I              | Negative differential RX subLVDS input data 4 (in case of 6/8/10-lane configuration) |

| d5_p_i         | I              | Positive differential RX subLVDS input data 5 (in case of 6/8/10-lane configuration) |

| d5_n_i         | I              | Negative differential RX subLVDS input data 5 (in case of 6/8/10-lane configuration) |

| Port Name       | Direction | Description                                                                        |  |  |

|-----------------|-----------|------------------------------------------------------------------------------------|--|--|

| d6_p_i          | I         | Positive differential RX subLVDS input data 6 (in case of 8/10-lane configuration) |  |  |

| d6_n_i          | 1         | Negative differential RX subLVDS input data 6 (in case of 8/10-lane configuration) |  |  |

| d7_p_i          | I         | Positive differential RX subLVDS input data 7 (in case of 8/10-lane configuration) |  |  |

| d7_n_i          | 1         | Negative differential RX subLVDS input data 7 (in case of 8/10-lane configuration) |  |  |

| d8_p_i          | I         | Positive differential RX subLVDS input data 8 (in case of 10-lane configuration)   |  |  |

| d8_n_i          | 1         | Negative differential RX subLVDS input data 8 (in case of 10-lane configuration)   |  |  |

| d9_p_i          | I         | Positive differential RX subLVDS input data 9 (in case of 10-lane configuration)   |  |  |

| d9_n_i          | I         | Negative differential RX subLVDS input data 9 (in case of 10-lane configuration)   |  |  |

| CSI-2 TX Interf | face      |                                                                                    |  |  |

| clk_p_o         | 0         | Positive differential TX CSI-2 output clock                                        |  |  |

| clk_n_o         | 0         | Negative differential TX CSI-2 output clock                                        |  |  |

| d0_p_o          | 0         | Positive differential TX CSI-2 output data 0 (in case of 1-lane configuration)     |  |  |

| d0_n_o          | 0         | Negative differential TX CSI-2 output data 0 (in case of 1-lane configuration)     |  |  |

| d1_p_o          | 0         | Positive differential TX CSI-2 output data 1 (in case of 2/4-lane configuration)   |  |  |

| d1_n_o          | 0         | Negative differential TX CSI-2 output data 1 (in case of 2/4-lane configuration)   |  |  |

| d2_p_o          | 0         | Positive differential TX CSI-2 output data 2 (in case of 4-lane configuration)     |  |  |

| d2_n_o          | 0         | Negative differential TX CSI-2 output data 2 (in case of 4-lane configuration)     |  |  |

| d3_p_o          | 0         | Positive differential TX CSI-2 output data 3 (in case of 4-lane configuration)     |  |  |

| d3_n_o          | 0         | Negative differential TX CSI-2 output data 3 (in case of 4-lane configuration)     |  |  |

# 3. Design and Module Description

The top-level design (sublvds2csi2\_NX.v) consists of the following modules:

- sensor\_sync (conditional)

- rx sublvds

- trim ctrl

- pix2byte

- lane ctrl

- tx\_dphy

- int gpll (conditional)

- i2c\_slave (optional)

- int osc (conditional)

The top-level design has a reset synchronization logic.

#### 3.1. sensor\_sync

This module is instantiated when SENSOR\_MODE\_SLAVE is defined to feed the horizontal and vertical sync signals (xhs\_o, xvs\_o) to the image sensor using the external clock (inck\_i). Sync pulse polarity and interval can be changed by directives described in the Synthesis Directives and Simulation Directives sections. Figure 5.4 shows xvs\_o having one line length of active pulse by XVS\_LENGTH\_LINE directive. This module has no interaction with other modules except for i2c\_slave. The following parameters are taken as input data:

- v\_total\_i[11:0] Total number of lines per frame including blanking lines.

- h\_total\_i[11:0] Total number of clock cycles per line including blanking period.

- xhs\_length[7:0] Pulse length of xhs\_o. In case that XVS\_LENGTH\_XHS is defined, this value also applies to xvs\_o active pulse length.

### 3.2. rx sublvds

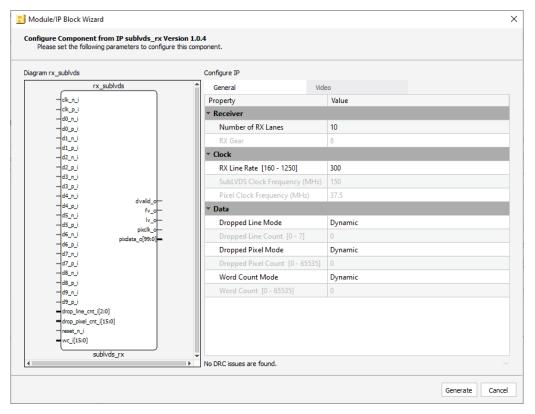

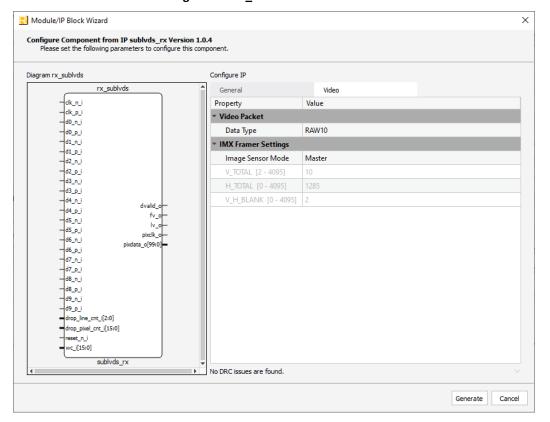

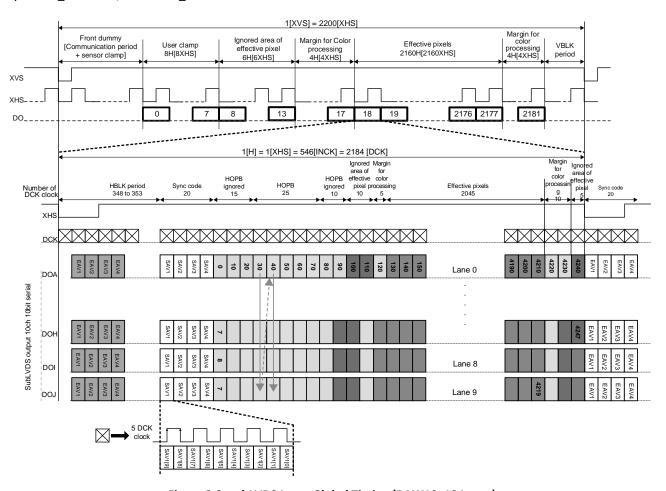

This module must be created for the RX channel according to channel conditions, such as the number of lanes, bandwidth, and others. Figure 3.1 and Figure 3.2 show an example of the IP interface settings in the Lattice Radiant software for the subLVDS Image Sensor Receiver IP Core. You can use the ipx file (rx\_sublvds/rx\_sublvds.ipx) included in the sample project and re-configure according to your needs. Refer to SubLVDS Image Sensor Receiver IP Core User Guide (FPGA-IPUG-02093) for details.

The following shows guidelines and parameter settings required for this reference design.

- Number of RX Lanes Set according to channel configuration. The value must match NUM\_RX\_LANE\_\* setting (4, 6, 8, or 10).

- RX Gear Always Select 8.

- RX Line Rate Set according to channel configuration. The following are the maximum values for different lane configurations:

- 4-Lane, Gear 8 1250 Mbps

- 6-Lane, Gear 8 1250 Mbps

- 8-Lane, Gear 8 1250 Mbps

- 10-Lane, Gear 8 1000 Mbps

- Dropped Line Mode Can be set as Dynamic or Static according to the channel configuration.

- Dropped Line Count Set 0. This value must not be 0 when TOP\_TRIM / I2C\_TOP\_TRIM are set to 0.

- Dropped Pixel Mode Can be set as Dynamic or Static according to the channel configuration.

- Dropped Pixel Count Set 0.

- Word Count Mode Can be set as Dynamic or Static according to the channel configuration.

- Word Count Set 0.

- Video Packet Data Type Select RAW10 or RAW12.

- Image Sensor Mode Always select Master. Slave mode is handled by sensor\_sync module.

Figure 3.1. rx\_sublvds IP Creation #1

Figure 3.2. rx\_sublvds IP Creation #2

© 2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

This module takes serial subLVDS data from the image sensor and outputs pixel data after de-serialization. In case that you generate this IP from scratch, it is recommended to set the module name to  $rx\_sublvds$  so that you do not need to modify the instance name of this IP in the top-level design as well as the simulation setup file. Otherwise, you have to modify the names accordingly.