# **10 Gb Ethernet MAC IP Core – Lattice Radiant Software**

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Acronyms in This Document                                                       | 5  |

|---------------------------------------------------------------------------------|----|

| 1. Introduction                                                                 | 6  |

| 1.1. Quick Facts                                                                | 6  |

| 1.2. Features                                                                   | 7  |

| 1.3. Conventions                                                                | 8  |

| 1.3.1. Nomenclature                                                             | 8  |

| 1.3.2. Signal Names                                                             | 8  |

| 1.3.3. Attribute Names                                                          | 8  |

| 2. Functional Description                                                       | 9  |

| 2.1. Overview                                                                   | 9  |

| 2.2. Block Diagram                                                              | 9  |

| 2.3. Signal Description                                                         | 10 |

| 2.4. Attribute Summary                                                          | 14 |

| 2.5. Registers Description                                                      | 14 |

| 2.5.1. Configuration Registers                                                  | 15 |

| 2.5.2. Interrupt Registers                                                      | 19 |

| 2.5.3. Statistics Counters                                                      |    |

| 2.6. Ethernet Data Format                                                       | 24 |

| 2.7. Receive MAC                                                                | 25 |

| 2.8. Transmit MAC                                                               | 26 |

| 2.9. Receive AXI4-Stream Interface                                              | 27 |

| 2.9.1. Default Normal Frame                                                     | 27 |

| 2.9.2. In-Band FCS Passing                                                      | 28 |

| 2.9.3. Custom Preamble Passing                                                  |    |

| 2.10. Transmit AXI4-Stream Interface                                            | 29 |

| 2.10.1. Default Normal Frame                                                    | 29 |

| 2.10.2. In-Band FCS Passing                                                     | 30 |

| 2.10.3. Custom Preamble Passing                                                 |    |

| 2.11. Data Packing                                                              |    |

| 2.12. Management                                                                |    |

| 2.13. Reset and Sequence                                                        |    |

| 2.13.1. Reset                                                                   |    |

| 2.13.2. Sequence                                                                |    |

| 3. Core Generation and Simulation                                               | 33 |

| 3.1. Generation and Synthesis                                                   | 33 |

| 3.2. Running Functional Simulation                                              | 36 |

| 4. Licensing and Evaluation                                                     |    |

| 4.1. Licensing the IP                                                           |    |

| 4.2. Hardware Evaluation                                                        |    |

| 5. Ordering Part Number                                                         |    |

| Appendix A. Resource Utilization                                                |    |

| Appendix B. Code Listing for Multicast Bit Selection Hash Algorithm in C Langua |    |

| References                                                                      | _  |

| Technical Support Assistance                                                    |    |

| Pavision History                                                                | 15 |

# **Figures**

| Figure 1.1. 10GBase-R Application                                       | 6  |

|-------------------------------------------------------------------------|----|

| Figure 2.1. 10 Gb Ethernet MAC IP Core Block Diagram                    | 9  |

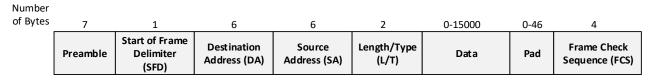

| Figure 2.2. Untagged Ethernet Frame Format                              | 24 |

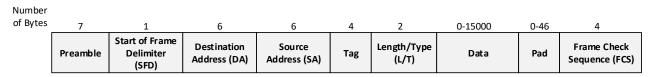

| Figure 2.3. Tagged Ethernet Frame Format                                | 24 |

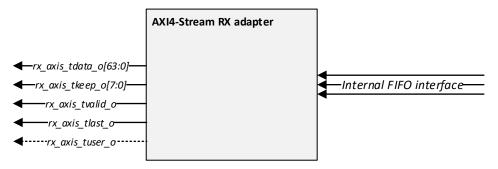

| Figure 2.4. AXI4-Stream RX Adapter Interface Diagram                    | 27 |

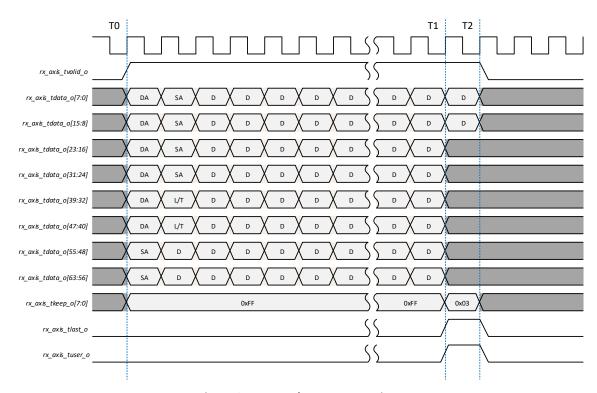

| Figure 2.5. Normal Frame Reception                                      | 27 |

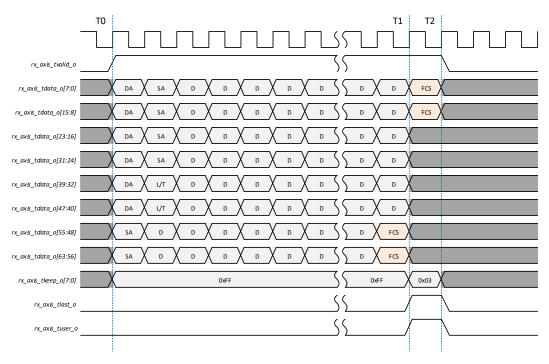

| Figure 2.6. Frame Reception with In-Band FCS Passing                    |    |

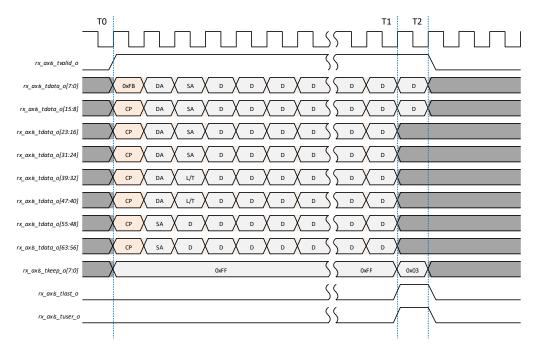

| Figure 2.7. Reception with Custom Preamble                              |    |

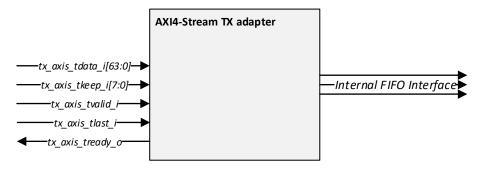

| Figure 2.8. AXI4-Stream TX Adapter Interface Diagram                    |    |

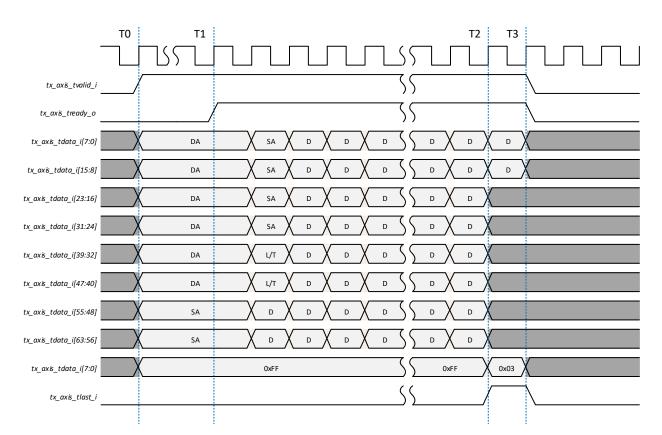

| Figure 2.9. Default Normal Frame Transmission                           |    |

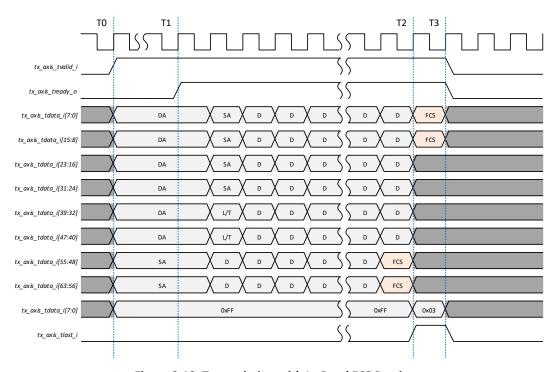

| Figure 2.10. Transmission with In-Band FCS Passing                      |    |

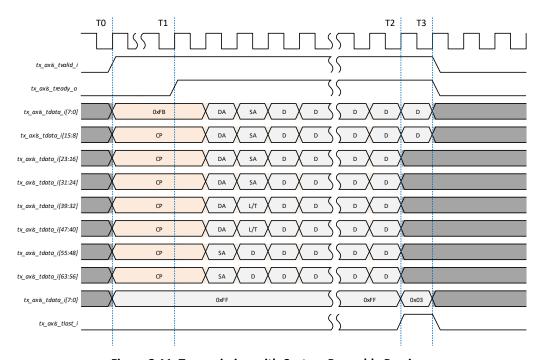

| Figure 2.11. Transmission with Custom Preamble Passing                  |    |

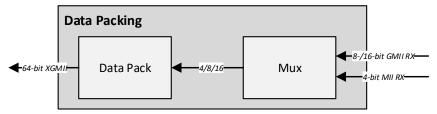

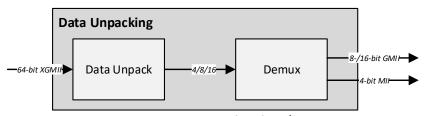

| Figure 2.12. Receive Physical Interface for 8/6-bit GMII or MII         |    |

| Figure 2.13. Transmit Physical Interface for 8/16-bit GMII or MII       |    |

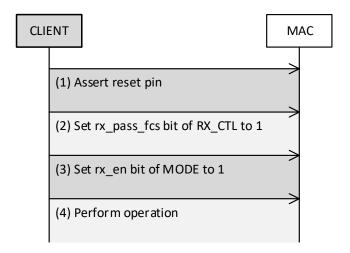

| Figure 2.14. Sequence to Configure RX MAC In-Band FCS Passing           |    |

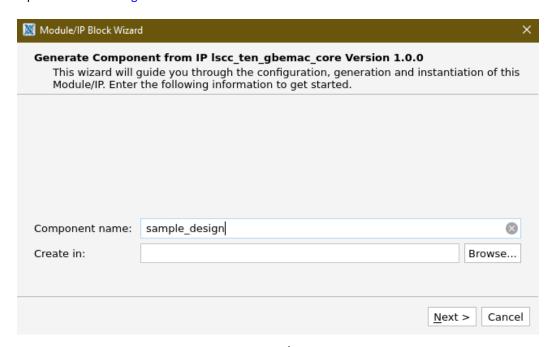

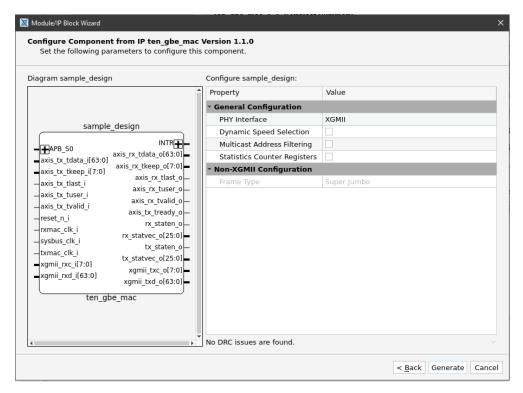

| Figure 3.1. Module/IP Block Wizard                                      |    |

| Figure 3.2. Configure User Interface of 10 Gb Ethernet MAC IP Core      |    |

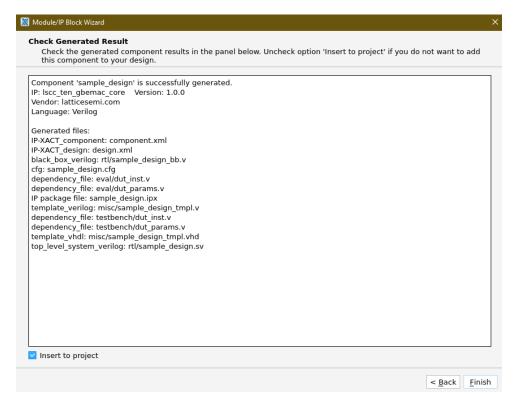

| Figure 3.3. Check Generating Result                                     |    |

| Figure 3.4. Synthesizing Design                                         |    |

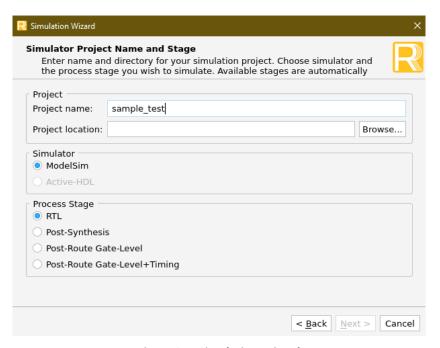

| Figure 3.5. Simulation Wizard                                           |    |

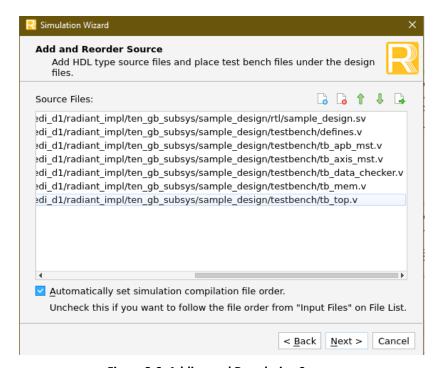

| Figure 3.6. Adding and Reordering Source                                | 36 |

| Table 1.1. 10 Gb Ethernet MAC IP Core Quick Facts                       |    |

| Table 2.1. Signal Description                                           | 10 |

| Table 2.2. Attributes Table                                             |    |

| Table 2.3. Access Types                                                 |    |

| Table 2.4. Summary of Configuration Registers                           |    |

| Table 2.5. MODE Register                                                |    |

| Table 2.6. TX_CTL Register                                              |    |

| Table 2.7. RX_CTL Register                                              |    |

| Table 2.8. MAX_PKT_LNGTH Register                                       |    |

| Table 2.9. IPG_VAL Register                                             |    |

| Table 2.10. MAC_ADDR_0 Register                                         |    |

| Table 2.11. MAC_ADDR_1 Register                                         |    |

| Table 2.12. TX_RX_STS Register                                          |    |

| Table 2.13. VLAN_TAG Register                                           |    |

| Table 2.14. MC_TABLE_0 Register                                         |    |

| Table 2.15. MC_TABLE_1 Register                                         |    |

| Table 2.16. PAUSE_OPCODE Register                                       |    |

| Table 2.17. MAC_CTL Register                                            |    |

| Table 2.18. PAUSE_TM Register                                           |    |

| Table 2.19. Summary of Interrupt Registers                              |    |

| Table 2.20. INT_STATUS Register                                         |    |

| Table 2.21. INT_ENABLE Register                                         |    |

| Table 2.22. INT_SET Register Table 2.23. Summary of Statistics Counters |    |

| Table 3.1. Generated File List                                          |    |

| Table A.1. Resource Utilization                                         |    |

| I ADIE M. J. NESOUI LE ULIIZALIUI                                       |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym     | Definition                             |

|-------------|----------------------------------------|

| APB         | Advanced Peripheral Bus                |

| AXI4-Stream | Advanced eXtensible Interface 4 Stream |

| GPLL        | Generic Phase-Locked Loop              |

| MAC         | Media Access Controller                |

| MTU         | Maximum Transmission Unit              |

| PCS         | Physical Coding Sublayer               |

| XGMII       | 10-Gigabit Media Independent Interface |

# 1. Introduction

The Lattice Semiconductor 10 Gb Ethernet MAC IP Core supports the ability to transmit and receive data between a host processor and an Ethernet network. The main function of the 10 Gb Ethernet MAC is to ensure that the Media Access rules specified in the 802.3 IEEE standards are met while transmitting a frame of data over Ethernet. On the receive side, the Ethernet MAC extracts the different components of a frame and transfers them to higher applications through an AXI4-stream interface.

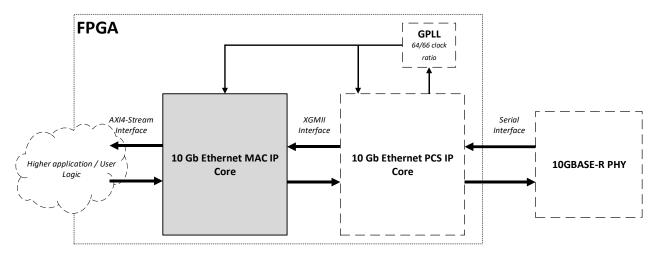

Figure 1.1 shows an example of a 10GBase-R application. The 10 Gb Ethernet MAC IP Core is connected to the 10G Ethernet PCS IP Core and its clock source is from the GPLL.

Figure 1.1. 10GBase-R Application

#### 1.1. Quick Facts

Table 1.1 provides quick facts about the 10 Gb Ethernet MAC IP Core.

Table 1.1. 10 Gb Ethernet MAC IP Core Quick Facts

| IP Requirements      | Supported FPGA Family    | CertusPro™-NX                                                                      |  |

|----------------------|--------------------------|------------------------------------------------------------------------------------|--|

|                      | Targeted Devices         | LFCPNX-100                                                                         |  |

| Resource Utilization | Supported User Interface | AXI4-Stream/APB/LINTR Interface                                                    |  |

|                      | Resources                | See Table A.1                                                                      |  |

|                      | Lattice Implementation   | IP Core v1.0.x – Lattice Radiant™ software 3.0 or later                            |  |

|                      | Cumbbasia                | Lattice Synthesis Engine                                                           |  |

| Design Tool Support  | Synthesis                | Synopsys® Synplify Pro®, O-2018.09LR-SP1                                           |  |

|                      | Simulation               | For the list of supported simulators, see the Lattice Radiant Software User Guide. |  |

#### 1.2. Features

The key features of the 10 Gb Ethernet MAC IP Core include:

- Compliant to IEEE 802.3-2012 standard

- Supports standard 10 Gbps Ethernet link layer data rate

- 64-bit wide internal data path operating at 156.25 MHz

- AXI4-stream interface on Client transmit and receive interfaces

- Supports Deficit Idle Count

- Supports VLAN, Jumbo Frames and WAN mode

- Custom Preamble mode

- Independent TX and RX Maximum Transmission Unit (MTU) frame length

- Comprehensive Statistics Support

- Optional FCS generation on transmission

- Optional FCS stripping during reception

- Optional Multicast address filtering

- Programmable Inter-Frame Gap

- Supports Flow control using PAUSE Frames

- Automatic padding of Short Frames

- Inter-Frame Stretch Mode during transmission

- Supports Full-Duplex Operation

- APB interface for register access

- Supports 8-bit/16-bit GMII or 4-bit MII to and from Physical (PHY) layer

7

## 1.3. Conventions

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.3.2. Signal Names

Signal names that end with:

- \_n are active low (asserted when value is logic 0)

- \_*i* are input signals

- \_o are output signals

- \_io are bi-directional input/output signals

#### 1.3.3. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

# 2. Functional Description

#### 2.1. Overview

The 10 Gb Ethernet MAC IP Core transmits and receives data between a host processor and an Ethernet network. The main function of the 10 Gb Ethernet MAC is to ensure that the Media Access rules specified in the 802.3 IEEE standards are met while transmitting a frame of data over Ethernet. On the receive side, the Ethernet MAC extracts the different components of a frame and transfers them to higher applications through an AXI4-stream interface.

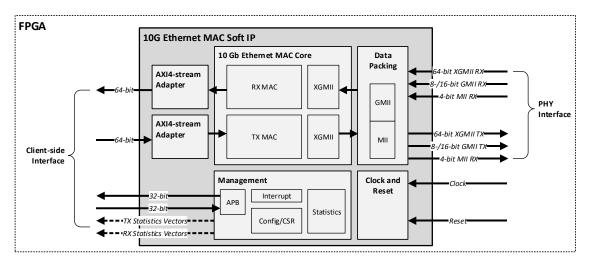

# 2.2. Block Diagram

Figure 2.1. 10 Gb Ethernet MAC IP Core Block Diagram

# 2.3. Signal Description

**Table 2.1. Signal Description**

| Port Name                    | I/O | Width | Default | Description                                                                                                                                                                                                                                                          |  |  |  |

|------------------------------|-----|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Clock and Reset              |     |       |         |                                                                                                                                                                                                                                                                      |  |  |  |

| reset_n_i                    | In  | 1     | _       | Active-low asynchronous reset.                                                                                                                                                                                                                                       |  |  |  |

| rx_mac_clk_i                 | In  | 1     | _       | Clock for Receive AXI4-stream and XGMII or 8-bit/16-bit GMII or MII data path.  156.25 MHz clock for XGMII Interface.  125 MHz clock for 8-bit GMII Interface.  156.25 MHz clock for 16-bit Interface.  125 MHz clock for MII RX data.                               |  |  |  |

| tx_mac_clk_i                 | In  | 1     | _       | Clock for Transmit AXI4-stream and XGMII/GMII/MII data path.     156.25 MHz clock for XGMII Interface.     125 MHz clock for 8-bit GMII Interface.     156.25 MHz clock for 16-bit Interface.     125 MHz clock for MII Interface.                                   |  |  |  |

| apb_clk_i                    | In  | 1     | _       | Clock for Management module                                                                                                                                                                                                                                          |  |  |  |

| PHY Interface                |     |       |         |                                                                                                                                                                                                                                                                      |  |  |  |

| XGMII Interface <sup>1</sup> |     |       |         |                                                                                                                                                                                                                                                                      |  |  |  |

| xgmii_rxd_i                  | In  | 64    | -       | 8-lane Receive SDR XGMII data from PHY.  Lane 0: xgmii_rxd_i[7:0]  Lane 1: xgmii_rxd_i[15:8]  Lane 2: xgmii_rxd_i[23:16]  Lane 3: xgmii_rxd_i[31:24]  Lane 4: xgmii_rxd_i[39:32]  Lane 5: xgmii_rxd_i[47:40]  Lane 6: xgmii_rxd_i[55:48]  Lane 7: xgmii_rxd_i[63:56] |  |  |  |

| xgmii_rxc_i                  | In  | 8     | _       | Control bits for each lane in xgmii_rxd_i[].  Lane 0: xgmii_rxc_i[0]  Lane 1: xgmii_rxc_i[1]  Lane 2: xgmii_rxc_i[2]  Lane 3: xgmii_rxc_i[3]  Lane 4: xgmii_rxc_i[4]  Lane 5: xgmii_rxc_i[5]  Lane 6: xgmii_rxc_i[6]  Lane 7: xgmii_rxc_i[7]                         |  |  |  |

| xgmii_txd_o                  | Out | 64    | 64'h0   | 8-lane Transmit SDR XGMII data to PHY.  Lane 0: xgmii_txd_o[7:0]  Lane 1: xgmii_txd_o[15:8]  Lane 2: xgmii_txd_o[23:16]  Lane 3: xgmii_txd_o[31:24]  Lane 4: xgmii_txd_o[39:32]  Lane 5: xgmii_txd_o[47:40]  Lane 6: xgmii_txd_o[55:48]  Lane 7: xgmii_txd_o[63:56]  |  |  |  |

| Port Name                   | 1/0      | Width | Default | Description                                                                                                                                      |

|-----------------------------|----------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | ,,,      |       |         | Control bits for each lane in xgmii txd o[ ].                                                                                                    |

|                             |          |       |         | Lane 0: xgmii_txc_o[0]                                                                                                                           |

|                             |          |       |         | Lane 1: xgmii_txc_o[1]                                                                                                                           |

|                             |          |       |         | Lane 2: xgmii txc o[2]                                                                                                                           |

| xgmii txc o                 | Out      | 8     | 8'h0    | Lane 3: xgmii_txc_o[3]                                                                                                                           |

| 0                           |          |       |         | Lane 4: xgmii_txc_o[4]                                                                                                                           |

|                             |          |       |         | Lane 5: xgmii_txc_o[5]                                                                                                                           |

|                             |          |       |         | Lane 6: xgmii_txc_o[6]                                                                                                                           |

|                             |          |       |         | Lane 7: xgmii_txc_o[7]                                                                                                                           |

| GMII Interface <sup>2</sup> |          |       |         |                                                                                                                                                  |

| gmii_rx_d_i                 | In       | 8     | ı       | 8-bit GMII RX data.                                                                                                                              |

| gmii_rx_dv_i                | In       | 1     | -       | Indicates the GMII RX data is valid when asserted.                                                                                               |

| gmii_rx_err_i               | In       | 1     | -       | Indicates the GMII RX data contains error.                                                                                                       |

| gmii_tx_d_o                 | Out      | 8     | 8'h0    | 8-bit GMII TX data.                                                                                                                              |

| gmii_tx_en_o                | Out      | 1     | 1'b0    | Indicates the GMII TX data is valid when asserted.                                                                                               |

| gmii_tx_err_o               | Out      | 1     | 1'b0    | Indicates the GMII RX data contains error.                                                                                                       |

| gmii_16_rx_d_i              | In       | 16    | _       | 16-bit GMII RX data.                                                                                                                             |

| gmii_16_rx_dv_i             | In       | 2     | _       | Indicates the GMII RX data is valid when asserted.                                                                                               |

| gmii_16_rx_err_i            | In       | 2     | _       | Indicates the GMII RX data contains error.                                                                                                       |

| gmii_16_tx_d_o              | Out      | 16    | 16'h0   | 16-bit GMII TX data.                                                                                                                             |

| gmii_16_tx_en_o             | Out      | 2     | 2'h0    | Indicates the GMII TX data is valid when asserted.                                                                                               |

| gmii_16_tx_err_o            | Out      | 2     | 2'h0    | Indicates the GMII RX data contains error.                                                                                                       |

| MII Interface <sup>3</sup>  |          |       |         |                                                                                                                                                  |

| mii_rx_d_i                  | In       | 4     | _       | 4-bit MII RX data.                                                                                                                               |

| mii_rx_dv_i                 | In       | 1     | _       | Indicates the MII RX data is valid when asserted.                                                                                                |

| mii_rx_err_i                | In       | 1     | _       | Indicates the MII RX data contains error.                                                                                                        |

| mii_tx_d_o                  | Out      | 4     | 4'h0    | 4-bit MII TX data.                                                                                                                               |

| mii_tx_en_o                 | Out      | 1     | 1'b0    | Indicates the MII TX data is valid when asserted.                                                                                                |

| mii_tx_err_o                | Out      | 1     | 1'b0    | Indicates the MII RX data contains error.                                                                                                        |

| Client-Side Interface       |          |       |         |                                                                                                                                                  |

| AXI4-Stream Receive I       | nterface |       |         |                                                                                                                                                  |

| axis_rx_tdata_o             | Out      | 64    | 64'h0   | AXI4-Stream data from PHY to client.                                                                                                             |

|                             |          |       |         | AXI4-Stream control that indicates which data is valid on axis_rx_tdata_o[ ].                                                                    |

|                             |          |       |         | axis_rx_tkeep_o[0]: axis_rx_tdata_o [7:0]                                                                                                        |

|                             |          |       |         | axis_rx_tkeep_o[1]: axis_rx_tdata_o [15:8]                                                                                                       |

| axis_rx_tkeep_o             | Out      | 8     | 8'h0    | axis_rx_tkeep_o[2]: axis_rx_tdata_o [23:16]                                                                                                      |

| uxi3_ix_tkeep_0             | Out      | Ü     | 0 110   | axis_rx_tkeep_o[3]: axis_rx_tdata_o [31:24]                                                                                                      |

|                             |          |       |         | axis_rx_tkeep_o[4]: axis_rx_tdata_o [39:32]                                                                                                      |

|                             |          |       |         | axis_rx_tkeep_o[5]: axis_rx_tdata_o [47:40]     axis_rx_tkeep_o[6]: axis_rx_tdata_o [55:40]                                                      |

|                             |          |       |         | axis_rx_tkeep_o[6]: axis_rx_tdata_o [55:48] axis_ry_tkeep_o[7]: axis_ry_tdata_o [63:56]                                                          |

| avia my tualid a            | O t      | 4     | 1/50    | axis_rx_tkeep_o[7]: axis_rx_tdata_o [63:56]  AXI4-Stream data valid.                                                                             |

| axis_rx_tvalid_o            | Out      | 1     | 1'b0    |                                                                                                                                                  |

| axis rx tuser o             | Out      | 1     | 1'b0    | AXI4-Stream user signal used to indicate that the frame had a length error, termination error, or a CRC error. This signal is qualified with the |

| - u.n.s_i.n_cusci_0         | Jul      | _     | 1 50    | axis_rx_tlast_o signal.                                                                                                                          |

| axis_rx_tlast_o             | Out      | 1     | 1'b0    | AXI4-Stream signal indicating the end of a packet.                                                                                               |

|                             | <u> </u> |       |         | 1                                                                                                                                                |

© 2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Port Name              | I/O   | Width | Default         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------|-------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AXI4-Stream Transm     |       |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| axis_tx_tready_o       | Out   | 64    | l –             | AXI4-Stream signal indicating that the core can accept data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| axis_tx_tdata_i        | In    | 64    | 64'h0           | AXI4-Stream data from client                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| axis_tx_tkeep_i        | In    | 8     | 8'h0            | AXI4-Stream control that indicates which data is valid on axis_rx_tdata_o[].  • axis_rx_tkeep_o[0]: axis_rx_tdata_o [7:0]  • axis_rx_tkeep_o[1]: axis_rx_tdata_o [15:8]  • axis_rx_tkeep_o[2]: axis_rx_tdata_o [23:16]  • axis_rx_tkeep_o[3]: axis_rx_tdata_o [31:24]  • axis_rx_tkeep_o[4]: axis_rx_tdata_o [39:32]  • axis_rx_tkeep_o[5]: axis_rx_tdata_o [47:40]  • axis_rx_tkeep_o[6]: axis_rx_tdata_o [55:48]  • axis_rx_tkeep_o[7]: axis_rx_tdata_o [63:56]                                                                                                                             |  |

| axis_tx_tvalid_i       | In    | 1     | 1'b0            | AXI4-Stream data valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| axis_tx_tuser_i        | In    | 1     | 1'b0            | AXI4-Stream user signal used to indicate an error in the frame. This signal is qualified with the axis_tx_tlast_i signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| axis_tx_tlast_i        | In    | 1     | 1'b0            | AXI4-Stream signal indicating the end of a packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| APB Interface          |       |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| apb_psel_i             | ı     | 1     | _               | Select signal. Indicates that the slave device is selected and a data transfer is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| apb_paddr_i            | I     | 32    | _               | Address signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| apb_pwdata_i           | - 1   | 32    | _               | Write data signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| apb_pwrite_i           | 1     | 1     | _               | Direction signal. Write = 1, Read = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| apb_penable_i          | I     | 1     | _               | Enable signal. Indicates the second and subsequent cycles of an APB transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| apb_pready_o           | 0     | 1     | 0               | Ready signal. Indicates transfer completion. Slave uses this signal to extend an APB transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| apb_prdata_o           | 0     | 32    | 0               | Read data signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Statistics Vector Inte | rface |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| tx_statvec_o           | 0     | 26    | 26'h000<br>4000 | Contains information on the frame transmitted. This bus is qualified by the tx_staten_o signal.  tx_statvec_o[13:0]: Frame byte count  tx_statvec_o[14]: Transmit is OK  tx_statvec_o[15]: MAC control inserted by MAC  tx_statvec_o[16]: MAC control inserted by Client  tx_statvec_o[17]: Jumbo frame  tx_statvec_o[18]: Tagged frame  tx_statvec_o[19]: Broadcast address  tx_statvec_o[20]: Multicast address  tx_statvec_o[21]: Underrun error  tx_statvec_o[22]: CRC error  tx_statvec_o[23]: Length check error  tx_statvec_o[24]: Terminate error  rx_statvec_o[25]: Long Frame error |  |

| tx_staten_o            | 0     | 1     | 1'b0            | When asserted, indicates that the contents of the tx_statvec_o bus are valid. This signal is asserted for 3 tx_mac_clk_i periods.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Port Name                | 1/0 | Width | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|--------------------------|-----|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| rx_statvec_o             | 0   | 26    | 26'h0   | Contains information on the frame received. This bus is qualified by the rx_staten_o signal.  rx_statvec_o[13:0]: Frame byte count  rx_statvec_o[14]: Frame dropped  rx_statvec_o[15]: Broadcast frame received  rx_statvec_o[16]: Multicast frame received  rx_statvec_o[17]: CRC error  rx_statvec_o[18]: VLAN Tag detected  rx_statvec_o[19]: PAUSE frame  rx_statvec_o[20]: Length check error  rx_statvec_o[21]: Frame is too long  rx_statvec_o[22]: MAC Address mismatch  rx_statvec_o[23]: Unsupported opcode. Only the opcode for PAUSE frame is supported.  rx_statvec_o[24]: Minimum IPG Violated  rx_statvec_o[25]: Receive packet ignored |  |  |

| rx_staten_o              | 0   | 1     | 1'b0    | When asserted, indicates that the contents of the tx_statvec_o bus are valid. This signal is asserted for 3 rx_mac_clk_i periods.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| LINTR                    |     |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| int_o                    | 0   | 1     | 0       | Interrupt request. See Interrupt registers for the details of the assertion of this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Miscellaneous            |     |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| speed_sel_i <sup>4</sup> | ı   | 2     | 0       | PHY speed selection.  • 0x0: XGMII interface  • 0x1: 8-bit GMII interface  • 0x2: 16-bit GMII interface  • 0x3: MII interface  Make sure that the MAC are idle with no packet transmission. After modifying this signal, Client is required to trigger the reset.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

#### Notes:

- 1. Available when PHY Inerface== XGMII or Dynamic Speed Selection == Enabled

- 2. 8-bit GMII is available when PHY Interface== 8-bit GMI or Dynamic Speed Selection == Enabled; 16-bit GMII signals is available when PHY Interface== 16-bit GMII or Dynamic Speed Selection == Enabled

- 3. Available when PHY Interface==MII or Dynamic Speed Selection == Enabled

- 4. Available when Dynamic Speed Selection == Enabled

# 2.4. Attribute Summary

The 10 Gb Ethernet MAC IP Core configurable attributes are as shown in Table 2.2. The values set for attributes with corresponding registers serves as the maximum values and cannot set higher than these values during dynamic reconfiguration.

**Table 2.2. Attributes Table**

| Attribute                    | Selectable Values                              | Default          | Description                                                                                                                       | Dependency on<br>Other Attributes                                          |

|------------------------------|------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| General Configuration        |                                                |                  |                                                                                                                                   |                                                                            |

| PHY Interface                | "XGMII",  "8-bit GMII",  "16-bit GMII",  "MII" | "XGMII"          | Set the default PHY Interface.                                                                                                    | _                                                                          |

| Dynamic Speed Selection      | Enabled, Disabled                              | Disabled         | Enables or disables dynamic speed selection.                                                                                      | _                                                                          |

| Multicast Address Filtering  | Enabled, Disabled                              | Disabled         | Enables or disables address filtering for Multicast frames                                                                        | _                                                                          |

| Statistics Counter Registers | Enabled, Disabled                              | Disabled         | Enabled or disables statistics counter registers                                                                                  | _                                                                          |

| Non-XGMII Configuration      |                                                |                  |                                                                                                                                   |                                                                            |

| Frame Type                   | "Standard", "Jumbo", "Super Jumbo"             | "Super<br>Jumbo" | Set Ethernet frame type to determine FIFO depth for 8-bit/16-bit GMII or MII configurations or when Dynamic Selection is enabled. | Enabled when Dynamic Speed Selection == Enabled, or PHY Interface != XGMII |

# 2.5. Registers Description

All registers are accessed through the APB interface. Access Types of each registers are defined in Table 2.3.

Table 2.3. Access Types

| Access Type | Behavior on Read Access | Behavior on Write Access                                                                      |

|-------------|-------------------------|-----------------------------------------------------------------------------------------------|

| RO          | Returns register value  | Ignores write access                                                                          |

| WO          | Returns 0               | Updates register value                                                                        |

| RW          | Returns register value  | Updates register value                                                                        |

| RW1C        | Returns register value  | Writing 1'b1 on register bit clears the bit to 1'b0. Writing 1'b0 on register bit is ignored. |

| RSVD        | Returns 0               | Ignores write access                                                                          |

# 2.5.1. Configuration Registers

The 10 Gb Ethernet MAC configuration registers are summarized in Table 2.4. These registers are accessed through APB Interface.

**Table 2.4. Summary of Configuration Registers**

| Offset | Register Name | Access | Description                          |

|--------|---------------|--------|--------------------------------------|

| 0x000  | MODE          | RW     | Mode of operation Register           |

| 0x004  | TX_CTL        | RW     | Transmit MAC Control Register        |

| 0x008  | RX_CTL        | RW     | Receive MAC Control Register         |

| 0x00C  | MAX_PKT_LNGTH | RW     | Maximum Packet Size Register         |

| 0x010  | IPG_VAL       | RW     | IPG Value Register                   |

| 0x014  | MAC_ADDR_0    | RW     | MAC Address Register Word 0          |

| 0x018  | MAC_ADDR_1    | RW     | MAC Address Register Word 1          |

| 0x01C  | TX_RX_STS     | RO     | Transmit and Receive Status Register |

| 0x020  | VLAN_TAG      | RO     | VLAN Tag Register                    |

| 0x024  | MC_TABLE_0    | RW     | Multicast Tables Register Word 0     |

| 0x028  | MC_TABLE_1    | RW     | Multicast Tables Register Word 1     |

| 0x02C  | PAUSE_OPCODE  | RW     | Pause Opcode                         |

| 0x030  | MAC_CTL       | RW     | MAC Control Register                 |

| 0x034  | PAUSE_TM      | RW     | PAUSE Time Register                  |

#### 2.5.1.1. MODE Register

This register enables the operation of the MAC. It can be written at any time.

Table 2.5. MODE Register

| Bit    | Label | Description                                                            | Default |

|--------|-------|------------------------------------------------------------------------|---------|

| [31:2] | RSVD  | Reserved bits.                                                         | 0       |

| [1]    | tx_en | TX Mac Enable When set to 1, the TX MAC is enabled to transmit frames. | 0       |

| [0]    | rx_en | RX MAC Enable When set to 1, the RX MAC is enabled to receive frames.  | 0       |

#### 2.5.1.2. TX\_CTL Register

This register should be overwritten only when the TX MAC is disabled. Writing this register while TX MAC is active results in unpredictable behavior.

Table 2.6. TX\_CTL Register

| Bit    | Label          | Description                                                                                                                                                                                                                                  | Default |

|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [31:5] | RSVD           | Reserved bits                                                                                                                                                                                                                                | 0       |

| [4]    | tx_pass_pream  | TX Custom Preamble Mode When set to 1, the TX MAC operates in custom preamble mode where it preserves the preamble field presented on the Client interface.                                                                                  | 0       |

| [3]    | transmit_short | Transmit Short Frames When set to 1, enables the TX MAC to transmit frames shorter than 64 bytes without adding padding bytes. When set to 0, TX MAC adds padding bytes when frames are shorter than 64 bytes before transmitted to the PHY. | 0       |

| [2]    | tx_ipg_stretch | IFG Stretch Mode When set to 1, the TX MAC operates in the IFG stretch mode, to match the data rates of OC-192. The IPG required to match OC-192 is added to the value specified in IPG_VAL register.                                        | 0       |

| [1]    | tx_fc_en       | Flow-control Enable When set to 1, this enables the flow control functionality of the TX MAC. This bit should be set for the TX MAC to transmit a PAUSE frame.                                                                               | 0       |

| [0]    | tx_pass_fcs    | In-band FCS Enable When set to 1, the FCS field generation is disabled in the TX MAC, and the Client is responsible to generate the appropriate FCS field.                                                                                   | 0       |

#### 2.5.1.3. RX\_CTL Register

This register should be overwritten only when the RX MAC is disabled. Writing this register while RX MAC is active results in unpredictable behaviour.

Table 2.7. RX\_CTL Register

| Bit    | Label          | Description                                                                                                                                                                                                                            | Default |

|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [15:8] | RSVD           | Reserved bits.                                                                                                                                                                                                                         | 0       |

| [7]    | rx_pass_pream  | RX Custom Preamble Mode.  When set to 1, the RX MAC operates in custom preamble mode where it preserves the preamble field of the received frame.                                                                                      | 0       |

| [6]    | drop_mac_ctrl  | Drop MAC Control Frames.  When set to 1, all MAC control frames are not passed on to the client interface.                                                                                                                             | 0       |

| [5]    | receive_short  | Receive Short Frames. When set to 1, enables the RX MAC to receive frames shorter than 64 bytes.                                                                                                                                       |         |

| [4]    | receive_bc     | Receive Broadcast Frames.  When set to 1, enables the RX MAC to receive broadcast frames.                                                                                                                                              |         |

| [3]    | receive_all_mc | Receive Multicast Frames.  When set to 1, the multicast frames are received per the filtering rules for such frames.  When set to 0, no Multicast (except PAUSE) frames are received.                                                  | 0       |

| [2]    | rx_pause_en    | Receive PAUSE Frames.  When set to 1, the RX MAC indicates the PAUSE frame reception to the TX MAC. PAUSE frames are received and transferred to the AXI4-stream interface only when drop_mac_ctrl bit is NOT set.                     | 0       |

| [1]    | rx_pass_fcs    | In-band FCS Passing. When set to 1, the FCS and any of the padding bytes are passed to the AXI4-stream interface. When set to 0, the MAC strips off the FCS and any padding bytes before transferring it to the AXI4-stream Interface. | 0       |

| Bit | Label | Description                                                                                                            | Default |

|-----|-------|------------------------------------------------------------------------------------------------------------------------|---------|

| [0] | prms  | Promiscuous Mode.  When set to 1, all filtering schemes are abandoned and the RX MAC receives frames with any address. | 0       |

#### 2.5.1.4. MAX\_PKT\_LNGTH Register

This register should be overwritten only when the MAC is disabled. All frames longer than the value (number of bytes) in this register is tagged as long frames. Writing this register while the MAC is active results in unpredictable behavior.

Table 2.8. MAX\_PKT\_LNGTH Register

| Bit     | Label       | Description                                                                                                                                                                  | Default |

|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [31:14] | RSVD        | /D Reserved bits.                                                                                                                                                            |         |

| [13:0]  | max_pkt_len | Maximum Frame Length.  Used only for statistical purposes, all frames longer than the value given here are marked as long. This value does not affect the frame's reception. | 0       |

#### 2.5.1.5. IPG\_VAL Register

This register contains the IPG value to be used by the TX MAC. Back to back packets in the transmit buffer is sent out with the IPG setting programmed in this register with Deficit Idle Count.

Table 2.9. IPG\_VAL Register

| Bit    | Label  | Description                                                                                                                                                                | Default |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [15:5] | RSVD   | Reserved bits.                                                                                                                                                             |         |

| [4:0]  | tx_ipg | Transmit Inter Packet Gap Specifies the amount of inter-frame gap in increments of 4 bytes. Refer to Section 2.8 for details. A value of 0 of this register is prohibited. | 5'h1    |

#### 2.5.1.6. MAC\_ADDR\_0 and MAC\_ADDR\_1 Register

The MAC address is stored in the registers in Hexadecimal form, so for example to set the MAC Address to: AC-DE-48-00-00-80 would require writing 0x00\_48\_DE\_AC to address 0x014 (MAC\_ADDR\_0). 0x80\_00 to address 0x018 (MAC\_ADDR\_1).

Table 2.10. MAC\_ADDR\_0 Register

| Bit    | Label      | Description                                                 | Default |

|--------|------------|-------------------------------------------------------------|---------|

| [31:0] | mac addr 0 | First four bytes of the MAC Address                         | 0       |

| [31:0] | mac_addr_0 | Ethernet address assigned to the port supported by the MAC. |         |

#### Table 2.11. MAC\_ADDR\_1 Register

| Bit     | Label        | Description                                                 | Default |

|---------|--------------|-------------------------------------------------------------|---------|

| [31:16] | RSVD         | Reserved bits.                                              | 0       |

| [15:0]  | mac addr 1   | Last two bytes of the MAC Address                           | 0       |

|         | iliac_auui_i | Ethernet address assigned to the port supported by the MAC. | U       |

#### 2.5.1.7. TX\_RX\_STS Register

#### Table 2.12. TX\_RX\_STS Register

| Bit    | Label        | Description                                                                                | Default |

|--------|--------------|--------------------------------------------------------------------------------------------|---------|

| [31:5] | RSVD         | Reserved bits.                                                                             | 0       |

| [4]    | link_ok      | Link OK When set to 1, indicates that no fault symbols were received on the link.          | 0       |

| [3]    | remote_fault | Remote fault When set to 1, indicates that remote fault symbols were received on the link. | 0       |

| [2]    | local_fault  | Local fault When set to 1, indicates that local fault symbols were received on the link.   | 0       |

| [1]    | rx_idle      | Receive MAC Idle When set to 1, indicates that the RX MAC is inactive.                     | 0       |

| [0]    | tx_idle      | Transmit MAC Idle When set to 1, indicates that the TX MAC is inactive.                    | 0       |

#### 2.5.1.8. VLAN\_TAG Register

This register has the VLAN tag field of the most recent tagged frame that was received.

#### Table 2.13. VLAN\_TAG Register

| Bit     | Label    | Description    | Default |

|---------|----------|----------------|---------|

| [31:16] | RSVD     | Reserved bits. | 0       |

| [15:0]  | vlan_tag | VLAN Tag ID.   | 0       |

#### 2.5.1.9. MC\_TABLE\_0 and MC\_TABLE\_1 Register

When the core is programmed to receive multicast frames, a filtering scheme is used to decide whether the frame should be received or not. This 64-bit matrix forms the hash table that is used to filter out the incoming multicast frames. For details, refer to Receive MAC and Appendix B.

#### Table 2.14. MC\_TABLE\_0 Register

| Bit    | Label      | Description                       | Default |

|--------|------------|-----------------------------------|---------|

| [21:0] | mc_table_0 | Multicast Table Word 0            | 0       |

| [31:0] |            | First 4-bytes of the 64-bit hash. |         |

#### Table 2.15. MC\_TABLE\_1 Register

| Bit    | Label        | Description                      | Default |

|--------|--------------|----------------------------------|---------|

| [21:0] | l mc table 1 | Multicast Table Word 1           | 0       |

| [31:0] |              | Last 4-bytes of the 64-bit hash. |         |

#### 2.5.1.10. PAUSE\_OPCODE Register

This register contains the PAUSE Opcode. This is compared against the Opcode in the received PAUSE frame. This value is also included in any PAUSE frame transmitted by the MAC.

#### Table 2.16. PAUSE\_OPCODE Register

| Bit     | Label        | Description    | Default |

|---------|--------------|----------------|---------|

| [31:16] | RSVD         | Reserved bits. | 0       |

| [15:0]  | pause_opcode | PAUSE Opcode   | 16'h01  |

#### 2.5.1.11. MAC\_CTL Register

#### Table 2.17. MAC\_CTL Register

| Bit    | Label      | Description                                                           | Default |

|--------|------------|-----------------------------------------------------------------------|---------|

| [31:5] | RSVD       | Reserved bits.                                                        |         |

| [4]    | ignore pkt | Ignore Packet.                                                        | 0       |

| [4]    | ignore_pkt | When set to 1, the RX MAC ignores/drops incoming packets.             | O       |

| [3:1]  | RSVD       | Reserved bits.                                                        |         |

|        |            | Transmit PAUSE Frame.                                                 |         |

|        |            | 1 = send request, 0 = do not send request. This is a positive edge-   |         |

| [0]    | tx_pausreq | triggered bit.                                                        | 0       |

|        |            | The tx_fc_en bit of TX_CTL register should be set to 1 to enable this |         |

|        |            | feature.                                                              |         |

#### 2.5.1.12. PAUSE\_TM Register

This register has the pause time for a flow control packet sourced by the 10 Gb MAC Transmitter.

## Table 2.18. PAUSE\_TM Register

| Bit     | Label      | Description     | Default |

|---------|------------|-----------------|---------|

| [31:16] | reserved   |                 | _       |

| [15:0]  | tx_paustim | PAUSE duration. | 0       |

## 2.5.2. Interrupt Registers

Refer to the Lattice Interrupt Interface (LINTR) User Guide for details of these registers.

**Table 2.19. Summary of Interrupt Registers**

| Offset | Register Name | Access | Description               |

|--------|---------------|--------|---------------------------|

| 0x038  | INT_STATUS    | RW1C   | Interrupt Status Register |

| 0x03C  | INT_ENABLE    | RW     | Interrupt Enable Register |

| 0x040  | INT_SET       | WO     | Interrupt Set Register    |

#### 2.5.2.1. INT\_STATUS Register

#### Table 2.20. INT\_STATUS Register

| Bit    | Label            | Description                    | Default |

|--------|------------------|--------------------------------|---------|

| [31:2] | RSVD             | Reserved bits                  | 0       |

| [1]    | remote_fault_int | Remote fault symbols received. | 0       |

| [0]    | local_fault_int  | Local fault symbols received.  | 0       |

#### 2.5.2.2. INT\_ENABLE Register

#### Table 2.21. INT\_ENABLE Register

| Bit    | Label           | Description             | Default |

|--------|-----------------|-------------------------|---------|

| [31:2] | RSVD            | Reserved bits           | 0       |

| [1]    | remote_fault_en | Enable remote_fault_int | 0       |

| [0]    | local_fault_en  | Enable local_fault_int  | 0       |

#### 2.5.2.3. INT\_SET Register

## Table 2.22. INT\_SET Register

| Bit    | Label            | Description           | Default |

|--------|------------------|-----------------------|---------|

| [31:2] | RSVD             | Reserved bits         | 0       |

| [1]    | remote_fault_set | Sets remote_fault_int | 0       |

| [0]    | local_fault_set  | Sets local_fault_int  | 0       |

#### 2.5.3. Statistics Counters

These statistic counters are wraparound counters and can only be reset when the system reset is asserted. Default value of these counters are 0.

Register name with "\_0" means the least significant word of the counter and "\_1" is the most significant word.

**Table 2.23. Summary of Statistics Counters**

| Offset | Register Name       | Access | Description                                                                                                                                            |

|--------|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x044  | TX_STAT_PKT_LNGTH_0 | RO     | Transmit Packet Length Statistics Counter. Indicates the total number of octet transmitted in a                                                        |

| 0x048  | TX_STAT_PKT_LNGTH_1 | RO     | particular frame. tx_statvec_o[13:0] is used to implement this counter.                                                                                |

| 0x04C  | TX_STAT_ERR_0       | RO     | Transmit TX Error Statistics Counter.  Counts the total number of PHY terminated packet. The                                                           |

| 0x050  | TX_STAT_ERR_1       | RO     | tx_statvec_o[24] is used to implement this counter.                                                                                                    |

| 0x054  | TX_STAT_UNDER_RUN_0 | RO     | Transmit Underrun Error Statistics Counter. Counts the total number of underrun packets                                                                |

| 0x058  | TX_STAT_UNDER_RUN_1 | RO     | transmitted. tx_statvec_o[21] is used to implement this counter.                                                                                       |

| 0x05C  | TX_STAT_CRC_ERR_0   | RO     | Transmit CRC Error Statistics Counter. Counts the total number of packets transmitted with crc                                                         |

| 0x060  | TX_STAT_CRC_ERR_1   | RO     | error. tx_statvec_o[22] is used to implement this counter.                                                                                             |

| 0x064  | TX_STAT_LNGTH_ERR_0 | RO     | Transmit Length Error Statistics Counter. Counts the total number of packets transmitted with length of the packet and length in the Length/Type field |

| 0x068  | TX_STAT_LNGTH_ERR_1 | RO     | mismatch. tx_statvec_o[23] is used to implement this counter.                                                                                          |

| 0x06C  | TX_STAT_LNG_PKT_0   | RO     | Transmit Long packet Statistics Counter. Counts the total number of packets transmitted with                                                           |

| 0x070  | TX_STAT_LNG_PKT_1   | RO     | length of the packet longer than the max_frm_size. tx_statvec_o[25] is used to implement this counter.                                                 |

| 0x074  | TX_STAT_MULTCST_0   | RO     | Transmit Multicast Packet Statistics Counter. Counts the                                                                                               |

| 0x078  | TX_STAT_MULTCST_1   | RO     | total number of multicast packets transmitted.  tx_statvec_o[20] is used to implement this counter.                                                    |

| 0x07C  | TX_STAT_BRDCST_0    | RO     | Transmit Broadcast Packet Statistics Counter. Counts                                                                                                   |

| 0x080  | TX_STAT_BRDCST_1    | RO     | the total number of broadcast packets transmitted. tx_statvec_o[19] is used to implement this counter.                                                 |

| Offset | Register Name           | Access | Description                                                                                              |

|--------|-------------------------|--------|----------------------------------------------------------------------------------------------------------|

| 0x084  | TX_STAT_CNT_0           | RO     | Transmit Control Packet Statistics Counter. Counts the total number of control packets (PAUSE frame)     |

| 0x088  | TX_STAT_CNT_1           | RO     | transmitted by the AXI4-stream interface. tx_statvec_o[16] is used to implement this counter.            |

| 0x08C  | TX_STAT_JMBO_0          | RO     | Transmit Jumbo Packet Statistics Counter. Counts the total number of jumbo packets transmitted.          |

| 0x090  | TX_STAT_JMBO_1          | RO     | tx_statvec_o[17] is used to implement this counter.                                                      |

| 0x094  | TX_STAT_PAUSE_0         | RO     | Transmit Pause Packet Statistics Counter. Counts the total number of PAUSE packets inserted by           |

| 0x098  | TX_STAT_PAUSE_1         | RO     | the MAC core (enabled through MAC_CTL register). tx_statvec_o[15] is used to implement this counter.     |

| 0x09C  | TX_STAT_VLN_TG_0        | RO     | Transmit VLAN Tag Statistics Counter.  Counts the total number of tagged packets transmitted.            |

| 0x0A0  | TX_STAT_VLN_TG_1        | RO     | tx_statvec_o[18] is used to implement this counter.                                                      |

| 0x0A4  | TX_STAT_PKT_OK_0        | RO     | Transmit Packet OK Statistics Counter. Counts the total number of packets transmitted without            |

| 0x0A8  | TX_STAT_PKT_OK_1        | RO     | any errors. tx_statvec_o[14] is used to implement this counter.                                          |

| 0x0AC  | TX_STAT_PKT_64_0        | RO     | Transmit Packet 64 Statistics Counter.                                                                   |

| 0x0B0  | TX_STAT_PKT_64_1        | RO     | Counts the total number of packets transmitted with length equal to 64.                                  |

| 0x0B4  | TX_STAT_PKT_65_127_0    | RO     | Transmit Packet 65 - 127 Statistics Counter. Counts the                                                  |

| 0x0B8  | TX_STAT_PKT_65_127_1    | RO     | total number of packets transmitted with length between 65 and 127.                                      |

| 0x0BC  | TX_STAT_PKT_128_255_0   | RO     | Transmit Packet 128-255 Statistics Counter. Counts the                                                   |

| 0x0C0  | TX_STAT_PKT_128_255_1   | RO     | <ul> <li>total number of packets transmitted with length<br/>between 128 and 255.</li> </ul>             |

| 0x0C4  | TX_STAT_PKT_256_511_0   | RO     | Transmit Packet 256-511 Statistics Counter. Counts the                                                   |

| 0x0C8  | TX_STAT_PKT_256_511_1   | RO     | total number of packets transmitted with length between 256 and 511.                                     |

| 0x0CC  | TX_STAT_PKT_512_1023_0  | RO     | Transmit Packet 512-1023 Statistics Counter. Counts the                                                  |

| 0x0D0  | TX_STAT_PKT_512_1023_1  | RO     | total number of packets transmitted with length between 512 and 1023.                                    |

| 0x0D4  | TX_STAT_PKT_1024_1518_0 | RO     | Transmit Packet 1024-1518 Statistics Counter. Counts the total number of packets transmitted with length |

| 0x0D8  | TX_STAT_PKT_1024_1518_1 | RO     | between 1024 and 1518.                                                                                   |

| 0x0DC  | TX_STAT_PKT_1518_0      | RO     | Transmit Packet 1518 Statistics Counter.                                                                 |

| 0x0E0  | TX_STAT_PKT_1518_1      | RO     | Counts the total number of packets transmitted with length greater than 1518.                            |

| 0x0E4  | TX_STAT_FRM_ERR_0       | RO     | Transmit Frame Error Statistics Counter. Counts the total number of packets transmitted with             |

| 0x0E8  | TX_STAT_FRM_ERR_1       | RO     | error. tx_statvec_o[14] is used to implement this counter.                                               |

| 0x0EC  | TX_STAT_PKT_1519_2047_0 | RO     | Transmit Packet 1519-2047 Statistics Counter. Counts                                                     |

| 0x0F0  | TX_STAT_PKT_1519_2047_1 | RO     | the total number of packets transmitted with length between 1024 and 2047.                               |