# **CertusPro-NX SerDes/PCS User Guide**

# **Technical Note**

2

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

|        | ts                                  |     |

|--------|-------------------------------------|-----|

|        | ms in This Document                 |     |

|        | troduction                          |     |

|        | atures                              |     |

|        | ing This Technical Note             |     |

|        | andards Supported                   |     |

|        | chitecture Overview                 |     |

| 5.1.   | Device Architecture                 |     |

| 5.2.   | SerDes/PCS Architecture             |     |

| 5.3.   | PCI Express Architecture            |     |

| 5.4.   | MPCS Architecture                   |     |

| 5.5.   | Reference Clock Architecture        |     |

| 5.6.   | Multi-Protocol Design Consideration |     |

| 5.7.   | SerDes/PCS Block Signal Interface   |     |

| 5.8.   | Detailed Interface Descriptions     |     |

| 5.9.   | Control and Status Signals          |     |

| 5.10.  |                                     |     |

|        | rDes/PCS Function Description       |     |

| 6.1.   | SerDes (PMA)                        |     |

| 6.2.   | PMA Controller                      |     |

| 6.3.   | PCI Express PCS                     |     |

| 6.4.   | MPCS                                |     |

| 6.5.   | Quad Common                         |     |

| 6.6.   | Reference Clock                     |     |

|        | ocks and Reset                      |     |

| 7.1.   | MPCS Channel Clock Detail           | 67  |

| 7.2.   | MPCS Quad Clock Detail              |     |

| 7.3.   | MPCS Quad-to-Quad Clock Connection  |     |

| 7.4.   | Clock Frequency                     |     |

| 7.5.   | Application Case                    |     |

| 7.6.   | PMA Clock Divider                   |     |

| 7.7.   | SerDes/PCS Reset                    | 81  |

| 8. Se  | rDes Equalization                   | 86  |

| 8.1.   | Tx Equalization                     |     |

| 8.2.   | Rx Equalization                     |     |

| 9. Se  | rDes/PCS Debug Capabilities         |     |

| 9.1.   | Loopback Mode                       | 95  |

| 9.2.   | Signal Detector                     | 97  |

| 9.3.   | Loss of Lock                        | 98  |

| 9.4.   | ECO Editor                          | 99  |

| 9.5.   | Eye Monitor                         | 100 |

| 10. Se | rDes/PCS Register Access            |     |

| 10.1.  | 3                                   |     |

| 10.2.  | Register Space                      | 103 |

|        | otocol Mode                         | 104 |

| 11.1.  | PCI Express Mode                    | 104 |

| 11.2.  | Generic 8B/10B Mode                 | 104 |

| 11.3.  | PMA Only Mode                       | 105 |

| 11.4.  | Ethernet Mode                       | 105 |

| 11.5.  | SLVS-EC Mode                        | 107 |

| 11.6.  | DisplayPort Mode                    | 108 |

| 11.7.      | CoaXPress Mode                           | 108 |

|------------|------------------------------------------|-----|

| 12. SerD   | es/PCS Block Latency                     | 109 |

| 13. Othe   | r Design Considerations                  | 110 |

| 13.1.      | Simulation of the SerDes/PCS             | 110 |

| 13.2.      | PMA PLL Filter                           | 110 |

| 13.3.      | Reference Clock Source Selection         | 111 |

| 13.4.      | Spread Spectrum Clocking Support         | 112 |

| 13.5.      | Unused Quad/Channel and Power Supply     | 112 |

| 13.6.      | Electrical Idle                          | 113 |

| 13.7.      | Multiple Data Rate Support               | 113 |

| 14. SerD   | es/PCS Generation in Radiant Software    | 114 |

| 14.1.      | Configuration GUI                        | 114 |

| 14.2.      | Primitive                                | 115 |

| Appendix   | A. Configuration Registers               | 120 |

| A.1. PN    | 1A Registers                             | 120 |

| A.1.1. R   | Register Address                         | 120 |

| A.1.2. R   | Register Description                     | 121 |

| A.2. MP    | PCS Registers                            | 132 |

| A.2.1. R   | Register Address                         | 132 |

| A.2.2. R   | Register Description                     | 134 |

| Appendix   | B. 8B/10B Symbol Coding                  | 157 |

| Appendix   | C. Calculating Parameters for SerDes PLL | 163 |

|            | <u>-</u><br>25                           |     |

| Technical  | Support Assistance                       | 171 |

| Revision F | History                                  | 172 |

## **Figures**

| Figure 5.1. CertusPro-NX 100k Device Block Diagram                       | 18 |

|--------------------------------------------------------------------------|----|

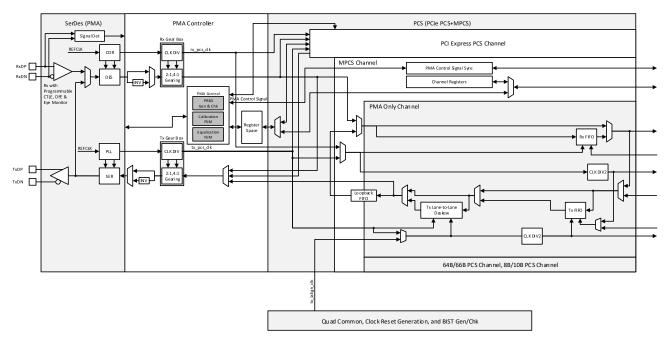

| Figure 5.2. CertusPro-NX SerDes/PCS Quad Architecture                    | 19 |

| Figure 5.3. PCI Express Hard IP Architecture                             |    |

| Figure 5.4. PCI Express Link Layer Functional Diagram                    | 21 |

| Figure 5.5. MPCS Quad Block Diagram                                      |    |

| Figure 5.6. MPCS Channel Functional Block Diagram                        |    |

| Figure 5.7. CertusPro-NX 100k Device SerDes Reference Clock Architecture |    |

| Figure 5.8. PCI Express Hard IP Mode                                     |    |

| Figure 5.9. MPCS Mode                                                    | 26 |

| Figure 5.10. PMA Only Mode                                               | 26 |

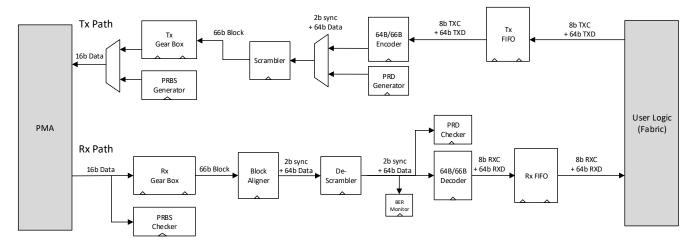

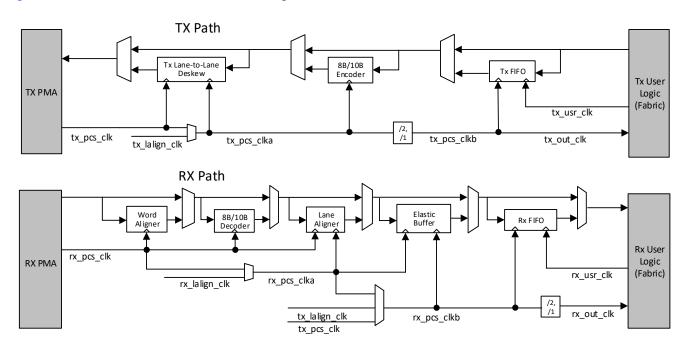

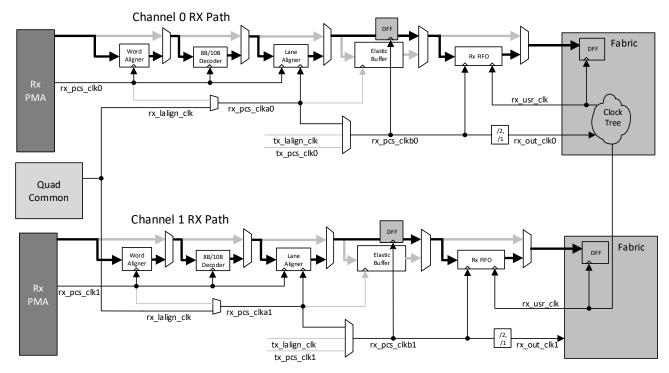

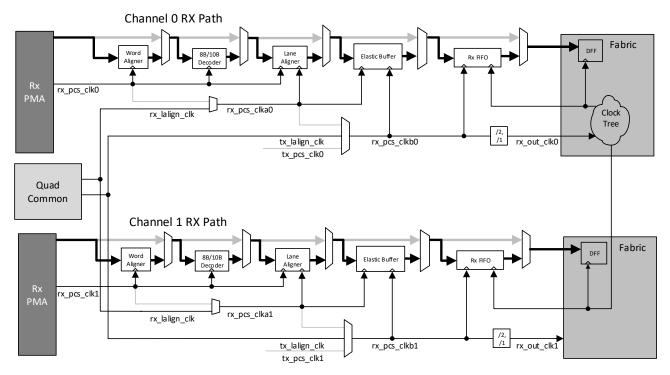

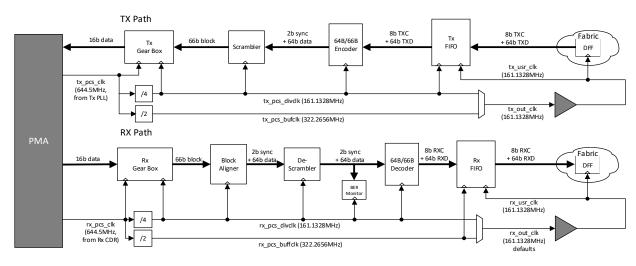

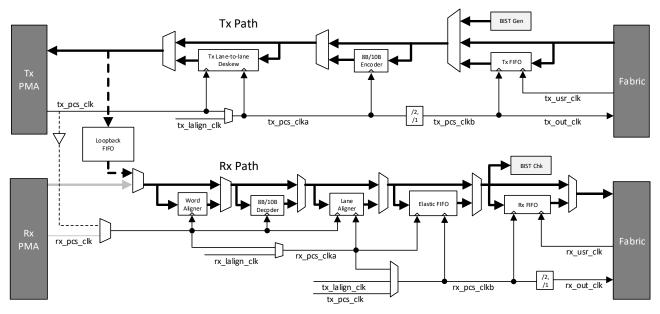

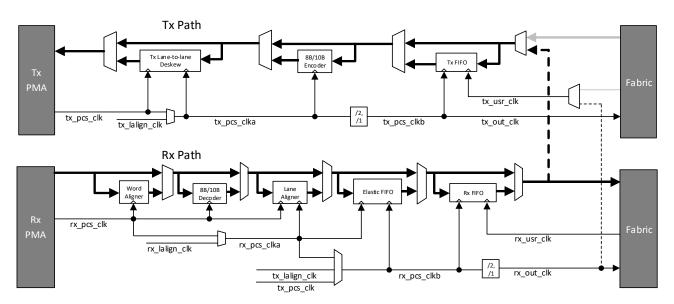

| Figure 5.11. Detailed Channel Block Diagram of MPCS-8B/10B Mode          | 39 |

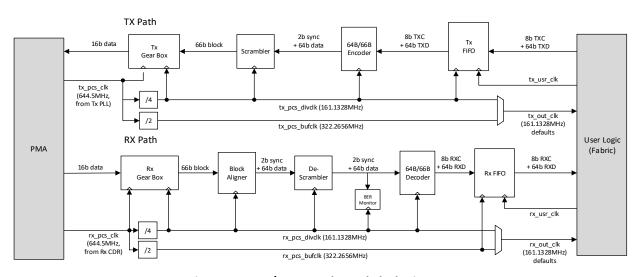

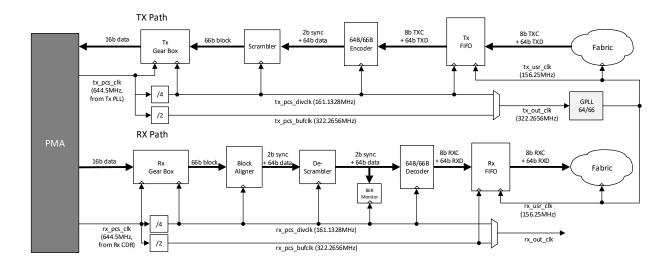

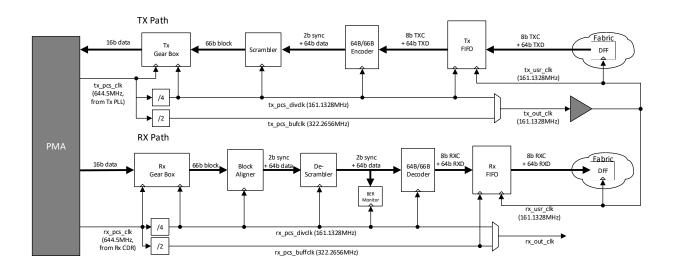

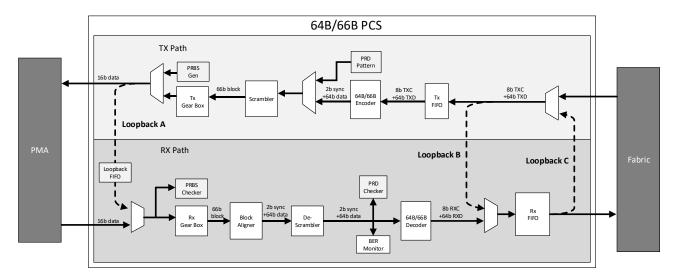

| Figure 5.12. Detailed Channel Block Diagram of MPCS-64B/66B Mode         | 40 |

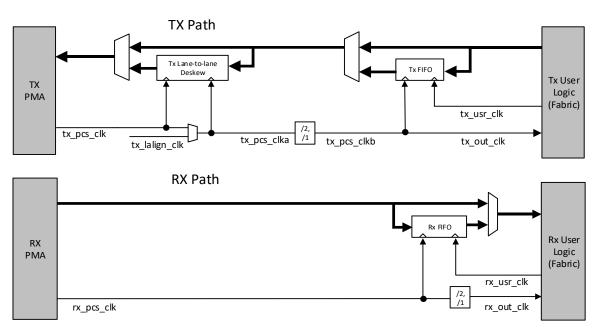

| Figure 5.13. Detailed Channel Block Diagram of MPCS-PMA Only Mode        | 40 |

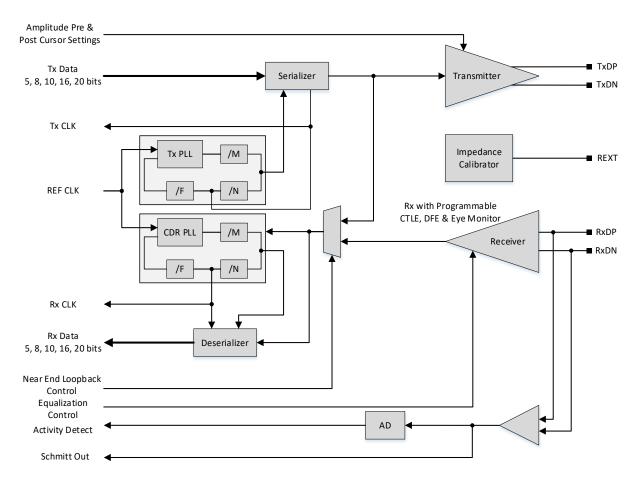

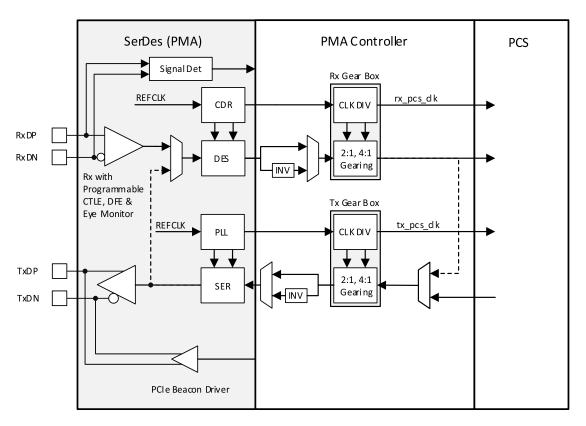

| Figure 6.1. Simplified Block Diagram of the SerDes (PMA)                 | 41 |

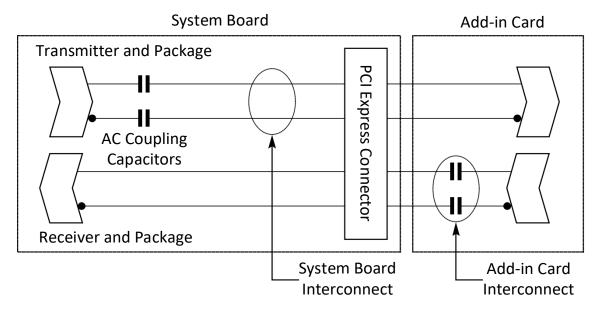

| Figure 6.2. PCI Express AC Coupling Capacitors Location                  |    |

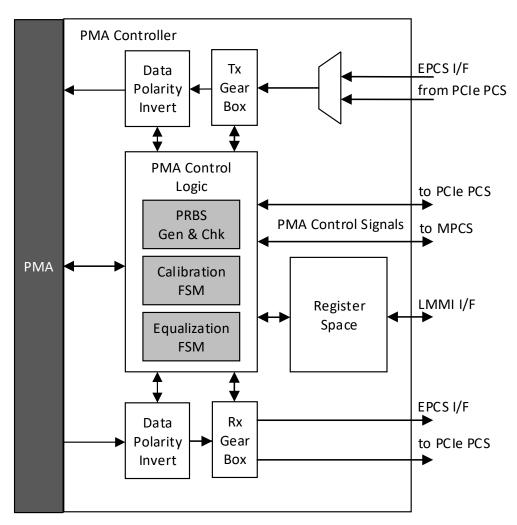

| Figure 6.3. PMA Controller Block Diagram                                 | 43 |

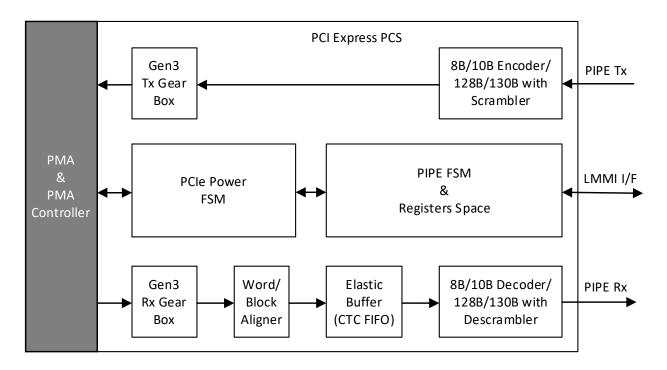

| Figure 6.4. PCI Express PCS & PMA Controller Block Diagram               | 44 |

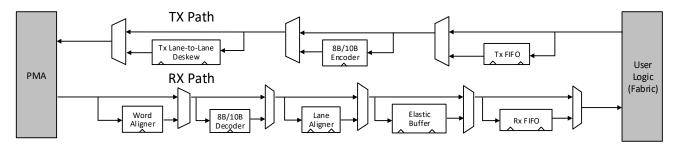

| Figure 6.5. MPCS 8B/10B PCS Block Diagram                                | 45 |

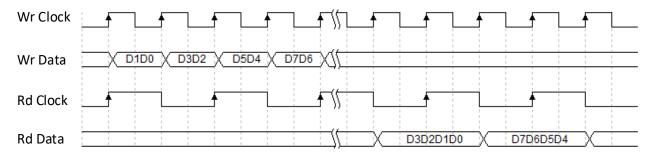

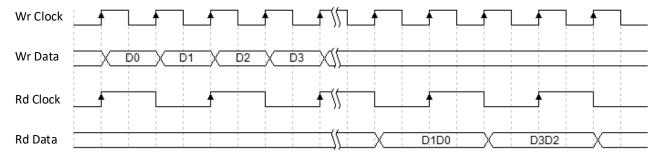

| Figure 6.6. Tx Gearing Case I                                            | 48 |

| Figure 6.7. Tx Gearing Case II                                           | 48 |

| Figure 6.8. Rx Gearing Case I                                            | 49 |

| Figure 6.9. Rx Gearing Case II                                           | 49 |

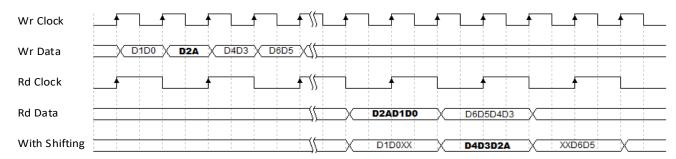

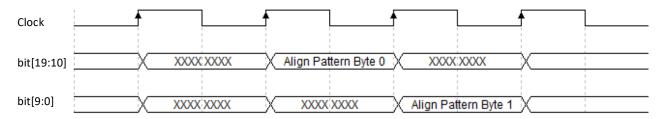

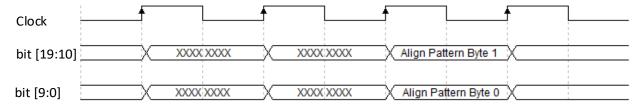

| Figure 6.10. Byte Shifting for Word Alignment Pattern                    | 50 |

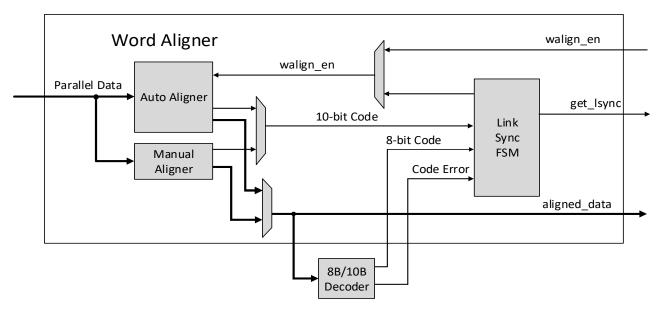

| Figure 6.11. Word Aligner Block Diagram                                  | 52 |

| Figure 6.12. Before 2-byte Boundary Alignment                            | 53 |

| Figure 6.13. After 2-byte Boundary Alignment                             | 53 |

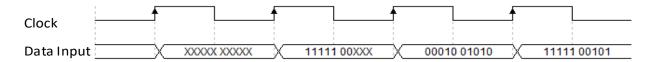

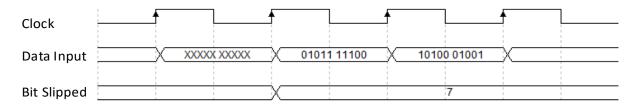

| Figure 6.14. Data Stream before Word Alignment                           | 53 |

| Figure 6.15. Data Stream after Word Alignment                            | 53 |

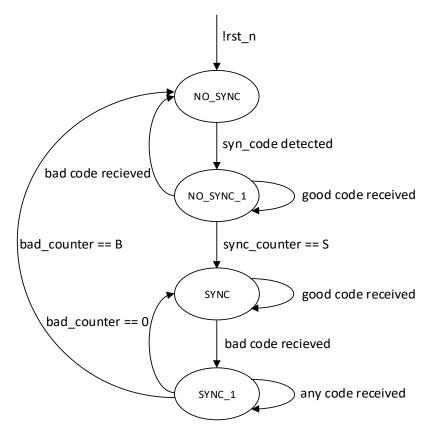

| Figure 6.16. Link Synchronization FSM                                    | 54 |

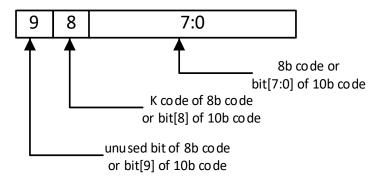

| Figure 6.17. Bit Mapping of Input Data                                   | 55 |

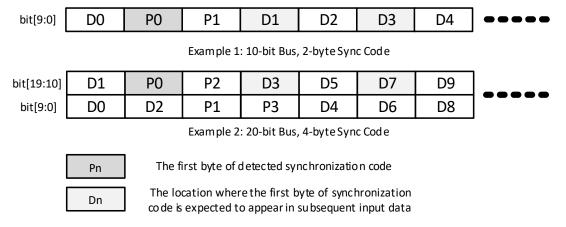

| Figure 6.18. The Expected Location of Synchronization Code               | 55 |

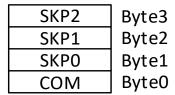

| Figure 6.19. SKIP Pattern Format                                         | 56 |

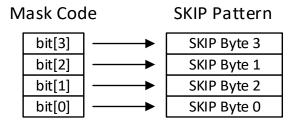

| Figure 6.20. SKIP Pattern Mask Code                                      |    |

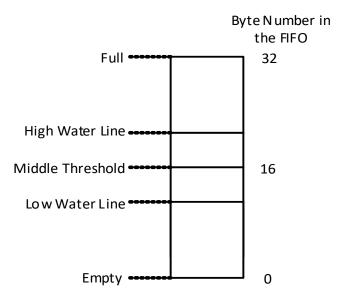

| Figure 6.21. FIFO High/Low Water Line                                    | 57 |

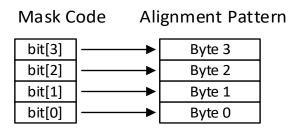

| Figure 6.22. Lane Alignment Pattern Mask Code                            | 58 |

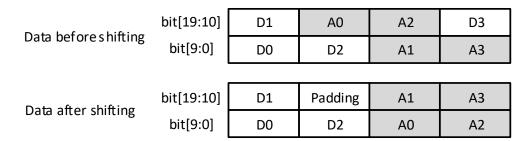

| Figure 6.23. Data Shifting for Alignment                                 | 58 |

| Figure 6.24. 64B/66B PCS Channel Block Diagram                           | 59 |

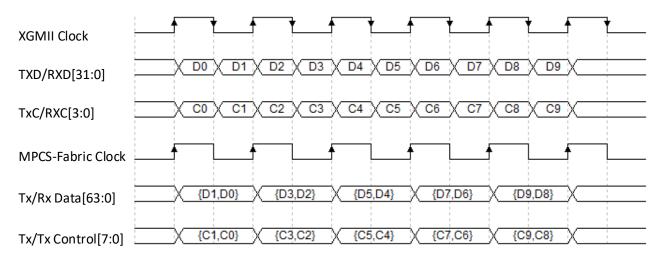

| Figure 6.25. XGMII vs. MPCS-Fabric Interface                             |    |

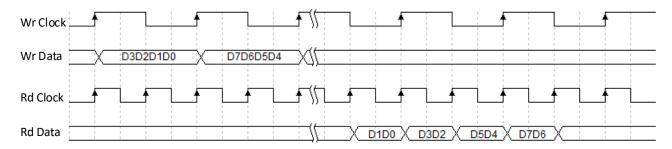

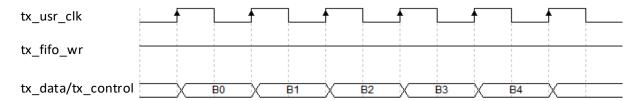

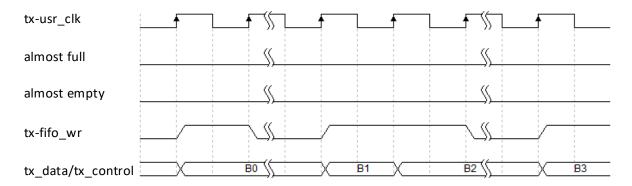

| Figure 6.26. 64B/66B PCS Tx FIFO Write Operation Case I                  | 61 |

| Figure 6.27. 64B/66B PCS Tx FIFO Write Operation Case II                 | 61 |

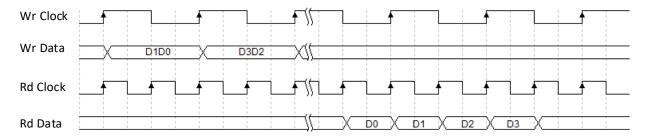

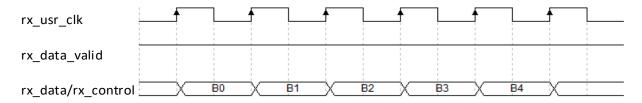

| Figure 6.28. 64B/66B PCS Rx FIFO Read Operation Case I                   | 62 |

| Figure 6.29. 64B/66B PCS Rx FIFO Read Operation Case II                  |    |

| Figure 6.30. PMA Only Mode Block Diagram                                 | 63 |

| Figure 6.31. Quad Reference Clock Source                                 | 65 |

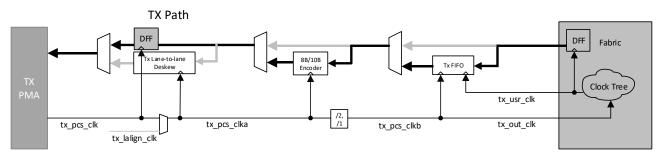

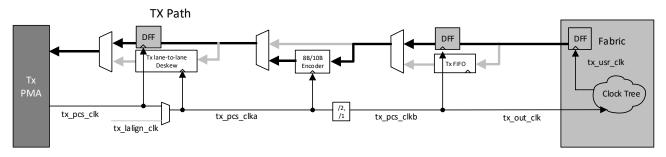

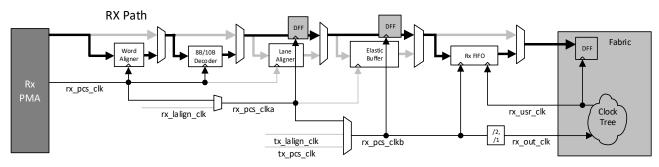

| Figure 7.1. 8B/10B PCS Channel Clock Diagram                             |    |

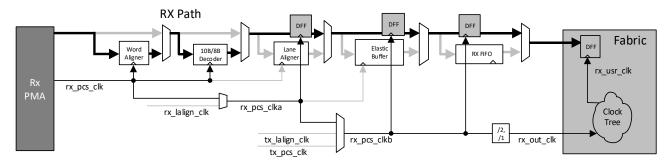

| Figure 7.2. 64B/66B PCS Channel Clock Diagram                            | 68 |

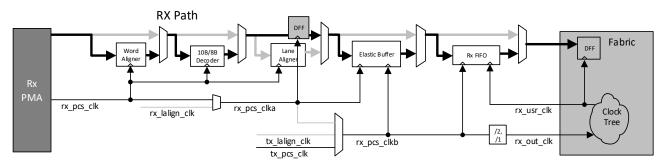

| Figure 7.3. PMA Only Mode Clock Diagram                                  |    |

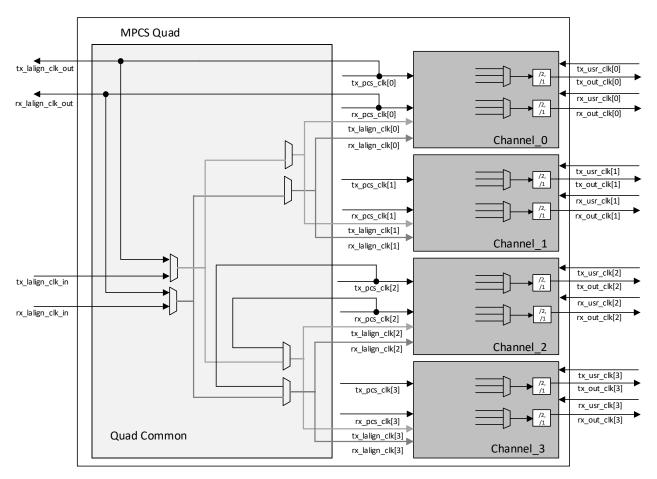

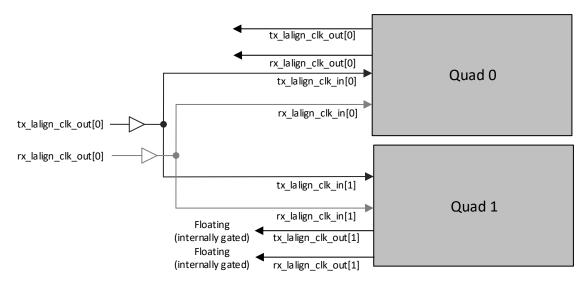

| Figure 7.4. Quad Clock Distribution Diagram                              | 72 |

| Figure 7.5. Two Quads Clock Connection                                   | 73 |

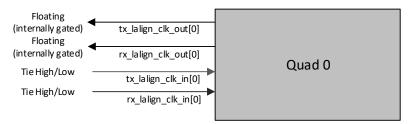

| Figure 7.6. Single Quad Clock Connection                                 | 73 |

| Figure 7.7. Case I-a Clock Structure                                     | 75 |

| Figure 7.8. Case I-b Clock Structure                               | 75  |

|--------------------------------------------------------------------|-----|

| Figure 7.9. Case II-a Clock Structure                              | 76  |

| Figure 7.10. Case II-b Clock Structure                             | 76  |

| Figure 7.11. Case II-c Clock Structure                             | 77  |

| Figure 7.12. Case III-a Clock Structure                            | 77  |

| Figure 7.13. Case IV-a Clock Structure                             | 78  |

| Figure 7.14. Case IV-b Clock Structure                             |     |

| Figure 7.15. 64B/66B PCS with Using GPLL                           | 80  |

| Figure 7.16. 64B/66B PCS without using GPLL (Case I)               | 80  |

| Figure 7.17. 64B/66B PCS without Using GPLL (Case II)              | 81  |

| Figure 7.18. CertusPro-NX SerDes/PCS Reset Generation              | 82  |

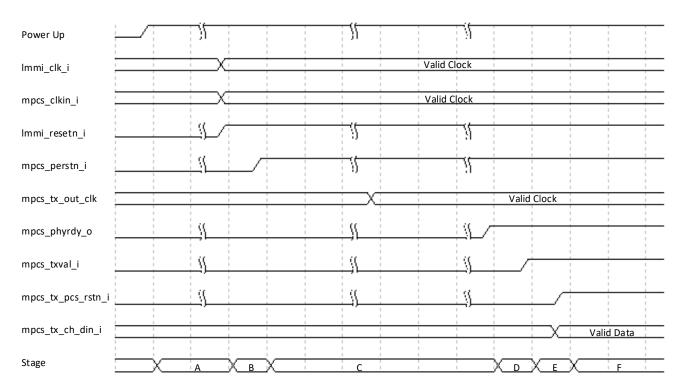

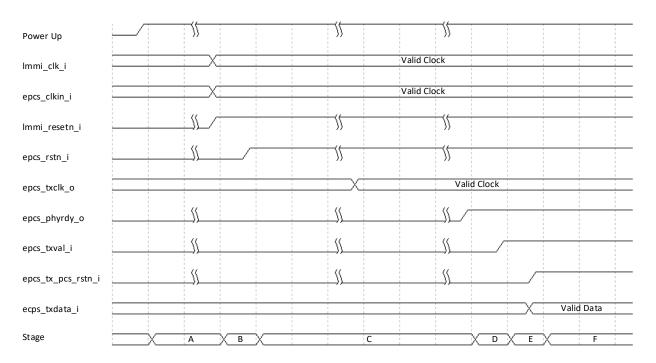

| Figure 7.19. MPCS Mode Reset Sequence (Tx Path)                    | 84  |

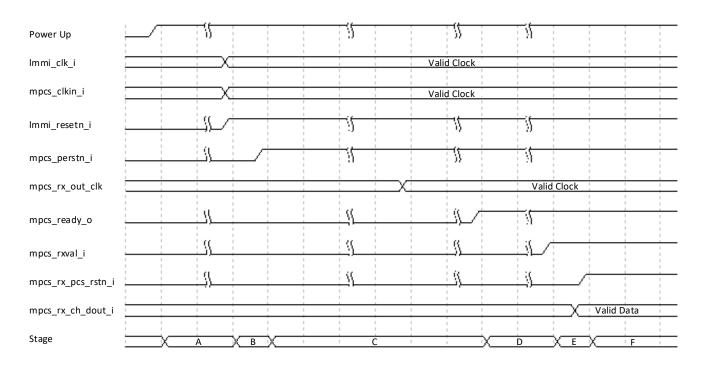

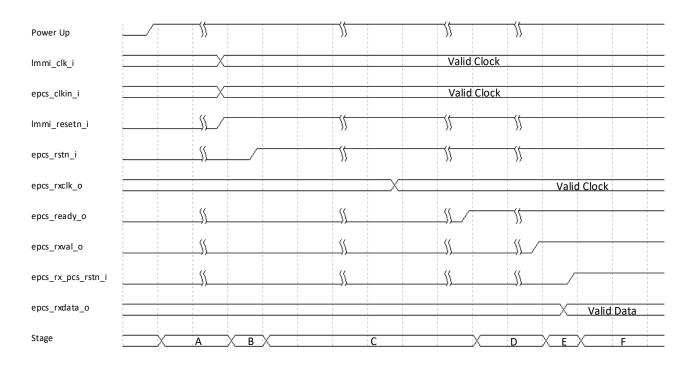

| Figure 7.20. MPCS Mode Reset Sequence (Rx Path)                    | 84  |

| Figure 7.21. EPCS Mode Reset Sequence (Tx Path)                    | 85  |

| Figure 7.22. EPCS Mode Reset Sequence (Rx Path)                    |     |

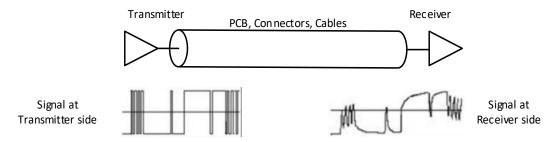

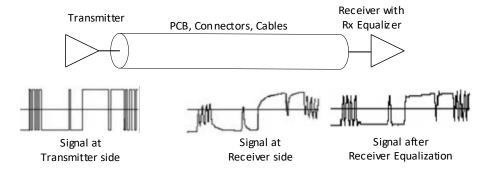

| Figure 8.1. Signal Distortion for Typical Backplane Application    | 86  |

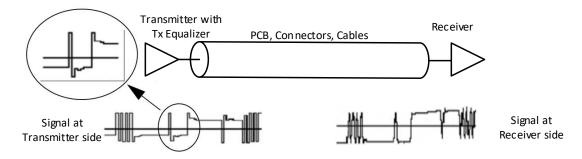

| Figure 8.2. Typical Backplane Application with Tx Equalizer        | 86  |

| Figure 8.3. Typical Backplane Application with Rx Equalizer        | 87  |

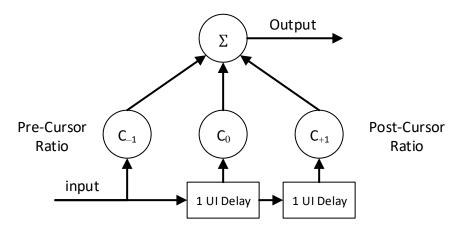

| Figure 8.4. Transmit Equalizer Block Diagram                       | 87  |

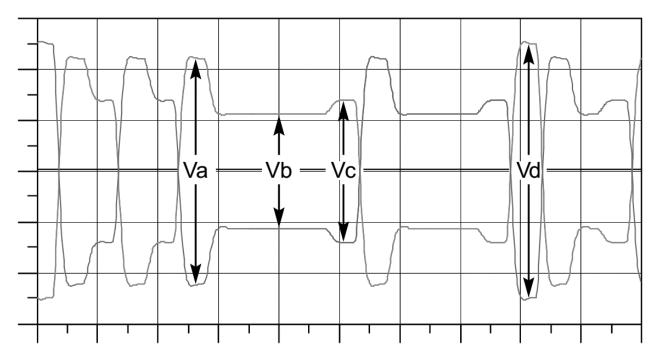

| Figure 8.5. Definition of Tx Voltage Levels                        | 88  |

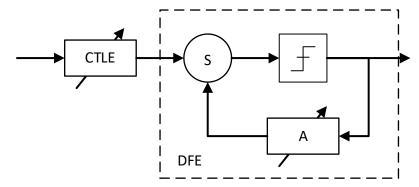

| Figure 8.6. Receive Equalizer Block Diagram                        | 89  |

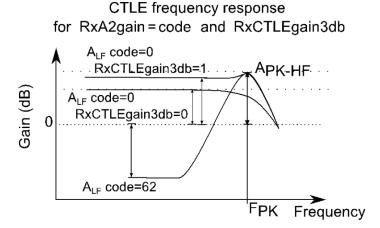

| Figure 8.7. CTLE Frequency Response                                | 89  |

| Figure 9.1. PMA Loopback Mode                                      | 95  |

| Figure 9.2. 8B/10B PCS Near-End Parallel Loopback Mode             | 96  |

| Figure 9.3. 8B/10B PCS Far-End Parallel Loopback Mode              |     |

| Figure 9.4. 64B/66B PCS Loopback Mode                              | 97  |

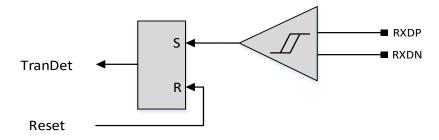

| Figure 9.5. Signal Detector                                        | 97  |

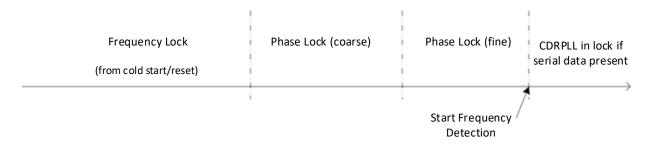

| Figure 9.6. CDR PLL Locking Flow                                   | 98  |

| Figure 9.7. Eye Monitor Block Diagram                              | 100 |

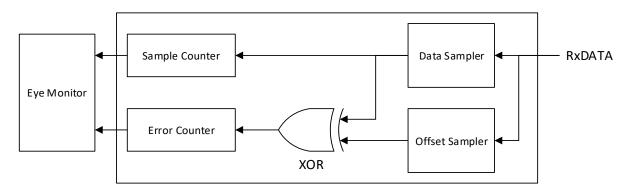

| Figure 9.8. Data Sample and Offset Sample                          |     |

| Figure 9.9. Eye Monitor Output (BER Map)                           | 101 |

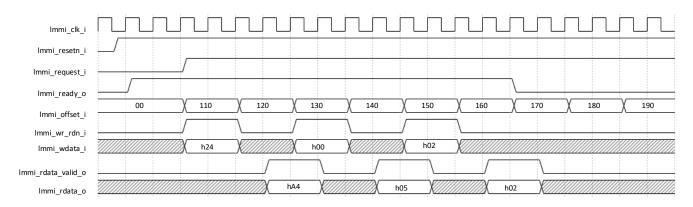

| Figure 10.1. Burst Read Transaction                                |     |

| Figure 10.2. Back-to-Back Read and Write Transaction               | 102 |

| Figure 10.3. Back-to-Back Write and Read Transaction               |     |

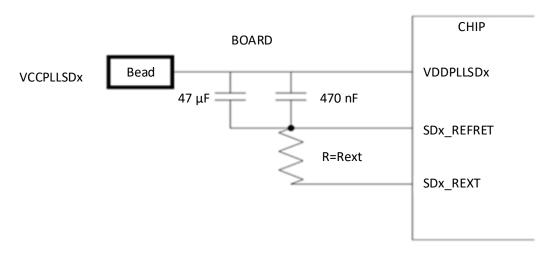

| Figure 13.1. Example Connection to Analog Power and Reference Pins | 111 |

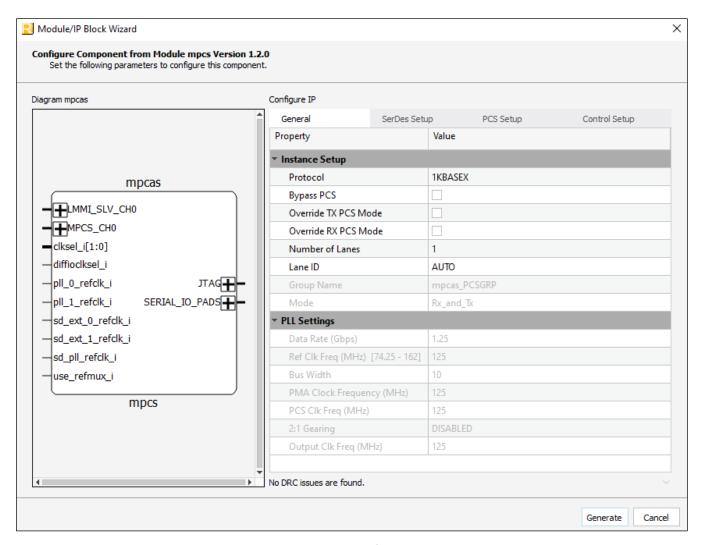

| Figure 14.1. MPCS Configuration GUI                                | 114 |

## **Tables**

| Table 4.1. Standards Supported by the SerDes/PCS                                                             | 17 |

|--------------------------------------------------------------------------------------------------------------|----|

| Table 5.1. Maximum Number of SerDes/PCS Channels per CertusPro-NX Device                                     | 18 |

| Table 5.2. Maximum Number of PCI Express Blocks per CertusPro-NX Device                                      | 19 |

| Table 5.3. Block Usage for the Corresponding SerDes/PCS Mode                                                 | 20 |

| Table 5.4. PCI Express Link Layer Quad Lane Mapping                                                          | 21 |

| Table 5.5. 10GBASE-R Lane Mapping                                                                            | 23 |

| Table 5.6. CertusPro-NX Mixed Protocols within a Quad                                                        | 25 |

| Table 5.7. MPCS Interface                                                                                    | 27 |

| Table 5.8. EPCS Interface                                                                                    | 29 |

| Table 5.9. LMMI Interface                                                                                    | 31 |

| Table 5.10. Other Signals                                                                                    | 31 |

| Table 5.11. Data Bus Sharing and Mapping                                                                     | 33 |

| Table 5.12. Control and Status Signals Functions (8B/10B PCS)                                                | 37 |

| Table 5.13. Control and Status Signals Functions (64B/66B PCS)                                               | 38 |

| Table 6.1. Operation Range for F <sub>Ref</sub> , F <sub>VCO</sub> , F <sub>bit</sub> , and F <sub>PMA</sub> | 43 |

| Table 6.2. Bit Mapping of Tx Data Bus                                                                        |    |

| Table 6.3. Bit Mapping of Rx Data Bus                                                                        | 47 |

| Table 6.4. Tx FIFO Usage                                                                                     |    |

| Table 6.5. Disparity Combinations                                                                            |    |

| Table 6.6. Example Settings for XAUI and GigE                                                                |    |

| Table 6.7. PMA Only Mode Data Bus                                                                            |    |

| Table 6.8. Channel Alignment within One Quad                                                                 |    |

| Table 6.9. Channel Alignment between Two Quads                                                               |    |

| Table 6.10. PCSREFMUX Usage                                                                                  |    |

| Table 7.1. 8B/10B PCS Channel Clock                                                                          |    |

| Table 7.2. 64B/66B PCS Channel Clock                                                                         |    |

| Table 7.3. PMA Only Mode Channel Clock                                                                       |    |

| Table 7.4. Quad Clock                                                                                        |    |

| Table 7.5. Recommend Settings for Some Protocols                                                             |    |

| Table 7.6. Reset and Power Control Signals                                                                   |    |

| Table 7.7. Reset Table for SerDes/PCS Quad                                                                   |    |

| Table 8.1. Description of Tx Voltage Levels                                                                  |    |

| Table 8.2. PCIe Tx Preset Ratios and Corresponding Coefficient Values                                        |    |

| Table 8.3. CTLE Gain Code (RxA2gain)                                                                         |    |

| Table 8.4. DFE Feedback Magnitude (RxA1gain)                                                                 |    |

| Table 8.5. Error Sampler Threshold Calculation                                                               |    |

| Table 8.6. Error Sampler Amplitude (RxA0gain)                                                                |    |

| Table 9.1. Signal Detection Conditions                                                                       |    |

| Table 9.2. Typical Duration Time for Each Lock Step                                                          |    |

| Table 9.3. CDR PLL Frequency Detector Operation Bounds                                                       |    |

| Table 10.1. Access Type Definition                                                                           |    |

| Table 11.1. PCI Express Recommend AC Capacitance                                                             |    |

| Table 11.2. GigE Configuration and IDLE Ordered Sets Definition                                              |    |

| Table 11.3. XAUI IDLE Ordered Sets Definition                                                                |    |

| Table 11.4. 64B/66B Blocks Formats                                                                           |    |

| Table 11.5. SLVS-EC Baud Rate                                                                                |    |

| Table 11.6. General Parameters of Receiver Characteristics for SLVS-EC                                       |    |

| Table 11.7. DisplayPort Recommend AC Capacitance                                                             |    |

| Table 12.1. Transmit/Receive SerDes/PCS Latency                                                              |    |

| Table 13.1. Recommended External Reference Resistor for Serval Differential Impedance Applications           |    |

| Table 13.2. SerDes Power Pins Numbering                                                                      |    |

|                                                                                                              |    |

| Table 13.3. Electrical Idle Related Signals                             | 113 |

|-------------------------------------------------------------------------|-----|

| Table 14.1. Protocol Descriptions                                       | 115 |

| Table 14.2. Pin-to-Pin Connection <sup>1</sup>                          | 115 |

| Table A.1. Register Address                                             | 120 |

| Table A.2. Control Register 0 [reg00] <sup>1</sup>                      | 121 |

| Table A.3. Clock Count for Error Counter Decrement [reg01] <sup>1</sup> |     |

| Table A.4. Error Counter Threshold – Rx Idle Detect Max Latency [reg02] |     |

| Table A.5. Rx Impedance Ratio [reg03] <sup>1</sup>                      |     |

| Table A.6. Tx PLL F Settings and PCLK Ratio [reg04] <sup>1</sup>        |     |

| Table A.7. Tx PLL M & N Settings [reg05] <sup>1</sup>                   |     |

| Table A.8. Rx PLL F Settings and PCLK Ratio [reg06] <sup>1</sup>        |     |

| Table A.9. Rx PLL M & N Settings [reg07] <sup>1</sup>                   |     |

| Table A.10. 250ns Timer Base Count [reg08] <sup>1</sup>                 |     |

| Table A.11. Tx Impedance Ratio [reg09] <sup>1</sup>                     |     |

| Table A.12. Tx Post-Cursor Ratio [reg0a] <sup>1</sup>                   |     |

| Table A.13. Tx Pre-Cursor Ratio [reg0b] <sup>1</sup>                    |     |

| Table A.14. Power down Feature [reg0e] <sup>1</sup>                     |     |

| Table A.15. Tx Amplitude Ratio [reg18]                                  |     |

| Table A.16. CDR PLL Frequency Comparator Maximum Difference [reg21]     |     |

| Table A.17. CDR PLL Frequency Comparator Maximum Difference [reg21]     |     |

| Table A.18. El4 Mode Register [reg23]                                   |     |

| Table A.19. PMA Controller Status [reg30]                               |     |

| Table A.20. PRBS Control Register [reg64] <sup>1</sup>                  |     |

| Table A.21. PRBS Error Counter Register [reg64]                         |     |

| Table A.21. PRBS Error Counter Register [reg65]                         |     |

|                                                                         |     |

| Table A.23. PHY Power Override Register [reg67]                         |     |

| Table A.25. Receive PLL Current Charge Pump [reg76] <sup>1</sup>        |     |

| Table A.25. Receive PLL Current Charge Pump [reg76]                     |     |

|                                                                         |     |

| Table A.29. RNA Status [reg79]                                          |     |

| Table A.28. PMA Status [reg7f]                                          |     |

| Table A.29. Update Settings Command Register [reg80]                    |     |

| Table A.30. Adaptive Equalization Enable Register [regd9]               |     |

| Table A.31. Applied Rx Equalization A0 Gain Register [rege4]            |     |

| Table A.32. Applied Rx Equalization A1 Gain Register [rege5]            |     |

| Table A.33. Applied Rx Equalization A2 Gain Register [rege6]            |     |

| Table A.34. Register Address                                            |     |

| Table A.35. MPCS Data Path Selection [reg00]                            |     |

| Table A.36. Tx Path Control [reg10]                                     |     |

| Table A.37. 8B/10B Encoder Control [reg11]                              |     |

| Table A.38. Rx Path Control [reg20]                                     |     |

| Table A.39. MPCS Rx Path Status [reg21]                                 |     |

| Table A.40. 8B/10B Decoder Control [reg22]                              |     |

| Table A.41. Word Alignment Control [reg30]                              |     |

| Table A.42. Primary Word Alignment Pattern Byte 0 [reg31]               |     |

| Table A.43. Primary Word Alignment Pattern Byte 1 [reg32]               |     |

| Table A.44. Primary Word Alignment Pattern MSB [reg33]                  |     |

| Table A.45. Secondary Word Alignment Pattern Byte 0 [reg34]             |     |

| Table A.46. Secondary Word Alignment Pattern Byte 1 [reg35]             |     |

| Table A.47. Secondary Word Alignment Pattern MSB [reg36]                |     |

| Table A.48. Word Alignment Pattern Mask Code Byte 0 [reg37]             |     |

| Table A.49. Word Alignment Pattern Mask Code Byte 1 [reg38]             |     |

| Table A.50. Word Alignment Pattern Mask Code MSB [reg39]                | 139 |

| Table A.51. Sync_Det FSM Configuration 0 [reg3a]                      | 139 |

|-----------------------------------------------------------------------|-----|

| Table A.52. Sync_Det FSM Configuration 1 [reg3b]                      | 139 |

| Table A.53. Sync_Det FSM Configuration 2 [reg3c]                      | 139 |

| Table A.54. Sync_Det FSM Configuration 3 [reg3d]                      | 140 |

| Table A.55. Number of Bit Slipped during Word Alignment [reg3e]       | 140 |

| Table A.56. Primary Sync_Det Pattern Byte 0 [reg3f]                   |     |

| Table A.57. Primary Sync_Det Pattern Byte 1 [reg40]                   |     |

| Table A.58. Primary Sync_Det Pattern Byte 2 [reg41]                   |     |

| Table A.59. Primary Sync Det Pattern Byte 3 [reg42]                   |     |

| Table A.60. Primary Sync_Det Pattern Byte MSB [reg43]                 |     |

| Table A.61. Secondary Sync_Det Pattern Byte 0 [reg44]                 |     |

| Table A.62. Secondary Sync Det Pattern Byte 1 [reg45]                 |     |

| Table A.63. Secondary Sync_Det Pattern Byte 2 [reg46]                 |     |

| Table A.64. Secondary Sync_Det Pattern Byte 3 [reg47]                 |     |

| Table A.65. Secondary Sync_Det Pattern Byte MSB [reg48]               |     |

| Table A.66. Sync Det Pattern Mask Code Byte 0 [reg49]                 |     |

| Table A.67. Sync_Det Pattern Mask Code Byte 1 [reg4a]                 |     |

| Table A.68. Sync_Det Pattern Mask Code Byte 2 [reg4b]                 |     |

| Table A.69. Sync_Det Pattern Mask Code Byte 3 [reg4c]                 |     |

| Table A.70. Sync_Det Pattern Mask Code MSB [reg4d]                    |     |

| Table A.71. Lane Alignment Control [reg50]                            |     |

| Table A.71. Lane Alignment Control [reg50]                            |     |

| Table A.73. Primary Lane Alignment Pattern Byte 0 [reg52]             |     |

| Table A.74. Primary Lane Alignment Pattern Byte 1 [reg53]             |     |

| Table A.75. Primary Lane Alignment Pattern Byte 2 [reg54]             |     |

| Table A.76. Primary Lane Alignment Pattern Byte 3 [reg55]             |     |

| Table A.77. Primary Lane Alignment Pattern Byte MSB [reg56]           |     |

| Table A.78. Secondary Lane Alignment Pattern Byte 0 [reg57]           |     |

| Table A.79. Secondary Lane Alignment Pattern Byte 1 [reg58]           |     |

| Table A.80. Secondary Lane Alignment Pattern Byte 2 [reg59]           |     |

| Table A.81. Secondary Lane Alignment Pattern Byte 3 [reg5a]           |     |

| Table A.82. Secondary Lane Alignment Pattern Byte MSB [reg5b]         |     |

|                                                                       |     |

| Table A.83. Lane Alignment Pattern Mask Code [reg5c]                  |     |

| Table A.84. Clock Frequency Compensation Control [reg60] <sup>1</sup> |     |

|                                                                       |     |

| Table A.83. Floatic FIFO Law Works Line [reg62]                       |     |

| Table A.88. Primary SKID Pattern Pute 0 [reg63]                       |     |

| Table A.88. Primary SKIP Pattern Byte 0 [reg64]                       |     |

| Table A.89. Primary SKIP Pattern Byte 1 [reg65]                       |     |

| Table A.90. Primary SKIP Pattern Byte 2 [reg66]                       |     |

| Table A.93. Primary SKIP Pattern Byte 3 [reg67]                       |     |

| Table A.92. Primary SKIP Pattern MSB [reg68]                          |     |

| Table A.93. Secondary SKIP Pattern Byte 0 [reg69]                     |     |

| Table A.94. Secondary SKIP Pattern Byte 1 [reg6a]                     |     |

| Table A.95. Secondary SKIP Pattern Byte 2 [reg6b]                     |     |

| Table A.96. Secondary SKIP Pattern Byte 3 [reg6c]                     |     |

| Table A.97. Secondary SKIP Pattern MSB [reg6d]                        |     |

| Table A.98. SKIP Pattern Mask Code [reg6e]                            |     |

| Table A.99. 64B/66B PCS Tx Path Control [reg80]                       |     |

| Table A.100. 64B/66B PCS Tx FIFO Almost Full Setting Control [reg81]  |     |

| Table A.101. 64B/66B PCS Tx FIFO Almost Empty Setting Control [reg82] |     |

| Table A.102. 64B/66B PCS Rx Path Control [reg83]                      |     |

| Table A.103. 64B/66B PCS CTC High Water Line Control [reg84]          | 148 |

| Table A.104. 64B/66B PCS CTC Low Water Line Control [reg85]      | 148 |

|------------------------------------------------------------------|-----|

| Table A.105. 64B/66B PCS Block Align Shift [reg86]               | 148 |

| Table A.106. 10GBASE-R BER Counter [reg90]                       |     |

| Table A.107. 10GBASE-R Block Error Counter [reg91]               |     |

| Table A.108. 10GBASE-R Test Pattern Seed A Byte 0 [reg92]        | 149 |

| Table A.109. 10GBASE-R Test Pattern Seed A Byte 1 [reg93]        | 149 |

| Table A.110. 10GBASE-R Test Pattern Seed A Byte 2 [reg94]        | 149 |

| Table A.111. 10GBASE-R Test Pattern Seed A Byte 3 [reg95]        | 149 |

| Table A.112. 10GBASE-R Test Pattern Seed A Byte 4 [reg96]        | 149 |

| Table A.113. 10GBASE-R Test Pattern Seed A Byte 5 [reg97]        | 149 |

| Table A.114. 10GBASE-R Test Pattern Seed A Byte 6 [reg98]        | 149 |

| Table A.115. 10GBASE-R Test Pattern Seed A Byte 7 [reg99]        | 150 |

| Table A.116. 10GBASE-R Test Pattern Seed B Byte 0 [reg9a]        | 150 |

| Table A.117. 10GBASE-R Test Pattern Seed B Byte 1 [reg9b]        | 150 |

| Table A.118. 10GBASE-R Test Pattern Seed B Byte 2 [reg9c]        | 150 |

| Table A.119. 10GBASE-R Test Pattern Seed B Byte 3 [reg9d]        | 150 |

| Table A.120. 10GBASE-R Test Pattern Seed B Byte 4 [reg9e]        | 150 |

| Table A.121. 10GBASE-R Test Pattern Seed B Byte 5 [reg9f]        | 150 |

| Table A.122. 10GBASE-R Test Pattern Seed B Byte 6 [rega0]        | 150 |

| Table A.123. 10GBASE-R Test Pattern Seed B Byte 7 [rega1]        | 150 |

| Table A.124. 10GBASE-R Test Pattern Control 0 [rega2]            | 151 |

| Table A.125. 10GBASE-R Test Pattern Control 1 [rega3]            | 151 |

| Table A.126. 10GBASE-R Test Pattern Error Counter Byte 0 [rega4] | 152 |

| Table A.127. 10GBASE-R Test Pattern Error Counter Byte 1 [rega5] | 152 |

| Table A.128. PMA Controller Status [regc6]                       | 152 |

| Table A.129. PMA Control [regc7]                                 | 152 |

| Table A.130. Loopback Mode Control [rege0]                       | 153 |

| Table A.131. MPCS BIST Control 0 [rege1]                         | 153 |

| Table A.132. MPCS BIST Control 1 [rege2]                         | 154 |

| Table A.133. User Defined BIST Constant 1 Byte_0 [rege3]         | 154 |

| Table A.134. User Defined BIST Constant 1 Byte_1 [rege4]         | 154 |

| Table A.135. User Defined BIST Constant 1 MSByte [rege5]         | 155 |

| Table A.136. User Defined BIST Constant 2 Byte_0 [rege6]         | 155 |

| Table A.137. User Defined BIST Constant 2 Byte_1 [rege7]         | 155 |

| Table A.138. User Defined BIST Constant 2 MSB [rege8]            | 155 |

| Table A.139. BIST Status 0 [rege9]                               | 155 |

| Table A.140. BIST Status 1 [regea]                               | 155 |

| Table A.141. PMA and PIPE PHY Status [regfe]                     | 156 |

| Table B.1. 8B/10B Data Symbol Codes                              | 157 |

| Table B.2. 8B/10B Control Symbol Codes                           |     |

| Table C.1. Recommended Parameters for SerDes PLL                 |     |

| Table C.2. Serial Protocol Applications                          | 168 |

|                                                                  |     |

# **Acronyms in This Document**

A list of vocabulary used in this document.

| list of vocabulary used in this document. |                                                                                            |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Vocabulary                                | Definition                                                                                 |  |  |  |

| AC                                        | Alternating Current                                                                        |  |  |  |

| AN                                        | Auto Negotiation                                                                           |  |  |  |

| ASIC                                      | Application Specific Integrated Circuit                                                    |  |  |  |

| BER                                       | Bit Error Ratio                                                                            |  |  |  |

| BIST                                      | Built In Self-Test                                                                         |  |  |  |

| CDR                                       | Clock and Data Recovery                                                                    |  |  |  |

| CE                                        | Consumer Electronic                                                                        |  |  |  |

| CIS                                       | CMOS Image Sensor                                                                          |  |  |  |

| CoaXPress                                 | An interface to connect devices (typical cameras) to host (typical frame grabbers)         |  |  |  |

| COMMA                                     | The seven bit comma string is defined as either 7'b0011111 (comma+) or 7'b1100000 (comma-) |  |  |  |

| CTC                                       | Clock Tolerance Compensation                                                               |  |  |  |

| CTLE                                      | Continuous Time Linear Equalizer                                                           |  |  |  |

| DC                                        | Direct Current                                                                             |  |  |  |

| DDR                                       | Double Data Rate                                                                           |  |  |  |

| DFE                                       | Decision Feedback Equalization                                                             |  |  |  |

| DFF                                       | D-Flip Flop                                                                                |  |  |  |

| DP                                        | DisplayPort                                                                                |  |  |  |

| DSP                                       | Digital Signal Processor                                                                   |  |  |  |

| eDP                                       | Embedded DisplayPort                                                                       |  |  |  |

| El1                                       | Electrical Idle 1                                                                          |  |  |  |

| EI2                                       | Electrical Idle 2                                                                          |  |  |  |

| EI4                                       | Electrical Idle 4                                                                          |  |  |  |

| EIEOS                                     | Electrical Idle Exit Ordered Set                                                           |  |  |  |

| EMI                                       | Electro-Magnetic Interference                                                              |  |  |  |

| EPCS                                      | External PCS                                                                               |  |  |  |

| ESR                                       | Equivalent Series Resistance                                                               |  |  |  |

| FEC                                       | Forward Error Correction                                                                   |  |  |  |

| FFE                                       | Feed Forward Equalizer                                                                     |  |  |  |

| FIFO                                      | First Input First Output                                                                   |  |  |  |

| FIR                                       | Finite Impulse Response                                                                    |  |  |  |

| FOM                                       | Figure of Merit                                                                            |  |  |  |

| FPGA                                      | Field-Programmable Gate Array                                                              |  |  |  |

| FS                                        | Full Swing                                                                                 |  |  |  |

| FSM                                       | Finite State Machine                                                                       |  |  |  |

| HBR                                       | High Bit Rate                                                                              |  |  |  |

| HBR2                                      | High Bit Rate 2                                                                            |  |  |  |

| HBR3                                      | High Bit Rate 3                                                                            |  |  |  |

| Gen1/Gen2/Gen3                            | Generation 1/Generation 2/Generation 3                                                     |  |  |  |

| GMII                                      | Gigabit Media Independent Interface                                                        |  |  |  |

| GPLL                                      | General Purpose PLL                                                                        |  |  |  |

| GUI                                       | Graphic User Interface                                                                     |  |  |  |

| HCSL                                      | High Speed Current Steering Logic, or Host Controller Signal Level                         |  |  |  |

| IP IP                                     | Intellectual Property                                                                      |  |  |  |

| IPG                                       | Inter-Packet Gap                                                                           |  |  |  |

| : 3                                       | inter i dence oup                                                                          |  |  |  |

| Vocabulary   | Definition                                         |

|--------------|----------------------------------------------------|

| ISI          | Inter-Symbol Interference                          |

| I/F          | Interface                                          |

| JIIA         | Japan Industrial Imaging Association               |

| JTAG         | Joint Test Action Group                            |

| L2           | A low power state inside PCIe LTSSM                |

| LF           | Low Frequency                                      |

| LMMI         | Lattice Memory Mapped Interface                    |

| LOS          | Loss of Signal                                     |

| LSByte/LSB   | Last Significant Byte                              |

| LTSSM        | Link Training and Status State Machine             |

| LVDS         | Low-Voltage Differential Signaling                 |

| MAC          | Media Access Control                               |

| MPCS         | Multi-protocol Physical Coding Sublayer            |

| MSByte/MSB   | Most Significant Byte                              |

| NL           | Number of Lane                                     |

| ООВ          | Out Of Band                                        |

| PC           | Personal Computer                                  |

| PCI          | Peripheral Component Interconnect                  |

| PCIe / PCI-E | PCI Express                                        |

| PCLK         | Primary Clock                                      |

| PCS          | Physical Coding Sublayer                           |

| PFD          | Phase Frequency Detector                           |

| PMA          | Physical Media Attachment                          |

| PMD          | Physical Medium Dependent                          |

| PIPE         | PHY Interface for PCI Express                      |

| PISO         | Parallel In Serial Out                             |

| PLL          | Phase Locked Loop                                  |

| PPM          | Parts Per Million                                  |

| PRBS         | Pseudo Random Bit Sequence                         |

| PRD          | Pseudo Random Data                                 |

| QSGMII       | Quad Serial Gigabit Media Independent Interface    |

| RBR          | Reduced Bit Rate                                   |

| RC           | Root Complex                                       |

| RS           | Reconciliation Sublayer                            |

| Rx           | Receiver                                           |

| RxDP         | Receiver Data Positive pin                         |

| RxDN         | Receiver Data Negative pin                         |

| RXAUI        | Reduced 10 Gigabit Attachment Unit Interface       |

| SATA         | Serial Advanced Technology Attachment              |

| SDR          | Single Data Rate                                   |

| SerDes       | Serializer/Deserializer                            |

| SIPO         | Serial In Parallel Out                             |

| SGMII        | Serial Gigabit Media Independent Interface         |

| SKP          | SKIP order sets defined by PCI Express             |

| SLVS-EC      | Scalable Low Voltage Signaling with Embedded Clock |

| SRIO         | Serial Rapid IO                                    |

|              | •                                                  |

13

| Vocabulary | Definition                                    |

|------------|-----------------------------------------------|

| SSC        | Spread Spectrum Clocking                      |

| SATA       | Serial ATA                                    |

| Sync       | Synchronous                                   |

| Тх         | Transmitter                                   |

| TxDP       | Transmitter Data Positive pin                 |

| TxDN       | Transmitter Data Negative pin                 |

| UI         | Unit Interval                                 |

| USB        | Universal Serial Bus                          |

| USB3       | USB SuperSpeed                                |

| VC0_RX     | Virtual Channel 0 Receiver                    |

| VC0_TX     | Virtual Channel 0 Transmitter                 |

| VESA       | Video Electronics Standards Association       |

| WAKE#      | A wake up signal defined by PCIe              |

| WIS        | WAN Interface Sublayer                        |

| XAUI       | 10 Gigabit Ethernet Attachment Unit Interface |

| XGMII      | 10 Gigabit Media Independent Interface        |

## 1. Introduction

The Lattice Semiconductor CertusPro-NX device family has up to 8 channels embedded SerDes with associated Physical Coding Sublayer (PCS) logic, which supports PCI Express Gen1/2/3 hard IP Core, DisplayPort, 10GBASE-R, 1000BASE-X, SGMII, QSGMII, XAUI, SLVS-EC, and CoaXPress protocols. There are two kinds of Physical Coding Sublayer logic inside the CertusPro-NX device: one is for PCI Express only; the other is Multi-Protocol Physical Coding Sublayer (MPCS) for protocols other than PCI Express.

Each channel of MPCS contains dedicated transmit and receive logic for high-speed, full-duplex serial data transfer at data rates up to 10.3125 Gb/s. The MPCS logic in each channel can be configured to support corresponding protocols. In addition, the protocol-based logic can be fully or partially bypassed in a number of configurations to provide the flexibility of designing user's own high-speed data interface. SerDes channel input can be independently AC-coupled or DC-coupled to meet the requirements from different protocols.

15

### 2. Features

- Single Channel MPCS Functionalities

- From 625 Mb/s up to 10.3125 Gb/s per channel

- Word alignment and link synchronization FSM

- Supports DisplayPort, SLVS-EC, CoaXPress, and Ethernet 1000BASE-X/SGMII/XAUI/QSGMII protocols

- Supports popular 8B/10B PCS-based protocols

- Supports user-specified generic 8B/10B mode

- Supports Ethernet 64B/66B coding and decoding

- Supports per channel configuration

- PMA-only mode allows direct 8-bit or 10-bit interface to FPGA logic

- Multiple Channel Alignment

- Up to eight channels of the same protocol

- Minimized Transmitter (Tx) lane-to-lane skew

- Receiver (Rx) multiple lane de-skew (up to 100 UI)

- Multiple Protocol Clock Tolerance Compensation (CTC) logic

- Compensates for frequency difference between reference clock and received data rate

- Allows user-defined SKIP pattern of 1, 2, or 4 bytes in length

- Integrated Loopback Modes for System Debugging

- Two loopback modes are provided by SerDes (PMA)

- Two loopback modes are provided by MPCS 8B/10B mode

- Three loopback modes are provided by MPCS 64B/66B mode

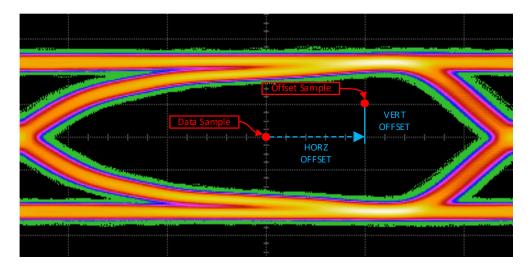

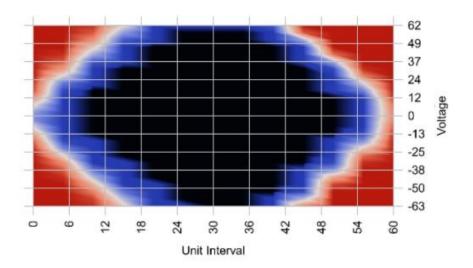

- Rx Eye Monitor

- Integrated 2D eye-scan for each Rx channel

- First on-chip SerDes debug tool in Lattice general purpose FPGAs

- SerDes Power Supply Monitor

- Integrated real-time monitor for SerDes power supply

- Easy-to-Use Design Interface in Lattice Radiant<sup>™</sup> Design Tool

- Easy-to-use Graphic User Interface (GUI)

- Some easy-to-use soft IP cores and example projects available

## 3. Using This Technical Note

This technical note provides a thorough description of the complete functionality of the embedded SerDes and associated PCS logic, including the description of:

- Architecture of the CertusPro-NX SerDes/PCS module and interface

- SerDes/PCS function

- Clock and reset

- SerDes/PCS debug capabilities

- SerDes/PCS register access

- SerDes/PCS usage for different protocols

- SerDes/PCS block latency

- SerDes/PCS generation in Lattice Radiant software

- The status and control registers associated with the SerDes and PCS logic, which can be accessed through the Lattice Memory Mapped Interface (LMMI).

The electrical and timing characteristics of the embedded SerDes and the package pinout information are provided in CertusPro-NX Family Data Sheet (FPGA-DS-02086).

The Lattice Radiant design tools support all modes of PCS. Most modes are dedicated to applications for specific industry standard data protocols listed in the Features section. Other modes are more general purpose in nature in order to let user customize user's own application settings. Radiant design tools allow the user to define the mode for each quad in the design. This technical note describes the operation of the SerDes and PCS for all modes supported by Lattice Radiant software.

## 4. Standards Supported

The supported standards are listed in Table 4.1. Note that only flip-chip package based device can support standards with data rate higher than 6.25 Gbps; refer to CertusPro-NX Family Data Sheet (FPGA-DS-02086) for more details.

Table 4.1. Standards Supported by the SerDes/PCS

| Standard                        | Data Rate (Mb/s) | System Reference<br>Clock (MHz) | FPGA Clock (MHz) | Number of Link<br>Width | Encoding Style |

|---------------------------------|------------------|---------------------------------|------------------|-------------------------|----------------|

| PCI Express Gen1 <sup>1</sup>   | 2500             | 100, 125                        | 125              | ×1, ×2, ×4              | 8b10b          |

| PCI Express Gen2 <sup>1</sup>   | 5000             | 100, 125                        | 125              | ×1, ×2, ×4              | 8b10b          |

| PCI Express Gen3 <sup>1</sup>   | 8000             | 100, 125                        | 250              | ×1, ×2, ×4              | 128b130b       |

| Ethernet 1000BASE-X             | 1250             | 125                             | 125              | x1                      | 8b10b          |

| Ethernet SGMII                  | 1250             | 125                             | 125              | ×1                      | 8b10b          |

| Ethernet XAUI                   | 3125             | 156.25                          | 156.25           | ×4                      | 8b10b          |

| Ethernet QSGMII                 | 5000             | 125                             | 125              | ×1                      | 8b10b          |

| Ethernet 10GBASE-R <sup>2</sup> | 10312.5          | 161.1328125                     | 161.1328125      | ×1                      | 64b66b         |

| SLVS-EC Grade1                  | ~1250            | _                               | ~125             | ×1, ×2, ×4, ×6, ×8      | 8b10b          |

| SLVS-EC Grade2                  | ~2500            | _                               | ~125             | ×1, ×2, ×4, ×6, ×8      | 8b10b          |

| SLVS-EC Grade3                  | ~5000            | _                               | ~125             | ×1, ×2, ×4, ×6, ×8      | 8b10b          |

| CoaXPress CXP-1                 | 1250             | 125                             | 125              | ×1~×8                   | 8b10b          |

| CoaXPress CXP-2                 | 2500             | 125                             | 125              | ×1~×8                   | 8b10b          |

| CoaXPress CXP-3                 | 3125             | 156.25                          | 156.25           | ×1~×8                   | 8b10b          |

| CoaXPress CXP-5                 | 5000             | 125                             | 125              | ×1~×8                   | 8b10b          |

| CoaXPress CXP-6                 | 6250             | 156.25                          | 156.25           | ×1~×8                   | 8b10b          |

| DP/eDP RBR                      | 1620             | 108                             | 162              | ×1, ×2, ×4              | 8b10b          |

| DP/eDP HBR                      | 2700             | 135                             | 135              | ×1, ×2, ×4              | 8b10b          |

| DP/eDP HBR2                     | 5400             | 135                             | 135              | ×1, ×2, ×4              | 8b10b          |

| DP/eDP HBR3                     | 8100             | 135                             | 202.5            | ×1, ×2, ×4              | 8b10b          |

| 10-bit/20-bit/40-bit<br>SerDes  | 625 – 8100       | _                               | _                | ×1~×8                   | N/A            |

| 8-bit/16-bit/32-bit<br>SerDes   | 625 – 8100       | _                               | _                | ×1~×8                   | N/A            |

| Generic 8b10b                   | 625 – 8100       | _                               | _                | ×1~×8                   | 8b10b          |

#### Notes:

<sup>1.</sup> CertusPro-NX supports a maximum of four lanes PCIe with hard IP, refer to the SerDes/PCS Architecture section and PCI Express Architecture section for more details.

<sup>2.</sup> CertusPro-NX SerDes does not support Ethernet 10GBASE-KR. Moreover, not all channels can support 10GBASE-R, refer to MPCS Architecture section for more details.

### 5. Architecture Overview

#### 5.1. Device Architecture

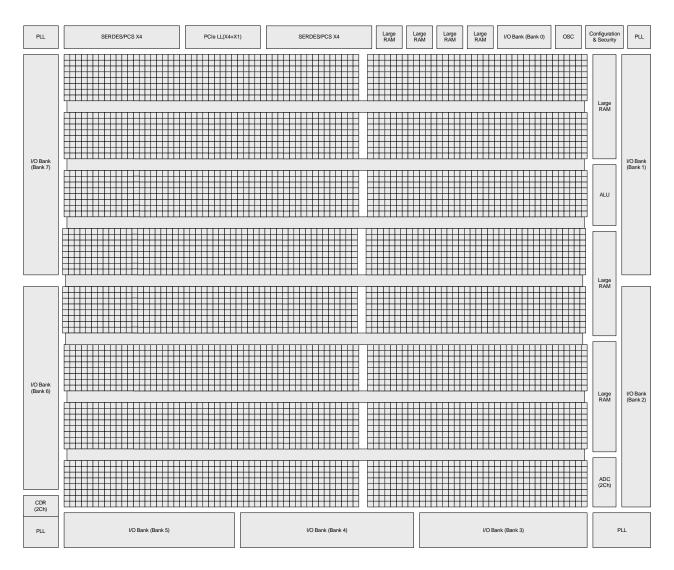

The SerDes/PCS block is arranged in quads containing logic for four full-duplex data channels. Figure 5.1 shows the arrangement of SerDes/PCS Quads on the CertusPro-NX 100k device.

Figure 5.1. CertusPro-NX 100k Device Block Diagram

Table 5.1 shows the maximum number of available SerDes/PCS channels for each CertusPro-NX device. Refer to CertusPro-NX Family Data Sheet (FPGA-DS-02086) for more details on the actual number of channels varying from package to package.

Table 5.1. Maximum Number of SerDes/PCS Channels per CertusPro-NX Device

| Package             | CertusPro-NX 50k | CertusPro-NX 100k |

|---------------------|------------------|-------------------|

| SerDes/PCS Quads    | 1                | 2                 |

| SerDes/PCS Channels | 4                | 8                 |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 5.2. SerDes/PCS Architecture

Each CertusPro-NX SerDes/PCS quad includes four PMA channels, one PCI Express PCS Quad, one MPCS Quad, and related glue logic. Each PMA channel integrates CDR for Receiver and PLL for Transmitter. The PCI Express PCS is designed only for PCI Express, while the Multi-Protocol PCS (MPCS) is designed for other protocols.

CertusPro-NX device also integrates one PCI Express Link Layer Quad, which contains one PCIe ×1 block and one PCIe ×4 block. The PCIe x4 PCI Express Link Layer block can be configured as ×1, ×2 or ×4 mode. The PCI Express Link Layer block, PCI Express PCS channels, and PMA channels constitute the complete PCI Express Hard IP block. Table 5.2 shows the maximum number of available PCI Express blocks information for the CertusPro-NX device. Refer to CertusPro-NX Family Data Sheet (FPGA-DS-02086) for more details on the actual number of channels varying from package to package.

Table 5.2. Maximum Number of PCI Express Blocks per CertusPro-NX Device

| Package                         | CertusPro-NX 50k | CertusPro-NX 100k |

|---------------------------------|------------------|-------------------|

| PCI Express Hard IP             | 1                | 1                 |

| PCI Express PCS Quad            | 1                | 2                 |

| PCI Express Link Layer ×1 Block | 1                | 1                 |

| PCI Express Link Layer ×4 Block | 1                | 1                 |

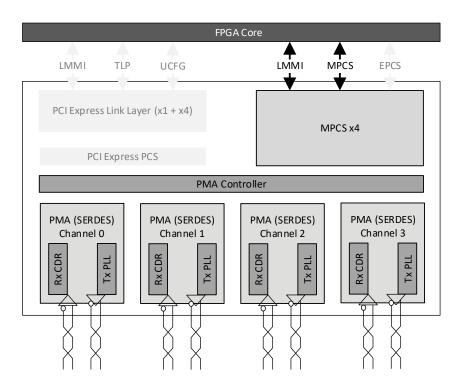

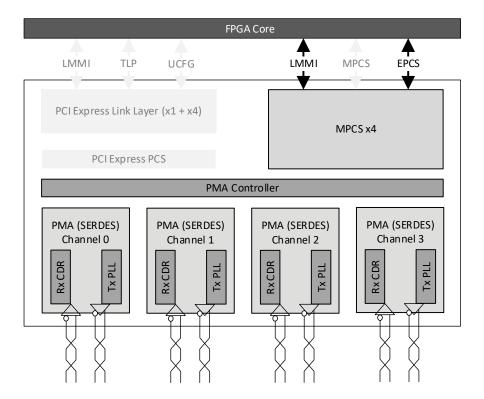

Figure 5.2 shows CertusPro-NX device SerDes/PCS quad architecture. For protocols other than PCI Express, the PCI Express PCS can be bypassed. The user can implement MPCS and PMA for Ethernet SGMII, XAUI, QSGMII, XGMII, SLVS-EC, CoaXpress, DP/eDP or Generic 8B/10B applications. The MPCS can also be bypassed so that the SerDes/PCS module works in PMA-only mode. Note that only SerDes/PCS Quad0 integrates PCIe Link Layer Hard IP (PCI Express Link Layer).

Figure 5.2. CertusPro-NX SerDes/PCS Quad Architecture

Table 5.3 shows the specific block usage for the corresponding SerDes/PCS mode.

20

Table 5.3. Block Usage for the Corresponding SerDes/PCS Mode

| SerDes/PCS Mode             | PCI Express | MPCS | PMA Only |

|-----------------------------|-------------|------|----------|

| PMA                         | V           | V    | ٧        |

| PMA Controller              | V           | ٧    | ٧        |

| PCI Express PCS             | V           | _    | _        |

| PCI Express Link Layer Quad | V           | _    | _        |

| MPCS                        | _           | ٧    | _        |

### 5.3. PCI Express Architecture

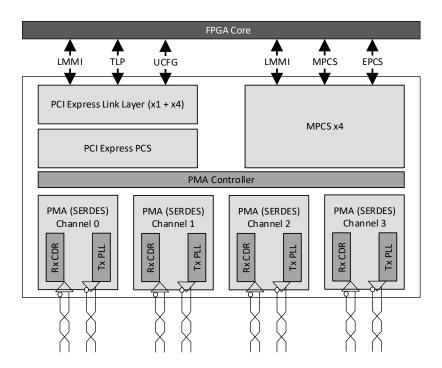

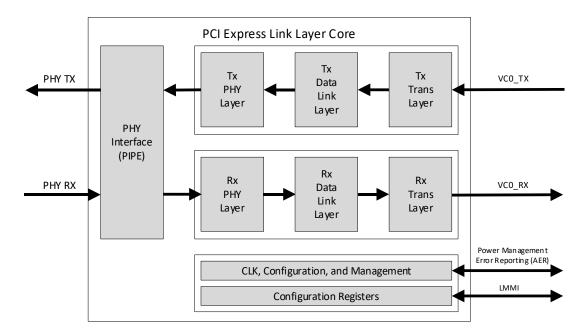

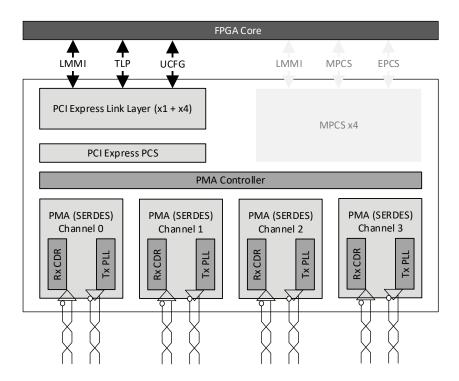

The CertusPro-NX PCI Express Link Layer block is a hard IP, which supports PCI Express Gen1, Gen2, and Gen3, and is compatible with PCI-SIG PCI Express Base Spec version 3.1a. The PCI Express Link Layer Block implements PHY Layer adaption, Data Link Layer, and Transaction Layer. The PCI Express Link Layer block together with PCI Express PCS, PMA Controller and PMA, constitute the complete PCI Express Hard IP block.

The PCI Express Hard IP supports both Endpoint and Root Complex modes. It supports up to four physical functions. Each of the four functions has independent PCI Express configurations space. It also supports ECC and parity data path protection. The LMMI interface is provided in the top wrapper that is to be used in user-controlled IP core configuration.

The PCI Express Link Layer Quad for all CertusPro-NX devices has four PIPE interfaces that can be used in different number of links. This can provide maximum flexibility, depending on the bandwidth of the application requirements.

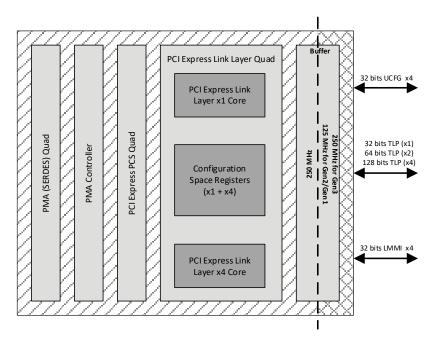

Figure 5.3 shows the architecture of the CertusPro-NX PCI Express Hard IP. There are four physical functions in the Link Layer ×4 block. There are eight physical functions in one Link Layer Quad. PCI Express Configuration Space access and Error Reporting are done through the dedicated interface (PCI Express Configuration Register Interface, UCFG). The core Configuration and Status Registers can be accessed using the corresponding LMMI interface per Link Layer block. PCI Express Link Layer block interface to PCI Express PCS block using the PIPE interface with up to 128-bit data width. The Link Layer block operates at the clock frequency of 250 MHz, while the user interface is at 125 MHz in Gen1/Gen2 speed and 250 MHz in Gen3 speed. The user interface, TLP interface, can be from 32 bits up to 128 bits wide depending on the core configuration. 32 bits of the TLP interface is used for ×1 mode, 64 bits of TLP interface is used for ×2 mode, and 128 bits of the TLP interface is used for ×4 mode.

Figure 5.3. PCI Express Hard IP Architecture

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

21

PCI Express Link Layer Quad0 can be configured as x4 mode, x2 mode, x1 mode, x2 x1 mode, and x1 x1 mode. In x2 x1 mode, the Link Layer Quad can support two independent PCI Express applications, one in ×2 mode and the other in ×1 mode. Table 5.4 describes the SerDes/PCS lane mapping details.

Table 5.4. PCI Express Link Layer Quad Lane Mapping

| Mode Name | Description                        |                             |  |  |  |

|-----------|------------------------------------|-----------------------------|--|--|--|

| ×4        | All 4 lanes are used.              |                             |  |  |  |

| ×2        | Lane 0 and Lane 1 are used.        | Lane 0 and Lane 1 are used. |  |  |  |

| ×1        | Lane 0 is used.                    |                             |  |  |  |

| ×2 ×1     | Lane 0 and Lane 1 are used for ×2. |                             |  |  |  |

| ^2_^1     | Lane 3 is used for ×1.             |                             |  |  |  |

| ×1_×1     | Lane 0 and Lane 3 are used for ×1. |                             |  |  |  |

Figure 5.4 shows the PCI Express Link Layer block functional diagram. For more detailed information on CertusPro-NX PCI Express features, function descriptions, and IP usage, refer to PCIe X4 IP Core User Guide (FPGA-IPUG-02126).

Figure 5.4. PCI Express Link Layer Functional Diagram

#### 5.4. MPCS Architecture

FPGA-TN-02245-1.5

CertusPro-NX Multi-Protocol PCS is designed for popular serial protocols other than PCI Express, such as Ethernet SGMII, XAUI, QSGMII, 10GBASE-R, SLVS-EC, CoaXpress, and DP/eDP. MPCS can be configured as Generic 8B/10B mode, for user-defined serial protocols other than those listed in the Features section.

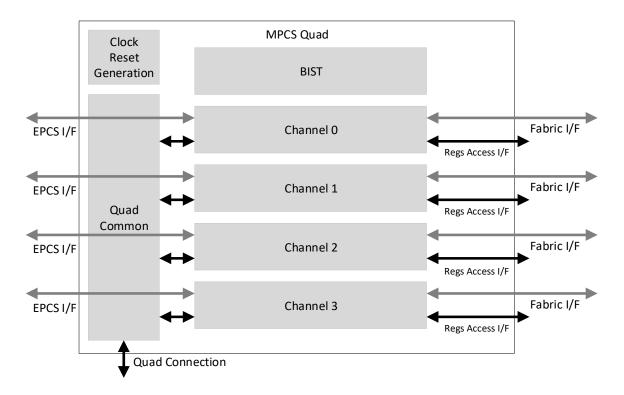

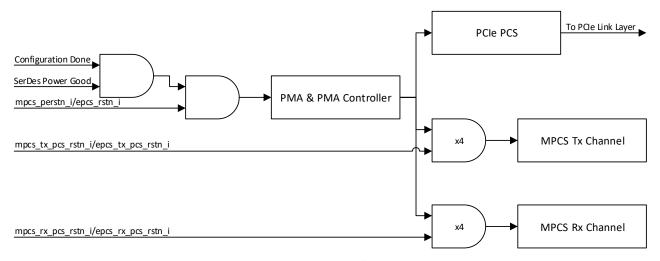

Each MPCS Quad includes four channels. One Quad Common block communicates with each channel within the Quad to implement the multiple lane alignment function for both transmitter and receiver. The Quad Common block also talks to neighboring Quads to implement the lane alignment across Quad boundary. Figure 5.5 shows the simplified block diagram of MPCS Quad.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

Figure 5.5. MPCS Quad Block Diagram

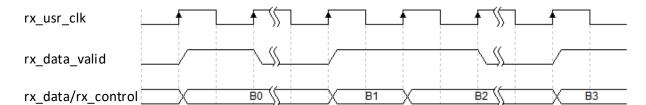

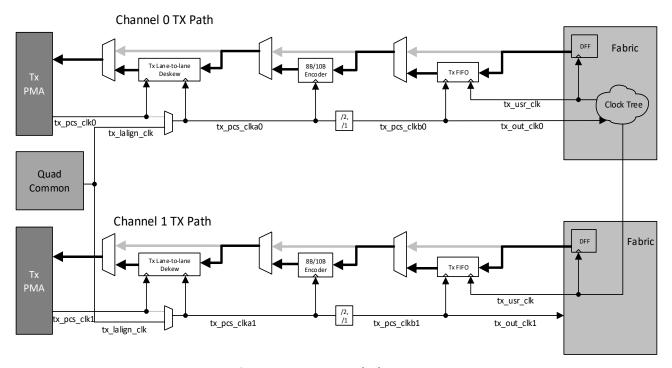

Four MPCS channels can work independently or together to compose multi-lane link. Each channel has one independent PMA interface, one LMMI interface, and one FPGA fabric interface. The internal functional block diagram of the channel is illustrated in Figure 5.6. Every Quad can be programed into one of the serval protocol-based modes.

Each Quad can be programmed with selected protocols that have the same reference clock source. For example, SGMII channel and QSGMII channel can share the same Quad using the same reference clock. When a Quad shares a PCI Express ×1 channel with a non-PCI Express channel, the reference clock for the Quad must be compatible with all protocols within the Quad. For example, a PCI Express spread spectrum reference clock is not compatible with most Gigabit Ethernet applications.

Since each Quad has its own reference clock, different Quads can support different standards on the same chip. This feature makes the CertusPro-NX family ideal for bridging between different standards. MPCS Quads are not dedicated solely to industry standard protocols. Each Quad and each channel within a Quad can be programmed for many user-defined data manipulation modes. For example, word alignment and clock tolerance compensation can be programmed for user-defined operation.

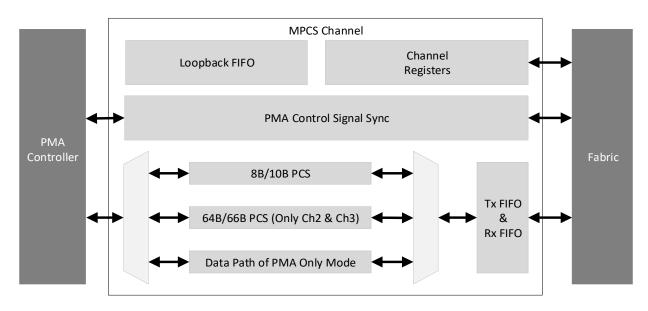

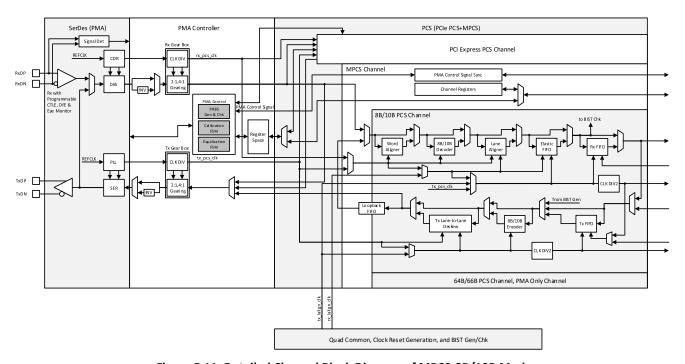

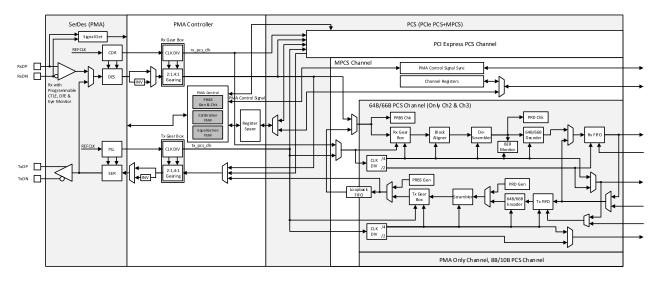

Figure 5.6. MPCS Channel Functional Block Diagram

Each MPCS channel has all the following functional blocks (Figure 5.6):

- The 8B/10B PCS: Supports popular 8B/10B PCS-based packet protocols.

- The 64B/66B PCS: Supports IEEE802.3 10GBASE-R protocol.

- PMA-only mode: Allows user logic to access PMA with very low latency.

- Channel register: Self-contained configuration and status register.

- PMA Control Signal Sync: Synchronize PMA control signals between PMA controller and user logic.

- Loopback FIFO: Internal FIFO for the corresponding loopback mode.

- Tx FIFO and Rx FIFO: Transmitter FIFO and Receiver FIFO, which are used for gearing and clock phase difference elimination.

However, in each quad, only lane 2 and lane 3 of the MPCS channel contains 64B/66B PCS. So, Ethernet 10GBASE-R is only supported by lane 2 and lane 3 of each quad, while other protocols can be supported by all lanes. Refer to Table 5.5 for more details. Lane 0 and lane 1 have no 64B/66B PCS path. So, related registers cannot be accessed by user logic.

Table 5.5. 10GBASE-R Lane Mapping

|                    | Quad0       |                                |      |      | Quad1 |     |      |      |

|--------------------|-------------|--------------------------------|------|------|-------|-----|------|------|

| Lane ID            | 0           | 1                              | 2    | 3    | 0     | 1   | 2    | 3    |

| Supported Protocol | All protoco | All protocols other than 10GE. |      |      |       |     |      |      |

| 10GE Supported     | N/A         | N/A                            | 10GE | 10GE | N/A   | N/A | 10GE | 10GE |

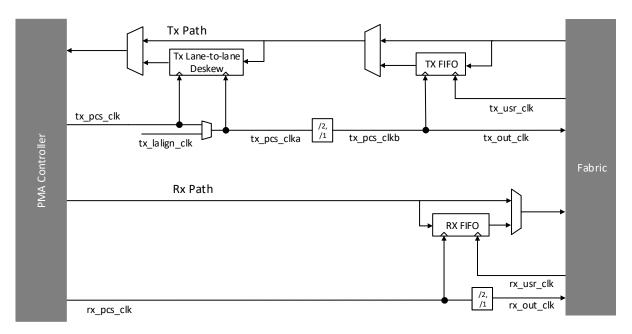

#### 5.5. Reference Clock Architecture

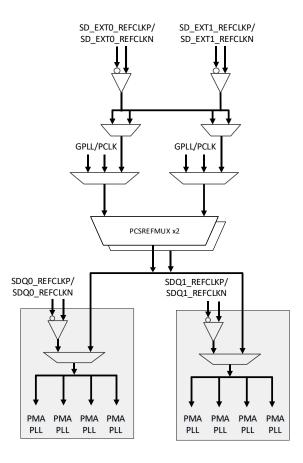

Each PMA Quad has four PMA channels. Each PMA channel has one independent Tx PLL and one independent CDR PLL. However, all PMA channels share the same reference clock source. Each Quad requires its own reference clock, which can be sourced externally from package pins, SDQx\_REFCLKP/SDQx\_REFCLKN, or from the FPGA internally.

Figure 5.7 shows CertusPro-NX 100k device SerDes/PCS reference clock architecture. The Clock Tree block is designed for balancing the skew between different Quads based on one reference clock source, and the skew between different clock sources. The reference clock can source from General-purpose PLL (GPLL) output or Primary Clock (PCLK). However, it is not suggested to use the clock from GPLL output which contains too much jitter. With the Clock Tree, different PMA Quads can use the same reference clock source, which allows the user to implement more than four lanes multi-lane serial protocols based on two or three PMA Quads.

Each device also has two dedicated external reference clock input package pins, SD\_EXTx\_REFCLKP, SD\_EXTx\_REFCLKN, which allow the user to have more choices about the reference clock sources. Reference clock source from these two dedicated pins are needed when the number of lanes is larger than four (applications across the Quad).

Figure 5.7. CertusPro-NX 100k Device SerDes Reference Clock Architecture

### 5.6. Multi-Protocol Design Consideration

Different combinations of protocols with a SerDes/PCS quad are permitted subject to certain conditions. One of the most basic requirements for two or more protocols sharing the same SerDes/PCS quad is that these protocols must have the same reference clock frequency. This restriction is due to these protocols share the same reference clock source.

Table 5.6 lists the support of mixed protocols within a CertusPro-NX SerDes/PCS quad. The reference clock must be without spread spectrum when PCI Express and other protocols share the same SerDes/PCS quad.

Table 5.6. CertusPro-NX Mixed Protocols within a Quad

| Protocol          |   | Protocol                    |

|-------------------|---|-----------------------------|

| PCI Express       | & | 1000BASE-X (GigE)           |

| PCI Express       | & | SGMII                       |

| PCI Express       | & | QSGMII                      |

| PCI Express       | & | CoaXPress CXP-1/CXP-2/CXP-5 |

| 1000BASE-X (GigE) | & | SGMII                       |

| 1000BASE-X (GigE) | & | QSGMII                      |

| 1000BASE-X (GigE) | & | CoaXPress CXP-1/CXP-2/CXP-5 |

| SGMII             | & | QSGMII                      |

| SGMII             | & | CoaXPress CXP-1/CXP-2/CXP-5 |

| QSGMII            | & | CoaXPress CXP-1/CXP-2/CXP-5 |

### 5.7. SerDes/PCS Block Signal Interface

For PCI Express Hard IP mode, the LMMI interface, TLP interface, and UCFG interface are accessible (Figure 5.8).

Figure 5.8. PCI Express Hard IP Mode

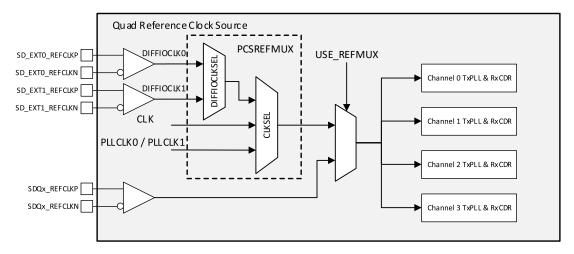

For MPCS mode, the MPCS interface and LMMI interface are accessible (Figure 5.9).

FPGA-TN-02245-1.5 25

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal

Figure 5.9. MPCS Mode

For PMA only mode, the EPCS interface and LMMI interface are accessible (Figure 5.10).

Figure 5.10. PMA Only Mode

## 5.8. Detailed Interface Descriptions

#### 5.8.1. MPCS Interface

MPCS interface is accessible when SerDes/PCS is configured as MPCS mode. MPCS mode is designed for applications other than PCIe or PMA Only modes. Table 5.7 shows the detailed MPCS interface descriptions. All the signals listed in this table are per lane, and NL means the number of lanes.

**Table 5.7. MPCS Interface**

| Port Name                         | I/O | Width | Description                                                                                                                                                                                                                                                                     |

|-----------------------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Reset                   |     |       |                                                                                                                                                                                                                                                                                 |

| mpcs_rx_usr_clk_i                 | In  | NL    | User interface Rx clock input.                                                                                                                                                                                                                                                  |

| mpcs_tx_usr_clk_i                 | In  | NL    | User interface Tx clock input.                                                                                                                                                                                                                                                  |

| mpcs_tx_pcs_rstn_i                | In  | NL    | Active low signal used to reset the Tx path of MPCS module. This signal must be released only when PMA has completed calibration.                                                                                                                                               |

| mpcs_rx_pcs_rstn_i                | In  | NL    | Active low signal used to reset the Rx path of MPCS module. This signal must be released only when PMA has completed calibration.                                                                                                                                               |

| mpcs_cc_ clk_i                    | In  | NL    | Input clock for Clock Frequency Compensation. CTC clock input.                                                                                                                                                                                                                  |

| mpcs_rx_out_clk_o                 | Out | NL    | PCS Rx output clock.                                                                                                                                                                                                                                                            |

| mpcs_tx_out_clk_o                 | Out | NL    | PCS TX output clock.                                                                                                                                                                                                                                                            |

| mpcs_perstn_i                     | In  | NL    | Fundamental reset. Triggers PCS auto calibration.                                                                                                                                                                                                                               |

| mpcs_clkin_i                      | In  | NL    | This low-speed clock drives all calibration logic inside PMA Controller. The recommended frequency range is 100-300 MHz. Note that this clock should be stable and continuous after power on.                                                                                   |

| Tx/Rx FIFO Signals                |     |       |                                                                                                                                                                                                                                                                                 |

| mpcs_tx_ch_din_i                  | In  | 80*NL | For the signal mapping of this port, refer to Table 5.11.                                                                                                                                                                                                                       |

| mpcs_tx_fifo_st_o                 | Out | 4*NL  | For the signal mapping of this port, refer to Table 5.11.                                                                                                                                                                                                                       |

| mpcs_rx_ch_dout_o                 | Out | 80*NL | For the signal mapping of this port, refer to Table 5.11.                                                                                                                                                                                                                       |

| mpcs_rx_fifo_st_o                 | Out | 4*NL  | For the signal mapping of this port, refer to Table 5.11.                                                                                                                                                                                                                       |

| Elastic Buffer Signals (8B/10B Po | CS) |       |                                                                                                                                                                                                                                                                                 |

| mpcs_ebuf_empty_o                 | Out | NL    | <ul> <li>Elastic Buffer Empty output port.</li> <li>1'b1 – the frequency compensation buffer, Elastic Buffer, is empty.</li> <li>1'b0 – the frequency compensation buffer, Elastic Buffer, is not empty.</li> </ul>                                                             |

| mpcs_ebuf_full_o                  | Out | NL    | <ul> <li>Elastic Buffer Full output port.</li> <li>1'b1 – the frequency compensation buffer, Elastic Buffer, is full.</li> <li>1'b0 – the frequency compensation buffer, Elastic Buffer, is not full.</li> </ul>                                                                |

| mpcs_anxmit_i                     | In  | NL    | In GigE application case, the high level of this signal indicates the current state is GigE Auto-negotiation. In this state, replace /C1/, /C2/ with /I2/ ordered sets periodically so that the following stage (CTC) gets opportunity to perform clock frequency compensation. |

| Word Aligner Signals (8B/10B Pe   | CS) |       |                                                                                                                                                                                                                                                                                 |

| mpcs_walign_en_i                  | In  | NL    | Word alignment enabling input port. This function is useful if the automatic synchronization is not enabled. The rising edge of this signal triggers the word alignment operation.                                                                                              |

| mpcs_get_lsync_o                  | Out | NL    | <ul> <li>Link Synchronization output port.</li> <li>1'b1 – link synchronization is acquired.</li> <li>1'b0 – loss of link synchronization.</li> </ul>                                                                                                                           |

| Port Name                      | 1/0        | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |