# **Automate Stack 2.0**

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| Acronyms in This Document                         | 11 |

|---------------------------------------------------|----|

| L. Introduction                                   | 12 |

| 1.1. Components                                   | 13 |

| 2. Design Overview                                | 14 |

| 2.1. Theory of Operation                          | 14 |

| 2.2. FPGA Design                                  | 15 |

| 2.2.1. Main System                                | 15 |

| 2.2.2. Node System                                | 18 |

| 2.3. EtherControl IP                              | 20 |

| 2.3.1. Features                                   | 21 |

| 2.3.2. EtherControl Master                        | 22 |

| 2.3.3. Register Description                       | 23 |

| 2.3.4. EtherControl Slave                         | 42 |

| 2.4. RISC-V to PCIe Bridge                        | 45 |

| 2.5. FIFO DMA                                     | 48 |

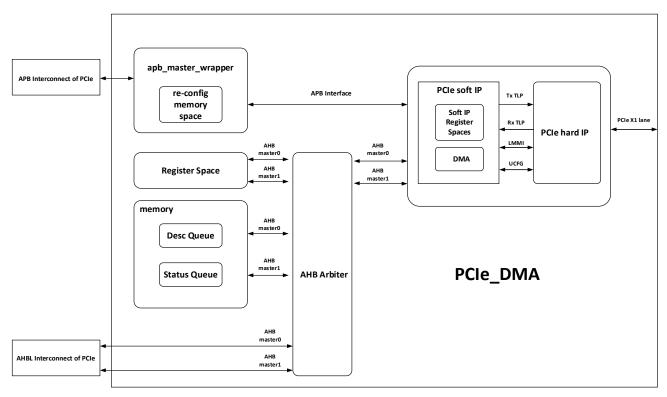

| 2.6. PCIe DMA IP Design Details                   | 51 |

| 2.6.1. Descriptor Field Format                    | 52 |

| 2.6.2. Status Field Format                        | 53 |

| 2.6.3. Triggering the DMA Operation               | 53 |

| 2.6.4. PCIe DMA Register Space                    |    |

| 2.7. SPI Flash Controller (QSPI Streamer)         |    |

| 2.8. CNN Co-Processor Unit (CCU)                  |    |

| 2.9. Motor Control and PDM Data Collector         |    |

| 2.10. SPI Master IP Design Details                |    |

| 2.10.1. Overview                                  |    |

| 2.10.2. SPI Master Register Map                   |    |

| 2.10.3. Programming Flow                          |    |

| 2.11. I <sup>2</sup> C Master IP Design Details   |    |

| 2.11.1. Overview                                  |    |

| 2.11.2. I <sup>2</sup> C Master Register Map      |    |

| 2.11.3. Programming Flow                          |    |

| 2.12. UART IP Design Details                      |    |

| 2.12.1. Overview                                  |    |

| 2.12.2. Programming Flow                          |    |

| 3. Resource Utilization                           |    |

| 1. Software APIs                                  |    |

| 4.1. Main System APIs                             |    |

| 4.1.1. Tasks of the Main System                   |    |

| 4.1.2. Key Functions                              |    |

| 4.2. Node System APIs                             |    |

| 4.2.1. Tasks of the Node System                   |    |

| 4.2.2. Key Functions                              |    |

| 4.3. PCie Driver                                  |    |

| 4.3.1. Linux Device Driver Design                 |    |

| 4.3.2. User-Space to Kernel-Space Access          |    |

| 4.3.3. File Operation and API Description         |    |

| 4.3.4. PCleProbe                                  |    |

| 4.3.5. PCIeRemove                                 |    |

| 4.3.6. Bus Master DMA Overview and Implementation |    |

| 4.4. Programming the DMA Write/Read               |    |

| 4.4.1. Supported Operating System                 |    |

| 4.4.2. Package Requirements                       |    |

| 30,400                                            |    |

| 4.4.3. Installing the Package                                                            | 92  |

|------------------------------------------------------------------------------------------|-----|

| 4.4.4. Manual Installation and Setup                                                     | 93  |

| 4.4.5. Automatic Installation and Setup                                                  | 93  |

| 5. Communications                                                                        | 94  |

| 5.1. Communication between Host and Main System                                          | 94  |

| 5.1.1. Messages from Host to Main System                                                 | 94  |

| 5.1.2. Messages from Main System to Host                                                 | 94  |

| 5.2. Communication between Main System and Node System(s)                                | 94  |

| 5.2.1. Messages from Main System to Node System                                          | 94  |

| 5.2.2. Messages from Node System to Main System                                          | 94  |

| 6. Demo Package Directory Structure                                                      | 95  |

| 6.1. Automate Stack Demonstration                                                        | 95  |

| 6.1.1. Documentation                                                                     |     |

| 7. Summary                                                                               | 96  |

| Appendix A. Predictive Maintenance with TensorFlow Lite                                  | 97  |

| A.1. Setting Up the Linux Environment for Neural Network Training                        |     |

| A.1.1. Installing the NVIDIA CUDA and cuDNN Library for Machine Learning Training on GPU |     |

| A.1.2. Setting Up the Environment for Training and Model Freezing Scripts                |     |

| A.1.3. Installing the TensorFlow version 1.15                                            |     |

| A.1.4. Installing the Python Package                                                     |     |

| A.2. Creating the TensorFlow Lite Conversion Environment                                 |     |

| A.3. Preparing the Dataset                                                               |     |

| A.3.1. Dataset Information                                                               |     |

| A.4. Preparing the Training Code                                                         |     |

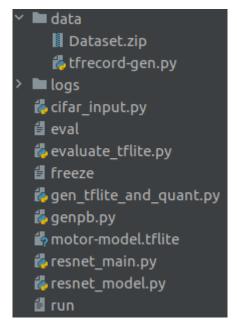

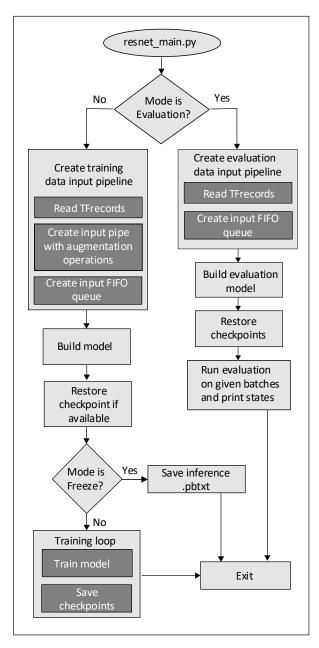

| A.4.1. Training Code Structure                                                           |     |

| A.4.2. Generating tfrecords from Augmented Dataset                                       |     |

| A.4.3 Neural Network Architecture                                                        |     |

| A.4.4. Training Code Overview                                                            |     |

| A.4.5. Training from Scratch and/or Transfer Learning                                    |     |

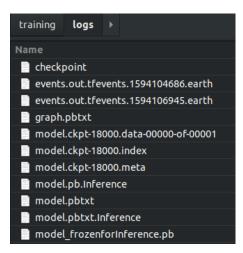

| A.5. Creating Frozen File                                                                |     |

| A.5.1. Generating .pbtxt File for Inference                                              |     |

| A.5.2. Generating the Frozen (.pb) File                                                  |     |

| A.6. TensorFlow Lite Conversion and Evaluation                                           |     |

| A.6.1. Converting Frozen Model to TensorFlow Lite                                        |     |

| A.6.2. Evaluating TensorFlow Lite model                                                  |     |

| A.6.3. Converting TensorFlow Lite To C-Array                                             |     |

| Appendix B. Setting up the Auto-Bootable MQTT-Based Client                               |     |

| B.1. Unzipping the Folder                                                                |     |

| B.2. OpenSSL Error                                                                       |     |

| B.3. Making the New Server Executable                                                    |     |

| B.4. Installing the Mosquitto Broker                                                     |     |

| B.5. Automating the Application                                                          |     |

| B.6. Setting Up the IPV4 Address and Router on Raspberry Pi                              |     |

| Technical Support Assistance                                                             |     |

| Revision History                                                                         | 123 |

# **Figures**

| Figure 1.1. Top Level Block Diagram of Automate Stack 2.0                      | 12 |

|--------------------------------------------------------------------------------|----|

| Figure 2.1. Automate Stack 2.0 Architecture                                    | 14 |

| Figure 2.2. Main System Architecture                                           | 16 |

| Figure 2.3. Node System Architecture                                           | 19 |

| Figure 2.4. EtherControl Block Diagram                                         | 20 |

| Figure 2.5. EtherControl Master Block Diagram                                  | 22 |

| Figure 2.6. EtherControl Slave                                                 | 42 |

| Figure 2.7. Top Level Architecture of PCIe DMA IP Design                       | 51 |

| Figure 2.8. FPGA Device Memory Segregation                                     | 54 |

| Figure 2.9. Motor Controller Interface with Motor                              | 59 |

| Figure 2.10. SPI Master IP Core Block Diagram                                  | 68 |

| Figure 2.11. I <sup>2</sup> C Master IP Core Functional Diagram                | 71 |

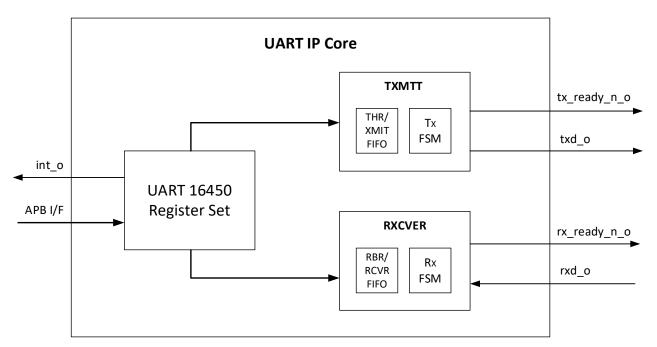

| Figure 2.12. UART IP Core Functional Block Diagram                             | 74 |

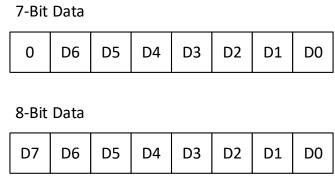

| Figure 2.13. UART Data Format                                                  | 76 |

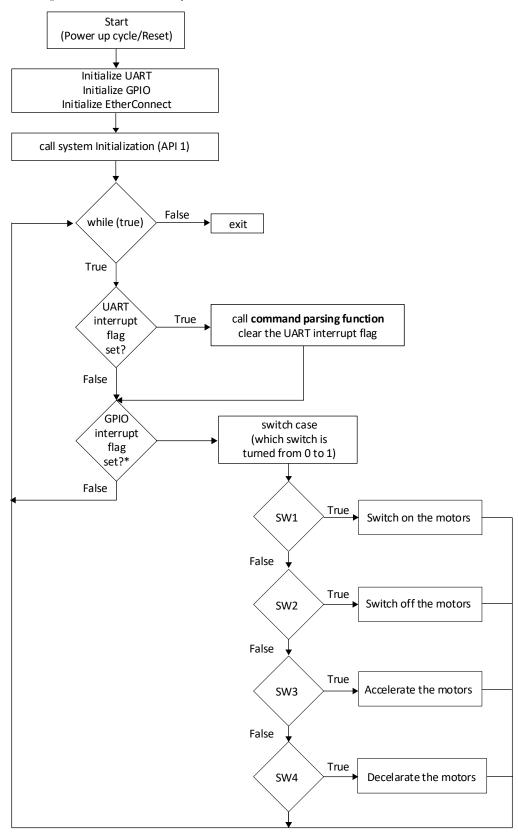

| Figure 4.1. Main Function                                                      | 80 |

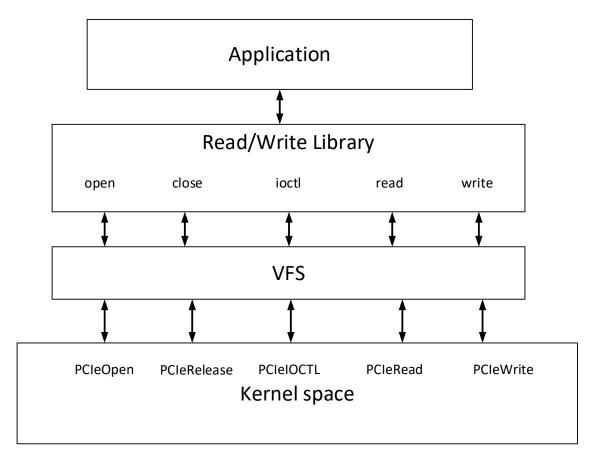

| Figure 4.2. User-Space and Kernel-Space Access Diagram                         |    |

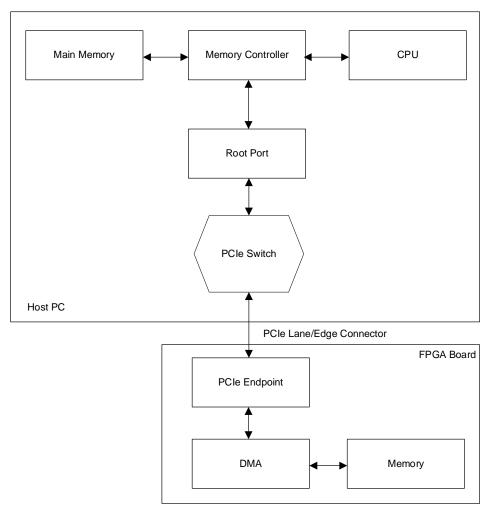

| Figure 4.3. Top-level Block Diagram                                            |    |

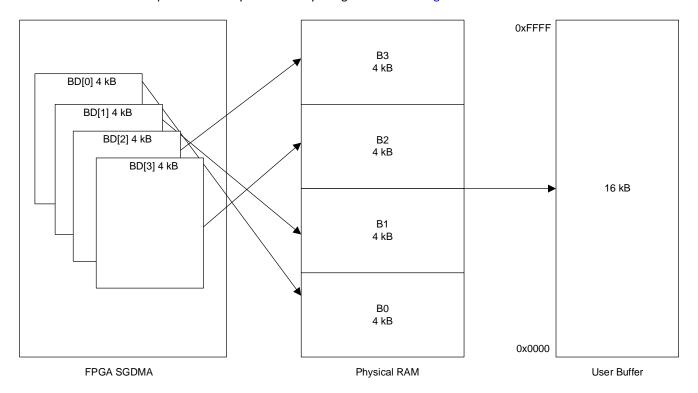

| Figure 4.4. BMD with Descriptor and Fixed Physical Memory in RAM               |    |

| Figure 4.5. Make Flle                                                          |    |

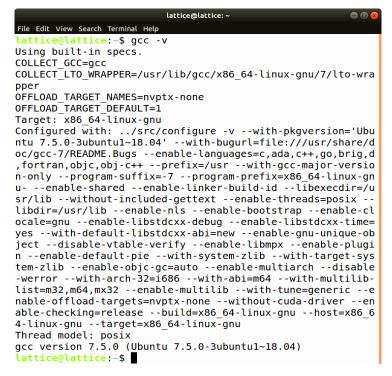

| Figure 4.6. GCC Command                                                        |    |

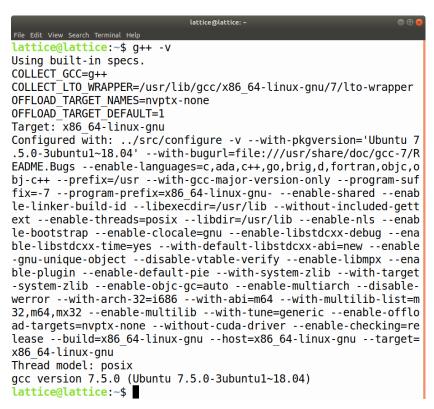

| Figure 4.7. G++ Command                                                        |    |

| Figure 4.8. Kernel Version Command                                             |    |

| Figure A.1. Download CUDA Repo                                                 |    |

| Figure A.2. Install CUDA Repo                                                  |    |

| Figure A.3. Fetch Keys                                                         |    |

| Figure A.4. Update Ubuntu Packages Repositories                                |    |

| Figure A.5. CUDA Installation                                                  |    |

| Figure A.6. cuDNN Library Installation                                         |    |

| Figure A.7. Anaconda Installation                                              |    |

| Figure A.8. Accept License Terms                                               |    |

| Figure A.9. Confirm/Edit Installation Location                                 |    |

| Figure A.10. Launch/Initialize Anaconda Environment on Installation Completion |    |

| Figure A.11. Anaconda Environment Activation                                   |    |

| Figure A.12. TensorFlow Installation                                           |    |

| Figure A.13. TensorFlow Installation Confirmation                              |    |

| Figure A.14. TensorFlow Installation Completion                                |    |

| Figure A.15. Easydict Installation                                             |    |

| Figure A.16. Joblib Installation                                               |    |

| Figure A.17. Keras Installation                                                |    |

| Figure A.18. OpenCV Installation                                               |    |

| Figure A.19. Pillow Installation                                               |    |

| Figure A.20. Predictive Maintenance Dataset                                    |    |

| Figure A.21. Training Code Directory Structure                                 |    |

| Figure A.22. Training Code Flow Diagram                                        |    |

| Figure A.23. Code Snippet: Hyper Parameters                                    |    |

| Figure A.24. Code Snippet: Build Input                                         |    |

| Figure A.25. Code Snippet: Parse tfrecords                                     |    |

| Figure A.26. Code Snippet: Convert Image to Gray Scale                         |    |

| Figure A.27. Code Snippet: Convert Image to BGR and Scale the Image            |    |

| Figure A.28. Code Snippet: Create Queue                                        |    |

| Figure A.29. Code Snippet: Add Queue Runners                                   |    |

| Figure A.30. Code Snippet: Create Model                                        |    |

| - O                                                                            |    |

| Figure A.31. Code Snippet: Fire Layer                                         | 109 |

|-------------------------------------------------------------------------------|-----|

| Figure A.32. Code Snippet: Convolution Block                                  |     |

| Figure A.33. Code Snippet: Feature Depth Array for Fire Layers                | 110 |

| Figure A.34. Code Snippet: Forward Graph Fire Layers                          | 111 |

| Figure A.35. Code Snippet: Loss Function                                      | 111 |

| Figure A.36. Code Snippet: Optimizers                                         | 111 |

| Figure A.37. Code Snippet: Restore Checkpoints                                |     |

| Figure A.38. Code Snippet: Save .pbtxt                                        | 112 |

| Figure A.39. Code Snippet: Training Loop                                      | 112 |

| Figure A.40. Code Snippet: _ LearningRateSetterHook                           | 113 |

| Figure A.41. Code Snippet: Save Summary for Tensorboard                       | 113 |

| Figure A.42. Code Snippet: logging hook                                       | 113 |

| Figure A.43. Predictive Maintenance – Run Script                              | 114 |

| Figure A.44. Predictive Maintenance – Trigger Training                        | 114 |

| Figure A.45. Predictive Maintenance – Trigger Training with Transfer Learning | 114 |

| Figure A.46. Predictive Maintenance – Training Logs                           |     |

| Figure A.47. Predictive Maintenance – Confusion Matrix                        | 115 |

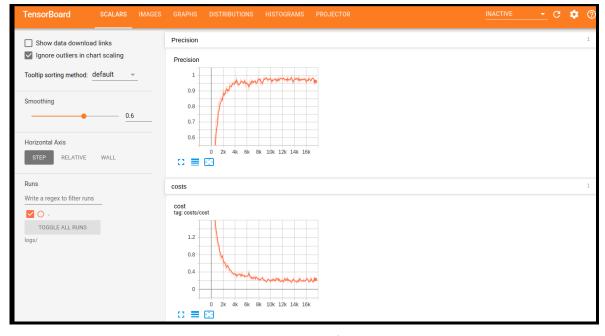

| Figure A.48. TensorBoard – Launch                                             | 115 |

| Figure A.49. TensorBoard – Link Default Output in Browser                     | 115 |

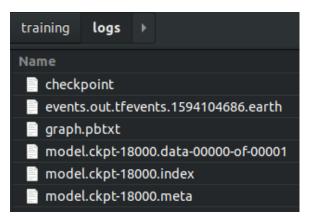

| Figure A.50. Checkpoint Storage Directory Structure                           | 116 |

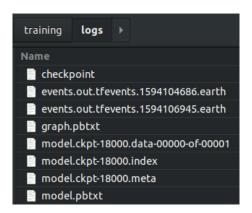

| Figure A.51. Generated '.pbtxt' for Inference                                 | 116 |

| Figure A.52. Run genpb.py To Generate Inference .pb                           | 117 |

| Figure A.53. Frozen Inference .pb Output                                      | 117 |

| Figure B.1. IPV4 Address Setting                                              | 120 |

| Figure B.2. Network Preferences Settings                                      | 120 |

| Figure B.3. IP Configuration                                                  | 121 |

|                                                                               |     |

# **Tables**

| Table 2.1. Main System Memory Map (RISC-V)                         | 17 |

|--------------------------------------------------------------------|----|

| Table 2.2. Main System Memory Map (PCIe)                           |    |

| Table 2.3. Node System Memory Map                                  | 19 |

| Table 2.4. EtherControl Interfaces                                 |    |

| Table 2.5. EtherControl Master Global Register Map (RISC-V)        | 23 |

| Table 2.6. EtherControl Master Local Chain 1 Register Map (RISC-V) | 23 |

| Table 2.7. EtherControl Master Local Chain 2 Register Map (RISC-V) | 23 |

| Table 2.8. DMA FIFO Enable/AHBL Disable Register                   |    |

| Table 2.9. PHY Link Status Register                                |    |

| Table 2.10. Active Nodes Register                                  |    |

| Table 2.11. FIFO Status Register for PDM Data                      |    |

| Table 2.12. Clear Interrupt Received Register                      |    |

| Table 2.13. Interrupt Polling Register                             |    |

| Table 2.14. Start Transaction in All Chains                        |    |

| Table 2.15. IP Busy Register                                       |    |

| Table 2.16. AHBL_TOUT_R                                            |    |

| Table 2.17. Chain 1 Start Transaction Register                     |    |

| Table 2.18. Chain 1 Packet Head Register                           |    |

| Table 2.19. Chain 1 Frame Number Register                          |    |

| Table 2.20. Chain 1 Number of Node Register                        |    |

| Table 2.21. Chain 1 Node Data Length Register                      |    |

| Table 2.22. Chain 1 Node Request Data Burst Register               |    |

| Table 2.23. Chain 1 Node Request Type Register                     |    |

| Table 2.24. Chain 1 Node Address Register                          |    |

| Table 2.25. Chain 1 CRC Count Register                             |    |

| Table 2.26. Chain 1 Interrupt Info Register                        |    |

| Table 2.27. Chain 1 FIFO Status Register Request Data              |    |

| Table 2.28. Chain 1 Node Motor Status Register                     |    |

| Table 2.29. Chain 1 Node Delay Register                            |    |

| Table 2.30. Chain 2 Start Transaction Register                     |    |

| Table 2.31. Chain 2 Packet Head Register                           |    |

| Table 2.32. Chain 2 Frame Number Register                          |    |

| Table 2.33. Chain 2 Number of Node Register                        |    |

| Table 2.34. Chain 2 Node Data Length Register                      |    |

| Table 2.35. Chain 2 Node Request Data Burst Register               |    |

| Table 2.36. Chain 2 Node Request Type Register                     |    |

| Table 2.37. Chain 2 Node Address Register                          |    |

| Table 2.38. Chain 2 CRC Count Register                             |    |

| Table 2.39. Interrupt Info Register                                |    |

| Table 2.40. Chain 2 FIFO Status Register Request Data              |    |

| Table 2.41. Chain 2 Node Motor Status Register                     |    |

| Table 2.43. EtherControl Master Global Register Map (PCIe)         |    |

| Table 2.44. EtherControl Master Global Register Map (PCIe)         |    |

| 5 , t ,                                                            |    |

| Table 2.45. EtherControl Master Local Chain 2 Register Map (PCIe)  |    |

| Table 2.46. DMA FIFO Enable/AHBL Disable Register                  |    |

| Table 2.48. Active Nodes Register                                  |    |

| Table 2.49. FIFO Status Register for PDM Data                      |    |

|                                                                    |    |

| Table 2.50. Interrupt Polling Register                             |    |

| Table 2.52. Start Transaction in All Chains                        |    |

| Table 2.32. Start Hallsaction III All Chairs                       |    |

| Table 2.53. IP Busy Register                                                          | 35 |

|---------------------------------------------------------------------------------------|----|

| Table 2.54. AHBL Bus Timeout Count Register                                           | 35 |

| Table 2.55. Node Response PDM Data Register                                           | 35 |

| Table 2.56. Chain 1 Start Transaction Register                                        | 36 |

| Table 2.57. Chain 1 Packet Head Register                                              | 36 |

| Table 2.58. Chain 1 Frame Number Register                                             | 36 |

| Table 2.59. Chain 1 Number of Node Register                                           | 36 |

| Table 2.60. Chain 1 Node Data Length Register                                         | 36 |

| Table 2.61. Chain 1 FIFO Status Register Request Data                                 | 37 |

| Table 2.62. Chain 1 Node Request Type Register                                        | 37 |

| Table 2.63. Chain 1 Node Address Register                                             | 37 |

| Table 2.64. Chain 1 CRC Count Register                                                | 37 |

| Table 2.65. Chain 1 Interrupt Info Register                                           | 37 |

| Table 2.66. Chain 1 FIFO Status Register Request Data                                 | 38 |

| Table 2.67. Chain 1 Node Request Burst Register                                       |    |

| Table 2.68. Chain 1 Node Motor Status Register                                        | 38 |

| Table 2.69. Chain 1 Node Delay Register                                               | 39 |

| Table 2.70. Chain 2 Start Transaction Register                                        | 39 |

| Table 2.71. Chain 2 Packet Head Register                                              |    |

| Table 2.72. Chain 2 Frame Number Register                                             |    |

| Table 2.73. Chain 2 Number of Node Register                                           |    |

| Table 2.74. Chain 2 Node Data Length Register                                         |    |

| Table 2.75. Chain 2 FIFO Status Register Request Data                                 |    |

| Table 2.76. Chain 2 Node Request Type Register                                        |    |

| Table 2.77. Chain 2 Node Address Register                                             |    |

| Table 2.78. Chain 2 CRC Count Register                                                |    |

| Table 2.79. Interrupt Info Register                                                   |    |

| Table 2.80. Chain 2 Node Request Burst Register                                       |    |

| Table 2.81. Chain 2 Node Motor Status Register                                        |    |

| Table 2.82. Chain 2 Node Delay Register                                               |    |

| Table 2.83. EtherControl Slave Register Map                                           |    |

| Table 2.84. DMA Control Register                                                      |    |

| Table 2.85. FIFO Data Register                                                        |    |

| Table 2.86. Motor Status Register                                                     |    |

| Table 2.87. DMA Done Indication Register                                              |    |

| Table 2.88. Interrupt Status Register                                                 |    |

| Table 2.89. Motor Config/Status Address Register (or) PDM Data Transfer Size Register |    |

| Table 2.90. Motor Configuration Data Register                                         |    |

| Table 2.91. FIFO Error Register                                                       |    |

| Table 2.92. Clear Interrupt Received Register                                         |    |

| Table 2.93. RISC-V to PCle Register Map                                               |    |

| Table 2.94. RISC-V Config Register 1                                                  |    |

| Table 2.95. RISC-V Config Register 2                                                  |    |

| Table 2.96. FIFO Error Register                                                       |    |

| Table 2.97. RISC-V Bulk Data Register                                                 |    |

| Table 2.98. PCIe Config Register 1 @ RISC-V Clock                                     |    |

| Table 2.99. PCIe Config Register 2 @ RISC-V Clock                                     |    |

| Table 2.100. PCIe Bulk Data Register @ RISC-V Clock                                   |    |

| Table 2.101. PCIe Config Register 1                                                   |    |

| Table 2.102. PCIe Config Register 2                                                   |    |

| Table 2.103. PCIe FIFO Status Register                                                |    |

| Table 2.104. PCIe Bulk Data Register                                                  |    |

| Table 2.105. RISC-V Config Register 1 @ PCIe Clock                                    |    |

| Table 2.106. RISC-V Config Register 2 @ PCIe Clock                                    |    |

|              | RISC-V Bulk Data Register @ PCIe Clock                                               |     |

|--------------|--------------------------------------------------------------------------------------|-----|

| Table 2.108. | FIFO DMA Register Map                                                                | .49 |

|              | FIFO DMA Control Registers                                                           |     |

| Table 2.110. | DEST_BASE_ADDR Register                                                              | .49 |

|              | DEST_END_ADDR Register                                                               |     |

| Table 2.112. | PING Ready Address Register                                                          | .49 |

| Table 2.113. | PONG Ready Address Register                                                          | .50 |

| Table 2.114. | PING PONG Index Register                                                             | .50 |

|              | Write Status Register                                                                |     |

|              | Read Status Register                                                                 |     |

|              | Descriptor Format                                                                    |     |

|              | Status Format                                                                        |     |

|              | Register Address (0x0)                                                               |     |

|              | Register Address (0x4)                                                               |     |

|              | Register Address (0x8)                                                               |     |

|              | Register Address (0xC)                                                               |     |

|              | Register Address (0x10)                                                              |     |

|              | Register Address (0x14)                                                              |     |

|              | Register Address (0x18)                                                              |     |

|              | Register Address (0x1C)                                                              |     |

|              | Register Address (0x20)                                                              |     |

|              | Register Address (0x24)                                                              |     |

|              | Register Address (0x28)                                                              |     |

|              | CNN Co-Processor Unit Registers                                                      |     |

|              | CNN Co-Processor unit control register                                               |     |

|              | CNN Co-Processor Unit Register                                                       |     |

|              | Sign Select Configuration Register                                                   |     |

|              | Input Offset Configuration Register                                                  |     |

|              | Filter Offset Configuration Register                                                 |     |

|              | Filter Offset Configuration Register                                                 |     |

|              | Input Depth Configuration Register                                                   |     |

|              | Input Data Address Configuration Register Filter Data Address Configuration Register |     |

|              | CNN Co-Processor Unit Output Register                                                |     |

|              | Predictive Maintenance and Motor Control Registers                                   |     |

|              | Motor Control 0 – Minimum RPM                                                        |     |

|              | Motor Control 1 – Maximum RPM                                                        |     |

|              | Motor Control 2 – RPM PI Control Loop Integrator Gain (kl)                           |     |

|              | Motor Control 3 – RPM PI Control Loop Proportional Gain (kP)                         |     |

|              | Motor Control 4 – Torque PI Control Loop Integrator Gain (kl)                        |     |

|              | Motor Control 5 – Torque PI Control Loop Proportional Gain (kP)                      |     |

|              | Motor Control 6 – Synchronization Delay and Control                                  |     |

|              | Motor Control Register 7 – Target RPM                                                |     |

|              | Motor Control Register 8 – Target Location                                           |     |

|              | Motor Control Register 9 – Current Location                                          |     |

|              | Motor Status Register 0 – RPM                                                        |     |

|              | Motor Status Register 1                                                              |     |

|              | Predictive Maintenance Control Register 0                                            |     |

|              | Predictive Maintenance Control Register 1                                            |     |

|              | Predictive Maintenance Status Register                                               |     |

|              | Predictive Maintenance Current/Voltage Data Register                                 |     |

|              | Predictive Maintenance Current/Voltage Data Register                                 |     |

|              | Versa Board Switch Status Register                                                   |     |

|              | Versa Board LED & PMOD Control Register                                              |     |

| Table 2.161. SPI Master Register Map                           | 69  |

|----------------------------------------------------------------|-----|

| Table 2.162. I <sup>2</sup> C Master IP Core Registers Summary |     |

| Table 2.163. UART Register Map                                 |     |

| Table 3.1. Main System Resource Utilization                    |     |

| Table 3.2. Node System Resource Utilization                    | 77  |

| Table 4.1. Types of UART Commands                              | 78  |

| Table 4.2. Types of GPIO Commands                              | 79  |

| Table A.1. Predictive Maintenance Training Network Topology    | 104 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                                  |

|---------|---------------------------------------------|

| AHBL    | Advanced High-performance Bus-Lite          |

| Al      | Artificial Intelligence                     |

| API     | Application Programming Interface           |

| BLDC    | Brushless DC                                |

| CCU     | CNN Co-Processor Unit                       |

| CNN     | Convolutional Neural Network                |

| CPU     | Central Processing Unit                     |

| DMA     | Direct Memory Access                        |

| FIFO    | First-In-First-Out                          |

| ISR     | Interrupt Service Routines                  |

| ML      | Machine Learning                            |

| QSPI    | Quad Serial Peripheral Interface            |

| RISC-V  | Reduced Instruction Set Computer-V          |

| RTL     | Register-Transfer Level                     |

| UART    | Universal Asynchronous Receiver-Transmitter |

# 1. Introduction

Lattice Automate stack provides a solution for industrial automation that includes predictive maintenance using ML/AI, communication over Ethernet cable and a BLDC motor control IP implemented in RTL. The solution enables user to control multiple motors connected to node systems that are chained using Ethernet cable. The main system that synchronizes operations of node system also runs neural network trained using RISC-V and CNN Co-Processor for predictive maintenance. The entire solution can work with or without external host. We provide reference design with a user interface that runs on host and controls motor operations. The user interface also displays the status of motor and alerts user when motor requires maintenance. User can use all APIs provided with this reference design and can implement entire system without host system. In this case C/C++ code running on RISC-V sends required commands to control motors. The entire system with all sub-components are shown in further sections.

Lattice Automate Stack 1.0 supports web-based user interface which is running on host (system PC) and single chain of nodes for controlling the motors.

Lattice Automate Stack 1.1 supports two chains of nodes which can be connected to 1 main system board. All the nodes are synchronized physically. Main system supports dynamic pulse based system synchronization scheme, in which it checks nodes disconnection during runtime and compensate clock ppm to calculate synchronization delay. It supports OPC UA server/client-based user interface which is running on host PC and client are running on Raspberry Pi board.

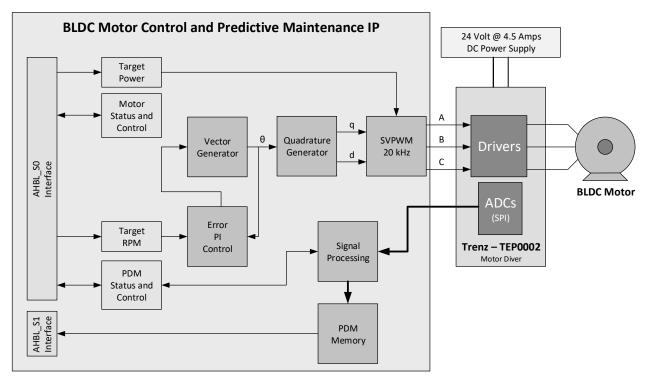

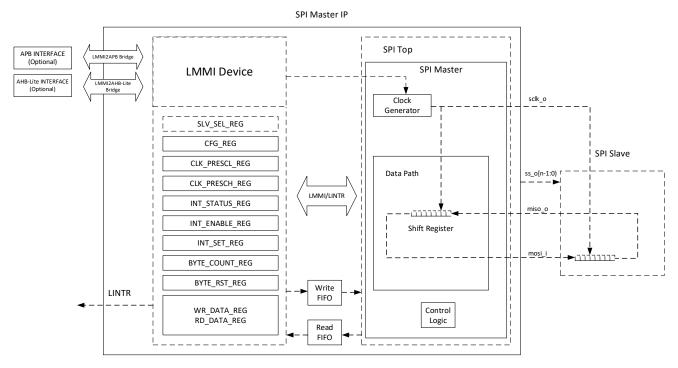

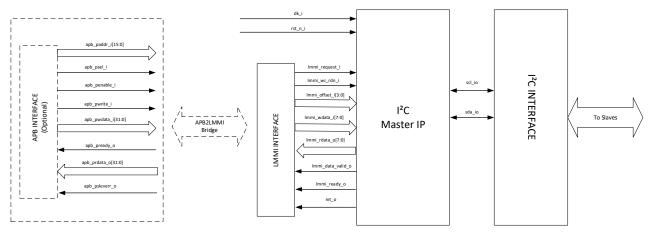

Lattice Automate Stack 2.0 supports all features of Lattice Automate Stack 1.1. It supports MQTT broker/client-based host application, Python Interface as host control, and also supports PCIe® interface as host for high speed applications. In the node side, it has motor IP for motor-based features and also has standard SPI Master, UART Interface (Modbus) and I<sup>2</sup>C Master interfaces to connect various peripherals (sensors) into system.

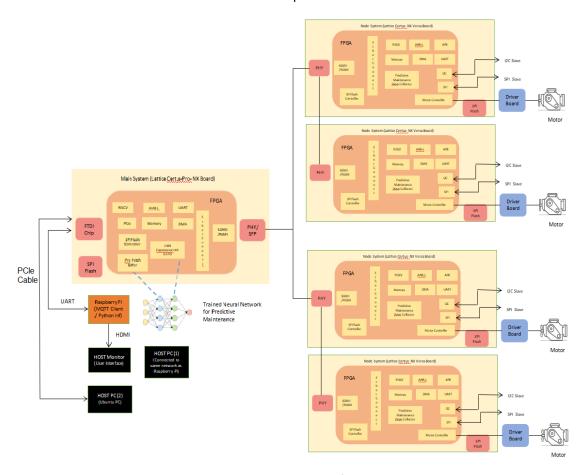

Figure 1.1 shows the Automate Stack solution and its sub components.

Figure 1.1. Top Level Block Diagram of Automate Stack 2.0

# 1.1. Components

The Automate Stack 2.0 release includes the following components:

- System on Chip (SOC)

- Main System IPs

- EtherControl IP (With SGMII/RGMII (phy or sfp)), FIFO DMA, CNN Co-Processor Unit (CCU) and SPI Flash Controller, PCIe DMA, PCIe-to-RISC-V Bridge and Reset Synchronizer.

- Node System IPs

EtherControl IP (With SGMII/RGMII (phy or sfp)), FIFO DMA, BLDC motor control IP, Data collector for predictive maintenance, UART for Modbus, I<sup>2</sup>C Master and SPI Master.

- Software

- Firmware (APIs)

- APIs to send instructions to motor control IP, collect status of motors and collect data for predictive maintenance Compiled TensorFlow-Lite C++ library for RISC-V (Required for neural network inference).

- Machine Learning

- Trained Neural Network for predictive maintenance, script to train network with user collected data.

- User Interface

Controls motor, collects status and data for predictive maintenance, displays warning when maintenance required.

Note: The generic RISC-V subsystem components are excluded from the list of components.

# Design Overview

# 2.1. Theory of Operation

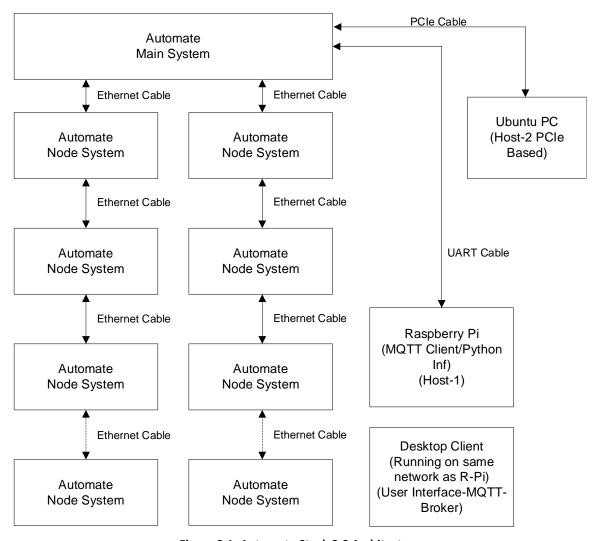

The overall architecture is shown in Figure 2.1. The automate stack consists of one Main System (MS) with multiple EtherControl master and multiple Node Systems (NS). A host R-pi board is connected to the MS through Uart port and another host is connected to MS through PCIe cable .An application software with user interface that can send commands to the MS and receive motor maintenance data from the system for AI training. The MS can propagate the commands to NS for motor control and gather maintenance data from NS.

The Certus™-NX versa board and CertusPro™-NX versa board are used for basic demo of complete system.

Figure 2.1. Automate Stack 2.0 Architecture

15

# 2.2. FPGA Design

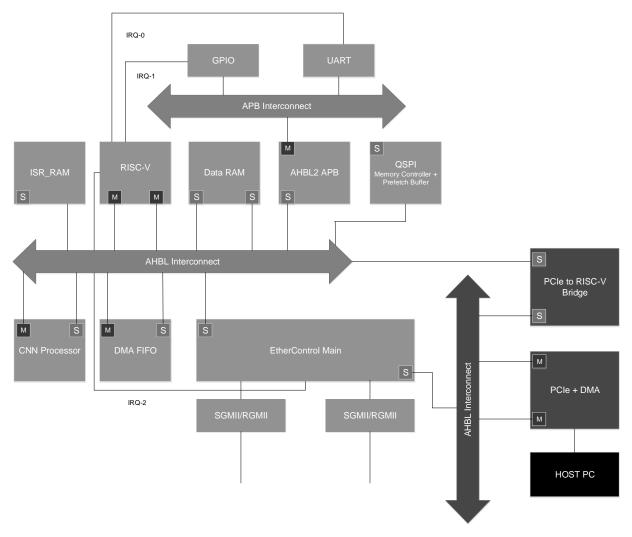

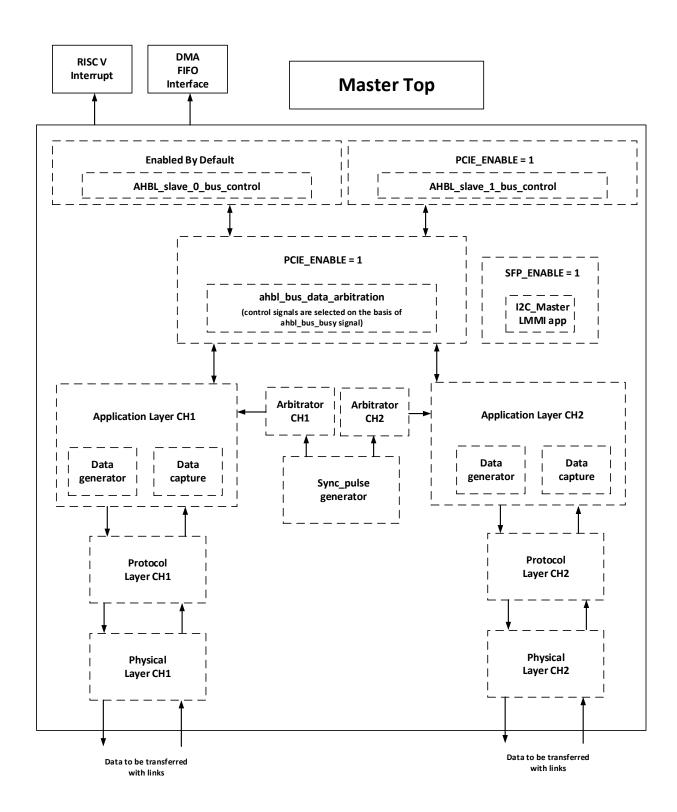

# 2.2.1. Main System

The Main System architecture is shown in Figure 2.2. The AHBL Interconnect has four masters and nineslaves:

The following are the AHBL Interconnect masters:

- RISC-V CPU Instruction Cache

- RISC-V CPU Data Cache

- CNN Co-Processor Unit

- FIFO DMA

The following are the AHBL Interconnect slaves:

- ISR RAM

- Data RAM (port S0 and S1)

- CNN Co-Processor Unit

- FIFO DMA

- EtherControl

- AHBL2APB Bridge

- PCIe-to-RISC-V Bridge

- QSPI Memory Controller with prefetch buffer (SPI Flash Controller)

The RISC-V CPU, CNN Co-Processor Unit, and FIFO DMA access data to the shared memory Data RAM, EtherControl, UART, and QSPI through the AHBL2APB bridge. The UART, SPI Flash Controller, and EtherControl generate interrupts to the RISC-V CPU.

For performance and nearly deterministic latency (DL), it uses port S0 of the Data RAM exclusively for RISC-V CPU access. The other two masters, CNN Co-Processor Unit and FIFO DMA, access port S1 of the Data RAM. This way, the contention is avoided.

EtherControl Master has two AHBL bus interfaces. One interface is used to connect EtherControl master to RISC-V based host path and another interface is used to connect EtherControl master to PCIe DMA based high speed host path.

PCIe DMA AHBL interconnect interfaces EtherControl Master, PCIe-to-RISC-V Bridge and PCIe DMA IPs. PCIe DMA IP supports PCIe-based host interface which can be connected to Linux-based PC.

Both the host path are independent of each other and both can perform same operation on nodes. But through PCIe-to-RISC-V Bridge information can be exchanged between RISC-V and PCIe DMA IP.

**Note:** Physically there is only one piece of shared memory but with two independent ports. In the memory map, S0 is assigned with a lower base address and S1 is assigned with a higher base address. In real terms, these refer to the same physical address. The two different address spaces for S0 and S1 allow the AHBL Interconnect to route the transaction to the right port.

For better performance and nearly deterministic latency, EtherControl port supports two physical interface (two master port) and it allows system to maintain two different chains of node and each chain can support up to 8 nodes.

The main firmware is stored in the external SPI flash. The ISR RAM contains the initial boot code for RISC-V as well as the interrupt service routines (ISRs) and other performance-critical functions. There are two implementation options:

- During boot, the bootloader copies the ISR code from the external flash to internal ISR RAM. It then sets up the ISR function pointer to this internal memory address.

- The ISR code is integrated in the bitstream and firm the ISR code in the ISR RAM as ROM code.

The first option can be used during initial development for debugging. The second option can be used in the final production release since it does not increase any system boot time.

The system is working at CPU frequency of 75 MHz, the protocol is working at 125 MHz and PCIe based host @ 62.5 MHz.

Figure 2.2. Main System Architecture

#### RISC-V-Based Path

The firmware binary is stored in the external QSPI flash. When RISC-V at the Main System boots up, it sets the registers at QSPI Memory Controller (SPI Flash Controller). Then RISC\_V jumps to the loaded firmware and executes the binary.

The application software at the host PC sends an interrupt through the UART port. Then RISC-V CPU fetches the commands and data from the host through UART by accessing APB port through the AHBL Interconnect, AHBL2APB bridge, and APB Interconnect.

RISC-V CPU sets the registers inside the CNN Co-Processor Unit and starts PDA operation. RISC-V CPU polls another register in the CNN Co-Processor Unit to check its operation status. RISC-V CPU requests for the new data for predictive maintenance from the slave PDM data collector by sending instruction through EtherControl IP. The data received from the slave through EtherConnect is transferred to data memory with DMA operation or sent to the host PC through UART.

For the motor control commands from the host PC, RISC-V CPU fetches them from UART and then sends them to EtherControl, which performs packetization and sends them to the downstream Node System.

The information is written/read to/from peripherals connected to Nodes through SPI Master/I<sup>2</sup>C Master/ Modbus same as information is written (config)/read to (status)/from motor control IP.

RISC-V CPU gathers predictive maintenance data from downstream Node Systems through EtherControl and sends this data to the host PC through UART. RISC-V CPU reads data from EtherControl through its AHBL Slave port, performs data processing, stores the data in the Data RAM, and then sends it to UART through APB. Alternatively, EtherControl can send downstream data to the FIFO DMA through its FIFO port, and FIFO DMA can write the data to the Data RAM or UART directly.

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

User can press buttons on the board that generate an interrupt by the GPIO block to RISC-V CPU. The interrupt service route firmware queries the interrupt status of the GPIO block and performs corresponding actions such as sending commands to start, stop, accelerate or decelerate all motors downstream.

At the end of every predictive maintenance cycle in software running on RISC-V, an update is sent to the host PC through UART.

#### PCIe DMA-Based Path

The application software running Linux PC connected to main system through the PCIe interface can check if EtherControl Path is engaged by other host(R-Pi). Linux PC can send/receive data to/from PCIe DMA module. PCIe DMA module can send data to EtherControl module to set certain register of EtherControl to send commands to nodes for motor controlling and different peripherals controlling connected to SPI/I<sup>2</sup>C/UART interfaces. PCIe DMA module can also receive data from node through the EtherControl module for training purpose. The PCIe DMA based host path is faster than RISC-V based host path.

Figure 2.2 shows that EtherControl block have two Ethernet ports (port 0 and port 1) in downstream direction. It means EtherControl master supports two master to support two split chains of nodes to improve performance.

Both chains can be synchronized and both the ethernet ports have options to select RGMII/SGMII physical interfaces. Both ports have options to select PHY or SFP IC for MII-to-RJ45 conversion.

#### 2.2.1.1. Memory Map

The Main System memory map is defined in Table 2.1 and Table 2.1.

Table 2.1. Main System Memory Map (RISC-V)

| Base Address | End Address | Range<br>(Bytes) | Range<br>(Bytes in hex) | Size (kB) | Block                                                                           |  |

|--------------|-------------|------------------|-------------------------|-----------|---------------------------------------------------------------------------------|--|

| 00190000     | 0197FFFF    | 32768            | 8000                    | 32        | CPU instruction RAM                                                             |  |

| 00080000     | 000807FF    | 2048             | 800                     | 2         | CPU PIC TIMER                                                                   |  |

| 00808000     | 00080BFF    | 1024             | 400                     | 1         | GPIO                                                                            |  |

| 00080C00     | 0009FFFF    | 128000           | 1F400                   | 125       | RESERVED                                                                        |  |

| 000A0000     | 000A03FF    | 1024             | 400                     | 1         | CNN Co-Processor Unit (CCU)                                                     |  |

| 000C0000     | 000FFFFF    | 262144           | 40000                   | 256       | CPU Data Ram Port S0: base address 0x000C0000 Port S1: base address: 0x000E0000 |  |

| 00100000     | 00107FFF    | 32768            | 8000                    | 32        | FIFO DMA                                                                        |  |

| 00108000     | 0010FFFF    | 32768            | 8000                    | 32        | EtherControl                                                                    |  |

| 00110000     | 0017FFFF    | 458752           | 70000                   | 448       | RESERVED                                                                        |  |

| 00000000     | 0007FFFF    | 512000           | 7D000                   | 512       | SPI FLASH CONTROLLER                                                            |  |

| 00182000     | 001823FF    | 1024             | 400                     | 1         | UART                                                                            |  |

| 00184000     | 00FFFFF     | 1.5E+07          | E7C000                  | 14832     | RESERVED                                                                        |  |

| 01000000     | 01FFFFFF    | 1.7E+07          | 1000000                 | 16384     | External SPI flash                                                              |  |

| 00110000     | 00117FFF    | 32768            | 8000                    | 32        | PCIe to RISC-V Bridge                                                           |  |

Table 2.2. Main System Memory Map (PCIe)

| Base Address | End Address | Range<br>(Bytes) | Range<br>(Bytes in hex) | Size (kB) | Block                 |

|--------------|-------------|------------------|-------------------------|-----------|-----------------------|

| 00108000     | 0010FFFF    | 32768            | 8000 32                 |           | EtherControl          |

| 00110000     | 00117FFF    | 32768            | 8000                    | 32        | PCIe to RISC-V Bridge |

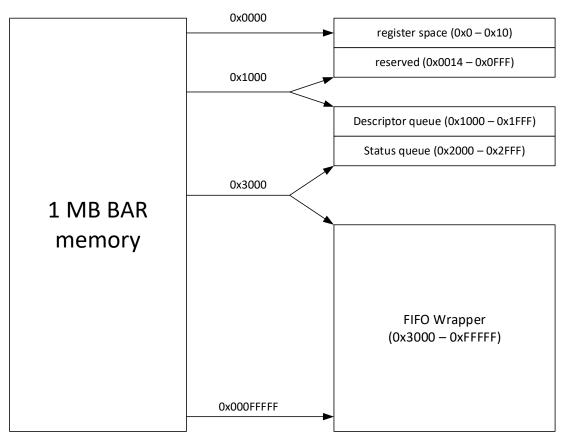

**Note**: The above address are for PCIe DMA IP (AHBL Master) to Slaves. But from host to PCIe DMA, the IP addressing is defined in further sections. Host use 0x0000 base address for PCIe register space, 0x1000 base address for descriptor memory and 0x3000 base address for application IPs (EtherControl and PCIe-to-RISC-V Bridge).

18

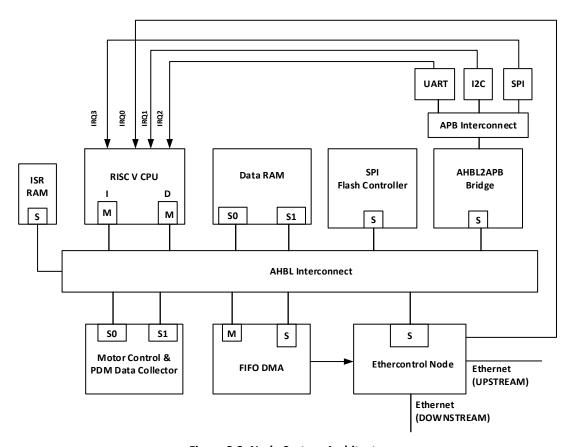

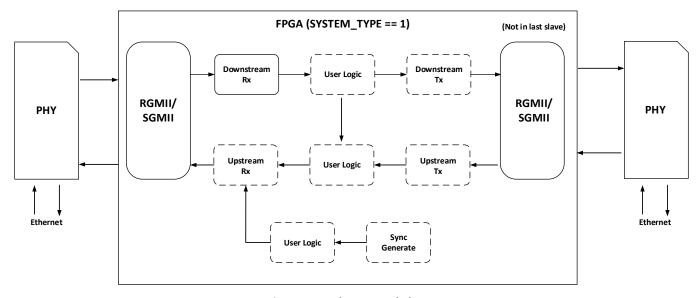

#### 2.2.2. Node System

The Node System architecture is shown in Figure 2.3. It consists of one AHBL Interconnect with three masters and eight slaves.

The following are the Node System masters:

- RISC-V CPU Instruction Cache

- RISC-V CPU Data Cache

- FIFO DMA

The following are the Node System slaves:

- ISR RAM

- Data RAM (port S0 and S1)

- Motor Control and PDM Data Collector (port S0 and S1)

- FIFO DMA

- EtherControl

- QSPI Memory Controller with prefect buffer(SPI Flash Controller)

- AHBL2APB bridge.

- SPI Master

- I<sup>2</sup>C Master

AHBL2APB bridge is connected to APB Interconnect which is having 3 APB interface based slaves SPI Master, I<sup>2</sup>C Master and UART to interface different peripherals in the system (for example, sensors).

For Data RAM with two AHBL slave ports, see the description in the previous section. For Motor Control and PDM Data Collector, it has two AHBL slave ports (S0 and S1). Port S0 is used to access the Motor Control and PDM registers while port S1 is used to access the data collected by PDM Data Collector.

The main firmware is stored in the external SPI flash. The ISR RAM contains the initial boot code for RISC-V as well as the interrupt service routines (ISRs) and other performance-critical functions. There are two implementation options:

- During boot, the bootloader copies the ISR code from the external flash to internal ISR RAM. It then sets up the ISR function pointer to this internal memory address.

- The ISR code is integrated in the bitstream and firm the ISR code in the ISR RAM as ROM code.

The first option can be used during initial development for debugging. The second option can be used in the final production release since it does not increase any system boot time.

The system is working at frequency of 75 MHz while the protocol is working at 125 MHz.

The CPU can access data from the Data RAM, access the register file inside EtherControl, and control the registers at FIFO DMA and QSPI Memory Controller. Either RISC-V CPU or FIFO DMA can move the data stored at the register file inside EtherControl to Motor Control block. They can also move the data collected by PDM Data Collector back to EtherControl and send out through the Ethernet upstream port.

There is one feature added in EtherControl IP in protocol layer. It supports additional frame/packet type 10 which enables the system to enhance performance while fetching bulk data. More details is given in the EtherControl user guide.

There is no major changes in EtherControl Slave module, but it has three more slave addition for different applications. RISC-V CPU can also send/receive data to/from different peripherals connected to system through SPI Master/I<sup>2</sup>C Master/UART (modbus).

Figure 2.3. Node System Architecture

# 2.2.2.1. Node System Memory Map of Node System

The Node System memory map is defined in Table 2.3.

Table 2.3. Node System Memory Map

| Base Address | End Address | Range (Bytes) | Range<br>(Bytes in hex) | Size (Kbytes) | Block                                                                                                      |

|--------------|-------------|---------------|-------------------------|---------------|------------------------------------------------------------------------------------------------------------|

| 00190000     | 00197FFF    | 32768         | 8000                    | 32            | CPU instruction RAM                                                                                        |

| 00080000     | 000807FF    | 2048          | 800                     | 2             | CPU PIC TIMER                                                                                              |

| 00808000     | 000BFFFF    | 260096        | 3F800                   | 254           | RESERVED                                                                                                   |

| 000C0000     | 000FFFFF    | 262144        | 40000                   | 256           | CPU Data Ram Port S0 base address: 0x000C0000 Port S1 base address: 0x000E0000                             |

| 00100000     | 00107FFF    | 32768         | 8000                    | 32            | FIFO DMA                                                                                                   |

| 00108000     | 0010FFFF    | 32768         | 8000                    | 32            | EtherControl                                                                                               |

| 00110000     | 0017FFFF    | 458752        | 70000                   | 448           | RESERVED                                                                                                   |

| 00000000     | 0007FFFF    | 512000        | 7D000                   | 512           | SPI Flash Controller                                                                                       |

| 001864000    | 001867FF    | 1024          | 400                     | 2             | UART                                                                                                       |

| 00184000     | 00185FFF    | 8192          | 2000                    | 8             | Motor Control & PDM Data Collector<br>Port S0 base address: 0x00184000<br>Port S1 base address: 0x00185000 |

| 00186000     | 00FFFFF     | 15179776      | E7A000                  | 14824         | RESERVED                                                                                                   |

| 01400000     | 01FFFFF     | 16777216      | 1000000                 | 16384         | External SPI flash                                                                                         |

| 001868000    | 00186BFF    | 1024          | 400                     | 1             | SPI Master                                                                                                 |

| 00186000     | 001863FF    | 1024          | 400                     | 1             | I <sup>2</sup> C Master                                                                                    |

20

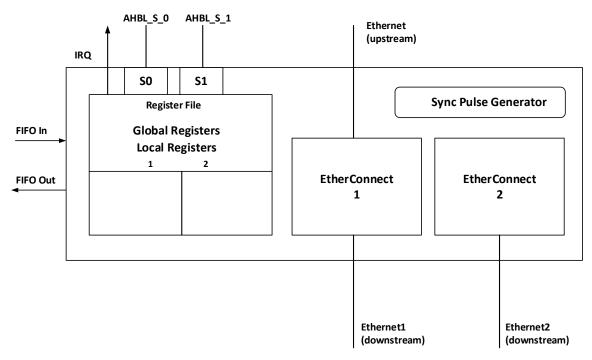

### 2.3. EtherControl IP

The EtherControl block is needed in both Main System and Node System. There is a Verilog parameter SYSTEM\_TYPE, which sets this block as either Main System or Node System. For the Main System, there is no Ethernet Upstream; only two Ethernet downstream ports. For Node System, it is has both Ethernet Upstream(1) and Ethernet Downstream(1) ports. For the last Node System, the Ethernet Downstream port can be disabled. Input/Output FIFO interface is selected using SYSTEM\_TYPE parameter.

In the main system, the EtherControl IP has an output FIFO interface to send bulk data to DMA FIFO block while in the node system, the EtherControl block has an input FIFO interface to receive bulk data from DMA FIFO module, which is coming from the Data Collector IP. The AHBL interface 0 (AHBL\_S\_0) is used to support one host along with FIFO interface for bulk data. The AHBL interface 1 (AHBL\_S\_1) is used to support another host without FIFO interface to control same operations of IP as AHBL\_S\_0. The AHBL\_S\_1 interface is used to read/write bulk data from/to IP as well.

Both AHBL interfaces are used independently from user end, but user needs to check each time if IP is engaged by another AHBL interface.

Two AHBL interfaces are available for EtherControl Master only, depending on the System Type parameter.

The Sync Pulse generator block is available in the EtherControl master only. It is used to generate pulse for dynamically synchronization of nodes.

The EtherControl consists of an existing IP block, EtherConnect, register file, and glue logic as shown in Figure 2.4.

Figure 2.4. EtherControl Block Diagram

**Table 2.4. EtherControl Interfaces**

| Interface         | Direction        | Description                                                                                                        |

|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------|

| IRQ               | Output           | Interrupt to RISC-V CPU                                                                                            |

| FIFO              | Output           | FIFO output to FIFO DMA                                                                                            |

| FIFO              | Input            | FIFO input to EtherControl                                                                                         |

| AHBL Slave 0      | Input and Output | AHBL slave port for host 1 along with FIFO output interface to control IP.                                         |

| AHBL Slave 1      | Input and Output | AHBL slave port for host 2 independent of FIFO and AHBL 0 interface to control IP.                                 |

| Ethernet Upstream | Input and Output | Send Ethernet packets to Main System or Upper Node System This interface is disabled for Main System EtherControl. |

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Interface             | Direction        | Description                                                                                                   |

|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Ethernet 1 Downstream | Input and Output | Send ethernet packets to lower Node Systems This interface is disabled for the last Node System EtherControl. |

| Ethernet 2 Downstream | Input and Output | Send ethernet packets to lower Node Systems This interface is disabled for the last Node System EtherControl. |

#### 2.3.1. Features

The key features of the EtherControl IP include:

- Real time Ethernet network support

- Two chain support

- Full Duplex data communication support

- RGMII interface support

- SGMII interface support

- AHBL Node interfaces for controlling IP from AHBL based master block

- FIFO Interface for bulk data transfer (both normal and extended mode) (only for AHBL Bus 0)

- Runtime Cable Break Detection Support

- Propagation Delay adjustment(Synchronization) Support

- Parameter based Main and Node Selection

- Maximum of 32 nodes support

- Two AHBL Bus support for EtherControl Master

- Max 256 bytes data length support

- Random Node access support EtherControl Master

- RGMII/SGMII Selection

- 1G(125 MHz) physical interface support- RGMII/SGMII PHY, SFP support

- Dynamic/Runtime node scanning

- 4 kB Rx and Tx data buffers support

- Configuration Write(Motor Configuration), Status Read(Motor Status), Bulk data read(PDM data) Normal and Extended

- Interrupt support (only for AHBL Bus 0)

#### 2.3.2. EtherControl Master

Figure 2.5. EtherControl Master Block Diagram

23

# 2.3.3. Register Description

#### 2.3.3.1. EtherControl Master (RISC-V)

The register address map for AHBL Bus 0 (RISC-V) shown in Table 2.5 specifies the available IP Core registers for the main system configuration. The offset of each register increments by four to allow easy interfacing with the processor and System Buses. In this case, each register is 32-bit wide wherein the used and unused bits are mentioned. The unused bits are treated as reserved – read access returns 0. The registers are divided into Global and Local ones. The global registers are common for all the chains, while the local ones are local to the respective chains.

Table 2.5. EtherControl Master Global Register Map (RISC-V)

| EtherControl Register Name | Register Function                     | Base Address (0x00108000) | Access     |

|----------------------------|---------------------------------------|---------------------------|------------|

| DMACTR_R                   | DMA FIFO Enable/AHBL Disable Register | Base + 0x00               | Read/Write |

| PHLNK_R                    | PHY Link Status Register              | Base + 0x04               | Read       |

| NDACT_R                    | Active Nodes Register                 | Base + 0x08               | Read       |

| FSRPDM_R                   | FIFO Status Register for PDM Data CDC | Base + 0x0C               | Read       |

| ETHINTR_R                  | Interrupt Poll Register               | Base + 0x10               | Read       |

| CLRCVD_R                   | Clear Interrupt Received Register     | Base + 0x14               | Read/Write |

| TX_ALL_STRT_R              | Transaction start for all chains      | Base + 0x18               | Read/Write |

| DTOUT_R                    | Node Response PDM Data Register       | Base + 0x1C               | Read       |

| IP_STATUS_R                | IP Busy Status                        | Base + 0x20               | Read/Write |

| AHBL_TOUT_R                | AHBL Bus Timeout Count Register       | Base + 0x28               | Write      |

Table 2.6. EtherControl Master Local Chain 1 Register Map (RISC-V)

| EtherControl Register Name | Register Function                 | Base Address (0x0010800) | Access     |

|----------------------------|-----------------------------------|--------------------------|------------|

| TXSTR_R_1                  | Start Transaction Register        | Base + 0x00              | Read/Write |

| PKTHD_R_1                  | Packet Head Register              | Base + 0x04              | Read/Write |

| FRNUM_R_1                  | Frame Number Register             | Base + 0x08              | Read/Write |

| NDCNT_R_1                  | Number of Node Register           | Base + 0x0C              | Read/Write |

| NDLN_R_1                   | Node Data Length Register         | Base + 0x10              | Read/Write |

| MTDT_R_1                   | Node Request Data Burst Register  | Base + 0x14              | Read/Write |

| RQDT_R_1                   | Node Request Type Register        | Base + 0x18              | Read/Write |

| RQAD_R_1                   | Node Address Register             | Base + 0x1C              | Read/Write |

| CRCNT_R_1                  | CRC Count Register                | Base + 0x20              | Read       |

| INTR_R_1                   | Interrupt Info Register           | Base + 0x24              | Read       |

| FSRREQD_R_1                | FIFO Status Register Request Data | Base + 0x28              | Read       |

| MTRST_R_1                  | Node Motor Status Register        | Base + 0x100 to 0x1FC    | Read       |

| DLY_R_1                    | Node Delay Register               | Base + 0x200 to 0x2FC    | Read       |

Table 2.7. EtherControl Master Local Chain 2 Register Map (RISC-V)

| EtherControl Register Name | Register Function                | Base Address (0x00108400) | Access     |

|----------------------------|----------------------------------|---------------------------|------------|

| TXSTR_R_2                  | Start Transaction Register       | Base + 0x00               | Read/Write |

| PKTHD_R_2                  | Packet Head Register             | Base + 0x04               | Read/Write |

| FRNUM_R_2                  | Frame Number Register            | Base + 0x08               | Read/Write |

| NDCNT_R_2                  | Number of Node Register          | Base + 0x0C               | Read/Write |

| NDLN_R_2                   | Node Data Length Register        | Base + 0x10               | Read/Write |

| MTDT_R_2                   | Node Request Data Burst Register | Base + 0x14               | Read/Write |

| RQDT_R_2                   | Node Request Type Register       | Base + 0x18               | Read/Write |

| RQAD_R_2                   | Node Address Register            | Base + 0x1C               | Read/Write |

| CRCNT_R_2                  | CRC Count Register               | Base + 0x20               | Read       |

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-RD-02255-1.0

| EtherControl Register Name | Register Function                 | Base Address (0x00108400) | Access |

|----------------------------|-----------------------------------|---------------------------|--------|

| INTR_R_2                   | Interrupt Info Register           | Base + 0x24               | Read   |

| FSRREQD_R_2                | FIFO Status Register Request Data | Base + 0x28               | Read   |

| MTRST_R_2                  | Node Motor Status Register        | Base + 0x100 to 0x1FC     | Read   |

| DLY_R_2                    | Node Delay Register               | Base + 0x200 to 0x2FC     | Read   |

The Global register description is given below:

Table 2.8. DMA FIFO Enable/AHBL Disable Register

| DMACTR_R |          |          |          | Base + 0x00 |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | DMACTR_R |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   |          |          | R/W      |             |

DMACTR\_R[0]: 0: DMA FIFO enabled, AHBL disabled | 1: DMA FIFO disabled, AHBL enabled

Table 2.9. PHY Link Status Register

| PHLNK_R |             |                       |   | Base + 0x04 |

|---------|-------------|-----------------------|---|-------------|

| Byte    | 3           | 2                     | 1 | 0           |

| Name    | Physical Li | Physical Link Chain 2 |   | cal Chain 1 |

| Default | 0           | 0                     | 0 | 0           |

| Access  |             |                       | R |             |

PHLNK\_R[0]: 1: Main System PHY link established for chain 1 and 0: Main System PHY link not established for chain 1

PHLNK\_R[15:1]: Each bit from bit 1 to bit 15 shows the link status of the respective nodes in chain 1

PHLNK\_R[16]: 1: Main System PHY link established for chain 2 and 0: Main System PHY link not established for chain 2

PHLNK\_R[31:17]: Each bit from bit 17 to bit 31 shows the link status of the respective nodes in chain 2

#### Table 2.10. Active Nodes Register

| NDACT_R |                       |                       |                     | Base + 0x08         |

|---------|-----------------------|-----------------------|---------------------|---------------------|

| Byte    | 3                     | 2                     | 1                   | 0                   |

| Name    | Active Node Chain 1+2 | Active Node Chain 1+2 | Active Node Chain 2 | Active Node Chain 1 |

| Default | 0                     | 0                     | 0                   | 0                   |

| Access  |                       |                       | R                   |                     |

NDACT R[7:0]: Gives number of nodes actually connected physically to the system

NDACT\_R[15:8]: Gives number of nodes actually connected physically to the system in chain 2

NDACT\_R[31:16]: Gives total number of physically connected nodes in both chains

Table 2.11. FIFO Status Register for PDM Data

| FSRPDM_R |          |          |          | Base + 0x0C |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | FSRPDM_R |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   |          |          | R        |             |

FSRPDM\_R[0]: Empty signal of RX FIFO

FSRPDM\_R[1]: Full signal of RX FIFO

FSRPDM R[2]: Overflow error of RX FIFO

FSRPDM\_R[3]: Underflow error of RX FIFO

FSRPDM\_R[4]: Reserved FSRPDM\_R[5]: Reserved FSRPDM\_R[6]: Reserved

FSRPDM\_R[7]: Reserved

Table 2.12. Clear Interrupt Received Register

| CLRCVD_R |          |          |          | Base + 0x10 |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | CLRCVD_R |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   |          |          | R/W      |             |

CLRCVD\_R[0]: Received clr bit from CPU

CLRCVD\_R[7:1] : Reserved CLRCVD\_R[31:8] : Reserved

Table 2.13. Interrupt Polling Register

| ETHINTR_R |                                 |   |                | Base + 0x14       |

|-----------|---------------------------------|---|----------------|-------------------|

| Byte      | 3                               | 2 | 1              | 0                 |

| Name      | Ethernet Interrupt from Chain 2 |   | Ethernet Inter | rupt from Chain 1 |

| Default   | Reserved                        | 0 | Reserved       | 0                 |

| Access    |                                 |   | R/W            |                   |

ETHINTR\_R[0]: Interrupt bit from Chain 1

ETHINTR\_R[7:1]: Reserved ETHINTR\_R[15:8]: Reserved

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

ETHINTR\_R[16]: Interrupt bit from Chain 2

ETHINTR\_R[31:17]: Reserved

**Table 2.14. Start Transaction in All Chains**

| TX_ALL_STRT_R |               |          |          | Base + 0x18 |

|---------------|---------------|----------|----------|-------------|

| Byte          | 3             | 2        | 1        | 0           |

| Name          | TX_ALL_STRT_R |          |          |             |

| Default       | Reserved      | Reserved | Reserved | 0           |

| Access        |               |          | R/W      |             |

TX\_ALL\_START\_R[0]: Received clr bit from CPU

TX\_ALL\_START\_R[7:1]: Reserved

Table 2.15. IP Busy Register

| IP_BUSY_R |             |          |          | Base + 0x20 |

|-----------|-------------|----------|----------|-------------|

| Byte      | 3           | 2        | 1        | 0           |

| Name      | AHBL_Busy_R |          |          |             |

| Default   | Reserved    | Reserved | Reserved | 0           |

| Access    |             |          | R/W      |             |

AHBL\_BUSY\_R[0]: 1: AHBL Bus 0 Busy | 0: AHBL 0 bus Free (Only for reading)

AHBL\_BUSY\_R[1]: 1: AHBL Bus 1 Busy | 0: AHBL 1 bus Free

AHBL\_BUSY\_R[7:2]: Reserved

Table 2.16. AHBL\_TOUT\_R

| IP_BUSY_R |             |   |   | Base + 0x28 |

|-----------|-------------|---|---|-------------|

| Byte      | 3           | 2 | 1 | 0           |

| Name      | AHBL_TOUT_R |   |   |             |

| Default   | 0           | 0 | 0 | 0           |

| Access    |             |   | W |             |

AHBL\_TOUT\_R[31:0]: Sets the value of AHBL timeout count to free the bus

The local register 1 description is given below:

Table 2.17. Chain 1 Start Transaction Register

| TXSTR_R_1 |           |          |          | Base + 0x00 |

|-----------|-----------|----------|----------|-------------|

| Byte      | 3         | 2        | 1        | 0           |

| Name      | TXSTR_R_1 |          |          |             |

| Default   | Reserved  | Reserved | Reserved | 0           |

| Access    | R/W       |          |          |             |

TXSTR\_R\_1[0]: 1: Start the transaction | 0: No transaction

Table 2.18. Chain 1 Packet Head Register

| PKTHD_R_1 |           |          |          | Base + 0x04 |

|-----------|-----------|----------|----------|-------------|

| Byte      | 3         | 2        | 1        | 0           |

| Name      | PKTHD_R_1 |          |          |             |

| Default   | Reserved  | Reserved | Reserved | 0           |

| Access    | R/W       |          |          |             |

© 2022 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### PKTHD\_R\_1[0]: 1: User values are updated | 0: No update

Table 2.19. Chain 1 Frame Number Register

| FRNUM_R_1 |           |          |          | Base + 0x08 |

|-----------|-----------|----------|----------|-------------|

| Byte      | 3         | 2        | 1        | 0           |

| Name      | FRNUM_R_1 |          |          |             |

| Default   | Reserved  | Reserved | Reserved | 0           |

| Access    |           |          | R/W      |             |

### FRNUM\_R\_1[7:0]: Frame number for the current frame

Table 2.20. Chain 1 Number of Node Register

| NDCNT_R_1 |           |          |          | Base + 0x0C |

|-----------|-----------|----------|----------|-------------|

| Byte      | 3         | 2        | 1        | 0           |

| Name      | NDCNT_R_1 |          |          |             |

| Default   | Reserved  | Reserved | Reserved | 0           |

| Access    | R/W       |          |          |             |

# NDCNT\_R\_1[7:0]: Number of nodes configured by the user

Table 2.21. Chain 1 Node Data Length Register

| NDLN_R_1 |          |          |          | Base + 0x10 |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | NDLN_R_1 |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   | R/W      |          |          |             |

#### NDLN\_R\_1[7:0]: Data length of nodes to be configured by the user

Table 2.22. Chain 1 Node Request Data Burst Register

| MTDT_R_1 |          |          |          | Base + 0x14 |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | MTDT_R_1 |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   |          |          | R/W      |             |

### MTDT\_R\_1[7:0]: Data to be send from the Main System to Node Systems by the user

Table 2.23. Chain 1 Node Request Type Register

| RQDT_R_1 |          |          |          | Base + 0x18 |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | RQDT_R_1 |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   |          |          | R/W      |             |

# RQDT\_R\_1[7:0]: Type of data requested by the user

### Table 2.24. Chain 1 Node Address Register

| RQAD_R_1 |          |          |          | Base + 0x1C |

|----------|----------|----------|----------|-------------|

| Byte     | 3        | 2        | 1        | 0           |

| Name     | RQAD_R_1 |          |          |             |

| Default  | Reserved | Reserved | Reserved | 0           |

| Access   | R/W      |          |          |             |

#### RQAD\_R\_1[7:0]: Address requested by the user

#### Table 2.25. Chain 1 CRC Count Register

| CRCNT_R_1 |           |          |          | Base + 0x20 |

|-----------|-----------|----------|----------|-------------|

| Byte      | 3         | 2        | 1        | 0           |

| Name      | CRCNT_R_1 |          |          |             |

| Default   | Reserved  | Reserved | Reserved | 0           |

| Access    | R         |          |          |             |

#### CRCNT\_R\_1[7:0]: Gives the count of error generated by doing CRC on the data

#### Table 2.26. Chain 1 Interrupt Info Register

| INTR_R_1 |          |          |          | Base + 0x24 |

|----------|----------|----------|----------|-------------|