# **CertusPro-NX Family**

# **Data Sheet**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Contents                                                    | 3  |

|-------------------------------------------------------------|----|

| Acronyms in This Document                                   | 12 |

| L. Description                                              | 14 |

| 1.1. Features                                               | 15 |

| 2. Architecture                                             | 18 |

| 2.1. Overview                                               | 18 |

| 2.2. PFU Blocks                                             | 21 |

| 2.2.1. Slice                                                | 21 |

| 2.2.2. Modes of Operation                                   | 24 |

| 2.3. Routing                                                | 25 |

| 2.4. Clocking Structure                                     | 25 |

| 2.4.1. Global PLL                                           | 25 |

| 2.4.2. Clock Distribution Network                           | 26 |

| 2.4.3. Primary Clocks                                       |    |

| 2.4.4. Edge Clock                                           | 28 |

| 2.4.5. Clock Dividers                                       | 28 |

| 2.4.6. Clock Center Multiplexer Blocks                      |    |

| 2.4.7. Dynamic Clock Select                                 |    |

| 2.4.8. Dynamic Clock Control                                | 30 |

| 2.4.9. DDRDLL                                               |    |

| 2.5. SGMII TX/RX                                            |    |

| 2.6. sysMEM Memory                                          |    |

| 2.6.1. sysMEM Memory Block                                  |    |

| 2.6.2. Bus Size Matching                                    |    |

| 2.6.3. RAM Initialization and ROM Operation                 |    |

| 2.6.4. Memory Cascading                                     |    |

| 2.6.5. Single, Dual, and Pseudo-Dual Port Modes             |    |

| 2.6.6. Memory Output Reset                                  |    |

| 2.7. Large RAM                                              |    |

| 2.8. sysDSP                                                 |    |

| 2.8.1. sysDSP Approach Compared to General DSP              |    |

| 2.8.2. sysDSP Architecture Features                         |    |

| 2.9. Programmable I/O (PIO)                                 |    |

| 2.10. Programmable I/O Cell (PIC)                           |    |

| 2.10.1. Input Register Block                                |    |

| 2.10.2. Output Register Block                               |    |

| 2.11. Tri-state Register Block                              |    |

| 2.12. DDR Memory Support                                    |    |

| 2.12.1. DQS Grouping for DDR Memory                         |    |

| 2.12.2. DLL Calibrated DQS Delay and Control Block (DQSBUF) |    |

| 2.13.1. Supported sysI/O Standards                          |    |

|                                                             |    |

| 2.13.2. sysI/O Banking Scheme                               |    |

| • •                                                         |    |

| 2.13.4. MIPI D-PHY Support                                  |    |

|                                                             |    |

| 2.14.1. Analog to Digital Converters                        |    |

| 2.14.3. Internal Junction Temperature Monitoring Diode      |    |

| 2.15. IEEE 1149.1-Compliant Boundary Scan Testability       |    |

| 2.16. Device Configuration                                  |    |

| 2.16.1. Enhanced Configuration Options                      |    |

| 2.10.1. Lilliancea Configuration Options                    |    |

| 2.17.          | Single Event Upset (SEU) Handling                             |    |

|----------------|---------------------------------------------------------------|----|

| 2.18.          | On-chip Oscillator                                            | 52 |

| 2.19.          | User I <sup>2</sup> C IP                                      | 52 |

| 2.20.          | Pin Migration                                                 |    |

| 2.21.          | SERDES and Physical Coding Sublayer                           |    |

|                | 1.1. SERDES Block                                             |    |

|                | 1.2. MPCS                                                     |    |

|                | 1.3. Peripheral Component Interconnect Express (PCIe)         |    |

|                | 1.4. LMMI (Lattice Memory Map Interface) Bus                  |    |

| 2.22.          | Cryptographic Engine                                          |    |

| 2.23.          |                                                               |    |

|                | and Switching Characteristics for Commercial and Industrial   |    |

| 3.1.           | Absolute Maximum Ratings                                      |    |

| 3.2.           | Recommended Operating Conditions                              |    |

| 3.3.<br>3.4.   | Power up Sequence                                             |    |

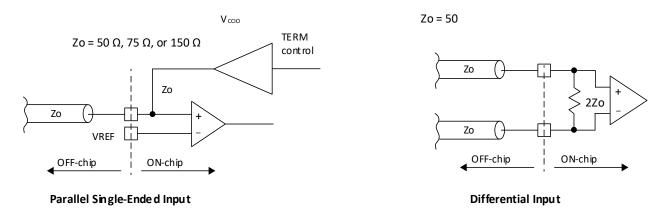

| 3.4.<br>3.5.   | On-chip Programmable Termination                              |    |

| 3.6.           | Hot Socketing Specifications                                  |    |

| 3.7.           | ESD Performance                                               |    |

| 3.7.<br>3.8.   | DC Electrical Characteristics                                 |    |

| 3.9.           | Supply Currents                                               |    |

| 3.10.          | sysI/O Recommended Operating Conditions                       |    |

| 3.11.          | sysI/O Single-Ended DC Electrical Characteristics             |    |

| 3.12.          | sysI/O Differential DC Electrical Characteristics             |    |

|                | 2.1. LVDS                                                     |    |

| _              | 2.2. LVDS25E (Output Only)                                    |    |

| 3.1            | 2.3. SubLVDS (Input Only)                                     |    |

| 3.1            | 2.4. SubLVDSE/SubLVDSEH (Output Only)                         |    |

| 3.1            | 2.5. SLVS                                                     | 71 |

| 3.1            | 2.6. Soft MIPI D-PHY                                          | 72 |

| 3.1            | 2.7. Differential HSTL15D (As Output)                         | 75 |

| 3.1            | 2.8. Differential SSTL135D, SSTL15D (As Output)               | 75 |

| 3.1            | 2.9. Differential HSUL12D (As Output)                         | 75 |

| 3.1            | 2.10. Differential LVSTLD (As Output)                         | 75 |

| 3.1            | 2.11. Differential LVCMOS25D, LVCMOS33D, LVTTL33D (As Output) |    |

| 3.13.          | Maximum sysI/O Buffer Speed                                   |    |

| 3.14.          | Typical Building Block Function Performance                   |    |

| 3.15.          | Derating Timing Tables                                        |    |

| 3.16.          | External Switching Characteristics                            |    |

| 3.17.          | sysCLOCK PLL Timing (V <sub>CC</sub> = 1.0 V)                 |    |

| 3.18.          | Internal Oscillators Characteristics                          |    |

| 3.19.          | User I2C Characteristics                                      |    |

| 3.20.          | Analog-Digital Converter (ADC) Block Characteristics          |    |

| 3.21.          | Comparator Block Characteristics                              |    |

| 3.22.          | Digital Temperature Readout Characteristics                   |    |

| 3.23.          | SERDES High-Speed Data Transmitter                            |    |

| 3.24.          | SERDES High-Speed Data Receiver                               |    |

| 3.25.<br>3.26. | Input Data Jitter Tolerance                                   |    |

| 3.26.<br>3.27. | PCI Express Electrical and Timing Characteristics             |    |

|                | 7.1. PCIe (2.5 Gbps)                                          |    |

|                | 7.2. PCIe (5 Gbps)                                            |    |

|                | 7.3. PCIe (8 Gbps)                                            |    |

| 3.28.          | SGMII Characteristics                                         |    |

| 5.20.          |                                                               |    |

| 3.2    | 8.1.   | SGMII Specifications                                    |     |

|--------|--------|---------------------------------------------------------|-----|

| 3.29.  | sys(   | CONFIG Port Timing Specifications                       | 101 |

| 3.30.  | JTA    | G Port Timing Specifications                            | 108 |

| 3.31.  | Swi    | tching Test Conditions                                  | 109 |

| 4. DC  |        | witching Characteristics for Automotive                 |     |

| 4.1.   |        | olute Maximum Ratings                                   |     |

| 4.2.   |        | ommended Operating Conditions                           |     |

| 4.3.   |        | ver Supply Ramp Rates                                   |     |

| 4.4.   | Pov    | ver up Sequence                                         | 112 |

| 4.5.   |        | chip Programmable Termination                           |     |

| 4.6.   |        | Socketing Specifications                                |     |

| 4.7.   |        | Performance                                             |     |

| 4.8.   |        | Electrical Characteristics                              |     |

| 4.9.   |        | ply Currents                                            |     |

| 4.10.  | sysl   | /O Recommended Operating Conditions                     | 115 |

| 4.11.  | -      | /O Single-Ended DC Electrical Characteristics           |     |

| 4.12.  | sysl   | /O Differential DC Electrical Characteristics           |     |

| 4.1    | 2.1.   | LVDS                                                    |     |

|        | 2.2.   | LVDS25E (Output Only)                                   |     |

| 4.1    | 2.3.   | SubLVDS (Input Only)                                    |     |

| 4.1    | 2.4.   | SubLVDSE/SubLVDSEH (Output Only)                        | 120 |

| 4.1    | 2.5.   | SLVS                                                    | 121 |

| 4.1    | 2.6.   | Soft MIPI D-PHY                                         |     |

| 4.1    | 2.7.   | Differential HSTL15D (As Output)                        |     |

| 4.1    | 2.8.   | Differential SSTL135D, SSTL15D (As Output)              |     |

| 4.1    | 2.9.   | Differential HSUL12D (As Output)                        |     |

| 4.1    | 2.10.  | Differential LVSTLD (As Output)                         |     |

| 4.1    | 2.11.  | Differential LVCMOS25D, LVCMOS33D, LVTTL33D (As Output) |     |

| 4.13.  |        | ximum sysI/O Buffer Speed                               |     |

| 4.14.  |        | ical Building Block Function Performance                |     |

| 4.15.  |        | ating Timing Tables                                     |     |

| 4.16.  |        | ernal Switching Characteristics                         |     |

| 4.17.  | •      | CLOCK PLL Timing (V <sub>CC</sub> = 1.0 V)              |     |

| 4.18.  |        | rnal Oscillators Characteristics                        |     |

| 4.19.  |        | r I2C Characteristics                                   |     |

| 4.20.  |        | llog-Digital Converter (ADC) Block Characteristics      |     |

| 4.21.  |        | nparator Block Characteristics                          |     |

| 4.22.  | _      | tal Temperature Readout Characteristics                 |     |

| 4.23.  |        | DES High-Speed Data Transmitter                         |     |

| 4.24.  |        | DES High-Speed Data Receiver                            |     |

| 4.25.  | •      | ut Data Jitter Tolerance                                |     |

| 4.26.  |        | DES External Reference Clock                            |     |

| 4.27.  |        | Express Electrical and Timing Characteristics           |     |

|        | 7.1.   | PCIe (2.5 Gbps)                                         |     |

|        | 7.2.   | PCIe (5 Gbps)                                           |     |

| 4.28.  |        | All Characteristics                                     |     |

| 4.2    | _      | SGMII Specifications                                    |     |

| 4.29.  | •      | CONFIG Port Timing Specifications                       |     |

| 4.30.  |        | G Port Timing Specifications                            |     |

| 4.31.  |        | tching Test Conditions                                  |     |

|        |        | formation                                               |     |

| 5.1.   | _      | nal Descriptions                                        |     |

| 5.2.   |        | Information Summary                                     |     |

| 6. Ord | lering | Information                                             | 168 |

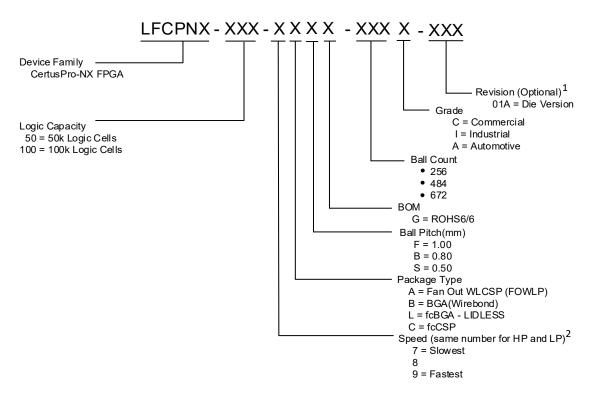

| 6.1.      | Part Number Description           | 168 |

|-----------|-----------------------------------|-----|

| 6.2.      | Ordering Part Numbers             | 169 |

|           | . Commercial                      |     |

| 6.2.2     | Commercial ("01A" Die Version)    | 170 |

| 6.2.3     | B. Industrial                     | 170 |

| 6.2.4     | l. Industrial ("01A" Die Version) | 171 |

| 6.2.5     | 5. Automotive                     | 171 |

| Reference | 25                                | 172 |

| Technical | Support Assistance                | 173 |

|           | History                           |     |

|           |                                   |     |

# **Figures**

| Figure 2.1. Simplified Block Diagram, LFCPNX-50 Device (Top Level)           | 19  |

|------------------------------------------------------------------------------|-----|

| Figure 2.2. Simplified Block Diagram, LFCPNX-100 Device (Top Level)          | 20  |

| Figure 2.3. PFU Diagram                                                      |     |

| Figure 2.4. Slice Diagram                                                    | 22  |

| Figure 2.5. Slice Configuration for LUT4 and LUT5                            | 23  |

| Figure 2.6. General Purpose PLL Diagram                                      | 26  |

| Figure 2.7. Clocking Network                                                 | 27  |

| Figure 2.8. Edge Clock Sources per Bank                                      | 28  |

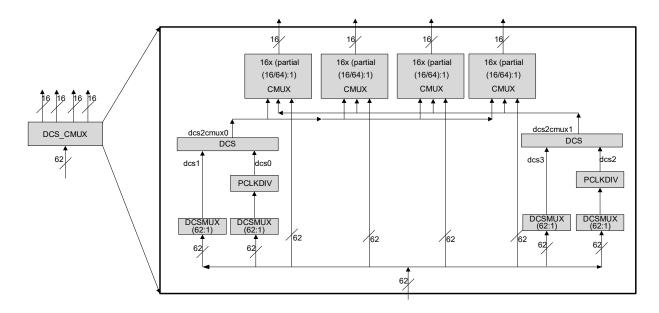

| Figure 2.9. DCS_CMUX Block Diagram                                           | 29  |

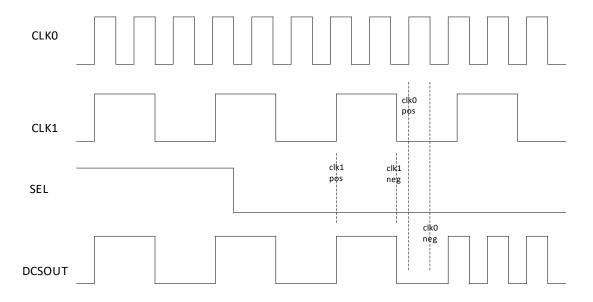

| Figure 2.10. DCS Waveforms                                                   | 30  |

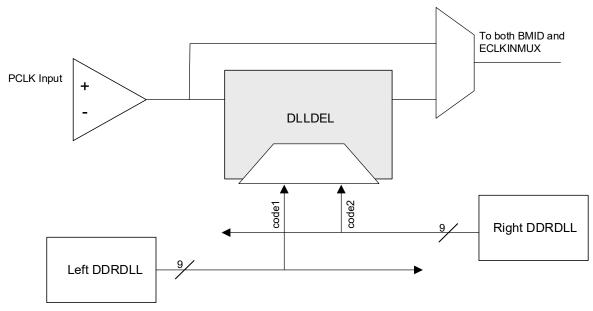

| Figure 2.11. DLLDEL Function Diagram                                         | 31  |

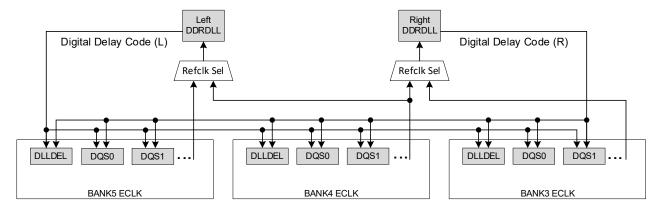

| Figure 2.12. CertusPro-NX DDRDLL Architecture                                | 31  |

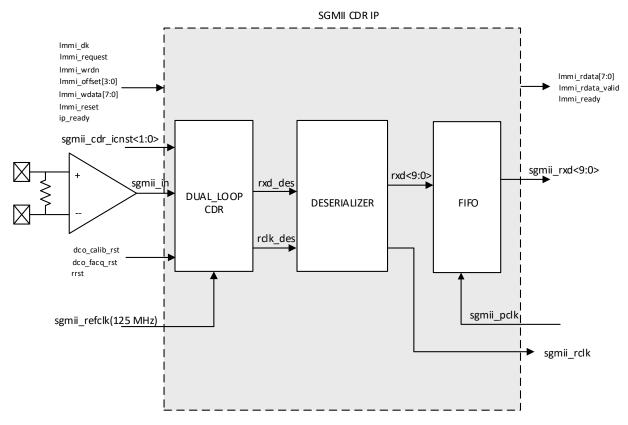

| Figure 2.13. SGMII CDR IP                                                    | 32  |

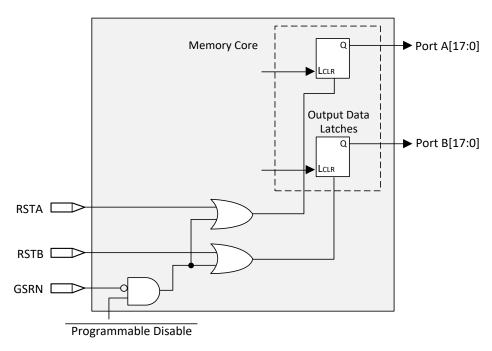

| Figure 2.14. Memory Core Reset                                               | 34  |

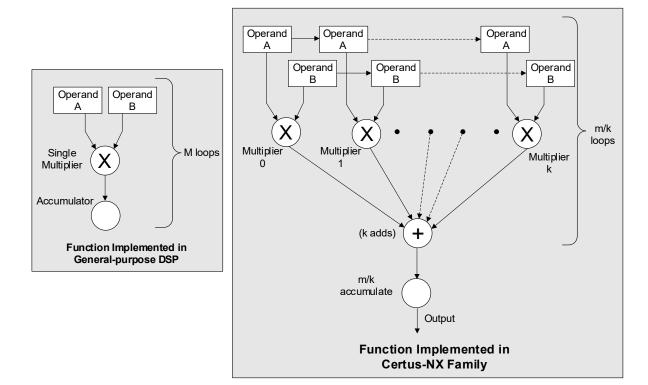

| Figure 2.15. Comparison of General DSP and CertusPro-NX Approaches           | 35  |

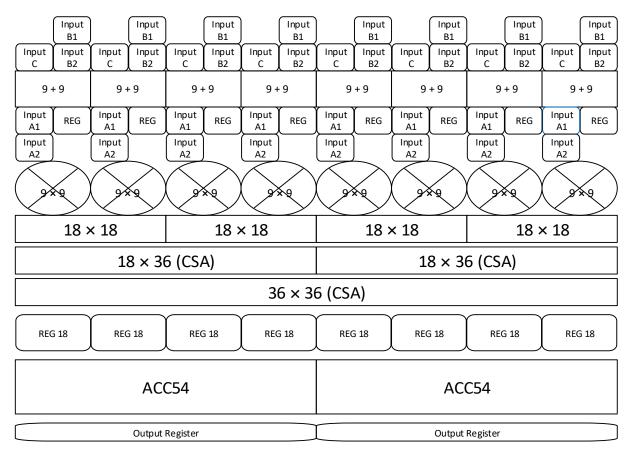

| Figure 2.16. CertusPro-NX DSP Functional Block Diagram                       | 37  |

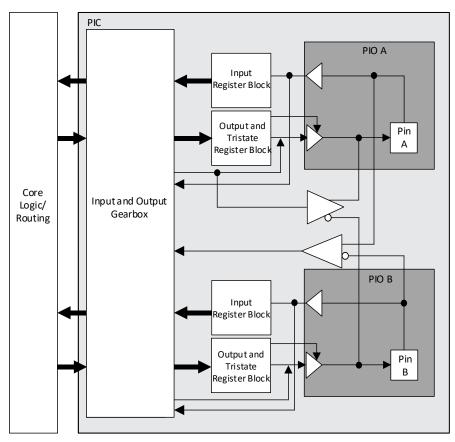

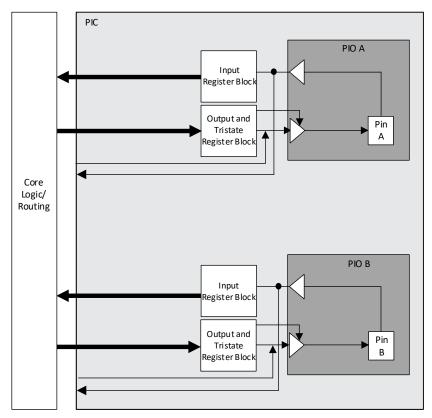

| Figure 2.17. A Group of Two High Performance Programmable I/O Cells          | 38  |

| Figure 2.18. Wide Range Programmable I/O Cells                               | 39  |

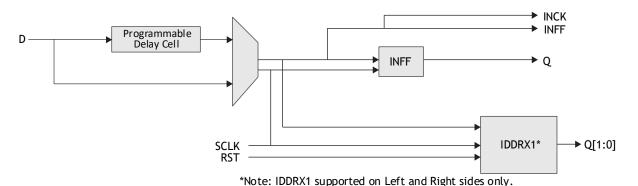

| Figure 2.19. Input Register Block for PIO on Top, Left, and Right Sides      | 40  |

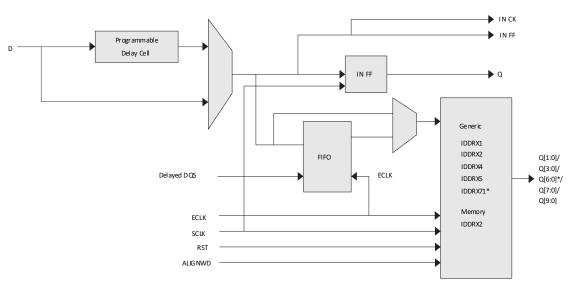

| Figure 2.20. Input Register Block for PIO on Bottom Side                     | 40  |

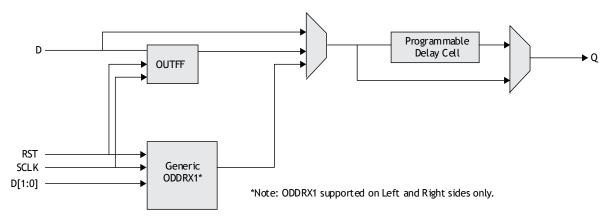

| Figure 2.21. Output Register Block on Top, Left, and Right Sides             | 41  |

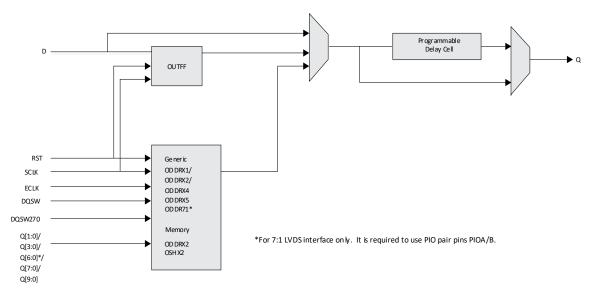

| Figure 2.22. Output Register Block on Bottom Side                            | 41  |

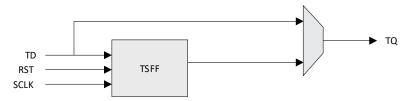

| Figure 2.23. Tri-state Register Block on Top, Left, and Right Sides          | 42  |

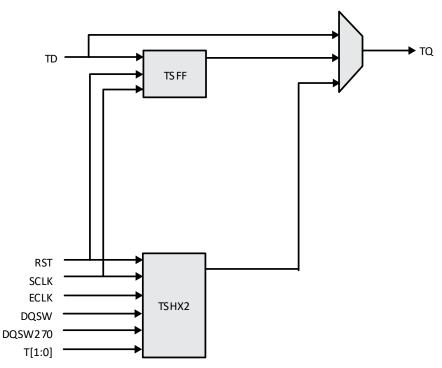

| Figure 2.24. Tri-state Register Block on Bottom Side                         | 42  |

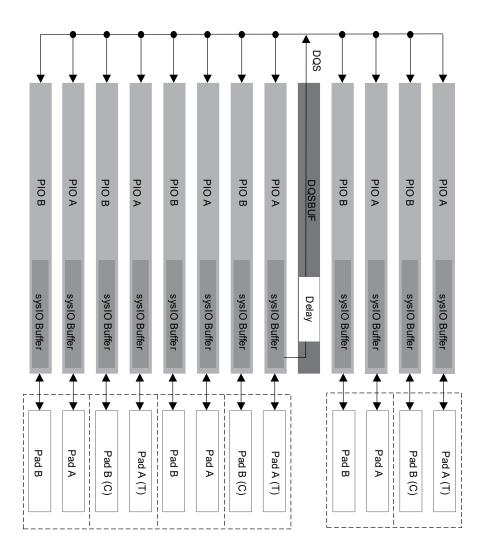

| Figure 2.25. DQS Grouping on the Bottom Edge                                 | 43  |

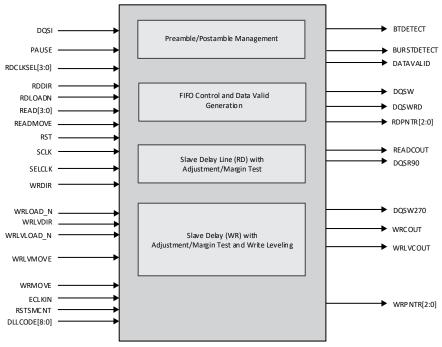

| Figure 2.26. DQS Control and Delay Block (DQSBUF)                            | 44  |

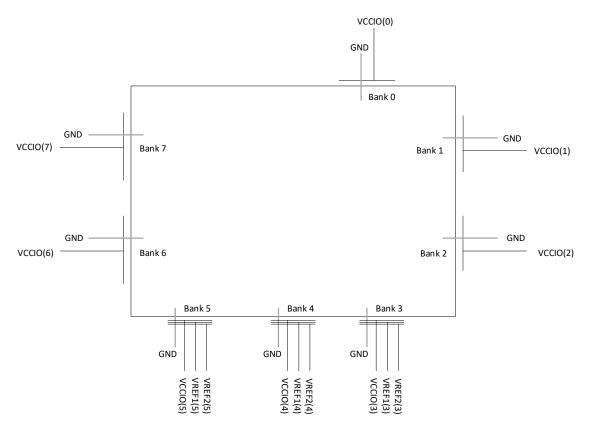

| Figure 2.27. sysI/O Banking                                                  | 47  |

| Figure 2.28. SERDES/PCS Overall Structure                                    | 53  |

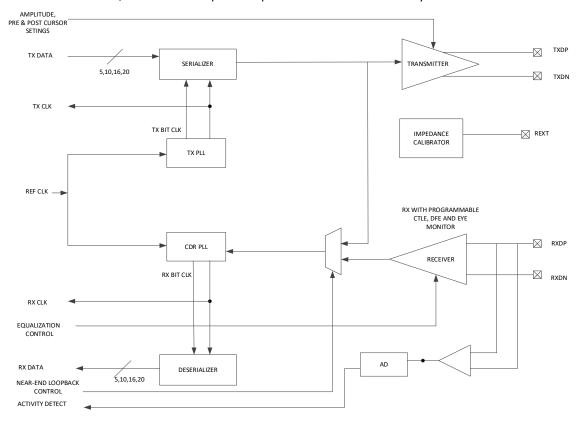

| Figure 2.29. Single-channel Block Diagram for SERDES Block                   | 55  |

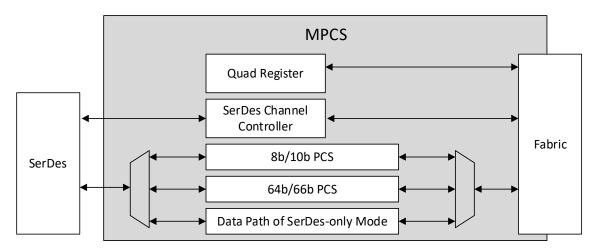

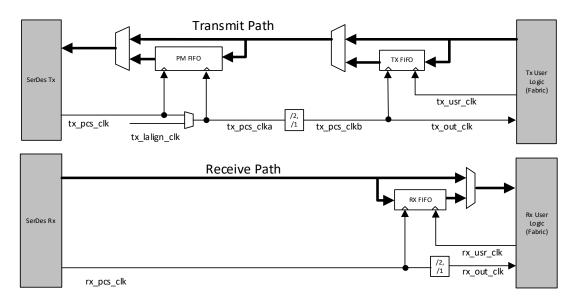

| Figure 2.30. Simplified Channel Block Diagram for MPCS Block                 | 56  |

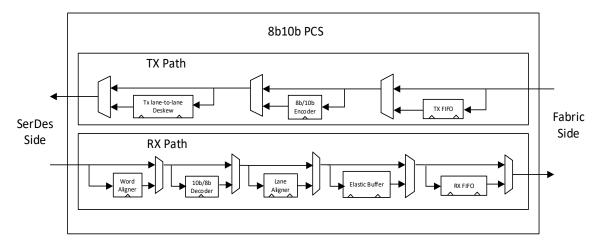

| Figure 2.31. Simplified Channel Block Diagram for MPCS 8b10b Sub-Block       | 56  |

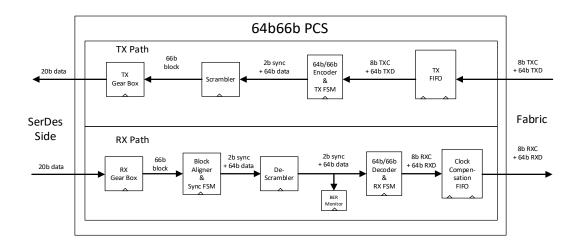

| Figure 2.32. Simplified Channel Block Diagram for MPCS 64b66b Sub-Block      | 56  |

| Figure 2.33. Simplified Channel Block Diagram for MPCS SERDES-only Sub-Block | 57  |

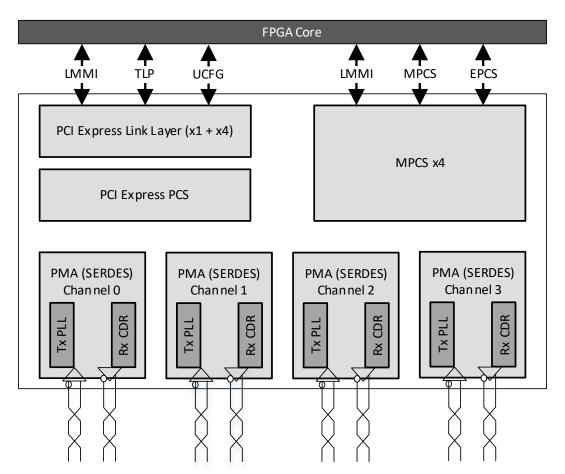

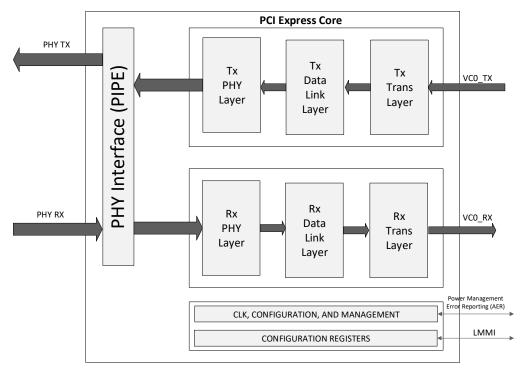

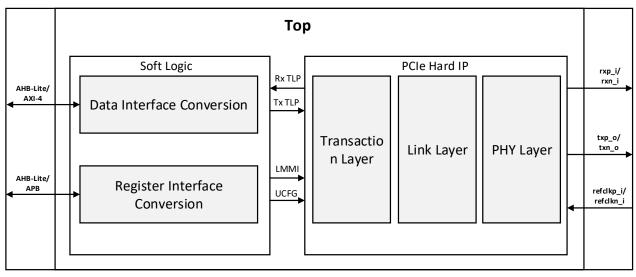

| Figure 2.34. PCIe Core                                                       | 58  |

| Figure 2.35. PCIe Soft IP Wrapper                                            | 58  |

| Figure 2.36. Cryptographic Engine Block Diagram                              | 59  |

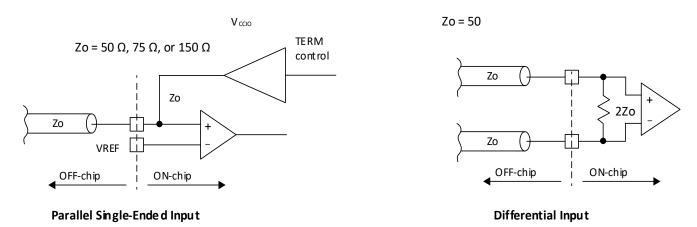

| Figure 3.1. On-chip Termination                                              | 62  |

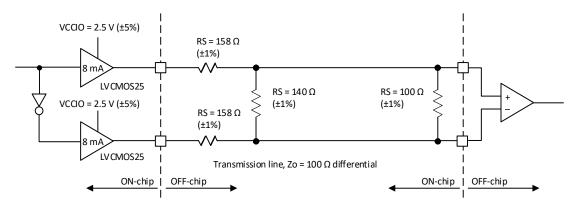

| Figure 3.2. LVDS25E Output Termination Example                               | 70  |

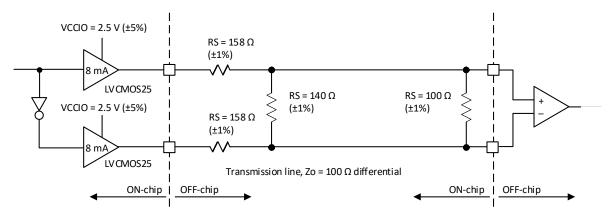

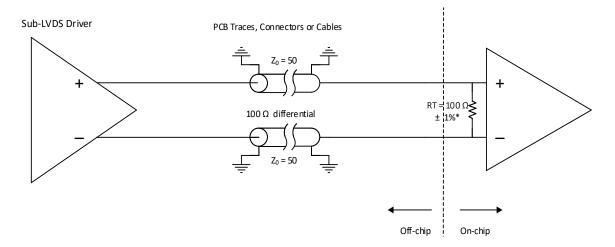

| Figure 3.3. SubLVDS Input Interface                                          | 70  |

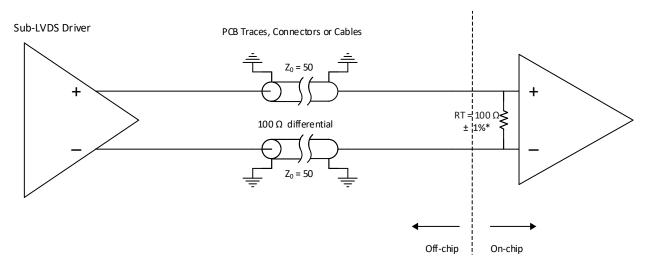

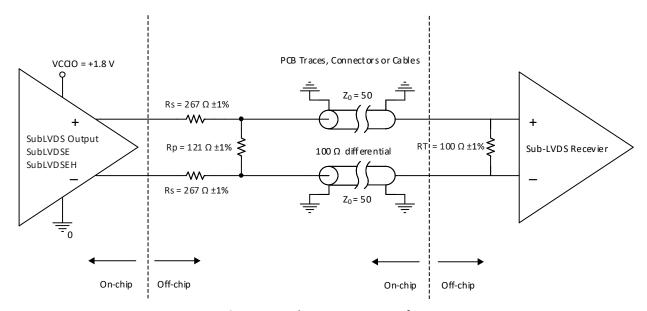

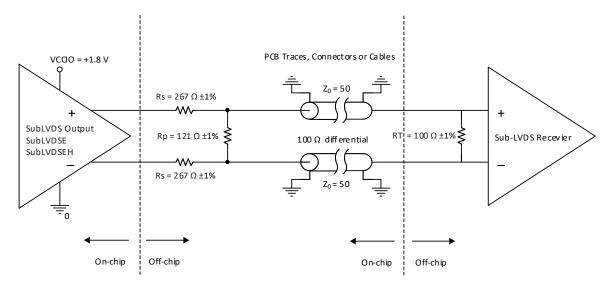

| Figure 3.4. SubLVDS Output Interface                                         | 71  |

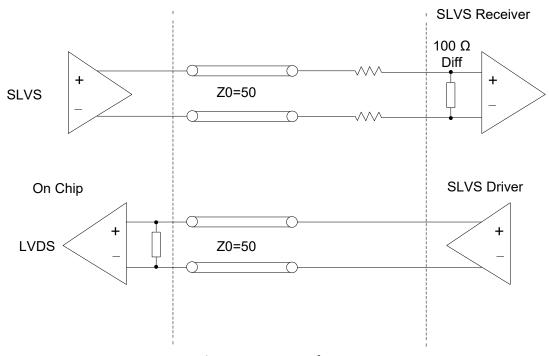

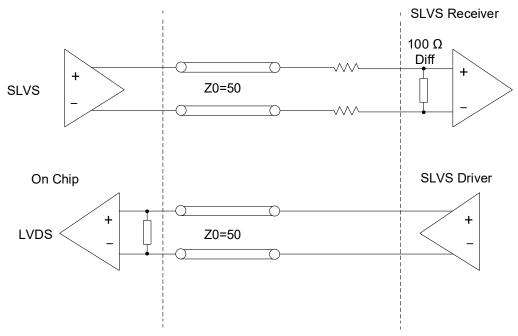

| Figure 3.5. SLVS Interface                                                   | 72  |

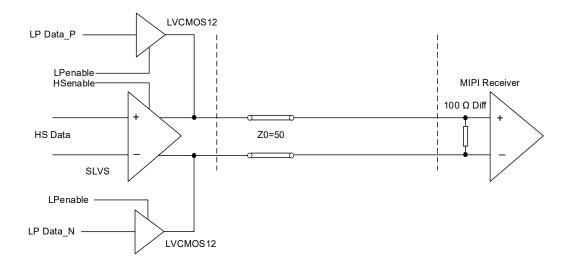

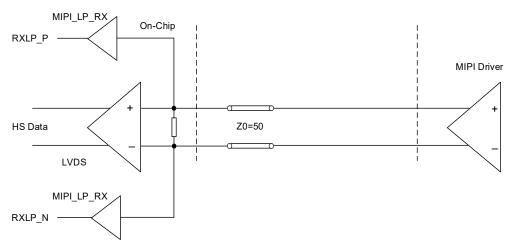

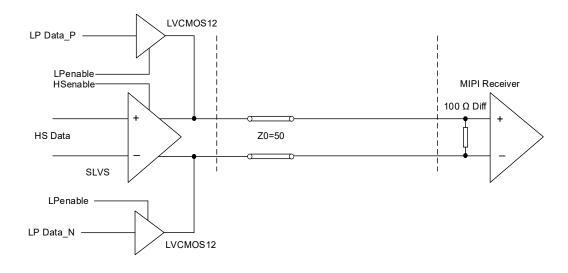

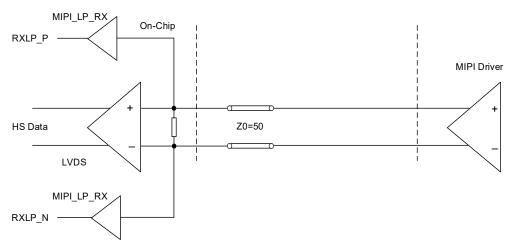

| Figure 3.6. MIPI Interface                                                   | 73  |

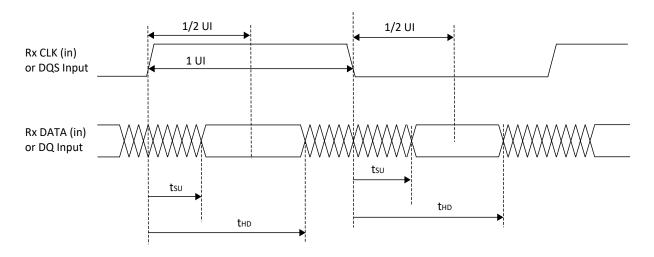

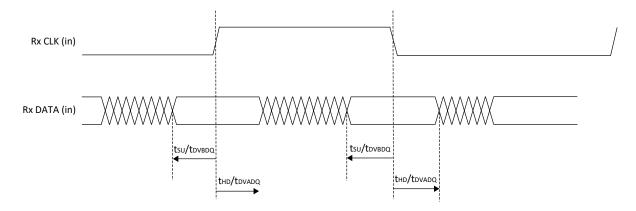

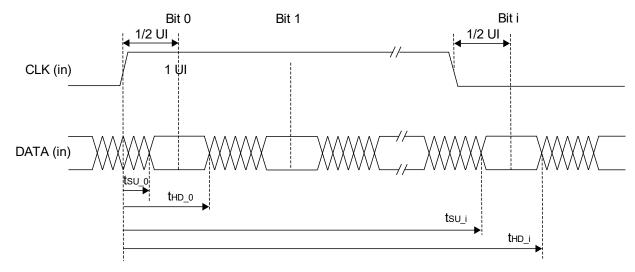

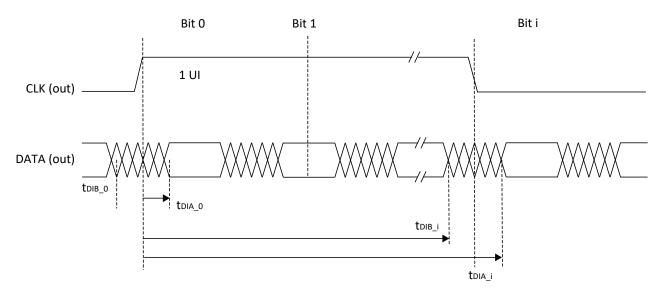

| Figure 3.7. Receiver RX.CLK.Centered Waveforms                               | 85  |

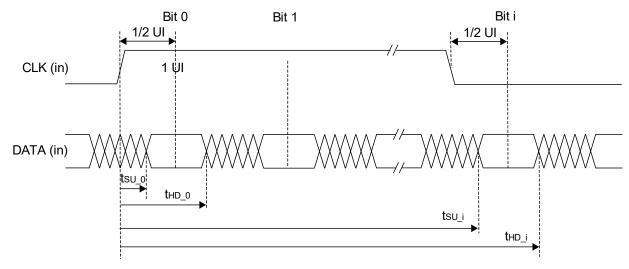

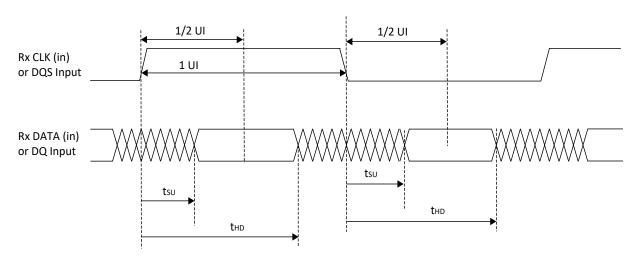

| Figure 3.8. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms           | 86  |

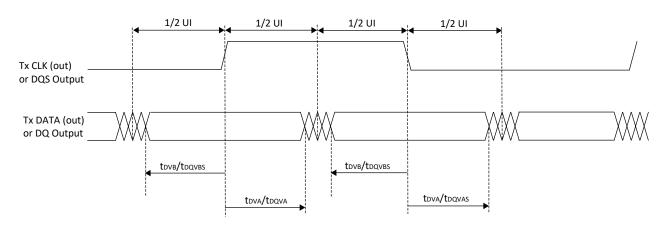

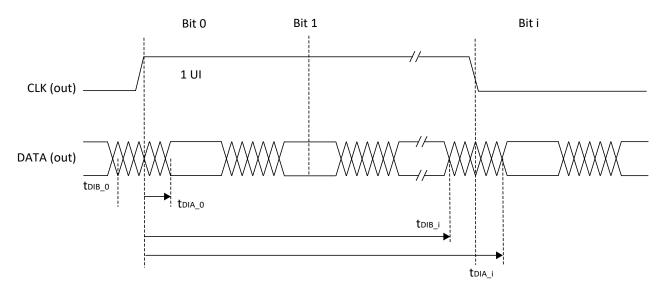

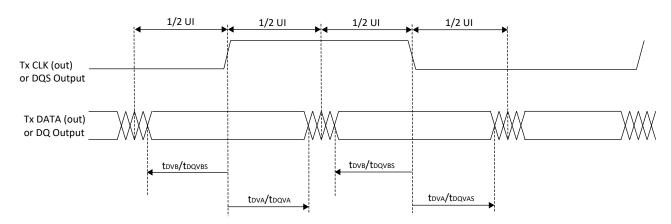

| Figure 3.9. Transmit TX.CLK.Centered and DDR Memory Output Waveforms         | 86  |

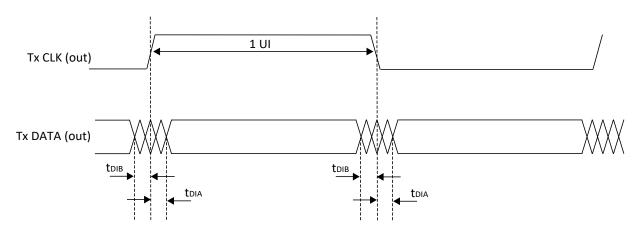

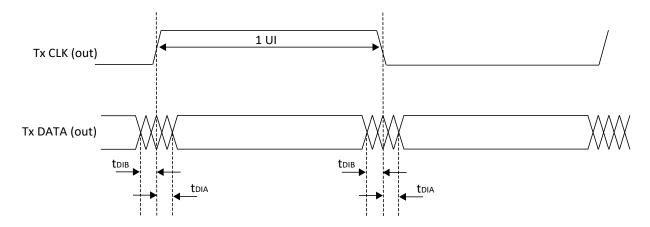

| Figure 3.10. Transmit TX.CLK.Aligned Waveforms                               |     |

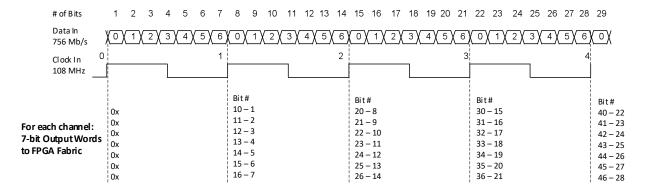

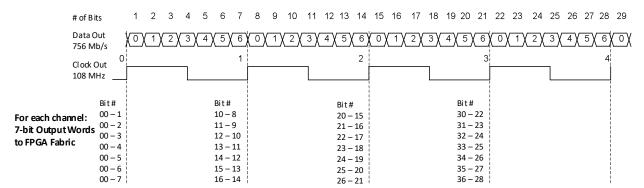

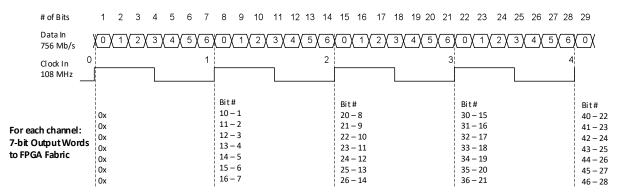

| Figure 3.11. DDRX71 Video Timing Waveforms                                   | 87  |

| Figure 3.12. Receiver DDRX71_RX Waveforms                                    | 87  |

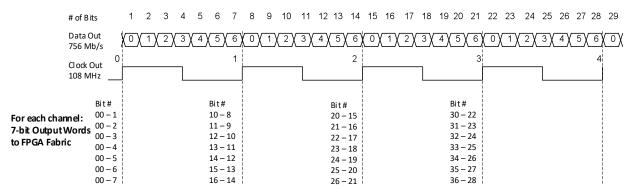

| Figure 3.13. Transmitter DDRX71_TX Waveforms                                 | 88  |

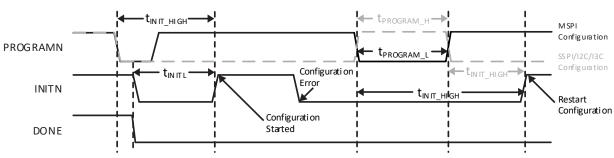

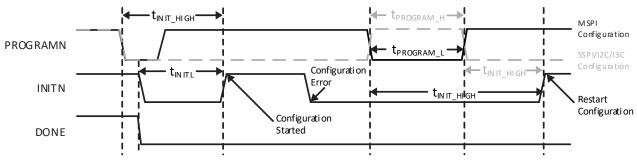

| Figure 3.14. Configuration Error Notification (1)                            | 103 |

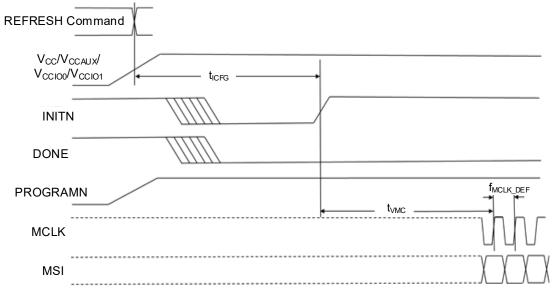

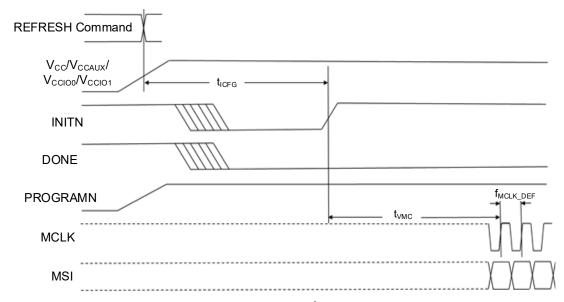

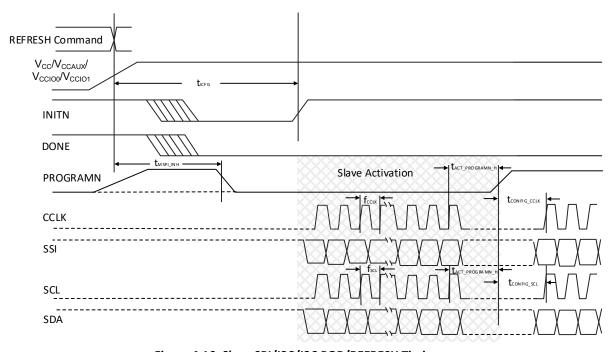

| Figure 3.15. Master SPI POR/REFRESH Timing                                   | 103 |

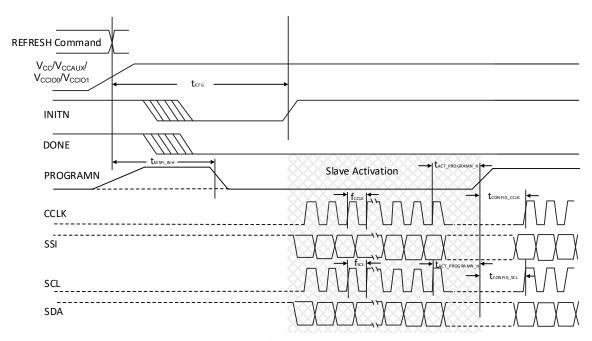

| Figure 3.16. Slave SPI/I2C/I3C POR/REFRESH Timing                            | 104 |

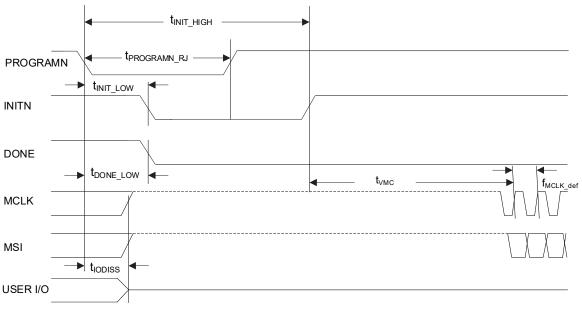

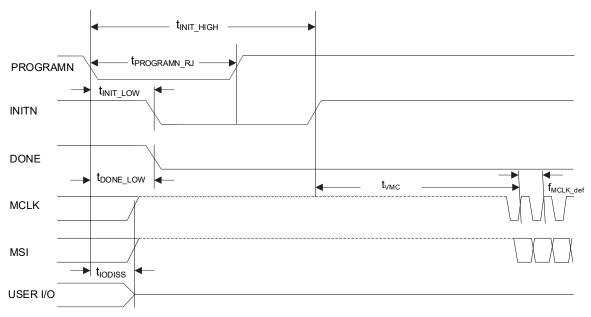

| Figure 3.17. Master SPI PROGRAMN Timing                              | 104 |

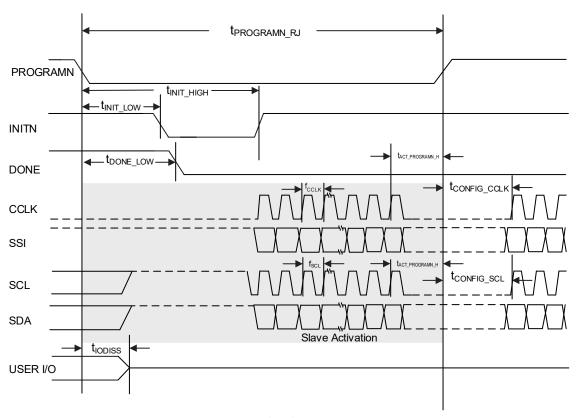

|----------------------------------------------------------------------|-----|

| Figure 3.18. Slave SPI/I2C/I3C PROGRAMN Timing                       | 105 |

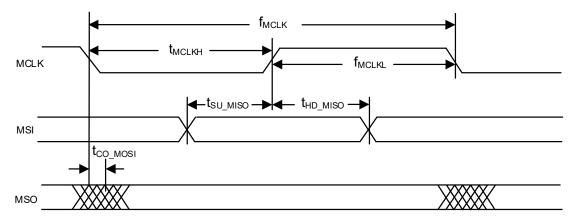

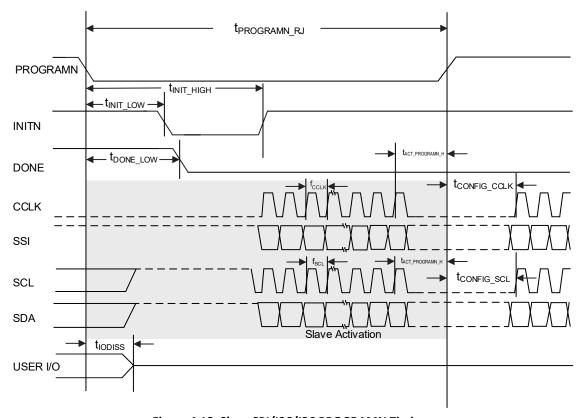

| Figure 3.19. Master SPI Configuration Timing                         | 105 |

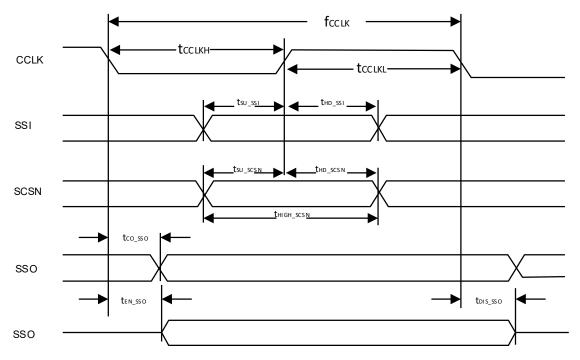

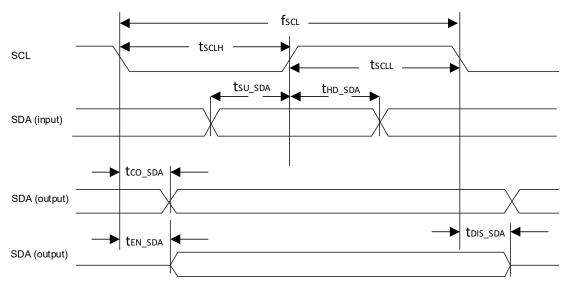

| Figure 3.20. Slave SPI Configuration Timing                          | 106 |

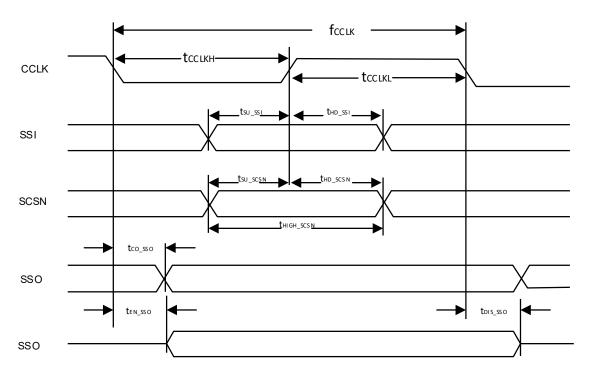

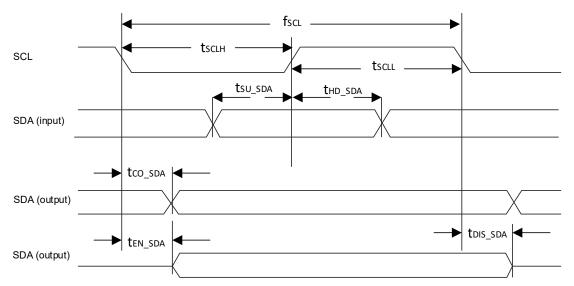

| Figure 3.21. I2C/I3C Configuration Timing                            | 106 |

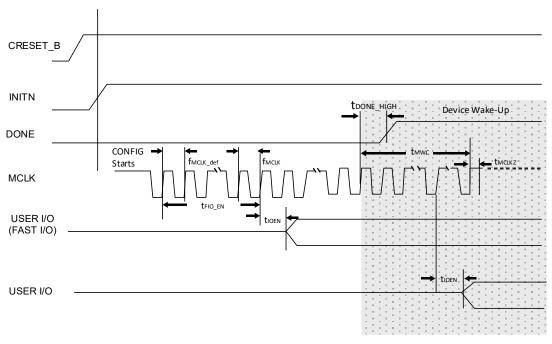

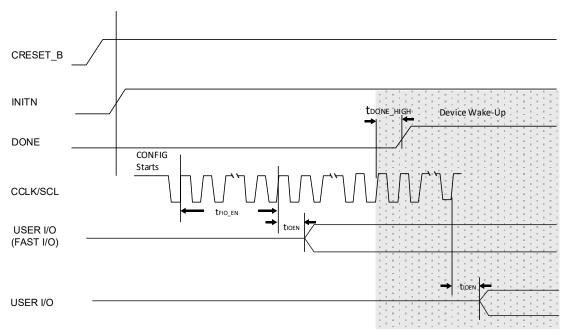

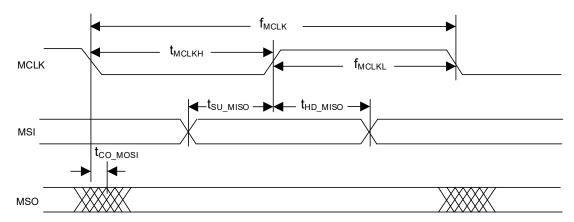

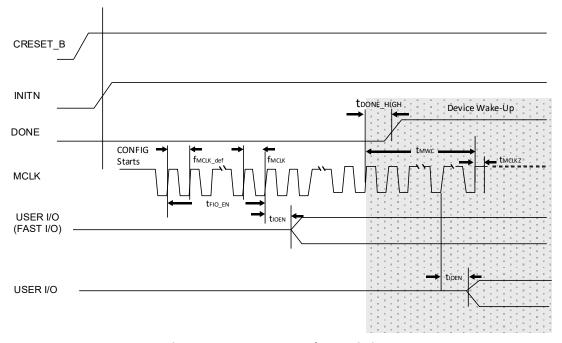

| Figure 3.22. Master SPI Wake-Up Timing                               | 107 |

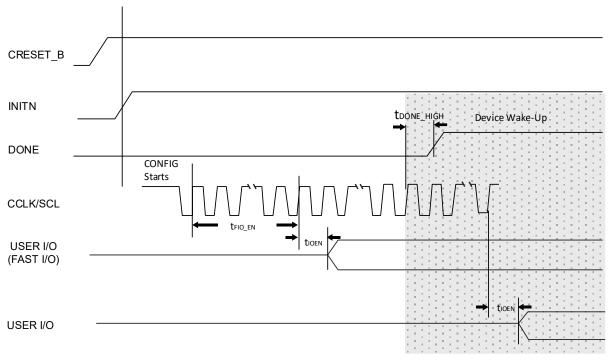

| Figure 3.23. Slave SPI/I2C/I3C Wake-Up Timing                        | 107 |

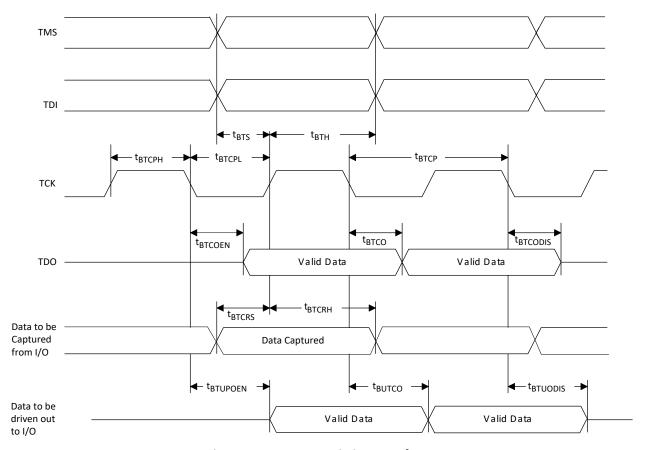

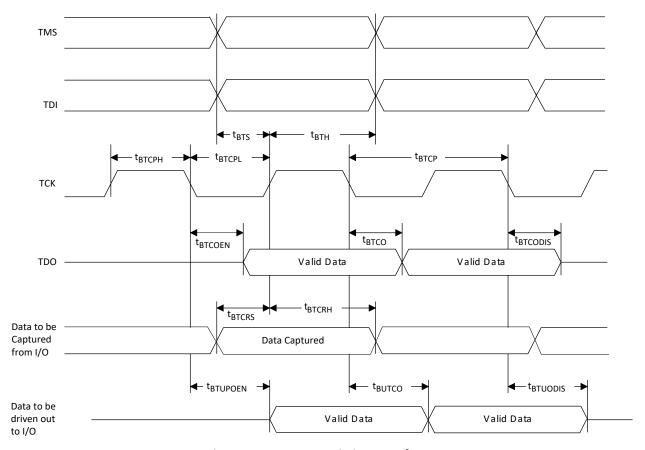

| Figure 3.24. JTAG Port Timing Waveforms                              |     |

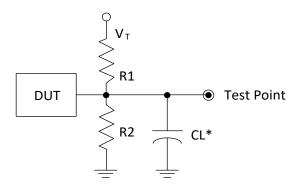

| Figure 3.25. Output Test Load, LVTTL and LVCMOS Standards            | 109 |

| Figure 4.1. On-chip Termination                                      | 112 |

| Figure 4.2. LVDS25E Output Termination Example                       | 120 |

| Figure 4.3. SubLVDS Input Interface                                  | 120 |

| Figure 4.4. SubLVDS Output Interface                                 | 121 |

| Figure 4.5. SLVS Interface                                           | 122 |

| Figure 4.6. MIPI Interface                                           | 123 |

| Figure 4.7. Receiver RX.CLK.Centered Waveforms                       | 135 |

| Figure 4.8. Receiver RX.CLK.Aligned and DDR Memory Input Waveforms   | 135 |

| Figure 4.9. Transmit TX.CLK.Centered and DDR Memory Output Waveforms | 135 |

| Figure 4.10. Transmit TX.CLK.Aligned Waveforms                       | 136 |

| Figure 4.11. DDRX71 Video Timing Waveforms                           | 136 |

| Figure 4.12. Receiver DDRX71_RX Waveforms                            |     |

| Figure 4.13. Transmitter DDRX71_TX Waveforms                         | 137 |

| Figure 4.14. Configuration Error Notification (2)                    | 151 |

| Figure 4.15. Master SPI POR/REFRESH Timing                           | 152 |

| Figure 4.16. Slave SPI/I2C/I3C POR/REFRESH Timing                    | 152 |

| Figure 4.17. Master SPI PROGRAMN Timing                              | 153 |

| Figure 4.18. Slave SPI/I2C/I3C PROGRAMN Timing                       | 153 |

| Figure 4.19. Master SPI Configuration Timing                         | 154 |

| Figure 4.20. Slave SPI Configuration Timing                          | 154 |

| Figure 4.21. I2C/I3C Configuration Timing                            | 155 |

| Figure 4.22. Master SPI Wake-Up Timing                               | 155 |

| Figure 4.23. Slave SPI/I2C/I3C Wake-Up Timing                        | 156 |

| Figure 4.24. JTAG Port Timing Waveforms                              | 157 |

| Figure 4.25. Output Test Load, LVTTL and LVCMOS Standards            | 158 |

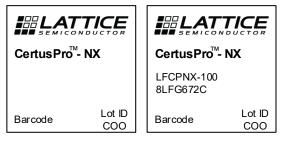

| Figure 6.1. Top Marking Diagram                                      | 169 |

## **Tables**

| Table 1.1. CertusPro-NX Family Selection Guide                                                                  | 17 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Table 2.1. Resources and Modes Available per Slice                                                              | 21 |

| Table 2.2. Slice Signal Descriptions <sup>1</sup>                                                               |    |

| Table 2.3. Number of Slices Required to Implement Distributed RAM <sup>1</sup>                                  | 24 |

| Table 2.4. sysMEM Block Configurations                                                                          | 33 |

| Table 2.5. Maximum Number of Elements in a sysDSP Block                                                         | 37 |

| Table 2.6. Input Block Port Description                                                                         | 39 |

| Table 2.7. Output Block Port Description                                                                        | 41 |

| Table 2.8. Tri-state Block Port Description                                                                     | 42 |

| Table 2.9. DQSBUF Port List Description                                                                         | 44 |

| Table 2.10. Single-Ended I/O Standards                                                                          | 46 |

| Table 2.11. Differential I/O Standards                                                                          | 46 |

| Table 2.12. Single-Ended I/O Standards Support on Various Sides                                                 | 48 |

| Table 2.13. Differential I/O Standards Supported on Various Sides                                               | 48 |

| Table 2.14. CertusPro-NX SERDES Standard Support                                                                | 54 |

| Table 2.15. Number of SERDES/PCS Channel per CertusPro-NX Device                                                | 54 |

| Table 3.1. Absolute Maximum Ratings                                                                             |    |

| Table 3.2. Recommended Operating Conditions <sup>1, 2, 3</sup>                                                  |    |

| Table 3.3. Power Supply Ramp Rates                                                                              |    |

| Table 3.4. Power-On Reset <sup>1</sup>                                                                          |    |

| Table 3.5. On-Chip Termination Options for Input Modes                                                          | 62 |

| Table 3.6. Hot Socketing Specifications for GPIO                                                                |    |

| Table 3.7. DC Electrical Characteristics – Wide Range (Over Recommended Operating Conditions)                   |    |

| Table 3.8. DC Electrical Characteristics – High Speed (Over Recommended Operating Conditions) <sup>1</sup>      |    |

| Table 3.9. Capacitors – Wide Range (Over Recommended Operating Conditions)                                      |    |

| Table 3.10. Capacitors – High Performance (Over Recommended Operating Conditions)                               |    |

| Table 3.11. Single Ended Input Hysteresis – Wide Range (Over Recommended Operating Conditions)                  |    |

| Table 3.12. Single Ended Input Hysteresis – High Performance (Over Recommended Operating Conditions)            |    |

| Table 3.13. sysI/O Recommended Operating Conditions                                                             |    |

| Table 3.14. sysI/O DC Electrical Characteristics – Wide Range I/O (Over Recommended Operating Conditions)       |    |

| Table 3.15. sysI/O DC Electrical Characteristics – High Performance I/O (Over Recommended Operating Conditions) |    |

| Table 3.16. I/O Resistance Characteristics (Over Recommended Operating Conditions)                              |    |

| Table 3.17. V <sub>IN</sub> Maximum Overshoot/Undershoot Allowance – Wide Range <sup>1, 2</sup>                 |    |

| Table 3.18. V <sub>IN</sub> Maximum Overshoot/Undershoot Allowance – High Performance <sup>1, 2</sup>           |    |

| Table 3.19. LVDS DC Electrical Characteristics (Over Recommended Operating Conditions) <sup>1</sup>             |    |

| Table 3.20. LVDS25E DC Conditions                                                                               |    |

| Table 3.21. SubLVDS Input DC Electrical Characteristics (Over Recommended Operating Conditions)                 | 70 |

| Table 3.22. SubLVDS Output DC Electrical Characteristics (Over Recommended Operating Conditions)                | 71 |

| Table 3.23. SLVS Input DC Characteristics (Over Recommended Operating Conditions)                               |    |

| Table 3.24. SLVS Output DC Characteristics (Over Recommended Operating Conditions)                              |    |

| Table 3.25. Soft D-PHY Input Timing and Levels                                                                  | 73 |

| Table 3.26. Soft D-PHY Output Timing and Levels                                                                 |    |

| Table 3.27. Soft D-PHY Clock Signal Specification                                                               | 75 |

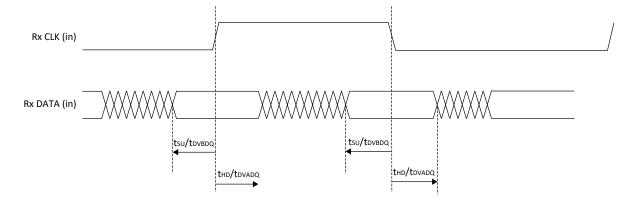

| Table 3.28. Soft D-PHY Data-Clock Timing Specifications                                                         | 75 |

| Table 3.29. Maximum I/O Buffer Speed <sup>1, 2, 3, 4, 7</sup>                                                   |    |

| Table 3.30. Pin-to-Pin Performance <sup>1</sup>                                                                 | 78 |

| Table 3.31. Register-to-Register Performance <sup>1, 3, 4</sup>                                                 |    |

| Table 3.32. External Switching Characteristics (Vcc = 1.0 V)                                                    |    |

| Table 3.33. sysCLOCK PLL Timing (V <sub>CC</sub> = 1.0 V)                                                       |    |

| Table 3.34. Internal Oscillators (Vcc = 1.0 V)                                                                  |    |

| Table 3.35. User I <sup>2</sup> C Specifications (V <sub>CC</sub> = 1.0 V)                                      | 89 |

| Table 3.36. ADC Specifications <sup>1</sup>                                                                     | 89 |

|                                                                                                                 |    |

| Table 3.37. Comparator Specifications                                                                           | 90   |

|-----------------------------------------------------------------------------------------------------------------|------|

| Table 3.38. DTR Specifications <sup>1, 2</sup>                                                                  |      |

| Table 3.39. Serial Output Timing and Levels                                                                     | 91   |

| Table 3.40. Channel Output Jitter                                                                               | 92   |

| Table 3.41. Serial Input Data Specifications                                                                    | 93   |

| Table 3.42. Receiver Total Jitter Tolerance Specification <sup>1</sup>                                          | 93   |

| Table 3.43. External Reference Clock Specification for SDQx_REFCLKP/N <sup>1</sup>                              | 95   |

| Table 3.44. External Reference Clock Specification for SD_EXTx_REFCLKP/N1                                       |      |

| Table 3.45. PCIe (2.5 Gbps)                                                                                     | 96   |

| Table 3.46. PCIe (5 Gbps)                                                                                       | 97   |

| Table 3.47. PCIe (8 Gbps)                                                                                       | 99   |

| Table 3.48. SGMII <sup>1</sup>                                                                                  |      |

| Table 3.49. sysCONFIG Port Timing Specifications                                                                |      |

| Table 3.50. JTAG Port Timing Specifications                                                                     |      |

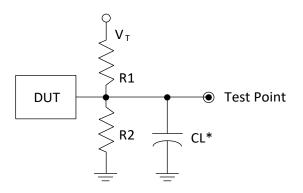

| Table 3.51. Test Fixture Required Components, Non-Terminated Interfaces <sup>1</sup>                            | .109 |

| Table 4.1. Absolute Maximum Ratings                                                                             |      |

| Table 4.2. Recommended Operating Conditions 1, 2, 3                                                             |      |

| Table 4.3. Power Supply Ramp Rates                                                                              | .111 |

| Table 4.4. Power-On Reset <sup>1</sup>                                                                          | .112 |

| Table 4.5. On-Chip Termination Options for Input Modes                                                          | .112 |

| Table 4.6. Hot Socketing Specifications for GPIO                                                                | .113 |

| Table 4.7. DC Electrical Characteristics – Wide Range (Over Recommended Operating Conditions)                   | .113 |

| Table 4.8. DC Electrical Characteristics – High Speed (Over Recommended Operating Conditions)                   | .114 |

| Table 4.9. Capacitors – Wide Range (Over Recommended Operating Conditions)                                      | .114 |

| Table 4.10. Capacitors – High Performance (Over Recommended Operating Conditions)                               | .114 |

| Table 4.11. Single Ended Input Hysteresis – Wide Range (Over Recommended Operating Conditions)                  | .114 |

| Table 4.12. Single Ended Input Hysteresis – High Performance (Over Recommended Operating Conditions)            | .115 |

| Table 4.13. sysI/O Recommended Operating Conditions                                                             | .115 |

| Table 4.14. sysI/O DC Electrical Characteristics – Wide Range I/O (Over Recommended Operating Conditions)       | .117 |

| Table 4.15. sysI/O DC Electrical Characteristics – High Performance I/O (Over Recommended Operating Conditions) | .117 |

| Table 4.16. I/O Resistance Characteristics (Over Recommended Operating Conditions)                              |      |

| Table 4.17. V <sub>IN</sub> Maximum Overshoot/Undershoot Allowance – Wide Range <sup>1, 2</sup>                 | .118 |

| Table 4.18. V <sub>IN</sub> Maximum Overshoot/Undershoot Allowance – High Performance <sup>1, 2</sup>           |      |

| Table 4.19. LVDS DC Electrical Characteristics (Over Recommended Operating Conditions) <sup>1</sup>             | .119 |

| Table 4.20. LVDS25E DC Conditions                                                                               |      |

| Table 4.21. SubLVDS Input DC Electrical Characteristics (Over Recommended Operating Conditions)                 | .120 |

| Table 4.22. SubLVDS Output DC Electrical Characteristics (Over Recommended Operating Conditions)                |      |

| Table 4.23. SLVS Input DC Characteristics (Over Recommended Operating Conditions)                               |      |

| Table 4.24. SLVS Output DC Characteristics (Over Recommended Operating Conditions)                              | .121 |

| Table 4.25. Soft D-PHY Input Timing and Levels                                                                  | .123 |

| Table 4.26. Soft D-PHY Output Timing and Levels                                                                 |      |

| Table 4.27. Soft D-PHY Clock Signal Specification                                                               | .125 |

| Table 4.28. Soft D-PHY Data-Clock Timing Specifications                                                         |      |

| Table 4.29. Maximum I/O Buffer Speed <sup>1, 2, 3, 4, 7</sup>                                                   |      |

| Table 4.30. Pin-to-Pin Performance <sup>1</sup>                                                                 | .128 |

| Table 4.31. Register-to-Register Performance <sup>1, 3, 4</sup>                                                 | .128 |

| Table 4.32. External Switching Characteristics (V <sub>CC</sub> = 1.0 V)                                        | .129 |

| Table 4.33. sysCLOCK PLL Timing (Vcc = 1.0 V)                                                                   |      |

| Table 4.34. Internal Oscillators (V <sub>CC</sub> = 1.0 V)                                                      |      |

| Table 4.35. User I2C Specifications (Vcc = 1.0 V)                                                               |      |

| Table 4.36. ADC Specifications <sup>1</sup>                                                                     |      |

| Table 4.37. Comparator Specifications                                                                           |      |

| Table 4.38. DTR Specifications <sup>1, 2</sup>                                                                  |      |

| Table 4.39. Serial Output Timing and Levels                                                                     | .141 |

| Table 4.40. Channel Output Jitter                                                     | 141 |

|---------------------------------------------------------------------------------------|-----|

| Table 4.41. Serial Input Data Specifications                                          |     |

| Table 4.42. Receiver Total Jitter Tolerance Specification <sup>1</sup>                | 143 |

| Table 4.43. External Reference Clock Specification for SDQx_REFCLKP/N <sup>1</sup>    | 145 |

| Table 4.44. External Reference Clock Specification for SD_EXTx_REFCLKP/N <sup>1</sup> | 145 |

| Table 4.45. PCIe (2.5 Gbps)                                                           | 146 |

| Table 4.46. PCIe (5 Gbps)                                                             |     |

| Table 4.47. SGMII <sup>1</sup>                                                        |     |

| Table 4.48. sysCONFIG Port Timing Specifications                                      | 149 |

| Table 4.49. JTAG Port Timing Specifications                                           | 157 |

| Table 4.50. Test Fixture Required Components, Non-Terminated Interfaces <sup>1</sup>  | 158 |

| Table 5.1. Signal Description                                                         | 159 |

| Table 5.2. Pin Information Summary                                                    |     |

| Table 6.1. Commercial Part Numbers                                                    |     |

| Table 6.2. Commercial Part Numbers - 01A Die Version                                  |     |

| Table 6.3. Industrial Part Numbers                                                    |     |

| Table 6.4. Industrial Part Numbers - 01A Die Version                                  | 171 |

| Table 6.5. Automotive Part Numbers                                                    | 171 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym          | sed in this document.  Definition                   |  |

|------------------|-----------------------------------------------------|--|

| ADC              | Analog to Digital Convertor                         |  |

| AES              | Advanced Encryption Standard                        |  |

| ALU              | Arithmetic Logic Unit                               |  |

| BGA              | Ball Grid Array                                     |  |

| CDR              | Clock and Data Recovery                             |  |

| CMUX             | Center MUX                                          |  |

| CRC              | Cycle Redundancy Code                               |  |

| CSI              | Camera Serial Interface                             |  |

| DCC              | Dynamic Clock Control                               |  |

| DCS              | Dynamic Clock Select                                |  |

| DDR              | Double Data Rate                                    |  |

| DLL              | Delay Locked Loop                                   |  |

| DQS              | DQ Strobe                                           |  |

| DRAM             | Dynamic RAM                                         |  |

| DSI              | Display Serial Interface                            |  |

| DSP              | Digital Signal Processing                           |  |

| EBR              | Embedded Block RAM                                  |  |

| ECC              | Error Correction Coding                             |  |

| ECDSA            | Elliptic Curve Digital Signature Algorithm          |  |

| ECLK             | Edge Clock                                          |  |

| ECLKDIV          | Edge Clock Divider                                  |  |

| eDP/DP           | Embedded DisplayPort/DisplayPort                    |  |

| FD-SOI           | Fully Depleted Silicon on Insulator                 |  |

| FFT              | Fast Fourier Transform                              |  |

| FIFO             | First In First Out                                  |  |

| FIR              | Finite Impulse Response                             |  |

| GPIO             | General Purpose I/O                                 |  |

| GPLL             | Global Phase Locked Loop                            |  |

| HFOSC            | High Frequency Oscillator                           |  |

| HMAC             | Hash-based Message Authentication Code              |  |

| НР               | High Performance                                    |  |

| HS               | High Speed                                          |  |

| I <sup>2</sup> C | Inter-Integrated Circuit                            |  |

| I3C              | Improved Inter-Integrated Circuit                   |  |

| IP               | Intellectual Property                               |  |

| LC               | Logic Cell                                          |  |

| LOL              | Loss Of Lock                                        |  |

| LFOSC            | Low Frequency Oscillator                            |  |

| LMMI             | Lattice Memory Mapped Interface                     |  |

| LP               | Low Power                                           |  |

| LSB              | Least Significant Bit                               |  |

| LPDDR            | Low Power Double Data Rate                          |  |

| LRAM             | Large Random Access Memory                          |  |

| LVCMOS           | Low-Voltage Complementary Metal Oxide Semiconductor |  |

| LVDS             | Low-Voltage Differential Signaling                  |  |

|                  | 1 0 1 1 1 1 1 0 1 0                                 |  |

| Acronym | Definition                                                                    |  |

|---------|-------------------------------------------------------------------------------|--|

| LVPECL  | Low Voltage Positive Emitter Coupled Logic                                    |  |

| LVTTL   | Low Voltage Transistor-Transistor Logic                                       |  |

| LUT     | Look Up Table                                                                 |  |

| MAC     | Multiply and Accumulate                                                       |  |

| MPCS    | Multi-Protocol PCS                                                            |  |

| MSPS    | Million Samples Per Second                                                    |  |

| MUX     | Multiplexer                                                                   |  |

| OSC     | Oscillator                                                                    |  |

| PCI     | Peripheral Component Interconnect                                             |  |

| PCS     | Physical Coding Sublayer                                                      |  |

| PCLK    | Primary Clock                                                                 |  |

| PCLKDIV | Primary Clock Divider                                                         |  |

| PDPR    | Pseudo Dual Port RAM                                                          |  |

| PFU     | Programmable Functional Unit                                                  |  |

| PIC     | Programmable I/O Cell                                                         |  |

| PLL     | Phase Locked Loop                                                             |  |

| POR     | Power On Reset                                                                |  |

| PTAT    | Proportional To Absolute Temperature                                          |  |

| RAM     | Random-access Memory                                                          |  |

| RGMII   | Reduced Gigabit Media Independent Interface                                   |  |

| ROM     | Read Only Memory                                                              |  |

| RST     | Reset                                                                         |  |

| SAR     | Successive Approximation Register                                             |  |

| SCI     | SERDES Client Interface                                                       |  |

| SCL     | Serial Clock                                                                  |  |

| SDA     | Serial Data                                                                   |  |

| SDR     | Single Data Rate                                                              |  |

| SEC     | Soft Error Correction                                                         |  |

| SED     | Soft Error Detection                                                          |  |

| SER     | Soft Error Rate                                                               |  |

| SERDES  | Serializer/Deserializer                                                       |  |

| SEU     | Single Event Upset                                                            |  |

| SGMII   | Serial Gigabit Media Independent Interface                                    |  |

| SHA     | Secure Hash Algorithm                                                         |  |

| SLVS    | Scalable Low-Voltage Signaling                                                |  |

| SLVS-EC | Scalable Low-Voltage Signaling  Scalable Low-Voltage Signaling Embedded Clock |  |

| SPI     | Serial Peripheral Interface                                                   |  |

| SSPI    | Slave Serial Peripheral Interface                                             |  |

| SPR     | Single Port RAM                                                               |  |

| SRAM    | Static Random-Access Memory                                                   |  |

| TAP     | Test Access Port                                                              |  |

| TDM     | Time Division Multiplexing                                                    |  |

| Tx      | Transmitter                                                                   |  |

| TLP     | Transaction Layer Packet                                                      |  |

| UCFG    | User Configuration Space Register Interface                                   |  |

| Rx      | Receiver                                                                      |  |

| WR      | Wide Range                                                                    |  |

|         | 1 3-                                                                          |  |

## 1. Description

The CertusPro™-NX family of low-power general purpose FPGAs featuring 10G SerDes, LPDDR4 memory interface support and up to 100k logic cells can be used in a wide range of applications across multiple markets. It is built on the Lattice Nexus FPGA platform, using low-power 28 nm FD-SOI technology. It combines the extreme flexibility of an FPGA with the low power and high reliability (due to extremely low SER) of FD-SOI technology, and offers small footprint package options as well as 0.8 mm and 1.0 mm ball-pitch package options.

CertusPro-NX supports a variety of interfaces including PCI Express® (Gen1, Gen2, and Gen3), Ethernet (up to 10G), SLVS-EC, CoaXPress, eDP/DP, LVDS, Generic 8b10b, LVCMOS (0.9–3.3 V), and more.

Processing features of CertusPro-NX include up to 100k logic cells, 156 multipliers ( $18 \times 18$ ), 7.3 Mb of embedded memory (consisting of EBR and LRAM blocks), distributed memory and DRAM interfaces (supporting DDR3, DDR3L, LPDDR2, and LPDDR4 up to 1066 Mbps  $\times$  64bit data width).

CertusPro-NX FPGAs support fast configuration of the reconfigurable SRAM-based logic fabric, ultra-fast configuration of its programmable sysI/O™ and the TransFR™ field upgrade feature. Design security features, such as AES-256 encryption and ECDSA authentication, are also supported. In addition to the high reliability inherent to FD-SOI technology (due to its extremely low SER), active reliability features such as built-in frame-based Soft Error Detection (SED)/Soft Error Correction (SEC) (for SRAM-based logic fabric), and ECC (for EBR and LRAM) are also supported in CertusPro-NX devices. Dual 1 MSPS 12-bit Analog to Digital Convertors (ADCs) are available on-chip for system monitoring functions.

The Lattice Radiant™ design software allows large complex user designs to be efficiently implemented in CertusPro-NX FPGA family. Synthesis library support for CertusPro-NX devices is available for popular logic synthesis tools. Radiant tools use the synthesis tool output along with constraints from its floor planning tools to place and route the user design in CertusPro-NX device. The tools extract timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered Intellectual Property (IP) modules for CertusPro-NX family. By using these configurable soft IP cores as standardized blocks, you are free to concentrate on the unique aspects of user design, increasing productivity.

### 1.1. Features

- Available in Commercial, Industrial, and Automotive temperature grades

- Programmable architecture

- 50k to 100k logic cells

- 96 to 156 multipliers (18 × 18) in sysDSP™ blocks

- 3.8 to 7.3 Mb of embedded memory (including EBR and LRAM)

- 170 to 299 programmable sysI/O (High Performance and Wide Range I/O)

- Programmable sysl/O designed to support wide variety of interfaces

- High Performance (HP) I/O supported on bottom I/O banks

- Supports up to 1.8 V Vccio

- Mixed voltage support (1.0 V, 1.2 V, 1.5 V, and 1.8 V)

- High-speed differential up to 1.5 Gbps

- Supports LVDS, Soft D-PHY Transmitter (Tx)/Receiver (Rx), LVDS 7:1 Tx/Rx, SLVS Tx/Rx, subLVDS Rx

- Supports SGMII<sup>1</sup> (Gb Ethernet):

Two channels (Tx/Rx) at 1.25 Gbps

- Dedicated DDR3/DDR3L and LPDDR2/LPDDR4 memory support with DQS logic, up to 1066 Mbps data rate and ×64bit data width

- Wide Range (WR) I/O supported on left, right, and top I/O Banks

- Supports up to 3.3 V V<sub>CCIO</sub>

- Mixed voltage support: 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V

- Programmable slew rate: slow, medium, and fast

- Controlled impedance mode

- Emulated LVDS support

- Hot Socketing Support

- Embedded SerDes

- From 625 Mbps up to 10.3125 Gbps per channel, with up to 8 channels

- Multiple Protocol PCS support

- PCle hard IP supports:

- Gen1, Gen2, and Gen3

- Endpoint

- Multi-function up to four functions

- Up to four lanes

- Ethernet

- 10GBASE-R at 10.3125 Gbps

- SGMII at 1.25 Gbps

- XAUI at 3.125 Gbps per lane

- SLVS-EC at 1.25 Gbps, 2.5 Gbps and 5 Gbps

- DP/eDP at 1.62 Gbps (RBR), 2.7 Gbps (HBR),

5.4 Gbps (HBR2) and 8.1 Gbps (HBR3)

- CoaXPress at 1.25 Gbps, 2.5 Gbps, 3.125 Gbps, 5 Gbps and 6.25 Gbps

- Generic 8b10b at multiple data rates

- SerDes-only mode allows direct 8-bit or 10-bit interface to FPGA logic

- Power modes Low Power mode and High Performance modes

- User selectable

- Low Power mode for power saving and/or thermal challenges

- High Performance mode for faster processing

- Small footprint package options

- 9 mm × 9 mm to 27 mm × 27 mm package size

- Two channels of Clock Data Recovery (CDR) up to 1.25 Gbps to support SGMII<sup>1</sup> on HP I/O

- CDR for Rx

- 8b/10b decoding

- Independent Loss of Lock (LOL) detector for each CDR block

- sysCLOCK™ analog PLLs

- Three in 50k LC, and four in 100k LC

- Six outputs per PLL

- Fractional N

- Programmable and dynamic phase control

- Support spread spectrum clocking

- sysDSP enhanced DSP blocks

- Hardened pre-adder

- Dynamic shift for AI/ML support

- Four 18 × 18, eight 9 × 9, two 18 × 36, or 36 × 36 multipliers

- Advanced 18 × 36, two 18 × 18, or four 8 × 8

MAC per sysDSP blocks

- Flexible memory resources

- Up to 3.7 Mb sysMEM™ Embedded Block RAM (EBR) available

- Programmable width

- Error Correction Coding (ECC)<sup>2</sup>

- First In First Out (FIFO)

- 344 kbits to 639 kbits distributed RAM

- Large RAM Blocks

- 0.5 Mbit per block

- Up to seven (3.5 Mbit total) per device

- Internal bus interface support

- APB control bus

- AHB-Lite for data bus

- AXI4-streaming

- Configuration Fast, Secure

- SPI ×1, ×2, ×4 up to 150 MHz

- Master and Slave SPI support

- JTAG

- I<sup>2</sup>C and I3C

- Ultrafast I/O configuration for instant-on support (using Early I/O Release feature)

- Less than 30 ms full device configuration for LFCPNX-100 device

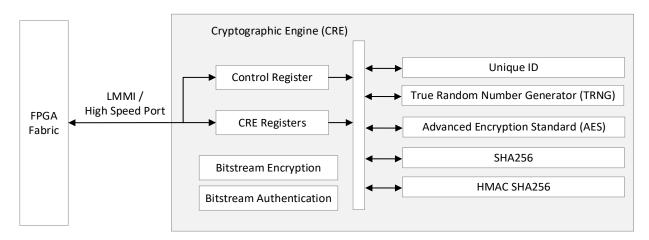

- Cryptographic engine

- Bitstream encryption using AES-256

- Bitstream authentication using ECDSA

- Hashing algorithms SHA, HMAC

- True Random Number Generator

- AES 128/256 Encryption

- Single Event Upset (SEU) Mitigation Support

- Extremely low Soft Error Rate (SER) due to FD-SOI technology

- Soft Error Detect Embedded hard macro

- Soft Error Correction Transparent to user design operation

- Soft Error Injection Emulate SEU event to debug system error handling

- Dual ADC 1 MSPS, 12-bit Successive Approximation Register (SAR), with Simultaneous Sampling<sup>2</sup>

- Three Continuous-time Comparators

- System-level support

- IEEE 1149.1 and IEEE 1532 compliant

- Reveal Logic Analyzer

- On-chip oscillator for device initialization and general use

- 1.0 V core power supply

#### Notes:

- The SGMII interface using LVDS I/O has limitations when operating across the full specified temperature range. Lattice recommends using alternative interfaces, such as SERDES or RGMII, for designs requiring Gigabit Ethernet. Refer to the Knowledge Database article for details. Contact your local Lattice sales representative for more information.

- 2. Available in Commercial/Industrial –8 and –9 speed grades and Automotive –7 and –8 speed grades.

Table 1.1. CertusPro-NX Family Selection Guide

| Device                                      | LFCPNX-50                                                                | LFCPNX-100                       |

|---------------------------------------------|--------------------------------------------------------------------------|----------------------------------|

| Logic Cells <sup>1</sup>                    | 52k                                                                      | 96k                              |

| Embedded Memory (EBR) Blocks (18 kb)        | 96                                                                       | 208                              |

| Embedded Memory (EBR) Bits (kb)             | 1,728                                                                    | 3,744                            |

| Distributed RAM Bits (kb)                   | 344                                                                      | 639                              |

| Large Memory (LRAM) Blocks (512 kb)         | 4                                                                        | 7                                |

| Large Memory (LRAM) Bits (kb)               | 2,048                                                                    | 3,584                            |

| 18 X 18 Multipliers                         | 96                                                                       | 156                              |

| ADC Blocks <sup>3</sup>                     | 2                                                                        | 2                                |

| 450 MHz High Frequency Oscillator           | 1                                                                        | 1                                |

| 32 kHz Low Power Oscillator                 | 1                                                                        | 1                                |

| GPLL                                        | 3                                                                        | 4                                |

| PCIe Gen3 hard IP                           | 1                                                                        | 14                               |

| SerDes (Quad/Channels)                      | 1/4                                                                      | 2/8²                             |

| Packages (Size, Ball Pitch)                 | Total I/O (Wide Range, High Performance, ADC <sup>6</sup> )/SerDes Lanes |                                  |

| ASG256 (9 mm × 9 mm, 0.5 mm)                | 165 (75, 84, 6)/4                                                        | 165 (75, 84, 6)/4                |

| CBG256 (14 mm × 14 mm, 0.8 mm)              | 165 (75, 84, 6)/4                                                        | 165 (75, 84, 6)/4                |

| BBG484 (19 mm × 19 mm, 0.8 mm) <sup>7</sup> | 269 (167, 96, 6)/4                                                       | 305 (167, 132, 6)/8              |

| BFG484 (23 mm × 23 mm, 1.0 mm) <sup>8</sup> | 269 (167, 96, 6)/45                                                      | 305 (167, 132, 6)/4 <sup>5</sup> |

| LFG672 (27 mm × 27 mm, 1.0 mm)              |                                                                          | 305 (167, 132, 6)/8 <sup>5</sup> |

#### Notes:

- 1. Logic Cells = LUTs  $\times$  1.2 effectiveness.

- 2. Some packages only with one Quad and four channels.

- 3. Available in Commercial/Industrial –8 and –9 speed grades and Automotive –7 and –8 speed grades.

- 4. For LFCPNX-100, PCIe Link Layer of Hard IP is only applicable to QUAD0.

- 5. Only available in Commercial and Industrial temperature grades.

- 6. Each ADC pin count reflects using dedicated complement pair and  $V_{\text{Ref.}}$

- 7. BBG package can support SerDes standards with data rate up to 6.25 Gbps.

- 8. BFG package can support SerDes standards with data rate up to 5.5 Gbps.

## 2. Architecture

### 2.1. Overview

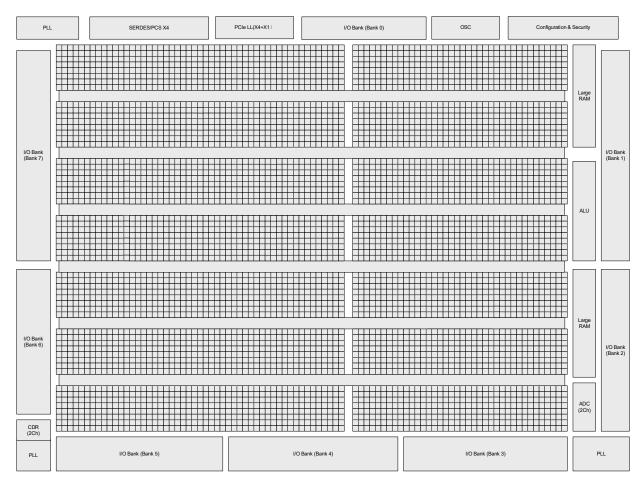

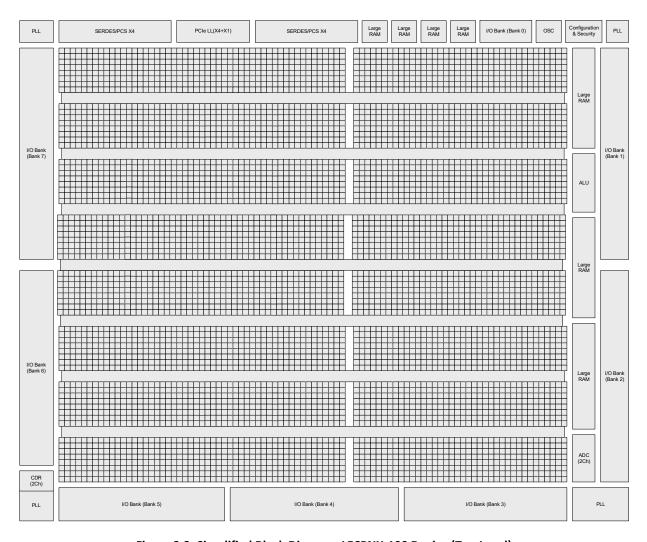

Each CertusPro-NX device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR) and rows of sysDSP Digital Signal Processing blocks, as shown in Figure 2.1 and Figure 2.2. For example, the LFCPNX-100 devices have three rows of DSP blocks and contain four rows of sysMEM EBR blocks. In addition, LFCPNX-100 devices include seven large SRAM blocks. The sysMEM EBR blocks are large, dedicated 18 kbits fast memory blocks and have built-in ECC and FIFO support. Each sysMEM block can be configured to a single, pseudo dual or true dual port memory in a variety of depths and widths as RAM or ROM. Each DSP block supports a variety of multiplier and adder configurations with one 108-bit or two 54-bit accumulators supported, which are the building blocks for complex signal processing capabilities.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysI/O buffers. The sysI/O buffers of the CertusPro-NX devices are arranged in eight banks allowing the implementation of a wide variety of I/O standards. The Wide Range (WR) I/O banks that are located on the top, left and right sides of the device provide flexible ranges of general purpose I/O configurations up to 3.3 V V<sub>CCIO</sub>. The banks located on the bottom side of the device are dedicated to High Performance (HP) interfaces such as LVDS, MIPI, DDR3, LPDDR2, and LPDDR4 supporting up to 1.8 V V<sub>CCIO</sub>.

The Programmable Functional Unit (PFU) contains the building blocks for logic, arithmetic, RAM, and ROM functions. The PFU block is optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. The registers in the PFU and sysI/O blocks in CertusPro-NX devices can be configured to be SET or RESET. After power up and device configuration, it enters into user mode with these registers SET/RESET according to the user design, allowing the device to power up in a known state for predictable system function.

The CertusPro-NX FPGAs feature up to 8 embedded 10 Gbps SerDes channels. Each SerDes channel contains independent 8b/10b encoding/decoding, polarity adjust and elastic buffer logic. Each group of four SerDes channels, along with its Physical Coding Sublayer (PCS) block, creates a Quad. The functionality of the SerDes/PCS Quads can be controlled by SRAM cell settings during device configuration or by registers that are addressable during device operation. The registers in every Quad can be programmed via the Lattice Memory Mapped Interface (LMMI). These Quads (up to two) are located at the top of the device. The FPGA also includes one hard PCIe link layer IP block which supports PCIe Gen1, Gen2, and Gen3.

In addition, CertusPro-NX devices provide various system level functional and interface hard IP such as I<sup>2</sup>C, SGMII/CDR, and ADC blocks. CertusPro-NX devices also provide security features to help protect user designs and deliver more robust reliability by offering the enhanced frame-based SED/SEC functions.

Other blocks provided include PLLs, DLLs, and configuration functions. The PLL and DLL blocks are located at the corners of each device. CertusPro-NX devices also include LMMI, which is a Lattice standard interface for simple read and write operations to control the internal IP.

Every device in the family has a JTAG port. This family also provides an on-chip oscillator and soft error detection (SED) capability. The CertusPro-NX devices use 1.0 V as their core voltage.

Figure 2.1. Simplified Block Diagram, LFCPNX-50 Device (Top Level)

Figure 2.2. Simplified Block Diagram, LFCPNX-100 Device (Top Level)

#### 2.2. PFU Blocks

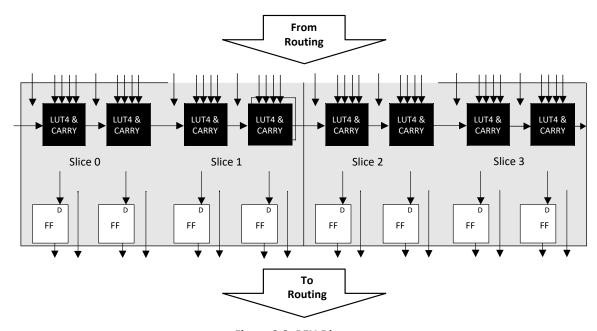

The core of the CertusPro-NX device consists of PFU blocks. Each PFU block consists of four interconnected slices numbered 0–3, as shown in Figure 2.3. Each slice contains two LUTs. All the interconnections to and from PFU blocks are from routing.

The PFU block can be used to perform Logic, Arithmetic, Distributed RAM or ROM functions. Table 2.1 shows the functions each slice can perform in either Distributed SRAM or non-Distributed SRAM modes.

Figure 2.3. PFU Diagram

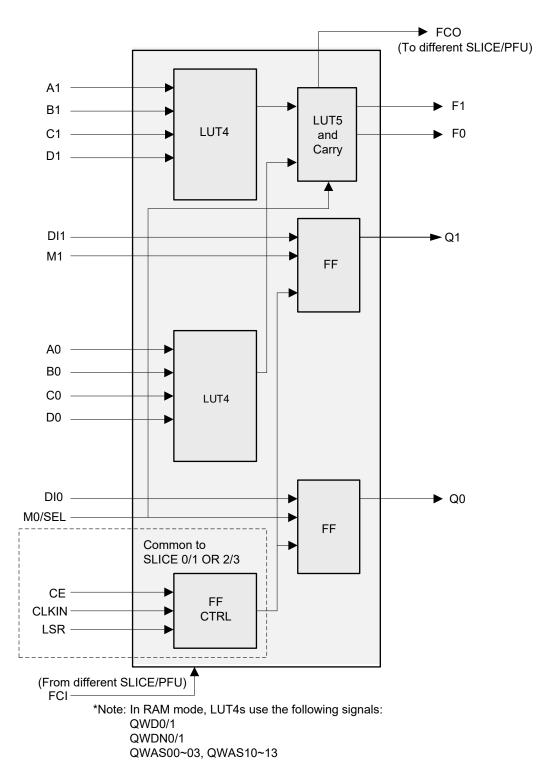

### 2.2.1. Slice

Each slice contains two LUT4s feeding two registers. In Distributed SRAM mode, Slice 0 and Slice 1 are configured as distributed memory and Slice 2 is not available as it is used to support Slice 0 and Slice 1, while Slice 3 is available as Logic or ROM. Table 2.1 shows the capability of the slices along with the operation modes they can enable. In addition, each Slice contains logic that allows the LUTs to be combined to perform a LUT5 function. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select, and wider RAM/ROM functions.

Table 2.1. Resources and Modes Available per Slice

| Slice   | PFU (Used as Distributed SRAM) |                    | PFU (Not used as Distributed SRAM) |                    |

|---------|--------------------------------|--------------------|------------------------------------|--------------------|

|         | Resources                      | Modes              | Resources                          | Modes              |

| Slice 0 | 2 LUT4s and 2 Registers        | RAM                | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

| Slice 1 | 2 LUT4s and 2 Registers        | RAM                | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

| Slice 2 | 2 LUT4s and 2 Registers        | RAM                | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

| Slice 3 | 2 LUT4s and 2 Registers        | Logic, Ripple, ROM | 2 LUT4s and 2 Registers            | Logic, Ripple, ROM |

Figure 2.4 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive or negative edge clocking.

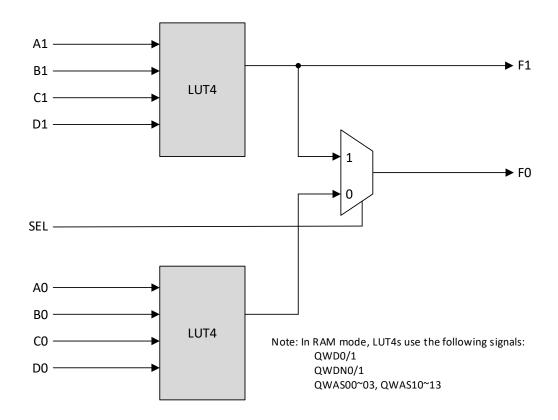

Each slice has 17 input signals: 16 signals from routing and one from the carry-chain (from the adjacent slice or PFU). Three of them are used for FF control and shared between two slices (0/1 or 2/3). There are five outputs: four to routing and one to carry-chain (to the adjacent PFU). Signals associated with all the slices can be found in Figure 2.4 and Table 2.2. Figure 2.5 shows the slice signals that support a LUT5 or two LUT4 functions. F0 can be configured to have a LUT4 or LUT5 output, while F1 can be configured as a LUT4 output only.

Figure 2.4. Slice Diagram

Figure 2.5. Slice Configuration for LUT4 and LUT5

Table 2.2. Slice Signal Descriptions<sup>1</sup>

| Function | Туре             | Signal Names   | Description                           |

|----------|------------------|----------------|---------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4.                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4.                       |

| Input    | Data signal      | M0, M1         | Direct input to FF from fabric.       |

| Input    | Control signal   | SEL            | LUT5 mux control input.               |

| Input    | Data signal      | DI0, DI1       | Inputs to FF from LUT4 F0/F1 outputs. |

| Input    | Control signal   | CE             | Clock Enable.                         |

| Input    | Control signal   | LSR            | Local Set/Reset.                      |

| Input    | Control signal   | CLKIN          | System Clock.                         |

| Input    | Inter-PFU signal | FCI            | Fast Carry-in.                        |

| Output   | Data signals     | F0             | LUT4/LUT5 output signal.              |

| Output   | Data signals     | F1             | LUT4 output signal.                   |

| Output   | Data signals     | Q0, Q1         | Register outputs.                     |

| Output   | Inter-PFU signal | FCO            | Fast carry chain output.              |

#### Note:

1. See Figure 2.4 for connection details.

#### 2.2.2. Modes of Operation

Slices 0-2 have up to four potential modes of operation: Logic, Ripple, RAM, and ROM. Slice 3 is not needed for the RAM mode. It can be used in Logic, Ripple, or ROM mode.

#### Logic Mode

In Logic mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, an LUT5 can be constructed within one slice.

#### **Ripple Mode**

The Ripple mode supports the efficient implementation of small arithmetic functions. In the Ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with asynchronous clear 2-bit using dynamic control

- Up/Down counter with preload (sync) 2-bit using dynamic control

- Comparator functions of A and B inputs 2-bit

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

- Up/Down counter with A greater-than-or-equal-to B comparator 2-bit using dynamic control

- Up/Down counter with A less-than-or-equal-to B comparator 2-bit using dynamic control

- Multiplier support Ai×Bj+1 + Ai+1×Bj in one logic cell with two logic cells per slice

- Serial divider 2-bit mantissa, shift 1 bit/cycle

- Serial multiplier 2-bit, shift 1 bit/cycle or 2 bits/cycle

The Ripple mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode), two additional signals, Carry Generate and Carry Propagate, are generated on a per-slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

#### **RAM Mode**

In the RAM mode, a  $16 \times 4$ -bit distributed single or pseudo dual port RAM can be constructed in one PFU using each LUT block in Slice 0 and Slice 1 as a  $16 \times 2$ -bit memory in each slice. Slice 2 is used to provide memory address and control signals. The CertusPro-NX devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different sized memories. Where appropriate, the software constructs these using distributed memory primitives that represent the capabilities of the PFU. Table 2.3 lists the number of slices required to implement different distributed RAM primitives. For more information about using RAM in CertusPro-NX devices, refer to Memory Usage Guide for Nexus Platform (FPGA-TN-02094).

Table 2.3. Number of Slices Required to Implement Distributed RAM<sup>1</sup>

|                  | SPR 16 × 4 | PDPR 16 × 4 |

|------------------|------------|-------------|

| Number of slices | 3          | 3           |

#### Note:

1. SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### **ROM Mode**

The ROM mode uses the LUT logic; hence, Slice 0 through Slice 3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information, refer to Memory Usage Guide for Nexus Platform (FPGA-TN-02094).

## 2.3. Routing

There are many resources provided in the CertusPro-NX devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers, and metal interconnect (routing) segments. The CertusPro-NX family has an enhanced routing architecture that produces a compact design. Lattice Radiant software tool takes the output of the synthesis tool and places and routes the design.

## 2.4. Clocking Structure

The CertusPro-NX clocking structure consists of clock synthesis blocks (sysCLOCK PLLs), balanced clock tree networks (PCLK and ECLK) and efficient clock logic modules: Clock Dividers (PCLKDIV and ECLKDIV), Dynamic Clock Select (DCS), Dynamic Clock Control (DCC), and DDRDLLs. Each of these functions is described as follows.

#### 2.4.1. Global PLL

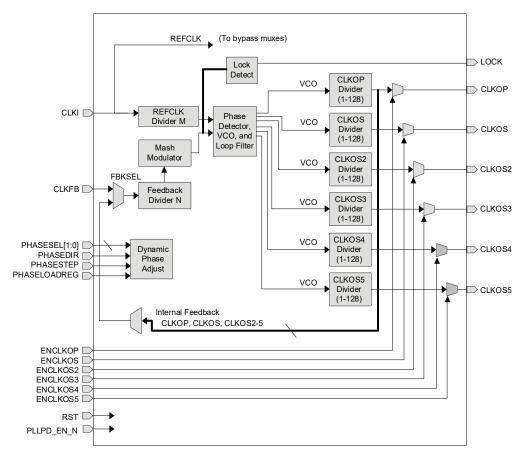

The Global PLLs (GPLL) provide the ability to synthesize clock frequencies. The devices in the CertusPro-NX family support three to four full-featured general purpose GPLLs.

The architecture of the GPLL is shown in Figure 2.6. A description of the GPLL functionality follows.

- 1. REFCLK is the reference frequency input to the PLL. The REFCLK source can come from external CLK inputs or from internal routing. The CLKI input feeds into the input Clock Divider block.

- 2. CLKFB is the feedback signal to the GPLL, which can come from a path internal to the PLL or from FPGA routing. The feedback divider is used to multiply the reference frequency and thus synthesize a higher or lower frequency clock output.

- 3. The PLL has six clock outputs, CLKOP, CLKOS, CLKOS2, CLKOS3, CLKOS4, and CLKOS5. Each output has its own output divider, thus allowing the GPLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. Each GPLL output can be used to drive the primary clock. Each bottom side GPLL output can be used to drive the edge clock networks.

- 4. The setup and hold times of the device can be improved by programming a phase shift into the output clocks which advances or delays the output clock with reference to the un-shifted output clock. This phase shift can be either programmed during the configuration or can be adjusted dynamically using the DIRSEL, DIR, DYNROTATE, and LOADREG ports.

- 5. The LOCK signal is asserted when the GPLL determines it has achieved lock and de-asserted if a loss of lock is detected. The LOCK signal is asynchronous to the PLL clock outputs.

Figure 2.6. General Purpose PLL Diagram

For more details on the PLL, refer to the sysCLOCK PLL Design and Usage Guide for Nexus Platform (FPGA-TN-02095).

#### 2.4.2. Clock Distribution Network

There are two main clock distribution networks for any member of the CertusPro-NX product family, namely Primary Clock (PCLK) and Edge Clock (ECLK). These clock networks can be driven from many different sources, such as Clock Pins, PLL outputs, DLLDEL outputs, Clock Divider outputs, SerDes/PCS clocks, and user logic. There are Clock Divider blocks, ECLKDIV and PCLKDIV, to provide a slower clock from these clock sources.

CertusPro-NX family supports glitchless Dynamic Clock Control (DCC) for the PCLK Clock to save dynamic power. There are also Dynamic Clock Selection logic to allow a glitchless selection between two clocks for the PCLK network (DCS).

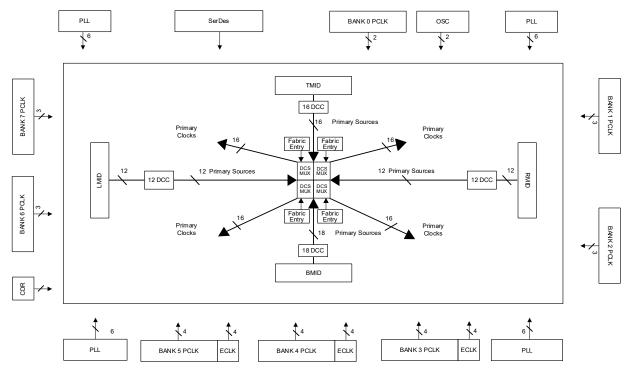

An overview of the Clocking network for the CertusPro-NX device is shown in Figure 2.7. The Upper Right PLL in Figure 2.7 is only for LFCPNX-100 Logic Cell devices.

Figure 2.7. Clocking Network

### 2.4.3. Primary Clocks

The CertusPro-NX device family provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric through the Primary Clock Network. The CertusPro-NX PCLK clock network is a balanced clock structure which is designed to minimize the clock skew across all destinations in the FPGA core.

The primary clock network is divided into four clock domains. Each of these domains has 16 clocks that can be distributed to the fabric in the domain.

The Lattice Radiant software can automatically route each clock to one of the domains up to a maximum of 16 clocks per domain. The user can change how the clocks are routed by specifying a preference in the Lattice Radiant software to locate the clock to a specific domain. The CertusPro-NX device provides the user with a maximum of 64 unique clock input sources that can be routed to the primary Clock network.

Primary clock sources are:

- Dedicated clock input pins

- PLL outputs

- PCLKDIV, ECLKDIV outputs

- Internal FPGA fabric entries (with minimum general routing)

- SGMII-CDR, SerDes/PCS clocks

- OSC clock

These sources routed to each of the four clock switches are called Mid Mux. They are LMID, RMID, TMID, and BMID. The outputs of the Mid MUX are routed to the center of the FPGA where additional clock switches (DCS MUX) are used to route the primary clock sources to primary clock distribution to the CertusPro-NX fabric. These routing multiplexers are shown in Figure 2.7. Potentially there are 64 unique clock domains that can be used in the CertusPro-NX device. For more information about the primary clock tree and connections, refer to sysCLOCK PLL Design and Usage Guide for Nexus Platform (FPGA-TN-02095).

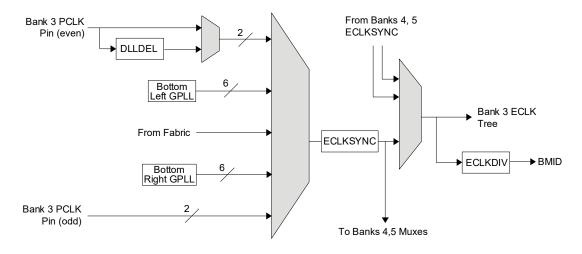

#### 2.4.4. Edge Clock

CertusPro-NX FPGAs have a number of high-speed edge clocks that are intended for use with the PIO in the implementation of high-speed interfaces. There are four ECLK networks per bank I/O on the bottom side of the device. The Edge clock network is powered by a separate power domain (to reduce power noise injection from the core and reduce overall noise induced jitter) while controlled by the same logic that gates the FPGA core and PCLK domains for power management.

Each Edge Clock can be sourced from the following:

- Dedicated PIO Clock input pins (PCLK)

- DLLDEL output (PIO Clock delayed by 90°)

- Bottom PLL outputs (CLKOP, CLKOS, CLKOS2, CLKOS3, CLKOS4, and CLKOS5)

- Internal Nodes

Figure 2.8 illustrates various ECLK sources. Bank 3 is an ECLK source example. Bank 4 and Bank 5 are similar.

Figure 2.8. Edge Clock Sources per Bank