# N Input to 1 Output MIPI CSI-2 Side-by-Side Aggregation

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Acronyms in This Document                         | 6  |

|---------------------------------------------------|----|

| 1. Introduction                                   | 7  |

| 1.1. Supported Device and IP                      | 7  |

| 1.2. Features                                     | 7  |

| 1.3. Block Diagram                                | 7  |

| 1.4. RX/TX Permutations and Parameter Calculation | 9  |

| 2. Parameters and Port List                       | 12 |

| 2.1. Synthesis Directives                         | 12 |

| 2.2. Simulation Directives                        | 15 |

| 2.3. Top-Level I/O                                | 16 |

| 3. Design and Module Description                  | 18 |

| 3.1. rx_dphy                                      | 18 |

| 3.1.1. RX FIFO                                    | 19 |

| 3.2. line_buf                                     | 20 |

| 3.2.1. Buffer Size                                | 20 |

| 3.2.2. RX Buffer Offset Control                   | 22 |

| 3.3. merge_ctrl                                   | 23 |

| 3.3.1. LP-HS Control in Non-Continuous Clock Mode | 23 |

| 3.3.2. LP-HS Control in Continuous Clock Mode     | 25 |

| 3.3.3. Line Buffer Read and Data Merge Operation  | 25 |

| 3.4. tx_dphy                                      | 27 |

| 3.5. Clock Distribution                           | 29 |

| 4. Design and File Modifications                  | 31 |

| 4.1. Top-Level RTL                                | 31 |

| 5. Design Simulation                              | 32 |

| 6. Known Limitations                              | 37 |

| 7. Design Package and Project Setup               | 38 |

| 8. Resource Utilization                           | 41 |

| 9. References                                     | 42 |

| Technical Support Assistance                      | 43 |

| Revision History                                  | 44 |

# **Figures**

| Figure 1.1. MIPI CSI-2 Side-by-Side Aggregation Block Diagram                                   | 8  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 1.2. Clocking Scheme Example in Continuous Clock Mode                                    |    |

| Figure 1.3. Clocking Scheme Example in Non-Continuous Clock Mode                                |    |

| Figure 1.4. Bandwidth and Parameter Calculator                                                  |    |

| Figure 3.1. rx_dphy IP Creation in Clarity Designer                                             |    |

| Figure 3.2. Buffer Size and Brief Write/Read Timings                                            |    |

| Figure 3.3. RX Buffer Offset Example #1 (RX bus width = 16, TX bus width = 32, WC residual = 1) |    |

| Figure 3.4. RX Buffer Offset Example #2 (RX bus width = 8, TX bus_width = 64, WC residual = 5)  |    |

| Figure 3.5. RX Buffer Offset Example #2 (RX bus width = 32, TX bus_width = 16, WC residual = 1) |    |

| Figure 3.6. LP-HS-LP Transition in Non-Continuous Clock Mode (Short Packet)                     |    |

| Figure 3.7. LP-HS-LP Transition in Non-Continuous Clock Mode (Long Packet)                      | 24 |

| Figure 3.8. LP-HS-LP Transition in Non-Continuous Clock Mode with KEEP_HS                       |    |

| Figure 3.9. LP-HS-LP Transition in Continuous Clock Mode (Short Packet)                         |    |

| Figure 3.10. Line Buffer Read and Data Merge for 5-Channel Aggregation                          |    |

| Figure 3.11. tx_dphy IP Creation in Clarity Designer                                            |    |

| Figure 5.1. Script Modification #1                                                              |    |

| Figure 5.2. Script Modification #2                                                              |    |

| Figure 5.3. Functional Simulation Example                                                       |    |

| Figure 7.1. Directory Structure                                                                 |    |

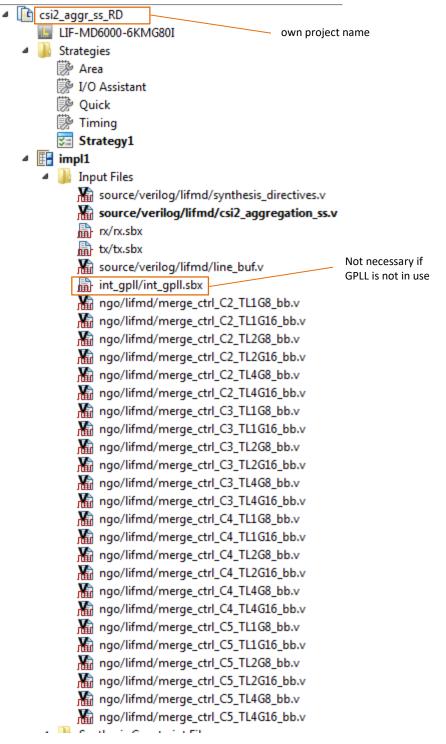

| Figure 7.2. Project Files                                                                       |    |

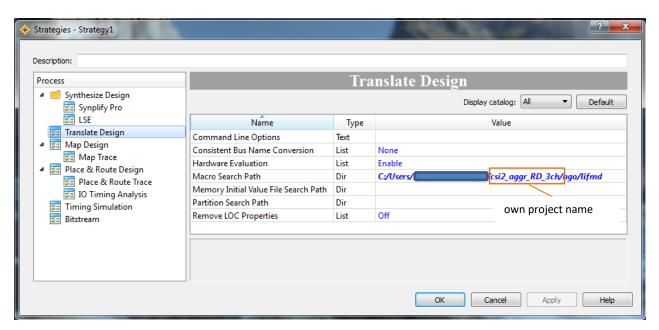

| Figure 7.3. Path Setting for .ngo Files                                                         |    |

## **Tables**

| Table 1.1. Supported Device and IP                      | 7  |

|---------------------------------------------------------|----|

| Table 1.2. RX and TX Permutation                        |    |

| Table 2.1. Synthesis Directives                         | 12 |

| Table 2.2. Simulation Directives                        | 15 |

| Table 2.3. CSI-2 Side-by-Side Aggregation Top-Level I/O | 16 |

| Table 3.1. Unit EBR and Payload Byte Count of RX Buffer |    |

| Table 8.1. Resource Utilization Examples                |    |

5

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                          |

|---------|-------------------------------------|

| AP      | Application Processor               |

| CSI-2   | Camera Serial Interface 2           |

| DDR     | Double Data Rate                    |

| EBR     | Embedded Block RAM                  |

| ECC     | Error Correction Code               |

| HS      | High Speed                          |

| ID      | Identification Data                 |

| LP      | Low Power                           |

| MIPI    | Mobile Industry Processor Interface |

| PLL     | Phase Locked Loop                   |

| GPLL    | General Purpose PLL                 |

| RX      | Receiver                            |

| SoT     | Start of Transmission               |

| TX      | Transmitter                         |

| VC      | Virtual Channel                     |

| VCO     | Voltage Controlled Oscillator       |

| WC      | Word Count                          |

## 1. Introduction

The majority of image sensors and application processors (AP) in the consumer market use the Mobile Industry Processor Interface (MIPI\*) Camera Serial Interface 2 (CSI-2) as a video signal interface. In some cases, the AP has to take multiple image data for various applications without increasing the physical interface signals.

The Lattice Semiconductor N Input to 1 Output MIPI CSI-2 Side-by-Side Aggregation reference design for CrossLink™ devices offers up to five-channel aggregation. Multiple channel image data are concatenated horizontally line by line. CrossLink has two MIPI hard macro IPs, which can be used as MIPI TX or RX module (D-PHY Hard IP). The RX module can also be realized by a soft macro utilizing general DDR modules (D-PHY Soft IP).

## 1.1. Supported Device and IP

This reference design supports the following devices with IP versions:

Table 1.1. Supported Device and IP

| Device Family  | Part Number              | Compatible IP                                                  |

|----------------|--------------------------|----------------------------------------------------------------|

| CrossLink      | LIF-MD6000<br>LIA-MD6000 | D-PHY Receiver IP version 1.4 D-PHY Transmitter IP version 1.3 |

| CrossLinkPlus™ | LIF-MDF6000              | D-PHT HallSillitter if Version 1.5                             |

Note: CrossLink refers to both CrossLink and CrossLinkPlus in this document unless noted.

#### 1.2. Features

- Two to five RX channels can be aggregated.

- One D-PHY Hard IP is used on TX channel.

- One Hard D-PHY IP is recommended to be used on RX Channel 0 to save FPGA resources.

- All RX channels must be in the same configuration.

- RX channels do not necessarily have to share the same clock source as long as their clock tolerance is within 500 ppm.

- All RX channels are expected to have almost same frame timing (20-pixel timing or less).

- RX channel can have one, two, or four lanes as long as the total number of RX clock and data lanes by RX D-PHY Soft IP does not exceed 15.

- Maximum RX bandwidth is 1.2 Gbps per lane.

- Number of TX lanes can be one, two, or four.

- Maximum TX bandwidth is 1.5 Gbps per lane.

- Non-continuous clock mode on RX channels is possible as long as the continuous clock can be obtained internally

or fed directly from the pin.

- External reference clock is required in case RX channels are in non-continuous clock mode.

## 1.3. Block Diagram

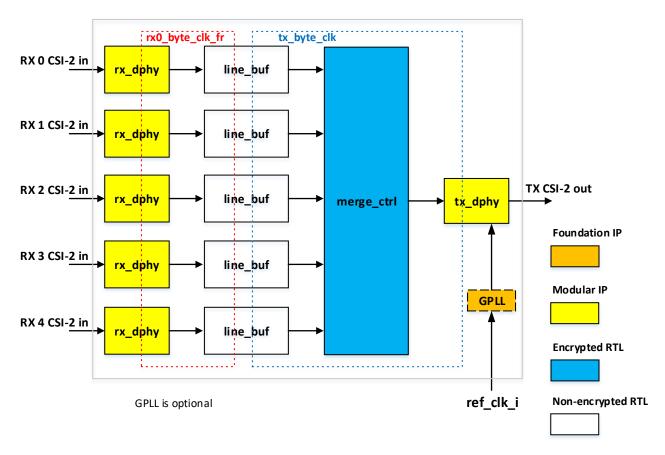

Figure 1.1 shows the block level diagram of the MIPI CSI-2 Side-by-Side Aggregation reference design with five RX channels.

Since TX D-PHY PLL has an input clock frequency requirement of between 24 MHz and 30 MHz (or a multiple of between 24 and 30 MHz), an on-chip GPLL may have to be used to create an appropriate clock.

Figure 1.1. MIPI CSI-2 Side-by-Side Aggregation Block Diagram

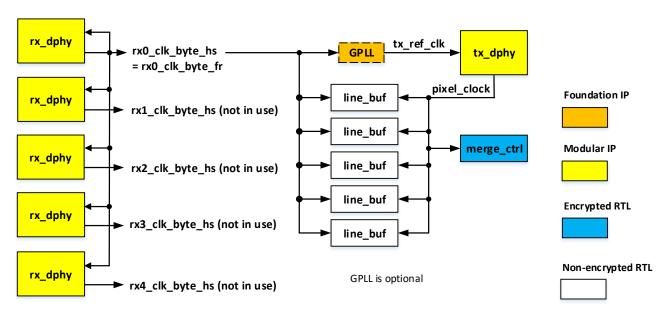

Figure 1.2 shows an example of clocking scheme in continuous clock mode. If continuous byte clock cannot be directly fed to tx\_dphy, using GPLL could be a solution.

Figure 1.2. Clocking Scheme Example in Continuous Clock Mode

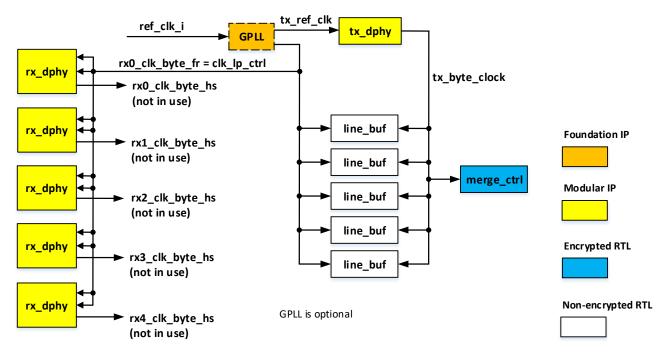

Figure 1.3 shows an example of clocking scheme in non-continuous clock mode. In this case, the external clock (ref\_clk\_i) is mandatory to generate both continuous byte clock and tx\_ref\_clk. GPLL may be bypassed if ref\_clk\_i is equal to rx0\_byte\_clk\_fr and TX D-PHY can create tx\_byte\_clk from this external reference clock.

Figure 1.3. Clocking Scheme Example in Non-Continuous Clock Mode

## 1.4. RX/TX Permutations and Parameter Calculation

Table 1.2 shows available permutations of RX and TX configurations. Due to the minimum lane bandwidth supported by D-PHY RX IP (160 Mbps) and number of differential I/O pairs (up to 15 differential I/O for Soft D-PHY RX), some permutations are not possible and grayed out in the table.

Table 1.2. RX and TX Permutation

| Number of RX<br>Channels | Number of RX Lanes | RX Lane Bandwidth<br>(Mbps) | Number of TX<br>Lanes | TX Lane Bandwidth/RX Lane Bandwidth |

|--------------------------|--------------------|-----------------------------|-----------------------|-------------------------------------|

|                          |                    | 160 - 750                   | 1                     | 2                                   |

|                          | 1                  | 160 -1200                   | 2                     | 1                                   |

|                          |                    | 160 - 1200                  | 4                     | 0.5                                 |

|                          |                    | 160 - 375                   | 1                     | 4                                   |

| 2                        | 2                  | 160 - 750                   | 2                     | 2                                   |

|                          |                    | 160 - 1200                  | 4                     | 1                                   |

|                          | 4                  | 160 - 187.5                 | 1                     | 8                                   |

|                          |                    | 160 - 375                   | 2                     | 4                                   |

|                          |                    | 160 - 750                   | 4                     | 2                                   |

|                          |                    | 160 - 500                   | 1                     | 3                                   |

|                          | 1                  | 160 - 1000                  | 2                     | 1.5                                 |

| 3                        |                    | 160 - 1200                  | 4                     | 0.75                                |

| 3                        | 3                  | 160 - 250                   | 1                     | 6                                   |

|                          | 2                  | 160 - 500                   | 2                     | 3                                   |

|                          |                    | 160 - 1000                  | 4                     | 1.5                                 |

| Number of RX<br>Channels | Number of RX Lanes | RX Lane Bandwidth<br>(Mbps) | Number of TX<br>Lanes | TX Lane Bandwidth/RX Lane Bandwidth |

|--------------------------|--------------------|-----------------------------|-----------------------|-------------------------------------|

|                          |                    | ≤ 125*                      | 1*                    | 12*                                 |

|                          | 4                  | 160 - 250                   | 2                     | 6                                   |

|                          |                    | 160 - 500                   | 4                     | 3                                   |

|                          |                    | 160 - 375                   | 1                     | 4                                   |

|                          | 1                  | 160 - 750                   | 2                     | 2                                   |

|                          |                    | 160 - 1200                  | 4                     | 1                                   |

|                          |                    | 160 - 187.5                 | 1                     | 8                                   |

| 4                        | 2                  | 160 - 375                   | 2                     | 4                                   |

|                          |                    | 160 - 750                   | 4                     | 2                                   |

|                          |                    | ≤ 93.75*                    | 1*                    | 16*                                 |

|                          | 4                  | 160 - 187.5                 | 2                     | 8                                   |

|                          |                    | 160 - 375                   | 4                     | 4                                   |

|                          |                    | 160 - 300                   | 1                     | 5                                   |

|                          | 1                  | 160 - 600                   | 2                     | 2.5                                 |

|                          |                    | 160 - 1200                  | 4                     | 1.25                                |

|                          |                    | ≤ 150*                      | 1*                    | 10*                                 |

| 5                        | 2                  | 160 - 300                   | 2                     | 5                                   |

|                          |                    | 160 - 600                   | 4                     | 2.5                                 |

|                          |                    | ≤ 75*                       | 1*                    | 20*                                 |

|                          | 4*                 | ≤ 150*                      | 2*                    | 10*                                 |

|                          |                    | 160 – 300*                  | 4*                    | 5*                                  |

\*Note: These permutations are not supported.

The Excel sheet (csi2\_aggregation\_ss\_param.xls) is provided to calculate the byte clock, number of channels, and other information. Also, some parameter values can be obtained from RX Data Type and horizontal pixel count. Figure 1.4 shows a sample entry of this sheet. In CSI-2, the amount of active video data per line must be a multiple of 8 bits and that sets some restrictions on horizontal pixel count according to RX Data Type. This amount shows up as Word Count in the sheet and as a byte count of active video data per line when you enter the Horizontal Pixel Count value. You must enter the correct Horizontal Pixel Count value so that Word Count has an integer value. Less common data types (for example, RGB555) are not covered by this sheet, but it is possible to support by manually entering the Word Count value in the sheet as long as the value is integer.

| N Input to 1 Output MIPI C | SI-2 Side-b | y-Side A | ggregation R | D Para | meter ( | alculator       |      |                 |             |

|----------------------------|-------------|----------|--------------|--------|---------|-----------------|------|-----------------|-------------|

|                            |             |          |              |        |         |                 |      |                 |             |

| RX Data Type               | RAW8        |          |              |        |         | Word Count      | 1004 | Word Count must | be an integ |

| Horizontal Pixel count     | 1004        |          |              |        |         |                 |      |                 |             |

| Number of RX Channels      | 4           |          | Set by us    | or     |         | RX0_POST_WRITE  | 2    |                 |             |

| Number of RX Lanes         | 2           |          | Jet by us    | ei     | CH#0    | RX0_POST_OFFSET | 4    |                 |             |

| RX Gear                    | 8           |          |              |        |         | RX0_EXT_R       | 0    |                 |             |

| RX Line Rate               | 240         | Mbps     | up to 1200   |        |         |                 |      |                 |             |

| RX DPHY Clock Frequency    | 120         | MHz/     |              |        |         | RX1_PRE_WRITE   | 2    |                 |             |

| RX Byte Clock Frequency    | 30          | MHz      |              |        |         | RX1_PRE_OFFSET  | 0    |                 |             |

| Number of TX Lanes         | 4           |          |              |        | CH#1    | RX1_POST_WRITE  | 0    |                 |             |

| TX Gear                    | 16          | Υ        |              |        |         | RX1_POST_OFFSET | 0    |                 |             |

| TX Line Rate (per lane)    | 480         | Mbps     | up to 1500   |        |         | RX1_EXT_R       | 0    |                 |             |

| TX DPHY Clock Frequency    | 240         | MHz      |              |        |         |                 |      |                 |             |

| TX Byte Clock Frequency    | 30          | MHz      |              |        |         | RX2_PRE_WRITE   | 0    |                 |             |

| no GPLL Required in case o | f RX_CLK_   | HS_ONLY  | ,            |        |         | RX2_PRE_OFFSET  | 0    |                 |             |

|                            |             |          |              |        | CH#2    | RX2_POST_WRITE  | 2    |                 |             |

|                            |             |          |              |        |         | RX2_POST_OFFSET | 4    |                 |             |

| RX Data Type of YUV420_8   | is Legacy Y | UV420 8- | bit format.  |        |         | RX2_EXT_R       | 0    |                 |             |

|                            |             |          |              |        |         |                 |      |                 |             |

|                            |             |          |              |        |         | RX3_PRE_WRITE   | 2    |                 |             |

|                            |             |          |              |        |         | RX3_PRE_OFFSET  | 0    |                 |             |

|                            |             |          |              |        | CH#3    | RX3_POST_WRITE  | 0    |                 |             |

|                            |             |          |              |        |         | RX3_POST_OFFSET | 0    |                 |             |

|                            |             |          |              |        |         | RX3_EXT_R       | 0    |                 |             |

|                            |             |          |              |        |         |                 |      |                 |             |

|                            |             |          |              |        |         | RX4_PRE_WRITE   | 0    |                 |             |

|                            |             |          |              |        | CH#4    | RX4_PRE_OFFSET  | 0    | always 0        |             |

|                            |             |          |              |        |         | RX4_POST_WRITE  | 2    |                 |             |

|                            |             |          |              |        |         | RX4_EXT_R       | 0    |                 |             |

Figure 1.4. Bandwidth and Parameter Calculator

## 2. Parameters and Port List

There are two directive files for this reference design:

- synthesis\_directives.v used for design compilation by Lattice Diamond® and for simulation.

- simulation\_directives.v used for simulation.

You can modify these directives according to your own configuration. The settings in these files must match RX D-PHY IP, TX D-PHY IP, and other module settings described in the Design and Module Description section.

## 2.1. Synthesis Directives

Table 2.1 shows the synthesis directives that affect this reference design. These are used for both synthesis and simulation. As shown in Table 2.1 and Table 2.2, some parameter selections are restricted by other parameter settings.

**Table 2.1. Synthesis Directives**

| Category                   | Directive           | Remarks                                                                                                                            |

|----------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Frame Sync Output          | FS_OUT              | Enable to output Frame Sync Pulse when defined.                                                                                    |

| Frame Sync Interval        | FS_INTERVAL {value} | Interval period of Frame Sync in ref_clk_i cycles. Effective when FS_OUT is defined. Value must be equal or less than 20'd1048575. |

| Frame Sync Pulse<br>Length | FS_LENGTH {value}   | Pulse width of Frame Sync in ref_clk_i cycles. Effective when FS_OUT is defined. Value must be 8'd1 – 8'd255.                      |

| Farance Come Bellevite     | FS_POL_POS          | Polarity of Frame Sync Pulse. Effective when FS_OUT is defined. Only                                                               |

| Frame Sync Polarity        | FS_POL_NEG          | one of these two directives must be defined.                                                                                       |

|                            | RAW8                |                                                                                                                                    |

|                            | RAW10               |                                                                                                                                    |

|                            | RAW12               |                                                                                                                                    |

|                            | RAW14               |                                                                                                                                    |

| Data Type                  | RGB888              | Data Type of the payload video data. Only one of these nine directives must be defined.                                            |

|                            | RGB666              | must be defined.                                                                                                                   |

|                            | RGB565              |                                                                                                                                    |

|                            | YUV422_8            |                                                                                                                                    |

|                            | YUV422_10           |                                                                                                                                    |

|                            | NUM_RX_CH_2         |                                                                                                                                    |

| RX Channel Count           | NUM_RX_CH_3         | Number of RX channels aggregated. Only one of these four directives                                                                |

| KX Chamiler Count          | NUM_RX_CH_4         | must be defined.                                                                                                                   |

|                            | NUM_RX_CH_5         |                                                                                                                                    |

| RX Channel Lane            | NUM_RX_LANE_1       | Number of lance in each BV channel. Only one of these three directives                                                             |

| Count                      | NUM_RX_LANE_2       | Number of lanes in each RX channel. Only one of these three directives must be defined.                                            |

| Count                      | NUM_RX_LANE_4       | mast be defined.                                                                                                                   |

| RX D-PHY Clock Gear        | RX_GEAR_8           | Only one of these directives must be selected. Gear 16 can be used for                                                             |

| KX D-FITT Clock Geal       | RX_GEAR_16          | only 1- and 2-lane configurations.                                                                                                 |

|                            | RXO_DPHY_HARD       |                                                                                                                                    |

| RX Hard D-PHY              | RX1_DPHY_HARD       | Specify RX channel that uses Hard D-PHY. Only one of these five                                                                    |

| Channel                    | RX2_DPHY_HARD       | directives can be defined. If none of these is defined, all RX channels use                                                        |

| Chamici                    | RX3_DPHY_HARD       | Soft D-PHY (up to four channels).                                                                                                  |

|                            | RX4_DPHY_HARD       |                                                                                                                                    |

| Category                              | Directive                   | Remarks                                                                                                                                                                   |

|---------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX D-PHY Clock                        | RX_CLK_MODE_HS_ONLY         | RX D-PHY Clock mode. Only one of these two directives must be defined.                                                                                                    |

| Mode <sup>1</sup>                     | RX_CLK_MODE_HS_LP           | TAX D-PHT Clock fillode. Offly offe of these two directives fillust be defined.                                                                                           |

| Use GPLL                              | USE_GPLL                    | Use GPLL to create a reference clock to be fed to PLL of TX D-PHY IP.                                                                                                     |

| Hard D-PHY Word<br>Alignment          | WORD_ALIGN                  | Enable word aligner in RX Hard D-PHY IP. Ignored when Hard D-PHY is not used.                                                                                             |

|                                       | RX0_BUF_SIZE_*              | RX channel 0 FIFO buffer size in byte. * must be 1024, 2048, 4096, or 8192.                                                                                               |

| RX Buffer Size <sup>2</sup>           | RX1_BUF_SIZE_*              | RX channel 1 FIFO buffer size in byte. * must be 1024, 2048, 4096, or 8192.                                                                                               |

| IX Duller Size                        | RX2_BUF_SIZE_*              | RX channel 2 FIFO buffer size in byte. * must be 1024, 2048, or 4096.                                                                                                     |

|                                       | RX3_BUF_SIZE_*              | RX channel 3 FIFO buffer size in byte. * must be 1024, 2048, or 4096.                                                                                                     |

|                                       | RX4_BUF_SIZE_*              | RX channel 4 FIFO buffer size in byte. * must be 1024, 2048, or 4096.                                                                                                     |

|                                       | RX1_PRE_WRITE {value}       | Pre-write cycle count to RX channel 1 FIFO buffer. Value must be 0 – 7.                                                                                                   |

| RX Buffer Pre-Write <sup>3</sup>      | RX2_PRE_WRITE {value}       | Pre-write cycle count to RX channel 2 FIFO buffer. Value must be 0, 2, 4, or 6.                                                                                           |

|                                       | RX3_PRE_WRITE {value}       | Pre-write cycle count to RX channel 3 FIFO buffer. Value must be 0 – 7.                                                                                                   |

|                                       | RX4_PRE_WRITE {value}       | Pre-write cycle count to RX channel 4 FIFO buffer. Value must be 0 or 4.                                                                                                  |

|                                       | RX1_PRE_OFFSET {value}      | Pre-offset byte count to RX channel 1 FIFO buffer. Value must be $0-3$ .                                                                                                  |

| RX Buffer Pre-Offset <sup>3</sup>     | RX2_PRE_OFFSET {value}      | Pre-offset byte count to RX channel 2 FIFO buffer. Value must be 0 or 2.                                                                                                  |

|                                       | RX3_PRE_OFFSET {value}      | Pre-offset byte count to RX channel 3 FIFO buffer. Value must be 0 – 3.                                                                                                   |

|                                       | RX0_POST_WRITE {value}      | Post-write cycle count to RX channel 0 FIFO buffer. Value must be $0-7$ .                                                                                                 |

|                                       | RX1_POST_WRITE {value}      | Post-write cycle count to RX channel 1 FIFO buffer. Value must be $0-7$ .                                                                                                 |

| RX Buffer Post-Write <sup>3</sup>     | RX2_POST_WRITE {value}      | Post-write cycle count to RX channel 2 FIFO buffer. Value must be 0, 2, 4, or 6.                                                                                          |

|                                       | RX3_POST_WRITE {value}      | Post-write cycle count to RX channel 3 FIFO buffer. Value must be 0 or 4.                                                                                                 |

|                                       | RX4_POST_WRITE {value}      | Post-write cycle count to RX channel 4 FIFO buffer. Value must be 0 - 7.                                                                                                  |

|                                       | RX0_POST_OFFSET {value}     | Post-offset byte count to RX channel 0 FIFO buffer. Value must be $0-7$ .                                                                                                 |

| RX Buffer Post-Offset <sup>3</sup>    | RX1_POST_OFFSET {value}     | Post-offset byte count to RX channel 1 FIFO buffer. Value must be 0, 2, 4, or 6.                                                                                          |

|                                       | RX2_POST_OFFSET {value}     | Post-offset byte count to RX channel 2 FIFO buffer. Value must be 0 - 7.                                                                                                  |

|                                       | RX3_POST_OFFSET {value}     | Post-offset byte count to RX channel 3 FIFO buffer. Value must be 0 or 4.                                                                                                 |

|                                       | RX0 EXT R {value}           | Extra Read Flag for RX channel 0 FIFO Buffer. Value must be 0 or 1.                                                                                                       |

|                                       | RX1_EXT_R {value}           | Extra Read Flag for RX channel 1 FIFO Buffer. Value must be 0 or 1.                                                                                                       |

| RX Buffer Extra Read <sup>3</sup>     | RX2_EXT_R {value}           | Extra Read Flag for RX channel 2 FIFO Buffer. Value must be 0 or 1.                                                                                                       |

|                                       | RX3_EXT_R {value}           | Extra Read Flag for RX channel 3 FIFO Buffer. Value must be 0 or 1.                                                                                                       |

|                                       | RX4_EXT_R {value}           | Extra Read Flag for RX channel 4 FIFO Buffer. Value must be 0 or 1.                                                                                                       |

| Long Packet Transfer<br>Request Delay | LP_TX_REQ_DLY {value}       | Long Packet Transfer Request Delay Time in tx_byte_clk cycles. Value must be 1 – 4095. Automatically calculated value is used if not defined.                             |

| Virtual Channel ID                    | VC {value}                  | Refer to Line Buffer Read and Data Merge Operation section for details.  Virtual Channel ID. Value must be 2'd0 – 2'd3. The value on RX channel 0 is used if not defined. |

|                                       | NUM TX LANE 1               |                                                                                                                                                                           |

| TX channel lane count                 | NUM_TX_LANE_2 NUM_TX_LANE_4 | Number of lanes in TX channel. Only one of these three directives must be defined.                                                                                        |

| TX D-PHY Clock Gear                   | TX_GEAR_8  TX GEAR 16       | TX D-PHY Clock Gear. Only one of these two directives must be defined.                                                                                                    |

| Category                         | Directive           | Remarks                                                                                                                                                |

|----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX D-PHY Clock Mode <sup>4</sup> | TX_CLK_MODE_HS_ONLY |                                                                                                                                                        |

| TX D-PHY Clock Wlode             | TX_CLK_MODE_HS_LP   | TX D-PHY Clock mode. Only one of these two directives must be defined.                                                                                 |

| TX Lane Bandwidth                | TX_LANE_BW {value}  | TX D-PHY Lane Bandwidth in Mbps. Effective when TX_CLK_MODE_HS_LP is defined.                                                                          |

| Keep HS mode                     | KEEP_HS             | Keep the clock lane in HS mode during the horizontal blanking periods of active video lines when defined. Effective when TX_CLK_MODE_HS_LP is defined. |

#### Notes:

- 1. HS\_LP mode means *non-continuous clock mode* and HS\_ONLY means *continuous clock mode*. HS\_LP mode works only if RX byte clock can be obtained directly or indirectly from the external clock.

- This value affects necessary EBR used in the device. Total number of EBR must not exceed 20. Refer to line\_buf section for details

- 3. These parameter values are obtained by the provided Excel sheet as shown in Figure 1.4.

- 4. HS\_LP mode means *non-continuous clock mode* and HS\_ONLY means *continuous clock mode*. This mode does not have to be same as RX D-PHY Clock Mode.

## 2.2. Simulation Directives

Table 2.2 shows the simulation directives for this reference design.

**Table 2.2. Simulation Directives**

| Category                                                            | Directive                   | Remarks                                                                                                         |

|---------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

| Simulation                                                          | SIM                         | Select behavioral models for simulation.                                                                        |

| Reference clock period                                              | REF_CLK_PERIOD {value}      | Reference clock period in ps                                                                                    |

|                                                                     | RXO_DPHY_CLK_PERIOD {value} | RX Channel 0 DPHY clock period in ps                                                                            |

|                                                                     | RX1_DPHY_CLK_PERIOD {value} | RX Channel 1 DPHY clock period in ps                                                                            |

| RX D-PHY clock period                                               | RX2_DPHY_CLK_PERIOD {value} | RX Channel 2 DPHY clock period in ps                                                                            |

|                                                                     | RX3_DPHY_CLK_PERIOD {value} | RX Channel 3 DPHY clock period in ps                                                                            |

|                                                                     | RX4_DPHY_CLK_PERIOD {value} | RX Channel 4 DPHY clock period in ps                                                                            |

|                                                                     | CH0_DELAY {value}           | Initial delay to activate RX Channel 0 in ps                                                                    |

|                                                                     | CH1_DELAY {value}           | Initial delay to activate RX Channel 1 in ps                                                                    |

| Initial delay on RX channel                                         | CH2_DELAY {value}           | Initial delay to activate RX Channel 2 in ps                                                                    |

|                                                                     | CH3_DELAY {value}           | Initial delay to activate RX Channel 3 in ps                                                                    |

|                                                                     | CH4_DELAY {value}           | Initial delay to activate RX Channel 4 in ps                                                                    |

| Gap (LP) time between active lines on RX Channel                    | RX_DPHY_LPS_GAP {value}     | Horizontal Blanking Gap time on RX Channels in ps                                                               |

| Gap (LP) time between<br>Frame End and Frame Start<br>on RX Channel | RX_DPHY_FRAME_GAP {value}   | Vertical Blanking Gap time on RX Channels in ps                                                                 |

| RX Channel 0 VC                                                     | RXO_VC {value}              | Virtual Channel ID on RX Channel 0. The value must be 4'd0 – 4'd3. The same values are used on all RX channels. |

| Video data configuration on                                         | NUM_FRAMES {value}          | Number of frames to feed                                                                                        |

| RX Channels                                                         | NUM_LINES {value}           | Number of active lines per frame                                                                                |

| Internal signal monitoring                                          | MISC_ON                     | Enables internal signals to be monitored by the testbench. Always enable this directive.                        |

## 2.3. Top-Level I/O

Table 2.3 shows the top-level I/O of this reference design. Actual I/O depend on the customer's channel and lane configurations. All necessary I/O ports are automatically declared by compiler directives.

Table 2.3. CSI-2 Side-by-Side Aggregation Top-Level I/O

| Port Name        | Direction | Description                                                                                        |  |  |  |

|------------------|-----------|----------------------------------------------------------------------------------------------------|--|--|--|

| Clocks and Rese  | ets       |                                                                                                    |  |  |  |

| ref_clk_i        | I         | I Input reference clock. Used to feed a clock to TX D-PHY PLL directly or indirectly. This port is |  |  |  |

| (optional)       |           | declared only when RX_CLK_MODE_HS_LP or FS_OUT is defined in synthesis_directive                   |  |  |  |

| reset_n_i        | 1         | Asynchronous active low system reset                                                               |  |  |  |

| CSI-2 RX Interfa | ice       |                                                                                                    |  |  |  |

| fs_o (optional)  | 0         | Frame Sync. Only declared when FS_OUT is defined in synthesis_directives.v.                        |  |  |  |

| rx0_clk_p_i      | 1         | Positive differential RX Ch0 D-PHY input clock                                                     |  |  |  |

| rx0_clk_n_i      | I         | Negative differential RX Ch0 D-PHY input clock                                                     |  |  |  |

| rx0_d0_p_i       | I         | Positive differential RX Ch0 D-PHY input data 0                                                    |  |  |  |

| rx0_d0_n_i       | 1         | Negative differential RX Ch0 D-PHY input data 0                                                    |  |  |  |

| rx0_d1_p_i       | 1         | Positive differential RX Ch0 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx0_d1_n_i       | 1         | Negative differential RX Ch0 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx0_d2_p_i       | I         | Positive differential RX Ch0 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| rx0_d2_n_i       | 1         | Negative differential RX Ch0 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| rx0_d3_p_i       | I         | Positive differential RX Ch0 D-PHY input data 3 (in case of 4-lane configuration)                  |  |  |  |

| rx0_d3_n_i       | I         | Negative differential RX Ch0 D-PHY input data 3 (in case of 4-lane configuration)                  |  |  |  |

| rx1_clk_p_i      | I         | Positive differential RX Ch1 D-PHY input clock                                                     |  |  |  |

| rx1_clk_n_i      | I         | Negative differential RX Ch1 D-PHY input clock                                                     |  |  |  |

| rx1_d0_p_i       | I         | Positive differential RX Ch1 D-PHY input data 0                                                    |  |  |  |

| rx1_d0_n_i       | I         | Negative differential RX Ch1 D-PHY input data 0                                                    |  |  |  |

| rx1_d1_p_i       | I         | Positive differential RX Ch1 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx1_d1_n_i       | I         | Negative differential RX Ch1 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx1_d2_p_i       | I         | Positive differential RX Ch1 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| rx1_d2_n_i       | I         | Negative differential RX Ch1 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| rx1_d3_p_i       | I         | Positive differential RX Ch1 D-PHY input data 3 (in case of 4-lane configuration)                  |  |  |  |

| rx1_d3_n_i       | I         | Negative differential RX Ch1 D-PHY input data 3 (in case of 4-lane configuration)                  |  |  |  |

| rx2_clk_p_i      | I         | Positive differential RX Ch2 D-PHY input clock                                                     |  |  |  |

| rx2_clk_n_i      | I         | Negative differential RX Ch2 D-PHY input clock                                                     |  |  |  |

| rx2_d0_p_i       | I         | Positive differential RX Ch2 D-PHY input data 0                                                    |  |  |  |

| rx2_d0_n_i       | I         | Negative differential RX Ch2 D-PHY input data 0                                                    |  |  |  |

| rx2_d1_p_i       | I         | Positive differential RX Ch2 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx2_d1_n_i       | I         | Negative differential RX Ch2 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx2_d2_p_i       | I         | Positive differential RX Ch2 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| rx2_d2_n_i       | I         | Negative differential RX Ch2 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| rx2_d3_p_i       | I         | Positive differential RX Ch2 D-PHY input data 3 (in case of 4-lane configuration)                  |  |  |  |

| <br>rx2_d3_n_i   | ı         | Negative differential RX Ch2 D-PHY input data 3 (in case of 4-lane configuration)                  |  |  |  |

| <br>rx3_clk_p_i  | ı         | Positive differential RX Ch3 D-PHY input clock                                                     |  |  |  |

| <br>rx3_clk_n_i  | ı         | Negative differential RX Ch3 D-PHY input clock                                                     |  |  |  |

| <br>rx3_d0_p_i   | ı         | Positive differential RX Ch3 D-PHY input data 0                                                    |  |  |  |

| rx3_d0_n_i       | ı         | Negative differential RX Ch3 D-PHY input data 0                                                    |  |  |  |

| <br>rx3_d1_p_i   | ı         | Positive differential RX Ch3 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx3_d1_n_i       | ı         | Negative differential RX Ch3 D-PHY input data 1 (in case of 2-lane or 4-lane configuration)        |  |  |  |

| rx3_d2_p_i       |           | Positive differential RX Ch3 D-PHY input data 2 (in case of 4-lane configuration)                  |  |  |  |

| Port Name        | Direction | Description                                                                                 |  |  |

|------------------|-----------|---------------------------------------------------------------------------------------------|--|--|

| rx3_d2_n_i       | 1         | Negative differential RX Ch3 D-PHY input data 2 (in case of 4 lane configuration)           |  |  |

| rx3_d3_p_i       | I         | Positive differential RX Ch3 D-PHY input data 3 (in case of 4 lane configuration)           |  |  |

| rx3_d3_n_i       | I         | Negative differential RX Ch3 D-PHY input data 3 (in case of 4 lane configuration)           |  |  |

| rx4_clk_p_i      | I         | Positive differential RX Ch4 D-PHY input clock                                              |  |  |

| rx4_clk_n_i      | I         | Negative differential RX Ch4 D-PHY input clock                                              |  |  |

| rx4_d0_p_i       | I         | Positive differential RX Ch4 D-PHY input data 0                                             |  |  |

| rx4_d0_n_i       | I         | Negative differential RX Ch4 D-PHY input data 0                                             |  |  |

| rx4_d1_p_i       | I         | Positive differential RX Ch4 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |

| rx4_d1_n_i       | I         | Negative differential RX Ch4 D-PHY input data 1 (in case of 2-lane or 4-lane configuration) |  |  |

| rx4_d2_p_i       | I         | Positive differential RX Ch4 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |

| rx4_d2_n_i       | I         | Negative differential RX Ch4 D-PHY input data 2 (in case of 4-lane configuration)           |  |  |

| rx4_d3_p_i       | I         | Positive differential RX Ch4 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |

| rx4_d3_n_i       | I         | Negative differential RX Ch4 D-PHY input data 3 (in case of 4-lane configuration)           |  |  |

| CSI-2 TX Interfa | ce        |                                                                                             |  |  |

| tx_clk_p_o       | 0         | Positive differential TX D-PHY output clock                                                 |  |  |

| tx_clk_n_o       | 0         | Negative differential TX D-PHY output clock                                                 |  |  |

| tx_d0_p_o        | 0         | Positive differential TX D-PHY output data 0                                                |  |  |

| tx_d0_n_o        | 0         | Negative differential TX D-PHY output data 0                                                |  |  |

| tx_d1_p_o        | 0         | Positive differential TX D-PHY output data 1 (in case of 2-lane or 4-lane configuration)    |  |  |

| tx_d1_n_o        | 0         | Negative differential TX D-PHY output data 1 (in case of 2-lane or 4-lane configuration)    |  |  |

| tx_d2_p_o        | 0         | Positive differential TX D-PHY output data 2 (in case of 4-lane configuration)              |  |  |

| tx_d2_n_o        | 0         | Negative differential TX D-PHY output data 2 (in case of 4-lane configuration)              |  |  |

| tx_d3_p_o        | 0         | Positive differential TX D-PHY output data 3 (in case of 4-lane configuration)              |  |  |

| tx_d3_n_o        | 0         | Negative differential TX D-PHY output data 3 (in case of 4-lane configuration)              |  |  |

## 3. Design and Module Description

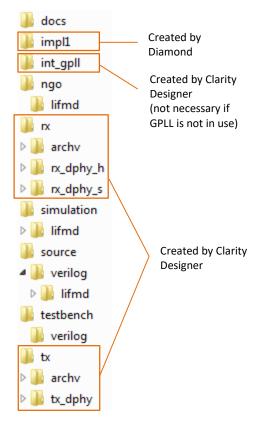

The top-level design (csi2\_aggregation\_ss.v) consists of the following modules:

- rx\_dphy (rx\_dphy\_h / rx\_dphy\_s)

- line buf

- merge\_ctrl

- tx dphy

The top-level design has a reset synchronization logic. In addition, GPLL may be added if necessary according to RX and TX configurations. When FS\_OUT is defined, Frame Sync pulse (fs\_o) is generated. This could be useful to give the frame timing synchronization to multiple camera sensors.

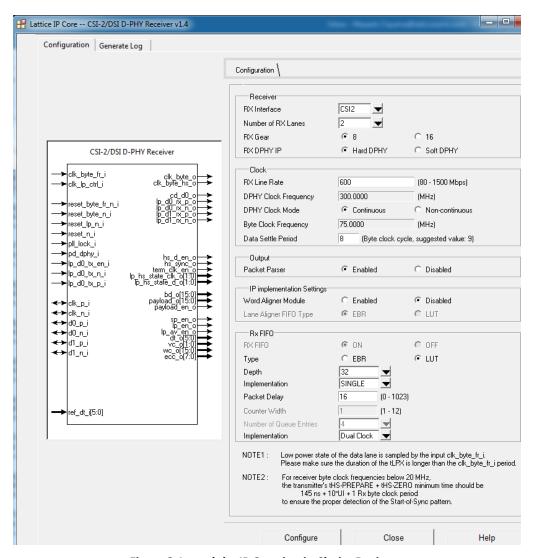

## 3.1. rx\_dphy

Since all RX channels must be in the same configuration, a single module can cover all RX channels when Hard D-PHY is not in use. Assuming one of RX channels uses a Hard D-PHY IP, two modules are considered; rx\_dphy\_h for Hard D-PHY RX IP and rx\_dphy\_s for Soft D-PHY RX IP. Figure 3.1 shows an example of IP interface settings in Clarity for the CSI-2/DSI D-PHY Receiver Submodule IP. Refer to CSI-2/DSI D-PHY Receiver Submodule IP User Guide (FPGA-IPUG-02025) for details.

Figure 3.1. rx\_dphy IP Creation in Clarity Designer

The following shows guidelines and parameter settings required for this reference design.

- RX Interface Select CSI-2.

- Number of RX Lanes Set according to channel configuration. The value must match NUM RX LANE \* setting.

- RX Gear Select 8 or 16; 16 is supported for 1-lane and 2-lane configurations only. 16 is recommended when the RX byte clock speed exceeds 100 MHz or STA fails with Gear 8.

- RX D-PHY IP Hard D-PHY can be selected only for one RX channel, others must be Soft D-PHY. The setting must match RX\*\_D-PHY\_HARD setting.

- RX Line Rate Set according to channel configuration. Must be 750 or below for 4 lane configuration.

- D-PHY Clock Mode Select Continuous or Non-continuous. Must match RX\_CLK\_MODE\_\* setting (Continuous = HS\_ONLY, Non-continuous = HS\_LP).

- Data Settle Period Enter the suggested value. You can try decreasing this value one by one when RX D-PHY is not operating properly.

- Packet Parser Select Enabled.

- Word Aligner Module Select Enabled in case of Hard D-PHY in high-temperature condition (ambient temperature > 125 °C). Automatically enabled for Soft D-PHY.

- Lane Aligner Module LUT or EBR for 2 and 4 lane configuration. LUT is highly recommended.

Refer to RX FIFO section for RX FIFO related settings.

This module takes serial CSI-2 data and outputs byte data after de-serialization in CSI-2 High Speed mode. It is recommended to set the design name to *rx* and module names to *rx\_dphy\_h* and *rx\_dphy\_s* so that you do not need to modify the instance names of these IPs in the top-level design as well as the simulation setup file. Otherwise, you have to modify the names accordingly.

RX Gear 16 is supported for only 1-lane and 2-lane configurations.

Data Settle Period determines when this module begin hunting SoT (start of Transmission) code (0xB8) on each lane after LP to HS transition is detected. The suggested value is around the middle of the allowable timing range defined by MIPI D-PHY specification so that this module does not work properly when SoT begins earlier than the timing obtained by this parameter. Therefore, reducing this value is one of the option you can try when this module is not working.

#### 3.1.1. RX FIFO

RX FIFO is useful especially in non-continuous clock mode and the continuous byte clock cannot have the exactly same frequency as the non-continuous byte clock used in D-PHY RX IP. It resides after the word aligner in case of Hard D-PHY RX IP and resides before the word aligner in case of Soft D-PHY RX IP.

#### 3.1.1.1. Hard D-PHY in Continuous Clock Mode

In this case, the minimum configuration of RX FIFO is recommended (LUT based, Depth = 16, *Type* Implementation = SINGLE, Packet Delay = 1, *Clock* Implementation = Dual Clock).

#### 3.1.1.2. Soft D-PHY in Continuous Clock Mode

In this case, RX FIFO is not necessary and can be set to OFF when the read clock is the same as write clock. In this application, read clocks on RX channels are often unified and the read clock might come from different RX channels even though the frequency is same. In such cases, LUT based RX FIFO must be used with Depth = 16, *Type* Implementation = SINGLE, Packet Delay = 1, Clock Implementation = Dual Clock.

#### 3.1.1.3. Non-Continuous Clock Mode

In this case, RX FIFO configuration depends on the relationship between the non-continuous byte clock in D-PHY RX IP and the continuous byte clock, which is most likely generated by GPLL. The non-continuous byte clock is used to write the data to RX FIFO and the continuous byte clock is used to read the data from RX FIFO.

- Continuous byte clock = non-continuous byte clock

In this case, the minimum configuration of RX FIFO is recommended (LUT based, Depth = 16, Type Implementation = SINGLE, Packet Delay = 1, Clock Implementation = Dual Clock).

- Continuous byte clock < non-continuous byte clock</li>

In this case, *Type* Implementation = SINGLE and Packet Delay = 1 is recommended and others depend on the frequency ratio between these two clocks. When the clock speed difference gets larger, the required depth of RX FIFO gets larger. First, it is important to know the horizontal blanking period of the incoming RX channel. For example, in case that one-line active video period is 40  $\mu$ s and the horizontal blanking is 4  $\mu$ s, then we have 10 % of extra time to process the active data. This means the continuous byte clock can be as slow as ~-10% comparing to the non-continuous byte clock to avoid RX FIFO overflow.

Continuous byte clock > non-continuous byte clock

There are two options in this case:

- Use Type Implementation = SINGLE with large Packet Delay

Set the Depth large enough to contain the necessary data to avoid RX FIFO underflow after FIFO read begins after the time specified by Packet Delay. In general, Packet Delay must be set close the depth of the RX FIFO. This configuration can be used when we have enough time interval between the last active line and the frame end short packet so that the frame end short packet is not written to RX FIFO while it still contains the last active line of video data.

- Use Type Implementation = QUEUE with Number of Queue Entries = 2

This is useful when the time interval between the last active line and frame end short packet is short or unknown. Depth must be set large enough to contain one active line data (plus some more for short packet data). This mode is also useful when line start and the line end short packets exist in the incoming RX stream. In this case, Number of Queue Entries = 4 and extra depth is required (one line plus two short packet data). FIFO read begins after each HS data transaction is completed. EBR must be used. Counter Width is determined by the amount of the one-line video data plus extra overheads by preceding HS zero data and trail byte in the end of HS transmission.

#### Frequency relationship is unknown

When the continuous byte clock is within the certain range against the non-continuous byte clock (for example, two clocks come from different clock sources which have ppm tolerance), we have no idea which clock is faster. The simplest way is to use *Type* Implementation = SINGLE with setting Packet Delay to the midpoint of FIFO depth when the tolerance is in ppm level. For example, assuming the clock tolerance is within +/- 500ppm for 2 lane Gear 8 RAW10 with 1920 horizontal pixels. The payload byte count is  $1920 \times 5/4 = 2400$  so that each lane takes 1200 bytes.  $1200 \times 500$  ppm = 0.6, which means small FIFO with middle point read delay (for example, FIFO depth = 16 with read delay of 8-byte clock cycles) works fine. Using LUT is preferable as long as FIFO depth is small since using EBR here might cause the shortage of EBR in line\_buf modules. QUEUE can also be used as described above even though it requires more EBR.

In case you do not have detailed information regarding RX data (whether containing line start/end short packet, interval of the horizontal blanking period against active line period), the safest way is to set the continuous byte clock faster than the non-continuous byte clock. You may use *Type* Implementation = QUEUE with Number of Queue Entries = 4, even though it may require more EBR resources comparing to *Type* Implementation = SINGLE. You have to make sure that total number of EBR used in the device does not exceed 20.

#### 3.2. line buf

This module is instantiated for each RX channel. It contains a dual clock FIFO to store payload data of active video lines. Data write is based on RX byte clock and data read is based on TX byte clock for merging. Data widths of write and read sides depend on bus width of RX and TX side respectively, which means bus widths could be different. Several things have to be considered regarding FIFO operation.

#### 3.2.1. Buffer Size

The required buffer size is obtained as shown below:

$$Buffer\,Size[CH\ \#n]\cong \frac{(N+n-1)}{N}*(Payload\ byte\ count\ per\ line)\ bytes,$$

where n is a channel number (0 to 4) and N is a number of RX channels (2 to 5).

© 2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

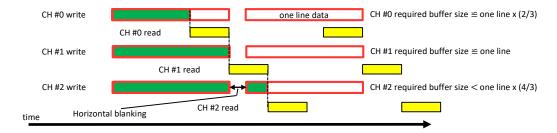

The above equation shows that the required buffer size for the first channel is less than 1-line data, the one for the second channel equals to 1-line data and rests are between 1 line and 2 line data. Required sizes for third and later channels are substantially smaller than the above calculated values due to the existence of horizontal blanking period. Figure 3.2 shows an example of brief buffer write and read timings in case of 3-channel aggregation.

Figure 3.2. Buffer Size and Brief Write/Read Timings

On the other hand, the minimum count of EBR (Embedded Block RAM) to form the FIFO depends on the wider bus width between RX and TX, where bus width is derived by (lane count) x Gear. Table 3.1 shows the relationship between RX/TX bus width and unit count of EBR and payload byte count. The number of EBR per RX channel is a multiple of the unit count shown in Table 3.1.

Table 3.1. Unit EBR and Payload Byte Count of RX Buffer

| RX Bus Width | TX Bus Width | Unit EBR Count | Unit Payload Byte Count |  |  |

|--------------|--------------|----------------|-------------------------|--|--|

|              | 8            | 1              | 1024                    |  |  |

| 0            | 16           | 1              | 1024                    |  |  |

| 8            | 32           | 2              | 2048                    |  |  |

|              | 64           | 4              | 4096                    |  |  |

|              | 8            | 1              | 1024                    |  |  |

| 16           | 16           | 1              | 1024                    |  |  |

| 16           | 32           | 2              | 2048                    |  |  |

|              | 64           | 4              | 4096                    |  |  |

|              | 8*           | 2*             | 2048*                   |  |  |

| 22           | 16           | 2              | 2048                    |  |  |

| 32           | 32           | 2              | 2048                    |  |  |

|              | 64           | 4              | 4096                    |  |  |

\*Note: This permutation does not exist.

Example: In case of 4 RX Channels with 2 lane, Gear 8, RAW10, 1920 pixels per line to TX with 4 lane, Gear 8:

Required RX Buffer Size [CH #0] =  $(4+0-1)/4 \times (1920 \times 10/8) = 1800$  bytes,

Required RX Buffer Size [CH #1] =  $(4+1-1)/4 \times (1920 \times 10/8) = 2400$  bytes,

Required RX Buffer Size [CH #2] =  $(4+2-1)/4 \times (1920 \times 10/8) = 3000$  bytes,

Required RX Buffer Size [CH #3] =  $(4+3-1)/4 \times (1920 \times 10/8) = 3600$  bytes.

Unit EBR count = 2, unit payload byte count = 2048.

Therefore, CH#0 requires 2 EBR and CH#1 – CH#3 require 4 EBR, which means 14 EBR are required in total.

Note that the total number of EBR cannot exceed 20 (assuming no EBR is used in rx\_dphy modules). Since the buffer read timing might vary depending on TX side status, it might be safe to raise the buffer size in case that the required buffer size is close to the byte count you get from the above table. For example, if the pixel count is changed from 1920 to 2180 in the above example, the required RX Buffer size of CH#3 changes to 4087.5 bytes, which is closer to 4096 bytes using 4 EBR and it might be better to raise the buffer size. On the other hand, if the horizontal blanking is long enough, it is possible to handle larger payload byte count by the EBR, which can contain less number of byte than the value obtained by the equation shown above. For these reasons, the values specified by RX\*BUF\_SIZE\* you can get from the above equation are reference only and you need to determine the actual values.

FPGA-RD-02192-1.0 21

© 2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

#### 3.2.2. RX Buffer Offset Control

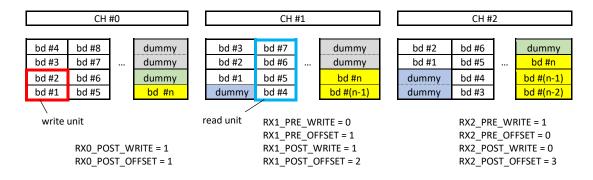

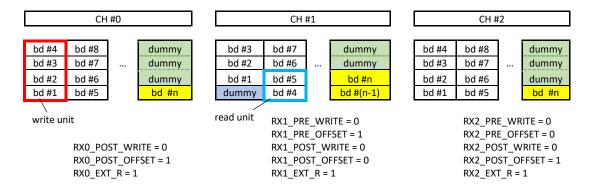

In case that the payload byte count does not match a multiple of RX bus width and/or TX bus width in the unit of byte, some considerations are necessary regarding RX buffer write and read. Figure 3.3 shows an example of (RX bus width) < (TX bus width). If WC (payload byte count) is not a multiple of TX bus width, RX side has to write some dummy data to the FIFO, otherwise the final data cannot read out from TX side. In this example, in the end of CH #0 data write transaction, bd #n is written to the FIFO with dummy data. Also, one extra dummy write cycle is necessary (RXO\_POST\_WRITE = 1) to make this data readable from TX side. The amount of the residual byte info (RXO\_POST\_OFFSET = 1) is used by merge\_ctrl module to make a proper concatenation of the previous channel data and the current channel data. In the beginning of the write transaction of CH #1, the write data has to be shifted according to the offset info (RX1\_PRE\_OFFSET = 1). This makes the concatenation process easier on TX side by merge\_ctrl. In the beginning of the write transaction of CH #2, one dummy write cycle is necessary (RX2\_PRE\_WRITE = 1) to make a necessary data shift since the offset in the end of previous channel write (RX1\_POST\_OFFSET = 2) is equal to the RX bus width. Figure 3.4 shows another example. In this case, RX\*\_PRE\_OFFSET is always 0 and RX\*\_POST\_OFFSET of the current channel always equals to RX\*\_PRE\_WRITE of the next channel since RX bus width = 8.

Figure 3.3. RX Buffer Offset Example #1 (RX bus width = 16, TX bus width = 32, WC residual = 1)

Figure 3.4. RX Buffer Offset Example #2 (RX bus width = 8, TX bus\_width = 64, WC residual = 5)

© 2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

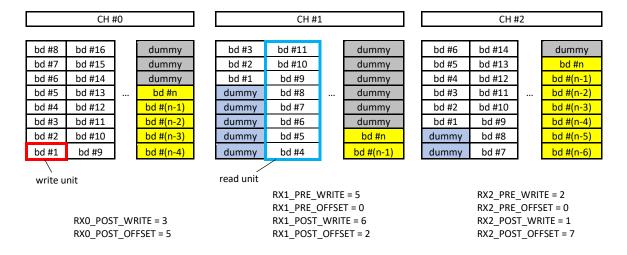

Figure 3.5 shows an example of (RX bus width) > (TX bus width). In this case, TX side has to have an extra dummy reads cycle to match the amount of write data and read data by the parameter RX $^*$  EXT R = 1.

Figure 3.5. RX Buffer Offset Example #2 (RX bus width = 32, TX bus\_width = 16, WC residual = 1)

These FIFO related parameter values are automatically obtained using the provided Excel sheet shown in Figure 1.4.

#### 3.3. merge\_ctrl

This module monitors the read ready flag of line\_buf of RX channel 0, then reads RX Buffer data from channel 0 followed by channel 1, 2, ... The read data are concatenated and sent to tx\_dphy as single line data along with a new WC value. This module uses two FIFO related parameters; RX\*\_POST\_OFFSET are used to make a necessary data shift when the new channel data are concatenated after finishing the previous channel data read. RX\*\_EXT\_R is used to make an extra read in some cases when (RX bus width) > (TX bus width).

#### 3.3.1. LP-HS Control in Non-Continuous Clock Mode

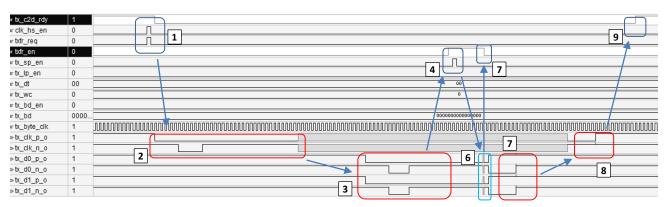

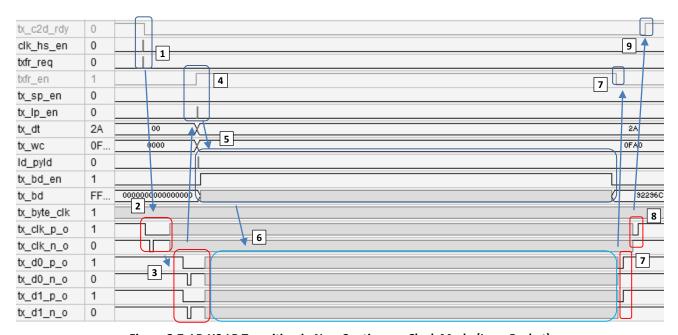

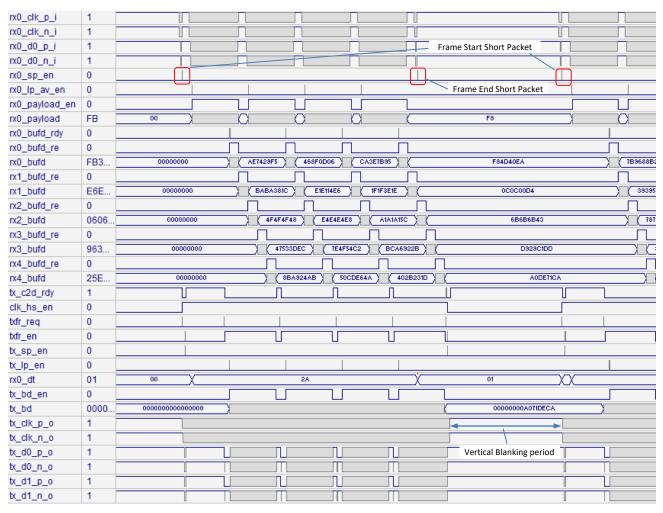

This module controls LP-HS-LP transition of tx\_dphy module as shown in Figure 3.6 and Figure 3.7 with a following sequence in case of non-continuous clock mode:

- Check tx\_c2d\_rdy = 1, then assert clk\_hs\_en and txfr\_req (at least one tx\_byte\_clk cycle).

- 2. Clock lane goes into HS mode.

- 3. Data lane goes into HS mode.

- 4. Wait for txfr\_en = 1, then assert tx\_sp\_en or tx\_lp\_en for one tx\_byte\_clk cycle.

- 5. In case of Long Packet data, assert tx\_bd\_en along with tx\_bd two cycles after ld\_pyld = 1.

- 6. HS data transmission.

- 7. After HS data transmission is done, txfr\_en goes 0 and data lane goes into LP mode.

- 8. Clock lane goes into LP mode.

- After all HS transaction ends, tx\_c2d\_rdy becomes 1, which means tx\_dphy is ready to handle the next HS transaction.

Figure 3.6. LP-HS-LP Transition in Non-Continuous Clock Mode (Short Packet)

Figure 3.7. LP-HS-LP Transition in Non-Continuous Clock Mode (Long Packet)

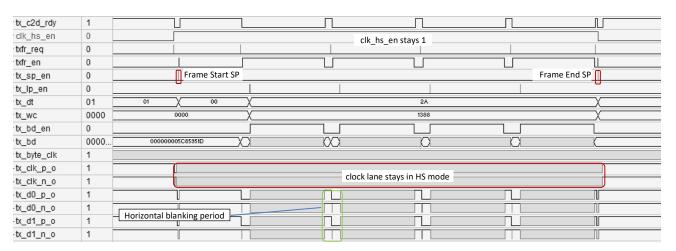

In case of non-continuous clock mode, it is possible to keep the clock lane in HS mode during active video period. By enabling `define KEEP\_HS in synthesis\_directives.v, the clock lane goes into LP mode only between frame end short packet and frame start short packet as shown in Figure 3.8. clk\_hs\_en stays 1 from Frame Start to Frame End that makes clock lane in HS mode without going in to LP mode during horizontal blanking periods. This is useful when the horizontal blanking period is too short to make both clock lane and data lane go into LP mode, which requires more overhead time.

Figure 3.8. LP-HS-LP Transition in Non-Continuous Clock Mode with KEEP HS

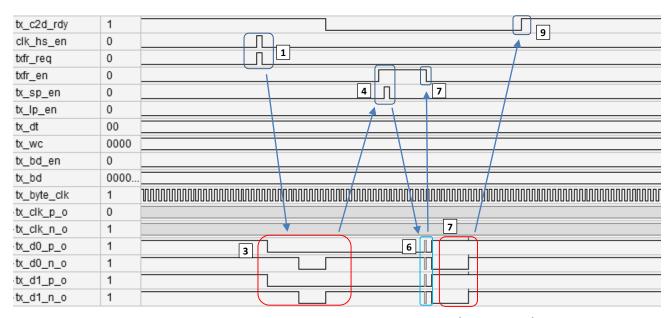

#### 3.3.2. LP-HS Control in Continuous Clock Mode

Figure 3.9 shows LP-HS-LP transition in continuous clock mode for Short Packet transaction. The control scheme by this module is the same as non-continuous clock mode. The only difference from Figure 3.6 is clock lane stays in HS mode all the time and does not go into LP mode.

Figure 3.9. LP-HS-LP Transition in Continuous Clock Mode (Short Packet)

#### 3.3.3. Line Buffer Read and Data Merge Operation

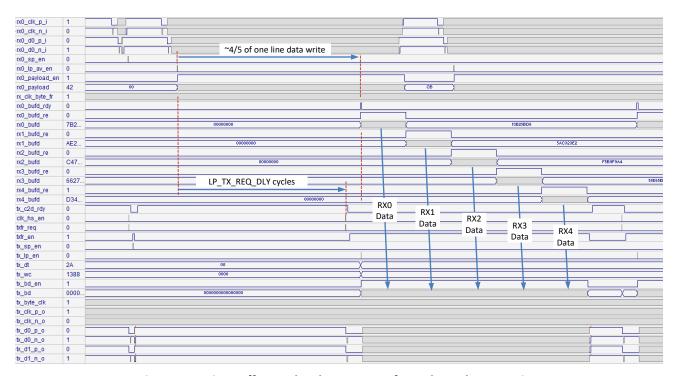

Figure 3.10 shows the global timing of the 5-channel merge operation. Only RX channel 0 signals are shown before Line Buffer module since timing are almost same in all RX channels. This module begins to read RX0 data when rx0\_bufd\_rdy is asserted followed by RX1, RX2... RX4 data reads for concatenation. The concatenated data are sent to tx\_dphy as tx\_bd. As described in line\_buf section, rx0\_bufd\_rdy is asserted when ~4/5 of one line data are written to the line buffer FIFO in case of 5-channel aggregation. On the other hand, tx\_dphy must be in HS mode before this module begins sending concatenated video data. To make this happen, the parameter *LP\_TX\_REQ\_DLY* is provided. This value determines the delay time from rx0\_lp\_av\_en assertion to txfr\_req assertion in tx\_byte\_clk cycles. The value is automatically calculated by the design. This calculation considers the transition time from LP to HS mode for data lane in case of continuous clock mode and both clock lane and data lane in case of non-continuous clock mode. When KEEP HS is defined in non-continuous clock mode, only data lane transition is considered.

© 2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

You can set your own value by enabling `define LP\_TX\_REQ\_DLY xxx in synthesis\_directives.v to overwrite the automatically calculated value. The smaller value makes data lane (and clock lane in case of non-continuous clock mode) goes into HS mode earlier, but that leads to higher power consumption. The larger value makes power consumption lower, but video data is corrupted if the value is too big and timing overlap happens between LP to HS transition and RXO buffer read.

Figure 3.10. Line Buffer Read and Data Merge for 5-Channel Aggregation

Regarding Word Count (payload video data byte count per active line), this module takes the original WC value on RX channel 0 and multiplies it by the number of RX channels. The result is sent to tx\_dphy as the final WC value of the aggregated video data.

Regarding VC (Virtual Channel ID), the value specified by `define VC x is used if defined, otherwise VC of RX channel 0 is sent to tx\_dphy.

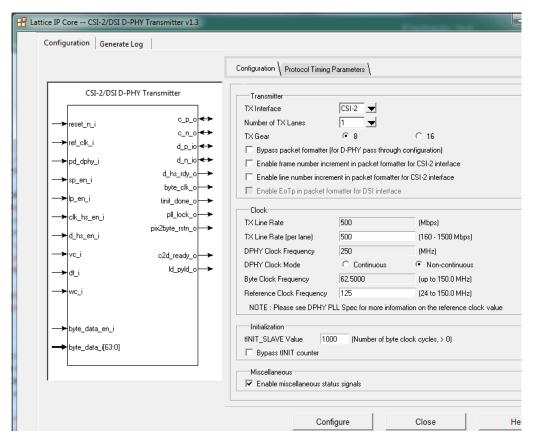

## 3.4. tx\_dphy

You must create this module according to channel conditions, such as number of lanes, bandwidth, and others. Figure 3.11 shows an example IP interface setting in Clarity Designer for the CSI-2/DSI D-PHY Transmitter Submodule IP. Refer to CSI-2/DSI D-PHY Transmitter Submodule IP User Guide (FPGA-IPUG-02024) for details.

Figure 3.11. tx\_dphy IP Creation in Clarity Designer

The following shows guidelines and parameter settings required for this reference design.

- TX Interface Select CSI-2.

- Number of TX Lanes Set according to channel configuration. Must match NUM TX LANE \* setting.

- TX Gear Set according to TX Line Rate. In general, 16 must be selected when TX Line Rate is 900 or higher.

- Bypass packet formatter Must be disabled (unchecked).

- Enable frame number Set according to the preference.

- Enable line number Must be disabled (unchecked).

- TX Line Rate Set according to channel configuration. This value must be equal to (number of RX channel) x (RX channel bandwidth) / (number of TX lanes).

- D-PHY Clock Mode Set according to channel configuration. Must select Continuous when the horizontal blanking period is short.

- Reference Clock Frequency Set the appropriate value, which can be obtained from ref\_clk\_i pin, continuous

rx0 byte clk, or on-chip GPLL. This clock frequency must be in one of the following ranges:

- 24-30 MHz

- 48-60 MHz

- 72-90 MHz

- 96-150 MHz

- tINIT\_SLAVE Value 1000 (default) is recommended.

- Bypass tINIT counter Disabled (unchecked) is recommended.

- Enable miscellaneous status signals must be set to enabled (checked).

- Protocol Timing Parameters tab Default values are recommended.

This module takes the byte data and outputs CSI-2 data after serialization in CSI-2 High Speed mode. It is recommended to set the design name to tx and module name to  $tx\_dphy$  so that you do not need to modify the instance name of this IP in the top-level design as well as the simulation setup file. Otherwise, you need to modify the names accordingly.

General guideline of TX Gear setting is to set 8 when the lane bandwidth is less than 900 Mbps, which means TX byte clock could be  $^{\sim}112$  MHz. If this causes timing violations in Static Timing Analysis (STA), TX Gear should be changed to 16.