# Lattice Radiant Software Guide for Lattice Diamond Users

#### Copyright

Copyright © 2020 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

# **Type Conventions Used in This Document**

| Convention        | Meaning or Use                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------|

| Bold              | Items in the user interface that you select or click. Text that you type into the user interface. |

| <italic></italic> | Variables in commands, code syntax, and path names.                                               |

| Ctrl+L            | Press the two keys at the same time.                                                              |

| Courier           | Code examples. Messages, reports, and prompts from the software.                                  |

| •••               | Omitted material in a line of code.                                                               |

|                   | Omitted lines in code and report examples.                                                        |

| [ ]               | Optional items in syntax descriptions. In bus specifications, the brackets are required.          |

| ( )               | Grouped items in syntax descriptions.                                                             |

| { }               | Repeatable items in syntax descriptions.                                                          |

|                   | A choice between items in syntax descriptions.                                                    |

|                   |                                                                                                   |

### **Contents**

#### Chapter 2 Migrating Designs from Diamond to CrossLink-NX on the Radiant Software 7 Architecture IP 9 PLL 9 DDR Generic 9 GDDR 7:1 11 DDR MEM 11 MIPI\_DPHY 12 SDR **13** Arithmetic IP 15 Adder 15 Adder Subtractor 15 Comparator 16 Complex Multiplier 16 Convert 17 Counter 17 LFSR 18 Multiply Accumulate 18 Multiply Add Subtract 19 Multiply Add Subtract Sum 20 Multiplier 20 Sin-Cos Table 21 Subtract 21 DSP Arithmetic IP 23 DSP Multiply Accumulate 23 DSP Multiply Add Subtract 25 DSP Multiply Add Subtract Sum 28 DSP Multiplier 29 Memory IP 31 FIFO 31 FIFO DC 32 RAM-Based Shift Register 33

```

Distributed SPRAM 35

Distributed ROM 35

RAM DP 36

RAM DP True 36

RAM DQ 38

ROM 39

PMI 40

Memory PMI 42

Primitives 45

Buffers 45

I/O Registers 46

Block RAM (EBR) 47

DSP Functions 49

Oscillator Functions 49

Registers 50

Constraints 51

Comparing the Constraint Flows 51

Radiant Constraint Tools 52

Preferences to Constraints 54

Primary Clock Net Access 55

Timing Preferences to Constraints 56

Attributes Compared 58

Chapter 3

Comparing Diamond and the Radiant Software

Design Entry 62

Using HDL in the Radiant Software 62

Using Radiant Primitives 63

Using Modules and Soft IP in the Radiant Software 63

Using Parameterized Module Instantiation 65

Design Implementation 66

Importing a Lattice Diamond Project into the Radiant Software 67

Compatible Settings and Files 68

Incompatible Settings and Files 69

Unsupported Design Source in Radiant Software 69

Lattice Diamond and the Radiant Process Flow 70

Design Analysis and Debug 71

Simulation Wizard 71

Power Calculator 71

Reveal 71

Timing Analysis 72

Radiant Software Tools 78

Revision History 81

```

Distributed DPRAM 34

# Migrating Designs from Diamond to CrossLink-NX on the Radiant Software

When migrating ECP5 and CrossLink designs to CrossLink-NX on the Radiant™ software, you should expect to go through the normal design process, such as design entry, design analysis, debug, simulation, and testing. While Diamond and the Radiant software are very similar, there are substantial differences.

This chapter provides tips on how to rebuild your design using the Radiant IP, PMI, primitives, and constraints.

**IP** and **Modules** IP are basic, configurable modules that provide a variety of functions including I/O, arithmetic, memory, and more. The Radiant IP Catalog works similarly to the IP configuration in Diamond's Clarity Designer. IP Catalog offers a collection of IP that are similar to those found in Clarity Designer.

In the Radiant software, signal names of the generated components have been converted to lower case and "\_i," "\_o," and "\_io" suffixes added. Some signals have been renamed. For example: DataA\_Re to data\_re\_i and Cout to overflow o.

For differences in specific IP, see:

- "Architecture IP" on page 9

- "Arithmetic IP" on page 15

- "DSP Arithmetic IP" on page 23

- "Memory IP" on page 31

For more information on the IP, see the Radiant Help under **References >** Lattice Module Reference Guide.

**PMI** PMI (Parameterized Module Instantiation) is an alternate way to use some of the components that come with IP Catalog. Instead of using IP

Catalog, PMI can directly instantiate a component into your HDL and customize it by setting parameters in the HDL. The Radiant software has a collection of PMI similar to Diamond's. To help you with PMI, templates for instantiating the modules are available in the Radiant Source Template view, which is similar to the Diamond Template Editor. See "PMI" on page 40.

**Primitives** Lattice library primitives are very basic functions, such as logic gates and flip-flops. Usually primitives are simply inferred in synthesis, but they can be directly instantiated as HDL into designs. See "Primitives" on page 45.

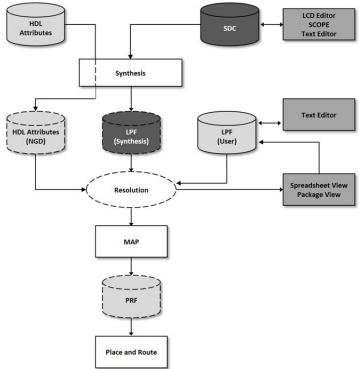

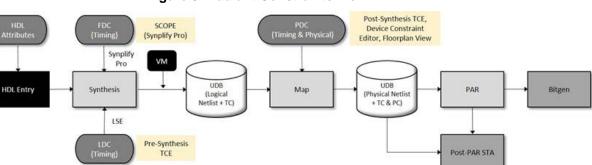

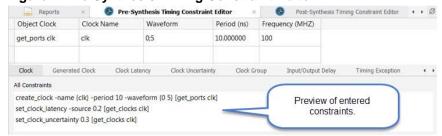

**Preferences and Constraints** Constraints are instructions applied to design elements that guide the design toward desired results and performance goals. The most common constraints are those for timing and pin assignments, but constraints are also available for placement, routing, and many other functions.

In Lattice Diamond, a Logical Preference File (.lpf) is used to constrain a design. In the Radiant software, preferences have been replaced by the industry standard Synopsys Design Constraints for ease of use and improved compatibility with third-party vendor tools such as Synopsys Synplify Pro.

This is one of the bigger differences between Diamond and Radiant designs. See "Constraints" on page 51.

### **Architecture IP**

The Radiant software has IP similar to all of Diamond's architecture modules except for dynamic bank controller.

#### **PLL**

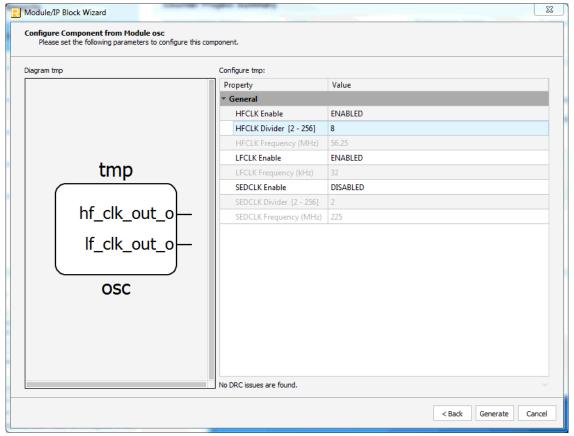

In Diamond for ECP5 and CrossLink, a PLL IP is generated using Clarity Designer. But in the Radiant software, IP Catalog is used to configure and generate the PLL IP, which can then be instantiated into the RTL.

The PLL IP is located under the Architecture\_Modules folder. The tool allows you to provide an instance name, configure the PLL settings, and generate the PLL module.

Once the configuration is completed, the PLL module can be generated by clicking the Generate button. The generated module is inserted into the project in the form of an .ipx file. From there, you can find all necessary source, constraint, and configuration files generated from the tool. A rightclick on the .ipx file allows you to create and copy a Verilog instantiation template or VHDL component declaration.

The following is the Verilog instantiation template from the generated PLL IP:

```

my_PLL u_PLL(.clki_i(),

.rstn i(),

.clkop o(),

.lock o()

);

```

### **DDR Generic**

There is a new data\_coarse\_dly\_i signal.

**Table 1: Feature Compatibility**

| Feature                         | CrossLink in Diamond:<br>ddr_generic | ECP5 in Diamond:<br>ddr_generic    | CrossLink-NX in Radiant Software: DDR_Generic |

|---------------------------------|--------------------------------------|------------------------------------|-----------------------------------------------|

| Interface Type                  | Transmit, Receive                    | Transmit, Receive,<br>Receive MIPI | Transmit, Receive                             |

| Enable Tri-state Control        | Check box                            | Check box                          | Check box                                     |

| I/O Standard for this Interface | Various                              | Various                            | Various                                       |

| Bus Width for this interface    | 1-256                                | 1-256                              | 1-256                                         |

**Table 1: Feature Compatibility (Continued)**

| Feature                                         | CrossLink in Diamond:<br>ddr_generic                                                                 | ECP5 in Diamond:<br>ddr_generic                                                                      | CrossLink-NX in Radiant Software: DDR_Generic                                                        |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Clock Frequency for this Interface              | Depends on Interface<br>Type, up to 600 MHz                                                          | Depends on Interface<br>Type, up to 400 MHz                                                          | Depends on Gearing<br>Ratio, up to 750 MHz                                                           |

|                                                 | Transmit: 4.685 – 600 MHz                                                                            | Transmit: 3.125 – 400 MHz                                                                            | X1: 100 – 250 MHz                                                                                    |

|                                                 | Receive: 100 – 600 MHz                                                                               | Receive: 100 – 400 MHz                                                                               | X2: 100 – 500 MHz                                                                                    |

|                                                 |                                                                                                      | Receive MIPI: 200 – 400                                                                              | X4: 100 – 750 MHz                                                                                    |

|                                                 |                                                                                                      | MHz                                                                                                  | X5: 100 – 750 MHz                                                                                    |

| Clock to Data Relationship at                   | Edge-to-Edge, Centered                                                                               | Depends on Interface Type                                                                            | Edge-to-Edge, Centered                                                                               |

| the Pins                                        |                                                                                                      | Transmit and Receive: Edge-to-Edge, Centered                                                         |                                                                                                      |

|                                                 |                                                                                                      | Receive MIPI: Centered                                                                               |                                                                                                      |

| Gearing Ratio                                   | X1, X2                                                                                               | X1, X2                                                                                               | X1, X2, X4, X5                                                                                       |

| Organize Parallel Data                          | By Lane, By Time                                                                                     | By Lane, By Time                                                                                     | N/A                                                                                                  |

| Enable ECLK Bridge                              | N/A                                                                                                  | Check box                                                                                            | N/A                                                                                                  |

| Data Path Delay                                 | Depends on Interface Type                                                                            | Depends on Interface Type                                                                            | Depends on Interface Type                                                                            |

|                                                 | Transmit: Bypass, Static<br>User Defined, Dynamic<br>User Defined                                    | Transmit: Bypass, Static<br>User Defined, Dynamic<br>User Defined                                    | Transmit: Bypass, Static<br>User Defined, Dynamic<br>User Defined                                    |

|                                                 | Receive: Bypass, Static<br>Default, Dynamic Default,<br>Static User Defined,<br>Dynamic User Defined | Receive: Bypass, Static<br>Default, Dynamic Default,<br>Static User Defined,<br>Dynamic User Defined | Receive: Bypass, Static<br>Default, Dynamic Default,<br>Static User Defined,<br>Dynamic User Defined |

|                                                 |                                                                                                      | Receive MIPI: Static<br>Default, Static User<br>Defined                                              |                                                                                                      |

| Delay Value for User Defined                    | 1-127                                                                                                | 1-127                                                                                                | 0-126 (Fine Delay for User<br>Defined)                                                               |

| Coarse Delay Value for User<br>Defined          | N/A                                                                                                  | N/A                                                                                                  | 0NS, 0P8NS, 1P6NS                                                                                    |

| Enable Dynamic Margin<br>Control on Clock Delay | Check box                                                                                            | Check box                                                                                            | Fixed, Dynamic (Clock Path Delay)                                                                    |

| Generate PLL with this<br>Module                | Check box                                                                                            | Check box                                                                                            | Check box (Enable PLL Instantiation)                                                                 |

| PLL Input Clock Frequency                       | Various                                                                                              | Various                                                                                              | 10 – (Clock Frequency for this interface) MHz                                                        |

| PLL Reference Clock From I/O Pin                | Check box                                                                                            | Check box                                                                                            | Check box                                                                                            |

| CLKI Input Buffer Type                          | Various                                                                                              | Various                                                                                              | N/A                                                                                                  |

| Reference Clock From I/O Pin                    | Check box                                                                                            | Check box                                                                                            | N/A                                                                                                  |

**Table 1: Feature Compatibility (Continued)**

| Feature                           | CrossLink in Diamond:<br>ddr_generic | ECP5 in Diamond:<br>ddr_generic | CrossLink-NX in Radiant Software: DDR_Generic |

|-----------------------------------|--------------------------------------|---------------------------------|-----------------------------------------------|

| Reference Clock Input Buffer Type | Various                              | Various                         | N/A                                           |

| PLL Output Clock Tolerance        | N/A                                  | N/A                             | Percentage                                    |

### **GDDR 7:1**

**Table 2: Feature Compatibility**

| Feature                                                                                           | CrossLink in Diamond: gddr_7:1 | ECP5 in Diamond: gddr_7:1 | CrossLink-NX in Radiant Software: GDDR 7:1 |

|---------------------------------------------------------------------------------------------------|--------------------------------|---------------------------|--------------------------------------------|

| Interface Type                                                                                    | Transmit, Receive              | Transmit, Receive         | Transmit, Receive                          |

| Bus Width                                                                                         | 1-16                           | 1-16                      | 1-16                                       |

| Interface Bandwidth                                                                               | 10 – 1200 Mbps                 | N/A                       | 70-945 Mbps                                |

| Clock Frequency (Pixel Clock)                                                                     | N/A                            | 8-108 MHz                 | N/A                                        |

| Enable Bit Alignment & Word<br>Alignment Soft IP                                                  | Check box                      | Check box                 | Check box                                  |

| Enable DELAYF Tuning<br>(Uses Dynamic Input Delay<br>block for adjusting Data and<br>Clock Delay) | Check box                      | N/A                       | Check box (Enable Data<br>Delay Control)   |

| Reference Clock from I/O Pin                                                                      | Check box                      | Check box                 | Check box                                  |

| Reference Clock Input Buffer<br>Type                                                              | Various                        | Various                   | Various                                    |

### **DDR MEM**

**Table 3: Feature Compatibility**

| Feature                     | ECP5 in Diamond: ddr_mem             | CrossLink-NX in Radiant Software: |  |

|-----------------------------|--------------------------------------|-----------------------------------|--|

|                             |                                      | DDR_MEM                           |  |

| Configuration (General) Tab |                                      |                                   |  |

| Interface                   | DDR2, DDR3, DDR3L, LPDDR2,<br>LPDDR3 | DDR3, DDR3L, LPDDR2, LPDDR3       |  |

| I/O Buffer Configuration    | Various, depending on Interface      | Various, depending on Interface   |  |

| Gearing Ratio               | N/A                                  | X2, X4                            |  |

| DDR Memory Frequency        | Various, depending on Interface      | Various, depending on Interface   |  |

|                             |                                      |                                   |  |

**Table 3: Feature Compatibility (Continued)**

| Feature                                      | ECP5 in Diamond: ddr_mem        | CrossLink-NX in Radiant Software: DDR_MEM |

|----------------------------------------------|---------------------------------|-------------------------------------------|

| DQS Buffer Configuration for DDR2            | Single-ended, Differential      | N/A                                       |

| Number of DQ per DQS                         | 4, 8                            | 4, 8                                      |

| Data Width                                   | Various, depending on Interface | Various, depending on Interface           |

| Data Mask                                    | Check box                       | Check box                                 |

| Clock/Address/Command                        | Check box                       | Check box                                 |

| Enable Dynamic Margin Control on Clock Delay | Check box                       | Check box                                 |

| Generate PLL with this module                | Check box                       | N/A                                       |

| PLL Input Clock Frequency                    | Various                         | N/A                                       |

| PLL Reference Clock from I/O Pin             | Check box                       | N/A                                       |

| CLKI Input Buffer Type                       | Various                         | N/A                                       |

| Clock/Address/Command Tab                    |                                 |                                           |

| Number of Clocks                             | 1, 2, 4                         | 1, 2, 4                                   |

| Address Width                                | 13-16                           | 13-16                                     |

| Bank Address Width                           | 2, 3                            | 3                                         |

| Number of Chip Selects                       | 1, 2, 4                         | 1, 2, 4                                   |

| Advanced Settings                            |                                 |                                           |

| DQS Read Delay Adjustment Enable             | N/A                             | Check box                                 |

| DQS Read Delay Adjustment                    | FACTORYONLY, PLUS, MINUS        | POSITIVE, COMPLEMENT                      |

| DQS Read Delay Value                         | PLUS: 1-255; MINUS: 1-256       | 0-255                                     |

| DQS Write Delay Adjustment Enable            | N/A                             | Check box                                 |

| DQS Write Delay Adjustment                   | FACTORYONLY, PLUS, MINUS        | POSITIVE, COMPLEMENT                      |

| DQS Write Delay Value                        | PLUS: 1-255; MINUS: 1-256       | 0-255                                     |

## MIPI\_DPHY

Modified for CrossLink-NX:

- Differential data paths has been combined to a bus.

- Improved performance for the Hard MIPI implementation.

#### Added for CrossLink-NX:

- Hard CIL for MIPI DPHY protocol

- Support for HS reverse transmission

- Added LMMI and CIL ports

- Support for Soft MIPI\_DPHY Transmitter

- Internal dedicated PLL for Hard MIPI DPHY

**Table 4: Feature Compatibility**

| Feature                               | CrossLink in Diamond: mipi_dphy                     | CrossLink-NX in Radiant Software: MIPI_DPHY       |

|---------------------------------------|-----------------------------------------------------|---------------------------------------------------|

| Interface Type                        | Receive, Transmit                                   | Receive, Transmit                                 |

| MIPI Interface Application            | CSI-2, DSI                                          | CSI-2, DSI                                        |

| DPHY Module Type                      | Hard MIPI DPHY (Tx/Rx),<br>Soft MIPI DPHY (Rx only) | Hard MIPI DPHY (Tx/Rx),<br>Soft MIPI DPHY (Tx/Rx) |

| MIXED DPHY Mode                       | N/A                                                 | CIL, No CIL (Crosslink Equivalent is No CIL)      |

| DPHY PLL Mode                         | N/A                                                 | Internal, External                                |

| DPHY Clock Mode                       | N/A                                                 | Continuous, Non-Continuous                        |

| Interface Data Rate                   | 20-1500 Mbps                                        | 80-2500 Mbps                                      |

| Gearing Ratio                         | 8:1, 16:1                                           | 8, 16                                             |

| Bus Width                             | 1-4                                                 | 1-4                                               |

| DPHY PLL Input Reference<br>Frequency | 24-200 MHz                                          | 24-200 MHz                                        |

| Reference Clock from I/O pin          | "supported"                                         | "supported"                                       |

| Reference Clock Input Buffer Type     | "supported" - LVDS default                          | "supported" - MIPI DPHY default                   |

| Interface Clock Frequency             | 10-750 MHz                                          | 40-1250 MHz                                       |

### **SDR**

CrossLink-NX has a new coarse\_dly\_i signal.

**Table 5: Feature Compatibility**

| Feature                            | CrossLink and ECP5 in Diamond: sdr | CrossLink-NX in Radiant Software: SDR |

|------------------------------------|------------------------------------|---------------------------------------|

| Interface Type                     | Transmit, Receive                  | Transmit, Receive                     |

| Enable Tri-state Control           | Check box                          | Check box                             |

| I/O Standard for this Interface    | Various                            | Various                               |

| Bus Width for this interface       | 1-256                              | 1-256                                 |

| Clock Frequency for this Interface | 1-200 MHz                          | 1-300 MHz                             |

| Clock Inversion                    | Check box                          | Check box (Enable Clock Inversion)    |

**Table 5: Feature Compatibility (Continued)**

| Feature                             | CrossLink and ECP5 in Diamond: sdr                                                                | CrossLink-NX in Radiant Software: SDR                                                             |

|-------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Data Path Delay                     | Depends on Interface Type                                                                         | Depends on Interface Type                                                                         |

|                                     | Transmit: Bypass, Static User Defined, Dynamic User Defined                                       | Transmit: Bypass, Static User Defined,<br>Dynamic User Defined                                    |

|                                     | Receive: Bypass, Static Default,<br>Dynamic Default, Static User Defined,<br>Dynamic User Defined | Receive: Bypass, Static Default,<br>Dynamic Default, Static User Defined,<br>Dynamic User Defined |

| Delay Value for User Defined        | 1-127                                                                                             | 0-126 (Fine Delay)                                                                                |

| Coarse Delay Value for User Defined | N/A                                                                                               | 0NS, 0P8NS, 1P6NS                                                                                 |

### **Arithmetic IP**

The Radiant software has IP similar to all of Diamond's arithmetic modules except for fft\_butterfly. The arithmetic IP of Diamond and the Radiant software are very similar except for a couple of differences:

- Data input widths often have a larger range. In Diamond, input widths are sometimes no more than 32 bits. In Radiant, input widths can be up to 64 bits.

- ► The Bus Ordering Style (Big Endian or Little Endian) option is not available in the Radiant software.

### **Adder**

**Table 6: Feature Compatibility**

| rabio or routare companionity           |                                      |                                         |

|-----------------------------------------|--------------------------------------|-----------------------------------------|

| Feature                                 | CrossLink and ECP5 in Diamond: adder | CrossLink-NX in Radiant Software: Adder |

| Specify the Data Width of the Adder     | 1-64                                 | 2-64 (Input Width)                      |

| Specify the Representation of the Adder | Signed, Unsigned                     | Signed, Unsigned (Input Signed)         |

| Complex Inputs                          | Check box                            | Check box (Complex Number Addition)     |

| Use Carry-in port                       | Check box                            | Check box (Carry-In Addition)           |

| Specify the Carry-out Port              | None, Carry-Out                      | None, Overflow (Carry-Out Addition)     |

| Enable Output Register                  | Check box                            | Check box (Registered Outputs)          |

| Specify number of pipeline stages       | Depends on Data Width                | Depends on Input Width (Pipelines)      |

| Bus Ordering Style                      | Big Endian, Little Endian, None      | N/A                                     |

|                                         |                                      |                                         |

### **Adder Subtractor**

**Table 7: Feature Compatibility**

| Feature                                            | CrossLink and ECP5 in Diamond: adder_subtractor | CrossLink-NX in Radiant Software: Adder_Subtractor |

|----------------------------------------------------|-------------------------------------------------|----------------------------------------------------|

| Specify the Data Width of the Adder_Subtractor     | 1-64                                            | 2-64 (Data Width)                                  |

| Specify the Representation of the Adder_Subtractor | Signed, Unsigned                                | Signed, Unsigned (Input Signed)                    |

| Complex Inputs                                     | Check box                                       | Check box (Inputs)                                 |

| Use Carry-in port                                  | Check box                                       | Check box (Carry-In)                               |

**Table 7: Feature Compatibility (Continued)**

| Feature                           | CrossLink and ECP5 in Diamond: adder_subtractor | CrossLink-NX in Radiant Software: Adder_Subtractor |

|-----------------------------------|-------------------------------------------------|----------------------------------------------------|

| Specify the Carry-out Port        | None, Carry-Out                                 | None, Overflow (Carry-Out)                         |

| Enable Output Register            | Check box                                       | Check box (Enable Output Register)                 |

| Specify number of pipeline stages | Depends on Data Width                           | Depends on Input Width (Pipelines)                 |

| Bus Ordering Style                | Big Endian, Little Endian, None                 | N/A                                                |

## Comparator

**Table 8: Feature Compatibility**

| Feature                                                | CrossLink and ECP5 in Diamond:  | CrossLink-NX in Radiant Software:  |

|--------------------------------------------------------|---------------------------------|------------------------------------|

|                                                        | comparator                      | Comparator                         |

| Specify the data width of the comparator               | 1-64                            | 2-64 (Data Width)                  |

| Specify the representation of comparator               | Signed, Unsigned                | Signed, Unsigned (Input Signed)    |

| Specify the output port compare function               | Various                         | Various (Compare Function)         |

| Use LUT based implementation (to use lesser resources) | Check box                       | N/A                                |

| Enable Output Register                                 | Check box                       | Check box (Enable Output Register) |

| Specify number of pipeline stages                      | Depends on data width           | Depends on Data Width (Pipelines)  |

| Bus Ordering Style                                     | Big Endian, Little Endian, None | N/A                                |

# **Complex Multiplier**

**Table 9: Feature Compatibility**

| Feature              | CrossLink in Diamond: complex_multiplier | ECP5 in Diamond: complex_multiplier | CrossLink-NX in Radiant Software: Complex_Mult |

|----------------------|------------------------------------------|-------------------------------------|------------------------------------------------|

| Block Implementation | LUT                                      | LUT, DSP                            | LUT, DSP<br>(Implementation)                   |

| Input A Width        | 2-36                                     | 2-36                                | 2-64 (Input A Width)                           |

| Input B Width        | 2-36                                     | 2-36                                | 2-64 (Input B Width)                           |

| Representation       | Signed, Unsigned                         | Signed, Unsigned                    | Signed, Unsigned (Input Signed)                |

**Table 9: Feature Compatibility (Continued)**

| Feature                               | CrossLink in Diamond: complex_multiplier | ECP5 in Diamond: complex_multiplier             | CrossLink-NX in Radiant<br>Software: Complex_Mult |

|---------------------------------------|------------------------------------------|-------------------------------------------------|---------------------------------------------------|

| Specify the Number of Pipeline Stages | Depends on Input Width                   | Depends on Input Width and Block Implementation | Depends on<br>Implementation (Pipelines)          |

| Enable Input Registers                | Check box                                | Check box                                       | Check box (Registered Inputs)                     |

| Enable Output Registers               | Check box                                | Check box                                       | Check box (Registered Outputs)                    |

| Implementation                        | 3 Multiplier, 4 Multiplier               | 3 Multiplier, 4 Multiplier                      | N/A                                               |

| Bus Ordering Style                    | Big Endian, Little Endian,<br>None       | Big Endian, Little Endian,<br>None              | N/A                                               |

### **Convert**

**Table 10: Feature Compatibility**

| Feature             | CrossLink and ECP5 in Diamond convert | : CrossLink-NX in Radiant Software: Convert |

|---------------------|---------------------------------------|---------------------------------------------|

| Input Width         | 1-256                                 | 1-256                                       |

| Input Binary Point  | 0-7                                   | 0-7                                         |

| Input Sign          | Signed, Unsigned                      | SIGNED, UNSIGNED                            |

| Output Width        | 1-256                                 | 1-256                                       |

| Output Binary Point | 0-7                                   | 0-7                                         |

| Output Sign         | Signed, Unsigned                      | N/A                                         |

| Rounding            | Truncate, Nearest, Convergent         | Truncate, Nearest, Convergent               |

| Saturate            | Wrap, Min_Max                         | Wrap, Min_Max                               |

### Counter

**Table 11: Feature Compatibility**

| Feature                               | CrossLink and ECP5 in Diamond: counter | CrossLink-NX in Radiant Software:<br>Counter |

|---------------------------------------|----------------------------------------|----------------------------------------------|

| Specify the data width of the counter | 1-64                                   | 1-64 (Data Width)                            |

| Specify the direction of the counter  | Up, Down, Up-Down                      | Up, Down, UpDown (Counter Direction)         |

| Optimized for speed                   | Check box                              | N/A                                          |

**Table 11: Feature Compatibility (Continued)**

| Feature            | CrossLink and ECP5 in Diamond counter | : CrossLink-NX in Radiant Software: Counter |

|--------------------|---------------------------------------|---------------------------------------------|

| Lower count value  | Depends on data width                 | Depends on Data Width                       |

| Upper count value  | Depends on data width                 | Depends on Data Width                       |

| Enable load input  | Check box                             | Check box                                   |

| Bus Ordering Style | Big Endian, Little Endian, None       | N/A                                         |

### **LFSR**

**Table 12: Feature Compatibility**

| ·                          | <u> </u>                            |                                        |

|----------------------------|-------------------------------------|----------------------------------------|

| Feature                    | CrossLink and ECP5 in Diamond: Ifsr | CrossLink-NX in Radiant Software: LFSR |

| LFSR Type                  | Fibonacci, Galois                   | Fibonacci, Galois                      |

| Gate Type                  | XOR, XNOR                           | XOR, XNOR                              |

| Number of Bits             | 1-512                               | 1-512                                  |

| Feedback Polynomial        | Various                             | Various                                |

| Initial Value              | Various                             | Various                                |

| Enable Parallel Output     | Check box                           | Check box                              |

| Use Reloadable Seed Values | Check box                           | Check box                              |

| Bus Ordering Style         | Big Endian, Little Endian, None     | N/A                                    |

# **Multiply Accumulate**

**Table 13: Feature Compatibility**

| Feature                 | CrossLink in Diamond: multiply_accumulate | ECP5 in Diamond: multiply_accumulate | CrossLink-NX in Radiant<br>Software: Mult_Accumulate |

|-------------------------|-------------------------------------------|--------------------------------------|------------------------------------------------------|

| Block<br>Implementation | LUT                                       | LUT, DSP                             | LUT, DSP (Implementation)                            |

| Add/Sub Operation       | Add, Sub                                  | Add, Sub                             | Addition, Subtraction (Addition/Subtraction)         |

| Input A Width           | 2-36                                      | 2-36                                 | 2-64                                                 |

| Representation          | Signed, Unsigned                          | Signed, Unsigned                     | Signed, Unsigned                                     |

| Input B Width           | 2-36                                      | 2-36                                 | 2-64                                                 |

| Representation          | Signed, Unsigned                          | Signed, Unsigned                     | Signed, Unsigned                                     |

|                         |                                           |                                      |                                                      |

**Table 13: Feature Compatibility (Continued)**

| Feature                               | CrossLink in Diamond: multiply_accumulate | ECP5 in Diamond: multiply_accumulate            | CrossLink-NX in Radiant Software: Mult_Accumulate |

|---------------------------------------|-------------------------------------------|-------------------------------------------------|---------------------------------------------------|

| Accumulator Width                     | 1-32                                      | 1-32                                            | Depends on Input Width                            |

| Specify the Number of Pipeline Stages | Depends on Input Width                    | Depends on Input Width and Block Implementation | Depends on Implementation (Pipelines)             |

| Enable Input<br>Registers             | Check box                                 | Check box                                       | Check box (Registered Inputs)                     |

| Enable Output<br>Registers            | Check box                                 | Check box                                       | Check box (Registered Outputs)                    |

| Bus Ordering Style                    | Big Endian, Little Endian,<br>None        | Big Endian, Little Endian,<br>None              | N/A                                               |

# **Multiply Add Subtract**

**Table 14: Feature Compatibility**

| Feature                               | CrossLink in Diamond:<br>mult_add_sub | ECP5 in Diamond:<br>mult_add_sub                | CrossLink-NX in Radiant Software: Mult_Add_Sub |

|---------------------------------------|---------------------------------------|-------------------------------------------------|------------------------------------------------|

| Block Implementation                  | LUT                                   | LUT, DSP                                        | LUT, DSP<br>(Implementation)                   |

| Add/Sub Operation                     | Add, Sub                              | Add, Sub                                        | Addition, Subtraction (Addition/Subtraction)   |

| Input A0/A1 Width                     | 2-36                                  | 2-36                                            | 2-64 (Input A Width)                           |

| Representation                        | Signed, Unsigned                      | Signed, Unsigned                                | Check box (Input A<br>Signed)                  |

| Input B0/B1 Width                     | 2-36                                  | 2-36                                            | 2-64 (Input B Width)                           |

| Representation                        | Signed, Unsigned                      | Signed, Unsigned                                | Check box (Input B<br>Signed)                  |

| Specify the Number of Pipeline Stages | Depends on Input Width                | Depends on Input Width and Block Implementation | Depends on<br>Implementation (Pipelines)       |

| Enable Input Registers                | Check box                             | Check box                                       | Check box (Registered Inputs)                  |

| Enable Output Registers               | Check box                             | Check box                                       | Check box (Registered Outputs)                 |

| Bus Ordering Style                    | Big Endian, Little Endian,<br>None    | Big Endian, Little Endian,<br>None              | N/A                                            |

# **Multiply Add Subtract Sum**

**Table 15: Feature Compatibility**

| Feature                               | CrossLink in Diamond:<br>mult_add_sub_sum | ECP5 in Diamond:<br>mult_add_sub_sum            | CrossLink-NX in Radiant<br>Software:<br>Mult_Add_Sub_Sum |

|---------------------------------------|-------------------------------------------|-------------------------------------------------|----------------------------------------------------------|

| Block Implementation                  | LUT                                       | LUT, DSP                                        | LUT, DSP<br>(Implementation)                             |

| Add/Sub 0 Operation                   | Add, Sub                                  | Add, Sub                                        | Add, Sub                                                 |

| Add/Sub 1 Operation                   | Add, Sub                                  | Add, Sub                                        | Add, Sub                                                 |

| Input A0/A1/A2/A3 Width               | 2-36                                      | 2-36                                            | 2-64                                                     |

| Representation                        | Signed, Unsigned                          | Signed, Unsigned                                | Signed, Unsigned                                         |

| Input B0/B1/B2/B3 Width               | 2-36                                      | 2-36                                            | 2-64                                                     |

| Representation                        | Signed, Unsigned                          | Signed, Unsigned                                | Signed, Unsigned                                         |

| Specify the Number of Pipeline Stages | Depends on Input Width                    | Depends on Input Width and Block Implementation | Depends on Input Width (Pipelines)                       |

| Enable Input Registers                | Check box                                 | Check box                                       | Check box (Registered Inputs)                            |

| Enable Output Registers               | Check box                                 | Check box                                       | Check box (Registered Outputs)                           |

| Bus Ordering Style                    | Big Endian, Little Endian,<br>None        | Big Endian, Little Endian,<br>None              | N/A                                                      |

# Multiplier

**Table 16: Feature Compatibility**

| CrossLink in Diamond: multiplier | ECP5 in Diamond: multiplier                                                        | CrossLink-NX in Radiant Software: Multiplier                                                                                         |

|----------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Check box                        | Check box                                                                          | Check box (Use<br>Multiplication Co-efficient)                                                                                       |

| (-2^31) to (2^31-1)              | (-2^31) to (2^31-1)                                                                | (-2^31) to (2^31-1)                                                                                                                  |

| Check box                        | Check box                                                                          | N/A                                                                                                                                  |

| LUT                              | LUT, DSP                                                                           | LUT, DSP<br>(Implementation)                                                                                                         |

| 2-36                             | 2-36                                                                               | 2-64                                                                                                                                 |

| Signed, Unsigned                 | Signed, Unsigned                                                                   | Signed, Unsigned (Input A Signed)                                                                                                    |

| 2-36                             | 2-36                                                                               | 2-64                                                                                                                                 |

|                                  | multiplier  Check box  (-2^31) to (2^31-1)  Check box  LUT  2-36  Signed, Unsigned | multiplier  Check box  Check box  (-2^31) to (2^31-1)  Check box  Check box  LUT  LUT, DSP  2-36  Signed, Unsigned  Signed, Unsigned |

**Table 16: Feature Compatibility (Continued)**

| Feature                               | CrossLink in Diamond: multiplier   | ECP5 in Diamond: multiplier                     | CrossLink-NX in Radiant<br>Software: Multiplier |

|---------------------------------------|------------------------------------|-------------------------------------------------|-------------------------------------------------|

| Representation                        | Signed, Unsigned                   | Signed, Unsigned                                | Signed, Unsigned (Input B Signed)               |

| Specify the Number of Pipeline Stages | Depends on Input Width             | Depends on Input Width and Block Implementation | Depends on Block<br>Implementation (Pipelines)  |

| Enable Input Registers                | Check box                          | Check box                                       | Check box (Registered Inputs)                   |

| Enable Output Registers               | Check box                          | Check box                                       | Check box (Registered Outputs)                  |

| Bus Ordering Style                    | Big Endian, Little Endian,<br>None | Big Endian, Little Endian,<br>None              | N/A                                             |

## **Sin-Cos Table**

**Table 17: Feature Compatibility**

| Feature                               | CrossLink and ECP5 in Diamond: sin-cos_table | CrossLink-NX in Radiant Software: Sin_Cos_Table |

|---------------------------------------|----------------------------------------------|-------------------------------------------------|

| Block Implementation                  | LUT, EBR                                     | LUT, EBR                                        |

| Input Theta Bit Width                 | 3-10                                         | 3-10                                            |

| Output Result Bit Width               | 4-32                                         | 4-32                                            |

| Output Mode                           | Sin, Cos, Sin-Cos                            | Sin, Cos, Sin-Cos                               |

| Use Tables for Quarter-wave only      | Check box                                    | Check box                                       |

| Use 1-bit for Signed Integer          | Check box                                    | Check box                                       |

| Enable Input Registers                | Check box                                    | Check box                                       |

| Enable Output Registers               | Check box                                    | Check box                                       |

| Specify the number of pipeline stages | 1-3                                          | 1-3                                             |

| Bus Ordering Style                    | Big Endian, Little Endian, None              | N/A                                             |

### **Subtract**

**Table 18: Feature Compatibility**

| Feature                                      | CrossLink and ECP5 in Diamond: subtractor | CrossLink-NX in Radiant Software: Subtractor |

|----------------------------------------------|-------------------------------------------|----------------------------------------------|

| Specify the Data Width of the Subtractor     | 1-64                                      | 2-64 (Input Width)                           |

| Specify the Representation of the Subtractor | Signed, Unsigned                          | Signed, Unsigned (Input Signed)              |

| Complex Inputs                               | Check box                                 | Check box (Complex Number Subtraction)       |

| Use Carry-in port                            | Check box                                 | Check box (Carry-In Subtraction)             |

| Specify the Carry-out Port                   | None, Carry-Out                           | None, Overflow (Carry-Out<br>Subtraction)    |

| Enable Output Register                       | Check box                                 | Check box (Registered Outputs)               |

| Specify number of pipeline stages            | Depends on Data Width                     | Depends on Input Width (Pipelines)           |

| Bus Ordering Style                           | Big Endian, Little Endian, None           | N/A                                          |

### **DSP Arithmetic IP**

For ECP5, Diamond provides several IP that implement arithmetic functions using DSP blocks. For CrossLink-NX, the Radiant software has some that are similar to the IP for ECP5 in Diamond but with fewer options to make configuration simpler. To see the differences, use the following tables. The DSP arithmetic IP for CrossLink-NX are:

- DSP\_Mult\_Accumulate

- DSP\_Mult\_Add\_Sub

- DSP\_Mult\_Add\_Sub\_Sum

- DSP\_Multiplier

## **DSP Multiply Accumulate**

**Table 19: Feature Compatibility**

| Feature              | ECP5 in Diamond: mac      | CrossLink-NX in Radiant Software: DSP_Mult_Accumulate |

|----------------------|---------------------------|-------------------------------------------------------|

| Input A Width        | 2-72                      | 2-72                                                  |

| Input B Width        | 2-72                      | 2-72                                                  |

| Data Type A          | Signed, Unsigned, Dynamic | Signed, Unsigned                                      |

| Data Type B          | Signed, Unsigned, Dynamic | Signed, Unsigned                                      |

| Source A             | Parallel, Shift, Dynamic  | N/A                                                   |

| Source B             | Parallel, Shift, Dynamic  | N/A                                                   |

| Select Shift Out A   | Check box                 | N/A                                                   |

| Select Shift Out B   | Check box                 | N/A                                                   |

| Add/Sub Operation    | Add, Sub, Dynamic         | N/A <sup>4</sup>                                      |

| Input Register A     | Check box                 | Check box                                             |

| Input A Clock        | CLK0, CLK1                | N/A <sup>1</sup>                                      |

| Input A Clock Enable | CE0, CE1, CE2, CE3        | N/A <sup>2</sup>                                      |

| Input A Reset        | RST0, RST1                | N/A <sup>3</sup>                                      |

| Input Register B     | Check box                 | Check box                                             |

| Input B Clock        | CLK0, CLK1                | N/A <sup>1</sup>                                      |

| Input B Clock Enable | CE0, CE1, CE2, CE3        | N/A <sup>2</sup>                                      |

| Input B Reset        | RST0, RST1                | N/A <sup>3</sup>                                      |

| Pipeline Mode        | Check box                 | N/A                                                   |

| Pipeline Register    | Check box                 | Check box                                             |

**Table 19: Feature Compatibility (Continued)**

| Feature            | ECP5 in Diamond: mac            | CrossLink-NX in Radiant Software: DSP_Mult_Accumulate |

|--------------------|---------------------------------|-------------------------------------------------------|

| Output Register    | Check box                       | Check box                                             |

| Bus Ordering Style | Big Endian, Little Endian, None | N/A                                                   |

<sup>&</sup>lt;sup>1</sup> Two clocks were used in ECP5. However, CrossLink-NX DSP primitives only use a single clock for input and output.

**Table 20: Port Compatibility**

| ECP5 in Diamond: mac | CrossLink-NX in Radiant Software: DSP_Mult_Accumulate |

|----------------------|-------------------------------------------------------|

| CLK0                 | N/A                                                   |

| CLK1                 | N/A                                                   |

| N/A                  | clk_i                                                 |

| CE0                  | N/A                                                   |

| CE1                  | N/A                                                   |

| CE2                  | N/A                                                   |

| CE3                  | N/A                                                   |

| N/A                  | ce_a_i                                                |

| N/A                  | ce_b_i                                                |

| N/A                  | ce_o_i                                                |

| RST0                 | N/A                                                   |

| RST1                 | N/A                                                   |

| N/A                  | rst_a_i                                               |

| N/A                  | rst_b_i                                               |

| N/A                  | rst_o_i                                               |

| SignA                | N/A                                                   |

| SignB                | N/A                                                   |

| SourceA              | N/A                                                   |

<sup>&</sup>lt;sup>2</sup> ECP5 has four selectable clock enables (CE0, CE1, CE2, and CE3). In CrossLink-NX DSPs, the clock enables are already designated (ce\_a\_i for input A, ce\_b\_i for input B, ce\_p\_i for pipeline, and ce\_o\_i for output).

<sup>&</sup>lt;sup>3</sup> Two resets are used in ECP5. However CrossLink-NX uses designated resets for input and output (rst\_a\_i for input A, rst\_b\_i for input B, rst\_p\_i for pipeline, and rst\_o\_i for output).

<sup>&</sup>lt;sup>4</sup> The Add/Sub operation in the Radiant software is always dynamic.

**Table 20: Port Compatibility (Continued)**

| CrossLink-NX in Radiant Software:<br>DSP_Mult_Accumulate |

|----------------------------------------------------------|

| N/A                                                      |

| accumsload                                               |

| addnsub_i                                                |

| input_a_i                                                |

| input_b_i                                                |

| ld                                                       |

| N/A                                                      |

| N/A                                                      |

| result_o                                                 |

| N/A                                                      |

| N/A                                                      |

| N/A                                                      |

|                                                          |

# **DSP Multiply Add Subtract**

**Table 21: Feature Compatibility**

| Feature                | ECP5 in Diamond: multaddsub | CrossLink-NX in Radiant Software: DSP_Mult_Add_Sub |

|------------------------|-----------------------------|----------------------------------------------------|

| Enable Cascade Input   | Check box                   | N/A                                                |

| Input A0/A1 Width      | 2-72                        | 2-72                                               |

| Input B0/B1 Width      | 2-72                        | 2-72                                               |

| Data Type A            | Signed, Unsigned, Dynamic   | Signed, Unsigned                                   |

| Data Type B            | Signed, Unsigned, Dynamic   | Signed, Unsigned                                   |

| Reset Mode             | SYNC, ASYNC                 | SYNC, ASYNC                                        |

| Input A0 Source        | Parallel, Shift, Dynamic    | N/A                                                |

| Input A1 Source        | Parallel, Shift, Dynamic    | N/A                                                |

| Input B0 Source        | Parallel, Shift, Dynamic    | N/A                                                |

| Input B1 Source        | Parallel, Shift, Dynamic    | N/A                                                |

| Select Shift Out A     | Check box                   | N/A                                                |

| Cascade Match Register | Check box                   | N/A                                                |

| Select Shift Out B     | Check box                   | N/A                                                |

| Add/Sub Operation      | Add, Sub, Dynamic           | N/A <sup>4</sup>                                   |

**Table 21: Feature Compatibility (Continued)**

| Feature                   | ECP5 in Diamond: multaddsub     | CrossLink-NX in Radiant Software: DSP_Mult_Add_Sub |

|---------------------------|---------------------------------|----------------------------------------------------|

| Input Register A          | Check box                       | N/A                                                |

| Input A Clock             | CLK0, CLK1                      | N/A <sup>1</sup>                                   |

| Input A Clock Enable      | CE0, CE1, CE2, CE3              | N/A <sup>2</sup>                                   |

| Input A Reset             | RST0, RST1                      | N/A <sup>3</sup>                                   |

| Input Register B          | Check box                       | N/A                                                |

| Input B Clock             | CLK0, CLK1                      | N/A <sup>1</sup>                                   |

| Input B Clock Enable      | CE0, CE1, CE2, CE3              | N/A <sup>2</sup>                                   |

| Input B Reset             | RST0, RST1                      | N/A <sup>3</sup>                                   |

| Input Register AB0        | N/A                             | Check box                                          |

| Input Register AB1        | N/A                             | Check box                                          |

| Pipeline Mode             | Check box                       | N/A                                                |

| Enable Pipeline Register  | Check box                       | Check box                                          |

| Output Register           | Check box                       | Check box                                          |

| Output Clock              | InputA, InputB                  | N/A                                                |

| Input Output Clock Enable | CE0, CE1, CE2, CE3              | N/A <sup>2</sup>                                   |

| Bus Ordering Style        | Big Endian, Little Endian, None | N/A                                                |

|                           |                                 |                                                    |

<sup>&</sup>lt;sup>1</sup> Two clocks were used in ECP5. However, CrossLink-NX DSP primitives only use a single clock for input and output.

**Table 22: Port Compatibility**

| · · ·                       |                                                    |

|-----------------------------|----------------------------------------------------|

| ECP5 in Diamond: multaddsub | CrossLink-NX in Radiant Software: DSP_Mult_Add_Sub |

| CLK0                        | N/A                                                |

| CLK1                        | N/A                                                |

| N/A                         | clk_i                                              |

| CE0                         | N/A                                                |

| CE1                         | N/A                                                |

<sup>&</sup>lt;sup>2</sup> ECP5 has four selectable clock enables (CE0, CE1, CE2, and CE3). In CrossLink-NX DSPs, the clock enables are already designated (ce\_a\_i for input A, ce\_b\_i for input B, ce\_p\_i for pipeline, and ce\_o\_i for output).

<sup>&</sup>lt;sup>3</sup> Two resets are used in ECP5. However CrossLink-NX uses designated resets for input and output (rst\_a\_i for input A, rst\_b\_i for input B, rst\_p\_i for pipeline, and rst\_o\_i for output).

<sup>&</sup>lt;sup>4</sup> The Add/Sub operation in the Radiant software is always dynamic.

**Table 22: Port Compatibility (Continued)**

| ECP5 in Diamond: multaddsub | CrossLink-NX in Radiant Software: DSP_Mult_Add_Sub |

|-----------------------------|----------------------------------------------------|

| CE2                         | N/A                                                |

| CE3                         | N/A                                                |

| N/A                         | ce_a_i                                             |

| N/A                         | ce_b_i                                             |

| N/A                         | ce_p_i                                             |

| N/A                         | ce_o_i                                             |

| RST0                        | N/A                                                |

| RST1                        | N/A                                                |

| N/A                         | rst_a_i                                            |

| N/A                         | rst_b_i                                            |

| N/A                         | rst_p_i                                            |

| N/A                         | rst_o_i                                            |

| SignA                       | N/A                                                |

| SignB                       | N/A                                                |

| ShiftA0                     | N/A                                                |

| ShiftA1                     | N/A                                                |

| ShiftB0                     | N/A                                                |

| ShiftB1                     | N/A                                                |

| SourceA                     | N/A                                                |

| SourceB                     | N/A                                                |

| ADDNSUB                     | addnsub_i                                          |

| A0                          | input_0_i                                          |

| A1                          | input_a1_i                                         |

| B0                          | input_b0_i                                         |

| B1                          | input_b1_i                                         |

| SRIA                        | N/A                                                |

| SRIB                        | N/A                                                |

| CIN                         | N/A                                                |

| SignCIN                     | N/A                                                |

| SignSUM                     | N/A                                                |

| SROA                        | N/A                                                |

**Table 22: Port Compatibility (Continued)**

| ECP5 in Diamond: multaddsub | CrossLink-NX in Radiant Software: DSP_Mult_Add_Sub |

|-----------------------------|----------------------------------------------------|

| SROB                        | N/A                                                |

| SUM                         | result_o                                           |

### **DSP Multiply Add Subtract Sum**

Added a designated clock enable and reset for input and output.

#### Removed for CrossLink-NX:

- Select shift Out A and Select shift Out B.

- Add/Sub 0 Operation (Add, Sub, or Dynamic).

- Add/Sub 1 Operation (Add, Sub, or Dynamic).

- Input Source A0, A1, A2, A3, B0, B1, B2, and B3 (Parallel, Shift, or Dynamic).

- Bus Ordering style not supported by primitive.

- Dynamic mode removed from Data Type.

- Ports:

- SROA (Shift Output)

- SROB (Shift Output)

- OVERFLOW

- SourceA

- SourceB

- SignA

- SignB

- **SRIA**

- SRIB (Shift Input)

#### Modified for CrossLink-NX:

Multiple clock support to single clock. Special primitive only uses single clock.

## **DSP Multiplier**

**Table 23: Feature Compatibility**

| Feature              | ECP5 in Diamond: mult           | CrossLink-NX in Radiant Software: DSP_Multiplier |

|----------------------|---------------------------------|--------------------------------------------------|

| Input Width          | 2-72                            | 2-72                                             |

| Data Type            | Signed, Unsigned, Dynamic       | Signed, Unsigned                                 |

| Source               | Parallel, Shift, Dynamic        | N/A                                              |

| Select Shift Out A   | Check box                       | N/A                                              |

| Select Shift Out B   | Check box                       | N/A                                              |

| Input Register A     | Check box                       | Check box                                        |

| Input A Clock        | CLK0, CLK1                      | N/A <sup>1</sup>                                 |

| Input A Clock Enable | CE0, CE1, CE2, CE3              | N/A <sup>2</sup>                                 |

| Input A Reset        | RST0, RST1                      | N/A <sup>3</sup>                                 |

| Input Register B     | Check box                       | Check box                                        |

| Input B Clock        | CLK0, CLK1                      | N/A <sup>1</sup>                                 |

| Input B Clock Enable | CE0, CE1, CE2, CE3              | N/A <sup>2</sup>                                 |

| Input B Reset        | RST0, RST1                      | N/A <sup>3</sup>                                 |

| Pipeline Mode        | Check box                       | N/A                                              |

| Pipeline Register    | Check box                       | N/A                                              |

| Output Register      | Check box                       | Check box                                        |

| Bus Ordering Style   | Big Endian, Little Endian, None | N/A                                              |

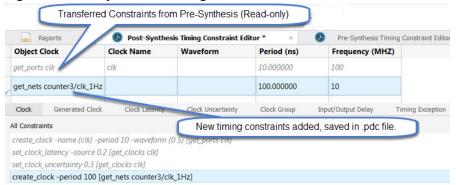

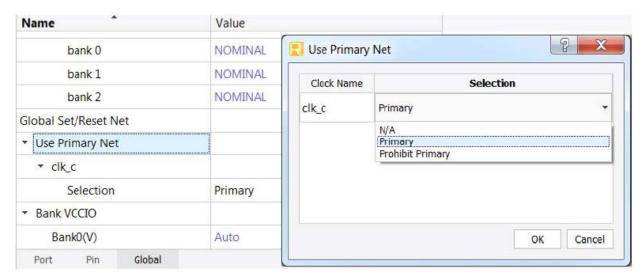

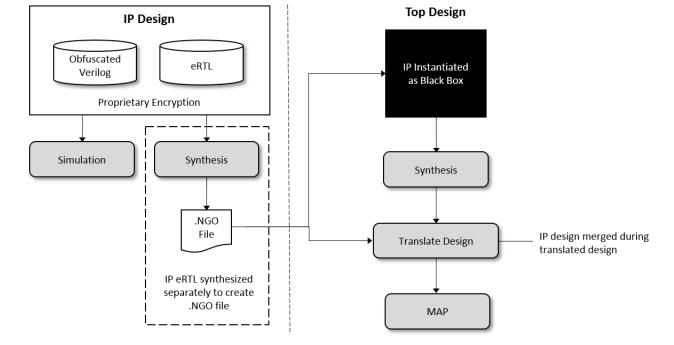

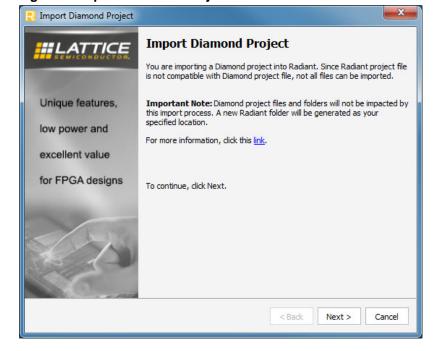

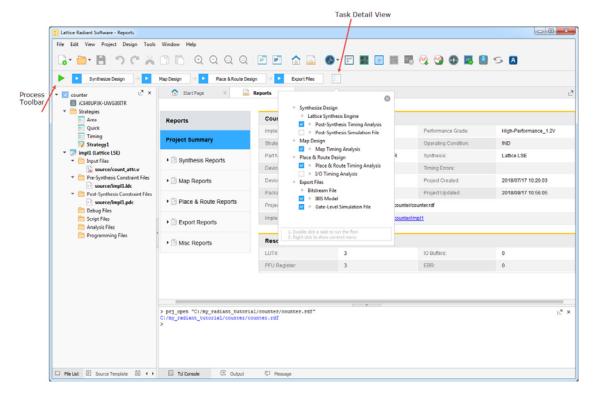

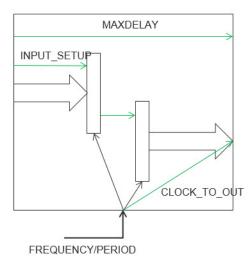

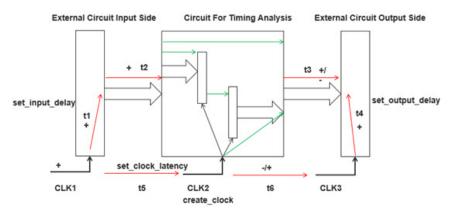

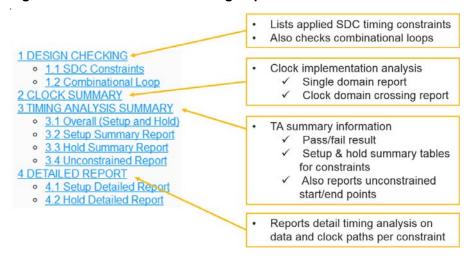

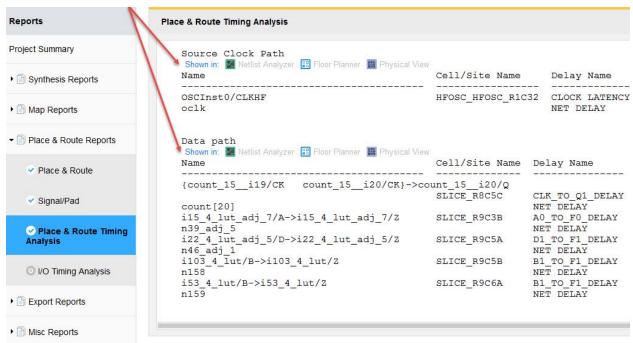

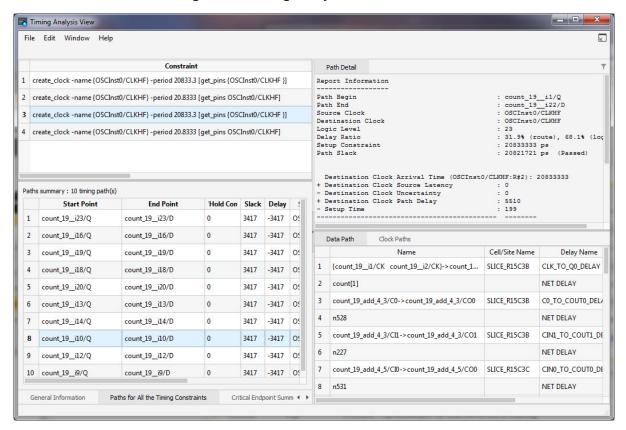

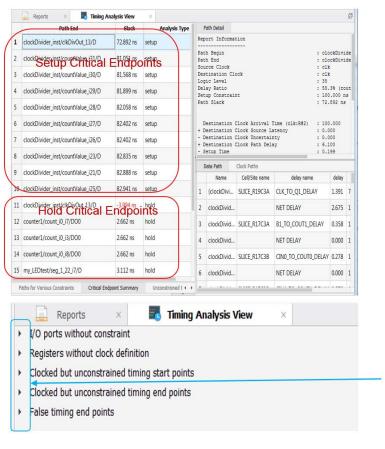

|                      |                                 |                                                  |