# **UART 16550 IP**

# **User Guide**

FPGA-IPUG-02100-1.4

April 2024

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

|               | 5                                         |    |

|---------------|-------------------------------------------|----|

| Acronym       | ns in This Document                       | 5  |

| 1. Intro      | oduction                                  |    |

| 1.1.          | Overview of the IP                        | 6  |

| 1.2.          | Quick Facts                               | 6  |

| 1.3.          | Features                                  | 6  |

| 1.4.          | Licensing Information                     | 7  |

| 1.5.          | IP Validation Summary                     | 8  |

| 1.6.          | Minimum Device Requirements               | 8  |

| 1.7.          | Naming Conventions                        | 8  |

| 1.7.          | 1. Nomenclature                           | 8  |

| 1.7.          | 2. Signal Names                           | 8  |

| 1.7.          | 3. Host                                   | 8  |

| 1.7.          |                                           |    |

| 2. Fund       | ctional Description                       |    |

| 2.1.          | IP Architecture Overview                  |    |

| 2.2.          | Clocking and Reset                        |    |

| 2.3.          | User Interfaces                           |    |

| 2.3.          |                                           |    |

| 2.4.          | Programming Flow                          |    |

| 2.4.          |                                           |    |

| 2.4.          |                                           |    |

| 2.4.          | ·                                         |    |

| 2.4.          | •                                         |    |

| 2.5.          | Operations Details                        |    |

| 2.5.          | ·                                         |    |

| 2.5.          |                                           |    |

| _             | arameter Description                      |    |

|               | al Description                            |    |

| _             | ister Description                         |    |

| 5.1.          | Receive Buffer Register (RBR)             |    |

| 5.2.          | Transmitter Holding Register (THR)        |    |

| 5.3.          | Interrupt Enable Register (IER)           |    |

| 5.3.<br>5.4.  | Interrupt Identification Register (IIR)   |    |

| 5.4.<br>5.5.  | FIFO Control Register (FCR)               |    |

| 5.5.<br>5.6.  | Line Control Register (LCR)               |    |

|               | MODEM Control Register (MCR)              |    |

| 5.7.          | e , ,                                     |    |

| 5.8.          | Line Status Register (LSR)                |    |

| 5.9.<br>5.10. | MODEM Status Register (MSR)               |    |

|               | Divisor Latch Register (DLR_MSB, DLR_LSB) |    |

|               | igning with the IP                        |    |

| 6.1.          | Generating and Instantiating the IP       |    |

| 6.1.          |                                           |    |

| 6.2.          | Running Functional Simulation             |    |

|               | ougging                                   |    |

| 7.1.          | Debug Methods                             |    |

| 7.1.          |                                           |    |

| 7.2.          | Debug Tools                               |    |

| 7.2.          | 1                                         |    |

| 7.2.          |                                           |    |

|               | ign Considerations                        |    |

| 8.1.          | Compatibility                             | 35 |

| 8.2.     | Configuration                                                              | 35 |

|----------|----------------------------------------------------------------------------|----|

| 8.3.     | Interrupts                                                                 | 35 |

| Append   | lix A. Resource Utilization                                                | 36 |

| Referen  | nces                                                                       | 37 |

| Technic  | al Support Assistance                                                      | 38 |

| Revision | n History                                                                  | 39 |

|          |                                                                            |    |

|          |                                                                            |    |

|          |                                                                            |    |

| Figur    | res                                                                        |    |

|          | L.1. Strategies Dialog Box                                                 |    |

| Figure 2 | 2.1. Functional Block Diagram                                              | 9  |

| _        | 2.2. Tx/Rx Data Format                                                     |    |

| _        | 2.3. Transmit Operation Timing Diagram with Flow Control Signals (1 byte)  |    |

| _        | 2.4. Transmit Operation Timing Diagram with Flow Control Signals (2 bytes) |    |

| _        | 2.5. Receive Operation Timing Diagram with Flow Control Signals (1 byte)   |    |

| _        | 2.6. Transmit Operation Timing Diagram with Flow Control Signals (2 bytes) |    |

| _        | 5.1. Module/IP Block Wizard                                                |    |

| _        | 5.2. IP Configuration                                                      |    |

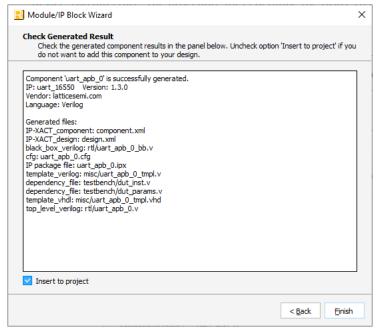

| _        | 5.3. Check Generated Result                                                |    |

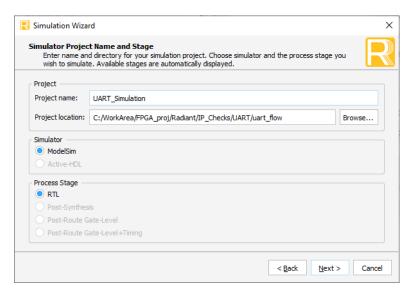

| _        | 5.4. Simulation Wizard                                                     |    |

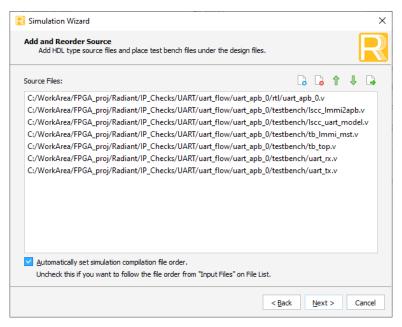

| U        | 5.5. Add and Reorder Source                                                |    |

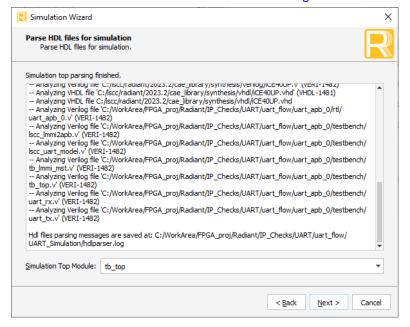

| _        | 5.6. Parse HDL Files for Simulation                                        |    |

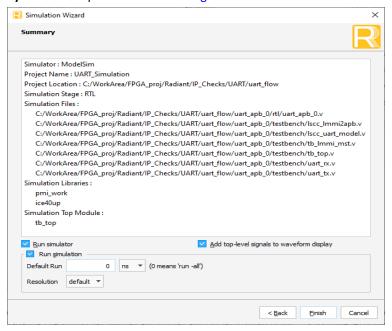

| _        | 5.7. Summary Window                                                        |    |

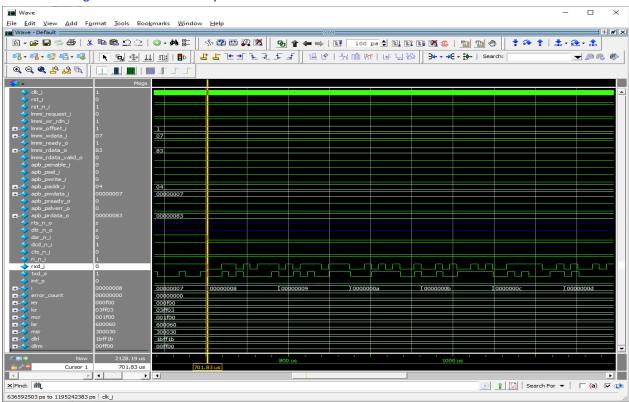

| Figure 6 | 5.8. Simulation Waveform                                                   | 32 |

|          |                                                                            |    |

|          |                                                                            |    |

|          |                                                                            |    |

| Table    | es                                                                         |    |

| Table 1. | .1. Summary of the UART 16550 IP                                           | 6  |

| Table 1. | .2. IP Validation Level                                                    | 8  |

| Table 3. | .1. Attributes List                                                        | 13 |

| Table 3. | .2. Attributes Descriptions                                                | 14 |

| Table 4. | .1. UART 16550 IP Core Signal Description                                  | 16 |

| Table 5. | .1. Registers Address Map                                                  | 18 |

| Table 5. | .2. Access Type Definition                                                 | 18 |

| Table 5. | .3. Receive Buffer Register                                                | 18 |

| Table 5. | .4. Transmitter Holding Register                                           | 19 |

| Table 5. | .5. Interrupt Enable Register                                              | 19 |

| Table 5. | .6. Interrupt Identification Register                                      | 20 |

| Table 5. | .7. Interrupt Control Function                                             | 20 |

| Table 5. | .8. FIFO Control Register                                                  | 21 |

| Table 5. | .9. Line Control Register                                                  | 21 |

| Table 5. | .10. MODEM Control Register                                                | 22 |

| Table 5. | .11. Line Status Control Register                                          | 24 |

| Table 5. | .12. Line Control Register                                                 | 25 |

| Table 5. | .13. Line Control Register                                                 | 26 |

| Table 5. | .14. Line Control Register                                                 | 26 |

| Table 5. | .15. Standard Baud Rates Grid with DLR Values for 55.296 MHz System Clock  | 27 |

| Table 6. | .1. Generated File List                                                    | 30 |

| Table A  | 1. Resource Utilization                                                    | 36 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Acronym | Definition                                  |  |  |

|---------|---------------------------------------------|--|--|

| APB     | Advanced Peripheral Bus                     |  |  |

| EIA     | Electronic Industries Association           |  |  |

| FIFO    | First In First Out                          |  |  |

| FPGA    | Field Programmable Gate Array               |  |  |

| GUI     | Graphical User Interface                    |  |  |

| LMMI    | Lattice Memory Mapped Interface             |  |  |

| MODEM   | Modulator-Demodulator                       |  |  |

| RTL     | Register Transfer Language                  |  |  |

| UART    | Universal Asynchronous Receiver/Transmitter |  |  |

6

# 1. Introduction

### 1.1. Overview of the IP

The Lattice Semiconductor UART (Universal Asynchronous Receiver/Transmitter) 16550 IP is designed for use in serial communication, supporting the RS-232, RS-422, RS-485, and Electronic Industries Association (EIA) standards, among others. The design features a receiver (serial to parallel converter) and a transmitter (parallel to serial converter), each controlled separately. The register set, data transfer protocol, and interrupt generation of this IP is compatible with the National Semiconductor PC16550D UART with integrated transmit and receive FIFOs which relieves the Host of excessive overhead.

## 1.2. Quick Facts

Table 1.1. Summary of the UART 16550 IP

| ID Dogginger out     | Supported FPGA Family    | All                                                                              |  |  |

|----------------------|--------------------------|----------------------------------------------------------------------------------|--|--|

| IP Requirements      | IP Version               | 1.3.0                                                                            |  |  |

|                      | Targeted Devices         | All                                                                              |  |  |

| Resource Utilization | Supported User Interface | LMMI (Lattice Memory Mapped Interface)*, APB (Advanced Peripheral Bus)           |  |  |

|                      | Resources                | Refer to Appendix A. Resource Utilization.                                       |  |  |

|                      | Lattice Implementation   | IP Core v1.x.x - Lattice Radiant™ Software 2.1 or later                          |  |  |

|                      | Cumthosis                | Lattice Synthesis Engine                                                         |  |  |

| Design Tool Support  | Synthesis                | Synopsys Synplify Pro® for Lattice                                               |  |  |

|                      | Simulation               | For a list of supported simulators, see the Lattice Radiant Software User Guide. |  |  |

### 1.3. Features

Key features of the UART 16550 IP include:

- Compatible with the National Semiconductor PC16550D UART (NS-PC16550D):

- Adds or deletes standard asynchronous communication bits (start, stop, and parity) to or from the serial data.

- Independently controlled transmit, receive, line status, and data set interrupts.

- MODEM control functions (CTS, RTS, DSR, DTR, RI, and DCD).

- False start bit detection.

- Complete status reporting capabilities.

- Line break generation and detection.

- Full prioritized interrupt system controls.

- FIFO mode transmitter and receiver, each are buffered with the 16-bytes FIFO to reduce the CPU overhead.

- Configurable data widths of 5, 6, 7, or 8 bits.

- Configurable stop bits 1 or 2 bits for transmit operations.

- Configurable Baud Rate support for Standard and Custom modes:

- In Standard mode, programmable divisor latch for baud rates provides fixed pre-defined values.

- In Custom mode, Baud Rate accepts any value from range 1-999999.

- Verilog RTL test bench.

## 1.4. Licensing Information

The UART 16550 IP is provided at no additional cost with the Lattice Radiant software. However, an IP-specific license string is required to enable full use of the UART 16550 IP Core in a complete, top-level design. For more information, contact your local Lattice Sales Office.

When the IP is used in the Lattice iCE40 UltraPlus devices, bit stream file cannot be generated without the license string. When the IP is used in FPGA devices built on the Lattice Nexus™ and Avant™ platforms, you can fully evaluate the IP through functional simulation and implementation (synthesis, map, place, and route) without an IP license string.

This IP supports Lattice's IP hardware evaluation capability which makes it possible to create versions of the IP that operate in hardware for a limited period (approximately four hours) without requiring a license string. It may also be used to evaluate the IP in hardware in the user-defined designs.

The IP evaluation setting is disabled by default and can be enabled/disabled within the Lattice Radiant software by performing the following steps:

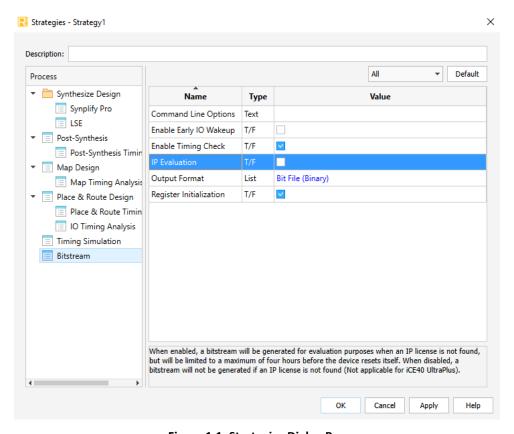

- Launch the Lattice Radiant software and select Project > Active Strategy > Bitstream Settings. This will open the Strategies dialog box as shown in Figure 1.1.

- 2. Enable bitstream generation for IP evaluation purposes by setting the IP Evaluation to True (checked) or disable this feature by setting the IP Evaluation to False (unchecked).

Figure 1.1. Strategies Dialog Box

## 1.5. IP Validation Summary

The IP is validated with the following synthesis tool: Synopsys Synplify Pro for Lattice or Lattice Synthesis Engine tool.

Table 1.2 shows the validation status for the UART 16550 IP . The ✓ mark indicates whether the IP has been validated for Simulation, Timing, or with Hardware and the ★ mark indicates otherwise.

**Table 1.2. IP Validation Level**

| Device Femily           | IP Version | Validation Level |             |        |          |  |

|-------------------------|------------|------------------|-------------|--------|----------|--|

| Device Family           | ir version | Simulation       | Compilation | Timing | Hardware |  |

| Lattice iCE40 UltraPlus | 1.3.0      | ✓                | ✓           | ✓      | *        |  |

| Lattice Nexus           | 1.3.0      | ✓                | ✓           | ✓      | √*       |  |

| Lattice Avant           | 1.3.0      | ✓                | ✓           | ✓      | √*       |  |

<sup>\*</sup>Note: Validated through hardware use cases, no isolated hardware validation was done.

## 1.6. Minimum Device Requirements

Refer to Appendix A. Resource Utilization for the minimum required resources to instantiate this IP.

## 1.7. Naming Conventions

### 1.7.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.7.2. Signal Names

Signal names that end with:

- *n* are active low (asserted when value is logic 0)

- *i* are input signals

- \_o are output signals

### 1.7.3. Host

The logic unit inside the FPGA interacts with the UART 16550 IP Core through either LMMI or APB.

### 1.7.4. Attribute Names

Attribute names in this document are formatted in title case and italicized (Attribute Name).

# 2. Functional Description

This section provides a detailed functional description of UART 16550 IP Core which includes information regarding clock and reset handling, and user interfaces.

### 2.1. IP Architecture Overview

The UART 16550 IP Core performs two main functions:

- Serial-to-parallel conversion on data characters received from an external UART device or a MODEM; and

- Parallel-to-serial conversion on data characters received from the Host located in the FPGA.

The Host can read the complete status of the UART at any time during the functional operation. Status information reported includes the type and condition of the transfer operations being performed by the UART 16550 IP Core, as well as any error conditions (parity, overrun, framing, or break interrupt).

The UART 16550 IP has a complete MODEM-control capability, and a processor-interrupt system. Interrupts can be programmed to your requirements, minimizing the computing required to handle the communications link.

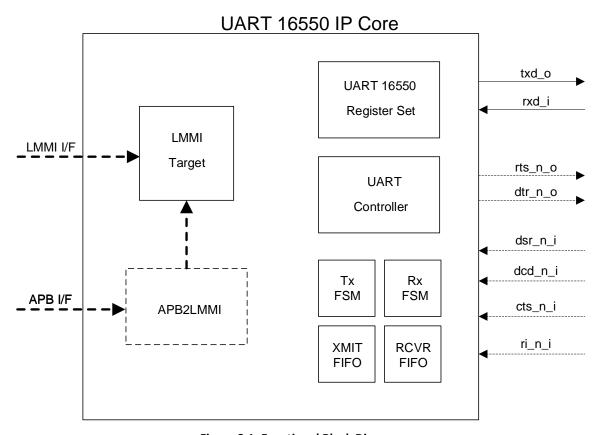

The registers of UART 16550 IP Core are accessed by the Host (FPGA internal components) through either Lattice Memory Mapped Interface (LMMI) or AMBA APB as selected by *Enable APB* attribute. The functional block diagram of UART 16550 IP Core is shown in Figure 2.1. The dashed lines in the figure are optional components/signals, which means they may not be available in the IP when disabled in the attribute.

Figure 2.1. Functional Block Diagram

### 2.2. Clocking and Reset

The UART 16550 IP requires a system clock: clk\_i. You need to provide this clock via an external source and route it to an appropriate pin on the FPGA. The system clock (externally sourced) provides a timing reference and is used to operate the IP's internal logic. Take note, the externally sourced clock frequency needs to match the system clock frequency set in the IP configuration GUI.

The UART 16550 IP contains an asynchronous active low reset: rst\_n\_i. When asserted, the output ports and registers are forced to their default values. The reset assertion can be asynchronous but reset negation should be synchronous. The IP contains internal logic to synchronously de-assert the internal reset once rst\_n\_i is de-asserted, so you do not need to worry about implementing your own de-assertion logic.

### 2.3. User Interfaces

### 2.3.1. Selectable Memory-Mapped Interface

The memory-mapped interface of UART 16550 IP is selected by the *Enable APB* attribute; it can be APB or LMMI. Register access are done via the selected memory-mapped interface. These interfaces are not described in this user guide, references to their respective specifications are provided below.

For LMMI interface, refer to the Lattice Memory Mapped Interface and Lattice Interrupt Interface (FPGA-UG-02039) document for information and timing diagram of the LMMI. Take note of the following information when checking LMMI timing diagram in the said document:

- Immi\_ready\_o is always asserted; thus, write and read transactions have no wait state.

- Read latency is one clock cycle.

For APB interface, refer to the AMBA 3 APB Protocol v1.0 Specification for information and timing diagram of the APB interface. Take note of the following information when checking APB timing diagram in the said document:

- Write transaction has one wait state.

- Read transaction has one wait state.

### 2.4. Programming Flow

### 2.4.1. Initialization

The following UART register fields should be set properly before performing UART transaction:

- Line Control Register: even\_parity\_sel, parity\_en, stop\_bit\_ctrl, char\_len\_sel

- Divisor Latch Registers: divisor\_msb, divisor\_lsb

These should match the corresponding setting in the communicating UART/MODEM for the serial transaction to be successful. Note that the reset values of these Register fields are configurable during IP generation. Thus, in some applications, initialization step is not necessary.

### 2.4.2. FIFO Interrupt Mode Operation

When Received Data Available Interrupt is enabled (IER.rda\_int\_en=1), Received Data Available and Character Timeout interrupts occur as follows:

- 1. The Receiver Data Available trigger is issued to the Host when the FIFO has reached its programmed trigger level, and the interrupt is cleared as soon as the FIFO falls below the programmed trigger level.

- 2. The IIR Receiver Data Available (int\_prio=2'b10) indication also occurs when the FIFO trigger level is reached, and like the interrupt, it is cleared when the FIFO drops below the trigger level.

- 3. The Data Ready Bit (LSR.data\_rdy) is set as soon as a character is transferred from the shift register to the RCVR FIFO. It is reset (logic low) when the FIFO is empty.

- 4. A FIFO character timeout interrupt occurs if all the following conditions exist:

- There is at least one character in the FIFO.

- The most recent serial character received was longer than four continuous character times ago (one character is eight data bits, one start bit, one parity bit and two stop bits).

- The most recent Host read of the FIFO was longer than four continuous character times ago.

- The timer resets when the Host reads one character from the RCVR FIFO.

- 5. With IER.thre\_int\_en set to 1'b1, the Transmitter Holding Register interrupt occurs when the XMIT FIFO is empty; it is cleared as soon as the Transmitter Holding Register is written to.

### 2.4.3. Transmit Operation

The steps for the transmitting character data through the UART 16550 IP Core is shown below. This step assumes that the IP core is not performing transmit operation or at least the XMIT FIFO is empty.

- 1. If MODEM control signals are used, set MCR.rts\_ctrl=1'b1. This asserts rts\_n\_o signal, telling the peripheral device that the UART would like to transmit data. In response to this, peripheral device asserts cts\_n\_i if it is ready to receive data.

- 2. Write data to THR. You can write up to 16-character data.

- 3. Set IER.thre\_int\_en=1'b1 to enable Transmit Holding Register Empty interrupt

- 4. Wait for Transmit Holding Register Empty interrupt to assert.

- Using interrupt: Wait for interrupt assertion and check that IIR[3:0]=4'b0010.

- Polling: Read LSR until the thr\_empty bit asserts. Note that Step 3 can be skipped for polling mode.

- 5. If you need to send more characters, write data to THR. You can write up to 16-character data.

- 6. Repeat Steps 4-5 until all characters are sent.

- 7. Optional: If MODEM control signals are used, poll LSR until xmitr\_empty bit is high. This ensure that the UART transmission of last character is completed. Set MCR.rts\_ctrl=1'b0 to negate the rts\_n\_o signal.

### 2.4.4. Receive Operation

The steps for the receiving character data through the UART 16550 IP Core is shown below. This step assumes that the IP core is not performing receive operation.

- 1. Optional: If MODEM control signals are used, set IER.ms\_int\_en=1'b1 to enable MODEM Status Interrupt. When interrupt occurs due to change in dsr\_n\_i signal (MSR.ddsr=1'b1) and MSR.cdsr=1'b1, this means the peripheral device is requesting to send data to UART. Set MCR.dtr\_ctrl=1 to indicate that UART is ready to receive data.

- 2. Enable the following interrupts:

- Received Data Available Interrupt (IER.rda\_int\_en=1'b1) to notify the host that received data in FIFO reaches trigger level setting (FCR.trig\_lvl) or when character timeout occurs.

- Receiver Line Status interrupt (IER.rls\_int\_en=1'b1) to notify the host of receive status such as error and break

condition.

- 3. Wait for Receive Data Available Interrupt or Character Timeout Interrupt. Wait for interrupt assertion and check that IIR[3:0]=4'b0100 (Receive Data Available) or 2'b1100 (Character Timeout). If Receiver Line Status Interrupt asserts (IIR[3:0]=4'b0110), read the LSR to determine the cause.

- 4. If Receiver Line Status Interrupt does not occur, read the character data from RBR:

- If Receive Data Available Interrupt occurs, read trigger level amount of data from RBR.

- If Character Timeout Interrupt occurs, read LSR. If LSR.data\_rdy=1'b1, read RBR. Continue reading RBR until LSR.data\_rdy becomes 1'b0.

- 5. Repeat Steps 3-4 until all expected data are received.

- 6. Optional: When interrupt occurs due to change in dsr\_n\_i signal (MSR.ddsr=1'b1) and MSR.cdsr=1'b0, this means the peripheral device is done sending data to UART. Set MCR.dtr\_ctrl=0 to indicate that UART is no longer available to receive data.

### 2.5. Operations Details

#### 2.5.1. Data Format

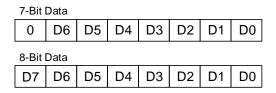

The character data is written to THR and read from RBR in little endian format as shown in Figure 2.2.

Figure 2.2. Tx/Rx Data Format

### 2.5.2. Timing Diagrams

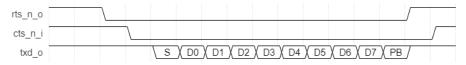

During transmission, data is shifted out by the transmitter logic in LSB first format as shown in Figure 2.3. This timing diagram shows the transmission of 1 character with flow control. UART IP Core asserts rts\_n\_o, MODEM cts\_n\_i signal as a response. The UART 16550 IP Core then sends the Start Bit, character data and Stop Bit on the txd o line.

Figure 2.3. Transmit Operation Timing Diagram with Flow Control Signals (1 byte)

When transmitting multiple data bytes, rts\_o and cts\_i are held low after the stop bit for the first byte to immediately start the next byte transfer. This is shown in Figure 2.4. In this diagram, one stop bit is generated.

Figure 2.4. Transmit Operation Timing Diagram with Flow Control Signals (2 bytes)

Figure 2.5 shows the transmit operation from the MODEM side. The MODEM asserts (logic 0) the dsr\_n\_i line signaling to the UART IP that it has data to send. The UART IP then asserts (logic 0) the dtr\_n\_o line when it is ready to receive data. The MODEM then initiates the transaction on the rxd\_i.

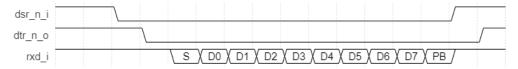

Figure 2.5. Receive Operation Timing Diagram with Flow Control Signals (1 byte)

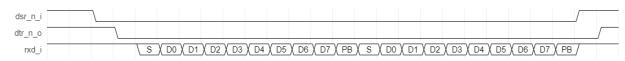

When receiving multiple data bytes, dsr\_n\_i and dtr\_n\_o are held low after the stop bit for the first byte so that the external MODEM device can immediately start the next byte transfer. This is shown in Figure 2.6.

Figure 2.6. Transmit Operation Timing Diagram with Flow Control Signals (2 bytes)

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

# 3. IP Parameter Description

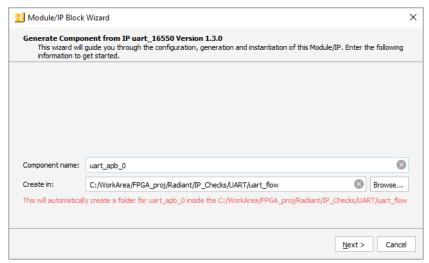

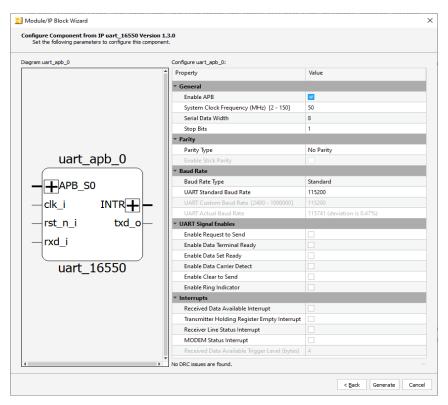

The configurable attributes of the UART 16550 IP are shown in Table 3.1 and are described in Table 3.2. You can configure the IP by setting the attributes accordingly in the IP Catalog's Module/IP wizard of the Lattice Radiant software.

**Table 3.1. Attributes List**

| Attribute                                     | Selectable Values                                                        | Default    | Dependency on Other Attributes                                                                                                                                                    |

|-----------------------------------------------|--------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General                                       |                                                                          |            | •                                                                                                                                                                                 |

| Enable APB                                    | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| System Clock Frequency (MHz) [2 - 150]        | 2–150                                                                    | 50         | _                                                                                                                                                                                 |

| Serial Data Width                             | 5, 6, 7, 8                                                               | 8          | _                                                                                                                                                                                 |

| Stop Bits                                     | 1, 2                                                                     | 1          | _                                                                                                                                                                                 |

| Parity                                        |                                                                          |            |                                                                                                                                                                                   |

| Parity Type                                   | No Parity, Even, Odd                                                     | No Parity  | _                                                                                                                                                                                 |

| Enable Stick Parity                           | Checked, Unchecked                                                       | Unchecked  | Active if Parity Type != No Parity                                                                                                                                                |

| Baud Rate                                     |                                                                          |            |                                                                                                                                                                                   |

| Baud Rate Type                                | Standard, Custom                                                         | Standard   | _                                                                                                                                                                                 |

| UART Standard Baud Rate                       | 2400, 4800, 9600, 14400,<br>19200, 28800, 38400,<br>56000, 57600, 115200 | 115200     | Active if Baud Rate Type == Standard                                                                                                                                              |

| UART Custom Baud Rate [2400 - 1000000]        | 2400-1000000                                                             | 115200     | Active if Baud Rate Type == Custom                                                                                                                                                |

| UART Actual Baud Rate                         | _                                                                        | Calculated | Calculated based on the formula:  Actual Baud Rate = (System Clock Frequency) / (16 × Divisor)  Where: Divisor = (System Clock Frequency) / (16 × (Standard or Custom Baud Rate)) |

| MODEM Signal Enables                          |                                                                          |            |                                                                                                                                                                                   |

| Enable Request to Send                        | Checked, Unchecked                                                       | Unchecked  |                                                                                                                                                                                   |

| Enable Data Terminal Ready                    | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Enable Data Set Ready                         | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Enable Data Carrier Detect                    | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Enable Clear to Send                          | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Enable Ring Indicator                         | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Interrupt                                     |                                                                          |            |                                                                                                                                                                                   |

| Received Data Available Interrupt             | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Transmitter Holding Register Empty Interrupt  | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Receiver Line Status Interrupt                | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| MODEM Status Interrupt                        | Checked, Unchecked                                                       | Unchecked  | _                                                                                                                                                                                 |

| Receiver FIFO Interrupt Trigger Level (bytes) | 1, 4, 8, 14                                                              | 4          | Active if <i>Received Data Available Interrupt</i> is checked                                                                                                                     |

### **Table 3.2. Attributes Descriptions**

| Attribute                    | Dependency on Other Attributes                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General                      |                                                                                                                                                                                                                                                                                                                                                                                           |

| Enable APB                   | Selects memory-mapped interface for register access by the host. Checked: AMBA APB Unchecked: LMMI                                                                                                                                                                                                                                                                                        |

| System Clock Frequency (MHz) | Specifies the target frequency of system clock. This is used for baud rate calculation.                                                                                                                                                                                                                                                                                                   |

| Serial Data Width            | Specifies the default data bit width of UART transactions by setting the reset value of char_len_sel field of Line Control Register. 7: Reset value is 2'b10. 8: Reset value is 2'b11.                                                                                                                                                                                                    |

| Stop Bits                    | Specifies the default number of stop bits to be transmitted and received by specifying the reset value of stop_bit_ctrl bit of Line Control Register.  1: Reset value is 1'b0.  2: Reset value is 1'b1.                                                                                                                                                                                   |

| Parity                       |                                                                                                                                                                                                                                                                                                                                                                                           |

| Parity Type                  | Specifies the absence/presence of parity as well as the default type (odd/even) of parity by setting the reset values of parity_en and even_parity_sel bits of Line Control Register.  No Parity: reset values are parity_en=1'b0 and even_parity_sel=1'b0  Even: reset values are parity_en=1'b1 and even_parity_sel=1'b1  Odd: reset values are parity_en=1'b1 and even_parity_sel=1'b0 |

| Enable Stick Parity          | Enables the generation and checking of Stick parity by specifying the reset value of stick_parity_en bit of Line Control Register. Checked: Reset value is 1'b1. Unchecked: Reset value is 1'b0.                                                                                                                                                                                          |

| Baud Rate                    |                                                                                                                                                                                                                                                                                                                                                                                           |

| Baud Rate Type               | Selects between Standard Baud Rate and Custom Baud Rate for the reset value of Divisor Latch Register.                                                                                                                                                                                                                                                                                    |

| Standard Baud Rate           | Specifies the baud rate of UART transactions from the standard baud rate options.                                                                                                                                                                                                                                                                                                         |

| Custom Baud Rate             | Specifies the baud rate of UART transactions based on user input.                                                                                                                                                                                                                                                                                                                         |

| Actual Baud Rate             | Calculates the actual baud rate that can be achieved based on Custom Baud Rate input.  This also specifies the reset values of Divisor Latch Register as follows:  ({divisor_msb,divisor_lsb}) = 'System Clock Frequency' / (16 × (Standard or Custom Baud Rate))                                                                                                                         |

| MODEM Signal Enables         |                                                                                                                                                                                                                                                                                                                                                                                           |

| Enable Request to Send       | Enables the presence of rts_n_o signal on the generated IP. Checked: Signal is available. Unchecked: Signal is removed.                                                                                                                                                                                                                                                                   |

| Enable Data Terminal Ready   | Enables the presence of dtr_n_o signal on the generated IP. Checked: Signal is available. Unchecked: Signal is removed.                                                                                                                                                                                                                                                                   |

| Enable Data Set Ready        | Enables the presence of dsr_n_i signal on the generated IP. Checked: Signal is available. Unchecked: Signal is removed and internally set to 1'b0 (asserted).                                                                                                                                                                                                                             |

| Enable Data Carrier Detect   | Enables the presence of dcd_n_i signal on the generated IP. Checked: Signal is available. Unchecked: Signal is removed and internally set to 1'b1 (negated).                                                                                                                                                                                                                              |

| Enable Clear to Send         | Enables the presence of cts_n_i signal on the generated IP. Checked: Signal is available. Unchecked: Signal is removed and internally set to 1'b1 (asserted). This should be unchecked only if the peripheral device is can always accommodate data transmission.                                                                                                                         |

| Attribute                             | Dependency on Other Attributes                                                         |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------|--|--|

| Enable Ring Indicator                 | Enables the presence of ri_n_i signal on the generated IP.                             |  |  |

|                                       | Checked: Signal is available.                                                          |  |  |

|                                       | Unchecked: Signal is removed and internally set to 1'b1 (negated).                     |  |  |

| Interrupts                            |                                                                                        |  |  |

| Received Data Available Interrupt     | Specifies the reset value of rda_int_en bit of Interrupt Enable Register.              |  |  |

|                                       | Checked: Reset value is 1'b1.                                                          |  |  |

|                                       | Unchecked: Reset value is 1'b0.                                                        |  |  |

| Transmitter Holding Register Empty    | Specifies the reset value of thre_int_en bit of Interrupt Enable Register thre_int_en. |  |  |

| Interrupt                             | Checked: Reset value is 1'b1.                                                          |  |  |

|                                       | Unchecked: Reset value is 1'b0.                                                        |  |  |

|                                       | It is recommended to uncheck this setting to avoid asserting interrupt upon power-up.  |  |  |

| Receiver Line Status Interrupt        | Specifies the reset value of rls_int_en bit of Interrupt Enable Register.              |  |  |

|                                       | Checked: Reset value is 1'b1.                                                          |  |  |

|                                       | Unchecked: Reset value is 1'b0.                                                        |  |  |

| MODEM Status Interrupt                | Specifies the reset value of ms_int_en bit of Interrupt Enable Register.               |  |  |

|                                       | Checked: Reset value is 1'b1.                                                          |  |  |

|                                       | Unchecked: Reset value is 1'b0.                                                        |  |  |

| Receiver FIFO Interrupt Trigger Level | Specifies the reset value of trig_lvl field of FIFO Control Register.                  |  |  |

| (bytes)                               | 1: Reset value is 2'b00.                                                               |  |  |

|                                       | 4: Reset value is 2'b01.                                                               |  |  |

|                                       | 8: Reset value is 2'b10.                                                               |  |  |

|                                       | 14: Reset value is 2'b11.                                                              |  |  |

# 4. Signal Description

This section describes the UART 16550 IP ports.

Table 4.1. UART 16550 IP Core Signal Description

| Port Name          | 1/0  | Width | Description                                                                                                                                                                                                                                                                                 |  |

|--------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock and Reset    |      |       |                                                                                                                                                                                                                                                                                             |  |

| clk_i              | In   | 1     | System clock.                                                                                                                                                                                                                                                                               |  |

| rst_n_i            | In   | 1     | Asynchronous active low reset. The reset assertion can be asynchronous but reset negation should be synchronous. When asserted, output ports and registers are forced to their reset values.                                                                                                |  |

| Interrupt Port     |      |       |                                                                                                                                                                                                                                                                                             |  |

| int_o              | Out  | 1     | Interrupt signal.                                                                                                                                                                                                                                                                           |  |

| Serial/MODEM Inter | face |       |                                                                                                                                                                                                                                                                                             |  |

| txd_o              | Out  | 1     | Serial Output. Serial data output to the communication link. Reset value: 1'b1                                                                                                                                                                                                              |  |

| rxd_i              | In   | 1     | Serial Input. Serial data input from the communication link.                                                                                                                                                                                                                                |  |

| rts_n_o            | Out  | 1     | Request to Send. When asserted, this informs the peripheral device (MODEM) that the UART is ready to exchange data. This signal is controlled by writing to the rts_ctrl bit of MODEM Control Register.  Reset value: 1'b1                                                                  |  |

| dtr_n_o            | Out  | 1     | Data Terminal Ready. When low, this informs the MODEM that the UART is ready to establish a communication link This signal is controlled by writing to the dtr_ctrl bit of MODEM Control Register.  Reset value: 1'b1                                                                       |  |

| dsr_n_i            | In   | 1     | Data Set Ready. When low, this indicates that the peripheral device (MODEM) is ready to establish a communication link with the UART.                                                                                                                                                       |  |

| dcd_n_i            | In   | 1     | Data Carrier Detect. When low, this indicates that the peripheral device (MODEM) detected the data carrier.                                                                                                                                                                                 |  |

| cts_n_i            | In   | 1     | Clear to Send. When low, this indicates that the peripheral device (MODEM) is ready exchange data. When this signal transitions to high logic in the middle of character transmission, the current character is completed, and the next character is pended uthis signal becomes low again. |  |

| ri_n_i             | In   | 1     | Ring Indicator. When low, indicates that the peripheral device (MODEM) has received a telephone-ringing signal.                                                                                                                                                                             |  |

| LMMI Interface*    |      |       |                                                                                                                                                                                                                                                                                             |  |

| Immi request i     | In   | 1     | Start transaction.                                                                                                                                                                                                                                                                          |  |

| lmmi_wr_rdn_i      | In   | 1     | Write = 1'b1, Read = 1'b0                                                                                                                                                                                                                                                                   |  |

| lmmi_offset_i      | In   | 4     | Register offset, starting at offset 0                                                                                                                                                                                                                                                       |  |

| lmmi_wdata_i       | In   | 8     | Output data bus                                                                                                                                                                                                                                                                             |  |

| lmmi_rdata_o       | Out  | 8     | Input data bus                                                                                                                                                                                                                                                                              |  |

| lmmi_rdata_valid_o | Out  | 1     | Read transaction is complete and Immi_rdata_o contains valid data.                                                                                                                                                                                                                          |  |

| lmmi_ready_o       | Out  | 1     | IP is ready to receive a new transaction. This is always asserted (tied to 1'b1).                                                                                                                                                                                                           |  |

| APB Interface*     |      |       |                                                                                                                                                                                                                                                                                             |  |

| apb_psel_i         | In   | 1     | Select signal. Indicates that the completer device is selected, and a data transfer is required.                                                                                                                                                                                            |  |

| apb_paddr_i        | In   | 6     | Address signal.                                                                                                                                                                                                                                                                             |  |

| apb_pwdata_i       | In   | 32    | Write data signal. Bits [31:8] are not used.                                                                                                                                                                                                                                                |  |

| apb_pwrite_i       | In   | 1     | Direction signal. Write = 1, Read = 0                                                                                                                                                                                                                                                       |  |

| apb_penable_i      | In   | 1     | Enable signal. Indicates the second and subsequent cycles of an APB transfer.                                                                                                                                                                                                               |  |

| apb_pready_o       | Out  | 1     | Ready signal. Indicates transfer completion. The completer uses this signal to extend an APB transfer.                                                                                                                                                                                      |  |

17

| Port Name     | I/O | Width | Description                                                              |  |

|---------------|-----|-------|--------------------------------------------------------------------------|--|

| apb_pslverr_o | Out | 1     | Error signal. Indicates a transfer failure. This signal is tied to 1'b0. |  |

| apb_prdata_o  | Out | 32    | Read data signal. Bits [31:8] are not used.                              |  |

<sup>\*</sup>Note: If Enable APB is Checked, APB Interface generated. Otherwise, LMMI Interface is generated.

# 5. Register Description

The register address map, shown in Table 5.1, specifies the available IP Core registers. The offset of each register is dependent on the *Enable APB* attribute setting as follows:

- LMMI (Unchecked): the offset increments by 1

- APB (Checked): the offset increments by four to allow easy interfacing with the Processor and System Buses. In this case, each register is 32-bit wide wherein the lower 8 bits are used, and the upper 24 bits are unused. The unused bits are treated as reserved write access is ignored and read access returns 0.

Table 5.1. Registers Address Map

| Offset<br>LMMI | Offset<br>APB  | Register Name | Access Type | Description                                                         |

|----------------|----------------|---------------|-------------|---------------------------------------------------------------------|

| 0x00           | 0x00           | RBR           | RO          | Receive Buffer Register. Active when LCR.dlab=0.                    |

| 0x00           | 0x00           | THR           | wo          | Transmitter Holding Register. Active when LCR.dlab=0.               |

| 0x01           | 0x04           | IER           | RW          | Interrupt Enable Register. Active when LCR.dlab=0.                  |

| 0x02           | 0x08           | IIR           | RO          | Interrupt Identification Register.                                  |

| 0x02           | 0x08           | FCR           | WO          | FIFO Control Register.                                              |

| 0x03           | 0x0C           | LCR           | RW          | Line Control Register.                                              |

| 0x04           | 0x10           | MCR           | RW          | MODEM Control Register.                                             |

| 0x05           | 0x14           | LSR           | RO          | Line Status Register.                                               |

| 0x06           | 0x18           | MSR           | RO          | MODEM Status Register.                                              |

| 0x00           | 0x00           | DLR_LSB       | RW          | Divisor Latch Register LSB. Active when LCR.dlab=1.                 |

| 0x01           | 0x04           | DLR_MSB       | RW          | Divisor Latch Register MSB. Active when LCR.dlab=1.                 |

| 0x07 –<br>0x0F | 0x1C -<br>0x3C | Reserved      | RSVD        | Reserved. Write access is ignored and 0 is returned on read access. |

The behavior of registers to write and read access is defined by its access type, which is defined in Table 5.2.

Table 5.2. Access Type Definition

| Access Type | Behavior on Read Access | Behavior on Write Access |

|-------------|-------------------------|--------------------------|

| RO          | Returns register value  | Ignores write access     |

| WO          | Returns 0               | Updates register value   |

| RW          | Returns register value  | Updates register value   |

| RSVD        | Returns 0               | Ignores write access     |

# 5.1. Receive Buffer Register (RBR)

The Receive Buffer Register is the interface to the Receiver Buffer/FIFO (RCVR FIFO). Reading from this register pops and returns the output data in the RCVR FIFO. If read is performed during RCVR FIFO empty, the last data in the FIFO is returned.

This register can be accessed when LCR.dlab=0.

**Table 5.3. Receive Buffer Register**

| Field | Name    | Access | Width | Reset |

|-------|---------|--------|-------|-------|

| [7:0] | rx_data | RO     | 8     | 0x00  |

#### rx data

Receive Data. Contains the received data from UART.

## 5.2. Transmitter Holding Register (THR)

The Transmitter Holding Register is the interface to the Transmitter Buffer/FIFO (XMIT FIFO). Writing to this register pushes the write data to the XMIT FIFO. If write is performed during XMIT FIFO full, data is lost. The host can only know if the XMIT FIFO is empty or not (via LSR.thr\_empty), it cannot know how many characters are currently in the XMIT FIFO. Thus, it is recommended to initiate the write sequence to this register only when XMIT FIFO is empty wherein the host can write up to 16-character data.

This register can be accessed when LCR.dlab=0.

**Table 5.4. Transmitter Holding Register**

| Field | Name    | Access | Width | Reset |

|-------|---------|--------|-------|-------|

| [7:0] | tx_data | WO     | 8     | 0x00  |

tx data

Transmit Data. Contains the transmit data to UART.

## 5.3. Interrupt Enable Register (IER)

This register enables the four types of UART interrupts. When enabled, each interrupt can individually activate the interrupt (int\_o) output signal. Each interrupt can individually be enabled/disabled by writing to the corresponding bit in the IER. Disabling an interrupt prevents it from being indicated as active in the IIR and from activating the int\_o output signal. On the other hand, the UART status including Line Status and MODEM Status Registers are not affected by IER setting.

This register can be accessed when LCR.dlab=0.

**Table 5.5. Interrupt Enable Register**

| Field | Name        | Access | Width | Reset                                                            |

|-------|-------------|--------|-------|------------------------------------------------------------------|

| [7:4] | reserved    | RSVD   | 3     | -                                                                |

| [3]   | ms_int_en   | RW     | 1     | Refer to attribute: MODEM Status Interrupt                       |

| [2]   | rls_int_en  | RW     | 1     | Refer to attribute: Receiver Line Status Interrupt               |

| [1]   | thre_int_en | RW     | 1     | Refer to attribute: Transmitter Holding Register Empty Interrupt |

| [0]   | rda_int_en  | RW     | 1     | Refer to attribute: Received Data Available Interrupt            |

ms int en

MODEM Status Interrupt Enable. This bit controls the enabling of MODEM Status Interrupt.

- 1'b0 Interrupt is disabled

- 1'b1 Interrupt is enabled

- rls int en

Receiver Line Status Interrupt Enable. This bit controls the enabling of Receiver Line Status Interrupt.

- 1'b0 Interrupt is disabled

- 1'b1 Interrupt is enabled

- thre int en

Transmitter Holding Register Empty Interrupt Enable. This bit controls the enabling of Transmitter Holding Register Empty Interrupt.

- 1'b0 Interrupt is disabled

- 1'b1 Interrupt is enabled

- rda\_int\_en

Received Data Available Interrupt Enable. This bit controls the enabling of Received Data Available Interrupt and Timeout Interrupt (timeout\_int).

- 1'b0 Interrupt is disabled

- 1'b1 Interrupt is enabled

## 5.4. Interrupt Identification Register (IIR)

To minimize software overhead during data character transfers, the UART 16550 IP Core prioritizes interrupts into four levels and records these in the Interrupt Identification Register. When the host reads the IIR, the IP Core only indicates the highest priority pending interrupt. After clearing the source of the highest priority pending interrupt, IIR updates to the next priority pending interrupt. The summary of controlling (asserting and clearing) the interrupt is described in Table 5.7.

**Table 5.6. Interrupt Identification Register**

| Field | Name        | Access | Width | Reset  |

|-------|-------------|--------|-------|--------|

| [7:6] | fifos_en    | RO     | 2     | 2'b11  |

| [5:4] | reserved    | RSVD   | 2     | _      |

| [3]   | timeout_int | RO     | 1     | 1'b0   |

| [2:1] | int_prio    | RO     | 2     | 2'b00* |

| [0]   | int_pending | RO     | 1     | 1'b1*  |

\*Note: The reset value of IER.thre\_int\_en is set by the *Transmitter Holding Register Empty Interrupt* attribute. Thus, depending on the value of this attribute, the value of int\_prio and int\_pending may immediately change after reset negation. Below are the observable reset values of {int\_prio, int\_pending} based on the *Transmitter Holding Register Empty Interrupt* attribute:

- When Unchecked, {int\_prio, int\_pending} = 3'b001 (No interrupt pending).

- When Checked, {int prio, int pending} = 3'b010 (Transmitter Holding Register Empty Interrupt pending).

- fifos en

FIFOs Enabled. Fixed to logic 2'b11 to indicate that both write and read FIFOs are enabled.

timeout\_int

Timeout Interrupt. This interrupt indicates that there is at least one character in RCVR FIFO and FIFO is not updated for a duration of four-character UART transaction. See the Programming Flow section for more information.

- 1'b0 Interrupt is negated

- 1'b1 Interrupt is asserted

- int\_prio

Interrupt Priority. This bit indicates the highest priority pending interrupt. For example, if all interrupts are asserted, int\_prio returns 2'b11 when read. After Receiver Line Status Interrupt is cleared, int\_prio becomes 2'b10 to indicate the next high priority pending interrupt.

- 2'b11 Receiver Line Status Interrupt

- 2'b10 Received Data Available Interrupt

- 2'b01 Transmitter Holding Register Empty Interrupt

- 2'b00 MODEM Status Interrupt

- int\_pending

Interrupt Pending. This bit indicates that an interrupt is pended.

- 1'b0 Interrupt is pending according to int\_prio and timeout\_int.

- 1'b1 No pending interrupt

**Table 5.7. Interrupt Control Function**

| IIR[3:0] | Priority | Interrupt Type*                          | Interrupt Assertion Cause                                                                                  | Interrupt Clearing Control                                                        |

|----------|----------|------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 4'b0001  | -        | None                                     | None                                                                                                       | _                                                                                 |

| 4'b0110  | Highest  | Receiver Line<br>Status                  | Overrun Error or Parity Error or<br>Framing Error or Break Interrupt                                       | Reading the Line Status Register                                                  |

| 4'b0100  | Second   | Received Data<br>Available               | RCVR FIFO reached the trigger level (FCR.trig_lvl)                                                         | Reading the Receiver Buffer Register until<br>RCVR FIFO drops below trigger level |

| 4'b1100  | Second   | Character Timeout                        | RCVR FIFO has at least 1 character and has not been updated for a duration of 4-character UART transaction | Reading the Receiver Buffer Register                                              |

| 4'b0010  | Third    | Transmitter<br>Holding Register<br>Empty | XMIT FIFO is empty                                                                                         | Writing to XMIT FIFO.                                                             |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

| IIR[3:0] | Priority | Interrupt Type* | Interrupt Assertion Cause             | Interrupt Clearing Control         |

|----------|----------|-----------------|---------------------------------------|------------------------------------|

| 4'b0000  | Fourth   | MODEM Status    | Clear to Send or Data Set Ready or    | Reading the MODEM Status Registers |

|          |          |                 | Ring Indicator or Data Carrier Detect |                                    |

<sup>\*</sup>Note: If the interrupt type is disabled in IER, the interrupt control function treats the interrupt as not asserted even if the source of interrupt is asserted. Hence, the IIR value is affected by the IER.

## 5.5. FIFO Control Register (FCR)

This is a write only register at the same offset as the IIR, which is a read only register. This register is used to control the XMIT FIFO and XCVR FIFO.

**Table 5.8. FIFO Control Register**

| Field | Name                  | Access | Width | Reset                                                     |

|-------|-----------------------|--------|-------|-----------------------------------------------------------|

| [7:6] | trig_lvl              | WO     | 2     | Refer to attribute: Receiver FIFO Interrupt Trigger Level |

| [5:4] | reserved              | RSVD   | 2     | -                                                         |

| [3]   | reserved <sup>1</sup> | RSVD   | 1     | -                                                         |

| [2]   | xmit_fifo_rst         | WO     | 1     | 1'b0                                                      |

| [1]   | rcvr_fifo_rst         | wo     | 1     | 1'b0                                                      |

| [0]   | reserved <sup>2</sup> | RSVD   | 1     | -                                                         |

#### Notes:

- 1. DMA signaling of NS-PC16550D is not implemented.

- 2. FIFO enable control is not implemented because FIFO is always enabled.

- trig lvl

Sets trigger level of Received Data Available interrupt. See the Programming Flow section for more information.

- 2'b00 Trigger level 1 byte

- 2'b01 Trigger level 4 bytes

- 2'b10 Trigger level 8 bytes

- 2'b11 Trigger level 14 bytes

- xmit\_fifo\_rst

Resets the XMIT FIFO. This bit is auto clear, after writing 1'b1 to this bit it automatically clears to 1'b0.

- 1'b0 Writing 0 is ignored

- 1'b1 Resets XMIT FIFO for 1 clock cycle. FIFO content is cleared.

- rcvr fifo rst

Resets the RCVR FIFO. This bit is auto clear, after writing 1'b1 to this bit it automatically clears to 1'b0.

- 1'b0 Writing 0 is ignored

- 1'b1 Resets RCVR FIFO for 1 clock cycle. FIFO content is cleared.

# 5.6. Line Control Register (LCR)

This configures character length, number stop bits, and parity bits. The most significant bit of the line control register defines the state of the DLAB (Divisor Latch Access Bit) and affects the selection of certain UART Transceiver registers.

**Table 5.9. Line Control Register**

| Field | Name            | Access | Width | Reset                                   |

|-------|-----------------|--------|-------|-----------------------------------------|

| [7]   | dlab            | RW     | 1     | 1'b0                                    |

| [6]   | break_ctrl_en   | RW     | 1     | 1'b0                                    |

| [5]   | stick_parity_en | RW     | 1     | Refer to attribute: Enable Stick Parity |

| [4]   | even_parity_sel | RW     | 1     | Refer to attribute: Parity Type         |

| [3]   | parity_en       | RW     | 1     | Refer to attribute: Parity Type         |

| [2]   | stop_bit_ctrl   | RW     | 1     | Refer to attribute: Stop Bits           |

22

| Field | Name         | Access | Width | Reset                                 |

|-------|--------------|--------|-------|---------------------------------------|

| [1:0] | char_len_sel | RW     | 2     | Refer to attribute: Serial Data Width |

#### dlab

Divisor Latch Access Bit. The RBR/THR and IER shares offset address with DLR\_LSB and DLR MSB respectively. This bit selects which registers are enabled for access from the host.

- 1'b0 Enables access to RBR/THR and IER

- 1'b1 Enables access to DLR LST and DLR LSB

- break ctrl en

Break Control Enable. When break control enabled, it causes serial output (txd\_o) to go and stay at logic 0, which is interpreted as long stream of 0 bits by the receiving UART - the *break condition*. The Break Control Bit acts only on txd\_o and does not control the transmitter logic.

- 1'b0 Disables break control

- 1'b1 Enables break control

- stick parity en

Stick Parity Bit. When Bits 3, 4 and 5 of this register are logic 1, the parity bit is transmitted and checked as a logic 0. When Bits 3 and 5 are logic 1 and Bit 4 is logic 0 then the parity bit is transmitted and checked as a logic 1. Stick parity is usually used for checking the parity check behavior of the external UART/MODEM. The parity bit will "stick" if there is an error in the data bits, regardless of the next data packet correctness, until it is cleared.

- 1'b0 Disables stick parity