# **System Memory Module**

IP Version: v2.5.0

# **User Guide**

FPGA-IPUG-02073-2.4

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

# **Contents**

| Content | S                                           | 3  |

|---------|---------------------------------------------|----|

|         | ations in This Document                     |    |

| 1. Inti | roduction                                   | 8  |

| 1.1.    | Overview of the IP                          | 8  |

| 1.2.    | Quick Facts                                 | 8  |

| 1.3.    | IP Support Summary                          | 8  |

| 1.4.    | Features                                    | g  |

| 1.5.    | Licensing and Ordering Information          | 10 |

| 1.6.    | Hardware Support                            | 10 |

| 1.7.    | Minimum Device Requirements                 | 10 |

| 1.8.    | Naming Conventions                          | 10 |

| 1.8     | 3.1. Nomenclature                           | 10 |

| 1.8     | 3.2. Signal Names                           | 10 |

| 2. Fur  | nctional Description                        | 11 |

| 2.1.    | IP Architecture Overview                    | 11 |

| 2.2.    | Clocking                                    | 12 |

| 2.2     | 2.1. Clocking Overview                      | 12 |

| 2.3.    | Reset                                       | 13 |

| 2.3     | 3.1. Reset Overview                         | 13 |

| 2.3     | 8.2. Reset Timing Diagram                   | 13 |

| 2.4.    | User Interfaces                             |    |

| 2.4     | -1. AHB-Lite                                | 14 |

| 2.4     |                                             |    |

| 2.4     |                                             |    |

| 2.4     | .4. AXI4 Stream                             | 14 |

| 2.5.    | Memory Implementation                       | 14 |

| 2.6.    | System Memory Error Information             | 17 |

| 2.7.    | Arbitration                                 |    |

| 2.7     | '.1. Arbitration in the AXI4 Interface      | 18 |

| 2.7     | '.2. Arbitration in the AHBL Interface      | 20 |

| 2.8.    | Initialization Format                       | 21 |

| 2.9.    | AXI4 Atomic Access                          | 22 |

| 2.9     | 0.1. Exclusive Access Restrictions          | 22 |

| 2.9     | 0.2. Exclusive Access Sequence              | 24 |

| 2.9     | ·                                           |    |

| 2.9     |                                             |    |

| 3. IP F | Parameter Description                       | 28 |

| 3.1.    | General                                     | 28 |

| 3.2.    | Port SO Settings                            | 29 |

| 3.3.    | Port S1 Settings                            | 30 |

| 3.4.    | IP Parameter Settings for Example Use Cases | 31 |

| 4. Sign | nal Description                             | 32 |

| 4.1.    | Clock Interface                             | 32 |

| 4.2.    | Reset Interface                             | 32 |

| 4.3.    | User-Interface                              | 32 |

|         | gister Description                          |    |

| -       | ample Design                                |    |

| 6.1.    | Example Design Supported Configuration      |    |

| 6.2.    | Overview of the Example Design and Features |    |

| 6.3.    | Example Design Components                   |    |

| 6.4.    | Test Cases                                  |    |

| 6.5.    | Lattice RISC-V Microcontroller              |    |

|         |                                             |    |

| 6.6.      | System Memory IP                               | 40 |

|-----------|------------------------------------------------|----|

| 6.7.      | Simulation the Example Design                  |    |

| 7. Design | gning with the IP                              | 44 |

| 7.1.      | Generating and instantiating the IP            |    |

| 7.1.1     |                                                |    |

| 7.2.      | Design Implementation                          | 46 |

| 7.3.      | Timing Constraints                             | 46 |

| 7.4.      | Physical Constraints                           | 46 |

| 7.5.      | Specifying the Strategy                        | 46 |

| 7.6.      | Running Functional Simulation                  | 47 |

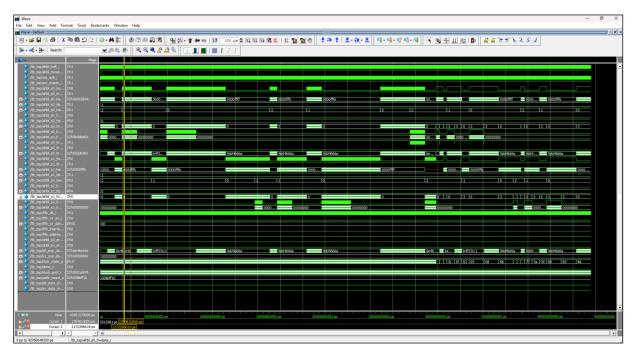

| 7.6.1     | 1. Simulation Results                          | 48 |

| 8. Debu   | ugging                                         | 49 |

| 8.1.      | Debug Methods                                  | 49 |

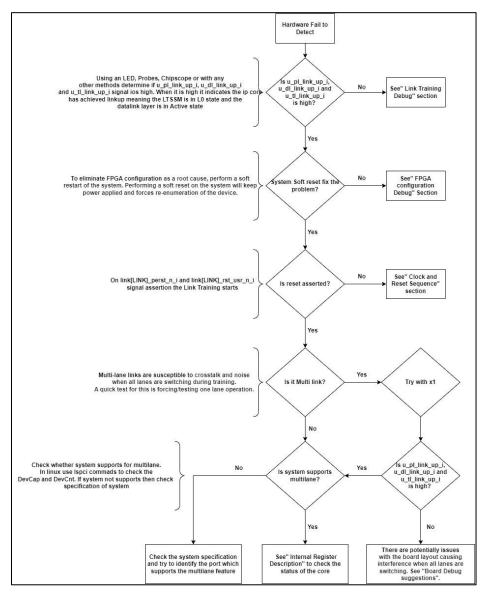

| 8.1.1     | 1. Hardware Detection Failure                  | 49 |

| 8.2.      | Debug Tools                                    | 49 |

| 9. Desig  | gn Considerations                              | 50 |

| 9.1.      | Design Considerations for External Programming | 50 |

| 9.2.      | Design Considerations for Memory Storage       | 50 |

| Appendix  | A. Resource Utilization                        | 51 |

|           | es                                             |    |

| Technical | Support Assistance                             | 53 |

|           | - · · · · · · · · · · · · · · · · · · ·        |    |

# **Figures**

| Figure 2.1. System Memory Module IP Core Block Diagram                               | 11 |

|--------------------------------------------------------------------------------------|----|

| Figure 2.2. System Memory Module IP Clock Domain Block Diagram                       |    |

| Figure 2.3. Reset Timing Diagram                                                     |    |

| Figure 2.4. Dual Port AXI Interface (Read Arbitration)                               |    |

| Figure 2.5. Dual Port AXI Interface (Write Arbitration)                              |    |

| Figure 2.6. Dual Port AHBL Interface Arbitration (Read Transaction)                  |    |

| Figure 2.7. Dual Port AHBL Interface Arbitration (Write Transaction)                 | 21 |

| Figure 2.8. Exclusive Access Sequence                                                | 24 |

| Figure 2.9. Successful Atomic Access Transaction                                     | 25 |

| Figure 2.10. Failed Atomic Access Transaction                                        | 26 |

| Figure 2.11. Atomic Access Exclusivity Granularity                                   |    |

| Figure 6.1. System Memory IP in Propel SoC Project                                   |    |

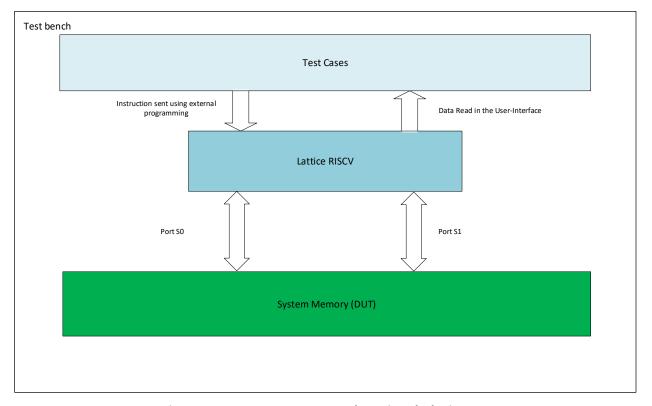

| Figure 6.2. System Memory Example Design Block Diagram                               | 40 |

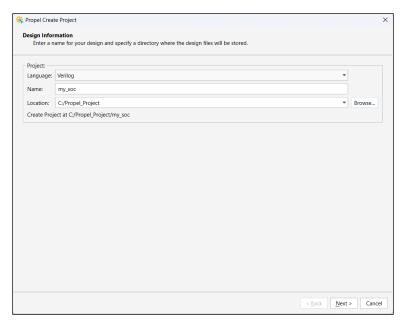

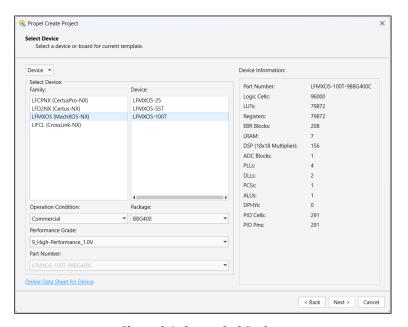

| Figure 6.3. Create SoC Project                                                       | 41 |

| Figure 6.4. Create SoC Project                                                       | 41 |

| Figure 6.5. Instantiating System Memory IP Module                                    | 42 |

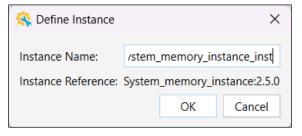

| Figure 6.6. Defining Instances                                                       |    |

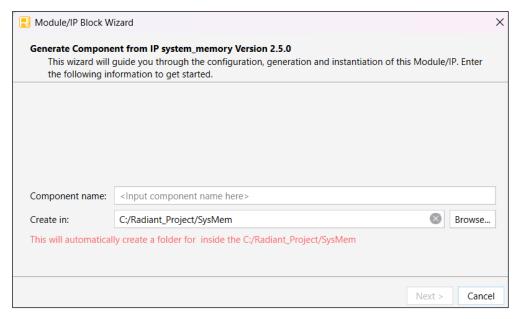

| Figure 7.1. Module/IP Block Wizard                                                   | 44 |

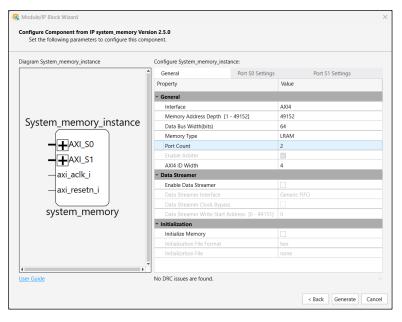

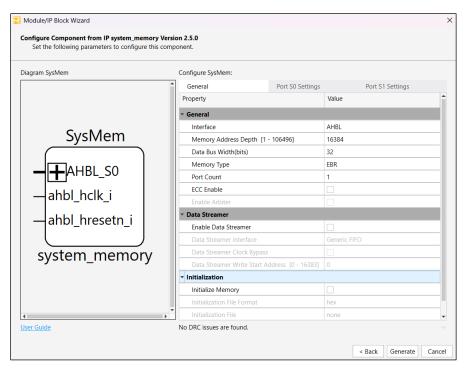

| Figure 7.2. IP Configuration                                                         | 45 |

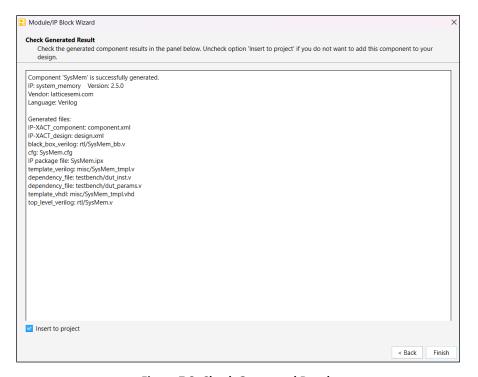

| Figure 7.3. Check Generated Result                                                   |    |

| Figure 7.4. Timing Constraint File (.pdc) for the System Memory IP                   | 46 |

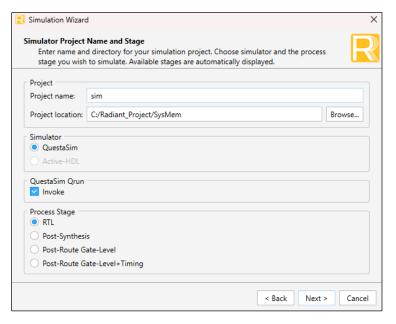

| Figure 7.5. Simulation Wizard                                                        | 47 |

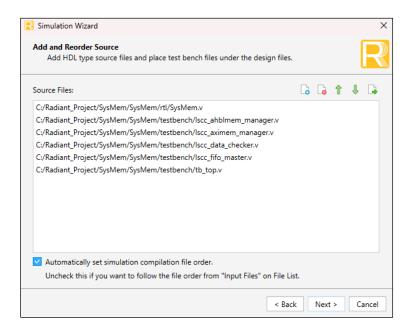

| Figure 7.6. Add and Reorder Source                                                   | 47 |

| Figure 7.7. Simulation Waveform                                                      | 48 |

| Figure 8.1. Hardware Detection Failure Debugging Flow                                | 49 |

| Tables                                                                               |    |

| Table 1.1. Summary of the System Memory Module IP                                    | c  |

| Table 1.2. System Memory Module IP Support Readiness                                 |    |

| Table 2.1. User Interfaces and Supported Protocols                                   |    |

| Table 2.2. System Core Memory Type – AHB-Lite                                        |    |

| Table 2.3. System Core Memory Type – ARIS—Lite                                       |    |

| Table 2.4. System Core Memory Implementation                                         |    |

| Table 2.5. Features Supported per Memory Block                                       |    |

| Table 2.6. ECC Implementation per Memory Block                                       |    |

| Table 2.7. Allowable Combination of Features for System Memory when INTERFACE = AHBL |    |

| Table 2.8. System Memory Error                                                       |    |

| Table 2.9. Request Information Atomic Access                                         |    |

| Table 3.1. General Attributes                                                        |    |

| Table 3.2. Port SO Settings                                                          |    |

| Table 3.3. Port S1 Settings                                                          |    |

| Table 3.4. IP Parameter Settings for Example Use Cases                               |    |

| Table 4.1. Clock Ports                                                               |    |

| Table 4.2. Reset Ports                                                               |    |

| Table 4.3. AHBL Ports                                                                |    |

| Table 4.4. AXI Ports                                                                 |    |

| Table 4.5. FIFO Streamer Ports                                                       |    |

| Table 4.6. AXI4 Streamer Ports                                                       |    |

| Table 4.7. ECC Ports                                                                 |    |

| Table 6.1. System Memory IP Configuration Supported by the Example Design | 38 |

|---------------------------------------------------------------------------|----|

| Table 7.1. Generated File List                                            |    |

| Table A.1. Resource Utilization                                           | 51 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                |

|--------------|-------------------------------------------|

| AHB-L        | Advanced High-Performance Bus – Lite      |

| AMBA         | Advanced Microcontroller Bus Architecture |

| AXI          | Advanced eXtensible Interface             |

| DUT          | Device Under Test                         |

| EBR          | Embedded Block RAM                        |

| ECC          | Error Correction Code                     |

| FIFO         | First In, First Out                       |

| FPGA         | Field Programmable Grid Array             |

| GUI          | Graphical User Interface                  |

| HDL          | Hardware Description Language             |

| IP           | Intellectual Property                     |

| JTAG         | Joint Test Action Group                   |

| LRAM         | Large Random Access Memory                |

| LSE          | Lattice Synthesis Engine                  |

| PDF          | Physical Design Constraints               |

| RAM          | Random Access Memory                      |

| RISC-V       | Reduced Instruction Set Computer – V      |

| ROM          | Read-Only Memory                          |

| RTL          | Register Transfer Level                   |

| SDK          | Software Development Kit                  |

| SoC          | System on Chip                            |

# 1. Introduction

This document provides technical information about System Memory Soft IP and aims to provide essential information for IP/system developers in verification, integration, testing, and validation.

## 1.1. Overview of the IP

The System Memory Module is designed to support external source programming, offering user-interface options such as AHBL and AXI for efficient instruction fetching of the microcontroller.

# 1.2. Quick Facts

Table 1.1. Summary of the System Memory Module IP

| ,                    | e system memory module n      |                                                                                                                                                                                                                                                                                                                                                                |  |  |

|----------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IP Requirements      | Supported FPGA Family         | iCE40 UltraPlus <sup>™</sup> , MachXO2 <sup>™</sup> , MachXO3 <sup>™</sup> , MachXO3D <sup>™</sup> , MachXO4 <sup>™</sup> , ECP5 <sup>™</sup> , ECP5-5G <sup>™</sup> , CrossLink <sup>™</sup> -NX, Certus <sup>™</sup> -NX, CertusPro <sup>™</sup> -NX, Mach <sup>™</sup> -NX, MachXO5 <sup>™</sup> -NX, Lattice Avant <sup>™</sup> , Certus <sup>™</sup> -N2. |  |  |

|                      | IP Changes <sup>1</sup>       | For a list of changes to the IP, refer to the System Memory Module IP Release Notes (FPGA-RN-02065).                                                                                                                                                                                                                                                           |  |  |

| Descures Hillingtion | Targeted Devices              | Refer to Table A.1                                                                                                                                                                                                                                                                                                                                             |  |  |

| Resource Utilization | Supported User Interface      | AXI, AHBL                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                      | Lattice levels are activities | IP Core v2.5.0 – Lattice Radiant™ Software 2025.2                                                                                                                                                                                                                                                                                                              |  |  |

|                      | Lattice Implementation        | IP Core v2.5.0 – Lattice Propel™ Builder Software 2025.2 IP Core v2.5.0 – Lattice Diamond™ Software 3.13                                                                                                                                                                                                                                                       |  |  |

| Design Tool Support  | Synthesis                     | Lattice Synthesis Engine (LSE) Synopsys® Synplify Pro for Lattice                                                                                                                                                                                                                                                                                              |  |  |

|                      | Simulation                    | For a list of supported simulators, see the Lattice Radiant Software User Guide                                                                                                                                                                                                                                                                                |  |  |

#### Note:

# 1.3. IP Support Summary

Table 1.2. System Memory Module IP Support Readiness

| Device<br>Family              | IP                         | User-<br>Interface | Data Width | Memory Type | Data<br>Rate<br>(Mbps) | Radiant<br>Timing<br>Model | Hardware<br>Validated |

|-------------------------------|----------------------------|--------------------|------------|-------------|------------------------|----------------------------|-----------------------|

|                               |                            |                    | X8         | EBR         | 1400                   | Preliminary                | Yes                   |

|                               |                            | AHBL               | X16        | EBR         | 2800                   | Preliminary                | Yes                   |

|                               | System                     |                    | X32        | EBR         | 5800                   | Preliminary                | Yes                   |

| Lattice<br>Avant <sup>1</sup> | Memory<br>Module           | ory                | X8         | EBR         | 1950                   | Preliminary                | Yes                   |

| Avaiit                        |                            |                    | X16        | EBR         | 3800                   | Preliminary                | Yes                   |

|                               |                            |                    | X32        | EBR         | 7700                   | Preliminary                | Yes                   |

|                               |                            |                    | X64        | EBR         | 15600                  | Preliminary                | Yes                   |

|                               | System<br>Memory<br>Module |                    | X8         | EBR         | 700                    | Preliminary                | Yes                   |

|                               |                            |                    | X16        | EBR         | 1400                   | Preliminary                | Yes                   |

|                               |                            |                    | V22        | EBR         | 2900                   | Preliminary                | Yes                   |

| CertusPro-<br>NX <sup>2</sup> |                            |                    | X32        | LRAM        | 2900                   | Preliminary                | Yes                   |

| INA-                          |                            | AXI4               | X8         | EBR         | 975                    | Preliminary                | Yes                   |

|                               |                            |                    | X16        | EBR         | 1950                   | Preliminary                | Yes                   |

|                               |                            |                    | X32        | EBR         | 3800                   | Preliminary                | Yes                   |

In some instances, the IP may be updated without changes to the user guide. This user guide may reflect an earlier IP version but remains fully compatible with the later IP version. Refer to the IP Release Notes for the latest updates.

| Device<br>Family       | IP                         | User-<br>Interface | Data Width | Memory Type | Data<br>Rate<br>(Mbps) | Radiant<br>Timing<br>Model | Hardware<br>Validated |             |     |

|------------------------|----------------------------|--------------------|------------|-------------|------------------------|----------------------------|-----------------------|-------------|-----|

|                        |                            |                    |            | LRAM        | 3800                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    | X64        | EBR         | 7700                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    | X8         | EBR         | 700                    | Preliminary                | No                    |             |     |

|                        |                            | AHBL               | X16        | EBR         | 1400                   | Preliminary                | No                    |             |     |

|                        |                            | AURT               | X32        | EBR         | 2900                   | Preliminary                | No                    |             |     |

|                        | System                     |                    | X32        | LRAM        | 2900                   | Preliminary                | No                    |             |     |

| Certus-NX <sup>2</sup> | Memory                     |                    | X8         | EBR         | 975                    | Preliminary                | No                    |             |     |

|                        | Module                     |                    | X16        | EBR         | 1950                   | Preliminary                | No                    |             |     |

|                        |                            | AXI4               | X32        | EBR         | 3800                   | Preliminary                | No                    |             |     |

|                        |                            |                    | X32        | LRAM        | 3800                   | Preliminary                | No                    |             |     |

|                        |                            |                    | X64        | EBR         | 7700                   | Preliminary                | No                    |             |     |

|                        | System<br>Memory<br>Module | ry                 | X8         | EBR         | 700                    | Preliminary                | Yes                   |             |     |

|                        |                            |                    | X16        | EBR         | 1400                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    | vaa        | EBR         | 2900                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    | X32        | LRAM        | 2900                   | Preliminary                | Yes                   |             |     |

| Mach-NX <sup>2</sup>   |                            |                    | X8         | EBR         | 975                    | Preliminary                | Yes                   |             |     |

|                        |                            |                    | X16        | EBR         | 1950                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    | vaa        | EBR         | 3800                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    |            |             | X32                    | LRAM                       | 3800                  | Preliminary | Yes |

|                        |                            |                    | X64        | EBR         | 7700                   | Preliminary                | Yes                   |             |     |

|                        |                            |                    | X8         | EBR         | 700                    | Preliminary                | No                    |             |     |

|                        |                            | AHBL               | X16        | EBR         | 1400                   | Preliminary                | No                    |             |     |

|                        | System                     |                    | X32        | EBR         | 2900                   | Preliminary                | No                    |             |     |

| ECP5 <sup>2</sup>      | Memory                     | у                  | X8         | EBR         | 975                    | Preliminary                | No                    |             |     |

|                        | Module                     |                    | X16        | EBR         | 1950                   | Preliminary                | No                    |             |     |

|                        |                            |                    | X32        | EBR         | 3800                   | Preliminary                | No                    |             |     |

|                        |                            |                    | X64        | EBR         | 7700                   | Preliminary                | No                    |             |     |

### Notes:

- 1. The Lattice Avant data rate was tested using 200 MHz clock frequency.

- 2. The CertusPro-NX, Certus-NX, ECP5, Mach-NX data rate was tested using 100 MHz clock frequency.

## 1.4. Features

Key features of the System Memory Module IP include:

- Compliant with AMBA 3 AHB-Lite Protocol v1.0

- Compliant with AMBA AXI4 Protocol

- Supports AXI4 atomic access

- Configurable as single or dual port memory, utilizing 1 or 2 AHB-Lite or AXI4 Interfaces

- Core memory can be implemented as EBR, Distributed RAM, or Large RAM

- Supports ROM and RAM mode

- Supports byte writes when used with compatible hardware

- Supports up to 1 Mb maximum memory (maximum varies per device and per memory implementation)

- Supports 8, 16, or 32-bit data word transfers

- Supports 64-bit data word transfers for AXI interface

- Uses Little-endian bit structure

- Has a dedicated high-speed interface for fast memory initialization using either FIFO Interface or AXI4-Stream

# 1.5. Licensing and Ordering Information

The System Memory Module IP is provided at no additional cost with the Lattice Radiant software.

# 1.6. Hardware Support

Refer to the Example Design section for more information on the boards used.

# 1.7. Minimum Device Requirements

There is no speed grade limitation for using the System Memory IP. However, the maximum clock frequency of the IP depends on the device used.

# 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.8.2. Signal Names

- \_n is active low (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

# 2. Functional Description

# 2.1. IP Architecture Overview

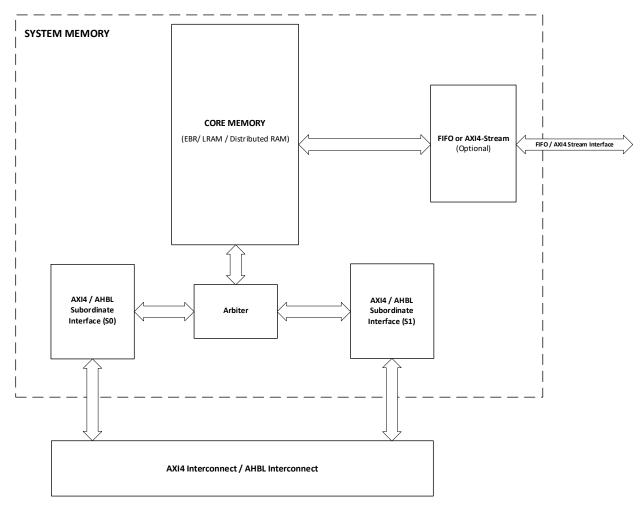

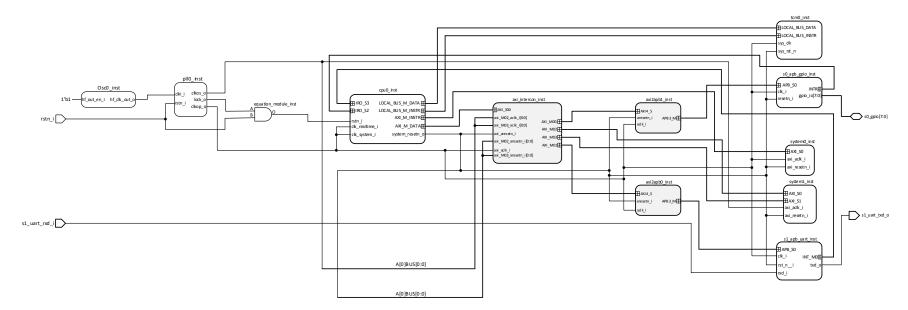

Figure 2.1. System Memory Module IP Core Block Diagram

The System Memory Module IP includes the following blocks:

- Core Memory

- AXI4/AHBL Subordinate Interface

- Arbiter

- FIFO or AXI4-Stream (Optional)

# 2.2. Clocking

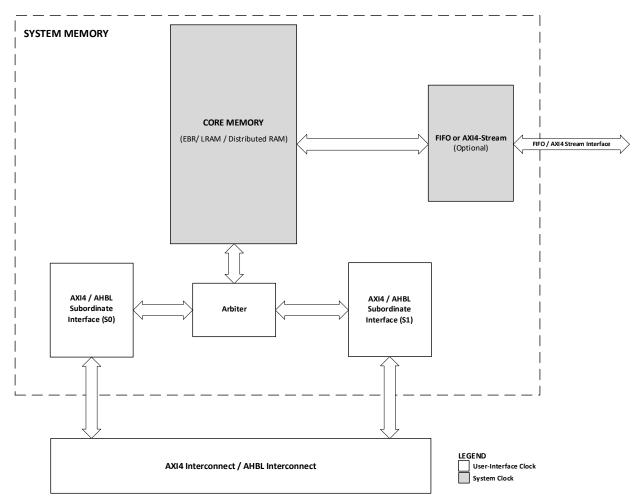

Figure 2.2. System Memory Module IP Clock Domain Block Diagram

# 2.2.1. Clocking Overview

- User-Interface Clock: ahbl\_clk\_i/ axi\_aclk\_i

- For AXI4, the supported frequency ranges from 1 MHz to 125 MHz.

- For AHBL, the supported frequency ranges from 1 MHz to 125 MHz.

- For Lattice Avant devices, the supported frequency range for both AHBL and AXI4 is up to 200 MHz.

- If you enable the data streamer clock bypass, the system clock uses the user interface clock.

## 2.3. Reset

#### 2.3.1. Reset Overview

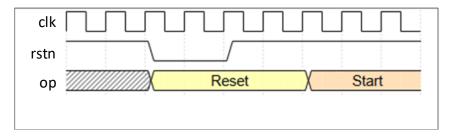

The System Memory IP Core has only one active-low reset. When you use the AXI interface, the active-low reset is named axi resetn i. When you use the AHBL interface, the active-low reset is named ahbl hresetn i.

The reset input signal affects only the registers in the System Memory IP. It does not affect the registers in the HARD IP (memory implementation). You must wait for at least two clock cycles before initiating transactions after the reset sequence. This allows the IP to complete its reset sequence.

Below are the steps in the reset sequence for the System Memory IP Core:

- 1. De-assert the active-low reset using axi\_resetn\_i for the AXI interface and ahbl\_hresetn\_i for the AHBL interface.

- 2. Wait for two or more system clock cycles. The clock name is axi\_aclk\_i for the AXI interface and ahbl\_hclk\_i for the AHBL interface.

- 3. Initiate the next transaction.

# 2.3.2. Reset Timing Diagram

Figure 2.3 illustrates the timing for the start of the next transaction.

Figure 2.3. Reset Timing Diagram

## 2.4. User Interfaces

**Table 2.1. User Interfaces and Supported Protocols**

| User Interface | Supported Protocols | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | AHB-Lite            | The System Memory Module is fully compatible with the AHB-Lite standard. You can configure it as single or dual AHB-Lite interfaces, depending on whether you need single or dual port memory.                                                                                                                                                                                                  |

| Control        | AXI                 | The System Memory Module is fully compatible with the AXI4 standard. Unlike the AHB-Lite interface, you always implement AXI4 as a dual port memory. You assign one port of the memory to AXI4 Write Channels and the other port to AXI4 Read Channels. Similar to the AHB-Lite interface, AXI4 transactions translate into memory-compatible signals that the core memory directly interprets. |

|                | FIFO                | The AHB-L port S1 shares a dedicated FIFO interface. You can use this interface to inject data from a FIFO stream. LIFCL, LFCPNX, LFD2NX, and LFMXO5 devices support this feature.                                                                                                                                                                                                              |

|                | AXI4-Streamer       | When you set the interface for System Memory to AXI4, you can set the data streamer interface to AXI4-Stream.                                                                                                                                                                                                                                                                                   |

#### 2.4.1. AHB-Lite

The AHBL interface for System Memory IP supports the INCR burst type for *write* and *read* operations. The WRAP burst type is currently unsupported.

For LFMXO4 devices, unaligned address and narrow transactions are only supported in 32-bit data width.

### 2.4.2. AXI4

The AXI4 interface for the System Memory IP supports the INCR burst type for both *write* and *read* operations. The WRAP burst type is not supported.

For LFMXO4 devices, unaligned address and narrow transactions are only supported in 32-bit data width.

#### 2.4.3. FIFO

You typically use this to upload firmware values to the core memory. The FIFO starts writing at the designated first byte-addressable data and writes up to the maximum depth of the implemented memory.

#### 2.4.4. AXI4 Stream

This interface is fully compatible with the AXI4-Stream standard and is implemented to prioritize other AXI4 write transactions when a valid data stream is given. Like the FIFO interface, the data starts at the designated first byte-addressable data and writes up to the maximum memory depth. The You can use the TLAST signal to indicate the end of the data stream, then the following AXI4-Stream transaction starts again at the designated first address. The AXI4-Stream write strobe is ignored when using Distributed RAM.

# 2.5. Memory Implementation

The System Memory Module uses Embedded Block RAMs (EBR) or Distributed RAM in the MachXO3D family devices, as well as Large RAM in LIFCL, LFCPNX, LFD2NX, and LFMXO5 family devices. You can configure the memory implementation as true-dual port, pseudo dual port, single port, or read-only memory. The number of ports and read/write configuration of the System Memory Module automatically select the best type of memory for the user-selected application.

Remember that the memory is not affected by the reset. All written data is stored even after the reset sequence.

Table 2.2. System Core Memory Type - AHB-Lite

| Memory Type      | AHB-Lite Configuration<br>Used <sup>1</sup>             | LatticeECP3, ECP5, ECP5-5G, MachXO2, MachXO3, MachXO3D, MachXO4 <sup>2</sup> , Lattice Avant, Certus-N2 | Crosslink-NX,<br>CertusPro-NX,<br>Certus-NX,<br>MachXO5-NX | iCE40 UltraPlus |

|------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|

| LRAM             | 1 port: "R/W, R/O" 2 ports: "R/W" + "R/W" "R/O" + "R/W" | _                                                                                                       | Yes                                                        | _               |

|                  | 1 port:<br>"R/W, R/O"                                   |                                                                                                         |                                                            | Yes             |

| EBR <sup>1</sup> | 2 ports: "R/W" + "R/W" "R/O" + "R/W"                    | Yes                                                                                                     | Yes                                                        | _               |

| Distributed RAM  | 1 port:                                                 | Yes                                                                                                     | Yes                                                        | _               |

| Memory Type | AHB-Lite Configuration | LatticeECP3,           | Crosslink-NX, | iCE40 UltraPlus |

|-------------|------------------------|------------------------|---------------|-----------------|

|             | Used <sup>1</sup>      | ECP5,                  | CertusPro-NX, |                 |

|             |                        | ECP5-5G,               | Certus-NX,    |                 |

|             |                        | MachXO2,               | MachXO5-NX    |                 |

|             |                        | MachXO3,               |               |                 |

|             |                        | MachXO3D,              |               |                 |

|             |                        | MachXO4 <sup>2</sup> , |               |                 |

|             |                        | Lattice Avant,         |               |                 |

|             |                        | Certus-N2              |               |                 |

|             | "R/W, R/O"             |                        |               |                 |

#### Notes:

- 1. The EBR ECC is limited to single port only.

- 2. ECC is not supported.

Table 2.3. System Core Memory Type – AXI

| Memory Type      | AXI Configuration Used                                      | LatticeECP3, ECP5, ECP5-5G, MachXO2, MachXO3, MachXO3D, MachXO4 <sup>2</sup> , Lattice Avant <sup>2</sup> , Certus-N2 | Crosslink-NX,<br>CertusPro-NX,<br>Certus-NX,<br>MachXO5-NX | iCE40 UltraPlus <sup>2</sup> |

|------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------|

| LRAM             | 1 port: "R/W, R/O" 2 ports: "R/W" + "R/W" "R/O" + "R/W"     | -                                                                                                                     | Yes                                                        | _                            |

| EBR <sup>1</sup> | 1 port:  "R/W, R/O"  2 ports:  "R/W" + "R/W"  "R/O" + "R/W" | Yes                                                                                                                   | Yes                                                        | _                            |

| Distributed RAM  | 1 port:<br>"R/W, R/O"                                       | Yes                                                                                                                   | Yes                                                        | _                            |

#### Notes:

- 1. The EBR ECC is limited to single port only.

- 2. ECC is not supported.

**Table 2.4. System Core Memory Implementation**

| Memory Type     | User Interface | Access Type                                | Memory Implementation |

|-----------------|----------------|--------------------------------------------|-----------------------|

|                 |                | 1 port:<br>"R/W", "R/O"                    | Single Port           |

| LRAM            | AHBL           | 2 ports:<br>"R/W" + "R/W"<br>"R/O" + "R/W" | Dual Port             |

| LNAIVI          |                | 1 port:<br>"R/W", "R/O"                    | Pseudo Dual Port      |

|                 | AXI            | 2 ports:<br>"R/W" + "R/W"<br>"R/O" + "R/W" | Pseudo Dual Port      |

|                 |                | 1 port:<br>"R/W", "R/O"                    | Single Port           |

| 500             | AHBL           | 2 ports:<br>"R/W" + "R/W"<br>"R/O" + "R/W" | Dual Port             |

| EBR             |                | 1 port:<br>"R/W", "R/O"                    | Pseudo Dual Port      |

|                 | AXI            | 2 ports:<br>"R/W" + "R/W"<br>"R/O" + "R/W" | Pseudo Dual Port      |

| Distributed RAM | AHBL           | 1 port:<br>"R/W", "R/O"                    | Single Port           |

|                 | AXI            | 1 port:<br>"R/W", "R/O"                    | Pseudo Dual Port      |

#### Table 2.5. Features Supported per Memory Block

| Device                  | LRAM             | EBR              | Distributed RAM |

|-------------------------|------------------|------------------|-----------------|

| ECC <sup>1</sup>        | Yes <sup>2</sup> | Yes <sup>2</sup> | No              |

| Memory Initialization   | Yes              | Yes              | Yes             |

| Registered Output       | Yes              | Yes              | Yes             |

| Dual Port Configuration | Yes              | Yes              | Yes             |

| Byte-Enable             | Yes <sup>2</sup> | Yes <sup>2</sup> | No              |

| Unaligned Read Access   | Yes <sup>3</sup> | Yes              | No              |

#### Notes:

- Lattice Avant devices do not support ECC.

- 2. You can use Byte-enable with ECC.

- 3. You cannot use unaligned read access with Byte-enable.

# Table 2.6. ECC Implementation per Memory Block

| Memory Type     | ECC Implementation             |

|-----------------|--------------------------------|

| LRAM            | Hard IP <sup>1,4</sup>         |

| EBR             | Hard IP <sup>1,2,3,4,5,6</sup> |

| Distributed RAM | No                             |

#### Notes:

- 1. Available in CrossLink-NX, CertusPro-NX, Certus-NX, and MachXO5-NX devices.

- 2. Available in LatticeECP3, ECP5, ECP5-5G, MachXO2, MachXO3, MachXO3D, Lattice Avant, and Certus-N2 devices.

- 3. Available in iCE40 UltraPlus devices.

- 4. You cannot use the ECC function in AXI4 because Byte-enable always supports AXI4 write strobes.

- 5. You cannot use the ECC function in AXI4 because it always implements dual port RAM in EBR.

- 6. The EBR ECC function is available only when the port count is equals one.

Table 2.7. Allowable Combination of Features for System Memory when INTERFACE = AHBL

| Device          | Byte-Enable | ECC | Unaligned Read<br>Access | FIFO     | Maximum Supported Port<br>Count |

|-----------------|-------------|-----|--------------------------|----------|---------------------------------|

| ×               | ×           | ×   | ×                        | ×        | 2                               |

|                 | ×           | ×   | ×                        | ✓        | 2                               |

|                 | ×           | ×   | ✓                        | ×        | 2                               |

|                 | ×           | ×   | ✓                        | ✓        | 2                               |

|                 | ×           | ✓   | ×                        | ×        | 2                               |

|                 | ×           | ✓   | ×                        | ✓        | Not Supported                   |

|                 | ×           | ✓   | ✓                        | ×        | 2                               |

| 15444           | ×           | ✓   | ✓                        | ✓        | Not Supported                   |

| LRAM            | ✓           | ×   | ×                        | ×        | 2                               |

|                 | ✓           | ×   | ×                        | ✓        | 2                               |

|                 | ✓           | ×   | ✓                        | ×        | 2                               |

|                 | ✓           | ×   | ✓                        | ✓        | 2                               |

|                 | ✓           | ✓   | ×                        | ×        | Not Supported                   |

|                 | ✓           | ✓   | ×                        | ✓        | Not Supported                   |

|                 | ✓           | ✓   | ✓                        | ×        | Not Supported                   |

|                 | ✓           | ✓   | ✓                        | ✓        | Not Supported                   |

|                 | ×           | ×   | N/A                      | ×        | 2                               |

|                 | ×           | ×   | N/A                      | ✓        | 2                               |

|                 | ×           | ✓   | N/A                      | ×        | 11                              |

| EBR             | ×           | ✓   | N/A                      | ✓        | Not Supported                   |

|                 | ✓           | ×   | N/A                      | ×        | 2                               |

|                 | ✓           | ×   | N/A                      | ✓        | 2                               |

| D' - '          | N/A         | N/A | N/A                      | ×        | 1 <sup>2</sup>                  |

| Distributed RAM | N/A         | N/A | N/A                      | <b>√</b> | 12                              |

#### Notes:

- 1. EBR ECC supports only a single port.

- 2. Distributed RAM supports only a single port.

# 2.6. System Memory Error Information

**Table 2.8. System Memory Error**

| Error                     | Description                                                                                                           | AHB-Lite Behavior                                                                           | AXI4 Behavior                                                                                           |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Dual Write                | Occurs when two ports attempt to write to the same address of the memory.                                             | The system prioritizes port SO and ignores port S1 transaction without generating an error. | The system does not generate an error. An arbiter decides which AXI Interface (S0 or S1) grants access. |

| Illegal Access            | Occurs when a manager attempts to access an address outside the bounds of the START_ADDRESS or END_ADDRESS parameter. | The system generates a bus error through the hresp_o port.                                  | The system generates a bus error through the bresp_o or rresp_o port.                                   |

| Illegal Transaction (W/R) | Occurs when a manager attempts to write to a readonly port, or read from a write-only port.                           | The system generates a bus error through the hresp_o port.                                  | The system generates a bus error through the bresp_o or rresp_o port.                                   |

| Error                        | Description                                                                                                                                                                           | AHB-Lite Behavior                                          | AXI4 Behavior                                                                        |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Unaligned Error              | Occurs when a manager attempts to access a wider data bit without providing appropriate pads for the lower address bits.  Example: A 32-bit data access with ahbl_addr[1:0] != 2'b00. | The system generates a bus error through the hresp_o port. | The system does not generate an error. The AXI4 Interface supports unaligned access. |

| ECC error                    | Occurs when an ECC error is generated during a read attempt.  • ecc_sec – a single error is detected and corrected.  • ecc_dec – two errors are detected and cannot be corrected.     | The system generates a bus error through the hresp_o port. | The AXI4 Interface does not support ECC.                                             |

| Multiple AXI4 Exclusive Read | Occurs when the AXI4 manager issues an exclusive read when there is already a standing exclusive transaction with different transaction ID in the subordinate.                        | _                                                          | The AXI4 subordinate generates a subordinate error in the rresp port.                |

## 2.7. Arbitration

When the System Memory Module has two ports (SO and S1), both ports can access the memory at the same time only if the ports target different addresses or if both ports are performing read operations.

If both ports access the same address and at least one is a write, the module enforces arbitration to prevent data corruption. In such cases, only one port is granted access, and port SO always has priority over port S1.

In the System Memory Module, port SO is always prioritized in every arbitration.

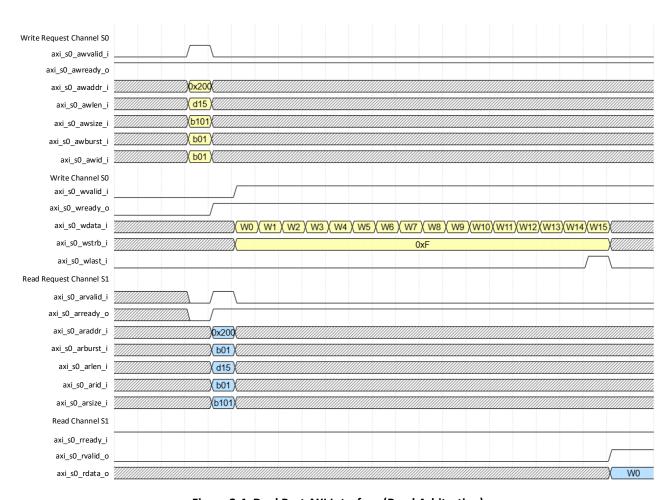

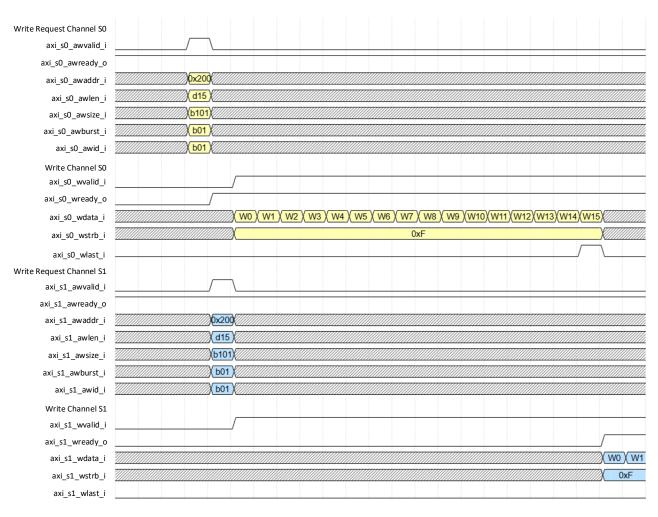

### 2.7.1. Arbitration in the AXI4 Interface

To manage the separate write and read channels of the AXI4 Interface, the implemented memory is always pseudo-dual port, with port A in the primitive for write transactions and port B in the primitive for read transactions. When the port count is two, an arbiter block manages the arbitration between the write channels of port S0 and port S1 using WREADY signals. Separate arbitration manages the read channels using the ARREADY signal.

For example, port S0 is doing a write transaction in address 0x0200 and port S1 attempts to request a read transaction to the same address. The RREADY signal for port S1 is delayed until the transaction in port S0 finishes. Refer to Figure 2.4 for the illustration of the example scenario.

Figure 2.4. Dual Port AXI Interface (Read Arbitration)

For the scenario when two ports are sending the same transaction (read/write), port S0 is doing a write transaction in address 0x0200 and port S1 attempts to request a write transaction. The WREADY signal for port S1 is delayed until the transaction in port S0 finishes. Refer to Figure 2.5 for the illustration of the example scenario.

Figure 2.5. Dual Port AXI Interface (Write Arbitration)

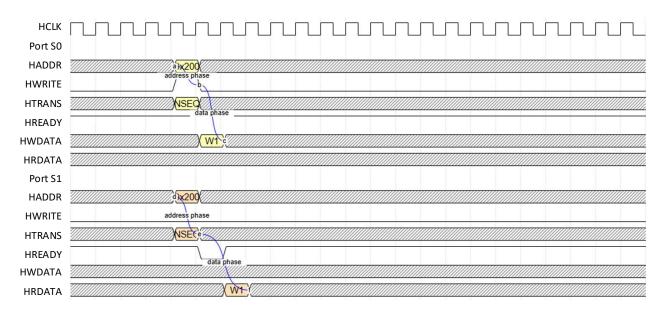

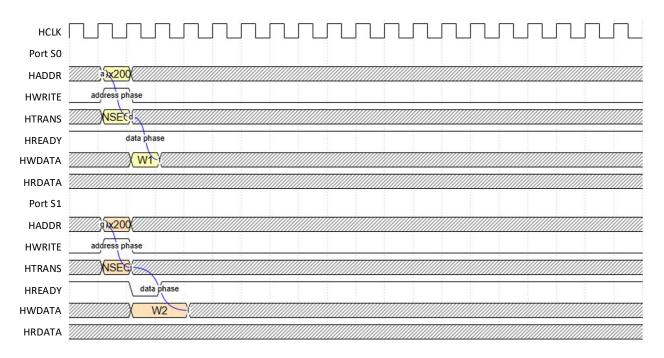

## 2.7.2. Arbitration in the AHBL Interface

To manage the arbitration in the AHBL interface, the HREADY signal of the port that loses the arbitration is delayed indicating that the subordinate cannot handle transactions as the other port has an ongoing write transaction at the same address. Refer to

Figure 2.6 and Figure 2.7 for the illustration of the example scenarios.

Figure 2.6. Dual Port AHBL Interface Arbitration (Read Transaction)

Figure 2.7. Dual Port AHBL Interface Arbitration (Write Transaction)

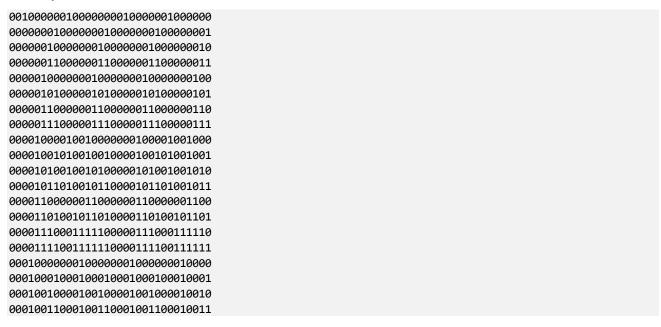

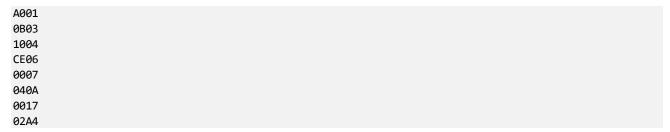

## 2.8. Initialization Format

You can create or edit the initialization file, an ASCII file, using any ASCII editor. The Module/IP Block Wizard supports the following memory file formats:

- Binary file

- Hex File

The memory initialization file is \*.mem (<file\_name>.mem). Each row stores the value for a specific memory location. The number of characters (or columns) represents the number of bits for each address (or the memory module width).

The memory initialization can be static or dynamic. For static initialization, the memory values are stored in the bitstream. Dynamic memory initialization involves storing memory values in the external flash which user logic can update knowing the EBR address locations. The bitstream (bit or rbt file) size is larger due to stored static values.

The initialization file is used when the System Memory is configured as a ROM. In RAM configuration, you can also use the initialization file to preload memory contents.

#### **Binary File**

The binary file contains 0s and 1s. The rows represent the number of words, and the columns represent the memory width.

#### Memory Size 20 x 32

#### **Hex File**

The hex file contains hexadecimal characters arranged in a similar row-column format. The number of rows matches the number of address locations, with each row representing the content of the memory location.

### Memory Size 8 x 16

# 2.9. AXI4 Atomic Access

The System Memory Module supports AXI4 atomic access. This section provides the details on how to use the atomic access feature.

#### 2.9.1. Exclusive Access Restrictions

The System Memory Module has the following restrictions:

- The address must be aligned with the total number of bytes in the transaction (AxSIZE x transaction length).

- The number of bytes must be power of 2.

- The maximum number of bytes in a transfer is 128.

- The length must not exceed 16.

- Exclusive read pipelining is not supported. Subordinate error response is sent if attempted.

- AxSIZE must match the data bus width.

- WSTRB must be fully asserted.

- Fixed burst is not supported.

Note that not following these restrictions may result in unexpected behavior from the System Memory Module.

To complete an exclusive transaction, the exclusive read and exclusive write must have the same request information. Table 2.9 lists the supported signals that must be the same in an exclusive sequence.

**Table 2.9. Request Information Atomic Access**

| Signal Name | Supported Signal |

|-------------|------------------|

| AXID        | Yes              |

| AxLEN       | Yes              |

| AxADDR      | Yes              |

| AxSIZE      | Yes              |

| AxBURST     | Yes              |

| AXLOCK      | Yes (v2.5.0)     |

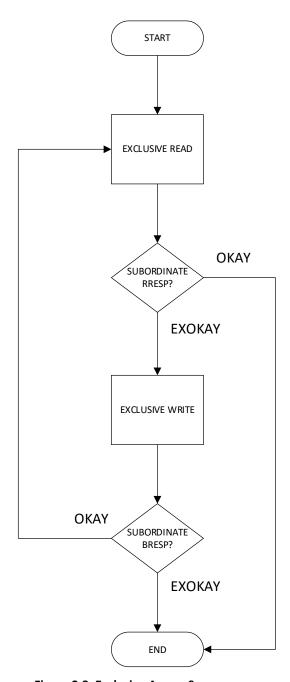

## 2.9.2. Exclusive Access Sequence

Figure 2.8. Exclusive Access Sequence

- 1. A manager issues an exclusive read request. The manager can resend another exclusive read using the same ARID to reset the monitored address for exclusive access.

- 2. At some later time, the manager attempts to complete the exclusive operation by issuing an exclusive write request to the same address, with an AWID that matches the ARID used for the exclusive read.

- Successful, if no other manager has written to that location since the exclusive read access. In this case, the

exclusive write updates memory.

- Fails, if another manager has written to that location since the exclusive read access or the monitored address is updated. In this case, the memory location is not updated.

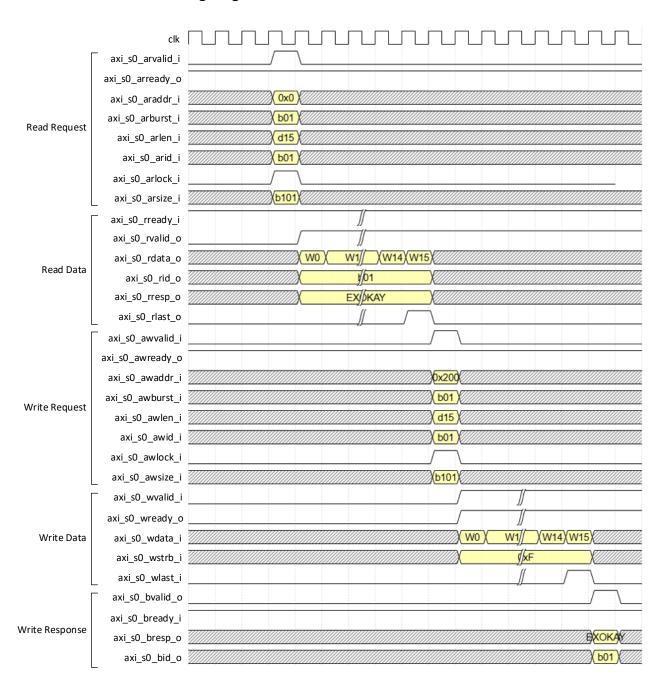

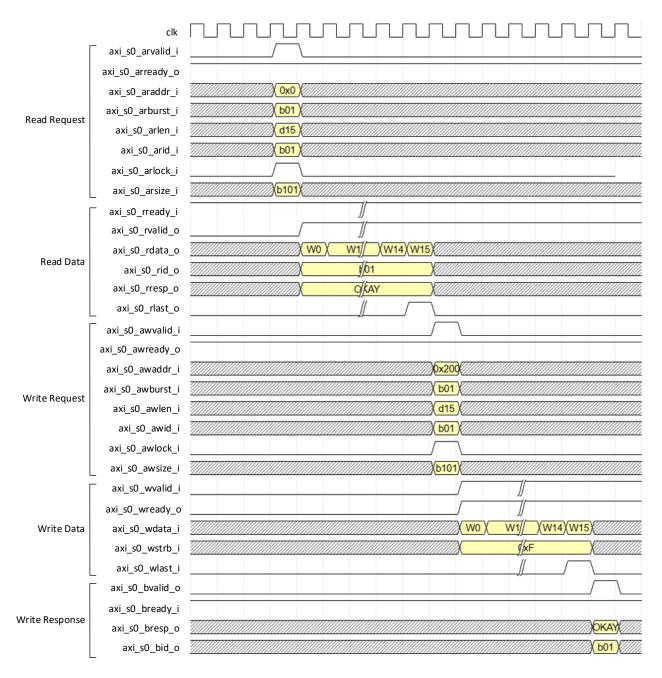

## 2.9.3. Exclusive Access Timing Diagram

Figure 2.9. Successful Atomic Access Transaction

Figure 2.10. Failed Atomic Access Transaction

# 2.9.4. Exclusivity Granularity

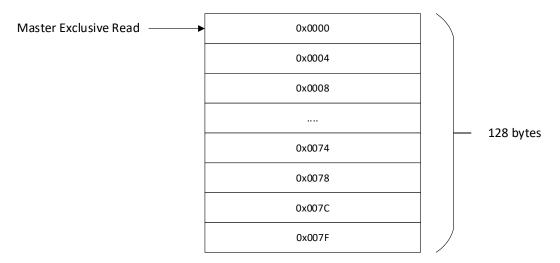

Figure 2.11. Atomic Access Exclusivity Granularity

In Figure 2.11, the AXI4 manager sends an exclusive read that starts in address 0x0000 and has a length of 128 bytes. All addresses from 0x0000 to 0x007F are now locked in exclusive access to that specific AXI4 manager. Any write transaction that modifies these addresses causes the exclusive write transaction to fail.

# 3. IP Parameter Description

The tables below show the configurable attributes of the System Memory IP. You can configure the IP by setting the attributes in the IP Catalog's Module/IP wizard within the Lattice Radiant software.

Default values, where applicable, are highlighted in bold.

# 3.1. General

#### **Table 3.1. General Attributes**

| Interface AHBL AXIA Select the subordinate bus interface.  Memory Address Depth 1 – 456,000 Measure the depth of the memory address in units of DATA_WIDTH. The maximum ADDR_DEPTH depends on DATA_WIDTH, memory type, and device used.  The data width of the memory measured in bits. The value of 64 bits is available only if the interface is AXIA and the target device has two or more LRAM blocks available.  BBR Distributed_RAM LRAM  Port Count [1-2] 1, 2 Determine whether the generated system memory uses one or two AHB-LITE/AXI Interfaces.  ECC Enable L.2.3 True, False Determines whether ECC is used, which applies to both ports. Refer to Table 2.5 for details. Note that the data width must be 32 bits when using ECC.  Enable Arbiter True, False Enable the ARBITER function. Editable only when PORT_COUNT is two.  AXIA ID Width 1-15 True, False Enable the data streamer interface is AXIA.  Data Streamer  Enable Data Streamer = TRUE  Data Streamer Interface  AXIA Stream  True, False Enable the data streamer interface.  Enable Data Streamer write Start AXIA Stream  Data Streamer Write Start (Data Bus Width/SI)  Data Streamer Clock Bus Width/SI Cock source. Otherwise, it uses its own dedicated clock, which is figic_clk_i or Generic FIFO or axis_rx_aclk_i for AXIA-Stream.  Initialization  Initialization File String  Select the initialization of the system memory by providing an initialization file.  Initialization File String  Select the initialization file for the system memory.                                                                                                                                                                                   | Attribute                                                                   | Selectable Values    | Description                                                                    |                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------|---------------------------------------|--|

| Memory Address Depth       1 – 456,000       maximum ADDR_DEPTH depends on DATA_WIDTH, memory type, and device used.         Data Bus Width(bits)       8, 16, 32, 64       The data width of the memory measured in bits. The value of 64 bits is available only if the interface is AXI4 and the target device has two or more LRAM blocks available.         Memory Type       EBR Distributed_RAM LRAM       Select the type of memory implemented for this instance of system memory.         Port Count [1-2]       1, 2       Determine whether the generated system memory uses one or two AHB-Lite/AXI Interfaces.         ECC Enable1-2.3       True, False       Determines whether ECC is used, which applies to both ports. Refer to Table 2.5 for details. Note that the data width must be 32 bits when using ECC.         Enable Arbiter       True, False       Enable the ARBITER function. Editable only when PORT_COUNT is two.         AXI4 ID Width       1 - 15       The width of the AXI4 ID for all channels. Available only when the interface is AXI4.         Data Streamer       True, False       Enable the data streamer interface.         Enable Data Streamer Interface       Select the interface for the data streamer. The AXI4-Stream is available only when the selected bus interface is AXI4.         Data Streamer Interface       O- (ADDR_DEPTH- (Data Bus Width/8))         Data Streamer Vite Start Address       O- (ADDR_DEPTH- (Data Bus Width/8))       The starting address where the data streamer begins writing. <th cols<="" td=""><td>Interface</td><td></td><td>Select the subordinate bus interface.</td></th>                                                                                                                                                                                                                                                                                                                                                   | <td>Interface</td> <td></td> <td>Select the subordinate bus interface.</td> | Interface            |                                                                                | Select the subordinate bus interface. |  |

| Data Bus Width(bits)       8, 16, 32, 64       The value of 64 bits is available only if the interface is AXI4 and the target device has two or more LRAM blocks available.         Memory Type       EBR Distributed_RAM LRAM       Select the type of memory implemented for this instance of system memory.         Port Count [1-2]       1, 2       Determine whether the generated system memory uses one or two AHB-Lite/AXI Interfaces.         ECC Enable <sup>1,2,3</sup> True, False       Determines whether ECC is used, which applies to both ports. Refer to Table 2.5 for details. Note that the data width must be 32 bits when using ECC.         Enable Arbiter       True, False       Enable the ARBITER function. Editable only when PORT_COUNT is two.         AXI4 ID Width       1 - 15       The width of the AXI4 ID for all channels. Available only when the interface is AXI4.         Data Streamer       True, False       Enable the data streamer interface.         Enable Data Streamer Interface       Enable the data streamer interface.         Enable Data Streamer Write Start Address       O_(ADDR_DEPTH-(Data Bus Width/8))       The AXI4-Stream is available only when the selected bus interface is AXI4.         Data Streamer Interface == AXI4 Stream       True, False       When enabled, the data streamer uses the abbl_clk_i or axi_aclk_i as its clock source. Otherwise, it uses its own dedicated clock, which is fifto_clk_i for Generic FIFO or axis_rx_aclk_i for AXI4-Stream.         Data Streamer Clock Bypass       True, False       En                                                                                                                                                                                                                                                                                                                                                                                                                   | Memory Address Depth                                                        | 1 – 456,000          | maximum ADDR_DEPTH depends on DATA_WIDTH, memory type, and                     |                                       |  |

| Select the type of memory implemented for this instance of system memory.  Port Count [1-2]  1, 2  Determine whether the generated system memory uses one or two AHB-Lite/AXI Interfaces.  Determines whether ECC is used, which applies to both ports. Refer to Table 2.5 for details. Note that the data width must be 32 bits when using ECC.  Enable Arbiter  True, False  Enable the ARBITER function. Editable only when PORT_COUNT is two.  The width of the AXI4 ID for all channels.  Available only when the interface is AXI4.  Data Streamer  Enable Data Streamer == TRUE  Data Streamer Interface  AXI4 Stream  Data Streamer Write Start Address  Data Streamer Write Start Address  Data Streamer Interface == AXI4 Stream  Data Streamer Clock Bypass  True, False  When enabled, the data streamer uses the ahbl_clk_i or axi_aclk_i as its clock source. Otherwise, it uses its own dedicated clock, which is fifoclk_i for Generic FIFO or axis_rx_aclk_i for AXI4-Stream.  Initialization  Initialize Memory  True, False  Determine whether the generated system memory uses one or two AHB-Lite/AXI Interfaces.  Determine whether the generated system memory uses one or two AHB-Lite/AXI Interface to the data width must be 32 bits when using ECC.  Enable the ARBITER function. Editable only when PORT_COUNT is two.  The width of the AXI4 ID for all channels.  Available only when the interface is AXI4.  Select the type of memory is each which applies to both ports. Refer to Table 2.5 for details. Note that the data width must be 32 bits when using ECC.  Enable the ARBITER function. Editable only when PORT_COUNT is two.  AXI4 Stream is available only when the selected bus interface is AXI4.  The starting address where the data streamer uses the abbl_clk_i or axi_aclk_i as its clock source. Otherwise, it uses its own dedicated clock, which is fife_clk_i for Generic FIFO or axis_rx_aclk_i for AXI4-Stream.  Initialize Memory = TRUE  Initialize Memory = TRUE | Data Bus Width(bits)                                                        | 8, 16, <b>32,</b> 64 | The value of 64 bits is available only if the interface is AXI4 and the target |                                       |  |

| ECC Enable 1,23  True, False  Enable Arbiter  True, False  Enable the ARBITER function. Editable only when PORT_COUNT is two.  The width of the AXI4 ID for all channels. Available only when the interface is AXI4.  Data Streamer  Enable Data Streamer == TRUE  Data Streamer Interface  AXI4 Stream  AXI4 Stream  Data Streamer Write Start Address  Data Streamer Interface == AXI4 Stream  Enable the initialization of the system memory by providing an initialization file.  Initialize Memory == TRUE  Initialization File Format Hex, Binary  Determine the file format of the initialization file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Memory Type                                                                 | Distributed_RAM      |                                                                                |                                       |  |

| ECC Enable 1-2.3 True, False Table 2.5 for details. Note that the data width must be 32 bits when using ECC.  Enable Arbiter True, False Enable the ARBITER function. Editable only when PORT_COUNT is two.  AXI4 ID Width 1 - 15 The width of the AXI4 ID for all channels. Available only when the interface is AXI4.  Data Streamer  Enable Data Streamer = TRUE  Data Streamer Interface Generic FIFO AXI4 Stream Select the interface for the data streamer. The AXI4-Stream is available only when the selected bus interface is AXI4.  Data Streamer Write Start (Data Bus Width/8)) The starting address where the data streamer begins writing.  Data Streamer Clock Bypass True, False When enabled, the data streamer uses the ahbl_clk_i or axi_aclk_i as its clock source. Otherwise, it uses its own dedicated clock, which is fifo_clk_i for Generic FIFO or axis_rx_aclk_i for AXI4-Stream.  Initialize Memory True, False Enable the initialization of the system memory by providing an initialization File Format Hex, Binary Determine the file format of the initialization file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Port Count [1 -2]                                                           | 1, 2                 | ,                                                                              |                                       |  |

| AXI4 ID Width  1 - 15  The width of the AXI4 ID for all channels. Available only when the interface is AXI4.  Data Streamer  Enable Data Streamer True, False  Enable the data streamer interface.  Enable Data Streamer Interface  Data Streamer Interface  Generic FIFO AXI4 Stream  Data Streamer Write Start Address  Data Streamer Interface = AXI4 Stream  Data Streamer Interface = Interface = Interface = Interface in the data streamer uses the abblected bus interface is AXI4.  When enabled, the data streamer uses the abblected in a sits clock source. Otherwise, it uses its own dedicated clock, which is fifocille, if or Generic FIFO or axis_rx_acille, if or AXI4-Stream.  Initialization  Initialize Memory  True, False  Enable the initialization of the system memory by providing an initialization file.  Initialization File Format  Hex, Binary  Determine the file format of the initialization file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ECC Enable <sup>1,2,3</sup>                                                 | True, <b>False</b>   | Table 2.5 for details. Note that the data width must be 32 bits when using     |                                       |  |

| Axia ID Width 1-15 Available only when the interface is AXi4.  Data Streamer  Enable Data Streamer = TRUE  Data Streamer Interface  Generic FIFO AXi4 Stream Streamer write Start Address  Data Streamer Interface == AXi4 Stream  Data Streamer Interface == AXi4 Stream  Data Streamer Interface == AXi4 Stream  Data Streamer Clock Bypass  True, False  When enabled, the data streamer uses the ahbl_clk_i or axi_aclk_i as its clock source. Otherwise, it uses its own dedicated clock, which is fifo_clk_i for Generic FIFO or axis_rx_aclk_i for AXi4-Stream.  Initialization  Initialize Memory  True, False  Enable the initialization of the system memory by providing an initialization file.  Determine the file format of the initialization file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Enable Arbiter                                                              | True, <b>False</b>   | Enable the ARBITER function. Editable only when PORT_COUNT is two.             |                                       |  |

| Enable Data Streamer  Enable Data Streamer = TRUE  Data Streamer Interface  Generic FIFO AXI4 Stream  Data Streamer Write Start Address  Data Streamer Interface == AXI4 Stream  Data Streamer Interface == AXI4 Stream  Data Streamer Clock Bypass  Initialization  Initialize Memory == TRUE  Enable the data streamer interface.  Enable the interface for the data streamer. The AXI4-Stream is available only when the selected bus interface is AXI4.  The starting address where the data streamer begins writing.  When enabled, the data streamer uses the ahbl_clk_i or axi_aclk_i as its clock source. Otherwise, it uses its own dedicated clock, which is fifo_clk_i for Generic FIFO or axis_rx_aclk_i for AXI4-Stream.  Enable the initialization of the system memory by providing an initialization file.  Initialize Memory == TRUE  Initialization File Format  Hex, Binary  Determine the file format of the initialization file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AXI4 ID Width                                                               | 1 - 15               |                                                                                |                                       |  |