# **DSP Arithmetic Modules - Lattice Radiant Software**

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Contents    |                                             | 3  |

|-------------|---------------------------------------------|----|

| Acronyms    | in This Document                            | 6  |

| L. Introd   | duction                                     | 7  |

| 2. DSP A    | rithmetic Modules                           | 8  |

| 2.1.        | Multiplier                                  | 8  |

| 2.1.1.      | Multiplier Operation                        | 8  |

| 2.1.2.      | Ports                                       | 8  |

| 2.1.3.      | Attributes                                  | 9  |

| 2.1.4.      | Timing Diagram                              | 10 |

| 2.2.        | Multiply-Accumulate                         | 11 |

| 2.2.1.      | Multiply-Accumulate Operation               | 11 |

| 2.2.2.      | Ports                                       | 11 |

| 2.2.3.      | Attributes                                  | 12 |

| 2.2.4.      | Timing Diagram                              | 13 |

| 2.3.        | Multiply-Add-Subtract                       | 14 |

| 2.3.1.      | Multiply-Add-Subtract Operation             | 14 |

| 2.3.2.      | Ports                                       | 14 |

| 2.3.3.      | Attributes                                  | 15 |

| 2.3.4.      | Timing Diagram                              | 17 |

| 2.4.        | Multiply-Add-Subtract-Sum                   | 17 |

| 2.4.1.      | Multiply-Add-Subtract-Sum Operation         | 18 |

| 2.4.2.      | Ports                                       | 18 |

| 2.4.3.      | Attributes                                  | 20 |

| 2.4.4.      | Timing Diagram                              | 21 |

| 2.5.        | Multiply-Multiply-Accumulate                | 22 |

| 2.5.1.      | Multiply-Multiply-Accumulate Operation      | 22 |

| 2.5.2.      | Ports                                       | 22 |

| 2.5.3.      | Attributes                                  | 24 |

| 2.5.4.      | Timing Diagram                              | 25 |

| 3. IP Ge    | neration                                    | 26 |

| 3.1.        | Generating a 32-bit Multiplier Module       | 26 |

|             | ation Flow                                  |    |

|             | Generating a Multiplier on Default Settings |    |

| 4.2.        | Constraining the IP                         | 32 |

| Appendix /  | A. Resource Utilization                     | 33 |

| A.1.        | Multiplier                                  | 33 |

| A.2.        | Multiply-Accumulate                         | 33 |

| A.3.        | Mult-Add-Subtract                           | 34 |

| A.4.        | Mult-Add-Subtract-Sum                       | 34 |

| A.5.        | Mult-Mult-Accumulate                        | 35 |

| References  | 5                                           | 36 |

| Technical S | Support Assistance                          | 37 |

| Pavisian H  | istory                                      | 38 |

# **Figures**

| Figure 2.1. Multiplier Schematic Diagram                                       | 8  |

|--------------------------------------------------------------------------------|----|

| Figure 2.2. Multiplier Timing Diagram                                          |    |

| Figure 2.3. Multiply-Accumulate Schematic                                      |    |

| Figure 2.4. Multiply-Accumulate Timing Waveforms                               |    |

| Figure 2.5. Multiply-Add-Subtract Schematic                                    |    |

| Figure 2.6. Multiply-Add-Subtract Timing Diagram                               |    |

| Figure 2.7. Multiply-Add-Subtract-Sum Schematic                                |    |

| Figure 2.8. Multiply-Add-Subtract-Sum Timing Diagram                           |    |

| Figure 2.9. Multiply-Multiply-Accumulate Schematic                             |    |

| Figure 2.10. Multiply-Multiply-Accumulate Timing Diagram                       |    |

| Figure 3.1. DSP Arithmetic Modules                                             |    |

| Figure 3.2. Example: Generating 32-bit Multiplier Using Module/IP Block Wizard |    |

| Figure 3.3. Example: Generating 32-bit Multiplier in IP Configuration          |    |

| Figure 4.1. Project with an Instance of Multiplier                             |    |

| Figure 4.2. File Selection Window                                              |    |

| Figure 4.3. Top Level Testbench Instance Added to the Project                  |    |

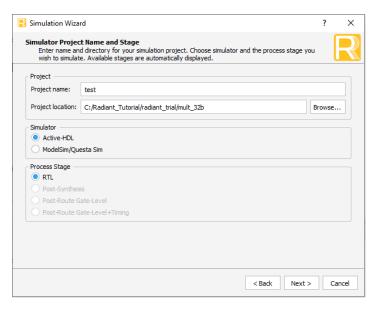

| Figure 4.4. Simulation Wizard                                                  | 30 |

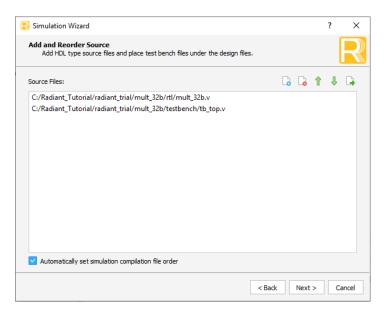

| Figure 4.5. Final Simulation Files                                             | 31 |

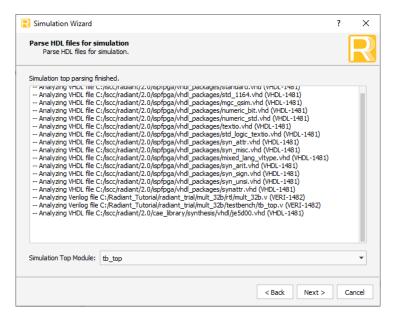

| Figure 4.6. File Parsing and Top Module Selection                              |    |

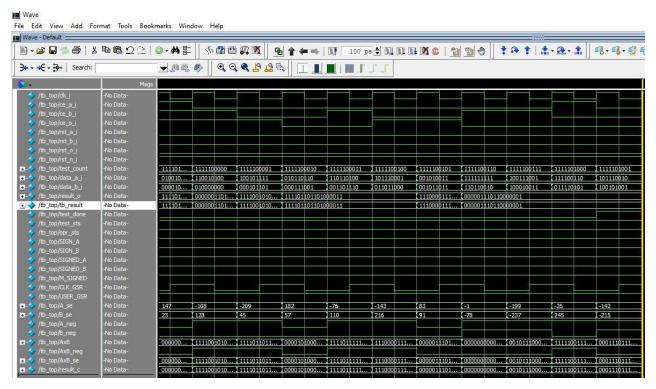

| Figure 4.7. Simulation Waveforms                                               |    |

## **Tables**

| Table 2.1. Multiplier Operation                           | 8  |

|-----------------------------------------------------------|----|

| Table 2.2. Multiplier Ports                               | 8  |

| Table 2.3. Multiplier Attributes                          | 9  |

| Table 2.4. Multiplier Timing Table                        | 10 |

| Table 2.5. Multiply-Accumulate Operations                 | 11 |

| Table 2.6. Multiply-Accumulate Ports                      | 11 |

| Table 2.7. Multiply-Accumulate Attributes                 | 12 |

| Table 2.8. Multiply-Accumulate Timing Table               | 13 |

| Table 2.9. Multiply-Add-Subtract Operations               | 14 |

| Table 2.10. Multiply-Add-Subtract Ports                   | 14 |

| Table 2.11. Multiply-Add-Subtract Attributes              | 15 |

| Table 2.12. Multiply-Add-Subtract Timing Table            | 17 |

| Table 2.13. Multiply-Add-Subtract-Sum Operation           | 18 |

| Table 2.14. Multiply-Add-Subtract-Sum Ports               | 18 |

| Table 2.15. Multiply-Add-Subtract-Sum Attributes          | 20 |

| Table 2.16. Multiply-Add-Subtract-Sum Timing Table        | 21 |

| Table 2.17. Multiply-Multiply-Accumulate Operations       | 22 |

| Table 2.18. Multiply-Multiply-Accumulate Ports            | 22 |

| Table 2.19. Multiply-Multiply-Accumulate Attributes       | 24 |

| Table 2.20. Multiply-Multiply-Accumulate Timing Table     | 25 |

| Table 4.1. File List                                      | 28 |

| Table A.1. Performance and Resource Utilization (LIFCL)   | 33 |

| Table A.2. Performance and Resource Utilization (LFCPNX)  | 33 |

| Table A.3. Performance and Resource Utilization (LIFCL)   | 33 |

| Table A.4. Performance and Resource Utilization (LFCPNX)  | 34 |

| Table A.5. Performance and Resource Utilization (LIFCL)   | 34 |

| Table A.6. Performance and Resource Utilization (LFCPNX)  | 34 |

| Table A.7. Performance and Resource Utilization (LIFCL)   | 34 |

| Table A.8. Performance and Resource Utilization (LFCPNX)  | 35 |

| Table A.9. Performance and Resource Utilization (LIFCL)   | 35 |

| Table A.10. Performance and Resource Utilization (LFCPNX) | 35 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                    |  |

|---------|-------------------------------|--|

| FPGA    | Field-Programmable Gate Array |  |

| IP      | Intellectual Property         |  |

| RTL     | Register Transfer Level       |  |

## 1. Introduction

The IP Catalog provides a variety of modules to assist your design work. These modules cover a variety of common functions and can be customized. They are optimized for Lattice FPGA devices built on the Lattice Nexus™ platform. Use these modules to speed up your design work and to produce the most effective results.

This guide describes the DSP Arithmetic modules that comes with the IP Catalog. These modules serve as the building block to realize a more complex or user-defined function. The descriptions mainly cover the ports, attributes and sample functional timing diagrams of the modules.

## 2. DSP Arithmetic Modules

## 2.1. Multiplier

A two-input multiplier performs signed/unsigned multiplication of the data from inputs data\_a\_i and data\_b\_i. The output result\_o carries the Product of the multiplication operation.

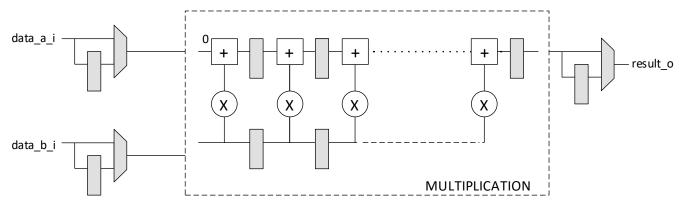

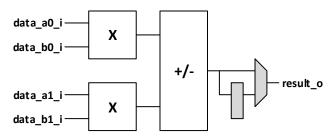

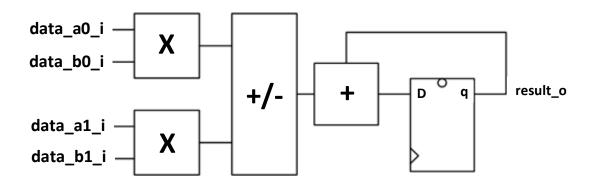

The shaded portions of the Multiplier Schematic Diagram, as shown in Figure 2.1, are optional and are removed/ignored in certain configurations. Function formula:

Figure 2.1. Multiplier Schematic Diagram

## 2.1.1. Multiplier Operation

**Table 2.1. Multiplier Operation**

| Configuration | Operation                    |

|---------------|------------------------------|

| Default       | result_o = data_a_i*data_b_i |

#### 2.1.2. Ports

**Table 2.2. Multiplier Ports**

| Signal Name | Direction | Width (bits) | Description                                                         |

|-------------|-----------|--------------|---------------------------------------------------------------------|

| clk_i       | IN        | 1            | This signal connects to the clock pin of the input, and output      |

|             |           |              | Unused when neither Input A, Input B or Output is set to Registered |

| ce_a_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input A  |

|             |           |              | 1'b0 – retain the previous state                                    |

|             |           |              | 1'b1 – toggle on the rising edge of the clock as per the logic      |

|             |           |              | Unused when Input A is not set to Registered.                       |

| ce_b_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input B  |

|             |           |              | 1'b0 – retain the previous state                                    |

|             |           |              | 1'b1 – toggle on the rising edge of the clock as per the logic      |

|             |           |              | Unused when Input B is not set to Registered                        |

| ce_o_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for Output   |

|             |           |              | 1'b0 – retain the previous state                                    |

|             |           |              | 1'b1 – toggle on the rising edge of the clock as per the logic      |

|             |           |              | Unused when Output is not set to Registered                         |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                                                         |

|-------------|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rst_a_i     | IN        | 1            | This signal initializes the flops of data_a_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Input A is not set to Registered. Reset mode depends on RST_MODE. |

| rst_b_i     | IN        | 1            | This signal initializes the flops of data_b_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Input B is not set to Registered. Reset mode depends on RST_MODE. |

| rst_o_i     | IN        | 1            | This signal initializes the flops of result_o in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Output is not set to Registered. Reset mode depends on RST_MODE.  |

| data_a_i    | IN        | A_WIDTH      | This signal contains an input for multiplication operation.                                                                                                                                                                                                         |

| data_b_i    | IN        | B_WIDTH      | This signal contains an input for multiplication operation.                                                                                                                                                                                                         |

| result_o    | ОИТ       | OUT_WIDTH    | This signal carries the product value of the multiplication.  Core functionality is represented below.  data_a_i × data_b_i                                                                                                                                         |

## 2.1.3. Attributes

## **Table 2.3. Multiplier Attributes**

| Configuration | Range            | Default Value | Description                                                                                                                                                                                                                      |

|---------------|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_WIDTH       | 2–72             | 9             | This configuration controls the width of the input data_a.                                                                                                                                                                       |

| B_WIDTH       | 2–72             | 9             | This configuration controls the width of the input data_b.                                                                                                                                                                       |

| OUT_WIDTH     | 4-144            | 18            | This parameter is uneditable and only gets the sum of A_WIDTH and B_WIDTH.  InputA Width + InputB Width = Result Width                                                                                                           |

| RST_MODE      | SYNC or ASYNC    | ASYNC         | This configuration controls the reset mode, either asynchronous reset or synchronous reset. When set to asynchronous reset, the reset value occurs at the preceding clock edge.                                                  |

| A_SIGNED      | Signed, Unsigned | Signed        | This configuration controls the sign interpretation of the input data_a_i, either signed or unsigned.                                                                                                                            |

| B_SIGNED      | Signed, Unsigned | Signed        | This configuration controls the sign interpretation of the input data_b_i, either signed or unsigned.                                                                                                                            |

| USE_IREGA     | on, off          | off           | This configuration controls the registering of input data_a_i before routing them to the multiplication operation.  off – Unregistered. Inputs are directly routed.  on – Registered. Inputs are registered before routing.      |

| USE_IREGB     | on, off          | off           | This configuration controls the registering of the inputs, data_b_i before routing them to the multiplication operation.  off — Unregistered. Inputs are directly routed. on — Registered. Inputs are registered before routing. |

| Configuration       | Range   | Default Value | Description                                                                                                                                                                                                         |  |

|---------------------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| USE_OREG            | on, off | off           | This configuration controls the registering of the multiplier result onto the output, result_o.  off – Unregistered. Result is directly routed to the output.  on – Registered. Result is registered at the output. |  |

| Internal Parameters |         |               |                                                                                                                                                                                                                     |  |

| A_WDT               | _       | _             | A_WDT = A_WIDTH                                                                                                                                                                                                     |  |

| B_WDT               | _       | _             | B_WDT = B_WIDTH                                                                                                                                                                                                     |  |

## 2.1.4. Timing Diagram

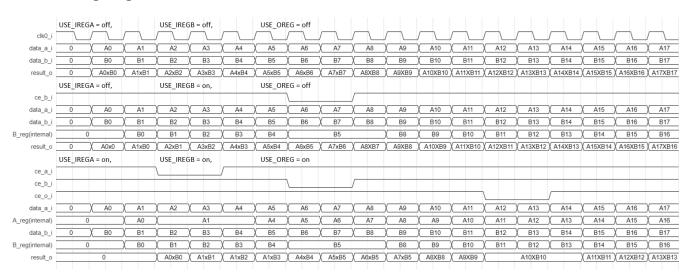

Figure 2.2. Multiplier Timing Diagram

**Table 2.4. Multiplier Timing Table**

| Att       | Latency from Input to Output |   |

|-----------|------------------------------|---|

| USE_IREG* | USE_OREG                     |   |

| 0         | 0                            | 0 |

| 0         | 1                            | 1 |

| 1         | 0                            | 1 |

| 1         | 1                            | 2 |

## 2.2. Multiply-Accumulate

A two-input multiplier with accumulate performs signed/unsigned multiplication of the data from inputs data\_a\_i and data\_b\_i and accumulates the result. The output result\_o carries the Accumulation of Products.

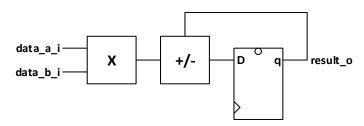

Figure 2.3. Multiply-Accumulate Schematic

## 2.2.1. Multiply-Accumulate Operation

**Table 2.5. Multiply-Accumulate Operations**

| Operation Dependency          | Operation                                      |

|-------------------------------|------------------------------------------------|

| addnsub_i = 0, accumsload = 0 | result_o = result_prev + (data_a_i × data_b_i) |

| addnsub_i = 0, accumsload = 1 | result_o = ld + (data_a_i × data_b_i)          |

| addnsub_i = 1, accumsload = 0 | result_o = result_prev - (data_a_i × data_b_i) |

| addnsub_i = 1, accumsload = 1 | result_o = ld - (data_a_i × data_b_i)          |

#### 2.2.2. Ports

**Table 2.6. Multiply-Accumulate Ports**

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                            |

|-------------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_i       | IN        | 1            | This signal connects to the clock pin of the input, and output Unused when neither Input A, Input B or Output is set to Registered                                                                                                     |

| ce_a_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input A  1'b0 – retain the previous state  1'b1 – toggle on the rising edge of the clock as per the logic  Unused when Input A is not set to Registered.                    |

| ce_b_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input B 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Unused when Input B is not set to Registered                        |

| ce_p_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for pipeline register  1'b0 – retain the previous state  1'b1 – toggle on the rising edge of the clock as per the logic  Unused when Pipeline Register is not set to Registered |

| ce_o_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for Output 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Unused when Output is not set to Registered                          |

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                                                                                |  |

|-------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rst_a_i     | IN        | 1            | This signal initializes the flops of data_a_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Input A is not set to Registered. Reset mode depends on RST_MODE.                        |  |

| rst_b_i     | IN        | 1            | This signal initializes the flops of data_b_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Input B is not set to Registered. Reset mode depends on RST MODE.                        |  |

| rst_p_i     | IN        | 1            | This signal initializes the flops of the pipelined signal in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Pipelined Register is not set to Registered. Reset mode depends on RST_MODE. |  |

| rst_o_i     | IN        | 1            | This signal initializes the flops of result_o in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Output is not set to Registered. Reset mode depends on RST MODE.                         |  |

| data_a_i    | IN        | A WIDTH      | This signal contains the multiplicand value of the multiplication.                                                                                                                                                                                                                         |  |

| data_b_i    | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication.                                                                                                                                                                                                                           |  |

| accumsload  | IN        | 1            | This signal destates if the ld input or the previews result_o is added/subtracted from the product of the two multipliers.                                                                                                                                                                 |  |

| ld          | IN        | ACC_WIDTH    | This signal is added or subtracted from the product of the two multiplier when accumsload is high.                                                                                                                                                                                         |  |

| addnsub_i   | IN        | 1            | This signal dictates the operation to be used by the accumulator – 1'b0 for addition and 1'b1 for subtraction.                                                                                                                                                                             |  |

| result_o    | ОИТ       | ACC_WIDTH    | This signal carries the accumulated value of the product of inputs data_a_i and data_b_i. Core functionality is represented below. $Result = LD + (DataA_i \times DataB_i) \; ; \; \text{accumsload} = 1, \\                   $                                                           |  |

## 2.2.3. Attributes

## **Table 2.7. Multiply-Accumulate Attributes**

| Configuration | Range                   | Default Value | Description                                                  |

|---------------|-------------------------|---------------|--------------------------------------------------------------|

| A_WIDTH       | 2–72                    | 9             | This configuration controls the width of the input data_a_i. |

| B_WIDTH       | 2–72                    | 9             | This configuration controls the width of the input data_b_i. |

| ACC_WIDTH     | (A_WIDTH+<br>B_WIDTH+1) | 19            | This configuration controls the accumulator width.           |

| Configuration | Range            | Default Value | Description                                                                                                                                                                                                                       |

|---------------|------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_SIGNED      | Signed, Unsigned | Unsigned      | This configuration controls the sign interpretation of the input data_a_i, either signed or unsigned.                                                                                                                             |

| B_SIGNED      | Signed, Unsigned | Unsigned      | This configuration controls the sign interpretation of the input data_b_i, either signed or unsigned.                                                                                                                             |

| RST_MODE      | SYNC or ASYNC    | ASYNC         | This configuration controls the reset mode, either asynchronous reset or synchronous reset. When set to asynchronous reset, the reset value occurs at the preceding clock edge.                                                   |

| USE_IREGA     | on, off          | off           | This configuration controls the registering of the inputs, data_a_i before routing them to the multiplication operation.  off – Unregistered. Inputs are directly routed.  on – Registered. Inputs are registered before routing. |

| USE_IREGB     | on, off          | off           | This configuration controls the registering of the inputs, data_b_i before routing them to the multiplication operation. off – Unregistered. Inputs are directly routed. on – Registered. Inputs are registered before routing.   |

| USE_PREG      | on, off          | off           | This configuration controls the insertion of pipeline into the multiplier operation.                                                                                                                                              |

| USE_OREG      | on               | on            | This configuration controls the registering of the result onto the output, result_o. This is not editable. Result is registered at the output.                                                                                    |

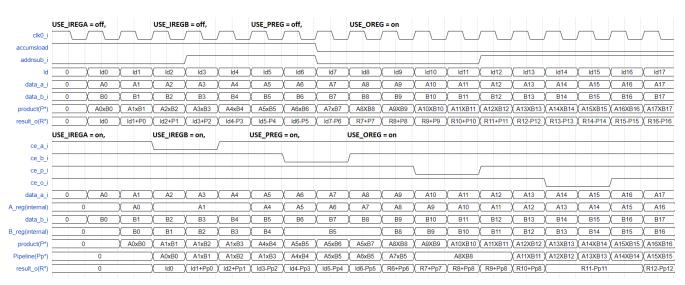

## 2.2.4. Timing Diagram

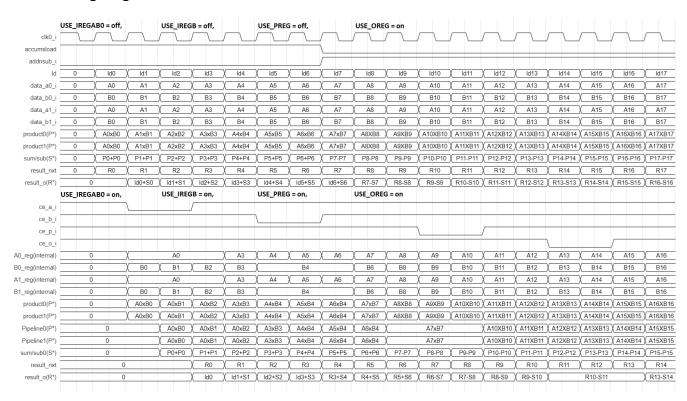

Figure 2.4. Multiply-Accumulate Timing Waveforms

Table 2.8. Multiply-Accumulate Timing Table

| Table Elot Maidply 7 | and Electrically / teaminated timing table |          |   |  |  |

|----------------------|--------------------------------------------|----------|---|--|--|

|                      | Latency from Input to Output               |          |   |  |  |

| USE_IREG*            | USE_PREG                                   | USE_OREG |   |  |  |

| 0                    | 0                                          | 1        | 1 |  |  |

| 0                    | 1                                          | 1        | 2 |  |  |

| 1                    | 0                                          | 1        | 2 |  |  |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

|           | Latency from Input to Output |   |   |

|-----------|------------------------------|---|---|

| USE_IREG* | USE_PREG                     |   |   |

| 1         | 1                            | 1 | 3 |

## 2.3. Multiply-Add-Subtract

A pair of two-input multipliers that performs signed/unsigned multiplication of the data from inputs data\_a and data\_b with addition/subtraction on the product pair. The output result\_o carries the Sum/Difference of Products.

Figure 2.5. Multiply-Add-Subtract Schematic

## 2.3.1. Multiply-Add-Subtract Operation

## **Table 2.9. Multiply-Add-Subtract Operations**

| Operation Dependency | Operation                                                    |

|----------------------|--------------------------------------------------------------|

| addnsub_i = 0        | result_o = (data_a0_i × data_b0_i) + (data_a1_i × data_b1_i) |

| addnsub_i = 1        | result_o = (data_a0_i × data_b0_i) - (data_a1_i × data_b1_i) |

## 2.3.2. Ports

**Table 2.10. Multiply-Add-Subtract Ports**

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                             |

|-------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_i       | IN        | 1            | This signal connects to the clock pin of the input, and output Unused when neither Input A, Input B or Output is set to Registered                                                                                                      |

| ce_a_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input A 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Unused when Input A is not set to Registered.                        |

| ce_b_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input B 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Unused when Input B is not set to Registered                         |

| ce_p_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for pipeline register  1'b0 – toggles the previous state  1'b1 – toggle on the rising edge of the clock as per the logic  Unused when Pipeline Register is not set to Registered |

| ce_o_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for Output 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Unused when Output is not set to Registered                           |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                                                                                |

|-------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rst_a_i     | IN        | 1            | This signal initializes the flops of data_a_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Input A is not set to Registered. Reset mode depends on RST_MODE.                        |

| rst_b_i     | IN        | 1            | This signal initializes the flops of data_b_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Input B is not set to Registered. Reset mode depends on RST_MODE.                        |

| rst_p_i     | IN        | 1            | This signal initializes the flops of the pipelined signal in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Pipelined Register is not set to Registered. Reset mode depends on RST_MODE. |

| rst_o_i     | IN        | 1            | This signal initializes the flops of result_o in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Unused when Output is not set to Registered. Reset mode depends on RST MODE.                         |

| data_a0_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a0_i - data_b0_i.                                                                                                                                                                                              |

| data_a1_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a1_i - data_b1_i.                                                                                                                                                                                              |

| data_b0_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a0_i - data_b0_i.                                                                                                                                                                                                |

| data_b1_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_b0_i - data_b1_i.                                                                                                                                                                                                |

| addnsub_i   | IN        | 1            | This signal dictates the operation to be used by the accumulator – 1'b0 for addition and 1'b1 for subtraction.                                                                                                                                                                             |

| result_o    | OUT       | ACC_WIDTH    | This signal carries the result_o of the addition/subtraction of the multiplication products.  Core functionality is represented below.  M0 = (data_a0_i × data_b0_i)  M1 = (data_a1_i × data_b1_i)  addnsub_i == 0: {M0 + M1}  addnsub_i == 1: {M0 - M1}                                   |

## 2.3.3. Attributes

## **Table 2.11. Multiply-Add-Subtract Attributes**

| Configuration | Range | Default Value | Description                                                                  |

|---------------|-------|---------------|------------------------------------------------------------------------------|

| A_WIDTH       | 2–72  | 9             | This configuration controls the width of the inputs data_a0_i and data_a1_i. |

| B_WIDTH       | 2–72  | 9             | This configuration controls the width of the inputs data_b0_i and data_b1_i. |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Configuration | Range            | Default Value | Description                                                                                                                                                                                                                                      |

|---------------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACC_WIDTH     | 5-145            | 19            | This parameter is uneditable and only gets the sum of A_WIDTH, B_WIDTH + 1. Input A Width + Input B Width + 1 = Result Width                                                                                                                     |

| A_SIGNED      | Signed, Unsigned | Unsigned      | This configuration controls the sign interpretation of the input data_a0_i and data_a1_i, either signed or unsigned.                                                                                                                             |

| B_SIGNED      | Signed, Unsigned | Unsigned      | This configuration controls the sign interpretation of the input data_b0_i and data_b1_i, either signed or unsigned.                                                                                                                             |

| RST_MODE      | SYNC or ASYNC    | SYNC          | This configuration controls the reset mode, either asynchronous reset or synchronous reset. When set to asynchronous reset, the reset value occurs at the preceding clock edge.                                                                  |

| USE_IREGAB0   | on, off          | on            | This configuration controls the registering of the inputs, data_a0_i and data_b0_i before routing them to the multiplication operation.  off – Unregistered. Inputs are directly routed.  on – Registered. Inputs are registered before routing. |

| USE_IREGAB1   | on, off          | on            | This configuration controls the registering of the inputs, data_a1_i and data_b1_i before routing them to the multiplication operation.  off – Unregistered. Inputs are directly routed.  on – Registered. Inputs are registered before routing. |

| USE_OREG      | on, off          | on            | This configuration controls the registering of the output, result_o.  off – Unregistered. Result is directly routed to the output.  on – Registered. Result is registered at the output.                                                         |

| USE_PREG      | on, off          | on            | This configuration controls the insertion of pipeline into the multiplier operation.                                                                                                                                                             |

#### 2.3.4. Timing Diagram

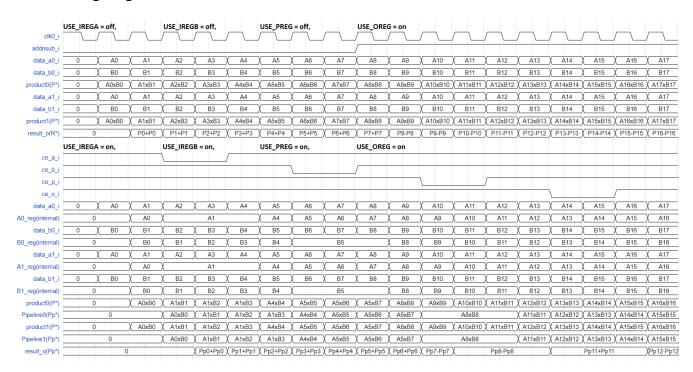

Figure 2.6. Multiply-Add-Subtract Timing Diagram

Table 2.12. Multiply-Add-Subtract Timing Table

|           | Attribute |          |   |  |  |

|-----------|-----------|----------|---|--|--|

| USE_IREG* | USE_PREG  | USE_OREG |   |  |  |

| 0         | 0         | 0        | 0 |  |  |

| 1         | 0         | 0        | 1 |  |  |

| 0         | 1         | 0        | 1 |  |  |

| 0         | 0         | 1        | 1 |  |  |

| 0         | 1         | 1        | 2 |  |  |

| 1         | 0         | 1        | 2 |  |  |

| 1         | 1         | 0        | 2 |  |  |

| 1         | 1         | 1        | 3 |  |  |

## 2.4. Multiply-Add-Subtract-Sum

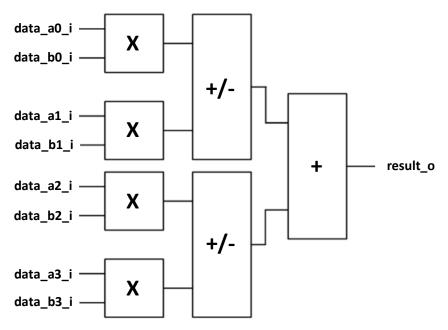

Two pair of two-input multipliers that performs signed/unsigned multiplication of the data from inputs data\_a and data\_b with addition/subtraction on the product pair. The output result\_o carries the Sumation of the results from the result of the added/subtracted procut pair.

Figure 2.7. Multiply-Add-Subtract-Sum Schematic

## 2.4.1. Multiply-Add-Subtract-Sum Operation

Table 2.13. Multiply-Add-Subtract-Sum Operation

| Operation Dependency             | Operation                                                                                                                                                          |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| addnsub0_i = 0<br>addnsub1_i = 0 | result_o = {(data_a0_i × data_b0_i) + (data_a1_i × data_b1_i) } + {(data_a2_i × data_b2_i) + (data_a3_i × data_b3_i)}                                              |

| addnsub0_i = 1<br>addnsub1_i = 1 | $result\_o = \{(data\_a0\_i \times data\_b0\_i) - (data\_a1\_i \times data\_b1\_i)\} + \{(data\_a2\_i \times data\_b2\_i) - (data\_a3\_i \times data\_b3\_i)\} \}$ |

## 2.4.2. Ports

Table 2.14. Multiply-Add-Subtract-Sum Ports

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                             |

|-------------|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_i       | IN        | 1            | This signal connects to the clock pin of the input, and output Unused when neither Input A, Input B or Output is set to Registered                                                                                                      |

| ce_a_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input A 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Un-used when Input A is not set to Registered.                       |

| ce_b_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input B 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Un-used when Input B is not set to Registered                        |

| ce_p_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for pipeline register  1'b0 – retain the previous state  1'b1 – toggle on the rising edge of the clock as per the logic  Un-used when Pipeline Register is not set to Registered |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ce_o_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for Output 1'b0 – retain the previous state 1'b1 – toggle on the rising edge of the clock as per the logic Un-used when Output is not set to Registered                                                                                                                                                                   |

| rst_a_i     | IN        | 1            | This signal initializes the flops of data_a_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Input A is not set to Registered. Reset mode depends on RST_MODE.                                                                                                             |

| rst_b_i     | IN        | 1            | This signal initializes the flops of data_b_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Input B is not set to Registered. Reset mode depends on RST_MODE.                                                                                                             |

| rst_p_i     | IN        | 1            | This signal initializes the flops of the pipelined signal in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Pipelined Register is not set to Registered. Reset mode depends on RST_MODE.                                                                                      |

| rst_o_i     | IN        | 1            | This signal initializes the flops of result_o in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Output is not set to Registered. Reset mode depends on RST_MODE.                                                                                                              |

| data_a0_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a0_i - data_b0_i.                                                                                                                                                                                                                                                                                    |

| data_a1_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a1_i - data_b1_i.                                                                                                                                                                                                                                                                                    |

| data_a2_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a2_i - data_b2_i.                                                                                                                                                                                                                                                                                    |

| data_a3_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a3_i - data_b3_i.                                                                                                                                                                                                                                                                                    |

| data_b0_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a0_i - data_b0_i.                                                                                                                                                                                                                                                                                      |

| data_b1_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a1_i - data_b1_i.                                                                                                                                                                                                                                                                                      |

| data_b2_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a2_i - data_b2_i.                                                                                                                                                                                                                                                                                      |

| data_b3_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a3_i - data_b3_i.                                                                                                                                                                                                                                                                                      |

| addnsub_i   | IN        | 1            | This signal dictates the operation to be used by the accumulator – 1'b0 for addition and 1'b1 for subtraction.                                                                                                                                                                                                                                                                   |

| result_o    | OUT       | ACC_WIDTH    | This signal carries the result_o of the addition/subtraction of the multiplication products.  Core functionality is represented below.  M0 = (data_a0_i × data_b0_i), M1 = (data_a1_i × data_b1_i),  M2 = (data_a2_i × data_b2_i), M3 = (data_a3_i × data_b3_i)  addnsub0_i == 0: {M0 + M1}, addnsub0_i == 1: {M0 - M1},  addnsub1_i == 0: {M2 + M3}, addnsub1_i == 1: {M2 - M3} |

## 2.4.3. Attributes

## Table 2.15. Multiply-Add-Subtract-Sum Attributes

| Configuration | Range            | <b>Default Value</b> | Description                                                                                                                                                                                                                                                             |  |

|---------------|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A_WIDTH       | 2–72             | 9                    | This configuration controls the width of the inputs data_a0_i, data_a1_i, data_a2_i, and data_a3_i.                                                                                                                                                                     |  |

| B_WIDTH       | 2–72             | 9                    | This configuration controls the width of the inputs data_b0_i, data_b1_i, data_b2_i, and data_b3_i.                                                                                                                                                                     |  |

| ACC_WIDTH     | 7-147            | 20                   | This parameter is uneditable, it only gets the sum of A_WIDTH, B_WIDTH + 3. Input A Width + Input B Width + 3 = Result Width                                                                                                                                            |  |

| A_SIGNED      | Signed, Unsigned | Unsigned             | This configuration controls the sign interpretation of the input data_a0_i, data_a1_i, data_a2_i, and data_a3_i; either signed or unsigned.                                                                                                                             |  |

| B_SIGNED      | Signed, Unsigned | Unsigned             | This configuration controls the sign interpretation of the input data_b0_i, data_b1_i, data_b2_i, and data_b3_i; either signed or unsigned.                                                                                                                             |  |

| USE_IREGA     | on, off          | on                   | This configuration controls the registering of the inputs, data_a0_i, data_a1_i, data_a2_i, and data_a3_i before routing them to the multiplication operation.  off — Unregistered. Inputs are directly routed.  on — Registered. Inputs are registered before routing. |  |

| USE_IREGB     | on, off          | on                   | This configuration controls the registering of the inputs, data_b0_i, data_b1_i, data_b2_i, and data_b3_i before routing them to the multiplication operation.  off — Unregistered. Inputs are directly routed. on — Registered. Inputs are registered before routing.  |  |

| USE_OREG      | on, off          | on                   | This configuration controls the registering of the output, result_o.  off – Unregistered. Result is directly routed to the output.  on – Registered. Result is registered at the output.                                                                                |  |

| USE_PREG      | on, off          | on                   | This configuration controls the insertion of pipeline into the multiplier operation.                                                                                                                                                                                    |  |

| RST_MODE      | SYNC or ASYNC    | SYNC                 | This configuration controls the reset mode, either asynchronous reset or synchronous reset. When set to asynchronous reset, the reset value occurs at the preceding clock edge.                                                                                         |  |

#### 2.4.4. Timing Diagram

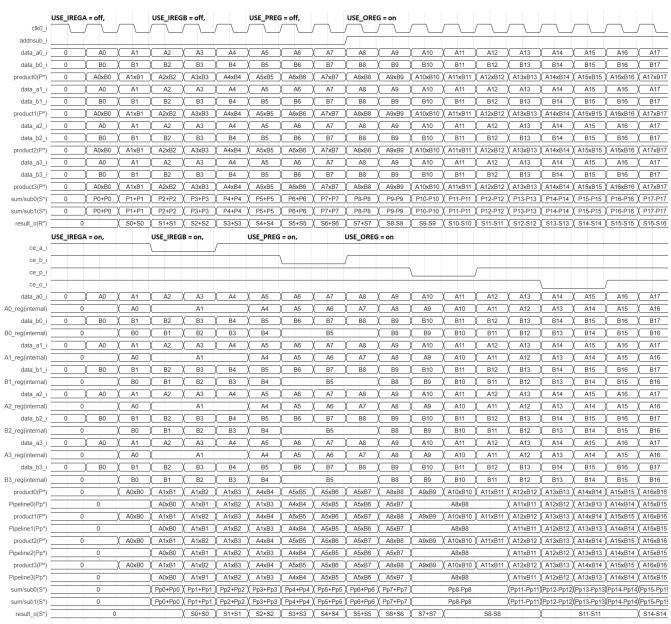

Figure 2.8. Multiply-Add-Subtract-Sum Timing Diagram

Table 2.16. Multiply-Add-Subtract-Sum Timing Table

|           | Attribute |          |   |  |  |

|-----------|-----------|----------|---|--|--|

| USE_IREG* | USE_PREG  | USE_OREG |   |  |  |

| 0         | 0         | 0        | 0 |  |  |

| 1         | 0         | 0        | 1 |  |  |

| 0         | 1         | 0        | 1 |  |  |

| 0         | 0         | 1        | 1 |  |  |

| 0         | 1         | 1        | 2 |  |  |

| 1         | 0         | 1        | 2 |  |  |

| 1         | 1         | 0        | 2 |  |  |

|           | Attribute |   |   |  |

|-----------|-----------|---|---|--|

| USE_IREG* | USE_PREG  |   |   |  |

| 1         | 1         | 1 | 3 |  |

## 2.5. Multiply-Multiply-Accumulate

A pair of two-input multipliers that performs signed/unsigned multiplication of the data from inputs data\_a\* and data\_b\* with addition/subtraction of the product pair and an accumulator at the end. The output result\_o carries the Sum/Difference of Products added to the previews result\_o or ld input depending on the accumsload value.

Figure 2.9. Multiply-Multiply-Accumulate Schematic

## 2.5.1. Multiply-Multiply-Accumulate Operation

Table 2.17. Multiply-Multiply-Accumulate Operations

| Operation Dependency          | Operation                                                                 |

|-------------------------------|---------------------------------------------------------------------------|

| addnsub_i = 0, accumsload = 0 | result_o = result_nxt + (data_a0_i × data_b0_i) + (data_a1_i × data_b1_i) |

| addnsub_i = 0, accumsload = 1 | result_o = ld + (data_a0_i × data_b0_i) + (data_a1_i × data_b1_i)         |

| addnsub_i = 1, accumsload = 0 | result_o = result_nxt + (data_a0_i × data_b0_i) - (data_a1_i × data_b1_i) |

| addnsub_i = 1, accumsload = 1 | result_o = ld + (data_a0_i × data_b0_i) - (data_a1_i × data_b1_i)         |

#### 2.5.2. Ports

22

Table 2.18. Multiply-Multiply-Accumulate Ports

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                       |

|-------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_i       | IN        | 1            | This signal connects to the clock pin of the input, and output Un-used when neither Input A, Input B or Output is set to Registered                                                                               |

| ce_a_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input A 1'b0 - retain the previous state 1'b1 - toggle on the rising edge of the clock as per the logic Un-used when Input A is not set to Registered. |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02050-1.5

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                                                                                 |

|-------------|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ce_b_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for input B 1'b0 - retain the previous state 1'b1 - toggle on the rising edge of the clock as per the logic Un-used when Input B is not set to Registered                                                                            |

| ce_p_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for pipeline register  1'b0 - retain the previous state of the multipliers  1'b1 - toggle on the rising edge of the clock as per the logic  Un-used when Pipeline Register is not set to Registered                                  |

| ce_o_i      | IN        | 1            | This signal is an active HIGH synchronous clock enable for Output 1'b0 - retain the previous state 1'b1 - toggle on the rising edge of the clock as per the logic Un-used when Output is not set to Registered                                                                              |

| rst_a_i     | IN        | 1            | This signal initializes the flops of data_a_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Input A is not set to Registered. Reset mode depends on RST_MODE.                        |

| rst_b_i     | IN        | 1            | This signal initializes the flops of data_b_i in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Input B is not set to Registered. Reset mode depends on RST_MODE.                        |

| rst_p_i     | IN        | 1            | This signal initializes the flops of the pipelined signal in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Pipelined Register is not set to Registered. Reset mode depends on RST_MODE. |

| rst_o_i     | IN        | 1            | This signal initializes the flops of result_o in the design to a known state.  It is an active HIGH reset whose deassertion should be synchronized with the clock during integration. Un-used when Output is not set to Registered. Reset mode depends on RST_MODE.                         |

| data_a0_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a0_i - data_b0_i.                                                                                                                                                                                               |

| data_a1_i   | IN        | A_WIDTH      | This signal contains the multiplicand value of the multiplication pair data_a1_i - data_b1_i.                                                                                                                                                                                               |

| data_b0_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a0_i - data_b0_i.                                                                                                                                                                                                 |

| data_b1_i   | IN        | B_WIDTH      | This signal contains the multiplier value of the multiplication pair data_a1_i - data_b1_i.                                                                                                                                                                                                 |

| accumsload  | IN        | 1            | This signal destates if the ld input or the previews result_o is added from the product of the two multipliers.                                                                                                                                                                             |

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Signal Name | Direction | Width (bits) | Description                                                                                                                                                                                                                                                                                                             |

|-------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ld          | IN        | ACC_WIDTH    | This signal is added or subtracted from the product of the two multiplier when accumsload is high.                                                                                                                                                                                                                      |

| addnsub_i   | IN        | 1            | This signal dictates the operation to be used on the product pair. '0' for addition and '1' for subtraction.                                                                                                                                                                                                            |

| result_o    | ОИТ       | ACC_WIDTH    | This signal carries the result_o of the addition/subtraction of the multiplication products added to the previews result_o.  Core functionality is represented below.  M0 = (data_a0_i × data_b0_i)  M1 = (data_a1_i × data_b1_i)  result_nxt = previews result_o  addnsub_i == 0: {M0 + M1}  addnsub_i == 1: {M0 - M1} |

## 2.5.3. Attributes

## Table 2.19. Multiply-Multiply-Accumulate Attributes

| Configuration | Range            | Default Value | Description                                                                                                                                                                                                                                     |

|---------------|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_WIDTH       | 2–72             | 9             | This configuration controls the width of the inputs data_a0_i and data_a1_i.                                                                                                                                                                    |

| B_WIDTH       | 2–72             | 9             | This configuration controls the width of the inputs data_b0_i and data_b1_i.                                                                                                                                                                    |

| ACC_WIDTH     | 7-147            | 21            | This parameter is uneditable, it only gets the sum A_WIDTH, B_WIDTH + 3.  Input A Width + Input B Width + 3 = Result Width                                                                                                                      |

| A_SIGNED      | Signed, Unsigned | Unsigned      | This configuration controls the sign interpretation of the input data_a0_i and data_a1_i, either signed or unsigned.                                                                                                                            |

| B_SIGNED      | Signed, Unsigned | Unsigned      | This configuration controls the sign interpretation of the input data_b0_i and data_b1_i, either signed or unsigned.                                                                                                                            |

| RST_MODE      | SYNC or ASYNC    | SYNC          | This configuration controls the reset mode, either asynchronous reset or synchronous reset.                                                                                                                                                     |

| USE_IREGAB0   | On, Off          | On            | This configuration controls the registering of the inputs, data_a0_i and data_b0_i before routing them to the multiplication operation.  off – Unregistered. Inputs are directly routed. on – Registered. Inputs are registered before routing. |

| USE_IREGAB1   | On, Off          | On            | This configuration controls the registering of the inputs, data_a1_i and data_b1_i before routing them to the multiplication operation.  off – Unregistered. Inputs are directly routed. on – Registered. Inputs are registered before routing. |

| USE_PREG      | On, Off          | Off           | This configuration controls the insertion of pipeline into the multiplier operation.                                                                                                                                                            |

| USE_OREG      | On               | On            | Not Configurable                                                                                                                                                                                                                                |

## 2.5.4. Timing Diagram

Figure 2.10. Multiply-Multiply-Accumulate Timing Diagram

Table 2.20. Multiply-Multiply-Accumulate Timing Table

|           | Attribute |          |   |  |  |

|-----------|-----------|----------|---|--|--|

| USE_IREG* | USE_PREG  | USE_OREG |   |  |  |

| 0         | 0         | 0        | 0 |  |  |

| 1         | 0         | 0        | 1 |  |  |

| 0         | 1         | 0        | 1 |  |  |

| 0         | 0         | 1        | 1 |  |  |

| 0         | 1         | 1        | 2 |  |  |

| 1         | 0         | 1        | 2 |  |  |

| 1         | 1         | 0        | 2 |  |  |

| 1         | 1         | 1        | 3 |  |  |

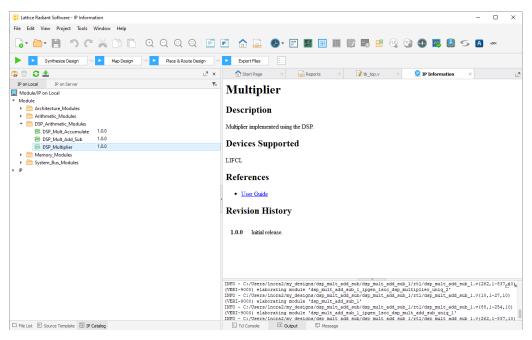

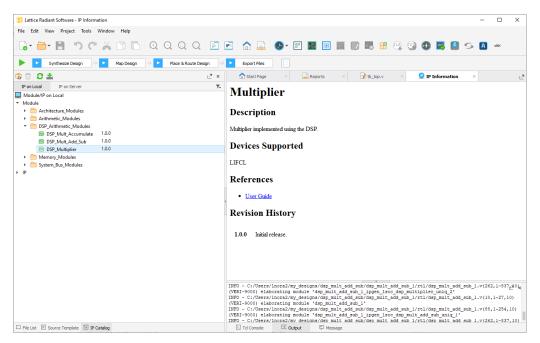

## 3. IP Generation

The Module/IP Block Wizard in Lattice Radiant™ Software allows you to generate, create, or open modules for the target device. From the Lattice Radiant Software, select the IP Catalog tab as shown in Figure 3.1.

The left pane of the IP Catalog window displays the module/IP tree. You can utilize this to specify a variety of arithmetic modules in your designs.

The available arithmetic modules in the Lattice Radiant Software IP catalog are:

- Multiplier

- Mult-Accumulate

- Mult-Add-Sub

The right pane of the window shows the description of the selected module and provides link(s) to the documentation.

Figure 3.1. DSP Arithmetic Modules

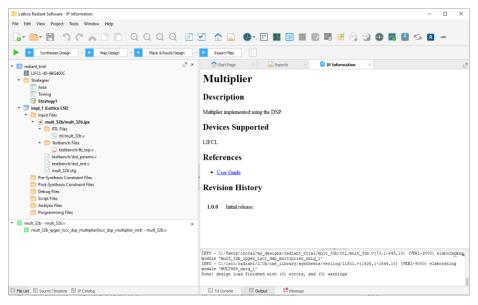

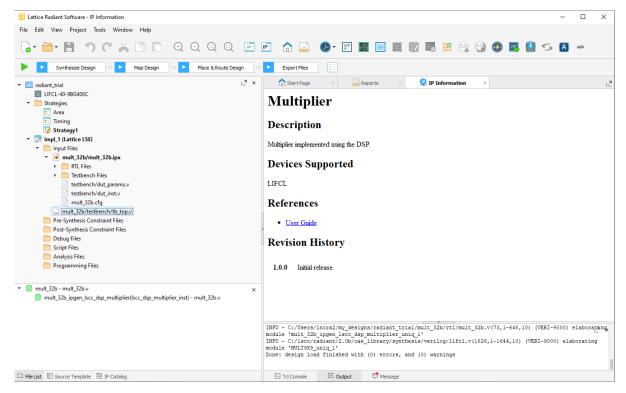

## 3.1. Generating a 32-bit Multiplier Module

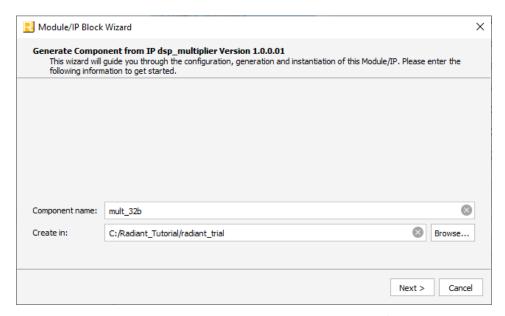

The following section shows an example of generating a 32-bit Multiplier module. This process is similar for all DSP Arithmetic Modules.

To generate a 32-bit Multiplier module:

- 1. Double-click Multiplier under DSP Arithmetic Modules. This opens the Module/IP Block Wizard.

- 2. Fill out the following information then click **Next**. An example is shown in Figure 3.3.

- Language

- Instance name

- Create in

Figure 3.2. Example: Generating 32-bit Multiplier Using Module/IP Block Wizard

3. In the IP Configuration page, customize the Multiplier by selecting options as shown in Figure 3.3.

Figure 3.3. Example: Generating 32-bit Multiplier in IP Configuration

- 4. When all the options are set, click **Generate**.

- 5. Click Finish.

Once this module is in the Lattice Radiant Software project, it can be instantiated in other modules within the project. You can view the files and instance/s added in the **File List** tab.

# 4. Simulation Flow

The Lattice Radiant software also allows you to simulate configured arithmetic modules, so you can observe the conditions of the output with a given stimuli. This section details the individual steps needed to run simulation through Simulation Wizard. In the sample procedure, a Multiplier on default settings is generated, including instance name for the multiplier.

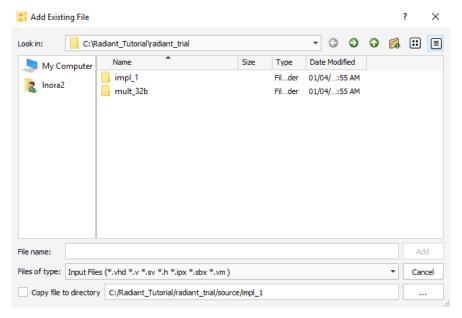

Table 4.1 provides a summary description of the files used in the project.

Table 4.1. File List

| File                                                                                        | Sim | Synthesis | Description                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rlt/ <instance_name>.v</instance_name>                                                      | Yes | Yes       | Top Level RTL file with the selected configuration. The main IP file                                                                                                                                                                                                                                                                  |

| testbench/dut_params                                                                        | Yes | _         | Top level parameters of the generated RTL file                                                                                                                                                                                                                                                                                        |

| testbench/dut_inst                                                                          | Yes | _         | Instantiated version of the <ip_name>.v file for simulation use</ip_name>                                                                                                                                                                                                                                                             |

| tb_top.v                                                                                    | Yes | _         | Test bench template, this can be edited by the user to match their specific needs.                                                                                                                                                                                                                                                    |

| <instance_name>.cfg</instance_name>                                                         | _   | _         | This file contains the configuration options used to recreate or modify the core in the IP Platform.                                                                                                                                                                                                                                  |

| <instance_name>.ipx</instance_name>                                                         | _   | _         | The IPX file holds references to all of the elements of an IP or Module after it is generated from the IP Platform GUI. The file is used to bring in the appropriate files during the design implementation and analysis. It is also used to re-load parameter settings into the IP Platform when the IP/Module is being regenerated. |