# Implementing High-Speed Interfaces with MachXO3D Usage Guide

# **Technical Note**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Acronyms in This Document                                     | t                                       |

|---------------------------------------------------------------|-----------------------------------------|

| 1. Introduction                                               | 7                                       |

| 2. Architecture for High-Speed Interfaces                     | 8                                       |

| 2.1. Gearing Logic Distribution                               | 8                                       |

| 2.2. Different Types of I/O Logic Cells                       | 8                                       |

| 2.3. Clock Domain Transfer at PIO Cells                       |                                         |

| 3. External High-Speed Interface Description                  | 16                                      |

| 4. High-Speed Interface Building Blocks                       | 17                                      |

| 4.1. ECLK                                                     |                                         |

| 4.2. ECLKSYNC                                                 | 17                                      |

| 4.3. SCLK                                                     | 17                                      |

| 4.4. CLKDIV                                                   | 17                                      |

| 4.5. PLL                                                      | 17                                      |

| 4.6. DQSDLL                                                   |                                         |

| 4.7. Input DDR (IDDR)                                         |                                         |

| 4.8. Output DDR (ODDR)                                        |                                         |

| 4.9. Delays                                                   |                                         |

| 5. Generic High-Speed DDR Interfaces                          |                                         |

| 5.1. High-Speed GDDR Interface Types                          |                                         |

| 5.2. High-Speed GDDR Interface Details                        |                                         |

| 5.2.1. Receive Interfaces                                     |                                         |

| 5.2.2. Transmit Interfaces                                    |                                         |

| 6. Using IPexpress to Build Generic High-Speed DDR Interfaces |                                         |

| 6.1. Building the SDR Interface                               |                                         |

| 6.2. Building DDR Generic Interfaces                          |                                         |

| 6.3. Building a Generic DDR 7:1 Interface                     |                                         |

| 7. Generic High-Speed DDR Design Guidelines                   |                                         |

| 7.1. I/O Logic Cells and Gearing Logic                        |                                         |

| 7.2. High-Speed ECLK Bridge                                   |                                         |

| 7.3. Reset Synchronization Requirement                        |                                         |

| 7.4. Timing Analysis for High-Speed GDDR Interfaces           |                                         |

| 7.4.1. Frequency Constraints                                  |                                         |

| 7.4.2. Setup and Hold Time Constraints                        |                                         |

| 7.4.3. Clock-to-Out Constraints                               | 47                                      |

| 7.4.4. Timing Rule Check for Clock Domain Transfers           |                                         |

| 8. DDR Software Primitives and Attributes                     | 51                                      |

| 8.1. Input DDR Primitives                                     | 51                                      |

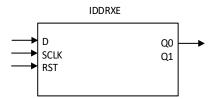

| 8.1.1. IDDRXE                                                 |                                         |

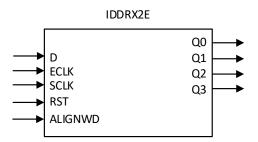

| 8.1.2. IDDRX2E                                                |                                         |

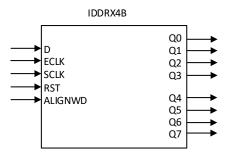

| 8.1.3. IDDRX4B                                                |                                         |

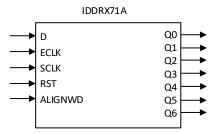

| 8.1.4. IDDRX71A                                               |                                         |

| 8.2. Output DDR Primitives                                    |                                         |

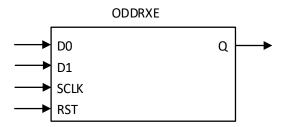

| 8.2.1. ODDRXE                                                 |                                         |

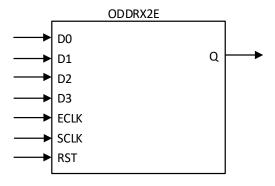

| 8.2.2. ODDRX2E                                                | • • • • • • • • • • • • • • • • • • • • |

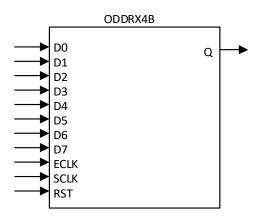

| 8.2.3. ODDRX4B                                                |                                         |

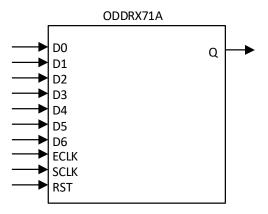

| 8.2.4. ODDRX71A                                               |                                         |

| 8.3. DDR Control Logic Primitives                             |                                         |

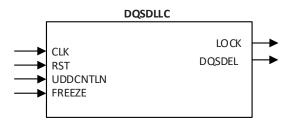

| 8.3.1. DQSDLLC                                                |                                         |

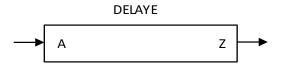

| 8.3.2. DELAYE                                                 |                                         |

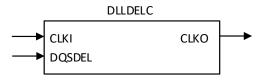

| 8.3.4. DLLDELC                                                |                                         |

| Technical Support Assistance                                  |                                         |

| Revision History                                              |                                         |

|                                                               |                                         |

# **Figures**

| Figure 2.1. Basic PIO Cell Support ×1 Gearing Ratio                            | 9  |

|--------------------------------------------------------------------------------|----|

| Figure 2.2. Video PIO Cell for ×2/×4 and 7:1 Applications in MachXO3D Devices  | 11 |

| Figure 2.3. 7:1 Deserializer Timing in MachXO3D Device                         |    |

| Figure 2.4. ×4 Deserializer Timing (Even Phases, SEL=0)                        |    |

| Figure 2.5. ×4 Deserializer Timing (Odd Phases, SEL=1)                         |    |

| Figure 2.6. ×2 Deserializer Timing (Even Phases, SEL=0)                        | 13 |

| Figure 2.7. ×2 Deserializer Timing (Odd Phases, SEL=1)                         |    |

| Figure 2.8. 7:1 Deserializer Timing in Response to ALIGNWD in MachXO3D Device  |    |

| Figure 2.9. ×4 Deserializer Timing in Response to ALIGNWD (Even-to-Odd Phase)  |    |

| Figure 2.10. ×4 Deserializer Timing in Response to ALIGNWD (Odd-to-Even Phase) |    |

| Figure 3.1. External Interface Definition                                      | 16 |

| Figure 5.1. GIREG_RX Interface                                                 | 20 |

| Figure 5.2. GDDRX1_RX.SCLK.Aligned Interface Using DQSDLL                      | 21 |

| Figure 5.3. GDDRX1_RX.SCLK.Centered                                            | 21 |

| Figure 5.4. GDDRX2_RX.ECLK.Aligned Interface                                   | 22 |

| Figure 5.5. GDDRX2_RX.ECLK.Centered Interface                                  | 23 |

| Figure 5.6. GDDRX4_RX.ECLK.Aligned Interface                                   |    |

| Figure 5.7. GDDRX4_RX.ECLK.Centered Interface                                  | 25 |

| Figure 5.8. GDDR71_RX.ECLK.7:1 Interface                                       |    |

| Figure 5.9. GOREG_TX.SCLK Interface                                            | 27 |

| Figure 5.10. GDDRX1_TX.SCLK.Aligned Interface                                  | 28 |

| Figure 5.11. GDDRX1_TX.SCLK.Centered Interface                                 | 29 |

| Figure 5.12. GDDRX2_TX.ECLK.Aligned Interface                                  |    |

| Figure 5.13. GDDRX2_TX.ECLK.Centered Interface                                 |    |

| Figure 5.14. GDDRX4_TX.ECLK.Aligned Interface                                  | 32 |

| Figure 5.15. GDDRX4_TX.ECLK.Centered Interface                                 |    |

| Figure 5.16. GDDR71_TX.ECLK.7:1 Interface                                      |    |

| Figure 6.1. SDR Interface Selection at the IPexpress Main Window               |    |

| Figure 6.2. Configuration Tab for the SDR Interface                            |    |

| Figure 6.3. DDR_Generic Interface Selection at the IPexpress Main Window       |    |

| Figure 6.4. Pre-Configuration Tab of the DDR_Generic Interfaces                |    |

| Figure 6.5. Configuration Tab of the DDR_Generic Modules                       |    |

| Figure 6.6. GDDR_71 Interface Selection at the IPexpress Main Window           |    |

| Figure 6.7. Configuration Tab of GDDR_71                                       |    |

| Figure 7.1. Reset Synchronization for Receive Interfaces                       |    |

| Figure 7.2. Reset Synchronization for Transmit Interfaces                      |    |

| Figure 7.3. Receiver RX.CLK.Centered Waveforms                                 |    |

| Figure 7.4. Receiver RX.CLK.Aligned Input Waveforms                            |    |

| Figure 7.5. Receiver GDDR71_RX. Waveforms                                      |    |

| Figure 7.6. t <sub>co</sub> Minimum and Maximum Timing Analysis                |    |

| Figure 7.7. Transmitter TX.CLK.Centered Output Waveforms                       |    |

| Figure 7.8. Transmitter TX.CLK.Aligned Waveforms                               |    |

| Figure 7.9. Transmitter GDDR71_TX. Waveforms                                   |    |

| Figure 8.1. IDDRXE Symbol                                                      |    |

| Figure 8.2. IDDRX2E Symbol                                                     |    |

| Figure 8.3. IDDRX4B Symbol                                                     |    |

| Figure 8.4. IDDRX71A Symbol                                                    |    |

| Figure 8.5. ODDRXE Symbol                                                      |    |

| Figure 8.6. ODDRX2E Symbol                                                     |    |

| Figure 8.9. ODDRY314 Symbol                                                    |    |

| Figure 8.8. ODDRX71A Symbol                                                    |    |

| Figure 8.9. DQSDLLC Symbol                                                     | 56 |

| Figure 8.10. DELAYE Symbol                                                               | 57 |

|------------------------------------------------------------------------------------------|----|

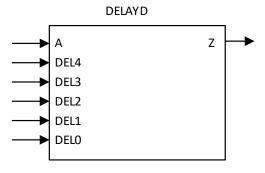

| Figure 8.11. DELAYD Symbol                                                               |    |

| Figure 8.12. DLLDELC Symbol                                                              |    |

|                                                                                          |    |

|                                                                                          |    |

| Tables                                                                                   |    |

|                                                                                          |    |

| Table 2.1. Gearing Logic Distribution for MachXO3D Devices                               |    |

| Table 5.1. Generic High-Speed I/O DDR Interfaces <sup>1</sup>                            | 19 |

| Table 6.1. Signal Names Used by IPexpress Modules                                        | 35 |

| Table 6.2. GUI Options for the SDR Interfaces                                            | 37 |

| Table 6.3. GUI Option for the Pre-Configuration Tab of DDR_Generic Modules               | 39 |

| Table 6.4. GUI Options of the Configuration Tab of the DDR_Generic Modules               | 40 |

| Table 6.5. Gearing Ratio Selection by the Software for MachXO3D Device                   | 41 |

| Table 6.6. GUI Options of the Configuration Tab for GDDR_71                              | 43 |

| Table 7.1. Gearing Logic Supported by Mixed Mode of I/O Logic Cells for MachXO3D Devices | 44 |

| Table 8.1. MachXO3D DDR Software Primitives                                              | 51 |

| Table 8.2. DQSDLLC Signals                                                               | 56 |

| Table 8.3. Attribute for DQSDLLC                                                         |    |

| Table 8.4. DELAYE Signals                                                                | 57 |

| Table 8.5. DELAYE attributes                                                             |    |

| Table 8.6. DEL_MODE Values Corresponding to the GDDR Interface                           |    |

| Table 8.7. DELAYD Signals                                                                |    |

| Table 8.8. DLLDELC Signals                                                               |    |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                |  |

|---------|---------------------------|--|

| DDR     | Double Data Rate          |  |

| ECLK    | Edge Clock                |  |

| GDDR    | Generic Double Data Rate  |  |

| PCLK    | Primary Clock             |  |

| PIO     | Programmable I/O          |  |

| PLD     | Programmable Logic Device |  |

| SCLK    | System Clock              |  |

| SDR     | Single Data Rate          |  |

## 1. Introduction

In response to the increasing need for higher data bandwidth, the industry has migrated from the traditional Single Data Rate (SDR) to the Double Data Rate (DDR) architecture. SDR uses either the rising edge or the falling edge of the clock signal to transfer data, while DDR uses both edges of the clock signal for data transfer. This essentially doubles the data transmission rate using the same clock frequency because the data is transferred twice per clock cycle. The Lattice MachXO3D PLD family supports high-speed interfaces for both DDR and SDR applications through built-in Programmable I/O (PIO) logic. This document focuses on the implementation of high-speed generic DDR interfaces in the MachXO3D devices. It also provides guidelines for making use of the built-in capabilities of the MachXO3D devices to achieve the best performance for high-speed interfaces.

# 2. Architecture for High-Speed Interfaces

## 2.1. Gearing Logic Distribution

The high-speed generic DDR (GDDR) interfaces are supported through the built-in gearing logic in the Programmable I/O (PIO) cells. This gearing is necessary to support high-speed I/O while reducing the performance requirement on the FPGA fabric.

There are four gearing ratio settings available in the MachXO3D devices depending on the I/O bank locations and the logic density. The ×1 gearing ratio is available in all banks for all the device densities. The ×2, ×4, and the 7:1 gearing ratio are available in the top and bottom banks of the MachXO3D devices. The 7:1 gearing ratio is mainly used for video display applications. The ×2/×4 gearing circuit is shared with the 7:1 circuit on both receive and the transmit sides. Table 2.1 gives a breakdown of gearing logic support in the different I/O banks. Details of PIO cells can be found in MachXO3D Family Data Sheet (FPGA-DS-02026).

Table 2.1. Gearing Logic Distribution for MachXO3D Devices

| Gearing Logic  | Definition | Gearing Ratio | Left | Right | Bottom | Тор |

|----------------|------------|---------------|------|-------|--------|-----|

| DDR ×1*        | GDDR       | 1:2 or 2:1    | Yes  | Yes   | Yes    | Yes |

| Input DDR ×2   | GDDR       | 1:4           | _    | _     | Yes    | _   |

| Input DDR ×4   | GDDR       | 1:8           | _    | _     | Yes    | _   |

| Input DDR 7:1  | GDDR       | 1:7           | _    | _     | Yes    | _   |

| Output DDR ×2  | GDDR       | 4:1           | _    | _     | _      | Yes |

| Output DDR ×4  | GDDR       | 8:1           | _    | _     | _      | Yes |

| Output DDR 7:1 | GDDR       | 7:1           | _    | _     | _      | Yes |

<sup>\*</sup>Note: DDR ×1 is available for all MachXO3D device densities.

## 2.2. Different Types of I/O Logic Cells

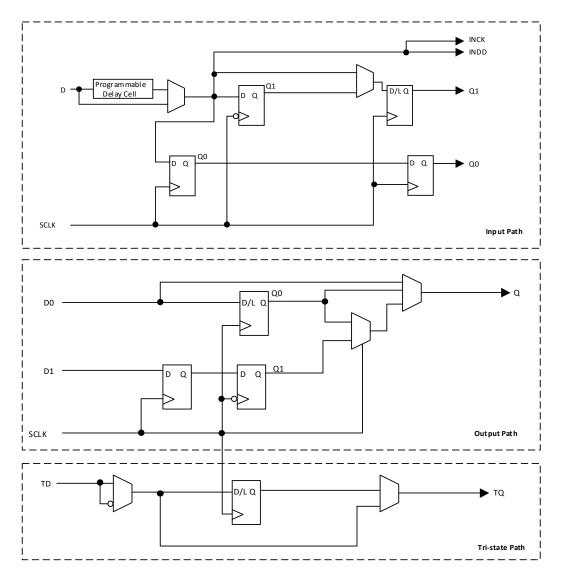

In order to support various gearing ratios, the MachXO3D devices support two types of PIO logic cells. These include a basic PIO cell and a video PIO cell. The basic PIO cell supports traditional SDR registers and DDR ×1 registers. It is available on all sides of all MachXO3D devices. The video PIO cell supports the ×2, ×4 (in MachXO3D devices) and 7:1 gearing applications. They are available on the bottom side for the receive interfaces, and on the top side for the transmit interfaces. The input and output structures of each type of PIO cell are discussed in detail in MachXO3D Family Data Sheet (FPGA-DS-02026). The block diagrams of the PIO cells are shown here again in this document for reference.

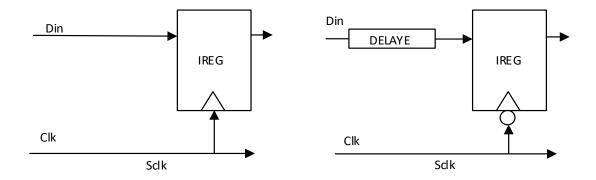

Figure 2.1. Basic PIO Cell Support ×1 Gearing Ratio

Figure 2.2. Video PIO Cell for ×2/×4 and 7:1 Applications in MachXO3D Devices

#### 2.3. Clock Domain Transfer at PIO Cells

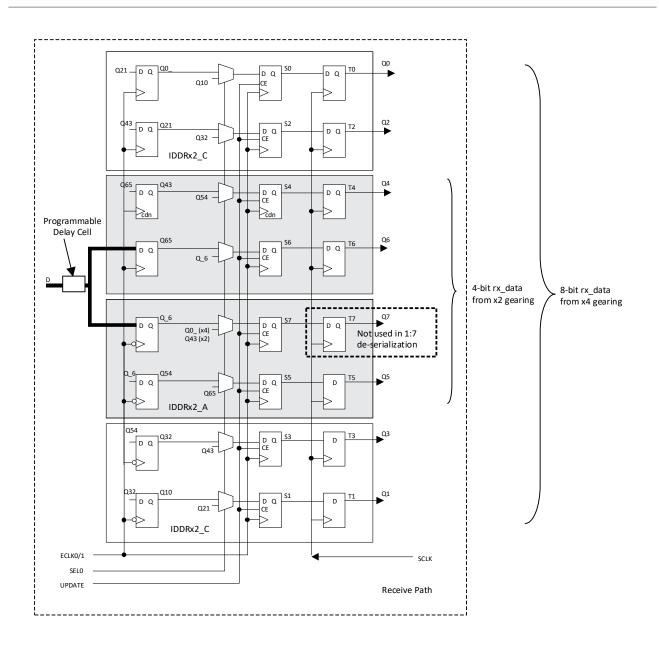

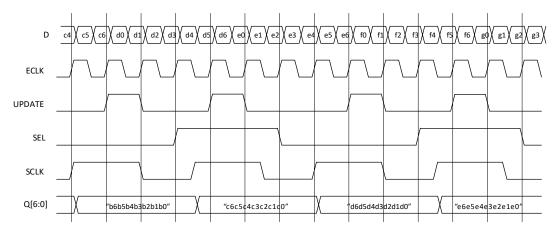

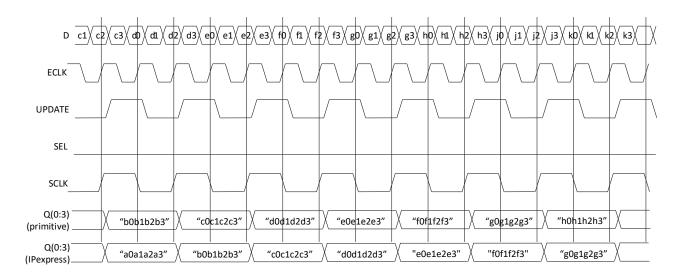

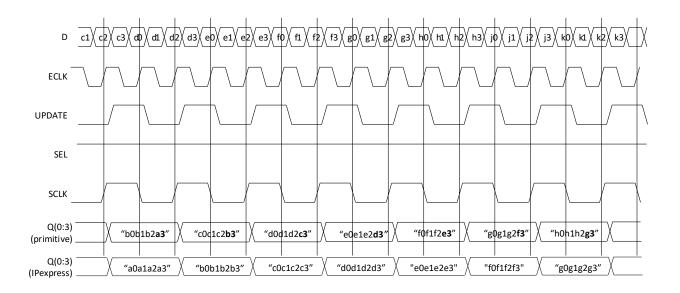

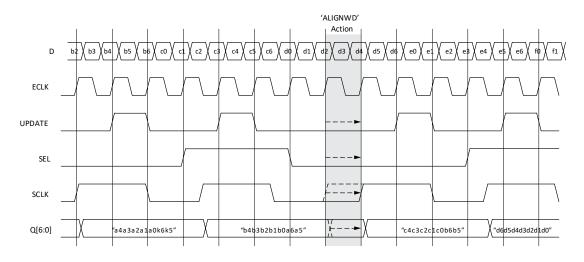

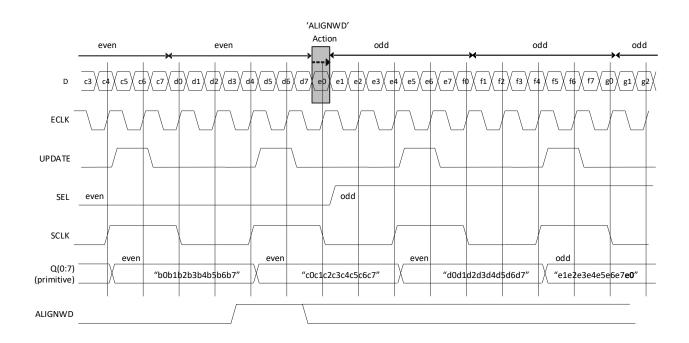

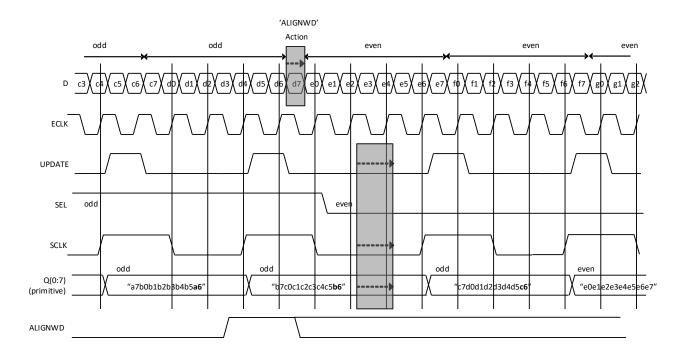

The MachXO3D gearing logic performs serializing and de-serializing of high-speed data in the PIO cells. The clock domain transfer for the data from the high-speed edge clock (ECLK) to the low-speed system clock (SCLK) is guaranteed by design through two internal signals, UPDATE and SEL. The SEL signal toggles between '0' and '1' to sample three bits or four bits of data at a time for the 7:1 gearing. It remains static during the ×2/×4 gearings. The UPDATE signal behaves the same for all the gearings to update the register with the correct byte of data. This data is then clocked by the SCLK for downstream processing. Figure 2.2 illustrates the architecture of ×2/×4 input gearing logic.

MachXO3D devices provide logic to support word alignment with minimal FPGA resources. The word alignment results in a shift to the UPDATE, SEL and the SCLK signals. It can be activated by providing an alignment request signal to the ALIGNWD port of the high-speed interface components. ALIGNWD can be asynchronous to the ECLK domain, but it must be at least two ECLK cycles wide. For the 7:1 gearing, ALIGNWD must be pulsed seven times to loop through a maximum of seven combinations of word orders. For the ×2/×4 gearings, ALIGNWD must be pulsed eight times to step through maximum eight possible word orders.

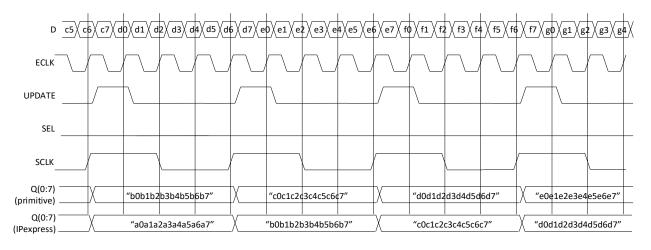

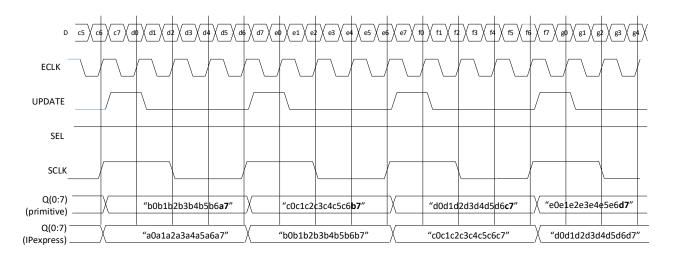

The MachXO3D PIO receive deserializer primitives contains a fundamental logic error for ×2 and ×4 applications. 'Odd' word alignments (SEL = '1') do not present the correct data at the 'Q3' output port (×2), or Q7 output port (×4). The timing diagrams below correctly show the actual behavior of the output port, with the actual output data bit highlighted in BOLD. You must be aware of this behavior if instantiating the primitive directly into his design, and take appropriate steps to correct the temporal misalignment. Note the 7:1 gearing primitives not impacted by this issue.

In Diamond 3.12 and later versions, the temporal misalignment mentioned above is corrected when using the Generic IDDRX4 and IDDRX2 logic interfaces (GDDRX2/X4\_RX.ECLK.Centered/Aligned) generated with the Lattice IPexpress tool. These are described in the Generic High-Speed DDR Interfaces section. As a result of the fix, the Q bus output is delayed by one SCLK cycle with respect to the primitive output, and with respect to previous versions of the GDDRX2/X4\_RX~ interfaces. In most applications, the additional delay is negligible.

Figure 2.3 through Figure 2.7 provide a timing relationship of UPDATE, SEL, ECLK, and SCLK signals under different gearing requirements. Figure 2.8 through Figure 2.10 show the word alignment procedure for various gearing ratios. The discussion of gearing logic is applicable to both receive and transmit sides of the high-speed interfaces.

Figure 2.3. 7:1 Deserializer Timing in MachXO3D Device

Figure 2.4. ×4 Deserializer Timing (Even Phases, SEL=0)

© 2019-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2.5. ×4 Deserializer Timing (Odd Phases, SEL=1)

Figure 2.6. ×2 Deserializer Timing (Even Phases, SEL=0)

Figure 2.7. ×2 Deserializer Timing (Odd Phases, SEL=1)

Figure 2.8. 7:1 Deserializer Timing in Response to ALIGNWD in MachXO3D Device

Figure 2.9. ×4 Deserializer Timing in Response to ALIGNWD (Even-to-Odd Phase)

Figure 2.10. ×4 Deserializer Timing in Response to ALIGNWD (Odd-to-Even Phase)

# 3. External High-Speed Interface Description

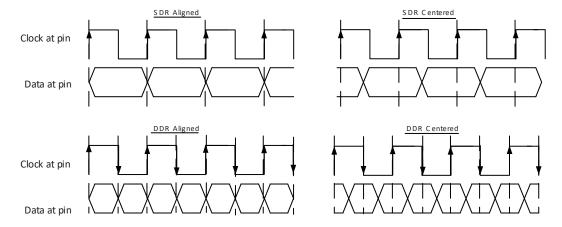

There are two types of external high-speed interface definitions that can be used with the MachXO3D devices: centered and aligned. In a centered external interface, at the device pins, the clock is centered in the data opening. In an aligned external interface, the clock and data transition are aligned at the device pins. This is sometimes called "edge-on-edge". Figure 3.1 shows external interface waveforms for SDR and DDR. At the receive side, an aligned interface requires clock delay adjustment to position the clock edge at the middle of the data opening to ensure that the capture flip-flop setup and hold times are not violated. Similarly a centered interface at the transmit side will require a clock delay adjustment to position the clock at the center of the data opening for transmission.

Figure 3.1. External Interface Definition

# 4. High-Speed Interface Building Blocks

MachXO3D devices provide dedicated logic blocks for building high-speed interfaces, with each block performing a unique function. Combining various blocks gives ultimate performance of a specific interface. The hardware components in the device are described in this section. The DDR Software Primitives and Attributes section describes the library elements for these components. Refer to MachXO3D sysCLOCK PLL Usage Guide (FPGA-TN-02070) for an indepth discussion of clocking and PLL architectures.

#### 4.1. ECLK

Edge clocks are high-speed, low-skew I/O dedicated clocks. Two edge clocks (ECLK) are available on each of the top and bottom sides. The primary clock nets (PCLK) have direct connectivity to ECLKs. The bottom PCLK pins also have minimal routing to PLLs for video applications.

#### 4.2. ECLKSYNC

This is the ECLK synchronization block. Each ECLK has its own ECLKCYNC component to synchronize the clock domain transfer of data. This block can also be used to dynamically disable an edge clock to save power during operation.

#### 4.3. SCLK

SCLK refers to the system clock of the design. SCLK must use primary clock (PCLK) pins or primary clock (PCLK) nets for high speed interfaces. There are eight PCLK pins available for the MachXO3D device, and eight PCLK nets in the MachXO3D devices.

#### 4.4. CLKDIV

Clock dividers are used to generate low-speed system clocks from a high-speed edge clock. The ECLK frequency can be divided down by 2, by 3.5, or by 4 through the CLKDIV component.

#### 4.5. PLL

A maximum of two PLLs are available in the MachXO3D devices. There are pre-assigned dual-purpose I/O pins that drive to PLLs as reference clock inputs.

#### 4.6. DQSDLL

A maximum of two DQSDLLs are available. The top-right DQSDLL controls the top and right banks. The bottom-left DQSDLL can be used by the bottom and left banks. The DQSDLL, together with the clock slave delay cell (DLLDEL), is used to create a 90° clock shift/delay for aligned receiver interfaces.

## 4.7. Input DDR (IDDR)

Generic input DDR components support  $\times 1$ ,  $\times 2$ ,  $\times 4$ , and 7:1 gearing ratios at the receiving side of the PIO cells.

The ×1 gearing is supported by IDDRX, or the basic PIO cell. It receives 1-bit DDR data and outputs 2-bit wide parallel data synchronized to the SCLK. There is no clock domain transfer involved in the ×1 gearing. The ×2 gearing is supported by IDDRX2. It receives 1-bit DDR data synchronized to the ECLK and outputs four bits of parallel data synchronized to the SCLK. The same function applies to the IDDRX4, which receives a single bit of DDR data synchronized to the ECLK and outputs eight bits of parallel data synchronized to the SCLK. The 7:1 gearing shares the

same structure as the ×4 gearing. The 7:1 gearing outputs seven bits of parallel data instead of eight. The generic high-speed interface gearings are supported by the video PIO cells.

## 4.8. Output DDR (ODDR)

Generic output DDR components support ×1, ×2, ×4, and 7:1 gearing ratios at the transmit side of the PIO cells.

The ×1 gearing is supported by ODDRX, or the basic PIO cell. It serializes the 2-bit data based on SCLK. There is no clock domain transfer involved in ×1 gearing. The ×2 gearing is supported by ODDRX2. The 4-bit parallel data is clocked by SCLK and is serialized using ECLK. The ×4 gearing is supported by ODDRX4. The 8-bit parallel data is clocked by SCLK and is serialized using ECLK. The 7:1 gearing shares the same structure as the ×4 gearing. The 7-bit parallel data is serialized by the ECLK. The generic high speed interface gearings are supported by the video PIO cells.

## 4.9. Delays

There are two types of delay available for high-speed interfaces. The first type is the I/O logic delay that can be applied on the input data paths, as shown in the block diagram of PIO architectures at the beginning of the document.

Although the 32-tap I/O logic delay can be static or dynamic, only the bottom side of the MachXO3D device supports dynamic data path delay. The static I/O logic delay (DELAYE) is used by default when configuring the interface in the Lattice design software. Software applies fixed delay values based on the interface used. Dynamic delay (DELAYD) at the bottom-side input data path provides dynamic or user-defined delay. Dynamic delay requires extra ports available on the module to be connected to user logic for delay control. The I/O logic delay is used to achieve the SDR zero hold timing, or match primary clock injection for ×1 gearing, or match the edge clock injection for ×2/×4 gearings.

The second type of delay is the clock slave delay cell (DLLDEL), which delays the incoming clock by 90° to place the clock in the middle of the data opening. This block is digitally controlled by the DQSDLL through 7-bit control code. There is one clock slave delay cell per primary clock pin. Its input comes from the primary clock pins and its output can drive the primary clock net for the ×1 aligned interface or ECLK for ×2/×4 aligned interfaces.

# 5. Generic High-Speed DDR Interfaces

Generic high-speed interfaces, or Generic DDR (GDDR), are supported in MachXO3D devices using the dedicated logic blocks. This section will discuss the GDDR types, the interface logic, and the software to support the GDDR capability in the silicon.

## 5.1. High-Speed GDDR Interface Types

The GDDR interfaces supported by the MachXO3D device family are pre-defined in the software and characterized in the silicon. Table 5.1 lists all the supported interfaces and gives a brief description of each interface.

Table 5.1. Generic High-Speed I/O DDR Interfaces<sup>1</sup>

| Mode               | Interface Name          | Description                                                             | Supporting Device & Sides |

|--------------------|-------------------------|-------------------------------------------------------------------------|---------------------------|

| RX SDR             | GIREG_RX.SCLK           | SDR input using SCLK                                                    | All sides                 |

| RX GDDRx1 Aligned  | GDDRX1_RX.SCLK.Aligned  | DDRx1 input using SCLK, data is edge-to-<br>edge with incoming clock    | All sides                 |

| RX GDDRx1 Centered | GDDRX1_RX.SCLK.Centered | DDRx1 input using SCLK, incoming clock is centered at the data opening  | All sides                 |

| RX GDDRx2 Aligned  | GDDRX2_RX.ECLK.Aligned  | DDRx2 input using ECLK, data is edge-to-<br>edge with incoming clock    | Bottom                    |

| RX GDDRx2 Centered | GDDRX2_RX.ECLK.Centered | DDRx2 input using ECLK, incoming clock is centered at the data opening  | Bottom                    |

| RX GDDRx4 Aligned  | GDDRX4_RX.ECLK.Aligned  | DDRx4 input using ECLK, data is edge-to-<br>edge with incoming clock    | Bottom                    |

| RX GDDRx4 Centered | GDDRX4_RX.ECLK.Centered | DDRx4 input using ECLK, incoming clock is centered at the data opening  | Bottom                    |

| RX GDDR71          | GDDR71_RX.ECLK.7:1      | GDDR 7:1 input using ECLK                                               | Bottom                    |

| TX SDR             | GOREG_TX.SCLK           | SDR output using SCLK                                                   | All sides                 |

| TX GDDRx1 Aligned  | GDDRX1_TX.SCLK.Aligned  | DDRx1 output using SCLK, data is edge-to-<br>edge with outgoing clock   | All sides                 |

| TX GDDRx1 Centered | GDDRX1_TX.SCLK.Centered | DDRx1 output using SCLK, outgoing clock is centered at the data opening | All sides                 |

| TX GDDRx2 Aligned  | GDDRX2_TX.ECLK.Aligned  | DDRx2 output using ECLK, data is edge-to-<br>edge with outgoing clock   | Тор                       |

| TX GDDRx2 Centered | GDDRX2_TX.ECLK.Centered | DDRx2 output using ECLK, outgoing clock is centered at the data opening | Тор                       |

| TX GDDRx4 Aligned  | GDDRX4_TX.ECLK.Aligned  | DDRx4 output using ECLK, data is edge-to-<br>edge with outgoing clock   | Тор                       |

| TX GDDRx4 Centered | GDDRX4_TX.ECLK.Centered | DDRx4 output using ECLK, outgoing clock is centered at the data opening | Тор                       |

| TX GDDR71          | GDDR71_TX.ECLK.7:1      | GDDR 7:1 output using ECLK                                              | Тор                       |

**Note**: MIPI D-PHY Receive can be built using GDDRX4\_RX.ECLK.Centered interface & MIPI D-PHY Transmit can be built using GDDRX4\_TX.ECLK.Centered interface. Refer to MIPI D-PHY Interface IP (FPGA-RD-02040) for details.

The following describes the naming conventions used for each of the interfaces listed in Table 5.1.

- G Generic

- IREG SDR input I/O register

- OREG SDR output I/O register

- DDRX1 DDR ×1 I/O register

- DDRX2 DDR ×2 I/O register

- DDRX4 DDR ×4 I/O register

- DDR71 DDR 7:1 I/I register

- RX Receive interface

- TX Transmit interface

- ECLK Uses ECLK (edge clock) clocking resource at the GDDR interface

- SCLK Uses SCLK (primary clock) clocking resource at the GDDR interface

- Centered Clock is centered to the data when coming into the device

- Aligned Clock is aligned edge-on-edge to the data when coming into the device

## 5.2. High-Speed GDDR Interface Details

This section describes each of the generic high-speed interfaces in detail including the clocking to be used for each interface. For detailed information about the MachXO3D clocking structure, refer to MachXO3D sysCLOCK PLL Usage Guide (FPGA-TN-02070). As listed in Table 5.1, each interface is supported in specific bank locations of the MachXO3D devices. It is important to follow the architecture and various interface rules and preferences listed under each interface in order to build these interfaces successfully. The discussion of each component can be found in the DDR Software Primitives and Attributes section of this document.

#### 5.2.1. Receive Interfaces

There are eight receive interfaces pre-defined and supported through Lattice IPexpress™ software.

#### GIREG\_RX.SCLK

This is a generic interface for single data rate (SDR) data. The standard I/O register in the basic PIO cell (Figure 2.1) is used for the implementation. An optional inverter can be used to center the clock for aligned inputs. PLLs or DLLs can be used to remove the clock injection delay or adjust the setup and hold times. There are a limited number of DLLs in the architecture and these should be saved for high-speed interfaces when necessary. This interface can either be built using IPexpress, instantiating an I/O register element, or inferred during synthesis.

Figure 5.1. GIREG\_RX Interface

The input data path delay cells can be used on the Din path of the interface. A DELAYE element provides a fixed delay to match the SCLK injection time. The dynamic input delay, DELAYD, is not available for this interface. Figure 5.1 shows possible implementations of this interface.

Interface rule:

A dedicated clock pin PCLK must be used as the clock source.

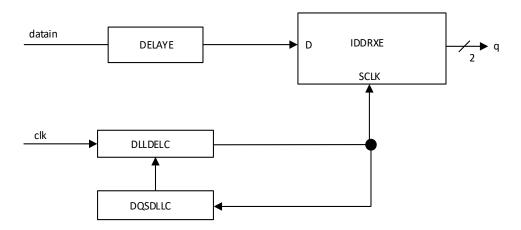

#### GDDRX1\_RX.SCLK.Aligned

This DDR interface uses the SCLK and the DQSDLL to provide a 90° clock shift to center the clock at the IDDRXE. A DELAYE element is used to adjust data delay for the SCLK clock injection time. The DELAYD is not available for the ×1 interface.

Figure 5.2. GDDRX1\_RX.SCLK.Aligned Interface Using DQSDLL

#### Interface rules:

- A dedicated clock pin PCLK must be used as the clock source for DLLDELC.

- A primary clock net must be used to connect DLL outputs to the SCLK port.

- The DELAYE value should be set to SCLK\_ALIGNED for the best timing.

- There are up to two DQSDLLCs per device. This limits the interface to a maximum of two clock frequencies per device.

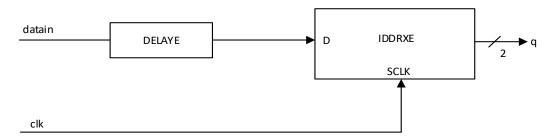

#### GDDRX1\_RX.SCLK.Centered

This DDR interface uses DELAYE to match the SCLK delay at the IDDRXE. DELAYD is not available for the ×1 interface. Since it is a centered interface, the clock edge is already in the middle of the data opening. There is no logic required to shift the clock.

Figure 5.3. GDDRX1\_RX.SCLK.Centered

#### Interface rules:

- A dedicated clock pin PCLK must be used as the clock source.

- DELAYE value should be set to SCLK\_CENTERED for the best timing.

- The clock connected to SCLK should be on a primary clock net.

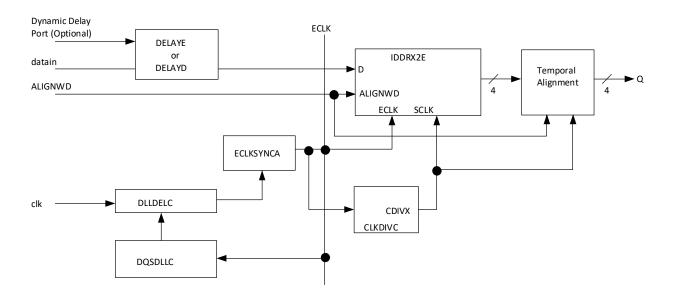

#### GDDRX2\_RX.ECLK.Aligned

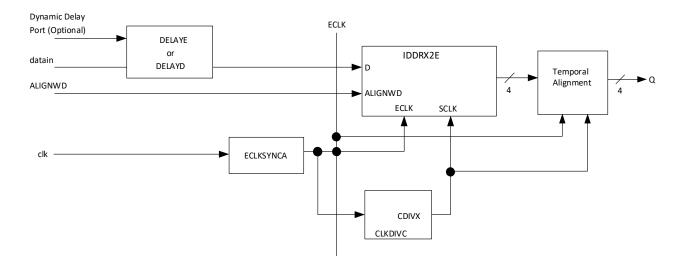

This DDR ×2 interface uses the DQSDLL to provide a 90° clock shift to center the clock at the IDDRX2E buffer. DELAYE is used to delay data to match the ECLK injection delay. DELAYD can also be used to control the delay dynamically. This interface uses ×2 gearing with the IDDRX2E element. This requires the use of a CLKDIVC to provide the SCLK which is half the frequency of the ECLK. The ECLKSYNCA element is associated with the ECLK and must be used to drive the ECLK. The port ALIGNWD can be used for word alignment at the interface. The Temporal Alignment block (generated in Diamond versions 3.12 and later) introduces a one SCLK period delay and corrects for the temporal misalignment of IDDRX2E Q3 data output.

Figure 5.4. GDDRX2\_RX.ECLK.Aligned Interface

#### Interface rules:

- A dedicated clock pin PCLK must be used as the clock source for DLLDELC.

- Clock net routed to SCLK must use primary clock net.

- There are up to two DQSDLLCs per device. It limits this interface to a maximum of two clock frequencies per device.

- DELAYE should be set to ECLK\_ALIGNED.

- When DELAYD is used, only one dynamic delay port is needed for the entire bus.

- This interface is supported at the bottom side of the devices.

#### GDDRX2\_RX.ECLK.Centered

This DDR ×2 interface uses DELAYE or DELAYD to match edge clock delay at the IDDRX2E. Since this interface uses the ECLK, it can be extended to support large data bus sizes for the entire side of the device. This interface uses ×2 gearing with the IDDRX2D element. This requires the use of a CLKDIVC to provide the SCLK which is half the frequency of the ECLK. The port ALIGNWD can be used for word alignment at the interface. The Temporal Alignment block (generated in Diamond versions 3.12 and later) introduces a one SCLK period delay and corrects for the temporal misalignment of IDDRX2E Q3 data output.

© 2019-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 5.5. GDDRX2\_RX.ECLK.Centered Interface

#### Interface rules:

- A dedicated clock pin PCLK must be used as the clock source for ECLKSYNCA.

- Clock net routed to SCLK must use primary clock net.

- DELAYE should be set to ECLK CENTERED.

- When DELAYD is used, only one dynamic delay port is needed for the entire bus.

- This interface is supported at the bottom side of the devices.

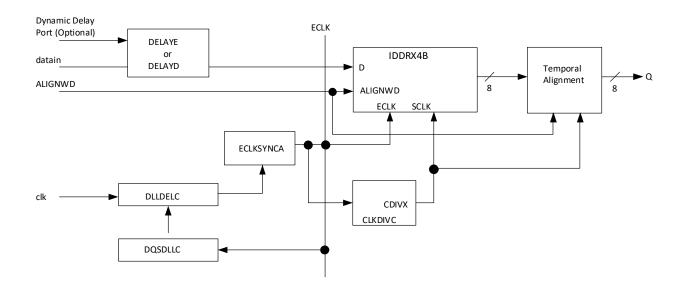

#### GDDRX4\_RX.ECLK.Aligned

This DDR ×4 interface uses the DQSDLL to provide a 90° clock shift to center the edge clock at the IDDRX4B buffer. DELAYE is used to delay data to match the ECLK injection delay. DELAYD can also be used to control the delay dynamically. Since this interface uses the ECLK, it can be extended to support large data bus sizes for the entire side of the device. This interface uses ×4 gearing with the IDDRX4B element. This requires the use of a CLKDIVC to provide the SCLK which is one quarter of the ECLK frequency. ECLKSYNCA element is associated with the ECLK and must be used to drive the ECLK. The port ALIGNWD can be used for word alignment at the interface. The Temporal Alignment block (generated in Diamond versions 3.12 and later) introduces a one SCLK period delay and corrects for the temporal misalignment of IDDRX4B Q7 data output.

Figure 5.6. GDDRX4\_RX.ECLK.Aligned Interface

#### Interface rules:

- A dedicated clock pin PCLK must be used as the clock source for DLLDELC.

- Clock net routed to SCLK must use primary clock net

- There are up to two DQSDLLCs per device. It limits this interface to have maximum of two clock frequencies per device.

- Data input must use A/B pair of the I/O logic cells for ×4 gearing.

- DELAYE should be set to ECLK\_ALIGNED

- When DELAYD is used, only one dynamic delay port is needed for the entire bus.

- This interface is supported at the bottom side of the MachXO3D-2100 and higher density devices.

**Note**: The GDDRX4\_RX.ECLK.Centered interface is used to build MIPI D-PHY Receive Interface. Refer to MIPI D-PHY Interface IP (FPGA-RD-02040) for details.

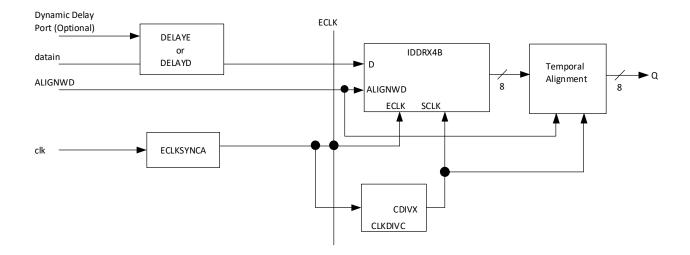

#### GDDRX4\_RX.ECLK.Centered

This DDR ×4 interface uses DELAYE or DELAYD to match edge clock delay at the IDDRX4B. Since this interface uses the ECLK it can be extended to support large data bus sizes for the entire side of the device. This interface uses ×4 gearing with the IDDRX4B element. This requires the use of a CLKDIVC to provide the SCLK that is one quarter of the ECLK frequency. The port ALIGNWD can be used for word alignment at the interface. The Temporal Alignment block (generated in Diamond versions 3.12 and later) introduces a one SCLK period delay and corrects for the temporal misalignment of IDDRX4B Q7 data output.

Figure 5.7. GDDRX4\_RX.ECLK.Centered Interface

#### Interface rules:

- A dedicated clock pin PCLK must be used as the clock source for ECLKSYNCA.

- Clock net routed to SCLK must use primary clock net.

- Data input must use A/B pair of the I/O logic for ×4 gearing.

- DELAYE should be set to ECLK\_CENTERED.

- When DELAYD is used, one dynamic delay port is needed for the entire bus.

- This interface is supported at the bottom side of the devices.

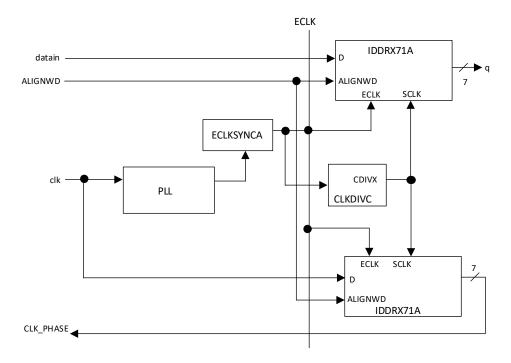

#### GDDR71\_RX.ECLK.7:1

The GDDR 7:1 receive interface is unique among the supported high-speed DDR interfaces. It uses the PLL to search the best clock edge to the data opening position during bit alignment process. The PLL steps through the 16 phases to give eight sampling points per data. The data path delay is not used in this interface. CLKDIVC is used to divide down the ECLK by 3.5 due to the nature of the 1:7 deserializing requirement. This means the SCLK is running seven times slower than the incoming data rate. ECLKSYNCA element is associated with the ECLK and must be used to drive the ECLK. The complete 7:1 LVDS video display application requires bit alignment and word alignment blocks to be built in the FPGA resources in addition to the built-in I/O gearing logic and alignment logic. The CLK\_PHASE signal is sent to the FPGA side to build the bit alignment logic.

Figure 5.8. GDDR71\_RX.ECLK.7:1 Interface

#### Interface rules:

- A dedicated clock pin PCLK at the bottom side must be used as the clock source for PLL.

- Clock net routed to SCLK must use primary clock net.

- There are up to two PLLs per device. It limits this interface to have maximum of two clock frequencies per device.

- The data input must use A/B pair of the I/O logic cell for 7:1 gearing.

- This interface is supported at the bottom side of the devices.

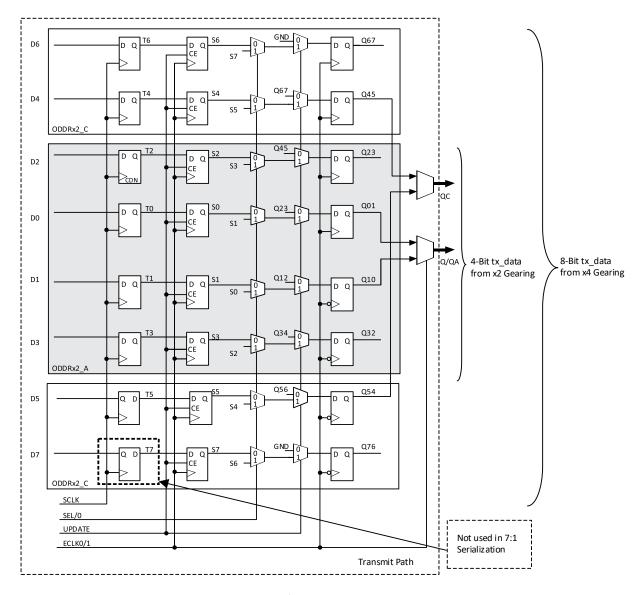

#### 5.2.2. Transmit Interfaces

There are eight transmit interfaces pre-defined and supported through Lattice IPexpress software.

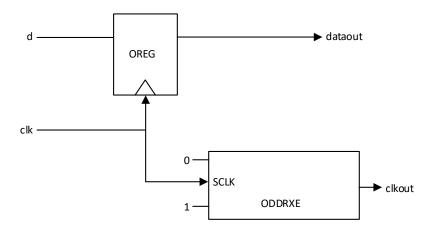

#### GOREG\_TX.SCLK

This is a generic interface for SDR data and a forwarded clock. The standard register in the basic PIO cell is used to implement this interface. The ODDRXE used for the output clock balances the clock path to match the data path. A PLL can also be used to clock the ODDRXE to phase shift the clock to provide a precise clock to data output. There are a limited number of PLLs in the architecture and these should be saved for high-speed interfaces when necessary. This interface can either be built using IPexpress, instantiating an I/O register element, or inferred during synthesis.

Figure 5.9. GOREG\_TX.SCLK Interface

#### Interface rule:

The clock source for SCLK must be routed on a primary clock net.

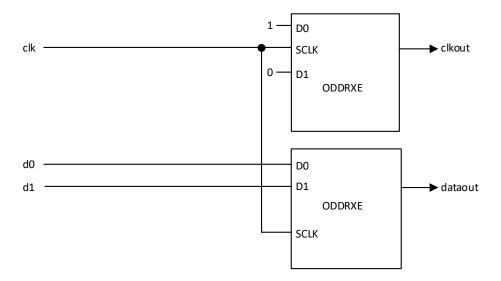

#### GDDRX1\_TX.SCLK.Aligned

This output DDR interface provides clock and data that are aligned using a single SCLK. The ODDRXE used for the output clock balances the clock path to match the data path.

Figure 5.10. GDDRX1\_TX.SCLK.Aligned Interface

#### Interface rule:

The clock source for SCLK must be routed on a primary clock net.

#### GDDRX1\_TX.SCLK.Centered

This output DDR interface provides clock and data that are pre-centered. PLL uses clkop and clkos ports to provide the 90° phase difference between the data and the clock. It requires two SCLK resources to drive the output data I/O cell and the output clock I/O cell.

Figure 5.11. GDDRX1\_TX.SCLK.Centered Interface

Interface rule:

SCLK and 90°-shifted SCLK must be routed on primary clock nets.

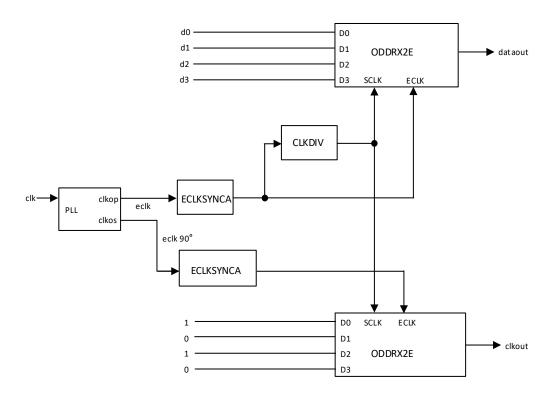

#### GDDRX2\_TX.ECLK.Aligned

This output DDR ×2 interface provides clock and data that are aligned. A CLKDIV is used to generate the SCLK which is half of the ECLK frequency. The ECLKSYNC element is used on the ECLK path for data synchronization.

Figure 5.12. GDDRX2\_TX.ECLK.Aligned Interface

#### Interface rules:

- Edge clock routing resources must be used for the ECLK.

- The routing of SCLK must use primary clock net.

- This interface is supported at the top side of the MachXO3D-2100 and higher density devices.

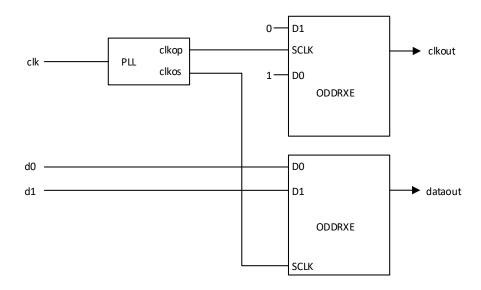

#### GDDRX2\_TX.ECLK.Centered

This output DDR ×2 interface provides a clock that is centered at the data opening. The PLL uses clkop and clkos ports to provide the 90° phase difference between the data and the clock. Two ECLK routing resources are used in this interface to drive the output data and the output clock. A CLKDIV is used to generate the SCLK which is half of the ECLK frequency.

Figure 5.13. GDDRX2\_TX.ECLK.Centered Interface

#### Interface rules:

- Edge clock routing resources must be used for the ECLK.

- Since two ECLKs are used on this interface, maximum one bus of this interface can be implemented at a time.

- The routing of the SCLK must use primary clock net.

- This interface is supported at the top side of the device.

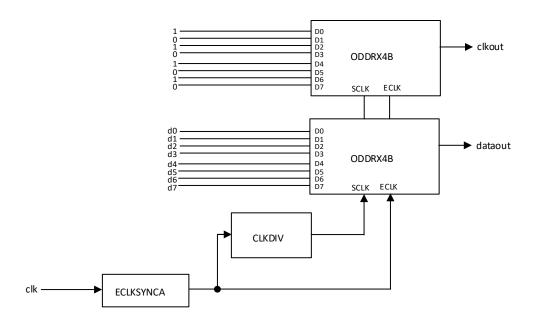

#### GDDRX4\_TX.ECLK.Aligned

This output DDR ×4 interface provides clock and data that are aligned. A CLKDIV is used to generate the SCLK which is a quarter of the ECLK frequency. The ECLKSYNC element is used on the ECLK path for data synchronization.

Figure 5.14. GDDRX4\_TX.ECLK.Aligned Interface

#### Interface rules:

- Edge clock routing resources must be used for the ECLK.

- The routing of SCLK must use primary clock net.

- Data output must use A/B pair of the I/O logic for ×4 gearing.

- This interface is supported at the top side of the device.

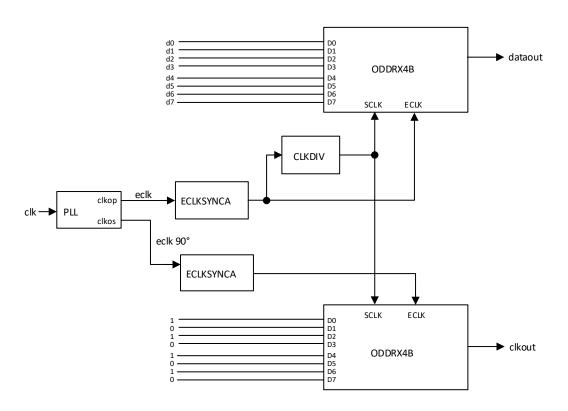

#### GDDRX4\_TX.ECLK.Centered

This output DDR ×4 interface provides a clock that is centered at the data opening. The PLL uses clkop and clkos ports to provide the 90° phase difference between the data and the clock. Two ECLK routing resources are used in this interface to drive the output data and the output clock. A CLKDIV is used to generate the SCLK which is one-quarter of the ECLK frequency.

Figure 5.15. GDDRX4\_TX.ECLK.Centered Interface

#### Interface rules:

- Edge clock routing resources must be used for the ECLK.

- Since two ECLKs are used on this interface, a maximum of one bus of this interface can be implemented at a time.

- The routing of the SCLK must use primary clock net.

- Data output must use A/B pair of the I/O logic for ×4 gearing.

- This interface is supported at the top side of the device.

**Note:** The GDDRX4\_TX.ECLK.Centered interface is used to build MIPI D-PHY Transmit Interface. Refer to MIPI D-PHY Interface IP (FPGA-RD-02040) for details.

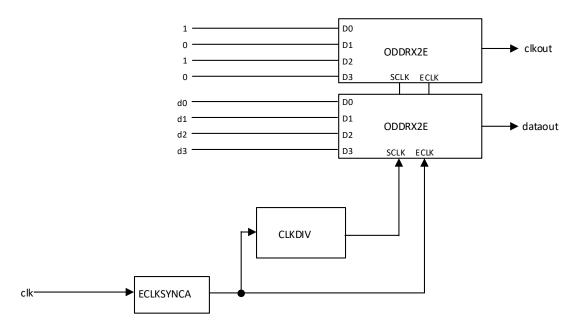

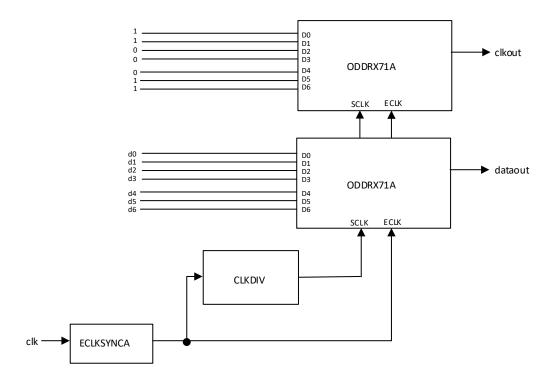

#### GDDR71\_TX.ECLK.7:1

The GDDR 7:1 transmit interface is unique among the supported high-speed DDR interfaces. It uses a specific pattern to generate the output clock, known as pixel clock. The CLKDIVC is used to divide down the ECLK by 3.5 due to the nature of the 7:1 serializing requirement. This means the SCLK is running seven times slower than the transmit data rate. ECLKSYNCA element is associated with the ECLK and must be used to drive the ECLK.

Figure 5.16. GDDR71\_TX.ECLK.7:1 Interface

#### Interface rules:

- Edge clock routing resources must be used for the ECLK.

- The routing of SCLK must use primary clock net.

- Data output must use A/B pair of the I/O logic for 7:1 gearing.

- This interface is supported at the top side of the device.

# 6. Using IPexpress to Build Generic High-Speed DDR Interfaces

The IPexpress tool of the Lattice development software should be used to configure and generate all the generic high-speed interfaces described above. IPexpress will generate a complete HDL module including clocking requirements for each of the interfaces described above. In the IPexpress GUI, all the DDR modules are located under **Architecture Modules > IO**. This section covers the SDR, DDR\_GENERIC, and GDDR\_71 interfaces in IPexpress.

Table 6.1 shows the signal names used in the IPexpress modules. Each signal can be used in all or some specified interfaces. The signals are listed separately for the GDDR receive interfaces and the transmit interfaces.

Table 6.1. Signal Names Used by IPexpress Modules

| Signal Name        | Direction | Description                                      | Supported Interfaces |

|--------------------|-----------|--------------------------------------------------|----------------------|

| Receive Interface  |           | ·                                                |                      |

| clk                | Input     | Source synchronous clock                         | All                  |

| reset              | Input     | Asynchronous reset to the interface, active high | All                  |

| datain             | Input     | Serial data input at Rx interfaces               | All                  |

| uddcntln           | Input     | Hold/update control of delay code, active low    | ×1, ×2, ×4 Aligned   |

| freeze             | Input     | Freeze or release DLL, active high               | ×1, ×2, ×4 Aligned   |

| alignwd            | Input     | Word alignment control signal, active high       | ×2, ×4, 7:1          |

| dqsdll_reset       | Input     | Asynchronous DQSDLL reset, active high           | ×2, ×4 Aligned       |

| clk_s*             | Input     | Slow clock for reset synchronization             | ×2, ×4, 7:1          |

| init               | Input     | Initialize reset synchronization, active high    | ×2, ×4, 7:1          |

| phase_dir          | Input     | PLL phase direction                              | 7:1                  |

| phase_step         | Input     | PLL phase step                                   | 7:1                  |

| sclk               | Output    | System clock for the FPGA fabric                 | All                  |

| q                  | Output    | Parallel data output of the Rx interfaces        | All                  |

| lock               | Output    | DLL or PLL lock                                  | ×2, ×4, 7:1          |

| eclk               | Output    | Edge clock generated from the input clock        | ×2, ×4 Aligned, 7:1  |

| rx_ready           | Output    | Indicate completion of reset synchronization     | ×2, ×4, 7:1          |

| clk_phase          | Output    | 7-bit representation of input clock phase        | 7:1                  |

| Transmit Interface |           | •                                                |                      |

| clk                | Input     | Main input clock for Tx interfaces               | All                  |

| reset              | Input     | Asynchronous reset to the interface, active high | All                  |

| dataout            | Input     | Parallel input data of the Tx interfaces         | All                  |

| clk_s*             | Input     | Slow clock for reset synchronization             | ×2, ×4, 7:1          |

| sclk               | Output    | System clock for the FPGA fabric                 | All                  |

| dout               | Output    | Serial data output for the Tx interfaces         | All                  |

| clkout             | Output    | Source synchronous clock                         | All                  |

| Tx_ready           | Output    | Indicate completion of reset synchronization     | ×2, ×4, 7:1          |

<sup>\*</sup>Note: clk\_s can be any slow clock to be used for reset synchronization process. This clock must be slower than eclk.

# 6.1. Building the SDR Interface

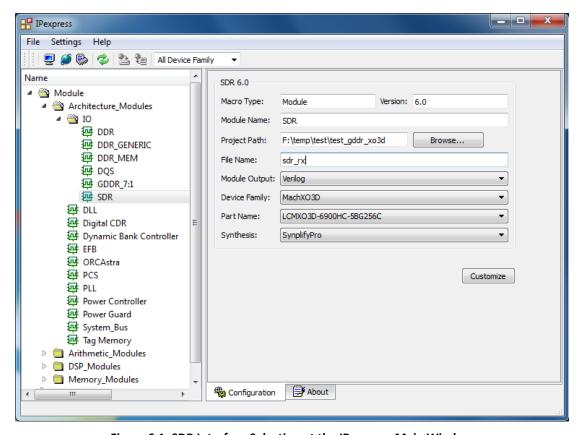

As shown in Figure 6.1, you can choose interface type SDR, enter the module name and click **Customize** to open the Configuration tab. Note that ×4 gearing is only on the MachXO3D devices.

Figure 6.1. SDR Interface Selection at the IPexpress Main Window

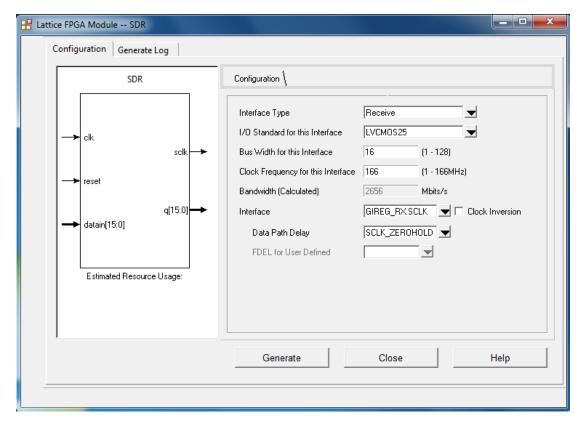

Figure 6.2 shows the Configuration tab for the SDR module in IPexpress. Table 6.2 lists the various configurations options available for SDR modules.

Figure 6.2. Configuration Tab for the SDR Interface

Table 6.2. GUI Options for the SDR Interfaces

| GUI Option                         | Description                                                                                      | Range                                                 | Default Value |

|------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|

| Interface Type                     | Types of interfaces                                                                              | Transmit, Receive                                     | Receive       |

| I/O Standard for this interface    | I/O standard to be used for the interface.                                                       | Supports all I/O types per selected<br>Interface Type | LVCMOS25      |

| Bus Width for this<br>Interface    | Bus size for the interface.                                                                      | 1-128                                                 | 16            |

| Clock Frequency for this Interface | Speed at which the interface will run                                                            | 1-166 MHz                                             | 166 MHz       |

| Interface Bandwidth (calculated)   | Calculated from the clock frequency entered.                                                     | (calculated)                                          | (calculated)  |

| Interface                          | Interface selected based on previous entries.                                                    | Transmit: GOREG_TX.SCLK Receive: GIREG_RX.SCLK        | GIREG_RX.SCLK |

| Clock Inversion                    | Option to invert the clock input to the I/O register.                                            | DISABLED, ENABLED                                     | DISABLED      |

| Data Path Delay                    | Data input can be optionally delayed using the DELAY block.                                      | Bypass, SCLK_ZEROHOLD, User Defined                   | Bypass        |

| FDEL for User Defined              | If Delay type selected above is "User Defined", delay values can be entered with this parameter. | Delay0 to Delay31                                     | Delay0        |

## 6.2. Building DDR Generic Interfaces

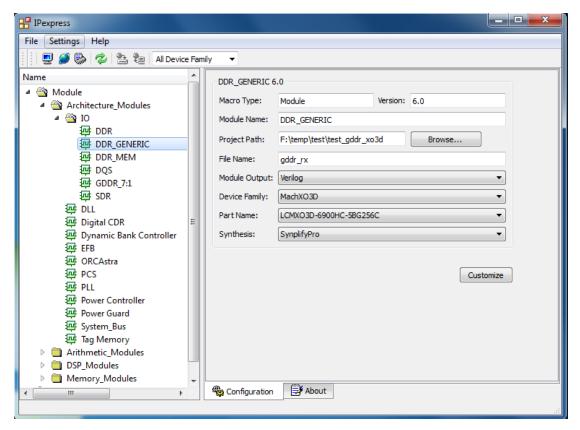

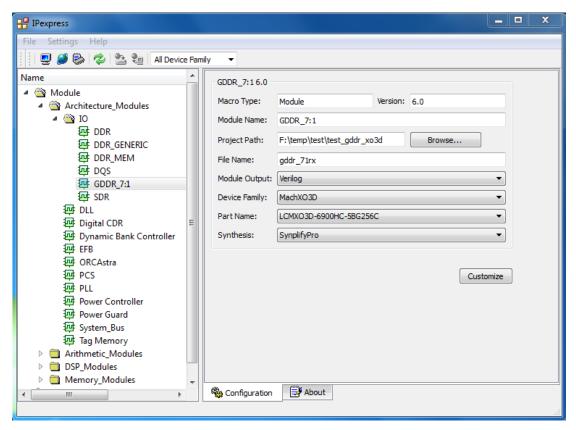

As shown in Figure 6.3, you can choose interface type DDR\_Generic, enter module name and click **Customize** to open the Configuration tab.

Figure 6.3. DDR\_Generic Interface Selection at the IPexpress Main Window

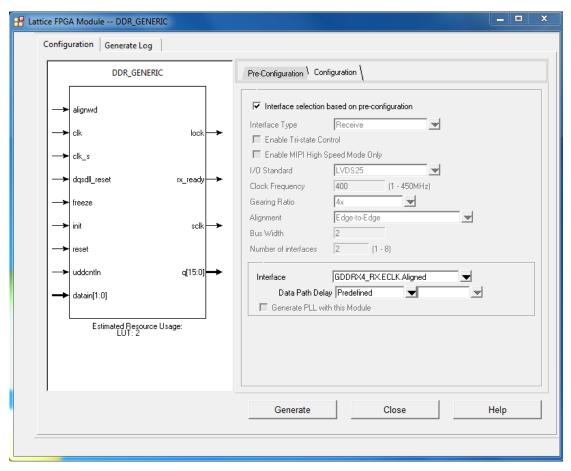

DDR\_Generic interfaces have a Pre-Configuration tab and a Configuration tab. The Pre-Configuration tab allows you to enter information about the type of interface to be built. Based on the entries in the Pre-Configuration tab, the Configuration tab is populated with the best interface selection. You can also, if necessary, override the selection made for the interface in the Configuration tab and customize the interface based on design requirements.

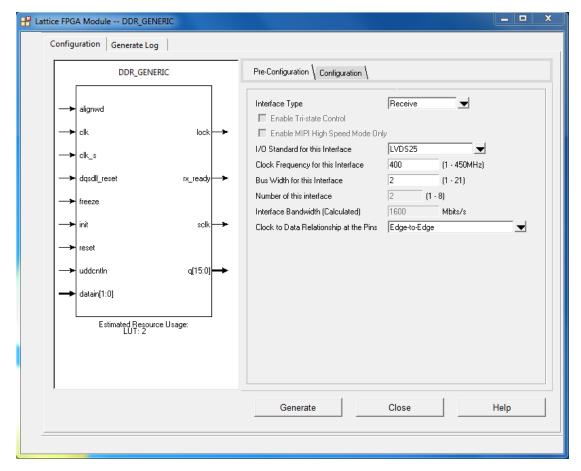

The following figures show the two tabs of the DDR\_Generic modules in IPexpress. Table 6.3 and Table 6.4 list the various configuration options available for DDR\_Generic modules.

Figure 6.4. Pre-Configuration Tab of the DDR\_Generic Interfaces

Table 6.3. GUI Option for the Pre-Configuration Tab of DDR\_Generic Modules

| GUI Option                                             | Description                                       | Range                                              | Default Value |

|--------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|---------------|

| Interface Type                                         | Types of interfaces                               | Transmit, Receive, Transmit_MIPI, Receive_MIPI     | *Note         |

| Enable MIPI High Speed<br>Mode Only (only for<br>MIPI) | Supports only HS mode, not LP mode                | DISABLED, ENABLED                                  | DISABLED      |

| I/O Standard for this interface                        | I/O Standard for this interface                   | Supports all I/O types per selected Interface Type | LVCMOS25      |

| Clock Frequency for this Interface                     | Speed at which the interface will run             | 1-450 MHz                                          | *Note         |

| Bus Width for this<br>Interface                        | Bus size for the interface                        | Various depending on the interface selected        | *Note         |

| Number of this Interface                               | Maximum number of buses supported                 | (Calculated)                                       | (Calculated)  |

| Interface Bandwidth (calculated)                       | Calculated from the clock frequency and bus width | (Calculated)                                       | (Calculated)  |

| Clock to Data<br>Relationship at the Pins              | Select the type of external interfaces            | Edge-to-Edge, Centered                             | *Note         |

<sup>\*</sup>Note: All fields of the Pre-Configuration tab are blank as default.

Figure 6.5. Configuration Tab of the DDR\_Generic Modules

Based on the selections made in the Pre-Configuration tab, the Configuration tab is populated with the selections as shown in Figure 6.6. The checkbox at the top of this tab indicates that the interface is selected based on entries in the Pre-Configuration tab. You can choose to change these values by disabling this entry. Note that IPexpress chooses the most suitable interface based on selections made in the Pre-Configuration tab.

Table 6.4. GUI Options of the Configuration Tab of the DDR\_Generic Modules

| <b>GUI Option</b>                              | Description                                                                                                                                                        | Range                                          | Default Value |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------|

| Interface Selection based on pre-configuration | Indicates interface is selected based on selection made in the Pre-configuration tab. Disabling this checkbox allows you to select gearing ratio, delay types etc. | Enabled, Disabled                              | Enabled       |

| Interface Type                                 | Types of interfaces                                                                                                                                                | Transmit, Receive, Transmit_MIPI, Receive_MIPI | _             |

| I/O Standard                                   | I/O standard for this interface                                                                                                                                    | All I/O types per selected Interface Type      | _             |

| Clock Frequency                                | Speed at which the interface will run                                                                                                                              | 1-378 MHz (for HP)<br>1-210 MHz (for LP)       | _             |

| Gearing Ratio                                  | Choose the gearing ratio of the interface                                                                                                                          | ×1, ×2, ×4                                     | _             |

| Alignment                                      | Determine the type of external interfaces                                                                                                                          | Edge-to-Edge, Centered                         | _             |

| Bus Width                                      | Bus size for the interface                                                                                                                                         | 1-128                                          | _             |

| <b>GUI Option</b>                          | Description                                                                      | Range                                               | Default Value |

|--------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|---------------|

| Number of Interfaces                       | Maximum number of buses supported                                                | 1-8                                                 | _             |

| Interface                                  | A list of the supported GDDR interfaces                                          | Dependent of the Gearing ratio and Alignment choice | _             |

| Data Path Delay <sup>1</sup>               | Data input can be optionally delayed using the DELAY block.                      | Bypass, Predefined, User defined, Dynamic           | _             |

| Generate PLL with this Module <sup>2</sup> | Option to generate PLL with this module or not to generate PLL with this module. | Enabled, Disabled                                   | _             |

#### Notes:

- 1. When "User Defined" is selected, the delay value field is enabled to allow you to select the delay values 0 to 31. When "Dynamic" is selected, a 5-bit delay port is added to the module. "Dynamic" can only be used for ×2 and ×4 receive interfaces.

- This option is only available for interfaces that are using a PLL. This includes, GDDRX1\_RX.SCLK.Aligned, GDDRX1\_TX.SCLK.Centered, GDDRX2\_TX.ECLK.Centered, and GDDRX4\_TX.ECLK.Centered interfaces.

If the Pre-Configuration tab is used, the gearing ratio of the interface is determined by the speed of the interface. Table 6.5 shows how the gearing ratio is selected.

Table 6.5. Gearing Ratio Selection by the Software for MachXO3D Device

| Device Type                   | Speed of the Interface   | Gearing Ratio |

|-------------------------------|--------------------------|---------------|

|                               | =< 166 MHz               | ×1            |

| High Performance (HP) devices | > 166 MHz and =< 266 MHz | ×2            |

|                               | > 266 MHz                | ×4            |

|                               | =< 70 MHz                | ×1            |

| Low Power (LP) devices        | >70 MHz and =< 133 MHz   | ×2            |

|                               | >133 MHz                 | ×4            |

# 6.3. Building a Generic DDR 7:1 Interface

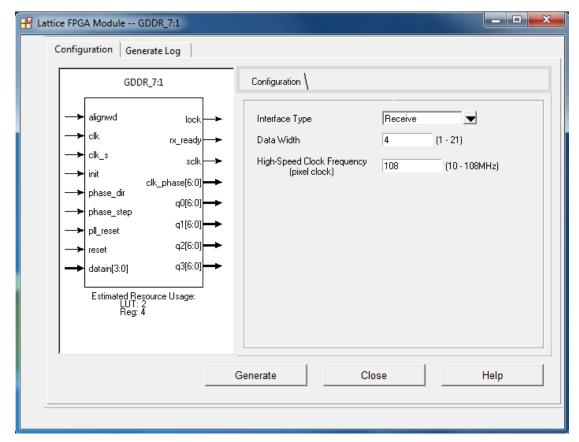

As shown in Figure 6.6, you can choose interface type GDDR\_71, enter module name and click **Customize** to open the Configuration tab. The Configuration tab options are listed in this section. The DDR 7:1 interface is a very specific application, so the options are relatively simple. Most of the necessary logic is built into the software for ease of use.

Figure 6.6. GDDR\_71 Interface Selection at the IPexpress Main Window

Figure 6.7. Configuration Tab of GDDR\_71

Table 6.6. GUI Options of the Configuration Tab for GDDR\_71

| GUI Option                               | Description                                  | Range             | Default Value |

|------------------------------------------|----------------------------------------------|-------------------|---------------|

| Interface Type                           | Types of interfaces                          | Transmit, Receive | Receive       |

| Data Width                               | The number of incoming channels              | 1-21              | 4             |

| High speed Clock Frequency (Pixel Clock) | Pixel clock frequency for 7:1 LVDS interface | 10-108 MHz        | 108           |

# 7. Generic High-Speed DDR Design Guidelines

## 7.1. I/O Logic Cells and Gearing Logic

Each Programmable I/O Cell (PIC) has four programmable I/O (PIOs), which form two pairs of I/O buffers. Each PIO by itself can support a ×1 gearing ratio. A pair of PIOs, either the A/B pair or C/D pair, can support a ×2 gearing ratio. Support of a ×4 or 7:1 gearing ratio will take up all four PIOs in one PIC block. The ×4 or 7:1 gearing ratio can only be supported when the A/B pair pins are available in the package, and are independent of the availability of the C/D pins. The total number of ×2 interfaces available in a specific package is determined by the total number of A/B and C/D pairs. The total number of ×4/7:1 interfaces available in a specific package is determined by the total number of A/B pairs.

Table 7.1. Gearing Logic Supported by Mixed Mode of I/O Logic Cells for MachXO3D Devices

| Gearing Type          | I/O Logic A                          | I/O Logic B                       | I/O Logic C                          | I/O Logic D                          |

|-----------------------|--------------------------------------|-----------------------------------|--------------------------------------|--------------------------------------|

| ×2 gearing (A/B pair) | IDDRX2 or ODDRX2                     | Not available                     | Basic I/O registers or<br>×1 gearing | Basic I/O registers or<br>×1 gearing |

| ×2 gearing (C/D pair) | Basic I/O registers or<br>×1 gearing | Basic I/O registers or x1 gearing | IDDRX2 or ODDRX2                     | Not available                        |

| ×4 gearing            | IDDRX4 or ODDRX4                     | Not available                     | Basic I/O registers or ×1 gearing    | Basic I/O registers or<br>×1 gearing |

| 7:1 gearing           | IDDRX71 or ODDRX71                   | Not available                     | Basic I/O registers or ×1 gearing    | Basic I/O registers or<br>×1 gearing |

## 7.2. High-Speed ECLK Bridge

The high-speed ECLK bridge is used to enhance communication of ECLKs across the MachXO3D device and is mainly used for high-speed video applications. The bridge allows a clock source to drive the edge clocks on the top and bottom edges of the device with minimal skew. The inputs to the bridge include primary clock pins from the top and bottom sides, PLL outputs from both sides, and clock tree routings.

Two bridge muxes are available in the ECLK bridge: one for each ECLK on the same side of the device. These muxes allow dynamic switching between two edge clocks. Refer to MachXO3D sysCLOCK PLL Usage Guide (FPGA-TN-02070) for ECLK bridge connectivity details.

The ECLK bridge supports all the generic high-speed interfaces except the high-speed ×2 and ×4 receive interfaces. The ECLK bridge component must be instantiated in the design in order to use the bridge function or to use it for routing purpose.

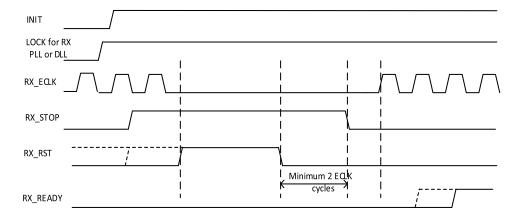

# 7.3. Reset Synchronization Requirement

The generic DDR interfaces are built with multiple dedicated circuits that are optimized for high-speed applications. It is therefore necessary to make sure all the components, such as CLKDIV and IDDR/ODDR, start with the same high-speed edge clock cycle to maintain the clock domain crossing margin between ECLK and SCLK, and to avoid bus bit-order scrambling due to the various delay of the reset pulse.

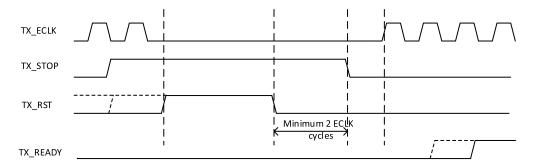

The ECLKSYNCA component and a particular reset sequence are required to guarantee a successful system implementation for interfaces using ×2, ×4, and 7:1 gearings. Figure 7.1 and Figure 7.2 show the timing requirements for receive interfaces and transmit interfaces. The RX\_STOP or TX\_STOP signal must be connected to the STOP port of the ECLKSYNCA component. The RX\_RST or the TX\_RST should be connected to the reset port of the ODDR/IDDR and CLKDIV components. The RX\_ECLK or TX\_ECLK are the outputs of the ECLKSYNCA components. It is necessary to have a minimum of two ECLK cycles between the RST and STOP signals as shown in the figures below. The receive interface

reset process should not start until the transmit interface reset process is complete in a loopback implementation. The clock signal used to generate the minimum two ECLK delay can be any clock that is slower than the ECLK frequency.

Figure 7.1. Reset Synchronization for Receive Interfaces

Figure 7.2. Reset Synchronization for Transmit Interfaces

These timing requirements are built into the generic DDR ×2/×4/7:1 modules when they are generated by IPexpress. The RX\_STOP/TX\_STOP, RX\_RST/TX\_RST, and RX\_ECLK/TX\_ECLK are internal signals when the modules are generated by IPexpress. The reset timing requirements must be followed and implemented in RTL code when the generic DDR interfaces are built outside of IPexpress.

## 7.4. Timing Analysis for High-Speed GDDR Interfaces

You must run Static Timing Analysis in the software for each of the high-speed interfaces. This section describes the timing preferences to use for each type of interface and the expected Trace results. The preferences can either be entered directly in the preference file (.lpf file) or through the Spreadsheet View graphical user interface.

The MachXO3D External Switching Characteristics section of MachXO3D Family Data Sheet (FPGA-DS-02026) should be used along with this section. The data sheet specifies the actual values for these constraints for each of the interfaces.

#### 7.4.1. Frequency Constraints

You must explicitly specify FREQUENCY (or PERIOD) PORT preferences to all input clocks in the design. This preference may not be required if the clock is generated out of a PLL or DLL or is input to a PLL or DLL. Refer to the Generic High-Speed DDR Interfaces section of this document for all the clock pin and clock routing requirements.

## 7.4.2. Setup and Hold Time Constraints

All of the receive interfaces can be constrained with setup and hold preferences.

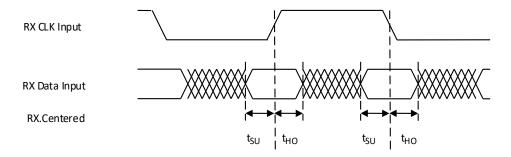

**Receive Centered Interface**: Figure 7.3 shows the data and clock relationship for a Receive Centered Interface. Since the clock is centered to the data, it often provides sufficient setup and hold time at the device interface.

Figure 7.3. Receiver RX.CLK.Centered Waveforms

You must specify in the software preference the amount of setup and hold time available. These parameters are listed in the figure as  $t_{SU}$  (setup time) and  $t_{HO}$  (hold time). They can be directly provided using the INPUT\_SETUP and HOLD preference as shown below:

```

INPUT_SETUP PORT "Data" <tSU> ns HOLD <tHO> ns CLKPORT "CLK";

```

Where: Data = Input Data Port; CLK = Input Clock Port.

The External Switching Characteristics section of MachXO3D Family Data Sheet (FPGA-DS-02026) specifies the minimum setup and hold times required for each of the high-speed interfaces running at maximum speed. For designs not running at the maximum speed, the Static Timing Analysis tool in the software can be used to calculate the setup and hold time values.

Using a GDDRX2\_RX.ECLK.Centered interface running at 250 MHz as an example, the preference can be set like this. The software will provide the minimum requirement of  $t_{SU}$  and  $t_{HO}$  for the interface.

```

INPUT_SETUP PORT Data 0.500000 ns HOLD 0.500000 ns CLKPORT "CLK";

```

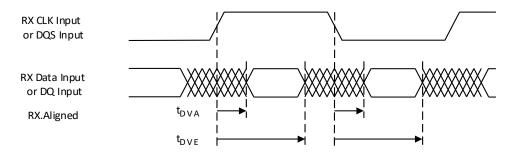

**Receive Aligned Interface:** Figure 7.4 shows the data and clock relationship for a Receive Aligned Interface. The clock is aligned edge-to-edge with the data.

Figure 7.4. Receiver RX.CLK.Aligned Input Waveforms

The worst case data may occur after the clock edge, and therefore has a negative setup time when entering the device. For this interface, the worst case setup time is specified by  $t_{DVA}$ , which is the data valid after the clock edge. The worst case hold time is specified as  $t_{DVE}$ , which is the data hold after clock. The setup and hold time for this interface can be specified as below.

${\tt INPUT\_SETUP\ PORT\ Data\ <-tDVA\ >\ ns\ HOLD\ <\ tDVE>\ ns\ CLKPORT\ ``CLK'';}$

Where: Data = Input Data Port; CLK= Input Clock Port

A negative number is used for SETUP time as the data occurs after the clock edge in this case. The External Switching Characteristics section of MachXO3D Family Data Sheet (FPGA-DS-02026) specifies the maximum t<sub>DVA</sub> and minimum t<sub>DVE</sub> values required for each of the high-speed interfaces running at maximum speed. The data sheet numbers for this preference are listed in UI (Unit Intervals). One UI is equal to half of the clock period. Hence these numbers will need to be calculated from the clock period used.

For the GDDRX2 RX.ECLK.Aligned interface running at a speed of 250 MHz (UI = 2.0 ns)

$t_{DVA}$  = 0.32 UI = 0.64 ns,  $t_{DVE}$  = 0.70 UI = 1.4 ns

The preference for this case is:

INPUT SETUP PORT Data -0.640000 ns HOLD 1.400000 ns CLKPORT "CLK";

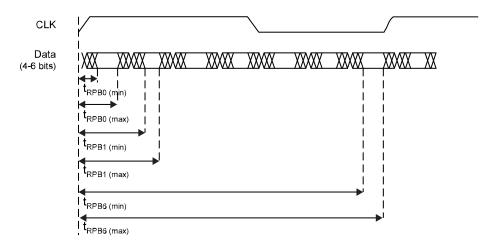

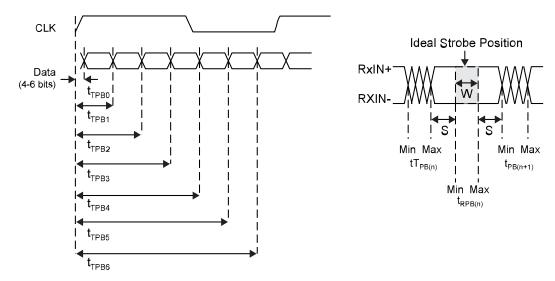

Receive 7:1 LVDS Interface: The 7:1 LVDS interface is a unique GDDR interface, which uses one cycle of the pixel clock to align the seven data bits. Figure 7.5 shows the timing of this interface, where t<sub>RPBi</sub> is the input stroke position for bit i. For this interface, the maximum setup time for bit0 is specified by the t<sub>RPBO</sub> min, while the minimum hold time is specified as t<sub>RPB0</sub> max. The t<sub>RPBi</sub> min and t<sub>RPBi</sub> max form the boundary of the input strobe position for bit i of this interface. The values can be found in the External Switching Characteristics section of MachXO3D Family Data Sheet (FPGA-DS-02026).

Figure 7.5. Receiver GDDR71\_RX. Waveforms

It is recommended to use Display Interface Reference Design for 7:1 interface implementation (RD1093).

Receive Dynamic Interfaces: Static Timing Analysis will not show timing for all the dynamic interface cases as the either the clock or data delay is dynamically updated at run time.

#### 7.4.3. Clock-to-Out Constraints

All of the transmit (TX) interfaces can be constrained with clock-to-out constraints to detect the relationship between the clock and data when leaving the device.

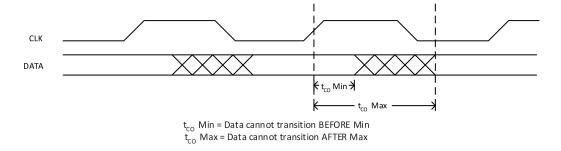

Figure 7.6 shows how the clock-to-out is constrained in the software. Minimum t<sub>CO</sub> is the minimum time after the clock edge transition that the data will not transit. So any data transition must occur between the t<sub>co</sub> minimum and maximum values.

Figure 7.6. t<sub>co</sub> Minimum and Maximum Timing Analysis

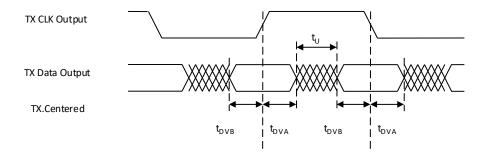

**Transmit Centered Interfaces**: The transmit clock is expected to be centered with the data when leaving the device. Figure 7.7 shows the timing for a centered transmit interface.

Figure 7.7. Transmitter TX.CLK.Centered Output Waveforms

Figure 7.7 shows that the maximum value after which the data cannot transit is  $-t_{DVB}$ . The  $t_{DVB}$  is also the data valid before clock edge value. The minimum value before which the data cannot transition is  $-(t_U + t_{DVB})$ , where  $t_U$  is the period of time the data is in transition. This is also the data valid after clock value. A negative sign is used because in this particular case where clock is forwarded centered-aligned to the data, these two conditions occur before the clock edge.

MachXO3D Family Data Sheet (FPGA-DS-02026) specifies the  $t_{DVB}$  and  $t_{DVA}$  values at maximum speed. But we do not know the  $t_U$  value, so the minimum  $t_{CO}$  can be calculated using the following equations

$t_{CO}$  Min. = - $(t_{DVB} + t_{U})$  $\frac{1}{2}T = t_{DVA} + t_{DVB} + t_{U}$

$-(t_{DVB} + t_{U}) = t_{DVA} - \frac{1}{2}T$

$t_{CO}$  Min. =  $t_{DVA} - \frac{1}{2}T$

The clock-to-out time in the software can be specified as:

CLOCK\_TO\_OUT PORT "Data" MAX <-tDVB> MIN <tDVA-1/2 Clock Period> CLKPORT "CLK" CLKOUT PORT "Clock";

Where: Data = Data Output Port; Clock = Forwarded Clock Output Port; CLK = Input Clock Port

The values for  $t_{DVB}$  and  $t_{DVA}$  can be found in the External Switching Characteristics section of MachXO3D Family Data Sheet (FPGA-DS-02026) for the maximum speed.

For a GDDRX2\_TX.SCLK.Centered interface running at 250 MHz, the preference would be:

CLOCK\_TO\_OUT PORT "Data" MAX -0.670000 ns MIN -1.330000 ns CLKPORT "CLK" CLKOUT PORT "Clock";

© 2019-2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

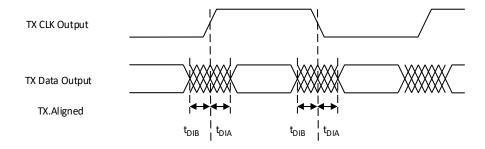

**Transmit Aligned Interfaces**: In this case, the clock and data are aligned when leaving the device. Figure 7.8 shows the timing diagram of this interface.

Figure 7.8. Transmitter TX.CLK.Aligned Waveforms

Figure 7.8 shows that maximum value after which the data cannot transition is  $t_{DIA}$ . This is the data invalid after the clock value. The minimum value before which the data cannot transition is  $-t_{DIB}$ , which is also the data invalid before the clock value. A negative sign is used for the minimum value because the minimum condition occurs before the clock edge.

The clock to out time in the software can be specified as:

```