# **DDR 7:1 Module**

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| Contents                                     |              |

|----------------------------------------------|--------------|

| Acronyms in This Document                    |              |

| 1. Introduction                              | <del>(</del> |

| 1.1. Features                                | 6            |

| 1.2. Conventions                             | 6            |

| 1.2.1. Nomenclature                          | 6            |

| 1.2.2. Signal Names                          |              |

| 2. Functional Description                    |              |

| 2.1. Overview                                |              |

| 2.2. Functional Diagrams                     | 8            |

| GDDRX71 RX.ECLK                              |              |

| 2.2.1. RX Output Data Mapping                |              |

| 2.2.2. GDDRX71 RX Word Alignment Function    |              |

| GDDRX71 TX.ECLK                              |              |

| 2.2.3. TX Input Data Mapping                 |              |

| 2.3. Signal Description                      |              |

| 2.4. Attribute Summary                       |              |

| 3. IP Generation, Simulation, and Validation |              |

| 3.1. Generating the IP                       | 20           |

| 3.2. Running Functional Simulation           |              |

| 3.3. Constraining the IP                     |              |

| 3.4. IP Evaluation                           | 24           |

| Appendix A. Resource Utilization             |              |

| References                                   |              |

| Technical Support Assistance                 |              |

| Revision History                             |              |

# **Figures**

| Figure 2.1. GDDR 7:1 I/O Soft IP Top-level Block Diagram                                                | 7    |

|---------------------------------------------------------------------------------------------------------|------|

| Figure 2.2. GDDRX71_RX.ECLK with GDDR_SYNC and Internal GPLL (without BW_ALIGN) Block Diagram           | 8    |

| Figure 2.3. GDDRX71_RX.ECLK with GDDR_SYNC and External PLL Enabled Block Diagram                       | 9    |

| Figure 2.4. GDDRX71_RX.ECLK with GDDR_SYNC, Internal GPLL and BW_ALIGN Block Diagram                    | 9    |

| Figure 2.5. GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN and External PLL Enabled Block Diagram             | 10   |

| Figure 2.6. GDDRX71_RX.ECLK with GDDR_SYNC, Internal GPLL, BW_ALIGN and Data Delay Control Block Diagr  | am10 |

| Figure 2.7. GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN, Data Delay Control and External PLL Enabled Block | ck   |

| Diagram                                                                                                 | 11   |

| Figure 2.8. Rx Output Data Mapping                                                                      | 12   |

| Figure 2.9. Rx Timing Diagram                                                                           | 12   |

| Figure 2.10. GDDRX71_RX Word Alignment Diagram                                                          | 13   |

| Figure 2.11. GDDRX71_TX.ECLK Static Delay Block Diagram                                                 | 13   |

| Figure 2.12. Tx Input Data Mapping                                                                      | 14   |

| Figure 2.13. Tx Timing Diagram                                                                          | 15   |

| Figure 3.1. Module/IP Block Wizard                                                                      | 20   |

| Figure 3.2. Configure Block of GDDR 7:1 I/O Module                                                      | 21   |

| Figure 3.3. Check Generated Result                                                                      | 22   |

| Figure 3.4. Simulation Wizard                                                                           | 23   |

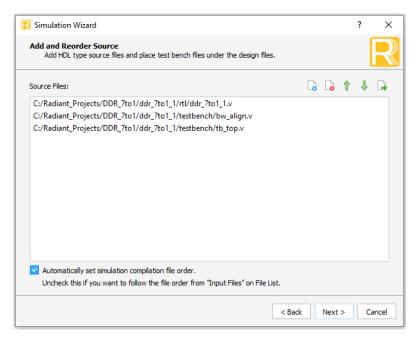

| Figure 3.5. Adding and Reordering Source                                                                | 24   |

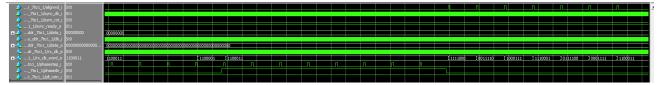

| Figure 3.6. Simulation Waveform                                                                         | 24   |

| Tables                                                                                                  |      |

| Table 2.1. Available GDDR 7:1 I/O Module Interfaces                                                     | 7    |

| Table 2.2. Summary of the Soft Logic                                                                    |      |

| Table 2.3. GDDR 7:1 I/O Module Receive Signal Description                                               |      |

| Table 2.4. GDDR 7:1 I/O Module Transmit Signal Description                                              |      |

| Table 2.5. Attributes Table                                                                             |      |

| Table 2.6. Attributes Description                                                                       |      |

| Table 3.1. Generated File List                                                                          |      |

| Table A.1. Resource Utilization (LIFCL)                                                                 |      |

| Table A.2. Resource Utilization (LFCPNX)                                                                |      |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition               |

|---------|--------------------------|

| GDDR    | Generic Double Data Rate |

| GUI     | Graphical User Interface |

| I/O     | Input/Output             |

| RTL     | Register Transfer Level  |

# 1. Introduction

The Lattice Semiconductor Generic Double Data Rate 7:1 Input/Output (GDDR 7:1 I/O) Module is designed to be used mainly for Flat-panel Display interface.

## 1.1. Features

Key features of the Generic Double Data Rate 7:1 Input/Output Module include:

- Receive and Transmit Interface up to 945 Mbps

- 1-bit to 16-bit data bus width

- Optional bit word alignment and data delay control (for Receive Interface only)

- Optional use of external PLL (for LFMXO5-25 device on Receive Interface only)

## 1.2. Conventions

### 1.2.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.2.2. Signal Names

Signal names that end with:

- \_n are active low

- \_i are input signals

- \_o are output signals

- \_io are bi-directional input/output signals

# 2. Functional Description

### 2.1. Overview

GDDR 7:1 I/O Module is a specific case of Generic DDR I/O Module designed to be used for Flat-panel Display interface.

Table 2.1 provides a summary of GDDR 7:1 I/O Interfaces.

Table 2.1. Available GDDR 7:1 I/O Module Interfaces

| Feature         | Description                                                                                                                                                                                             | Comments                                                                              |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| GDDRX71_RX.ECLK | GDDRX71_RX.ECLK  Generic DDR 7:1 Receive Interface  Supports bypassed and dynamic data path delay w BW_ALIGN is enabled.  Optional BW_ALIGN support soft logic.  Required GDDR SYNC support soft logic. |                                                                                       |

| GDDRX71_TX.ECLK | Generic DDR 7:1 Transmit Interface                                                                                                                                                                      | Supports bypassed and dynamic data path delay. Required GDDR_SYNC support soft logic. |

#### Notes:

- G Generic

- RX Receive interface

- \_TX Transmit interface

- ECLK Uses edge clock clocking resource

The following Table 2.2 are the Summary of the Soft Logic

The following Soft Logic Modules are utilized by the Generic DDR 7:1 IP for synchronization and alignment. The GDDR\_SYNC module is used by all configurations of the IP and automatically included when generating the IP. The module BW\_ALIGN, on the other hand is optional but is only available when the interface of the IP is Receive.

Table 2.2. Summary of the Soft Logic

| Module    | Description                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------|

| GDDR_SYNC | Needed to tolerate large skew between stop and reset input.                                                        |

| BW_ALIGN  | This soft IP is used to perform bit and word alignment using PLL's dynamic phase shift interface and dynamic DELAY |

|           | adjustment.                                                                                                        |

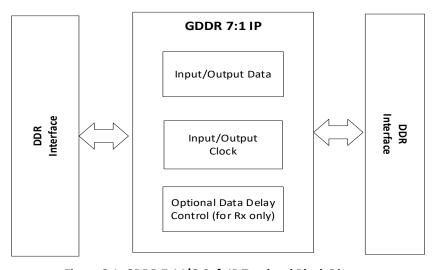

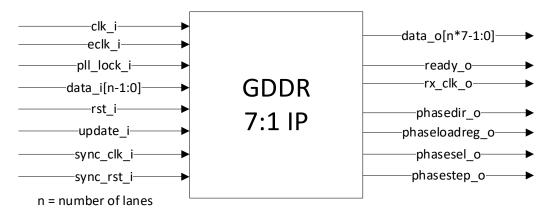

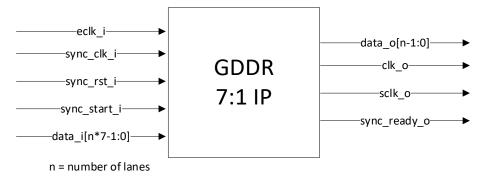

Figure 2.1 presents top-level diagram describing GDDR 7:1 I/O Module.

Figure 2.1. GDDR 7:1 I/O Soft IP Top-level Block Diagram

# 2.2. Functional Diagrams

## GDDRX71\_RX.ECLK

This is a specialized receive interface (called 7:1 LVDS, FPD-Link, or OpenLDI) using 1:7 gearing and ECLK. The input clock coming in is multiplied 3.5X using a PLL. The multiplied clock is used to capture the data at the receive IDDR71 module. Internal PLL is available on all devices. Optional use of external PLL when using LFMXO5-25 device is also available.

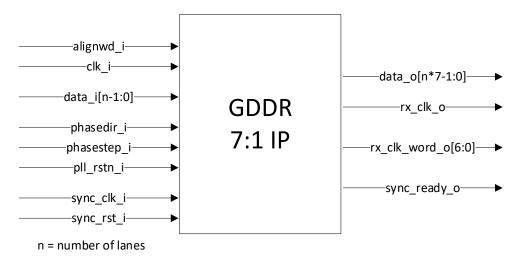

Figure 2.2 shows the GDDR 7:1 I/O Receive Interface only with Bit and Word Alignment, and Data Delay Control options disabled.

Figure 2.2. GDDRX71 RX.ECLK with GDDR SYNC and Internal GPLL (without BW ALIGN) Block Diagram

Described are the components of this configuration:

- PLL IP, which is automatically instantiated on this IP configuration, generates the edge clock from *clk\_i*. The frequency of the generated edge clock of clk\_i is 3.5x clk\_i, This has a dedicated reset input signal, *pll\_rstn\_i*. This IP configuration provides you the control over clock phase shifting through the *phasedir\_i* and *phasestep\_i* signals. The value of phasedir\_i dictates whether to delay or advance the phase of the output clock; 0 to delay the phase, 1 to advance. To activate these changes in the output clock dictated by phasedir\_i, phasestep\_i should be asserted.

- Clock IP components provides edge clock alignment. It also derives the slow clock,  $rx\_clk\_o$ , from the edge clock divided by 3.5 to support the gearing data ratio. The divided clock is available externally, but its frequency is similar to clk\_i. The only difference between rx\_clk\_o and clk\_i is that rx\_clk\_o is aligned to the edge clock.

- DDR Clock IP component generates the receiver clock word as parallel output.

- DDR Data IP component captures the input data. The edge clock is also the clock used to capture data.

- GDDR\_SYNC Soft IP logic performs sequence to synchronize all the resets of the IP components after PLL lock is achieved. The synchronization happens before RX operation starts. When done, it asserts sync\_ready\_o signal to indicate that an operation can already be started. This component has its own clock input, sync\_clk\_i and reset input, sync\_rst\_i.

9

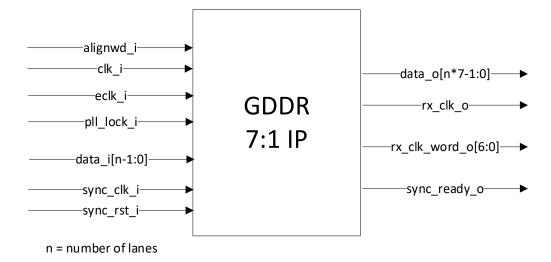

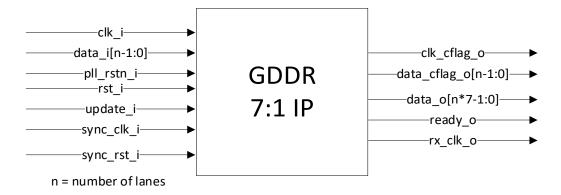

Figure 2.3 show receive interface type block diagram and interface with external PLL.

Figure 2.3. GDDRX71\_RX.ECLK with GDDR\_SYNC and External PLL Enabled Block Diagram

Described are the components of this configuration:

- When External PLL is enabled, the external PLL will generate from one of its clock outputs the edge clock to be

used for this IP configuration. The PLL lock output is also passed to this IP configuration to signify the GDDR SYNC

module to start the clock and reset synchronization.

- Clock IP components provides edge clock alignment. It also derives the slow clock, rx\_clk\_o, from the edge clock divided by 3.5 to support the gearing data ratio. The divided clock is available externally, but its frequency is the similar to clk\_i. The only difference between rx\_clk\_o and clk\_i is that rx\_clk\_o is aligned to the edge clock.DDR Clock IP component generates the receiver clock word as parallel output.

- DDR Clock IP component generates the receiver clock word as parallel output.

- DDR Data IP component captures the input data. The edge clock is also the clock used to capture data

- GDDR\_SYNC Soft IP logic performs sequence to synchronize all the resets of the IP components after PLL lock is achieved. The synchronization happens before RX operation starts. When done, it asserts sync\_ready\_o signal to indicate that an operation can already be started. This component has its own clock input, sync\_clk\_i and reset input, sync\_rst\_i.

Figure 2.4 show receive interface type with bit and word alignment block diagram and interface with internal PLL.

Figure 2.4. GDDRX71\_RX.ECLK with GDDR\_SYNC, Internal GPLL and BW\_ALIGN Block Diagram

When Bit and Word Alignment feature is enabled, the BW\_ALIGN Soft IP logic is added on the Receive interface IP components. This component will control the PLL dynamic clock phase shifting, and DDR components align input to perform the bit and word alignment respectively. Notice that on this configuration the phasedir\_i, phasestep\_i, and alignwd\_i signals are no longer available on the interface. During bit alignment, PLL generated edge clock will be placed on the center of the valid window of the DDR clock and data words. Word alignment automatically controls the alignment on the DDR clock component by slipping the clock word until 7'h63 clock word value is achieved. Once synchronization and alignment are performed, ready\_o signal will be asserted by the IP.

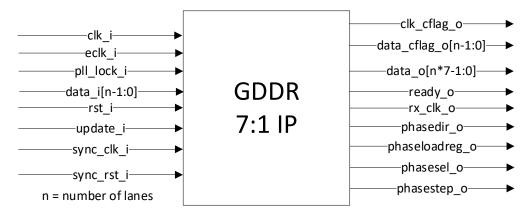

Figure 2.5 show receive interface type with bit and word alignment block and interface diagram with external PLL.

Figure 2.5. GDDRX71\_RX.ECLK with GDDR\_SYNC, BW\_ALIGN and External PLL Enabled Block Diagram

When Bit and Word Alignment feature is enabled, the BW\_ALIGN Soft IP logic is added on the Receive interface IP components. This component will control the PLL dynamic clock phase shifting, and DDR components align input to perform the bit and word alignment respectively. When the setting *Use External PLL* is enabled, ports eclk\_i, pll\_lock\_i, phasedir\_o, phaseload\_reg\_o, phasesel\_o, and phasestep\_o are available. In this case, edge clock signal is generated from any of the external PLL's output clocks while the PLL's lock output is also passed to this IP configuration to signify the GDDR SYNC module to start the clock and reset synchronization. Aside these differences, functionality remains the same

Figure 2.6 show receive interface type, bit and word alignment and data delay control enabled block diagram and interface with internal PLL.

Figure 2.6. GDDRX71\_RX.ECLK with GDDR\_SYNC, Internal GPLL, BW\_ALIGN and Data Delay Control Block Diagram

When data delay control option is enabled, it provides the IP automatic control to add data delay on the DDR data path. For this feature, the IP checks if the data is on the center of the edge clock. It delays the data to determine the valid window then place the data on the center of the window. Once synchronization, alignment and data delay are all performed, ready\_o signal will be asserted by the IP.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2.7 show receive interface type, bit and word alignment and data delay control enabled block diagram and interface with external PLL.

Figure 2.7. GDDRX71\_RX.ECLK with GDDR\_SYNC, BW\_ALIGN, Data Delay Control and External PLL Enabled Block Diagram

When data delay control option is enabled, it provides the IP automatic control to add data delay on the DDR data path. For this feature, the IP checks if the data is on the center of the edge clock. It delays the data to determine the valid window then place the data on the center of the window. Once synchronization, alignment and data delay are all performed, ready\_o signal will be asserted by the IP. In this case, edge clock signal is generated from any of the external PLL's output clocks while the PLL's lock output is also passed to this IP configuration to signify the GDDR SYNC module to start the clock and reset synchronization. Aside these differences, functionality remains the same.

## 2.2.1. RX Output Data Mapping

Bus Width = 2 data\_i[1:0] = a[1:0], b[1:0], c[1:0], d[1:0], e[1:0], f[1:0], g[1:0] data\_o[7\*2-1:0] = {g[1:0],f[1:0], e[1:0], d[1:0], c[1:0], b[1:0], a[1:0]}

Figure 2.8. Rx Output Data Mapping

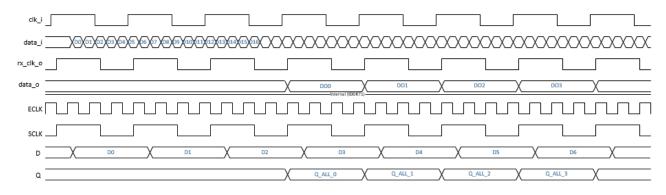

Figure 2.9. Rx Timing Diagram

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

As shown in Figure 2.8, for GDDR71 Rx configuration, when Bus Width is 2 bits, the IP generates two IDDR71 modules (in our example for X3.5, the number of data i batches is seven.).

The first batch of incoming data\_i[a1:a0] is captured on the rising edge of the fast clock. The next batch of data\_i[b1:b0] is captured on the falling edge of the fastest clock and so on. The fast clock in this case is ECLK since it has the greater frequency.

In the figure, this translates to the batch of the input data's slowest bits data\_i[g1:g0] being placed on the data\_o vector's highest bits [13:12]. Similarly, data\_i[f1:f0] bits are placed on data\_o[11:10] and so on. The sum of all the IDDR71 outputs is a data\_o[13:0] vector.

Figure 2.9 shows the timing diagram of the said example.

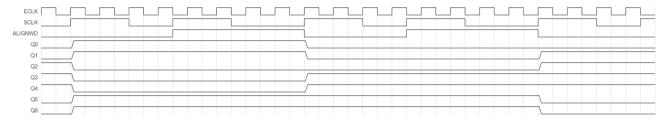

## 2.2.2. GDDRX71\_RX Word Alignment Function

The IDDR71 supports slip function for word alignment. This operation stops the clock (SCLK) for one ECLK cycle when the ALIGNWD signal has a transition from low to high. Each time ALIGNWD has a transition from low to high it can skip two bits.

Figure 2.10 shows the Word Alignment Diagram.

Figure 2.10. GDDRX71 RX Word Alignment Diagram

### **GDDRX71 TX.ECLK**

This is a specialized transmit interface (called 7:1 LVDS, FPD-Link, or OpenLDI) using 7:1 gearing and ECLK. The output clock going out is divided by 3.5 using ECLKDIV. The output clock is used to capture the data at the ODDR71 module. Transmit side for the 7:1 LVDS interface DDR using the 7:1 gearing with ECLK. The clock output is aligned to the data output.

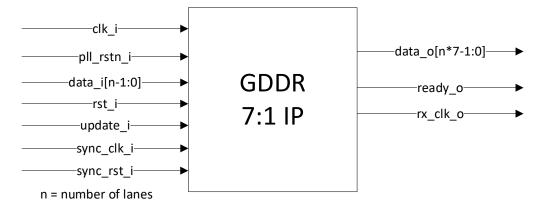

Figure 2.11 show GDDR 7:1 I/O transmit block diagram and interface respectively.

Figure 2.11. GDDRX71\_TX.ECLK Static Delay Block Diagram

Described below are the components of this configuration:

- Clock IP components provides edge clock alignment. It also derives the slow clock, sclk\_o, from the edge clock

divided by 3.5 to support the gearing data ratio. The divided clock is available externally. Like the slow clock, the

output clock, clk\_o is derived by dividing the edge clock by 3.5.

- DDR Clock IP component generates the receiver clock word as parallel output.

FPGA-IPUG-02058-1.8 13

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal

- DDR Data IP component generates the output data. Output is generated with the slow clock.

- GDDR\_SYNC Soft IP logic performs sequence to synchronize all the resets of the IP components once sync\_start\_i signal is asserted. The synchronization happens before TX operation starts. When done, it asserts sync\_ready\_o signal to indicate that an operation can already be started. This component has its own reset input, sync\_rst\_i.

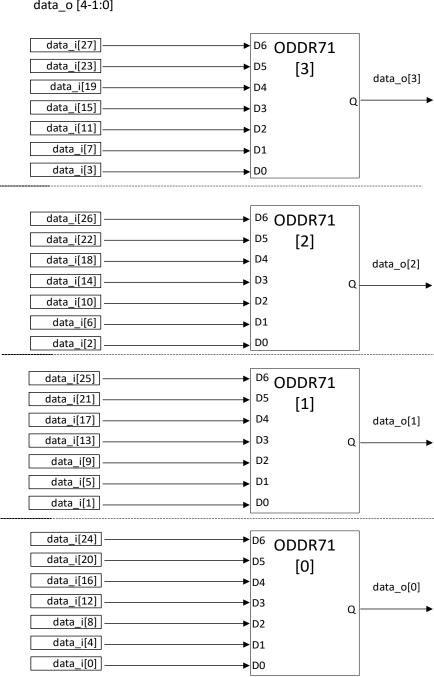

## 2.2.3. TX Input Data Mapping

Bus Width = 4 data\_i [7 \* 4 - 1 : 0] data\_o [4-1:0]

Figure 2.12. Tx Input Data Mapping

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

14

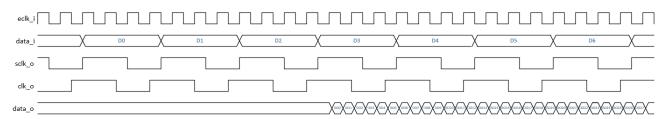

Figure 2.13. Tx Timing Diagram

As shown in Figure 2.12, for GDDR 7:1 Tx configuration, when Bus Width is 4 bits, the IP generates four ODDR71 modules. The entire input data is broken down into 7 groups, each group with the size of 4 bits. The group with the fastest bits data\_i[3:0] is transmitted first, followed by data\_i[7:4] and so on.

Figure 2.13 shows the timing diagram of the said example.

# 2.3. Signal Description

Table 2.3. GDDR 7:1 I/O Module Receive Signal Description

| Port Name       | Direction | Width(bits) | Description                                                                                                                                                                                                                                         |  |

|-----------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock and Reset |           |             |                                                                                                                                                                                                                                                     |  |

| rx_clk_o        | OUT       | 1           | Clock output for Receive interface. Divided RX clock form 7:1 RX interface produced by ECLKDIV. This is only available when <i>Interface Type</i> is Receive.                                                                                       |  |

| sync_clk_i      | IN        | 1           | Startup clock. A low-speed continuously running clock input. Its frequency is independent to the input clock but it must be significantly lower.                                                                                                    |  |

| sync_rst_i      | IN        | 1           | Active high reset signal. Can be used asynchronously to the input clock, but it is recommended to be de-asserted synchronously with sync_clk_i.                                                                                                     |  |

| rst_i           | IN        | 1           | Active HIGH reset signal when <i>Enable Bit and Word Alignment Soft IP</i> is enabled.                                                                                                                                                              |  |

| eclk_i          | IN        | 1           | Receive data sampling clock. This clock can be from a PLL clock output. This is only available when <i>Use External PLL</i> is enabled.                                                                                                             |  |

| User Interface  | ·         |             |                                                                                                                                                                                                                                                     |  |

| alignwd_i       | IN        | 1           | This signal is used for word alignment. It shifts word by one bit. This is only available when <i>Enable Bit and Word Alignment Soft IP</i> is disabled.                                                                                            |  |

| pll_rstn_i      | IN        | 1           | Active low reset of internal PLL. This is available only when<br>Interface Type is Receive and Use External PLL is disabled.                                                                                                                        |  |

| phasedir_i      | IN        | 1           | Phase rotation direction of internal PLL. This is available only when Interface Type is Receive, Enable Bit and Word Alignment Soft IP, Enable Data Delay Control and Use External PLL are all disabled.                                            |  |

| phasestep_i     | IN        | 1           | Rotate phase of internal PLL. This is available only when Interface Type is Receive, Enable Bit and Word Alignment Soft IP, Enable Data Delay Control and Use External PLL are all disabled.                                                        |  |

| update_i        | IN        | 1           | Start bit and word alignment, or restart procedure if optimization is needed again. This is available only when Interface Type is Receive and Enable Bit and Word Alignment Soft IP is enabled                                                      |  |

| pll_lock_i      | IN        | 1           | Starts GDDR_SYNC clock and reset synchronization. This can be the PLL lock output. This is only available when <i>Use External PLL</i> is enabled.                                                                                                  |  |

| data_cflag_o    | ОПТ       | n           | Underflow or overflow flag to indicate minimum or maximum data path delay adjustment is reached. This is available only when <i>Interface Type</i> is Receive <i>and Enable Data Delay Control</i> is enabled.                                      |  |

| clk_cflag_o     | OUT       | 1           | Underflow or overflow flag to indicate minimum or maximum clock path delay adjustment is reached. This is available only when <i>Interface Type</i> is Receive <i>and Enable Data Delay Control</i> is enabled.                                     |  |

| data_o          | OUT       | n*7         | Received input data to fabric.                                                                                                                                                                                                                      |  |

| sync_ready_o    | OUT       | 1           | Indicate that startup is finished, and RX circuit is ready to operate. Only available when <i>Enable Bit and Word Alignment Soft IP</i> is disabled.                                                                                                |  |

| ready_o         | OUT       | 1           | Indicates alignment is done, startup is finished, and RX circuit is ready to operate. This is only available when <i>Enable Bit and Word Alignment Soft IP</i> is enabled.                                                                          |  |

| rx_clk_word_o   | OUT       | 7           | Valid receiver clock word size allowance. Parallel data output. Only available when <i>Enable Bit and Word Alignment Soft IP</i> is disabled.                                                                                                       |  |

| phasedir_o      | OUT       | 1           | BW_ALIGN module output signal to control the direction of rotate phase for dynamic phase shift of external PLL clock output. This is only available when <i>Use External PLL</i> and <i>Enable Bit and Word Alignment Soft IP</i> are both enabled. |  |

| Port Name         | Direction | Width(bits) | Description                                                                                                                                                                                                                            |  |

|-------------------|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| phasestep_o       | OUT       | 1           | BW_ALIGN module output signal to control the rotate phase for dynamic phase shift of external PLL clock output. This is only available when <i>Use External PLL</i> and <i>Enable Bit and Word Alignment Soft IP</i> are both enabled. |  |

| phaseloadreg_o    | OUT       | 1           | BW_ALIGN module output signal to initiate the dynamic phase shift of external PLL. This is only available when <i>Use External PLL</i> and <i>Enable Bit and Word Alignment Soft IP</i> are both enabled.                              |  |

| phasesel_o        | OUT       | 3           | BW_ALIGN module output signal, which specifies the clock output to where dynamic phase shift of external PLL will be applied. The is only available when Use External PLL and Enable Bit and Word Alignment Soft IP are both enabled.  |  |

| I/O Pad Interface |           |             |                                                                                                                                                                                                                                        |  |

| clk_i             | IN        | 1           | Clock input signal from I/O.                                                                                                                                                                                                           |  |

| data_i            | IN        | n           | Data input signal from I/O.                                                                                                                                                                                                            |  |

**Note:** n = number of lanes.

Table 2.4. GDDR 7:1 I/O Module Transmit Signal Description

| Port Name         | Direction | Width(bits) | Description                                                            |

|-------------------|-----------|-------------|------------------------------------------------------------------------|

| Clock and Reset   |           |             |                                                                        |

| eclk_i            | IN        | 1           | Transmit data sampling clock.                                          |

| sclk_o            | OUT       | 1           | Clock output for Interface Type is Transmit.                           |

| sync_clk_i        | IN        | 1           | Low speed continuously running clock input.                            |

| sync_rst_i        | IN        | 1           | Active HIGH reset signal.                                              |

| User Interface    |           |             |                                                                        |

| data_i            | IN        | n*7         | Transmit output data going to I/O.                                     |

| sync_ready_o      | OUT       | 1           | Indicate that startup is finished, and TX circuit is ready to operate. |

| sync_start_i      | IN        | 1           | Waits for the PLL lock signal to start the synchronization.            |

| I/O Pad Interface |           |             |                                                                        |

| clk_o             | OUT       | 1           | Clock output signal to I/O.                                            |

| data_o            | OUT       | n           | Data output signal to I/O. Value range is [1, 16].                     |

**Note:** n = number of lanes

# 2.4. Attribute Summary

Table 2.5 provides a list of user-configurable attributes for the GDDR 7:1 I/O Module. Attributes settings are specified using GDDR 7:1 I/O Module Configuration user interface in Lattice Radiant.

**Table 2.5. Attributes Table**

| Attribute                                                          | Selectable Values                      | Default   | Dependency on other<br>Attributes                                                      | Additional<br>Requirements                                             |

|--------------------------------------------------------------------|----------------------------------------|-----------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Interface Type                                                     | Receive, Transmit                      | Receive   | _                                                                                      | _                                                                      |

| Bus Width                                                          | 1–16                                   | 8         | _                                                                                      | _                                                                      |

| Interface Bandwidth (Mbps)                                         | 126-945 (Receive)<br>70-945 (Transmit) | 945       | _                                                                                      | _                                                                      |

| Use External PLL                                                   | Checked, Unchecked                     | Unchecked | Interface Type = Receive                                                               | Device used is LFMXO5-25.                                              |

| Clock Frequency (MHz)                                              | 18–135 (Receive)<br>10-945 (Transmit)  | 135       | Bandwidth/7                                                                            | Display for information only                                           |

| External PLL Reference Clock and<br>Primary Clock Output Frequency | 18–135                                 | 135       | Interface Type = Receive<br>Bandwidth/7                                                | Display for information only when device used is LFMXO5-25             |

| External PLL Secondary Clock Output<br>Frequency                   | 63–472.5                               | 472.5     | Interface Type = Receive<br>Bandwidth/2                                                | Display for<br>information<br>only when<br>device used is<br>LFMXO5-25 |

| Enable Bit and Word Alignment Soft IP                              | Checked, Unchecked                     | Unchecked | Interface Type = Receive                                                               | _                                                                      |

| Enable Data Delay Control                                          | Checked, Unchecked                     | Unchecked | Interface Type = Receive<br>and Enable Bit and Word<br>Alignment Soft IP is<br>checked | _                                                                      |

| Reference Clock from I/O Pin                                       | Checked, Unchecked                     | Unchecked | Interface Type =<br>Transmit                                                           | _                                                                      |

| Reference Clock Input Buffer Type                                  | (Legal Combination<br>Table)           | LVDS      | Reference Clock from I/O<br>Pin is checked                                             | _                                                                      |

Note: The attributes can be configured from the General Tab of the Lattice Radiant Software user interface.

# Table 2.6 below presents attribute description.

# **Table 2.6. Attributes Description**

| Attribute Name                                                     | Description                                                                                                                                                                                                         |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Type                                                     | RECEIVE or TRANSMIT interface type                                                                                                                                                                                  |

| Bus Width                                                          | Total number of lanes/bus width                                                                                                                                                                                     |

| Interface Bandwidth (Mbps)                                         | Interface Clock Frequency                                                                                                                                                                                           |

| Use External PLL                                                   | Option to use external PLL on Receive interface type                                                                                                                                                                |

| External PLL Reference Clock and Primary Clock<br>Output Frequency | Value for both external PLL reference clock and primary clock output frequencies. The PLL primary clock output will control the edge clock input of Receive interface type.                                         |

| External PLL Secondary Clock Output Frequency                      | Value of external PLL secondary clock output frequency to be used as input to Receive interface type. This can be dynamically phase-shifted manually or automatically depending on BW_ALIGN Soft IP setting.        |

| Enable Bit and Word Alignment Soft IP                              | Optional bit and word alignment Soft IP (BW_ALIGN) module. The bit alignment module centers the edge clock to the middle of the data eye and the word alignment module is used to achieve the 7-bit word alignment. |

| Enable Data Delay Control                                          | When enabled, BW_ALIGN Soft IP module automatically controls the movement of the data on DELAY module.                                                                                                              |

| Reference Clock from I/O Pin                                       | Reference Clock from I/O Pin                                                                                                                                                                                        |

| Reference Clock Input Buffer Type                                  | List of Single-ended or Differential I/O supported                                                                                                                                                                  |

# 3. IP Generation, Simulation, and Validation

This section provides information on how to generate the IP using the Lattice Radiant Software and how to run simulation and synthesis. For more details on the Lattice Radiant Software, refer to the Lattice Radiant software user guide.

# 3.1. Generating the IP

The Lattice Radiant Software allows you to customize and generate modules and IPs and integrate them into the device's architecture. The procedure for generating the GDDR 7:1 I/O module in Lattice Radiant Software is described below

To generate GDDR 7:1 I/O Module:

1. Create a new Lattice Radiant Software project or open an existing project.

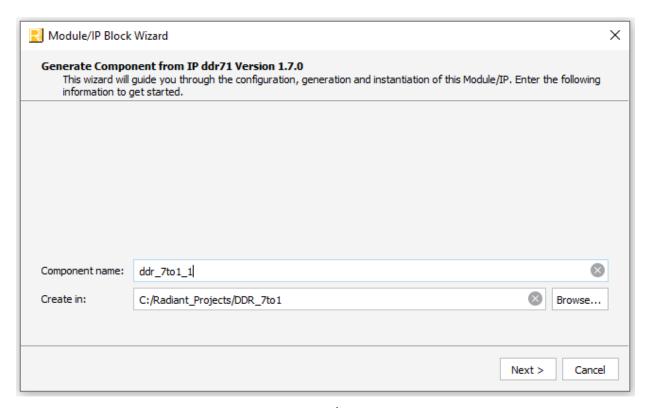

In the IP Catalog tab, double-click on GDDR 7:1 under Module, Architecture\_Modules, I/O category. The Module/IP Block Wizard opens as shown in Figure 3.1. Enter values in the Component name and the Create in fields and click Next.

Figure 3.1. Module/IP Block Wizard

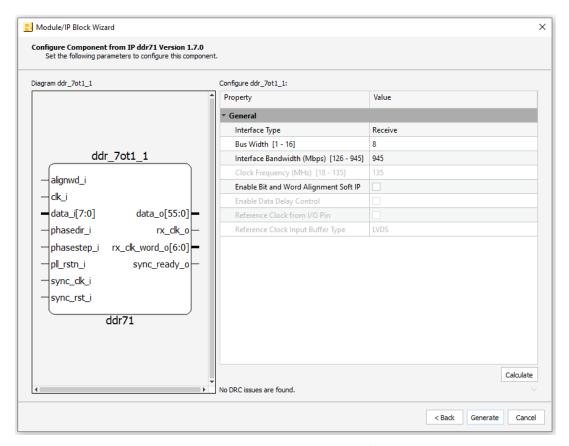

2. In the module's dialog box of the **Module/IP Block Wizard** window, customize the selected GDDR 7:1 I/O module using drop-down menus and check boxes. As a sample configuration, see Figure 3.2. For configuration options, see the Attribute Summary section.

Figure 3.2. Configure Block of GDDR 7:1 I/O Module

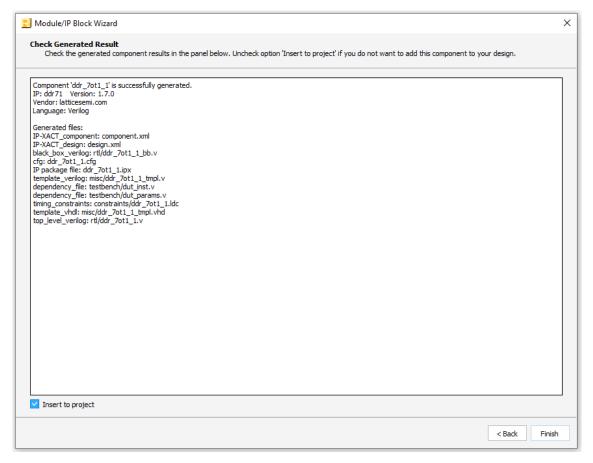

3. Click **Generate**. The **Check Generated Result** dialog box opens, showing design block messages and results as shown in Figure 3.3.

Figure 3.3. Check Generated Result

4. Click the **Finish** button. All the generated files are placed under the directory paths in the **Create in** and the **Component name** fields shown in Figure 3.1.

The generated GDDR 7:1 I/O module package includes the black box (<Instance Name>\_bb.v) and instance templates (<Instance Name>\_tmpl.v/vhd) that can be used to instantiate the module in a top-level design. An example RTL top-level reference source file (<Instance Name>.v) that can be used as an instantiation template for the module is also provided. You may also use this top-level reference as the starting template for the top-level for their complete design. The generated files are listed in Table 3.1.

Table 3.1. Generated File List

| Attribute                                                                                   | Description                                                                     |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| <instance name="">.ipx</instance>                                                           | This file contains the information on the files associated to the generated IP. |

| <instance name="">.cfg</instance>                                                           | This file contains the parameter values used in IP configuration.               |

| component.xml                                                                               | Contains the ipxact:component information of the IP.                            |

| design.xml                                                                                  | Documents the configuration parameters of the IP in IP-XACT 2014 format.        |

| rtl/ <instance name="">.v</instance>                                                        | This file provides an example RTL top file that instantiates the module.        |

| rtl/ <instance name="">_bb.v</instance>                                                     | This file provides the synthesis black box.                                     |

| misc/ <instance name="">_tmpl.v<br/>misc /<instance name="">_tmpl.vhd</instance></instance> | These files provide instance templates for the module.                          |

# 3.2. Running Functional Simulation

After the IP is generated, running functional simulation can be performed using different available simulators. The default simulator already has pre-compiled libraries ready for simulation. Choosing a non-default simulator, however, may require additional steps.

To run functional simulation using the default simulator:

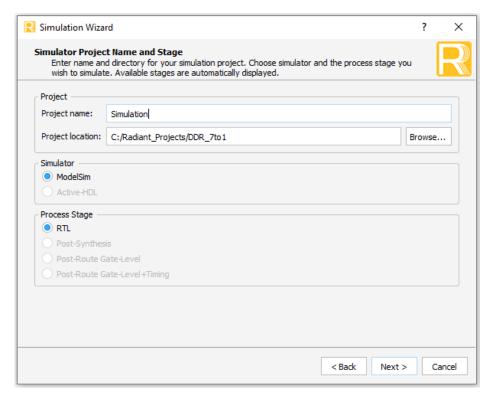

1. Click the button located on the **Toolbar** to initiate **Simulation Wizard**, as shown in Figure 3.4.

Figure 3.4. Simulation Wizard

2. Click **Next** to open the **Add and Reorder Source** window as shown in Figure 3.5.

Figure 3.5. Adding and Reordering Source

3. Click **Next**. The Summary window is shown. Click **Finish** to run the simulation. **Note:** It is necessary to follow the procedure above until it is fully automated in the Lattice Radiant Software Suite. The results of the simulation in our example are provided in Figure 3.6.

Figure 3.6. Simulation Waveform

# 3.3. Constraining the IP

You need to provide proper timing and physical design constraints to ensure that your design meets the desired performance goals on the FPGA. Add the content of the following IP constraint file to your design constraints: <IP\_Instance\_Path>/<IP\_Instance\_Name>/eval/constraints.pdc.

The constraint file has been verified during IP evaluation with the IP instantiated directly in the top-level module. You can modify the constraints in this file with thorough understanding of the effect of each constraint.

To use this constraint file, copy the content of *constraints.pdc* to the top-level design constraint for post-synthesis. Refer to Lattice Radiant Timing Constraints Methodology (FPGA-AN-02059) for details on how to constraint your design.

### 3.4. IP Evaluation

There is no restriction on the IP evaluation of this module.

# **Appendix A. Resource Utilization**

DDR 7:1 module resource utilization are shown on Table A.1 and Table A.2 using LIFCL-40-9BG400I, and LFCPNX-100-9LFG672I device with Lattice Synthesis Engine of Lattice Radiant software 3.1. The default configuration is used and some attributes are changed from the default value to show the effect on the resource utilization.

#### Table A.1. Resource Utilization (LIFCL)

| Configuration                               | Clk Fmax (MHz) <sup>1</sup> | Registers | LUTs <sup>2</sup> | EBRs | DSPs |

|---------------------------------------------|-----------------------------|-----------|-------------------|------|------|

| Default                                     | 135                         | 12        | 34                | 0    | 0    |

| Interface Type = Transmit, others = Default | 135                         | 12        | 33                | 0    | 0    |

#### Notes:

- 1. Fmax s generated when the FPGA design only contains the DDR 7:1 module and target frequency is 135 MHz. FPGA can run up to 200 MHz, but the DDR 7:1 module can be used up to 945 MHz ECLK and 135 MHz SCLK only. These values may be reduced when user logic is added to the FPGA design.

- 2. The distributed RAM utilization is accounted for in the total LUT4s utilization. The actual LUT4 utilization is distribution among logic, distributed RAM, and ripple logic.

#### Table A.2. Resource Utilization (LFCPNX)

| Configuration                               | Clk Fmax (MHz) <sup>1</sup> | Registers | LUTs <sup>2</sup> | EBRs | DSPs |

|---------------------------------------------|-----------------------------|-----------|-------------------|------|------|

| Default                                     | 135                         | 12        | 34                | 0    | 0    |

| Interface Type = Transmit, others = Default | 135                         | 12        | 33                | 0    | 0    |

#### Notes:

- 1. Fmax is generated when the FPGA design only contains the DDR 7:1 module and target frequency is 135 MHz. FPGA can run up to 250 MHz, but the DDR 7:1 module can be used up to 945 MHz ECLK and 135 MHz SCLK only. These values may be reduced when user logic is added to the FPGA design.

- 2. The distributed RAM utilization is accounted for in the total LUT4s utilization. The actual LUT4 utilization is distribution among logic, distributed RAM, and ripple logic.

# **References**

- Lattice Radiant Software web page

- Lattice Solutions IP Cores web page

- Lattice Radiant Timing Constraints Methodology (FPGA-AN-02059)

- Lattice Insights web page for Lattice Semiconductor training courses and learning plans

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport. For frequently asked questions, refer to the Lattice Answer Database at www.latticesemi.com/en/Support/AnswerDatabase.

# **Revision History**

#### Revision 1.8. June 2024

| Section                        | Change Summary                                                                                                                               |  |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| All                            | Update title from DDR 7:1 Module - Lattice Radiant Software to DDR 7:1 Module.                                                               |  |  |  |  |

|                                | Made editorial fixes.                                                                                                                        |  |  |  |  |

| Introduction                   | Added option to use external PLL in the Features section.                                                                                    |  |  |  |  |

| Functional Description         | Overview:                                                                                                                                    |  |  |  |  |

|                                | Added description for Table 2.2. Summary of the Soft Logic.                                                                                  |  |  |  |  |

|                                | Functional Diagrams:                                                                                                                         |  |  |  |  |

|                                | <ul> <li>Added description for Figure 2.2. GDDRX71_RX.ECLK with GDDR_SYNC and Internal<br/>GPLL (without BW_ALIGN) Block Diagram.</li> </ul> |  |  |  |  |

|                                | <ul> <li>Removed the following figures and updated the figures numbers of remaining<br/>figures accordingly:</li> </ul>                      |  |  |  |  |

|                                | <ul> <li>Removed Figure 2.3 GDDRX71_RX.ECLK with GDDR_SYNC and Internal GPLL<br/>(without BW_ALIGN) Interface</li> </ul>                     |  |  |  |  |

|                                | <ul> <li>Figure 2.5 GDDRX71_RX.ECLK with GDDR_SYNC and External PLL Enabled<br/>Interface</li> </ul>                                         |  |  |  |  |

|                                | <ul> <li>Figure 2.7 GDDRX71_RX.ECLK with GDDR_SYNC, Internal GPLL and BW_ALIGN<br/>Interface</li> </ul>                                      |  |  |  |  |

|                                | <ul> <li>Figure 2.9 GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN and External PLL<br/>Enabled Interface</li> </ul>                               |  |  |  |  |

|                                | <ul> <li>Figure 2.11 GDDRX71_RX.ECLK with GDDR_SYNC, Internal GPLL, BW_ALIGN<br/>and Data Delay Control Interface</li> </ul>                 |  |  |  |  |

|                                | <ul> <li>Figure 2.13 GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN and Data Delay<br/>Control and External PLL Enabled Interface</li> </ul>       |  |  |  |  |

|                                | <ul> <li>Figure 2.14 Internal GPLL Control of GDDRX71_RX.ECLK with BW_ALIGN<br/>Interface</li> </ul>                                         |  |  |  |  |

|                                | <ul> <li>Figure 2.15 Internal GPLL Control of GDDRX71_RX.ECLK without BW_ALIGN<br/>Interface</li> </ul>                                      |  |  |  |  |

|                                | Figure 2.19 GDDRX71_RX.ECLK Static Delay Interface                                                                                           |  |  |  |  |

|                                | Added description for Figure 2.11. GDDRX71_TX.ECLK Static Delay Block Diagram.                                                               |  |  |  |  |

|                                | Added new figure:                                                                                                                            |  |  |  |  |

|                                | Figure 2.9. Rx Timing Diagram.                                                                                                               |  |  |  |  |

|                                | Figure 2.13. Tx Timing Diagram.                                                                                                              |  |  |  |  |

|                                | • Signal Description:                                                                                                                        |  |  |  |  |

|                                | <ul> <li>Updated the descriptions for the following ports in Table 2.3. GDDR 7:1 I/O Module<br/>Receive Signal Description:</li> </ul>       |  |  |  |  |

|                                | • sync_clk_i                                                                                                                                 |  |  |  |  |

|                                | • sync_rst_i                                                                                                                                 |  |  |  |  |

|                                | Attribute Summary:                                                                                                                           |  |  |  |  |

|                                | <ul> <li>Updated the Selected Values for the following attributes in Table 2.5. Attributes         Table:     </li> </ul>                    |  |  |  |  |

|                                | Interface Bandwidth (Mbps)                                                                                                                   |  |  |  |  |

|                                | Clock Frequency (Mhz)                                                                                                                        |  |  |  |  |

| IP Generation, Simulation, and | Removed Required Post Synthesis Constraints section.                                                                                         |  |  |  |  |

| Validation                     | Newly added section Constraining the IP.                                                                                                     |  |  |  |  |

| Reference                      | Updated the reference list.                                                                                                                  |  |  |  |  |

## Revision 1.7, March 2023

| Section                        | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Acronyms in This Document      | Updated the GDDR definition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Introduction                   | Added option to use external PLL in the Features section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Functional Description         | <ul> <li>Functional Diagrams:         <ul> <li>updated description adding the support of external PLL in the section;</li> <li>added new interface and block diagrams Figure 2.4. GDDRX71_RX.ECLK with GDDR_SYNC and External PLL Enabled Block Diagram,</li> <li>Figure 2.5. GDDRX71_RX.ECLK with GDDR_SYNC and External PLL Enabled Interface, Figure 2.8. GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN and External PLL Enabled Block Diagram, Figure 2.9. GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN and External PLL Enabled Interface,</li> <li>Figure 2.12. GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN, Data Delay Control and External PLL Enabled Block Diagram, and Figure 2.13. GDDRX71_RX.ECLK with GDDR_SYNC, BW_ALIGN, Data Delay Control and External PLL Enabled Interface.</li> </ul> </li> <li>Signal Description:         <ul> <li>Table 2.3. GDDR 7:1 I/O Module Receive Signal Description: newly added eclk_i, pll_lock_i, phasedir_o, phasestep_o, phaseloadreg_o, and phasesel_o signals and their related data.</li> </ul> </li> <li>Attribute Summary:         <ul> <li>Table 2.5. Attributes Table: newly added <i>Use External PLL, External PLL Reference Clock and Primary Clock Output Frequency</i>, and External PLL Secondary Clock Output Frequency attributes and their related data.</li> <li>Table 2.6. Attributes Description: newly added <i>Use External PLL, External PLL Reference Clock and Primary Clock Output Frequency</i>, and External PLL Secondary Clock Output Frequency attributes and their related description.</li> </ul> </li> </ul> |  |  |  |

| IP Generation, Simulation, and | Updated Figure 3.1. Module/IP Block Wizard, Figure 3.2. Configure Block of GDDR 7:1 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Validation                     | Module, Figure 3.3. Check Generated Result reflecting the most recent Lattice Radiant software user interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Technical Support Assistance   | Added the Frequently Asked Questions website link.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

### Revision 1.6, October 2022

| Section                                   | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functional Diagrams                       | <ul> <li>Updated Figure 2.16. Rx Output Data Mapping.</li> <li>Updated from "The entire input data is broken down into four groups, each group with the size of 7 bits. The group with the fastest bits [24, 20, 16, 12, 8, 4, 0] is transmitted first, and so on." to "The entire input data is broken down into 7 groups, each group with the size of 4 bits. The group with the fastest bits data_i[3:0] is transmitted first, followed by data_i[7:4] and so on." in TX Input Data Mapping section.</li> <li>Added user interface signals in Signal Description section.</li> </ul> |

|                                           | Updated Selectable values in Attribute Summary section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IP Generation, Simulation, and Validation | Updated the heading of Section 3 from "IP Generation and Evaluation" to "IP Generation, Simulation, and Validation".                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                           | Removed "Licensing the IP" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           | Updated the heading of Section 3.1 from "Generation and Synthesis" to "Generating the IP".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                           | • Updated Figure 3.1. Module/IP Block Wizard, Figure 3.2. Configure Block of GDDR 7:1 I/O Module, Figure 3.3. Check Generated Result.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                           | Updated the heading of Section 3.3 from "Hardware Evaluation" to "IP Evaluation".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# Revision 1.5, December 2021

| Section                          | Change Summary                                             |

|----------------------------------|------------------------------------------------------------|

| Appendix A. Resource Utilization | Updated section content including adding table for LFCPNX. |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Revision 1.4, June 2021

| Section                          | Change Summary                                                                                                                                                                                                                 |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Introduction                     | <ul> <li>Revised introductory paragraph.</li> <li>Removed Quick Facts section.</li> </ul>                                                                                                                                      |  |  |

| IP Generation and Evaluation     | <ul> <li>Revised reference to Lattice Radiant Software User Guide and removed link.</li> <li>Updated the procedures/user interfaces in the Generation and Synthesis and the Running Functional Simulation sections.</li> </ul> |  |  |

| Appendix A. Resource Utilization | Added this section.                                                                                                                                                                                                            |  |  |

| References                       | Revised reference to Lattice Radiant Software User Guide and removed link.                                                                                                                                                     |  |  |

### Revision 1.2, June 2020

| Section                | Change Summary                                                 |  |  |

|------------------------|----------------------------------------------------------------|--|--|

| Introduction           | Added Certus-NX support.                                       |  |  |

|                        | Updated Table 1.1 to add LFD2NX-40 as targeted device.         |  |  |

|                        | Updated Lattice Implementation to Lattice Radiant 2.1.         |  |  |

| Functional Description | Added the GDDRX71_RX Word Alignment Function.                  |  |  |

| All                    | Updated references to Lattice Radiant Software 2.1 User Guide. |  |  |

# Revision 1.1, February 2020

| Section                      | Change Summary                                           |

|------------------------------|----------------------------------------------------------|

| Acronyms in this Document    | Updated the table.                                       |

| Introduction                 | Updated Table 1.1 to add LIFCL-17 as targeted device.    |

| Functional Description       | Updated Figure 2.7.                                      |

| IP Generation and Evaluation | Updated content of the Generation and Synthesis section. |