# Lattice sensAl Neural Network Compiler Software

# **User Guide**

FPGA-UG-02052-8.0

December 2025

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING PROVIDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| Conte        | nts                                           |    |

|--------------|-----------------------------------------------|----|

| Abbre        | eviations in This Document                    | 8  |

| 1. Ir        | ntroduction                                   |    |

| 1.1.         | . Prerequisites                               |    |

| 1.2.         | . Purpose                                     | 10 |

| 1.3.         | . Limitations                                 | 10 |

| 2. Ir        | nstalling the Software                        |    |

|              | Getting Started                               |    |

| 3.1.         | -                                             |    |

| 3.2.         | •                                             |    |

| 3.3.         |                                               |    |

| 3.4.         | •                                             |    |

| 3.5.         | •                                             |    |

| 3.6.         | •                                             |    |

| 3.7.         |                                               |    |

| 3.8.         |                                               |    |

|              | Norking with Projects                         |    |

| 4.1.         |                                               |    |

| 4.2.         | •                                             |    |

| 4.3.         | •                                             |    |

| 4.4.         |                                               |    |

|              | Advanced Topics                               |    |

| 5.1.         | •                                             |    |

| 5.2.         |                                               |    |

| 5.3.         |                                               |    |

| 5.4.         | ·                                             |    |

|              | Supported Frameworks                          |    |

| 6.1.         | ··                                            |    |

| 6.2.         |                                               |    |

| 6.3.         |                                               |    |

|              | SB Debugging                                  |    |

| 7. 3<br>7.1. |                                               |    |

| 7.1.<br>7.2. | 5                                             |    |

| 7.2.<br>7.3. | ·                                             |    |

| 7.3.<br>7.4. |                                               |    |

|              |                                               |    |

| 7.5.         |                                               |    |

| 7.6.         | · · · · · · · · · · · · · · · · · · ·         |    |

|              | RISC-V Register Interface Generator           |    |

| 8.1          | · · · · · · · · · · · · · · · · · · ·         |    |

| 8.2.         |                                               |    |

|              | ndix A. Supported Keras Layers                |    |

|              | ndix B. Supported Layer Configuration         |    |

|              | ndix C. Supported TensorFlow Operations       |    |

|              | ndix D. USB Debugging Register Map            |    |

|              | ndix E. Supported ONNX Layers                 |    |

|              | ndix F. Network Topology and Device Table     |    |

|              | ndix G. Common CNN Blocks Used in Lattice NNC |    |

|              | ences                                         |    |

|              | ical Support Assistance                       |    |

| Kevisi       | on History                                    |    |

# **Figures**

| Figure 2.1. Installation Location Specification                                | 11 |

|--------------------------------------------------------------------------------|----|

| Figure 2.2. Installation Component Specification                               |    |

| Figure 2.3. Installation Ready to Install Dialog Box                           | 12 |

| Figure 2.4. Lattice Neural Network Compiler Software for Windows Splash Screen | 13 |

| Figure 3.1. Project Settings Window                                            | 14 |

| Figure 3.2. Example cmd for Post Processing                                    | 14 |

| Figure 3.3. Proto File Selection Window                                        | 15 |

| Figure 3.4. Project Implementation Options Window                              | 16 |

| Figure 3.5 Project Implementation Window 2 (Only for Advanced IP)              |    |

| Figure 3.6. Project Window                                                     |    |

| Figure 3.7. Load Project Window                                                |    |

| Figure 3.8. Python Code for Raw Input                                          |    |

| Figure 3.9. Multiple Input Selection Window                                    |    |

| Figure 4.1. Project Implementation Options Window                              |    |

| Figure 4.2. Analyze Results                                                    |    |

| Figure 4.3. Compile Results                                                    |    |

| Figure 4.4. Simulate Results                                                   |    |

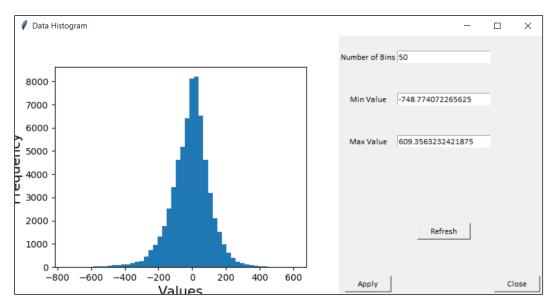

| Figure 4.5. Data Histogram for the Blob                                        |    |

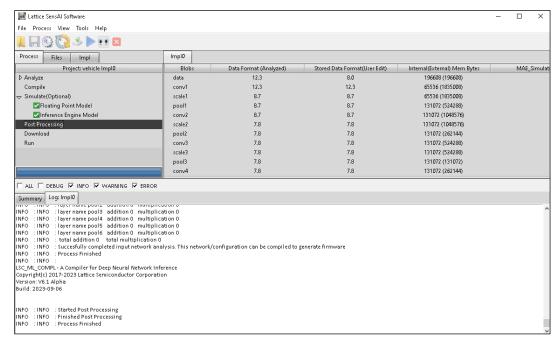

| Figure 4.6. Post Processing                                                    |    |

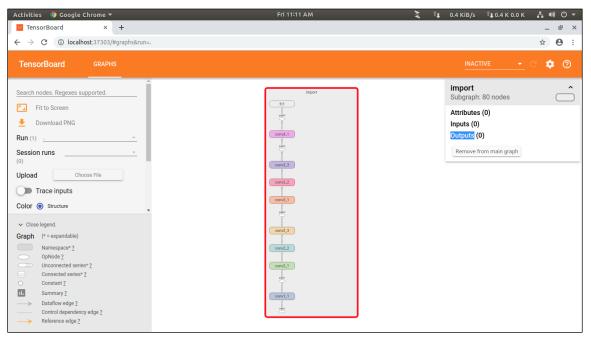

| Figure 4.7. Input Network – TensorFlow or Keras                                |    |

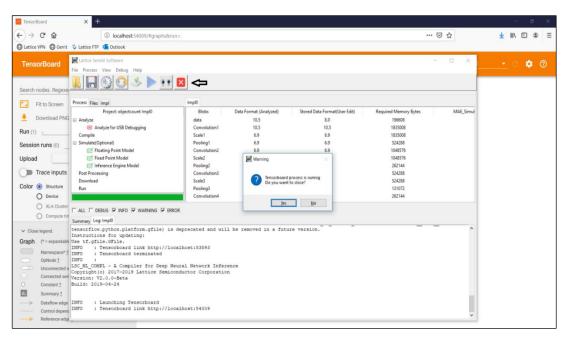

| Figure 4.8. Close Tensorboard Process                                          |    |

| Figure 4.9. GUI Themes                                                         |    |

| Figure 4.10. HTML Log                                                          |    |

| Figure 4.11. Default View of HTML log                                          |    |

| Figure 4.12. Search Functionality of Warning                                   |    |

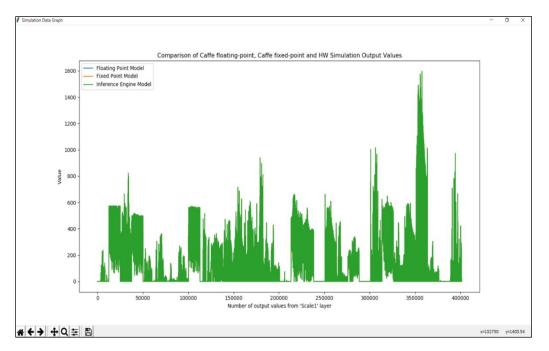

| Figure 4.13. Simulation Data Graph                                             |    |

| Figure 5.1. Project Implementation Window – ECP5                               |    |

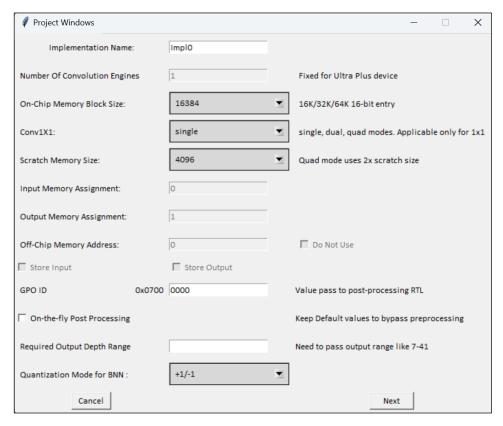

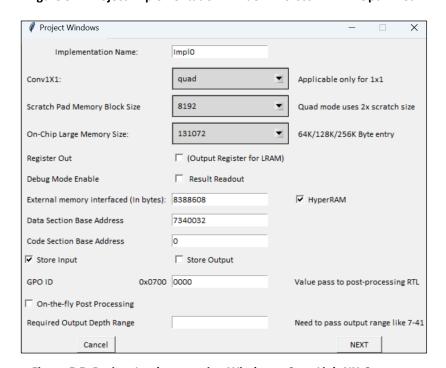

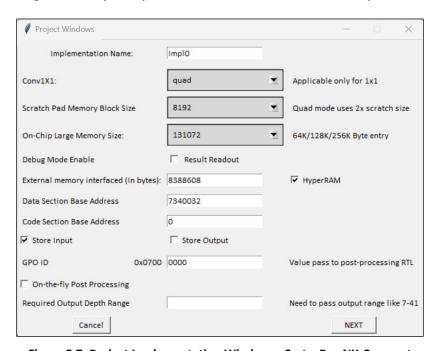

| Figure 5.2. Project Implementation Window – UltraPlus (1)                      |    |

| Figure 5.3. Project Implementation Window – UltraPlus (2)                      |    |

| Figure 5.4. Project Implementation Window – CrossLink-NX-Optimized             |    |

| Figure 5.5. Project Implementation Window – CrossLink-NX-Compact               |    |

| Figure 5.6. Project Implementation Window – CertusPro-NX-Optimized             |    |

| Figure 5.7. Project Implementation Window – CertusPro-NX-Compact               |    |

| Figure 5.8. Project Implementation Window – CertusPro-NX-Extended              |    |

| Figure 5.9 Project Implementation Window – CertusPro-NX Advanced IP Part 1     |    |

| Figure 5.10 Project Implementation Window – CertusPro-NX Advanced IP Part 2    |    |

| Figure 5.11 Project Implementation Window – CertusPro-IVX Advanced IP Part 1   |    |

| Figure 5.12 Project Implementation Window – Avant Advanced IP Part 2           |    |

| Figure 5.13. On-the-Fly Post Processing Format                                 |    |

| Figure 5.14. On-the-Fly Post Processing Pornat                                 |    |

| ·                                                                              |    |

| Figure 5.15. Create Quantized Version Flag                                     |    |

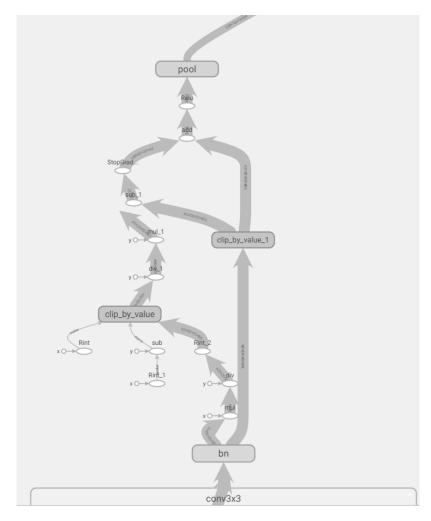

| Figure 5.16. Tensor Graph Quantization Nodes                                   |    |

| Figure 5.17. Activation Data Quantization Nodes                                |    |

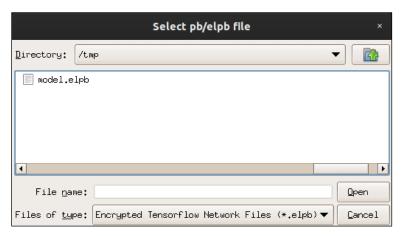

| Figure 5.18. SensAl Security Flow: Encrypt Model                               |    |

| Figure 5.19. SensAl Security Flow: Encrypted Model Selection                   |    |

| Figure 5.20. SensAl Security Flow: Encrypt Model                               |    |

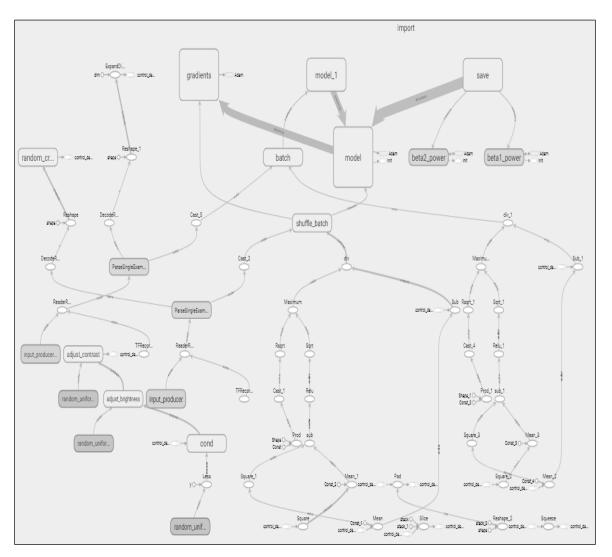

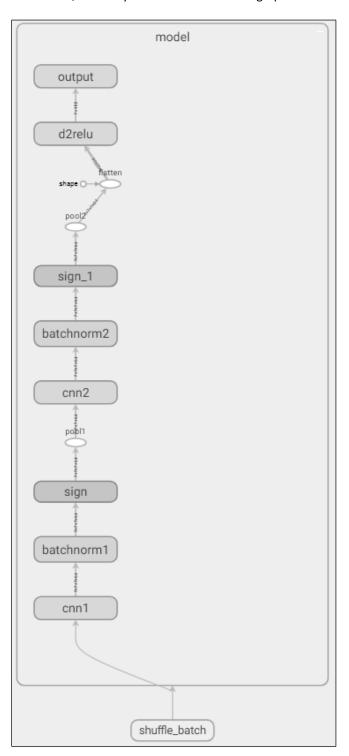

| Figure 6.1. Original TensorFlow Training Model                                 |    |

| Figure 6.2. Simplified TensorFlow Inference Model                              |    |

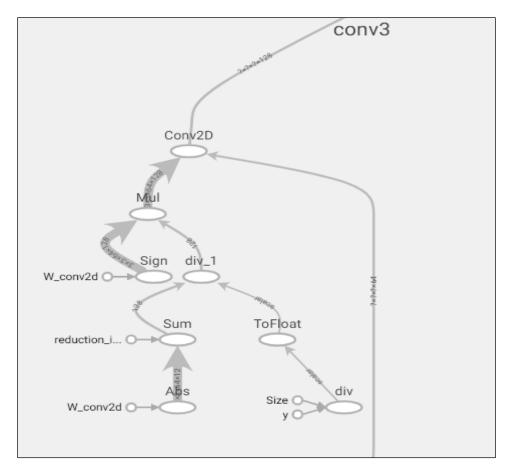

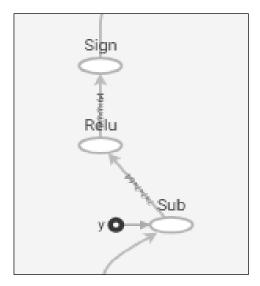

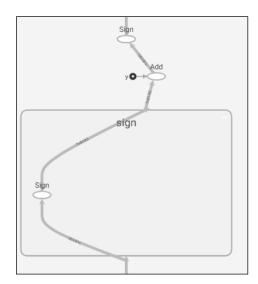

| Figure 6.3. Tensorboard Visualization of Binarization                          |    |

| Figure 6.4. Binary Neural Network Modes in TensorFlow                          |    |

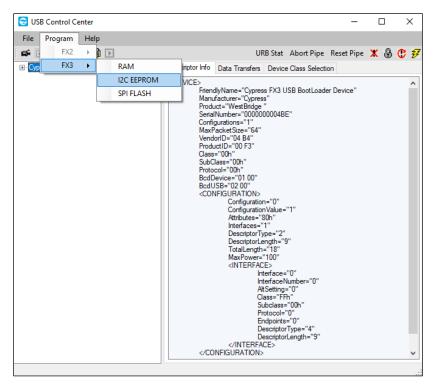

| Figure 7.1. Cypress Window                                                     | 83 |

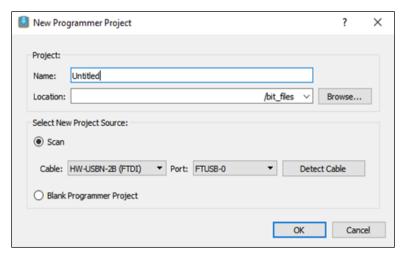

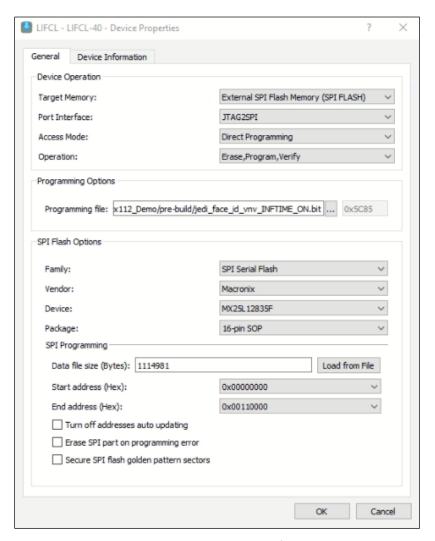

| Figure 7.2. Radiant Programmer – Default Screen            | 84  |

|------------------------------------------------------------|-----|

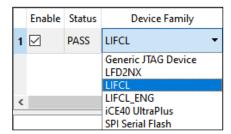

| Figure 7.3. Radiant Programmer Device Selection            |     |

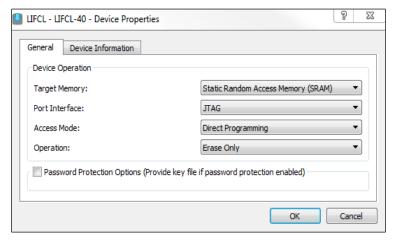

| Figure 7.4. Radiant Programmer – Device Operation          | 84  |

| Figure 7.5. Selecting Device Properties for CrossLink-NX   |     |

| Figure 7.6. Output Console after Successful Flashing       |     |

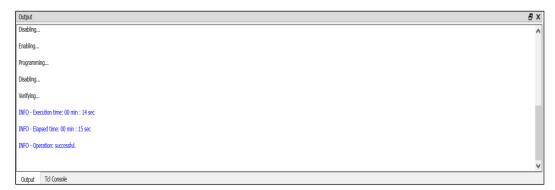

| Figure 7.7 Avant Board with FX3 USB Board                  |     |

| Figure 7.8. USB Debug Window                               |     |

| Figure 7.9. USB3-GigE VIP Board Label                      |     |

| Figure 7.10. CNX-VnV Board Label                           |     |

| Figure 7.11. CPNX-VnV Board Label                          |     |

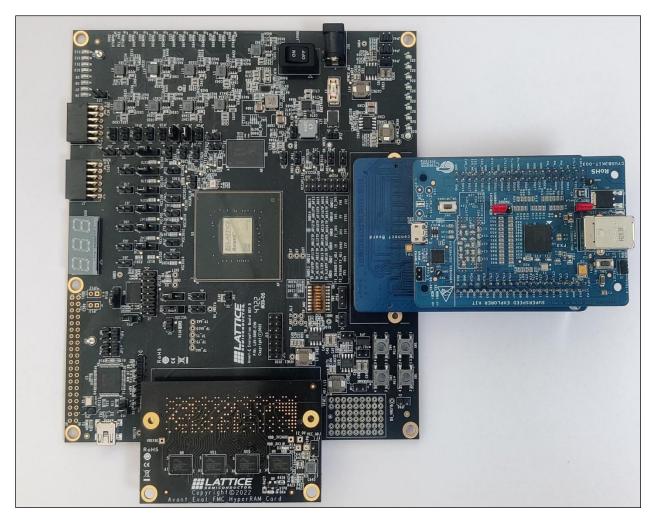

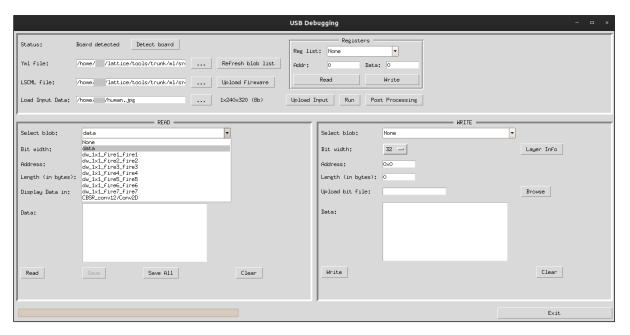

| Figure 7.12. USB Debug Window                              |     |

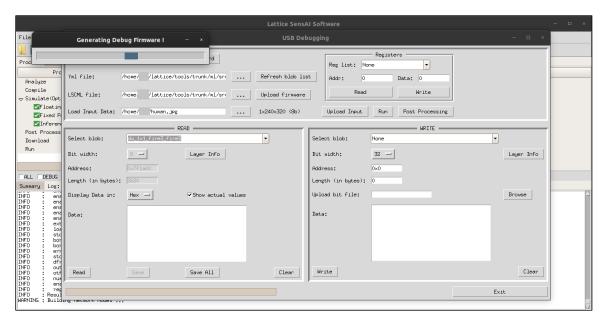

| Figure 7.13. USB Debug Firmware Generation                 |     |

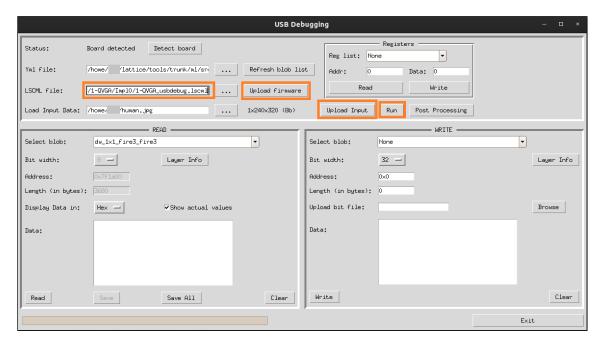

| Figure 7.14. Upload FW, Input and Run USB-Debugging        |     |

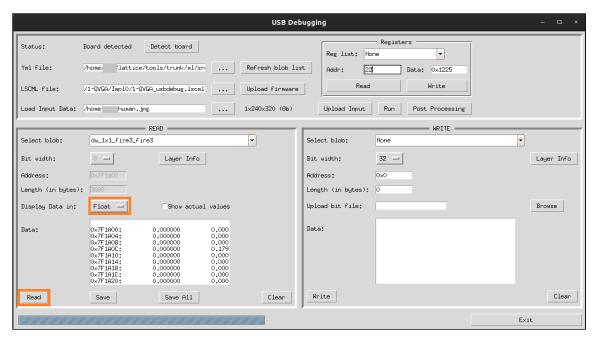

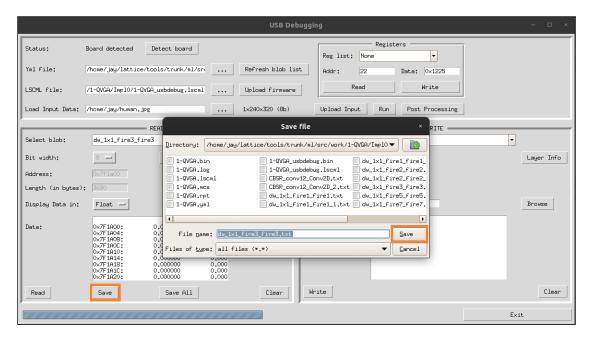

| Figure 7.15. Read USB Data with Blob Selected              |     |

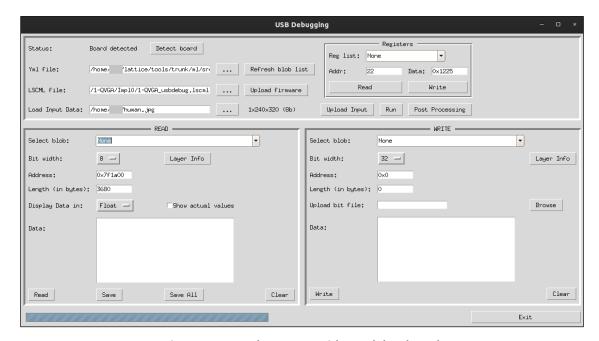

| Figure 7.16. Read USB Data without Blob Selected           |     |

| Figure 7.17. Save USB Data                                 |     |

| Figure 7.18. Expected Values for Corresponding Blob        |     |

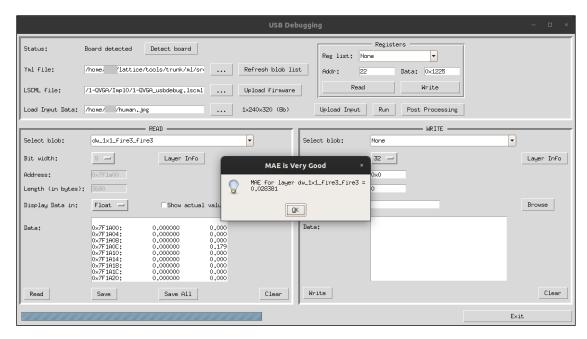

| Figure 7.19. Show Expected vs HW MAE                       |     |

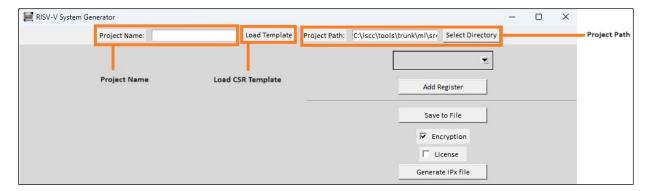

| Figure 8.1. Opening the RISC-V System Generator            |     |

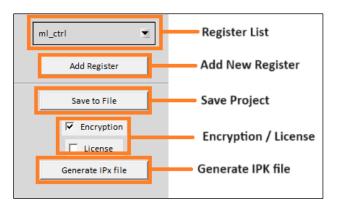

| Figure 8.2. System Generator Home Window                   |     |

| Figure 8.3. System Generator Functions                     |     |

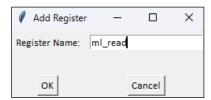

| Figure 8.4. System Generator Add New Register              | 99  |

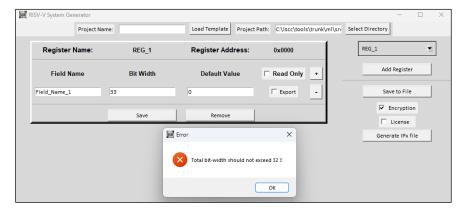

| Figure 8.5. System Generator Add and Remove Register Field | 100 |

| Figure 8.6. System Generator Register Bit Width Limitation | 100 |

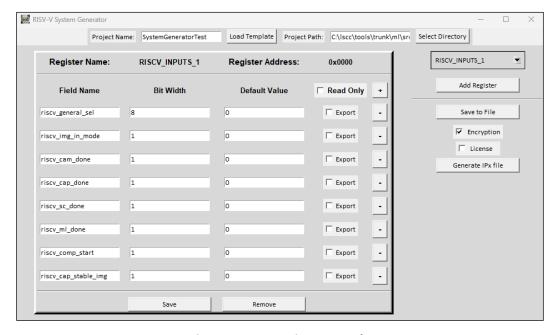

| Figure 8.7. System Generator Example CSR Template          |     |

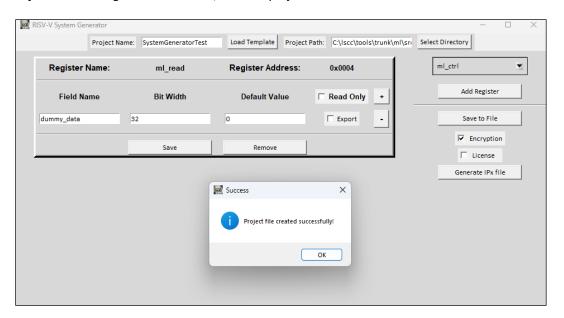

| Figure 8.8. CSR Register Example                           |     |

| Figure 8.9. System Generator Save Project                  |     |

| Figure 8.10. System Generator Generate IPK File            |     |

| Figure B.1. Sigmoid Function                               |     |

| Figure B.2. Strided Slice Example                          |     |

| Figure C.1. Batch Normalization                            |     |

| Figure C.2. Unpool Implementation                          |     |

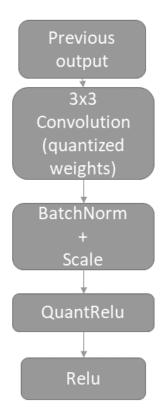

| Figure H.1. Non-Quantized 3x3 CBSR or 3x3 Depthwise CBSR   |     |

| Figure H.2. Quantized 3x3 CBSR or 3x3 Depthwise CBSR       |     |

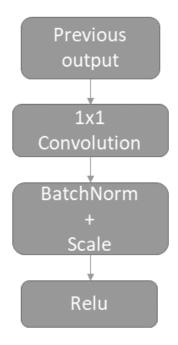

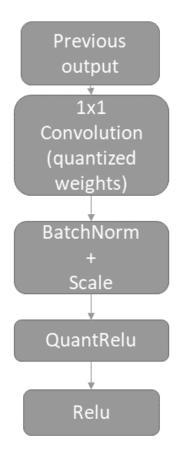

| Figure H.3. Non-Quantized 1x1 CBSR                         |     |

| Figure H.4. Quantized 1x1 CBSR                             |     |

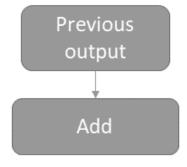

| Figure H.5. Non-Quantized Add Block                        |     |

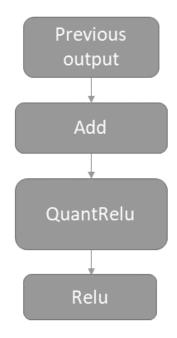

| Figure H.6. Quantized Add Block                            |     |

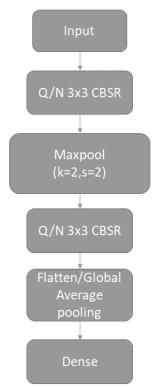

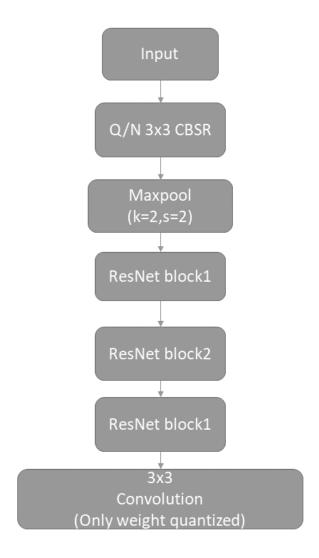

| Figure H.7. VGG toy model                                  |     |

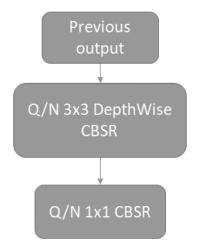

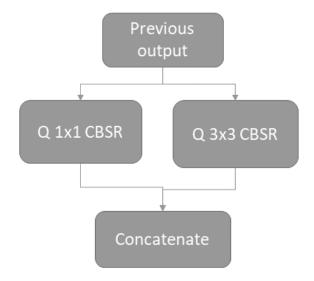

| Figure H.8. MobileNetV1 Block                              |     |

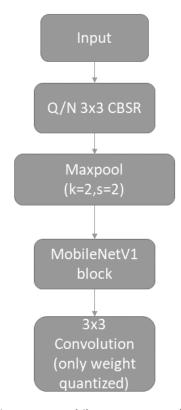

| Figure H.9. MobileNetV1 Toy Model                          |     |

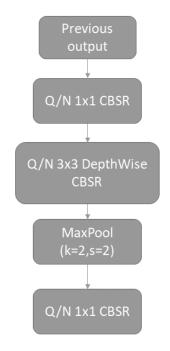

| Figure H.10. MobileNetV2 Block 1                           |     |

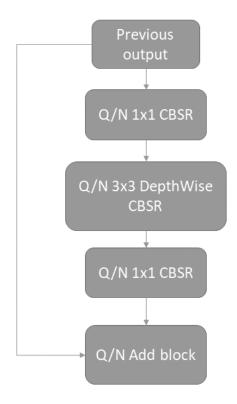

| Figure H.11. MobileNetV2 Block 2                           |     |

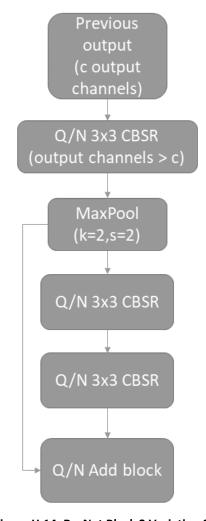

| Figure H.12. ResNet Toy Model                              |     |

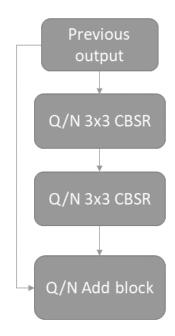

| Figure H.13. ResNet Block 2 Variation 1                    |     |

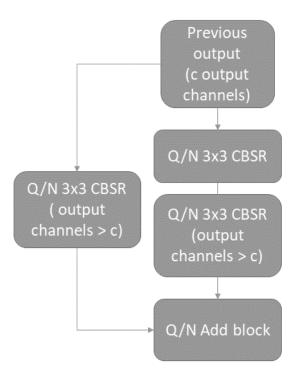

| Figure H.14. ResNet Block 2 Variation 2                    |     |

| Figure H.15. ResNet Block 2 Variation 3                    |     |

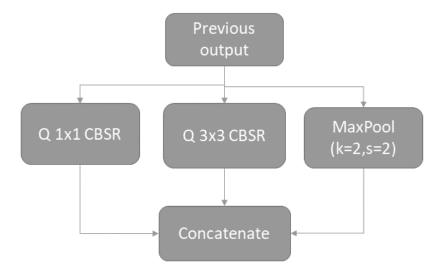

| Figure H.16. GoogleNet Inception Block 1                   |     |

| Figure H.17. GoogleNet Inception Block 2                   |     |

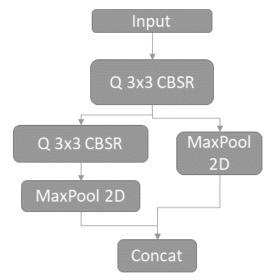

| Figure H.18. Init Block                                    |     |

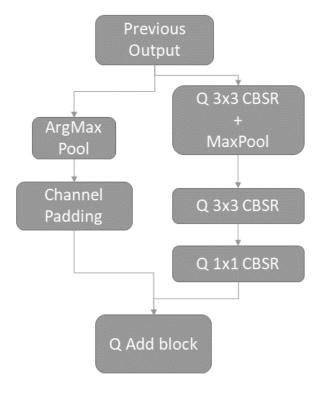

| Figure H.19. DownSample Block                              |     |

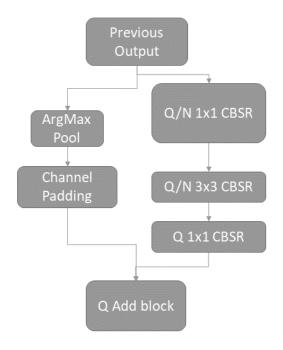

| Figure H.20. Regular Block                                 | 125 |

|                                                            |     |

6

# **Tables**

| Table 3.1. Arguments and Usage                                    | 20  |

|-------------------------------------------------------------------|-----|

| Table 5.1. Learned Step Quantization Details with Device Type     | 61  |

| Table 5.2. Unsigned 8-Bit Quantization (Fixed Point Quantization) | 63  |

| Table 5.3. Signed 8-Bit Quantization (Fixed Point Quantization)   | 63  |

| Table 5.4. Fixed Point Quantization Details with Device Type      | 63  |

| Table 5.5 Quantization Support in Layers                          | 64  |

| Table 5.6. SensAl Security Flow: File Extension Mapping           | 70  |

| Table B.1. Supported Layer Configuration                          | 106 |

| Table E.1. USB Debugging Register Map                             | 111 |

| Table F.1. Network Topology and Device                            | 113 |

| Table G.1. Enet Example Architecture                              | 126 |

# **Abbreviations in This Document**

A list of abbreviations used in this document.

| Abbreviation | Definition                                 |

|--------------|--------------------------------------------|

| BNN          | Binarized Neural Networks                  |

| CLI          | Command Line Interface                     |

| CNN          | Convolutional Neural Network               |

| CNX          | CrossLink-NX                               |

| CPNX         | Certus-Pro-NX                              |

| CSR          | Control and Status Register                |

| DRAM         | Dynamic Random Access Memory               |

| FC           | Fully Connected                            |

| FPQ          | Fixed Point Quantization                   |

| FPS          | Frames Per Second                          |

| GUI          | Graphic User Interface                     |

| HRAM         | Hyper Random-Access Memory                 |

| IP           | Intellectual Property                      |

| LRAM         | Large Random-Access Memory                 |

| LSQ          | Learned Step Quantization                  |

| LUT          | Lookup Table                               |

| ML           | Machine Learning                           |

| NCHW         | Number of Samples, Channels, Height, Width |

| NNC          | Lattice Neural Network Compiler tool       |

| ONNX         | Open Neural Network Exchange               |

| PTQ          | Post Training Quantization                 |

| RAM          | Random Access Memory                       |

| ReLU         | Rectified Linear Unit                      |

| RTL          | Register Transfer Level                    |

| TCL          | Tool Command Language                      |

| USB          | Universal Serial Bus                       |

# 1. Introduction

This document describes the usage and troubleshooting of Lattice Neural Network Compiler software.

## 1.1. Prerequisites

The hardware, software, connection, and general requirements for this demonstration are provided in the following sections.

#### 1.1.1. Hardware Requirements

The software requires the following hardware components:

- PC with either Windows 10 x64 or newer; or PC with compatible Ubuntu x64 distribution for running software flow only.

- Lattice Inference Machine-compatible FPGA.

## 1.1.2. Software Requirements

This software product requires the following software components:

- Lattice Neural Network Compiler Software for Windows or Linux.

- Diamond Programmer System software for downloading the FPGA bitstream.

- Lattice Diamond™ design software for modifying the platform and regenerating the bitstream.

- Radiant Programmer System software for downloading FPGA bitstream.

- Lattice Radiant™ design software for modifying the platform and regenerating the bitstream.

#### 1.1.3. Connection Requirements

Programming the device and running Lattice Neural Network Compiler Software directly from the GUI requires a Windows installation and a Windows-compatible connection, such as the USB driver for Lattice FPGA development boards.

#### 1.1.4. General Requirements

This document requires knowledge of the following:

- Familiarity with TensorFlow or Keras machine learning frameworks.

- Familiarity with Lattice FPGA development, including basic concepts and troubleshooting skills, as well as

experience establishing connectivity between the device and computer or using other hardware (such as an SD

card) for transfer data to the target hardware.

#### 1.1.5. IP Requirements

- Neural Network Compiler 8.0 supports IP cores for the ECP5, iCE40 UltraPlus, CrossLink-NX, CertusPro-NX, and Lattice Avant device families.

- For ECP5, use CNN Accelerator IP Core v2.1.

- For iCE40 UltraPlus, use Compact CNN Accelerator IP Core v2.0.0.

- For CrossLink-NX, use Crosslink-NX CNN Accelerator IP Core v3.0.

- For CertusPro-NX, use CertusPro-NX CNN Accelerator IP Core v3.0.

- For Lattice Avant, use Advanced CNN Accelerator IP Core v3.0.

- IP cores from previous releases may not work with this version. Ensure you use the versions provided by Lattice for Neural Network Compiler 8.0.

# 1.2. Purpose

This application shows the ability and features of Lattice Neural Network Compiler Software to:

- Analyze and compile a neural network for use with selected Lattice Semiconductor FPGA products.

- Simulate hardware to obtain expected fixed and floating-point output.

- Download and run neural networks directly on hardware via USB debugging.

- Manage multiple implementations per project to view the effects of different strategies.

## 1.3. Limitations

The following cautions apply to the software as a whole:

- Operations are conducted in fixed point notation on the hardware as a result of floating-point values being converted to and from fixed point representation.

- Specific neural network features, such as layers or functions, require certain configurations to function or may not be supported.

# 2. Installing the Software

The demonstration package of the Lattice Neural Network Compiler Software is available as an executable installer for Windows and Linux. Install the software on Windows using the Machine Learning Software Setup executable (.exe) or on Ubuntu Linux using the run file (.run). Launch the installation process and customize the options as detailed in this section.

To install the Lattice Neural Network Compiler Software:

- 1. Close all applications before starting the Lattice Neural Network Compiler Software installation.

- 2. Double-click the Lattice Neural Network Compiler Software installer you downloaded.

- 3. The Welcome to Lattice Machine Learning Software 8.0 Software Setup dialog box opens.

- 4. Click **Next** to select the installation folder.

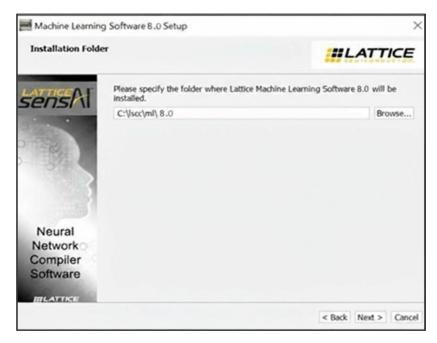

- 5. On Windows, the default destination folder is C:\lscc\ml\8.0; on Linux, it is ~/lscc/ml/8.0. Click **Browse** to change the destination (see Figure 2.1).

Figure 2.1. Installation Location Specification

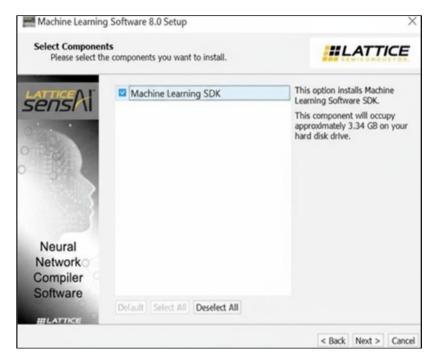

- 6. Click **Next** to open the Product Options dialog box (see Figure 2.2).

- 7. Select the Machine Learning Software components you want to install by checking or clearing the listed options.

Figure 2.2. Installation Component Specification

- 8. Click **Next** to open the License Agreement dialog box.

- 9. Read the license agreement. If you agree, click I accept the license to open the Start Menu shortcuts dialog box.

- 10. Click **Next** to open the Select Program Folder dialog box. The default name is Lattice Machine Learning Software 8.0. If you want to change the name, enter it in the Program Folder text box.

- 11. Click **Next** to display the Ready to Install dialog box (Figure 2.3). Review the current settings, including the destination folder and selected components. If everything is correct, select **Install** to start the installation.

Figure 2.3. Installation Ready to Install Dialog Box

- 12. In the Installation Wizard Complete dialog box, read the confirmation note and click Finish.

- 13. Run the executable either by using the desktop shortcut or Start menu shortcut, if created, or by navigating to your installation directory and running **lsc\_ml\_compl.exe** on Windows or **lsc\_ml\_compl** on Ubuntu Linux. You can then see the main window, as shown in Figure 2.4.

Figure 2.4. Lattice Neural Network Compiler Software for Windows Splash Screen

14. The installed software is now ready for use.

# 3. Getting Started

In this chapter, you can learn how to use Lattice Neural Network Compiler Software to create new projects and edit existing projects.

## 3.1. Creating a New Project

A project is a collection of all the files necessary to create and download your design to the selected device. The New Project window guides you through the steps of specifying a project name and adding existing sources to the new project.

To create a new project:

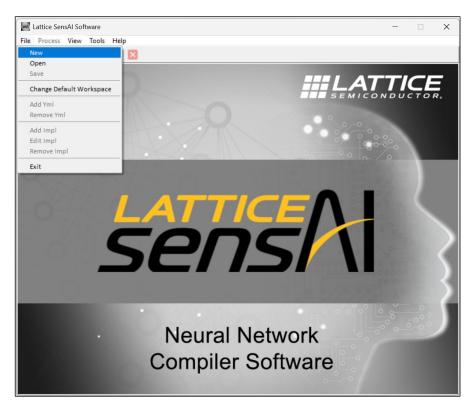

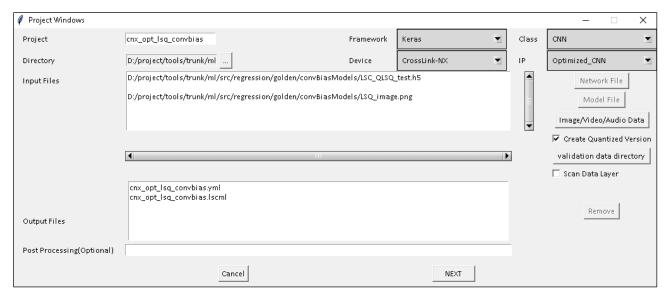

1. From the main window, click File > New. The Project Settings window opens, as shown in Figure 3.1.

Figure 3.1. Project Settings Window

- 2. Enter a project name in the Project field at the top-left.

- 3. Select a framework for your design. Currently, sensAl™ supports TensorFlow, Keras, and ONNX (experimental).

- 4. Select the device you intend to run this network on.

- 5. Enter an optional post-processing command. Post-processing commands use the following format:

python test.py [<script-arg1> <script-arg2> ... ] <input-data-file> <simulation-npy-datafile>

Figure 3.2. Example cmd for Post Processing

The input-data-file and simulation-npy-data-file arguments displayed in the angle brackets are added by the sensAl tool in this command.

The script-arg parameters displayed in square brackets [] are script-dependent arguments.

- 1. Select a class for your network. SensAl supports Convolution Neural Network (CNN) and Binary Neural Network (BNN).

- 2. Select the MOBILENET mode checkbox if you want to use a model with the Mobilenet IP for ECP5 devices using the CNN class. See the Advanced Topics section for more information on Mobilenet mode. Similarly, select Compact mode, Optimized mode, or Extended mode from the drop-down list if you want to use a model for the respective IPs of the CrossLink-NX device and the CertusPro-NX device.

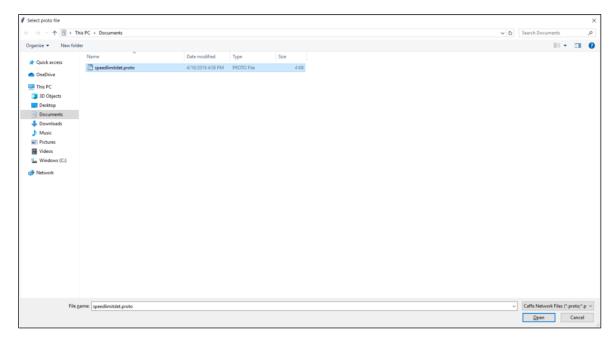

- 3. Click Network File. The Proto File Selection window opens, as shown in Figure 3.3.

Figure 3.3. Proto File Selection Window

- 4. Navigate to your proto file and select it in the window.

- 5. Click **Open** to load the proto file into your project.

- 6. Click Model File and follow a similar process to steps 3-5, selecting your model file this time.

- 7. Click Image/Video Data and follow a similar process to steps 3-5, this time selecting your image or video file. You can check Scan Data Layer to let the software attempt to locate your data file if it is defined in your network.

- 8. Click **Next** to open the Project Implementation Options window, as shown in Figure 3.4.

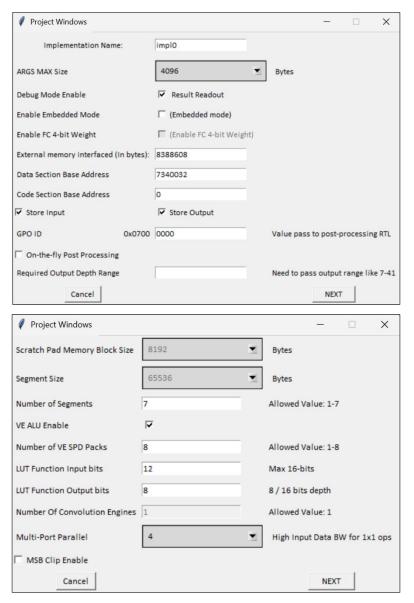

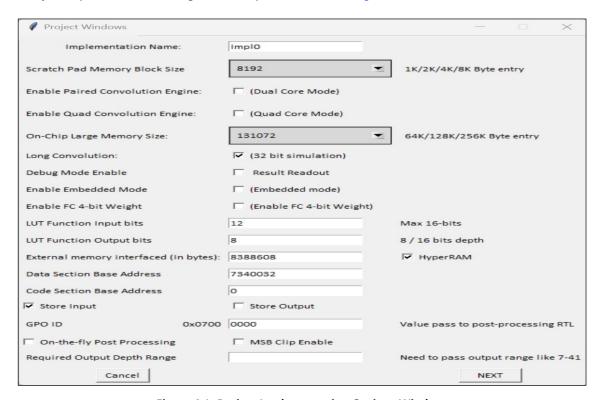

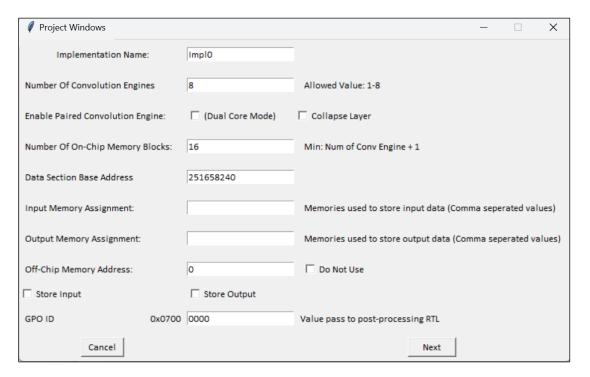

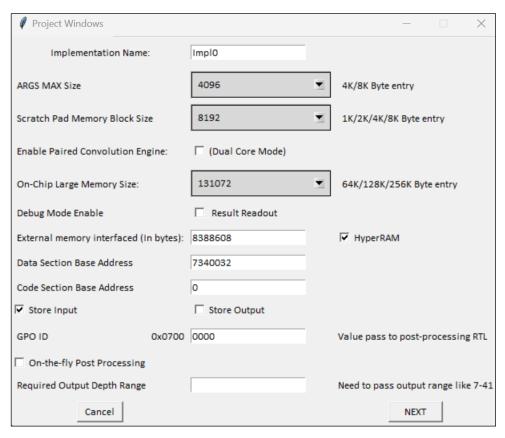

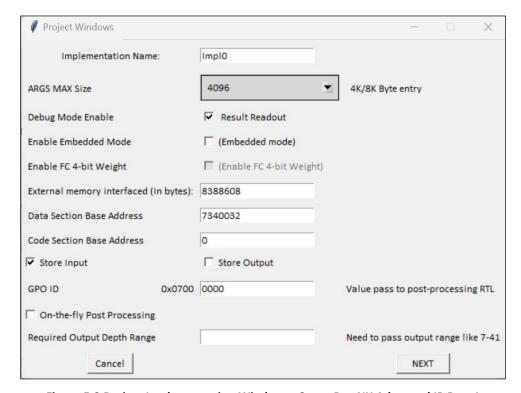

Figure 3.4. Project Implementation Options Window

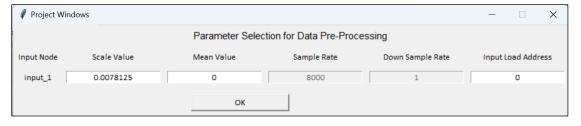

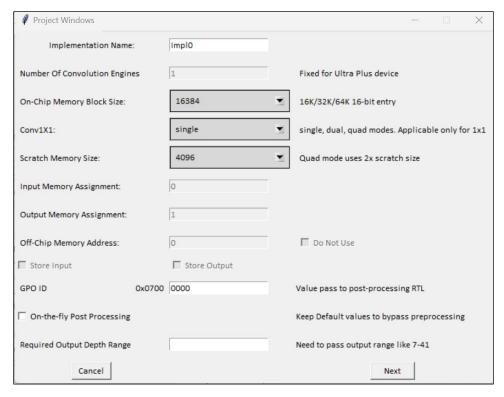

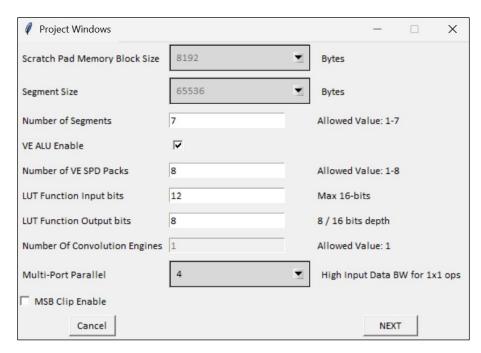

Figure 3.5 Project Implementation Window 2 (Only for Advanced IP)

- 9. The Project Implementation window is automatically filled with default settings for the Implementation Name, as well as the parameters. You can change the name and parameters if desired. For more information on how each parameter works and their limitations, read the Project Implementation Settings section.

- 10. Click **Ok** to create your project. The Project Window opens, as shown in Figure 3.6.

Figure 3.6. Project Window

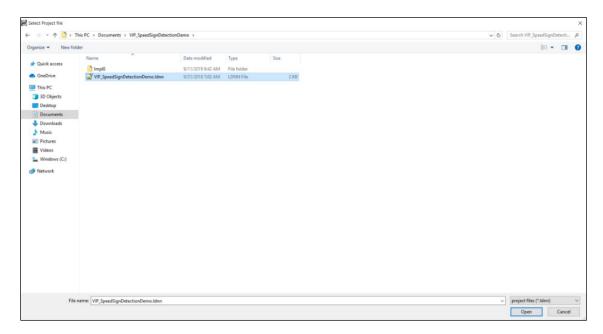

# 3.2. Opening an Existing Project

- 1. Use one of the following methods to open an existing Lattice Neural Network Compiler Software project:

- In the Main Window, click the Open Project button.

- From the **File** menu, choose **Open**.

The Open Project Window opens, as shown in Figure 3.7.

Figure 3.7. Load Project Window

- 2. Navigate to an existing LDNN type file and select it.

- 3. Click Open to open the project.

## 3.3. Saving a Project

When working on a project you want to save, click on the floppy disk icon or navigate to **File > Save** in order to save your project. This can save the files with the project name into the project directory, as specified in your project settings.

# 3.4. Inputs

In addition to images, sensAl supports other types of input data as well.

#### 3.4.1. Audio Input

The tool only accepts .wav files with a minimum length of 1 second. There is no preprocessing performed on audio input as of version 7.0.

#### **3.4.2.** Raw Input

By enabling the **Raw Input** option when creating a new project, you can pass input data in the form of .npy array. The array size should match exactly with the inputs in the network. This is because the array is directly fed to the network without performing any preprocessing. For example, mean and scale are not used on raw input data. Preprocessing can be performed in Python and then passed as a saved numpy array to sensAI.

To save an array, A, in a file, raw\_input.npy, it only requires two lines of Python code, as shown in Figure 3.8.

```

import numpy as np

np.save("raw_input.npy",A)

```

Figure 3.8. Python Code for Raw Input

**Note**: For image input as raw input, the data must be in BGR format.

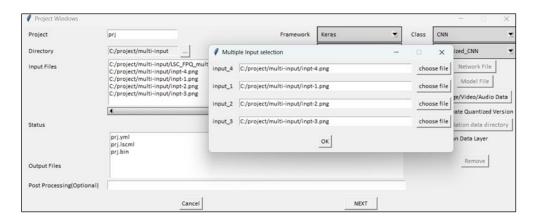

#### 3.4.3. Multiple Input Selection

The tool automatically detects if the model has multiple inputs. Select the image or raw input according to the model inputs. Model input names are displayed so you can select the input files accordingly. Figure 3.9 shows the input selection window.

Figure 3.9. Multiple Input Selection Window

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

## 3.5. Help

For more software help, the **Help** menu contains links to relevant help topics.

#### 3.5.1. About

To find out more versions and license information, navigate to **Help > About** to bring up the About window, which has tabs for different software information sections. The **About** tab contains information about the software. Your current version and build number are displayed here. The **License** tab provides a convenient way to view the license agreement.

#### 3.5.2. User Guide

This user guide is routinely updated and may not be the latest version. To quickly go to the Lattice Semiconductor web page, which contains the latest version of the User Guide as well as supplemental material, navigate to **Help > User Guide**, and you will be taken to the correct page.

#### 3.6. Command Line Interface

The executable can be used from a command line interface if you prefer not to use the GUI. To execute a command, launch the executable from the command line and pass it the arguments you wish to use.

For example, to bring up the help Windows CLI in Cygwin, the command is:

lsc\_ml\_compl.exe --help

While on Linux, execute it as:

./lsc\_ml\_compl --help

This brings up the help menu for the CLI. You can see the usage and arguments in the following sections of this chapter.

#### 3.6.1. Arguments and Usage

Table 3.1. Arguments and Usage

| Argument                                                | Description                                                                                                                                                                                              |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| h,help                                                  | Show this help message and exit                                                                                                                                                                          |

| cryptography                                            | To run encryption/decryption flow                                                                                                                                                                        |

| input_file_path                                         | Input model path that user wants to Encrypt/Decrypt                                                                                                                                                      |

| input_file_path                                         | Output model path to store encrypted/decrypted model                                                                                                                                                     |

| password                                                | Password to perform encryption/decryption                                                                                                                                                                |

| mode                                                    | To select mode from encrypt/decrypt                                                                                                                                                                      |

| gui [GUI]                                               | Invoke GUI tool                                                                                                                                                                                          |

| cmd [CMD]                                               | Valid commands are analyze, compile, simulate, download, run, and all                                                                                                                                    |

| framework {TensorFlow,Keras,ONNX}                       | Framework used to train the network. Currently TensorFlow, Keras, and ONNX are supported. The support for Caffe has been removed.                                                                        |

| network_file NETWORK_FILE                               | <ul><li>TensorFlow .pb file</li><li>Keras .h5 file</li><li>ONNX .onnx file</li></ul>                                                                                                                     |

| image_files IMAGE_FILES                                 | .jpg Image file                                                                                                                                                                                          |

| num_conv_eng NUM_CONV_ENG                               | Number of convolution engines used. Only for CPNX and AVANT devices with Advanced CNN IP $4*N$ number of output channels are getting generated in parallel. N = 1 for CPNX and N = 1-4 for AVANT devices |

| num_ebr NUM_EBR                                         | Number of embedded block ram.                                                                                                                                                                            |

| ebr_blk_size {16384,32768,65536}                        | Size of each embedded block ram for UltraPlus.                                                                                                                                                           |

| crosslink_scratch_pad_blk_size<br>{1024,2048,4096,8192} | CrossLink-NX and CertusPro-NX scratch embedded block RAM size.                                                                                                                                           |

| Argumentcrosslink_lram_size {65536,131072,262144}cross_link_external_mem_size CROSS_LINK_EXTERNAL_MEM_SIZEcrosslink_code_base_addr CROSSLINK_CODE_BASE_ADDR | CrossLink-NX and CertusPro-NX On-chip large RAM size.  CrossLink-NX and CertusPro-NX External memory (dram/hyper ram) interfaced size.  CrossLink-NX and CertusPro-NX Code/Binary base address of external memory. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CROSS_LINK_EXTERNAL_MEM_SIZEcrosslink_code_base_addr CROSSLINK_CODE_BASE_ADDR                                                                               | size.                                                                                                                                                                                                              |

| CROSSLINK_CODE_BASE_ADDR                                                                                                                                    | CrossLink-NX and CertusPro-NX Code/Binary base address of external memory.                                                                                                                                         |

|                                                                                                                                                             |                                                                                                                                                                                                                    |

| crosslink_data_base_addr<br>CROSSLINK_DATA_BASE_ADDR                                                                                                        | CrossLink-NX and CertusPro-NX data base address of external memory.                                                                                                                                                |

| hyper_ram {0,1}                                                                                                                                             | Use hyper RAM as external memory in CrossLink-NX or CertusPro-NX.                                                                                                                                                  |

| extmem_start_addr<br>EXTMEM_START_ADDR                                                                                                                      | Starting address of external DRAM to store data.                                                                                                                                                                   |

| mean MEAN                                                                                                                                                   | Mean value used to preprocess data during training.                                                                                                                                                                |

| scale SCALE                                                                                                                                                 | Scale value used to preprocess data during training.                                                                                                                                                               |

| sample_rate SAMPLE_RATE                                                                                                                                     | Sample rate value used for sampling the audio file.                                                                                                                                                                |

| down_sampling DOWN_SAMPLING                                                                                                                                 | Down sampling value used for down sampling the audio file.                                                                                                                                                         |

| extmem_off {0,1}                                                                                                                                            | Turn off using external memory to store data. By default, external memory is used to store input/output and scratch data.                                                                                          |

| load_from_extmem {0,1}                                                                                                                                      | By default, data is loaded from external memory to internal memory. If this option is '0', it makes sure data is directly loaded to EBR from sensor or host.                                                       |

| store_to_extmem {0,1}                                                                                                                                       | By default, data is output to external memory. If this option is '0', it makes sure to read data from internal memory.                                                                                             |

| project_name PROJECT_NAME                                                                                                                                   | Sets the project name.                                                                                                                                                                                             |

| project_dir PROJECT_DIR                                                                                                                                     | Project Directory.                                                                                                                                                                                                 |

| device {Ultra Plus, ECP5, CrossLink-NX,<br>CertusPro-NX, AVANT}                                                                                             | Sets the Device to ECP5, UltraPlus, CrossLink-NX, CertusPro-NX or Avant.                                                                                                                                           |

| mobilenet_mode {0, 1}                                                                                                                                       | Enable MOBILENET mode by setting value to 1. Default is 0.                                                                                                                                                         |

| ip_mode {Optimized_CNN, Compact_CNN, Extended_CNN, Advanced_CNN}                                                                                            | Sets the machine learning (ML) intellectual property (IP).                                                                                                                                                         |

| nnMode {0,1}                                                                                                                                                | Sets class CNN(0)/BNN(1).                                                                                                                                                                                          |

| bnn_sign_mode {0,1}                                                                                                                                         | Quantization mode for BNN(0: "0/1" and 1: "+1/-1")                                                                                                                                                                 |

| enable_hw_sim {0,1}                                                                                                                                         | Enable Hardware simulation. Default is 1.                                                                                                                                                                          |

| enable_fixed_sim {0,1}                                                                                                                                      | Enable Fixed-point simulation. Default is 1.                                                                                                                                                                       |

| enable_float_sim {0,1}                                                                                                                                      | Enable Floating-point simulation. Default is 1.                                                                                                                                                                    |

| collapse_layer {0,1}                                                                                                                                        | Collapse layers. Default is 0.                                                                                                                                                                                     |

| enable_dualcore {0,1}                                                                                                                                       | Enable Dual core functionality. Default is 1enable_dualcore {0,1}                                                                                                                                                  |

| enable_quadcore {0,1}                                                                                                                                       | Enable Quad core functionality for CertusPro-NX Optimized Only. Default is 0.                                                                                                                                      |

| enable_embedded_mode{0,1}                                                                                                                                   | Enable Embedded Mode. Default is 0.                                                                                                                                                                                |

| input_ebr INPUT_EBR                                                                                                                                         | Specify comma separated input EBR numbers.                                                                                                                                                                         |

| output_ebr OUTPUT_EBR                                                                                                                                       | Specify comma separated output EBR numbers.                                                                                                                                                                        |

| reg_out {0,1}                                                                                                                                               | Enable Register out functionality for CrossLink-NX, CPNX and Avant device. Default: 0.                                                                                                                             |

| required_output_depth_range<br>REQUIRED_OUTPUT_DEPTH_RANGE                                                                                                  | Specify Required Output Depth Range. For example, "7-13" only processes the $7^{th}$ to $13^{th}$ filters of the output convolution layer.                                                                         |

| user_added_yml USER_ADDED_YML                                                                                                                               | Specify User added yml file.                                                                                                                                                                                       |

| conv1x1_mode {single,quad,dual}                                                                                                                             | Specify conv1x1 mode like quad, dual or single. Default single for iCE40 UltraPlus, CrossLink-NX and CertusPro-NX Compact.                                                                                         |

| scratch_blk_size {1024,2048,4096,8192}                                                                                                                      | Size of scratch embedded block RAM for UltaPlus. Default: 8192.                                                                                                                                                    |

| arg_max {4096, 8192}                                                                                                                                        | Size of memory block RAM for arg max operation. Functionality for Extended and advanced CNN only. Default: 4096.                                                                                                   |

| otf post processing {0,1}                                                                                                                                   | Specify on the fly post processing for UltraPlus. Default: 0.                                                                                                                                                      |

| Argument                                                                               | Description                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| number_of_det_class NUM_OF_DET_CLASS                                                   | Size of scratch embedded block RAM for UltaPlus. Default: 4096.                                                                                                                                                                                                        |

| enable_debug_mode {0,1}                                                                | Enable debug mode or not. Supported only in CNX, CPNX and Avant devices.  Default: 0.                                                                                                                                                                                  |

| num_ve_segments                                                                        | LRAM Segment numbers we want to use . Iram size will be equal to (number of segments x segment size) value ranges from 1 to 7 for CPNX Advanced CNN and 1 to 16 for Avant Advanced CNN IP. Default value : 16.                                                         |

| segment_size                                                                           | Size of segment for advanced CNN IP. For CPNX and Avant device, advanced IP, with 32 bit datapath size segment size has fixed value of 65536. For Avant device, for 64 bit datapath size, segment size is 131072.                                                      |

| num_ve_spd_packs                                                                       | Number of the VE scratchpad in advanced CNN IP. Values ranges from 1 to 8.                                                                                                                                                                                             |

| ve_alu_enable                                                                          | Enable VE ALU or not. For Advanced IP only.                                                                                                                                                                                                                            |

| multi_port                                                                             | Multi-Port Parallel Values for advanced CNN IP. Values : {2,4}.                                                                                                                                                                                                        |

| datapath_width {32, 64}                                                                | Width of datapath for transferring of data within IP. More datapath width means more bytes of data transferred in each transaction.                                                                                                                                    |

| lut_input_bits {5,6,7,8,9,10,11,12}                                                    | Input bits for LUT for activation function. Only available in Optimized_CNN.                                                                                                                                                                                           |

| lut_output_bits {8, 16}                                                                | Output bits of data given by LUT of activation function. Only available in Optimized_CNN IP.                                                                                                                                                                           |

| msb_clip_enable {0,1}                                                                  | Clip MSB of input data bit for LUT of activation function.                                                                                                                                                                                                             |

| create_quantized_version {0, 1}                                                        | Create a quantized version of the selected input model. If the input model is not quantized, enabling this creates a quantized version of the input model to be used for further network compilation processing. Default: 0.                                           |

| validation_data_path {path of directory}                                               | Path of directory containing validation data. The compiler tool uses the validation data contained in this directory when creating the quantized version of a model.                                                                                                   |

| enable_fc_4_bit_weights {0, 1}                                                         | Enable weights of Fully Connected (FC) engine to be converted into 4 bits. Otherwise, used as 8 bits. Default: 0.                                                                                                                                                      |

| number_of_ml_ips                                                                       | Number of ML IP used to run the network. Default: 1.                                                                                                                                                                                                                   |

| external_memory_port                                                                   | Active only when LPDDR4 is selected. Based on the external memory port, logical external memory addresses are derived when the compiler generates instructions. This external memory port mapping must match with the hardware address mapping used in the RTL design. |

| Commands for Multi-Input Network                                                       |                                                                                                                                                                                                                                                                        |

| <pre>image_files "input1_name:IMAGE1_PATH;<br/>input2_name:IMAGE2_PATH"</pre>          | Specify the input image names according to the input model. Separate input image names with the semicolon (;).                                                                                                                                                         |

| multi_input_scale<br>"input1_name:0.0078125;input2_name:<br>0.0078125"                 | Specify the different scale values for each input.                                                                                                                                                                                                                     |

| multi_input_mean "input1_name:1;<br>input2_name: 1"                                    | Specify the different mean values for each input.                                                                                                                                                                                                                      |

| multi_input_sample_rate "input1_name:<br>8000;input2_name:8000"                        | Specify the different sample rate values for each input.                                                                                                                                                                                                               |

| multi_input_down_sampling<br>"input1_name:0;input2_name:0"                             | Specify the different down sampling values for each input.                                                                                                                                                                                                             |

| multi_input_load_address "input1_name:0;input2_name:1000"                              | Specify the address of the different locations to store each input.                                                                                                                                                                                                    |

| validation_data_path "input1_name:DATASET1_DIRECTORY; input2_name: DATASET2_DIRECTORY" | Path to directory for each input validation dataset. While creating the quantized version, this validation directory is used. A validation directory must be provided for each input in the model.                                                                     |

## 3.7. Design Restrictions

There are a few constraints and restrictions that should be kept in mind when designing a neural network with sensAl. The general hardware, software, and framework restrictions are listed below.

#### 3.7.1. General Restrictions

The mean operation is not performed in the network itself. It must be implemented in your RTL. For more information, see the Data Preprocessing section.

To support asymmetric padding on hardware, the Convolution layer should be followed by BatchNorm operation.

#### 3.7.2. ECP5 Restrictions

- Mean is not supported in firmware.

- Binary Convolution and Convolution: The maximum kernel size for Convolution is 9x9, while Binary Convolution has a maximum size of 3. The pad is recommended to be 1.

- If there is asymmetric padding in the convolution layer, then the convolution layer should be followed by Batch-Normalization layer.

- Pooling

- Global Average Pooling

- The kernel must be symmetric.

- The stride must be 1. The pad must be 0.

- Max Pooling

- The kernel must be symmetric.

- The recommended size is 2 × 2.

- The pad must be symmetric. It is recommended to use a kernel size of 9 × 9 or smaller to reduce the number of cycles used.

- For leaky\_ReLU, the negative activation slope is fixed to 1/16 in hardware. Models must be trained with alpha = 0.0625 (1/16) in leaky\_ReLU.

#### 3.7.3. ECP5 - Mobilenet Mode Restrictions

In addition to the previously-stated ECP5 restrictions, Mobilenet mode has a few additional restrictions to consider.

- Depthwise Convolution only supports kernel sizes of 3 × 3, with stride restricted to 1 or 2, and pad values restricted to 0 or 1.

- 1 × 1 convolution must have the pad set to 0.

- Mobilenet mode supports branching and merging using eltwise addition. Both inputs and outputs of eltwise addition must be in the same format [either in 16b or in 8b].

- The Depth wise kernel input is restricted to 8,192. For given channels (C, H, W), this means that (W \* H/2) must be less than or equal to 8, 192.

- The number of engines cannot be changed. sensAl disables the ability to change this number to prevent generating

an invalid firmware file. The number of engines used is eight convolution engines, eight depthwise convolution

engines, and 64 1 × 1 convolution engines.

- Because the eight Convolution engines are in dual core configuration, there are only four dual core engines. This is less than the limit of the normal ECP5 mode, meaning that the number of output EBRs is four when using the dual core engines instead of eight.

- There are still eight output EBRs when using the eight depthwise convolution engines.

- ReLU6 is not supported in Neural Network Compiler 7.0. Ensure that the model does not contain this activation.

- Currently, if Mobilenet is trained with TensorFlow and the first convolution layer uses padding, the hardware simulation results may be inexact when compared to the actual hardware output. Test the hardware in this situation. The TensorFlow implementation of padding introduces differences from the present implementation employed in hardware.

#### 3.7.4. UltraPlus Restrictions

- **Binary Convolution and Convolution**: When using a CNN design in UltraPlus, the Convolution layer should have a weight size of less than or equal to 3 and a stride (conv\_stride) of 1. It is recommended to keep the pad size at 1, although larger pad sizes can be supported. Data may be lost due to the fixed-point width losing significant figures as the padding size increases. When using a BNN design on UltraPlus, the Binary Convolution layer has the same constraints as the standard Convolution layer.

- Kernel sizes are restricted to  $3 \times 3$  for BNN and  $3 \times 3$  and  $1 \times 1$  for CNN.

- Pooling: The Pooling layer must have a stride (pool\_stride) and kernel (pool\_ksize) size of 2, and a pad (pool\_pad) of 0.

- Mean and Scale are not supported in firmware.

- All intermediate data in a model, except the output, is represented in unsigned 8-bit format in the hardware, using the format 1.7 to represent the data. Because of this, you should use Mean = 0 and Scale = 0.0078125 in settings for UltraPlus for any design you intend to run on the UltraPlus IP.

- Bias is not supported in the convolution layer.

- BNN supports input dimensions of 32 × 32.

- CNN supports the 32 × 32, 64 × 64, 128 × 128, and 160 × 160 input dimensions. 160 × 160 support requires Quad SPRAM.

- Unlike ECP5, there is no discrete Mobilenet mode. If a depthwise convolution is detected followed by a 1 × 1 convolution, the software will automatically generate firmware for handling Mobilenet.

- ReLU6 is not supported. Please ensure that the Mobilenet model does not contain this activation.

#### 3.7.5. CrossLink-NX and CertusPro-NX Optimized and Extended Mode Restrictions

- CrossLink-NX and CertusPro-NX devices only support CNN designs. At this time, there is no support for BNN-based networks. Use ECP5 or UltraPlus if binary network support is required.

- Weights and activations must be quantized for CrossLink-NX and CertusPro-NX. Refer to the Fixed Point

Quantization for iCE40 UltraPlus, CrossLink-NX, CertusPro-NX, and Avant section for more details on how to

quantize your network correctly.

- 3 × 3 and 1 × 1 are the only supported convolution kernel sizes. The stride required to be 1 for both types (except for optimized IP, where stride 2 is also supported for 3 x 3 kernel size). The pad can be 0 or 1 for 3 × 3 kernels, and the pad must be 0 for 1 × 1 convolution.

- Depthwise Convolution only supports 3 × 3 kernel size, with the stride required to be 1 for non-optimized IP and 1 or 2 for optimized IP. The pad can be either 0 or 1.

- Bias is not supported in the convolution layer.

- 4-bit weight quantization is only supported with the Learned Step Quantized model in Optimized IP mode.

- 2 × 2 is the only supported pooling kernel size. The stride must be 2, and the pad must be 0. Odd input to the pooling layer is not supported.

- ReLU and leaky ReLU are both supported. The negative slope for leaky ReLU must be 0.0625 (or 1/16). QuantReLU must be present after each ReLU.

- QuantReLU only supports numbits = 8, minimum = 0, and maximum = 2.

- The fully connected layer is only supported at last layer (no intermediate fully connected is supported).

- The last layer must be fully connected or CBSR. In CBSR, convolution types should be normal, depthwise, or 1 × 1 convolution.

- Mean and Scale are not supported in the firmware.

- For resize operation, bilinear and nearest-neighbor method are supported. The scale factor of 2 is only supported.

- Unlike ECP5, there is no discrete Mobilenet mode. If a depthwise convolution is detected followed by a 1 × 1 convolution, the software automatically generates firmware for handling Mobilenet.

- ReLU6 is not supported. Please ensure that the Mobilenet model does not contain this activation.

- Branching or merging structures, such as Concat and ELTwise addition, are not supported in compact mode. Use

either optimized mode or extended mode if you wish to use the ELTwise or Concat operations. Also, both inputs

and outputs of eltwise addition must be in 8-bit quantized format.

- CrossLink-NX and CertusPro-NX utilize external memory by allowing the base address for the data and code to be

specified. As a result, you to accidentally set a start address that leaves insufficient memory available for the data

or firmware. If the data base section address leaves insufficient room for the data, the analysis stage produces an

error indicating this. Likewise, if the code base address leaves insufficient room for the code, the analysis stage

produces an error stating as much. In either case, the address must be changed to allow for sufficient space.

- Depths/channels used in Crosslink-NX and CertusPro-NX are recommended to be multiples of 4 for depthwise and 1 × 1 convolution for better performance.

- CrossLink-NX with Quad LRAM (262,144 bytes) on-chip large memory size is available only for the CrossLink-NX 17k device, and due to the limitation of EBR on the 17k device, it will be available with a 1k scratch pad size only. Do not use firmware compiled with a Quad LRAM size for the CrossLink-NX 40k device. For CertusPro-NX, all scratch pad sizes are supported with Quad LRAM.

- Large input resolutions like VGA and QVGA are only supported in CrossLink-NX optimized mode, CrossLink-NX extended mode, CertusPro-NX optimized mode, and CertusPro-NX extended mode.

- Embedded mode is only supported for CrossLink-NX Optimized and CertusPro-NX Optimized devices.

- Embedded mode only allows dual or Quad LRAM (such as, with Embedded Mode on, you cannot use 64 KB of LRAM).

- Embedded mode does not allow external memory. If you observe a memory error, reduce the filter size or model dimension, or run the model with Embedded Mode off.

- Focus Layer is supported as the first layer only in the Optimized IP mode.

- 4-bit activation is only supported in Optimized IP mode.

- 4-bit input data to the fully connected layer is not supported.

#### 3.7.6. CertusPro-NX and Avant Advanced CNN IP Restrictions

Currently, the CertusPro-NX and Avant devices' advanced CNN IP only support the following layers.

- Convolution (kernel size:  $7 \times 7$ ,  $5 \times 5$ ,  $3 \times 3$ ,  $1 \times 1$ )

- Eltwise addition

- Concat

- Fully Connected

- Pooling (2 × 2 kernel, stride = 2, pad = 0)

- Pooling (K × K kernel, stride = 1, pad = K/2)

- Multiply, subtract, divide and reciprocate.

- The focus layer is currently implemented using RTL and must be part of preprocessing. It is always supported after the input layer.

- For the resize operation, bilinear and nearest-neighbor methods are supported. The scale factor of 2 is only supported.

- CertusPro-NX and Lattice Avant devices only support CNN designs. At this time, there is no support for BNN-based networks. Use ECP5 or UltraPlus if binary network support is required.

- Weights and activations must be quantized for CertusPro-NX and Lattice Avant devices. Refer to the Fixed Point

Quantization for iCE40 UltraPlus, CrossLink-NX, CertusPro-NX, and Avant section for details on how to quantize

your network correctly.

- 3 × 3, 1 × 1, 5 × 5, and 7 × 7 are the only supported convolution kernel sizes. The stride must be 1 for a 5 × 5 kernels; pad = 2. For 3 × 3, stride = 2 with asymmetric padding is supported to achieve output dimension (H/2, W/2). Pad = 0 is not supported with the 3 × 3 kernel.

- Depthwise Convolution supports  $5 \times 5$ ,  $3 \times 3$  kernel size, with stride = 1, and pad = 1.

- The 2 × 2 kernel is supported for pooling. Stride = 2, and pad = 0 are required. Odd input to the pooling layer is not supported.

26

- For pooling with a K × K kernel, stride = 1, and padding must equal K/2.

- ReLU and leaky ReLU are both supported. The negative slope for leaky ReLU must be 0.0625 (or 1/16). QuantReLU must be present before or after each ReLU.

- QuantReLU only supports numbits = 8, minimum = 0, and maximum = 2.

- The fully connected layer is supported as the last and intermediate layer. The intermediate fully connected layer must be followed by the last fully connected layer and must be quantized.

- The last layer must be fully connected, CBSR, or resized bilinear. In CBSR, convolution types should be normal, depthwise, or 1×1 convolution.

- Mean and Scale are not supported in the firmware.

- Unlike ECP5, there is no discrete Mobilenet mode. If a depthwise convolution is detected, followed by a 1 × 1 convolution, the software automatically generates firmware for handling Mobilenet.

- ReLU6 is not supported. Please ensure that the Mobilenet model does not contain this activation.

- CertusPro-NX and Lattice Avant devices utilize external memory by allowing the base address for the data and

code to be specified. As a result, you to accidentally set a start address that leaves insufficient memory available

for the data or the firmware. If the data base section address leaves insufficient room for the data, the analysis

stage produces an error. Likewise, if the code base address leaves insufficient room for the code, the analysis stage

produces a warning. In either case, the address must be changed to allow sufficient space for both data and code.

- Depths/channels used in CertusPro-NX and Lattice Avant are recommended to be multiples of 4 for depthwise and 1 × 1 convolution for better performance.

- Currently, 2 and 4 multiport modes are supported. These modes use more resources but speed up 1 × 1 convolution execution.

- The focus layer is supported as the first layer only in Advanced IP mode.

- 4-bit activation is not supported in Advanced IP.

#### 3.7.7. Keras Restrictions

See the Supported Keras Layers section for more requirements for individual layers.

#### 3.7.8. TensorFlow Restrictions

Versions 1.14, 2.0, 2.3, 2.5, and 2.9 of TensorFlow are supported by sensAl. Networks designed for other versions may not be compatible.

See the Supported TensorFlow Operations section for more requirements for individual operations.

#### 3.7.9. AutoKeras Restrictions

- The model training was done considering a multiclass **CLASSIFICATION** task only.

- The model architectures were experimented with an input size of  $32 \times 32 \times 1$ .

- The optimizer that AutoKeras chooses sometimes has a very small initial learning rate, and sometimes it is used along with learning rate decay, which affects training accuracy and loss. Hence, a constant optimizer was used (SGD with an initial LR=0.1 and a learning rate scheduler callback option).

- For now, the only hyperparameter that is varying is the number of channels (depth) in each layer. If the number of layers is kept as a hyperparameter, then it tries to go for a very large depth near the FC layer, and this creates the FC output value to explode. So the number of layers is now fixed.

- The *max model size* parameter is tested with a few experiments (with a given seed and resolution) to create a model (.bin file size) smaller than the limit for certain devices like UltraPlus.

- For reproducibility, when the seed is provided, it searches through the same hyperparameter combinations every time we run the script. However, the loss value that the AutoKeras get might differ slightly, and as a result, they may not have the same architecture as earlier. But the accuracy remains approximately within the +/-3% range.

- Note that if FC layer output crosses the range of [-32,+32], then we may experience a little higher MAE in the Neural Network Compiler, which is expected.

Refer to AutoKeras Reference Design document to know about training a model in AutoKeras for NNC.

#### 3.7.10. ONNX Restrictions

ONNX model support is experimental. Only float and PTQ models are supported. The input to the network should be in the NCHW format. See the Supported ONNX Layers section for more requirements on individual operations.

# 3.8. Next Steps

Now that you have created or opened a project, you are ready to edit your project and run through the design flow, as detailed in the next section.

# 4. Working with Projects

# 4.1. Implementations

Implementations organize the structure of your design and allow you to try alternate structures and tool settings to determine which one can give you the best results. To help determine which scenario best meets your project goals, try using a different implementation of a design with different settings. Each implementation has associated active settings. When you create a new implementation, you must select its active settings.

#### 4.1.1. Creating a New Implementation

To try a new implementation with different strategies within an existing project, you must create a new implementation.

- 1. Choose File > Add Impl to bring up the Implementation Options window.

- 2. The Implementation Options window has the same parameters as the one you encountered when creating your project initially. You can change the implementation name to a unique string if desired. Within the project, each implementation must have a unique name.

- 3. Change the implementation settings from the default settings, if desired.

#### 4.1.2. Editing an Implementation

You can edit an existing implementation to change the specific input and output files, as well as the implementation settings.

- Choose File > Edit Impl to bring up the Project Settings window.

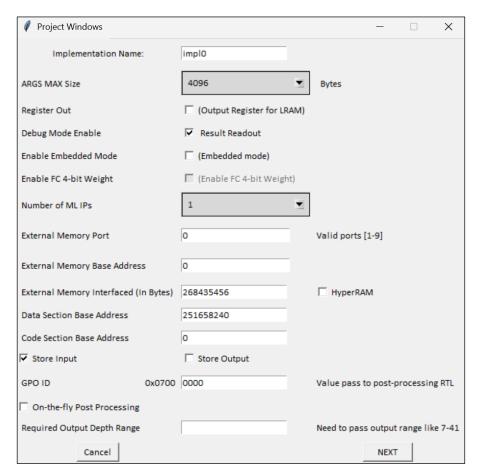

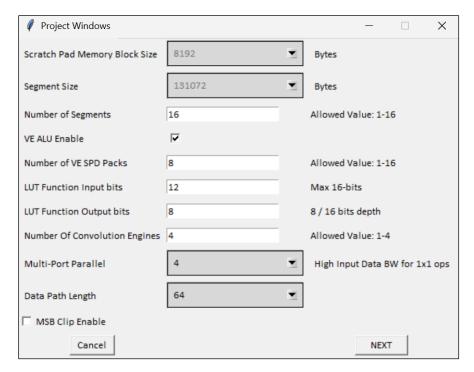

- 2. The Project Implementation Settings window opens, as shown in Figure 4.1.

Figure 4.1. Project Implementation Options Window

3. Edit your existing settings and click **OK** to apply them to your project implementation. For more information on parameters and their limitations, refer to the Project Implementation Settings section.

# 4.2. Project Flow

#### 4.2.1. Analyze

You must first run the Analyze function on your project before you can progress to the Compile or Simulate stages. It analyzes your code to verify compatibility with the Lattice CNN Compiler. You can run the Analyzer by selecting **Process > Analyze**.

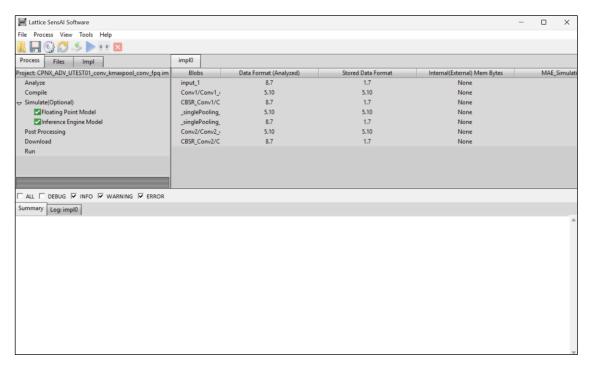

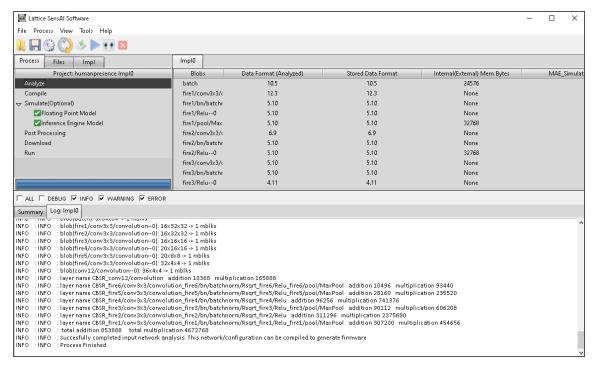

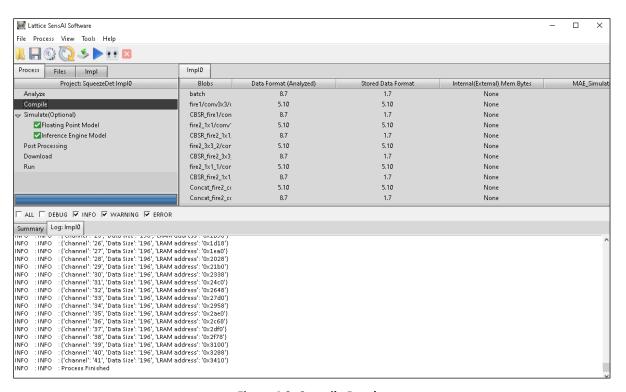

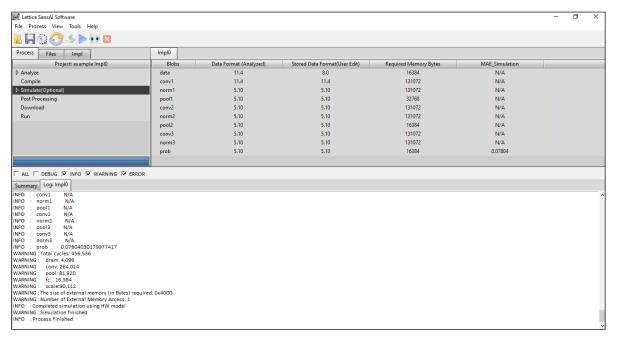

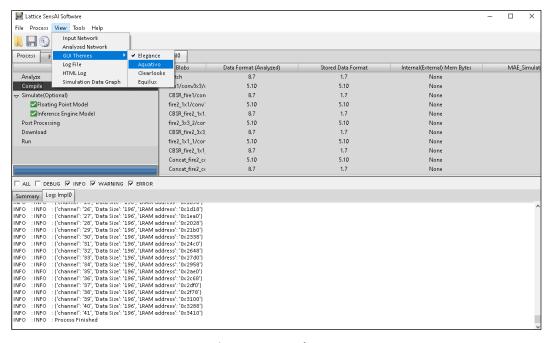

Figure 4.2. Analyze Results

After successfully analyzing a neural network file, the implementation window is updated with a set of columns listing the properties of your neural network under the current settings.

- **Blobs:** Each blob that is detected and implemented by the software is listed in this column. Some blobs that are in the network file are not implemented in the hardware, such as those used for external data processing, and are not listed here.

- **Data Format:** This column lists the breakdown of the fixed-point representation of the blob. The number preceding the period is the number of bits used to represent the integer component of the number, while the number following it is the number of bits used in the fractional component. For signed data, the total number of bits is one less than the total number of bits used, as one bit is always used for signage.

- For clarification, the following represents a 16-bit signed number, using 15 bits to represent the integer and fraction:

- 3.12 represents a signed number with 3 integer bits and 12 fractional bits. The sum of the two values is 15. The software thus uses a 16-bit signed format.

- For a signed 8-bit number, the total would be 7, as shown:

- 5.2 represents a signed number with 5 integer bits and 2 fractional bits. The sum of the two values is 7. The software thus uses an 8-bit signed format. Finally, unsigned numbers can be used in 8-bit format.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

- 5.3 represents an unsigned number. The sum of the two values is 8. The software thus uses an 8-bit unsigned format. SensAl only supports unsigned 8-bit and signed 8- and 16-bit formats. Some settings, such as layer collapse, force a certain combination of integer and fractional bits.

- Stored Data Format: This column is a user-editable list of the fixed-point representations of each blob. It is populated with the default values that are automatically calculated by the software. Values are written in the same format as the signed data format entry above. In order to edit the stored data format for a blob, double-click the entry in that column for the blob in question.

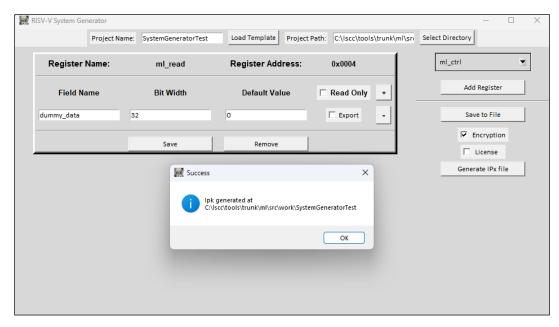

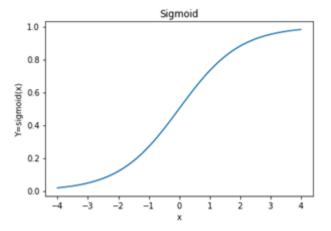

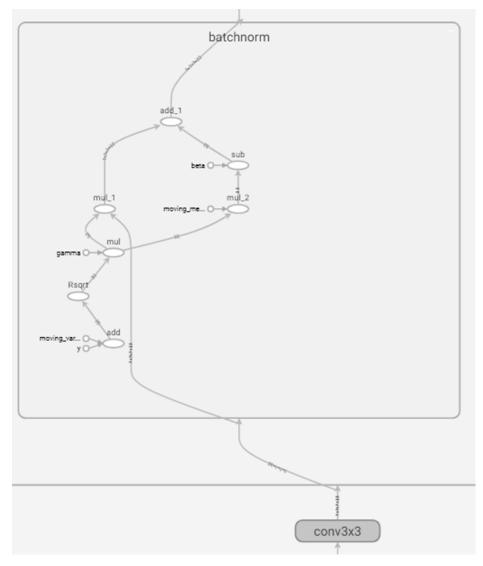

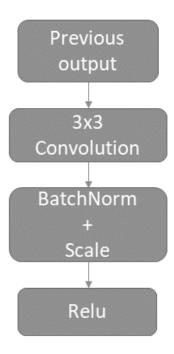

You can allocate how many bits you want dedicated to the integer and fractional components for EBR storage for the specified blob. You have to specify whether the EBR accepts 16-bit mode or 8-bit mode. To use 16-bit mode, your two values need to add up to 15. To use 8-bit mode, your two values need to add up to 7.