# NEW USE CASES HIGHLIGHT CROSSLINK'S BROAD APPLICABILITY

A Lattice Semiconductor White Paper February 2017

Lattice Semiconductor

111 5<sup>th</sup> Ave., Suite 700

Portland, Oregon 97204 USA

Telephone: (503) 268-8000

www.latticesemi.com

### Introduction

Approximately nine months ago, Lattice Semiconductor introduced an innovative new video bridging solution to help designers take advantage of the latest generation of processors, displays and sensors. Called <u>CrossLink™</u>, this new device addresses the challenges of today's rapidly changing I/O landscape by offering designers a new way to develop high performance, low power and compact bridging solutions.

CrossLink is the world's most versatile video interface bridge. Its appeal is obvious. The new device offers the industry's fastest MIPI D-PHY bridging solution capable of up to 4K UHD resolution at 12 Gbps bandwidth. At the same time, it delivers low power operation in a tiny 6 mm² package for mobile applications. For designers seeking to take advantage of the innovations in the current generation of mobile processors, migrate to MIPI standard interfaces, and still preserve investments in legacy sensors and/or displays, CrossLink offers a highly attractive and cost-effective way to bridge between different video interface standards.

In September, Lattice also announced the addition of CrossLink bridging devices for applications in Automotive Advanced Driver Assistance Systems (ADAS) and infotainment applications. As auto makers integrate more low cost image sensors and displays to keep pace with rising technology requirements, they will need to address the interface mismatches between sensors, displays and application processors. CrossLink will help them meet those needs while reducing overall cost, power and size.

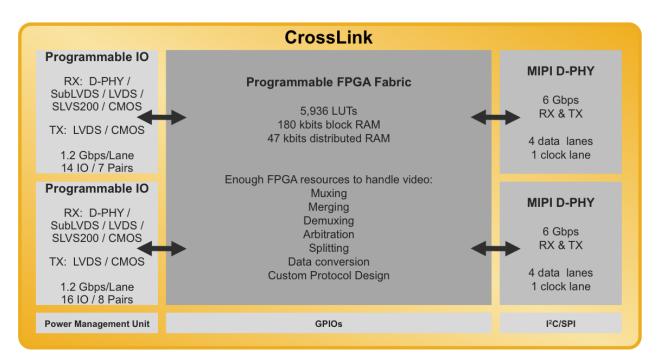

Initially, Lattice engineers, relying on customer feedback, focused on offering CrossLink bridging solutions for the most popular mobile, camera, display and legacy interfaces. The FPGA features two MIPI D-PHY hard blocks surrounded by a mobile FPGA fabric. The programmable I/O on the device supports a wide range of popular interfaces including MIPI D-PHY, MIPI CSI-2, MIPI DSI, CMOS, RGB, MIPI DPI, MIPI DBI, subLVDS, SLVS, LVDS and OpenLDI.

CrossLink Block Diagram

Typical early applications were simple interface conversions of MIPI CSI-2, MIPI DSI, RGB, CMOS, OpenLDI, LVDS and SLVS interfaces as well as merging or splitting multiple interfaces on image sensors, application processors and displays. As prospective customers have learned more about CrossLink, however, they have begun to approach Lattice with problems that represent slight permutations from their systems' previous functionality. In most of these applications no bridging solution exists and the application is far too narrow to justify the cost of developing a standalone ASSP. By leveraging CrossLink's programmability, designers are developing new solutions never considered before. Moreover, Crosslink's high level of programmability allows developers to find new applications.

## **New Video Bridging Solutions**

On February 21, 2017, Lattice announced the availability of five new applications for Crosslink, underscoring the device's flexibility to support the fast evolving video bridging market. The first three represent an emphasis on new video bridging solutions. The last two are traditional interface conversion applications.

## New Bridging Intellectual Property (IP)

#### **CSI-2** Repeater

This new IP can serve multiple applications. In larger systems, an image sensor output can degrade as it travels across the system. Typically, the signal passes from a module through a flex cable to a connector and across a PCB. As the system grows in size, a signal running at high speed and low power can quickly degrade. In this example the repeater would take the signal after the connector, clean it up, and regenerate it across the PCB (see diagram).

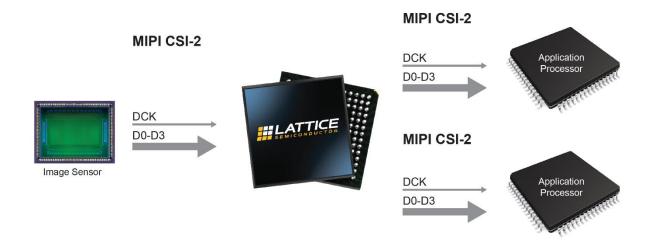

One Input to One Output MIPI CSI-2 Display Interface Bridge

**CrossLink's repeater function** allows designers to more easily integrate CSI-2 cameras into larger systems. The repeater is also useful in applications where there are issues with the packetization and timing between the image sensor and the applications processor. In some cases, the designer needs to rework or reorganize some packets before the processor can accept the data.

In addition, some cameras employ extra overhead in the video frame outside of the active pixels region. These systems sometimes find it useful to crop or scale the image before it reaches the AP. Using the FPGA fabric in Lattice's CrossLink device, designers can program the CSI-2 repeater to perform this type of task with a high level of granularity.

#### **CSI-2 Splitter**

In some mobile devices, drones and automotive applications performing machine vision functions, designers need to send the same output from a CSI-2 camera to two processors. This CSI-2 Splitter IP can be very useful in systems that feature a standard applications processor and a secondary niche image or machine vision processor (see diagram).

One Input to Two Output MIPI CSI-2 Camera Splitter Bridge

By splitting the CSI-2 signal to each processor separately, the AP can display image data directly on a monitor or engage in user-interactive functions while the specialty processor can use the same data to perform analytics or image enhancement for highend applications.

#### 4:1 CSI-2 to CSI-2 Mux/Merge

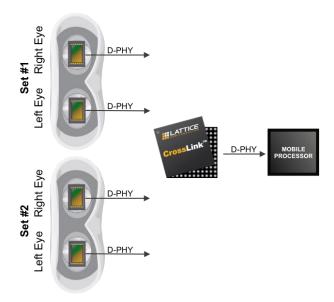

The number of cameras used in a growing number of applications is climbing rapidly. In the current generation of auto and drone designs, for example, four cameras are considered typical. As the number of cameras rises, designers often need to take the output from four image sensors and merge two of the four into a single CSI-2 output. With CrossLink, designers can now use a GPIO pin to switch between whichever set of two cameras they wish to use.

4:1 CSI-2 to CSI-2 Mux/Merge

# **Updated IP**

While the three new IPs described above will help designers use CrossLink to better manage bandwidth, Lattice is also continuing to expand its traditional bridge portfolio with solutions that convert one format to another.

#### 2:2 LVDS to MIPI DSI

The first example is a new 2:2 LVDS/FPD-Link/OpenLDI to MIPI DSI bridge. In applications where bandwidth requirements are rising rapidly, such as VR headsets, automotive infotainment and industrial machine vision, designers need to support higher resolution mobile displays. This new IP allows designers to convert from a dual-link LVDS interface to two MIPI DSI outputs. That capability gives designers the flexibility to use either one high resolution or two lower resolution displays in their design.

2:2 LVDS to MIPI DSI

CrossLink Solutions

A Lattice Semiconductor White Paper

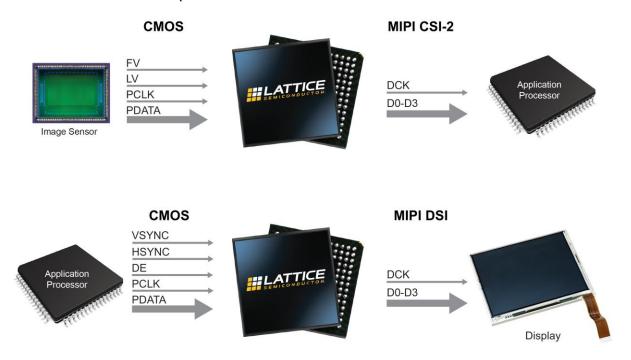

#### 300 MHz CMOS to MIPI DSI/CSI

At the same time, several existing solutions for applications such as projectors, VR/AR, video conferencing, set-top boxes and automotive infotainment incorporate processors and cameras that offer valuable features, but are of limited utility because they only support CMOS at a high (300 MHz) bus rate. For example, some devices have a CMOS or RGB interface that can operate up to 300 MHz, but must be upgraded to support CSI-2. Similarly, some processors cannot support 300 MHz CMOS, but can support DSI or CSI-2. This bridge now allows designers to convert to MIPI DSI displays or CSI-2 camera at resolutions up to 4K.

300 MHz CMOS to MIPI DSI/CSI

## **Development Support**

To accelerate development, Lattice offers the CrossLink LIF-MD6000 Master Link board which allows designers to evaluate the CrossLink device. The evaluation board can be used with the free CrossLink IP available in Lattice's Diamond design software.

Master Link Board

For system integration needs, the kit includes SMA and breakout I/O link daughter boards. The LIF-MD6000 Master Link board also includes a Mini USB Type-B connector to program the CrossLink device as well as a MachXO3 FPGA which can be used for additional GPIO and peripheral resources. Lattice also provides daughter boards for Raspberry Pi. This allows users to connect two MIPI CSI-2 cameras through CrossLink to a Raspberry Pi processor.

## **Conclusion**

The solutions described above represent just a small sample of the new CrossLink use cases to come. The device's unique programmability and design flexibility will likely continue to spur the development of innovative new applications. With CrossLink not only can designers handle operations directly on the video stream, but can also handle peripheral conversions within the same device such as converting an I<sup>2</sup>C slave to multiple I<sup>2</sup>C masters, an I<sup>2</sup>C slave to a SPI master, or creating I<sup>2</sup>C register maps to control a variety of GPIOs for image sensor triggering. This bundling of capabilities can reduce the system chip count and cost.

While use cases for sensors and displays will continue to grow, it's important to note that CrossLink is not limited to handling video data. In the not-too-distant future expect to see developers begin to use CSI-2 and DSI ports on APs as serialized links for various types of data such as radar, high speed ADC and DAC, peripheral sensors and time stamping. CrossLink can then take this non-video data, packetize it into MIPI CSI-2 and MIPI DSI formats with custom or standard data types, and send the data to the AP for post-processing. The possibilities are virtually endless.