# Power Management and Calculation for CrossLink Devices

# **Technical Note**

FPGA-TN-02018 Version 1.1

## **Contents**

| Acronyms in This Document                                      | 4  |

|----------------------------------------------------------------|----|

| 1. Introduction                                                | 5  |

| 2. Power Management Unit                                       | 5  |

| 2.1. PMU Block                                                 |    |

| 2.1.1. PMU State Machine                                       | 6  |

| 2.1.2. State Transitions                                       |    |

| 2.1.3. Types of Triggers                                       | 8  |

| 2.1.4. Using the PMU                                           |    |

| 2.2. PMU Module, Primitive and Attributes                      |    |

| 2.2.1. PMU Port Definitions and Parameters                     |    |

| 2.2.2. PMU Control Bus and Primitive Attributes                |    |

| 2.3. Using Diamond Clarity Designer GUI to Generate PMU        | 19 |

| 3. User Standby Mode during Normal State                       | 21 |

| 3.1. Usage of User Standby Mode                                | 21 |

| 3.1.1. User Standby Mode for PLL                               | 22 |

| 3.1.2. User Standby Mode for Oscillator                        | 22 |

| 3.1.3. User Standby Mode for MIPI DPHY                         | 22 |

| 3.1.4. User Standby Mode for Inputs and Outputs                | 22 |

| 4. Power Consumption and Calculation                           | 25 |

| 4.1. Power Calculator                                          | 25 |

| 4.1.1. Typical and Worst Case Process                          | 26 |

| 4.1.2. Junction Temperature                                    | 26 |

| 4.1.3. Maximum Safe Ambient Temperature                        | 26 |

| 4.1.4. Operating Temperature Range                             | 26 |

| 4.1.5. Dynamic Power Multiplier                                | 27 |

| 4.1.6. Peak Startup Current                                    | 27 |

| 4.1.7. Power Budgeting                                         | 27 |

| 4.1.8. Device Operational Limits                               | 27 |

| 4.1.9. Dynamic Power Savings                                   | 28 |

| 4.1.10. Activity Factor Calculation                            | 28 |

| 4.1.11. Power Calculator Assumptions                           | 28 |

| 4.2. Using Power Calculator for CrossLink Devices              | 29 |

| 4.2.1. Power Calculator in Normal State, and User Standby Mode | 29 |

| 4.2.2. Power Calculator in Sleep State                         | 30 |

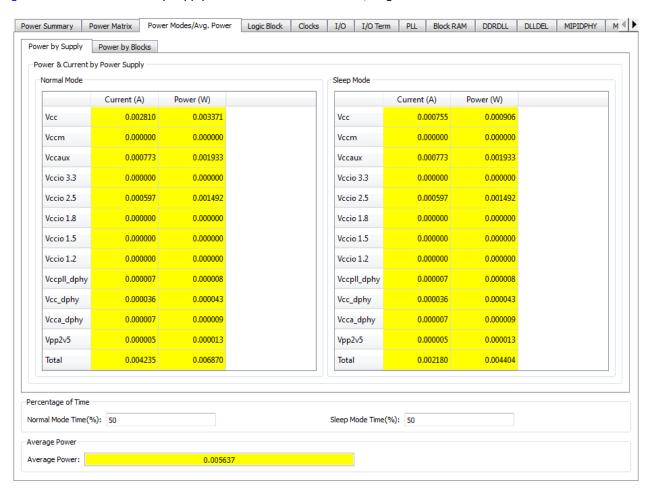

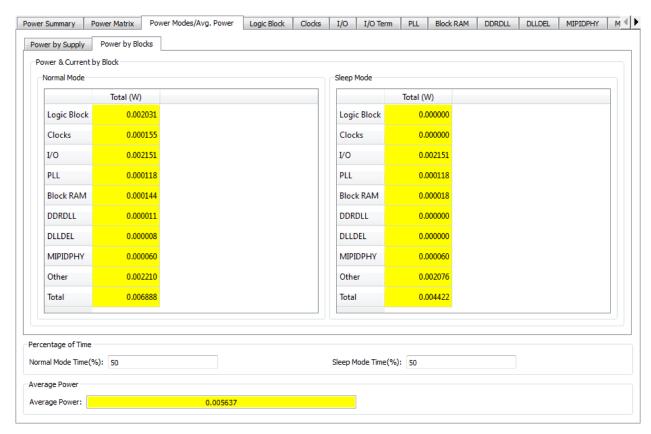

| 4.2.3. Calculating Average Power                               | 31 |

| 5. Thermal Management                                          | 32 |

| 5.1. Thermal Impedance and Airflow                             | 32 |

| 5.2. Thermal Management in Power Calculator                    | 32 |

| 5.3. DELPHI Models                                             | 33 |

| 6. Conclusion                                                  | 33 |

| References                                                     | 34 |

| Technical Support Assistance                                   | 34 |

| Revision History                                               | 34 |

## **Figures**

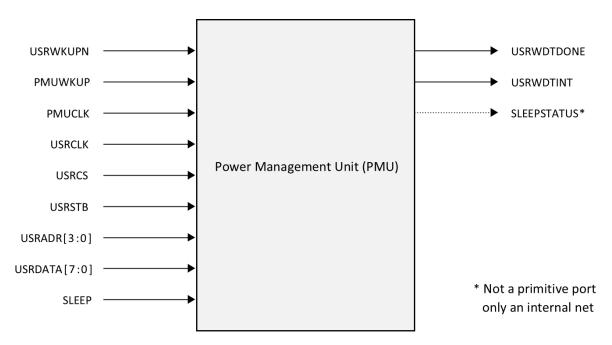

| Figure 2.1. PMU Block Diagram                                                                   | 5  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2.2. CrossLink PMU State Machine                                                         | 6  |

| Figure 2.3. Using USRWKUPN Pin for sleep and wakeup (functional depiction, not timing)          | 10 |

| Figure 2.4. Using GPIO for SLEEP when directly routed to PMU (functional depiction, not timing) | 10 |

| Figure 2.5. PMU HDL Primitive –PMUA                                                             | 12 |

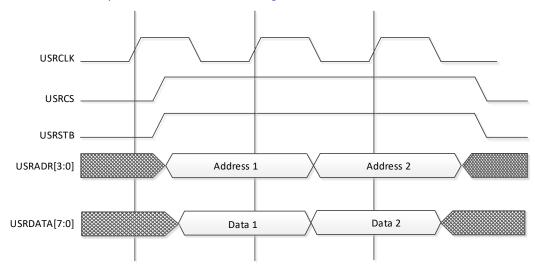

| Figure 2.6. PMU Control Bus Write Operation                                                     | 14 |

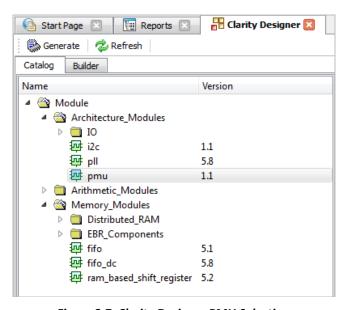

| Figure 2.7. Clarity Designer PMU Selection                                                      | 19 |

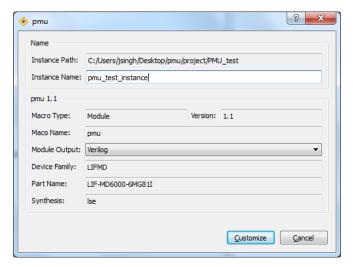

| Figure 2.8. PMU Instance Name Options Window                                                    | 20 |

| Figure 2.9. PMU Configuration GUI Window                                                        | 20 |

| Figure 3.1. User Standby Mode Use Case Example Block Diagram                                    | 21 |

| Figure 3.2. Primitive for Bank Controller for Inputs – Referenced and Differential              | 23 |

| Figure 3.3. INRDB Simulation Primitive                                                          |    |

| Figure 3.4. Bank Controller for LVDS Outputs Primitive                                          | 24 |

| Figure 3.5. LVDSOB Simulation Primitive                                                         |    |

| Figure 4.1. Power Calculator (Summary Tab for CrossLink Devices)                                |    |

| Figure 4.2. Power Controller Window for User Standby Mode options                               |    |

| Figure 4.3. Power Calculator – Power Modes/ Avg. Power Tab (Power by Supply)                    |    |

| Figure 4.4. Power Calculator – Power Modes/ Avg. Power Tab (Power by Blocks)                    | 31 |

| Tables                                                                                          |    |

| Table 2.1. PMU HDL Primitive Port Definitions                                                   | 12 |

| Table 2.2. PMU Control Bus Address Mapping                                                      |    |

| Table 2.3. PMU Control Register (PMUCR) bit map                                                 |    |

| Table 2.4. PMU Control Register (PMUCR) Component Port Definition                               |    |

| Table 2.5. PMU Watch Dog Timer Control Register 1 (PMUWDTCR1) bit map                           |    |

| Table 2.6. PMUWDTCR1 Definitions and Settings                                                   |    |

| Table 2.7. PMU Watch Dog Timer Counter 1 (PMUWDTCNT1) bit map                                   |    |

| Table 2.8. PMU Watch Dog Timer Counter 2 (PMUWDTCNT2) bit map                                   |    |

| Table 2.9. PMU Watch Dog Timer Counter 3 (PMUWDTCNT3) bit map                                   |    |

| Table 2.10. PMU Watch Dog Timer Counter 3 (PMUWDTCNT3) bit map                                  |    |

| Table 3.1. Blocks Supporting User Standby Mode                                                  | 21 |

| Table 3.2. BCINRD Primitive Attributes                                                          | 23 |

| Table 3.3. BCINRD Simulation Behavior                                                           | 23 |

| Table 3.4. BCLVDSOB Primitive Attributes                                                        | 24 |

| Table 3.5. BCLVDSOB Simulation Behavior                                                         | 24 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym                         | Definition                                      |

|---------------------------------|-------------------------------------------------|

| AF%                             | Activity Factor Percentage                      |

| AP                              | Application Processor                           |

| EBR                             | Embedded Block RAM                              |

| FPGA                            | Field Programmable Gate Array                   |

| GPIO                            | General Purpose Input/Output                    |

| GUI                             | Graphical User Interface                        |

| HDL                             | Hardware Descriptive Language (Verilog or VHDL) |

| 10                              | Input Output                                    |

| LUT                             | Look-Up Table                                   |

| LVDS                            | Low Voltage Differential Signalling             |

| OSC                             | Oscillator                                      |

| PLL                             | Phase Locked Loop                               |

| PMUCR                           | PMU Control Register                            |

| PMUWDTCR                        | PMU Watch Dog Timer Control Register            |

| PMUWDTCNT                       | PMU Watch Dog Timer Counter                     |

| $T_J$ , $T_A$ , $T_B$ , $T_C$ , | Junction, Ambient, Board and Case Temperatures  |

| USR                             | User Interface                                  |

| WDT                             | Watch Dog Timer                                 |

## 1. Introduction

CrossLink™ devices from Lattice Semiconductor help stretch the battery life of an application by lowering the power consumption. CrossLink is a low power FPGA device with a configurable Power Management Unit (PMU) block that places the device in lower power consumption state (*Sleep State*) to save power, reduce average power consumption and increase battery life for the applications it is used in.

This document serves as a usage guide for managing and determining power consumption of the CrossLink device family. The document details the conceptual and functional description along with a guide to utilize the features of the PMU. Power consumption in Diamond Power Calculator (power saving feature of CrossLink) is also described.

## 2. Power Management Unit

The Power Management Unit (PMU) is a configurable IP available in CrossLink devices. The PMU allows the device to be placed in a lower power consumption state called Sleep State when the device is not active. This helps reduce the average power consumption of the device which can be beneficial in portable or mobile applications.

The HDL (Verilog or VHDL) module can be generated through the Clarity Designer in Diamond software. It is configurable based on application requirements. Each configuration settings help set up options unique to the application and can place the device in Sleep State or wake up to active Normal State. PMU works closely with user applications or application processor, providing dynamic options to user like wake up (using different signals), or when to wake (using timers).

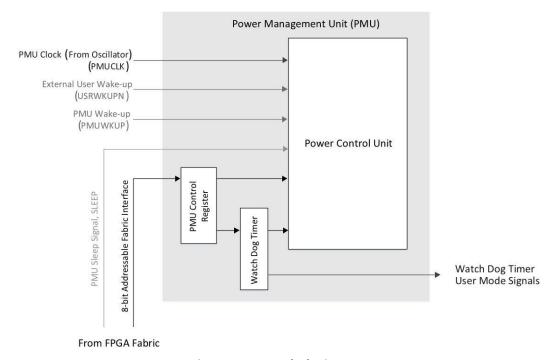

#### 2.1. PMU Block

Power Management Unit has two active states – Normal State and Sleep State. The device is active and running in Normal State. During Sleep State, the device is placed in a low power consuming state for periods when the device is not required to be active (or operational).

Figure 2.1 shows an overview of the PMU IP. The functional and usage descriptions of the PMU are detailed in the sections below.

Figure 2.1. PMU Block Diagram

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

The low speed PMU clock coming in from the internal oscillator is the heart of the PMU. This connection is hardwired from the oscillator to the PMU. The speed of operation for the PMU is fixed at 10 kHz.

The brain of the PMU IP is a Power Control Unit, which essentially controls the various power supplies of the device. Power Control Unit has hard wired connections to the device's internals that control the power supply switches. These connections are not user accessible.

There are a number of inputs to the Power Control Units. One of the most important ones is the PMU Sleep Signal (SLEEP). This is an active high signal, which when triggered, sends a command to the Power Control Unit to place the device in a low power Sleep State.

There are two wake up signals – External User Wake-Up (USRWKUPN) and PMU Wake-Up (PMUWKUP). External User Wake-Up (USRWKUPN) is a shared dedicated pin that is hardwired to the PMU block.

Along with the Power Control Unit, there are two other blocks inside the PMU - PMU Control Register and Watch Dog Timer.

#### **PMU Control Register**

The PMU Control Register (also referred to as PMUCR in this document) stores the configuration settings of the PMU, such as how does the PMU wake up (from external pin or Watch Dog Timer expiry), the settings of the Watch Dog Timer, and so on.

PMUCR also has a dedicated 8-bit addressable PMU Control Bus interface to the FPGA fabric. This interface is very useful for applications that demand dynamic update of the PMU configuration as it can be used to update the configuration. The FPGA fabric has to be active (that is Normal State) in order to access the PMUCR via this interface. During the Sleep State, the FPGA fabric interface is inactive.

#### **Watch Dog Timer**

The Watch Dog Timer (WDT) is the final block of the PMU, and is used to set timers. The PMU can be configured to wake up on the expiry of these WDT timers. An example for a timer would be the timer available in our cell phones. You can set a timer for your device to wake up, say, in 10 minutes. When the PMU places the CrossLink device in Sleep State, the Watch Dog Timer is available exclusively for the PMU, whether it is set to wake up the device upon expiry or not.

WDT is not used by PMU in the Normal State, and has an optional user mode available. This WDT resource is made available to the application to perform functions that require timer(s). If the SLEEP signal is sent to the PMU, then going to Sleep State takes precedence over the user mode of Watch Dog Timer and it stops all operations and goes to sleep. Any required housekeeping needs to be taken care of at the user end (see the Using the PMU section on page 9).

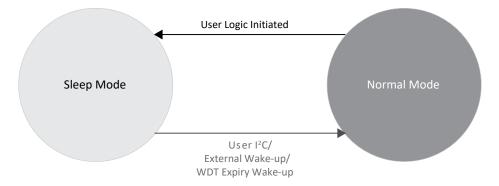

#### 2.1.1. PMU State Machine

As already mentioned, there are two states for PMU in CrossLink devices – Normal State and Sleep State. Both are mutually exclusive and the device can be placed in either one of the states. Figure 2.2 shows the PMU's State Machine and triggers that helps transition one to the other.

Figure 2.2. CrossLink PMU State Machine

Each state is discussed in detail below. It is important to understand the transition to each states, and the triggers that change the state from one to the other.

#### 2.1.1.1. Normal State

All elements of the device are active in the Normal State to the extent required by the design. The device is fully active and performing as required by the application.

The device is at its highest power consumption in the Normal State. There are certain blocks of the device that can be placed in User Standby mode if they are not required by the application (see the User Standby Mode during Normal State section on page 21). These blocks (PLL, I/Os, OSC, and MIPI DPHY) can be placed in a lower power state when they are neither used nor needed by the application. This helps save some power in the Normal State; however User Standby Mode is different from the Sleep State. In the User Standby Mode, these blocks have a smaller static leakage current associated with them; there is no dynamic current because these are inactive.

PMU's Sleep State, on the other hand, makes the device inactive and places everything in the lower power. Sleep State overrides the User Standby mode.

#### 2.1.1.2. Sleep State

In the Sleep State, the device is power gated and is not operational. The configuration of the device (the application bitstream that the device is programmed with) and EBR contents are retained. When it transitions to Normal State, the device will operate with these contents preserved.

The device is at its lowest power during the Sleep State. This helps reduce the overall power consumption for the device.

The PMU block stays powered on and active along with the associated I/Os even during Sleep State.

#### **Retention in Sleep State**

- CrossLink devices retain configuration SRAM, EBR contents when in Sleep State

- All registers within the IPs (EBR registers for example), and PFU registers will not retain their state

- User I<sup>2</sup>C registers retain their state

- The I/Os hold their values during the Sleep State. The last value of each I/O is held to avoid issues with other devices connected downstream from the CrossLink device.

- Differential I/Os do not hold their value; all differential I/Os are tri-stated

#### 2.1.2. State Transitions

Figure 2.2 shows the two state transitions to move from one state to the other.

#### 2.1.2.1. Normal to Sleep

This transition happens when user requests the device to go to sleep. The trigger can come from an external source or generated within the application; the SLEEP signal is toggled high and the PMU goes to Sleep State.

The PMU can only be placed in Sleep State through the SLEEP signal coming in from the FPGA fabric. There are no external pins wired directly to place the device to sleep.

#### Example

Assume an external trigger or signal coming from an AP (Application Processor), requesting the CrossLink device to be placed in Sleep State. This signal comes in through an I/O and initiates a 'go to sleep' command to the application logic. This logic can then initiate the SLEEP signal to PMU through the fabric interface, and the PMU places the device in Sleep State. The signal can be routed directly to the PMU's SLEEP input via FPGA fabric in a simple scenario. For more complex design requirements, Lattice recommends a more graceful shutdown of the functions and operations being performed, and then initiate the SLEEP signal to the PMU using a state machine (see the Using the PMU section on page 9).

#### 2.1.2.2. Sleep to Normal

Before looking at triggers needed to wake up the device from the Sleep State, let us look at the device in this state. PMU block, along with associated I/Os, are active; the FPGA fabric has been power gated and inactive; the configuration (or programming) of the device along with EBR contents are preserved; and the I/Os are holding their state.

We can wake the device up in a number of ways. One simple way is by using the External User Wake-Up (USRWKUPN). This option should be enabled in the module generated through Diamond's Clarity Designer. USRWKUPN is an active low signal, users toggle it low and device wakes up (adherence to timing requirements to wake up the device is required). USRWKUPN is a dedicated shared pin, and if required by the application, must be selected in the Clarity Designer GUI.

Another way to wake up the device is through Watch Dog Timer (WDT) expiry. The Watch Dog Timer is set as per application requirement – when the device needs to wake up and upon expiry of the timer, WDT sends a trigger to the Power Control Unit to wake up. In the Diamond Clarity Designer GUI, users can place some initial timers in the GUI (see the Using Diamond Clarity Designer GUI to Generate PMU section on page 19). If left black, these are set to 0 seconds. The values of the timers can be updated dynamically; this has to be taken care of through the application.

The device wake up can also be initiated internally through Always-On power domain blocks – PSEQ Control Block and via user I<sup>2</sup>C.

The device can always be reconfigured, even in Sleep State, but this will wake it up. This is **not** a recommended method to wake up, because all the changes made in the device will be lost (EBR contents and PMUCR settings could be updated during operation of the device). It reconfigures the device to its very first original bitstream and initializes everything. Although not recommended, it can be used to wake up the device.

Sleep State to Normal State transition has multiple triggers; however, there is no priority when it comes to these triggers. All triggers cause the same transition, and hence are dealt on a first come first serve basis.

#### 2.1.3. Types of Triggers

There are a number of triggers that cause the PMU to change the device from Normal State to Sleep State, and viceversa. These triggers can be categorized into two main types based on how the trigger is originated.

#### 2.1.3.1. Internal Triggers

These are triggers generated from the logic within the fabric.

Looking at the transition from Sleep State to the Normal State, it is seen that Watch Dog Timer expiry is an internal trigger.

The trigger that changes the device state from Normal to Sleep can be internal if generated within the FPGA fabric. This also contains decoded commands in internal Always-On logic that are sent from user I<sup>2</sup>C port from an external signal.

#### 2.1.3.2. External Triggers

These are triggers generated from external pin on General Purpose I/O (GPIO) pins.

For example, the Application Processor may require the device to go to Sleep. This signal, when directly routed to the SLEEP port of the PMU, can be considered an External Trigger.

#### 2.1.3.3. Recommendations

It is recommended that all triggers be internal, including ones changing from Normal State → Sleep State. This is further discussed in the Using the PMU section on page 9. Even if the request to place the device to Sleep State is coming off-chip, it is recommended that the request be processed and housekeeping taken care of, before generating a SLEEP signal.

The triggers causing the device to wake up from Sleep State  $\rightarrow$  Normal State can be either internal (WDT expiry) or external (user I<sup>2</sup>C/ External). The device cannot be woken up via FPGA fabric because the FPGA fabric is powered down.

#### 2.1.4. Using the PMU

The previous sections have touched on a few recommendations for changing states of the device. This section covers typical (and recommended) use case for the PMU. It is not mandatory to strictly adhere to this use case, but is provided as a guideline and best practices model.

It is essential to include the PMU IP in the FPGA design if it is to be able to place the CrossLink device into lower power Sleep State. Diamond Clarity Designer tool can be used to configure the PMU (see the Using Diamond Clarity Designer GUI to Generate PMU section on page 19). When instantiated in the design, PMU is always On, and uses the low speed clock from internal oscillator of the device to perform its operations.

#### 2.1.4.1. Recommended Use Case

A recommended use case scenario is controlling the PMU through a user implemented state machine. This state machine is unique to each application and controls the interface to the PMU through the FPGA fabric interface (SLEEP and 8-Bit Addressable PMUCR interface).

An external event or request to go to sleep can come to this state machine. The state machine then processes the request, manages the operation(s) that the CrossLink device is handling, performs housekeeping of these operation(s), updates the PMUCR (if needed) and then initiates the SLEEP signal.

The PMU IP available to the user does not implement any fixed state machines, because the requirements of each application is unique. PMU IP is a more open and simple interface that can be interfaced with the user state machine that will process the state transitions request. Any dynamic updates, as needed, for the PMU configuration can be done through 8-bit addressable PMUCR (see PMU Control Register (PMUCR) section on page 15). For example, the application processor can request the device to go to sleep for 2 hours. If the 2 hour time is different from what was initially programmed in the WDT, the state machine will have to update the WDT with the new 2 hour time and then initiate SLEEP.

PMUCR can be used to enable and set Watch Dog Timer, and to enable and disable various triggers. This interface is referred to as System Control Bus Interface (SCI Interface), and is accessed via the fabric using CIB interface signals. Usage of SCI interface is discussed in the PMU Control Bus and Primitive Attributes section on page 13.

Lastly, based on PMU configuration, the device can be woken up using I<sup>2</sup>C interface, or using PMUWKUP or USRWKUPN pins.

#### 2.1.4.2. Using SLEEP Signal

Lattice recommends that SLEEP signal in CrossLink devices be used under the recommended settings. When not used correctly, the device can stay in permanent Sleep State and not wake up.

Here are a couple of scenarios when SLEEP is directly routed to the PMU.

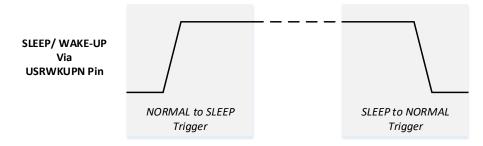

#### **Routing SLEEP signal to USRWKUPN Pin**

In CrossLink devices, the USRWKUPN pin is a dedicated dual purpose shared pin.

One of the functions of the pin is to be used as User Wake Up port. This function on the pin is hardwired and directly connected to the Power Management Unit (PMU). The other function of this pin is as a General Purpose IO. To use this pin as User Wake Up port, persistence on this pin must be turned On, otherwise it acts as a General Purpose Input/Output (GPIO) pin. Turning On persistence on this pin makes it available as GPIO during Normal State, and as User Wake Up pin during Sleep State.

Take an example when we need to just place the CrossLink device to sleep. The device is operating in the Normal State; and the SLEEP signal is directly routed to USRWKUPN pin.

The pin can then be used to place the device to Sleep State by toggling the signal high. When the device is in Sleep State, this pin resumes its wake up function (USRWKUPN) and can be used to wake up the device. USRWKUPN is active low and toggling this pin low initiates the trigger for the device to wake up.

So in Normal State, the pin acts as trigger to change state from Normal to Sleep, and when in Sleep State, it can be used to transition from Sleep to Normal.

Figure 2.3 shows a functional depiction of how the change in signal puts the device to sleep and wake up when routed to the same pin (USRWKUPN).

9

Figure 2.3. Using USRWKUPN Pin for sleep and wakeup (functional depiction, not timing)

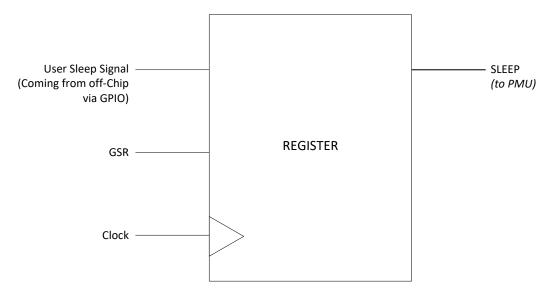

#### **Routing SLEEP signal to GPIO**

Another use case scenario is when SLEEP signal is routed to a General Purpose Input/Output (or GPIO) for the CrossLink device.

Take an example where the SLEEP signal needs to be directly routed to PMU. Routing SLEEP signal this way should always be avoided under all conditions, because it will not wake up the device once placed into Sleep State.

Let us look at what effects directly routing SLEEP signal has and a recommended workaround.

The device is operating in the Normal State; and the SLEEP signal is coming in to the PMU via GPIO routed through FPGA fabric. SLEEP signal is going high, and the PMU places the device in Sleep State.

Now, the device needs to be woken up (via any trigger). The fabric comes alive and GPIOs would be holding value before going to sleep. The signal drives high, routed through FPGA fabric, and to PMU that triggers the device to go to sleep. The device gets stuck in this permanent Sleep State when the SLEEP signal is using GPIO.

Lattice recommends that users follow the recommended method of using application specific state machine (discussed earlier in this section). If you need to use a GPIO for the SLEEP signal that needs to be directly fed into the PMU, then register this signal which is reset by a Global Set-Reset (GSR). By employing a GSR reset register, the PMU will never see the high when waking up the device and this will avoid glitches or placing the device in Sleep State inadvertently. Figure 2.4 shows the block diagram for the same.

Figure 2.4. Using GPIO for SLEEP when directly routed to PMU (functional depiction, not timing)

CrossLink devices retain configuration SRAM, EBR contents when in Sleep state. All the registers within the IPs (for example EBR registers), and PFU registers do not retain their state during the sleep mode. User I<sup>2</sup>C registers retain their state.

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 2.1.4.3. Global Clocks, Memories and PMU

Most FPGA designs use memories. The CrossLink device has built in Embedded Block RAM (EBR) blocks that are complemented by the LUT-based Distributed Memories.

When creating designs that employ EBRs or Distributed RAMs, use global clocks. Use of non-global clocks can potentially cause issues with memory contents retention/ corruption issues when changing states. When using non-global clocks, all read or write operations must be completed (and stopped) before entering the Sleep mode.

The guidelines under Recommended Use Case section on page 9 should be strictly followed when using non-global clocks in the designs. User state machine should take care of housekeeping when going into Sleep State. All activities related to memory contents must be stopped before the device goes into Sleep State to avoid potential memory corruption issues.

Diamond software identifies this situation and generates an appropriate warning for the user.

#### 2.1.4.4. State of the I/Os

CrossLink devices hold the state of the I/Os during Sleep State. The last value of each I/Os is held to avoid any issues with other devices connected downstream from the CrossLink devices. The Differential I/Os do not hold their value and are all tri-stated.

When the CrossLink device is coming out of Sleep State (that is device is waking up), the fabric becomes active and it is reset. As the fabric comes out of reset, it starts to drive some of the I/Os; the values it drives to can potentially conflict with the last frozen state of the I/Os.

This however does not affect how the CrossLink device operates. To avoid potential conflict between freeze I/Os and what the fabric will drive coming out of the Sleep State, we recommend some housekeeping before placing the device to sleep; like wrapping up the operations being performed, and ensuring the I/Os states before going to sleep is what they will still be after the device wakes up.

#### 2.1.4.5. Synthesis Attribute for PMU Primitive

Users can enable the PMU in their code. Watch Dog Timer user mode in Normal state is optional for PMU.

To avoid optimization of PMU when the user mode for Watch Dog Timer is not enabled, the wrapper should include the syn\_noprune attribute for the instance. This attribute prevents instance optimization for black-box module with unused output ports.

Here is an example of the syntax:

/\* synthesis syn noprune=1 \*/

#### 2.2. PMU Module, Primitive and Attributes

The HDL module gets generated for the PMU and serves as PMU Primitive. It can be used in user design via module generated by Clarity Designer, or as direct PMU Primitive instantiation. The block level diagram for HDL module is shown in Figure 2.5.

Certain inputs and outputs are optional based on the application/ design requirements. Clarity Designer provides these options and allows configurations needed for each unique application.

Figure 2.5. PMU HDL Primitive -PMUA

#### 2.2.1. PMU Port Definitions and Parameters

Table 2.1 on the next page describes the ports available in the PMU, along with their functions, and default values. When the PMU is not used in a design, it has certain default settings that can be different from the settings when it is used in a design. Table 2.1 provides values for both cases. The FPGA fabric interface that comprises of PMU Control Register and the SLEEP signal is tied low when PMU is not in use. When used, this interface is available to update the PMU settings as needed.

Watch Dog Timer (WDT) User Mode makes the WDT available for use in Normal State. During Sleep State, WDT is available for use by PMU and not available for the application.

**Table 2.1. PMU HDL Primitive Port Definitions**

| Port Name    | Description                                              | Width | Direction | Signal Source                    | Port Default | Optional Port<br>Requirements | Default GUI<br>Options | Note |

|--------------|----------------------------------------------------------|-------|-----------|----------------------------------|--------------|-------------------------------|------------------------|------|

| USRWKUPN     | User Provided Wake<br>Up Signal                          | 1     | Input     | External Pin                     | 1 –Disabled  | 0 – Enabled<br>1 – Disabled   | 1 –<br>Disabled        | 1, 3 |

| PMUWKUP      | PMU Wake Up<br>Signal coming from<br>Configuration Logic | 1     | Input     | Configuration<br>Logic/ User Pin | 0 – Disabled | 1– Enabled<br>0 – Disabled    | 1– Enabled             | 2, 3 |

| PMUCLK       | PMU Clock coming<br>in from Internal<br>Oscillator       | 1     | Input     | Internal Oscillator              | 0            | _                             | _                      | _    |

| USRCLK       | PMU Control                                              | 1     | Input     | From FPGA Fabric                 | 0            | _                             | _                      | _    |

| USRCS        | Register User                                            | 1     | Input     | From FPGA Fabric                 | 0            | _                             | _                      | _    |

| USRSTB       | Interface – Clock,<br>Chip Select,                       | 1     | Input     | From FPGA Fabric                 | 0            | _                             | -                      | 1    |

| USRADR[3:0]  | Standby, Address                                         | 4     | Input     | From FPGA Fabric                 | 0            | -                             | -                      | -    |

| USRDATA[7:0] | and Data                                                 | 8     | Input     | From FPGA Fabric                 | 0            | _                             | _                      | _    |

| SLEEP        | Sleep Signal                                             | 1     | Input     | From FPGA Fabric                 | 0            | _                             | -                      | 1    |

| USRWDTDONE   | Watch Dog Timer<br>User Mode Done<br>Signal              | 1     | Output    | To FPGA Fabric                   | _            | 1– Enabled<br>0 – Disabled    | 0 –<br>Disabled        | 3    |

| USRWDTINT    | Watch Dog Timer<br>User Mode<br>Interrupt Signal         | 1     | Output    | To FPGA Fabric                   |              | 1– Enabled<br>0 – Disabled    | 0 –<br>Disabled        | 3    |

#### Notes:

- 1. If the user does not select the User Wakeup option in the interface (see the Using Diamond Clarity Designer GUI to Generate PMU section on page 19), this port is set to DISABLED (or 1).

- 2. PMUWKUP is connected to I2C0 (of the two) user I<sup>2</sup>C which is hardwired to the PMU block.

- 3. The ports available in the wrapper change according to the selections made by users in the interface section. Some of these options are as follows:

- a. USRWKUPN (active low signal) is disabled by default. Selections in the interface change it as follows:

- When Enabled (0), the port is available in the wrapper.

- When Disabled, the port is not brought out as user port, and is connected to '1' inside the wrapper.

- b. PMUWKUP is the user I<sup>2</sup>C wake up. This port is available in the wrapper when user enables the User I<sup>2</sup>C Wake Up

- When Enabled (1), the port is available in the wrapper.

- When Disabled, the port is not brought out as user port, and is connected to '0' inside the wrapper.

- c. USRWDTDONE is the user mode for WDT in Normal mode.

- When Enabled (1), the port is available in the wrapper.

- When Disabled, the port is not brought out as user port (and can be left unconnected).

- d. USRWDTINT is the trigger for the user mode for WDT in Normal mode.

- When Enabled (1), the port is available in the wrapper.

- When Disabled, the port is not brought out as user port (and can be left unconnected).

#### 2.2.2. PMU Control Bus and Primitive Attributes

PMU Control Bus is an 8-bit addressable fabric interface through which the application can access various registers and settings in the PMU. This interface can be used to update the PMU Control Register (PMUCR), (if needed) before placing the device in the Sleep mode. Updating the PMUCR provides an ability to change these settings. If the user does not update the PMUCR before going to Sleep State, then the original settings used during configuration of the PMU are kept. If the PMUCR is updated, then new settings take effect, and the device operation is updated accordingly. Changes made to these settings when device is operational are effective as long as the device is not rebooted. If the device is rebooted, the initial settings are programmed in the registers.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal

Additionally, the PMU Control Bus interface can be used to update PMU Watch Dog Control Register 1 (PMUWDTCR1). If the Watch Dog Timers (WDT) is being used in the design, users are required to preset the three 32-bit WDT Count values for the PMU Watch Dog Counters (PMUWDTCNT1, PMUWDTCNT2, and PMUWDTCNT3). The details of each of these registers are discussed in the sections that follow.

One of the features of the PMU is that the settings and the attributes can be changed dynamically through the 8-bit addressable PMU Control Bus interface to the block, based on the application requirement; for example, an alarm or timer settings that can be set for different times. Understanding of these attributes is very essential if the user wishes to be able to change these settings.

Table 2.2 provides the list of addresses and their corresponding usage through the PMU Control Bus interface. Each address corresponds to the 8-bit data that can be written on to those registers. Few addresses are not available in the CrossLink device family; these are indicated as N/A (or Not Available).

Table 2.2. PMU Control Bus Address Mapping

| Address<br>USRADR[3:0] | Data USRDATA[7:0]  Usage |       | Usage                                 | Access |

|------------------------|--------------------------|-------|---------------------------------------|--------|

| 0000                   | N/A                      | _     | Not Available                         | _      |

| 0001                   | PMUCR                    | 8-bit | PMU Control Register                  | Write  |

| 0010                   | N/A                      | _     | Not Available                         | _      |

| 0011                   | PMUWDTCR1                | 8-bit | PMU Watch Dog Timer Control Register1 | Write  |

| 0100                   | PMUWDTCNT1_3             | 8-bit | PMU WDT Count Register1_3             | Write  |

| 0101                   | PMUWDTCNT1_2             | 8-bit | PMU WDT Count Register1_2             | Write  |

| 0110                   | PMUWDTCNT1_1             | 8-bit | PMU WDT Count Register1_1             | Write  |

| 0111                   | PMUWDTCNT1_0             | 8-bit | PMU WDT Count Register1_0             | Write  |

| 1000                   | PMUWDTCNT2_3             | 8-bit | PMU WDT Count Register2_3             | Write  |

| 1001                   | PMUWDTCNT2_2             | 8-bit | PMU WDT Count Register2_2             | Write  |

| 1010                   | PMUWDTCNT2_1             | 8-bit | PMU WDT Count Register2_1             | Write  |

| 1011                   | PMUWDTCNT2_0             | 8-bit | PMU WDT Count Register2_0             | Write  |

| 1100                   | PMUWDTCNT3_3             | 8-bit | PMU WDT Count Register3_3             | Write  |

| 1101                   | PMUWDTCNT3_2             | 8-bit | PMU WDT Count Register3_2             | Write  |

| 1110                   | PMUWDTCNT3_1             | 8-bit | PMU WDT Count Register3_1             | Write  |

| 1111                   | PMUWDTCNT3_0             | 8-bit | PMU WDT Count Register3_0             | Write  |

Typical PMU Control Bus write operation is demonstrated in Figure 2.6.

Figure 2.6. PMU Control Bus Write Operation

The PMU Control Bus does not support read operation, since PMU IP does not require data read back functionality.

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 2.2.2.1. PMU Control Register (PMUCR)

The first address (0001) through the PMU Control Bus interface corresponds to the PMU Control Register (PMUCR). This interface can be used to update the PMUCR, (if needed) before placing the device in the Sleep mode. If the user does not update the PMUCR before going to sleep, then the original settings from Diamond Clarity Designer configuration for the PMU are used. If the PMUCR is updated, then new settings takes into effect, and the device operation is updated accordingly.

PMU Control Register (PMUCR) is an 8-bit user accessible register that can be used to update the settings like how PMU wakes up the device; through Watch Dog Timer, or external wake up signal and so on.

During the PMU configuration through Diamond Clarity Designer, the PMUCR will be set to certain value based on the selected GUI options. These will become the initial settings for the PMU (and PMUCR), and these can be easily changed through the 8-bit addressable PMU Control Bus interface to the PMU.

Table 2.3 shows what each of the bits of 8-bit PMUCR stands for. For details on each attribute check the detailed attribute in Table 2.4.

Table 2.3. PMU Control Register (PMUCR) bit map

| Bit #     | Bit7  | Bit6   | Bit5   | Bit4    | Bit3  | Bit2 | Bit1  | Bit0  |

|-----------|-------|--------|--------|---------|-------|------|-------|-------|

| Attribute | PMUEN | UWDTEN | UWDTMD | UWDTINT | EXTEN | N/A  | I2CEN | WDTEN |

Table 2.4 shows the detailed selections of the all the bits along with the various values. PMUCR[7] bit is set to 1 when PMU is instantiated in the design; if PMU is not used, this bit is set to 0 and PMU is disabled.

Table 2.4. PMU Control Register (PMUCR) Component Port Definition

| <b>GUI Selection</b>                                             | Attribute        | PMUCR Bit | Description                               | Core         | <b>GUI Option</b> | Value Range                | Default Value | Notes |

|------------------------------------------------------------------|------------------|-----------|-------------------------------------------|--------------|-------------------|----------------------------|---------------|-------|

| _                                                                | PMUEN            | PMUCR[7]  | PMU Enable                                | _            | _                 | 1– Enabled<br>0 – Disabled | _             | 1, 2  |

| Enable User<br>Mode for<br>Watch Dog<br>Timer in<br>Normal State | UWDTEN           | PMUCR[6]  | User WDT<br>Enable                        | Core/<br>Sim | Check Box         | 1– Enabled<br>0 – Disabled | 0 – Disabled  | 3     |

| Mode<br>Selection                                                | UWDTMD           | PMUCR[5]  | User WDT<br>Mode<br>Selection             | Core/<br>Sim | Drop Down<br>Menu | COUNT_ONCE , COUNT_REPE AT | COUNT_ONCE    | 3     |

| Interrupt<br>Enable                                              | UWDTINT          | PMUCR[4]  | User WDT<br>Interrupt<br>Enable           | Core/<br>Sim | Check Box         | 1– Enabled<br>0 – Disabled | 1– Enabled    | _     |

| External User<br>Wake Up                                         | EXTEN            | PMUCR[3]  | External Pin<br>Interrupt<br>Enable       | Core/<br>Sim | Check Box         | 1– Enabled<br>0 – Disabled | 0 – Disabled  | -     |

|                                                                  | Not<br>Available | PMUCR[2]  | _                                         | _            | _                 | _                          | 0 – Disabled  | ı     |

| User I2C<br>Wake Up                                              | I2CEN            | PMUCR[1]  | Slave I2C<br>Interrupt<br>Enable          | Core/<br>Sim | Check Box         | 1– Enabled<br>0 – Disabled | 1– Enabled    | 1     |

| Watch Dog<br>Timer (WDT)<br>Expiry Wake<br>Up                    | WDTEN            | PMUCR[0]  | Watch Dog<br>Timer<br>Interrupt<br>Enable | Core/<br>Sim | Check Box         | 1– Enabled<br>0 – Disabled | 1– Enabled    | _     |

#### Notes:

- 1. PMUCR [7] is automatically set to ENABLED (1) when PMU is included in the design. If the PMU is not instantiated, then the PMUCR [7] is DISABLED (set to 0). In the disabled state, none of the features or interfaces of the PMU are available.

- 2. When the user enables the User mode for the built-In WDT in Normal Mode, then UWDTEN is set to ENABLED. The other GUI options should get active based on this check box, that is when the User mode for the WDT is ENABLED, and then the Mode Selection and Interrupt Enable Bit option will be available for users to set. UWDTEN and WDTEN are applicable in mutually exclusive states (Normal and Sleep), and they apply to the built-in Watch Dog Timer.

- 3. In Normal mode the Watch Dog Timer is available to access for user logic via PMU Control Bus by enabling the UWDTEN option. In sleep mode, the user logic is inactive and hence the Watch Dog Timer is not used for user logic. When set properly, WDT can be set to wake up the device from Sleep (to Normal State), once the WDT count expires.

#### 2.2.2.2. PMU Watch Dog Timer Control Register 1 (PMUWDTCR1) Settings

The next available address is 0011, and it corresponds to the PMU Watch Dog Timer Control Register 1 (PMUWDTCR1). This register is used for selecting the counter that will be used by the Watch Dog Counter (discussed in the following section) to wake up the device.

Although this is an 8-bit register, only the two lowest bits are available to select between the three counters available. Table 2.5 shows the bit mapping for PMUWDTCR1.

#### Table 2.5. PMU Watch Dog Timer Control Register 1 (PMUWDTCR1) bit map

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

|      | N/A  |      |      |      |      |      |      |

|      | N/A  |      |      |      |      |      | CNT) |

Settings for the two bits correspond to the following selections:

- 00 = WDT Disabled.

- 01 = Use PMUWDTCNT1 for WDT for Sleep Mode if WDT is enabled.

- 10 = Use PMUWDTCNT2 for WDT for Sleep Mode if WDT is enabled.

- 11 = Use PMUWDTCNT3 for WDT for Sleep Mode if WDT is enabled.

Table 2.6 lists the options available in the GUI for the selection of Watch Dog Timer to use when waking up. The default value (when WDT wake option is selection) is set to Watch Dog Counter # 1.

**Table 2.6. PMUWDTCR1 Definitions and Settings**

| GUI Selection                                                                    | Attribute | PMUWDTCR1<br>Bits | Description                       | Core/<br>Sim | GUI<br>Option        | Value Range                           | Default Value |

|----------------------------------------------------------------------------------|-----------|-------------------|-----------------------------------|--------------|----------------------|---------------------------------------|---------------|

| Select the<br>Watch Dog<br>Timer (WDT)<br>Counter that<br>wakes up the<br>device | SLPCNT    | 1:0               | Sleep Mode<br>WDT Count<br>Select | Core/<br>Sim | Drop<br>Down<br>Menu | COUNTER_1,<br>COUNTER_2,<br>COUNTER_3 | COUNTER_1     |

As an example, if the data 00110010 is written to the PMUWDTCR1, then the six MSB are ignored (that is 001100) and only the two LSBs are considered (10); these indicate to the PMU that it needs to wake up using the expiry of Watch Dog Counter #2 (PMUWDTCNT2), after Sleep phase initiation.

#### 2.2.2.3. Watch Dog Timer Counters and their Initialization Options

The next set of addresses from 0100 through 1111 on the PMU Control Bus corresponds to the Watch Dog Timer Counters. These are the counters that are set to a specific value (in terms of time) upon expiry of which the PMU wakes up the device.

There are three Watch Dog Timer Counters and each counter is 32 bit. Four addresses cover the 32-bit space for each counter (each address corresponding to 8-bits). The three counters are PMUWDTCNT1, PMUWDTCNT2, and PMUWDTCNT3.

The PMU WDT Count Registers, total 32 bits, holds the binary number of PMU clock cycle for built-in Watch Dog Timer to achieve desired timing. For normal application, user should set the counter prior to entering power saving mode if it is set to be used.

Each counter should be written sequentially from MSB to LSB; for example PMUWDTCNT1\_3 to PMUWDTCNT1\_0 when writing PMUWDTCNT1. On receiving interrupts, the PMU takes a clock cycle to activate the programmable sequence logic to perform the enter and exit power saving mode, so the logical PMU\_WDT count setting should be always larger than 1.

The mapping of each of the counters is shown in the following tables.

PMUWDTCNT1 comprises of four bytes PMUWDTCNT1\_3, PMUWDTCNT1\_2, PMUWDTCNT1\_1, and PMUWDTCNT1\_0. The bit mapping is as shown in the Table 2.7.

Table 2.7. PMU Watch Dog Timer Counter 1 (PMUWDTCNT1) bit map

| PMUWDTCNT1 [31:0]  |                    |                    |                    |  |  |  |

|--------------------|--------------------|--------------------|--------------------|--|--|--|

| PMUWDTCNT1_3 [7:0] | PMUWDTCNT1_2 [7:0] | PMUWDTCNT1_1 [7:0] | PMUWDTCNT1_0 [7:0] |  |  |  |

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

PMUWDTCNT2 comprises of four bytes PMUWDTCNT2\_3, PMUWDTCNT2\_2, PMUWDTCNT2\_1, and PMUWDTCNT2\_0. The bit mapping is as shown in the Table 2.8.

Table 2.8. PMU Watch Dog Timer Counter 2 (PMUWDTCNT2) bit map

| PMUWDTCNT2 [31:0]  |                    |                    |                    |  |  |  |

|--------------------|--------------------|--------------------|--------------------|--|--|--|

| PMUWDTCNT2_3 [7:0] | PMUWDTCNT2_2 [7:0] | PMUWDTCNT2_1 [7:0] | PMUWDTCNT2_0 [7:0] |  |  |  |

PMUWDTCNT3 comprises of four bytes PMUWDTCNT3\_3, PMUWDTCNT3\_2, PMUWDTCNT3\_1, and PMUWDTCNT3\_0. The bit mapping is as shown in the Table 2.9.

Table 2.9. PMU Watch Dog Timer Counter 3 (PMUWDTCNT3) bit map

| PMUWDTCNT3 [31:0]  |                    |                    |                    |  |  |  |

|--------------------|--------------------|--------------------|--------------------|--|--|--|

| PMUWDTCNT3_3 [7:0] | PMUWDTCNT3_2 [7:0] | PMUWDTCNT3_1 [7:0] | PMUWDTCNT3_0 [7:0] |  |  |  |

Each of these registers is 32-bit. All values in the 32-bit range are supported and user accessible. Table 2.10 provides the Clarity Designer GUI options.

Table 2.10. PMU Watch Dog Timer Counter 3 (PMUWDTCNT3) bit map

| GUI<br>Selection | Attribute         | PMUWDTCNT<br>Bits | Description                       | Core/<br>Sim | GUI<br>Option | Value Range<br>(hh:mm:ss) | Default<br>Value |

|------------------|-------------------|-------------------|-----------------------------------|--------------|---------------|---------------------------|------------------|

| WDT              |                   |                   | Preset value for                  | Core/        |               | 00:00:00                  |                  |

| Counter 1        | PMUWDTCNT1 [31:0] | 31:0              | WDT Counter 1                     | Sim          | Text Box      | То                        | 00:00:00         |

| Counter 1        |                   | WDI Counter 1     | 31111                             |              | 08:00:00      |                           |                  |

| WDT<br>Counter 2 | PMUWDTCNT2[31:0]  | 31:0              | Preset value for<br>WDT Counter 2 | Core/<br>Sim | Text Box      | 00:00:00                  |                  |

|                  |                   |                   |                                   |              |               | То                        | 00:00:00         |

|                  |                   |                   |                                   |              |               | 08:00:00                  |                  |

| WDT<br>Counter 3 | PMUWDTCNT3[31:0]  | 31:0              | Preset value for<br>WDT Counter 3 | Core/<br>Sim |               | 00:00:00                  |                  |

|                  |                   |                   |                                   |              | Text Box      | То                        | 00:00:00         |

| Counter 3        |                   |                   |                                   |              |               | 08:00:00                  |                  |

When configuring the PMU module in the Diamond Clarity Designer, users can preset the values of these registers to a set count value they would like their WDT to count to. These values serve as the initial values. If the application desires fixed counter values and does not need to change, set these counters in the Clarity Designer. If no value is provided, then these are all set to zeros (0s).

Clarity Designer require values to be set in terms of time, that is Hours: Minutes: Seconds (HH:MM:SS). At the application level, when accessing the registers through the PMU Control Bus Interface, the users need to provide the binary values corresponding to the desired time. The next section describes the conversion between the two.

The maximum value of the counter can be set to 8 hours.

#### **PMU Watch Dog Timer Count Calculation**

PMU runs on the clock from the internal oscillator. The default frequency for the Low Speed Oscillator is 10 kHz.

The user inputs to the WDT counters preset value is in Hours: Minutes: Seconds (HH:MM:SS). Clarity designer automatically converts the given value into corresponding 32-bit number. When the application is accessing the PMUWDTCNT registers, 32-bit value is expected.

For directly writing to the PMUWDTCNT registers, the time needs to be converted to its corresponding 32-bit value. The formula below can be used for settings these values. This is a simple example that shows the calculation.

| Frequency of the PMU Clock, f | = | 10 kHz                              |

|-------------------------------|---|-------------------------------------|

| Time Period, t                | = | 1/f                                 |

|                               | = | 100 μ sec                           |

| User Input (Time)             | = | hh:mm:ss                            |

|                               | = | 00:30:00                            |

| Total Number of Seconds, T    | = | hh*3600+mm*60+ss                    |

|                               | = | 0*3600+30*60+0                      |

|                               | = | 1800 sec.                           |

| Number of clock cycles, n     | = | T/t                                 |

|                               | = | 1800 sec / 100 μ sec                |

|                               | = | 18,000,000                          |

| PMUWDTCNT0                    | = | BINARY (n)                          |

|                               | = | BINARY (18,000,000)                 |

|                               | = | 00000001 00010010 10101000 10000000 |

#### 2.3. Using Diamond Clarity Designer GUI to Generate PMU

Diamond Clarity Designer can be used to generate an HDL wrapper for the PMU.

1. When a project is created, launch Clarity Designer using **Tools > Clarity Designer** option or by clicking on the button on the toolbar.

- 2. Provide the name of the project and select the HDL language of choice. The window appears as Figure 2.7.

- 3. Select the module you wish to generate. In this case, select **pmu**, under **Architecture\_Modules**, as shown in Figure 2.7.

Figure 2.7. Clarity Designer PMU Selection

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

FPGA-TN-02018-1.1

- 4. Double click on **pmu** to open another window (Figure 2.8) that requires you to provide an instance name (we use *pmu\_test\_instance* as our instance name for example),

- 5. Click Customize.

Figure 2.8. PMU Instance Name Options Window

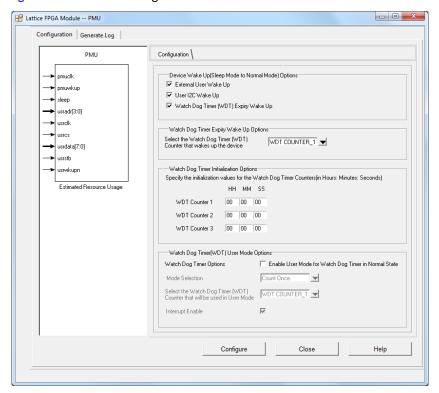

6. The next screen shows the various options to configure the PMU. All these options have been discussed in the earlier sections. Figure 2.9 shows the Configuration GUI.

Figure 2.9. PMU Configuration GUI Window

- 7. When all selections are made, click **Configure** button and then click **Close** button.

- 8. Click **Generate** button to include the SBX file in the Diamond project file.

If you need to include the HDL file, you can select the option to *add an existing file*, browse to the Clarity Designer project location and add the HDL file.

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

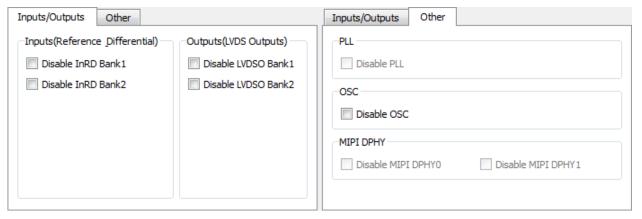

## 3. User Standby Mode during Normal State

User Standby Mode for CrossLink devices is useful in reducing power consumption when the device is in operation state, that is Normal State. User Standby Mode is a dynamically controlled option where some blocks can be placed in a User Standby Mode when the block is not required by the application. The reduction in power in achieved by placing these blocks in a low leakage state.

Take care when enabling the User Standby Mode for the blocks. This renders the blocks non-functional. Only the block capable of being placed in User Standby Mode should be placed in the state if it is not used in the application.

This feature is available only in Normal State. Sleep State overrides the Standby Mode, and places the whole device in lower power state.

Table 3.1 provides a list of blocks that have User Standby Mode and the signal required to place it in a Standby Mode.

Table 3.1. Blocks Supporting User Standby Mode

| Block     | User Standby Control Signal                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------|

| PLL       | Through User Standby (USRSTDBY) Signal                                                                                 |

| 10        | Through LVDS output buffer disable (per bank control) and INR disable (per bank control) (BCINRD and BCLVDSOB signals) |

| OSC       | Through OSC Enable port                                                                                                |

| MIPI DPHY | Through the USRSTDBY port                                                                                              |

#### 3.1. Usage of User Standby Mode

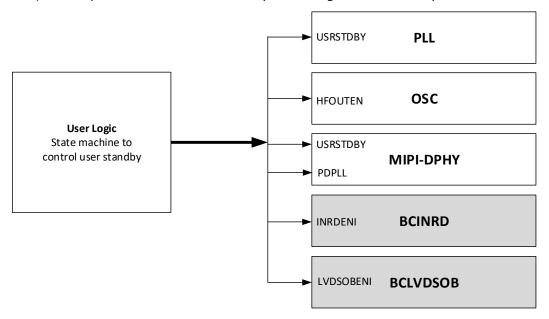

Each block with User Standby Mode option has a signal that can be accessed through FPGA fabric via soft logic. Unlike the Power Management Unit, there is no controller available in the hardware. Application should include a soft controller for accessing User Standby Mode features. This soft controller can place the (unused) blocks in the User Standby Mode, and hence provide the power savings.

Figure 3.1 gives an example block diagram of the User Standby Mode use case. The diagram shows a soft user logic (like a state machine) that can place each block in User Standby Mode – together or selectively.

Figure 3.1. User Standby Mode Use Case Example Block Diagram

The next sections discuss how each of the blocks can be placed in User Standby Mode, the signals that can be used, and recommendations.

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

#### 3.1.1. User Standby Mode for PLL

The CrossLink device PLL contains a User Standby Mode that allows the PLL to be placed into a standby state to save power when not needed in the design. User Standby Mode is very similar to holding the PLL in reset since the Voltage Controlled Oscillator (VCO) is turned off and needs to regain lock when exiting standby. In both cases, reset and standby mode, the PLL retains its programming.

When generating the PLL using Diamond Clarity Designer, the standby option can be enabled by checking **Provide Standby Port** under **Optional Ports** tab in the PLL configuration GUI. This adds the User Standby Port (USRSTDBY) which is an active high signal.

This port can then be connected to the soft controller for dynamic control during periods when PLL is not required.

#### 3.1.2. User Standby Mode for Oscillator

The CrossLink device includes an internal oscillator (OSCI) that generates a high frequency output and a low frequency output. Low frequency output, running 10 kHz is always on output and is used by blocks like Power Management Unit (PMU).

The high frequency output can generate maximum 48 MHz clock, with output divider settings at 1, 2, 4 and 8. The high frequency output clock can be turned off for power savings. The signal that controls the high frequency output clock is High Frequency Output Enable (or HFOUTEN).

HFOUTEN is an active high signal, and when high, turns off the high frequency of the internal oscillator.

#### 3.1.3. User Standby Mode for MIPI DPHY

DPHY block in the CrossLink device can also be placed in a lower User Standby Mode in *Normal State* when it is not required. There are two signals that can place the block in standby – USRSTDBY and PDPLL.

User Standby signal for DPHY (or USRSTDBY) is an active high signal that can power down the DPHY block. USRSTDBY signal is always included in the module generated using Diamond Clarity Designer, during both modes – Transmit and Receive.

Power Down PLL (PDPLL) is also an active high signal and can power down the PLL for the DPHY block. Powering down the PLL resets the PLL, and thus it can be used to reset the DPHY PLL. PDPLL signal is always included in the module generated using Diamond Clarity Designer, during Transmit mode. If the application does not require DPHY PLL block to be powered down, then this signal should be tied low (0).

#### 3.1.4. User Standby Mode for Inputs and Outputs

Referenced, differential and LVDS I/O standards consume more power than other I/O standards and are not always required to be active. Bank Controller allows the designer to turn these I/Os off dynamically on a per-bank selection. The Dynamic INRD (input referenced and differential I/Os) is used to turn off referenced and differential inputs. Dynamic LVDS control is used to turn off the LVDS output driver.

These options are available during *Normal State* only. In order to use these feature, the application must instantiate the primitives that control these bank controllers. Primitives and corresponding simulation behavior are discussed in the sections below. The control signals to enable and disable this feature has to be controlled by user logic.

Each of the bank controllers – INRD and LVDSOB work independent of each other.

#### 3.1.4.1. Bank Controller for Input Reference and Differential

In the CrossLink device, the Dynamic Bank Controller is used to power down banks that have Referenced and Differential inputs. The control is dynamic and if needed can release these inputs, including bidirectional I/Os. The next sections discuss the primitive and simulation of BCINRD.

#### **BCINRD Primitive**

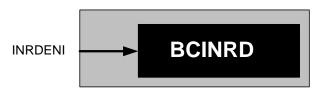

BCINRD Dynamic Bank Controller is represented with primitives as shown in Figure 3.2. Each instantiation controls a single bank; so if the control is required for both banks, two BCINRD primitives have to be instantiated, one for each bank (bank 1 and bank 2).

This disables the referenced and differential receivers and any bank controller reference circuits that consume dynamic power, resulting in reduction in power consumption by these circuits. The Inputs Reference and Differential Enable (or INRDENI) signal is an active high signal that can place these inputs in User Standby Mode.

Figure 3.2. Primitive for Bank Controller for Inputs - Referenced and Differential

#### **BCINRD Attributes**

Table 3.2 shows the attributes for the BCINRD, with values 1 and 2 representing each bank.

**Table 3.2. BCINRD Primitive Attributes**

| Port    | Attribute | Value | Default | Description                                          |

|---------|-----------|-------|---------|------------------------------------------------------|

| INRDENI | _         | _     | _       | Dynamic signal to enable and disable Bank INRD       |

| _       | BANKID    | 1, 2  | 2       | Bank ID for each bank for Dynamic power control INRD |

#### **BCINRD Simulation**

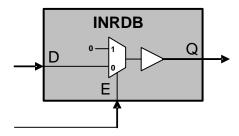

For application utilizing BCINRD, Diamond only supports post-Place & Route simulation. The functional diagram for the simulation model and simulation behavior for each inputs is as shown in Figure 3.3.

For functional simulation, that is before Place & Route, the design requires users to manually instantiate the simulation primitives as per Figure 3.3 (INRDB) on their inputs and bidirectional buffers that are affected by the bank controller.

Figure 3.3. INRDB Simulation Primitive

Table 3.3 shows the behavior of the INRDB simulation primitive.

**Table 3.3. BCINRD Simulation Behavior**

| Port | Port Name for Input Buffer | Output       |

|------|----------------------------|--------------|

| D    | Input                      |              |

| E    | Enable                     | _            |

| Q    | Output                     | 0, when E =1 |

|      |                            | D, when E=0  |

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 3.1.4.2. Bank Controller for LVDS Output Buffers

In the CrossLink device, the Dynamic Bank Controller is used to power down banks that have LVDS Outputs. The control is dynamic and can release these outputs as needed. The primitive and simulation of BCINRD is detailed next.

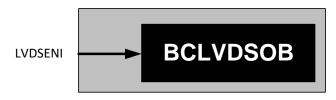

#### **BCLVDSOB Primitive**

BCLVDSOB Dynamic Bank Controller is represented with primitives as shown in Figure 3.4. Each instantiation controls a single bank; so if the control is required for both banks, two BCLVDSOB primitives have to be instantiated, one for each bank (Bank 1 and Bank 2).

This disables the LVDS output receiver circuits that consume dynamic power, resulting in reduction in power consumption by these circuits. The LVDS Output Enable (or LVDSENI) signal is an active high signal that can place these outputs in User Standby Mode.

Figure 3.4. Bank Controller for LVDS Outputs Primitive

#### **BCLVDSOB Attributes**

Table 3.4 shows the attributes for the BCLVDSOB, with values 1 and 2 representing each bank.

**Table 3.4. BCLVDSOB Primitive Attributes**

| Port    | Attribute | Value | Default | Description                                                  |

|---------|-----------|-------|---------|--------------------------------------------------------------|

| LVDSENI | _         | _     | _       | Dynamic signal to enable and disable Bank LVDS Outputs       |

| _       | BANKID    | 1, 2  | 2       | Bank ID for each bank for Dynamic power control LVDS Outputs |

#### **BCLVDSOB Simulation**

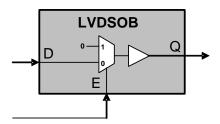

For application utilizing BCLVDSOB, Diamond only supports post-Place & Route simulation. The functional diagram for the simulation model and simulation behavior for each inputs is as shown in Figure 3.5.

For functional simulation, that is before Place & Route, the design requires users to manually instantiate the simulation primitives as per Figure 3.5 (LVDSOB) on their output buffers that are affected by the bank controller.

Figure 3.5. LVDSOB Simulation Primitive

Table 3.5 shows the behavior of the LVDSOB simulation primitive.

**Table 3.5. BCLVDSOB Simulation Behavior**

| Port | Port Name for Output Buffer | Output                                     |

|------|-----------------------------|--------------------------------------------|

| D    | Input                       | _                                          |

| E    | Enable                      | _                                          |

| Q    | Output                      | Z (High Impedance), when E =1; D, when E=0 |

## 4. Power Consumption and Calculation

Diamond software includes a Power Calculator tool that can determine the power consumption of the CrossLink devices. Power Calculator is the fastest power simulation tool available in the industry. It offers two modes — *Estimation mode* (for what-if analysis) and *Calculation mode* (for the more accurate application-specific power consumption by importing NCD design files). The engine performs each calculation quickly and accurately.

When running the Power Calculator tool in **Estimation mode**, designers provide estimates of the utilization of various components and the tool provides an estimate of the power consumption. This is a good start, especially for what-if analyses and device selection.

**Calculation mode**, on the other hand, is a more accurate approach, where the designer imports the actual device utilization by importing the post place and route netlist design file (or NCD) file. Additionally, Power Calculator supports features like Trace Report (or TWR) import, to get the clock frequencies for various clocks. Trace Report only includes frequencies of the clocks nets that are constrained in the Preference file. Users are still required to provide frequencies of the clocks that are not included in Preference file (and hence the Trace Report).

The default Activity Factor (AF%) for dynamic power calculation is set to 10% in the Power Calculator. Users can change the default AF for the entire project or for each clock net individually. Activity Factor is discussed in detail in the Activity Factor Calculation section on page 28.

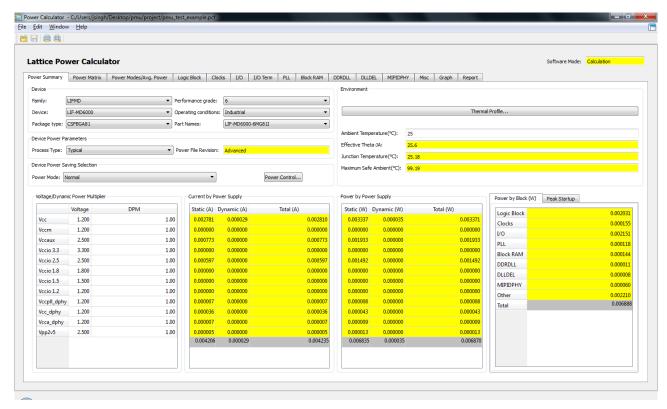

#### 4.1. Power Calculator

Refer to the Diamond<sup>®</sup> Tutorial under Diamond Startup Page. When you go through the procedure, the Lattice Power Calculator main window appears as shown in Figure 4.1

Figure 4.1. Power Calculator (Summary Tab for CrossLink Devices)

FPGA-TN-02018-1 1

It is important to understand how the options available in Power Calculator affect the power. For example, if the ambient temperature is changed, the junction temperature is affected according to the following equation:

$$T_J = T_A + \theta_{JA \text{ EFFECTIVE}} * P$$

Where  $T_J$  and  $T_A$  are the junction and ambient temperatures, respectively, and P is the power.

$\theta_{\text{JA EFFECTIVE}}$  is the effective thermal impedance between the die and its environment.

The junction temperature is directly dependent on the ambient temperature. An increase in  $T_A$  increases  $T_J$  and result in an increase of the static leakage component.

Power can be affected by selecting the Process Type or the frequency at which the application runs. Process primarily changes the static leakage (or Static Power) and frequency changes dynamic power (increasing the frequency of toggling increases the dynamic component of power).

#### 4.1.1. Typical and Worst Case Process

Process variation is a naturally occurring variation in the attributes of transistors (length, widths, oxide thickness) when integrated circuits are fabricated. Process variation causes measurable and predictable variance in the output performance of all circuits.

Diamond Power Calculator provides option to select the Typical (the mean current/ power of distribution) and Worst Case (the maximum current/ power of distribution) as a result of the variation. Process variation primarily affects the static leakage component of the device.

**Process Type** selection in the Power Calculator allows users to understand the current and power variation of the devices, and predicts accurate results that are application specific. These can be used for power supply design, battery capacity design and thermal management for each application.

#### 4.1.2. Junction Temperature

Junction temperature is the temperature of the die during operation. It is one of the most important factors that affects the device power. For a fixed junction temperature, voltage and device package combination, static power is fixed.

Ambient temperature affects the junction temperature. Devices operating in a high-temperature environment have higher leakage since their junction temperature is higher. Power Calculator models the interdependence of ambient and junction temperature. When the user provides an ambient temperature, it is rolled into an algorithm that calculates the junction temperature and power through an iterative process to find the thermal equilibrium of the system (device running with the design) with respect to its environment (T<sub>A</sub>, airflow and so on).

Thermal impedance plays an important role in determining the devices behavior, and the tool takes it into account to calculate maximum safe ambient temperature. See the Thermal Management section on page 32 for details on how the Power Calculator uses thermal impedances.

#### 4.1.3. Maximum Safe Ambient Temperature

Maximum Safe Ambient Temperature is one of the most important numbers displayed in the Summary tab of the Power Calculator. This is the maximum ambient temperature at which the device application can run without violating the junction temperature limits for the grade of the device (commercial or industrial).

Power Calculator uses an algorithm to accurately predict this temperature. The algorithm adjusts itself as the user changes options such as voltage, process, frequency, activity factor, thermal impedance and so on (or any factor that may affect the power dissipation of the device).

Thus it becomes extremely important to provide more accurate inputs to the tool, for more accurate predicted results.

#### 4.1.4. Operating Temperature Range

26

When designing a system, engineers must make sure a device operates at specified temperatures within the system environment. This is particularly important to consider before a system is designed. With Power Calculator, users can predict device thermodynamics and estimate the dynamic power budget. The ability to estimate device's operating temperature prior to board design also allows the designer to better plan for power budgeting and thermal management.

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Although total power, ambient temperature, thermal resistance and airflow all contribute to device thermodynamics, the junction temperature as specified in Operating Conditions in the Datasheet is the key to device operation.

The allowed junction temperature range is 0°C to 85°C for commercial grade devices and –40°C to 105°C for industrial grade devices. If the junction temperature of the die is not within these temperature ranges, the performance, reliability and functionality can get affected.

#### 4.1.5. Dynamic Power Multiplier

In general, for semiconductors devices, the dynamic power consumption is independent of the variation in process and temperature. Power Calculator follows this rule, and hence any changes to either process or temperature will not change the dynamic current/ power.