# MachXO2 Family Data Sheet Supplement for LVCMOS10 Inputs and BIDIs

## **Data Sheet**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| 1    | Overview                                                 | 1                 |

|------|----------------------------------------------------------|-------------------|

| 2.   | sysI/O Recommended Operating Conditions                  | <del>-</del><br>4 |

| 3.   | sysI/O Single-Ended DC Electrical Characteristics        | 4                 |

| Tec  | sysI/O Single-Ended DC Electrical Characteristics        | 5                 |

| Rev  | ision History                                            | 6                 |

|      |                                                          |                   |

|      |                                                          |                   |

|      |                                                          |                   |

|      |                                                          |                   |

| FI   | gures                                                    |                   |

| Figu | ıre 1.1                                                  | 4                 |

|      |                                                          |                   |

|      |                                                          |                   |

|      |                                                          |                   |

| _    |                                                          |                   |

| Ta   | bles                                                     |                   |

| Tab  | le 2.1. sysI/O Recommended Operating Conditions          | 4                 |

| Tah  | le 3.1 syst/O Single-Ended DC Electrical Characteristics | 4                 |

## 1. Overview

This document is a supplement to the MachXO2 Family Data Sheet and provides the following additions or customizations:

Support for LVCMOS10R33 and LVCMOS10R25 inputs and BIDIs for all ZE devices and –6 speed grade for HE and HC devices

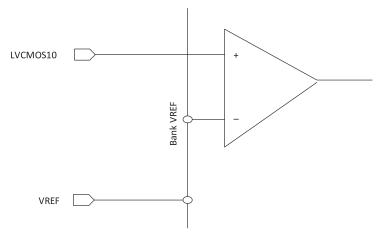

Figure 1.1.

## 2. sysI/O Recommended Operating Conditions

Table 2.1. sysI/O Recommended Operating Conditions

| Standard    | V <sub>CCIO</sub> (V) |      |       |      | V <sub>REF</sub> (V) |      |

|-------------|-----------------------|------|-------|------|----------------------|------|

|             | Min.                  | Тур. | Max.  | Min. | Тур.                 | Max. |

| LVCMOS10R33 | 3.135                 | 3.3  | 3.6   | 0.35 | 0.5                  | 0.65 |

| LVCMOS10R25 | 2.375                 | 2.5  | 2.625 | 0.35 | 0.5                  | 0.65 |

## 3. sysI/O Single-Ended DC Electrical Characteristics

Table 3.1. sysI/O Single-Ended DC Electrical Characteristics<sup>1</sup>

| Input/Output | V <sub>IL</sub> |            | V <sub>IH</sub> |          | V <sub>OL</sub> Max. | V <sub>он</sub> Min. | I <sub>OL</sub> (mA) | I <sub>OH1</sub> (mA) |

|--------------|-----------------|------------|-----------------|----------|----------------------|----------------------|----------------------|-----------------------|

| Standard     | Min. (V)        | Max. (V)   | Min. (V)        | Max. (V) | (V)                  | (V)                  |                      |                       |

| LVCMOS10R33  | -0.3            | VREF - 0.1 | VREF + 0.1      | 3.465    | 0.40                 | N/A Open             | 16, 12, 8, 4         | N/A Open              |

|              |                 |            |                 |          |                      | Drain                |                      | Drain                 |

| LVCMOS10R25  | -0.3            | VREF - 0.1 | VREF + 0.1      | 3.465    | 0.40                 | N/A Open             | 12, 8, 4             | N/A Open              |

|              |                 |            |                 |          |                      | Drain                |                      | Drain                 |

<sup>1.</sup> For I/Os with mixed voltage support, V<sub>OH</sub> follows respective sysI/O bank V<sub>CCIO</sub> supply voltage, and V<sub>IL</sub> / V<sub>IH</sub> follows the I/O signaling standard.

## **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

# **Revision History**

## Revision 1.3, July 2021

| Section                           | Change Summary                                                                             |

|-----------------------------------|--------------------------------------------------------------------------------------------|

| sysI/O Single-Ended DC Electrical | Added note 1 in Table 3.1 to better clarify the voltage specifications for I/Os with mixed |

| Characteristics                   | voltage support.                                                                           |

### Revision 1.2, November 2019

| Section     | Change Summary                                          |  |

|-------------|---------------------------------------------------------|--|

| All         | Changed document number from DS1035 S to FPGA-DS-02062. |  |

|             | Updated document template.                              |  |

| Disclaimers | Added this section.                                     |  |

### Revision 1.1, November 2015

| Section  | Change Summary                        |

|----------|---------------------------------------|

| Overview | Corrected typo error in this section. |

### Revision 1.0, November 2015

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

www.latticesemi.com