# Lattice Synthesis Engine for Diamond User Guide

## Copyright

Copyright © 2019 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. All other trademarks are the property of their respective owners.

### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

## **Type Conventions Used in This Document**

| Convention                                                                                        | Meaning or Use                                                                           |  |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| <b>Bold</b> Items in the user interface that you select or click. Text t into the user interface. |                                                                                          |  |  |

| <italic></italic>                                                                                 | Variables in commands, code syntax, and path names.                                      |  |  |

| Ctrl+L                                                                                            | Press the two keys at the same time.                                                     |  |  |

| Courier                                                                                           | Code examples. Messages, reports, and prompts from the software.                         |  |  |

|                                                                                                   | Omitted material in a line of code.                                                      |  |  |

|                                                                                                   | Omitted lines in code and report examples.                                               |  |  |

| [ ]                                                                                               | Optional items in syntax descriptions. In bus specifications, the brackets are required. |  |  |

| ( )                                                                                               | Grouped items in syntax descriptions.                                                    |  |  |

| { }                                                                                               | Repeatable items in syntax descriptions.                                                 |  |  |

|                                                                                                   | A choice between items in syntax descriptions.                                           |  |  |

|                                                                                                   |                                                                                          |  |  |

## **Contents**

### Lattice Synthesis Engine for Diamond User Guide Design Flow Overview: User Interface 5 LSE Strategy Settings in Diamond 6 LSE Strategy Option Settings 7 Allow Duplicate Modules 9 Carry Chain Length 9 Command Line Options 9 Decode Unreachable States 9 Disable Distributed RAM 10 DSP Style 10 DSP Utilization 10 EBR Utilization 10 Fix Gated Clocks 10 Force GSR 11 FSM Encoding Style 11 Hardware Evaluation 11 Intermediate File Dump 12 Loop Limit 12 Macro Search Path 12 Max Fanout Limit 12 Memory Initial Value File Search Path 13 MUX Style 13 Number of Critical Paths 13 Optimization Goal 13 Propagate Constants 14 RAM Style 15 Remove Duplicate Registers 15 Remove LOC Properties 15 Resolved Mixed Drivers 15 Resource Sharing 16 ROM Style 16 Target Frequency 17 Use Carry Chain 17

```

Use IO Insertion 17

Use IO Registers 17

Use LPF Created from SDC in Project 17

VHDL 2008 18

Design Flow Overview: Command Line 18

Preparing the Input 22

Constraint Files 23

Specifying Constraints and Attributes 23

Defining Synthesis Constraints Using LDC Editor 24

Defining Synthesis Constraints Using Text Editor 24

Defining Clocks 25

Defining Generated Clocks 26

Defining Clock Groups 28

Setting Input Delays 29

Setting Output Delays 30

Defining Minimum Delay Paths 31

Defining Maximum Delay Paths 31

Setting Up Attributes 34

black_box_pad_pin 35

full case 36

GSR 36

loc 37

parallel case 38

syn black box 39

syn encoding 40

syn_force_pads 44

syn_hier 46

syn insert pad 46

syn keep 49

syn maxfan 51

syn_multstyle 51

syn noprune 54

syn pipeline 56

syn_preserve 58

syn_ramstyle 60

syn replicate 62

syn_romstyle 64

syn_srlstyle 65

syn sharing 68

syn_state_machine 70

syn use carry chain 74

syn_useenables 75

syn useioff 77

translate off/translate on 77

Inferring Block Primitives 78

Inferring Memory 78

Inferring RAM 79

Inferring RAM with Synchronous Read 81

Inferring Dual-Port RAM 83

Inferring ROM 86

Initializing Inferred RAM 87

Creating Memory Initialization File 91

Inferring Lattice DSP Blocks Using Behavioral HDL 92

```

MULT9X9 **92** MULT18X18 92 MULT36X36 92 MULTADDSUB 95 MULTADDSUBSUM 98 MULTACC 103

Optimizing LSE for Area and Speed 105

Specifying Optimization Options 107

Preserving Objects from Optimization 107

Setting Fanout Limits 107 Sharing Resources 108

Inserting I/Os 108

Optimizing State Machines 108

Working with Gated Clocks 108

Analyzing the Synthesis Report 108

Viewing Logs and Reports 108

Cross-Probing from Reports to Schematics 110

Navigating Messages/Warnings 110

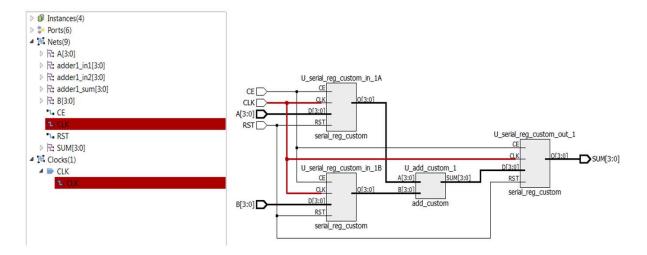

Analyzing Using Netlist Analyzer 112

Simulating the Synthesis Output 114

Designing with Modules/IP 116

Using IPexpress Modules 117

Using Clarity Modules 118

Creating Your Own Black Box Modules 118

Designing with Lattice Library Primitives 120

Revision History 120

Index 121

## Lattice Synthesis Engine for Diamond User Guide

Lattice Synthesis Engine (LSE) is the fully-integrated synthesis tool packaged with Lattice Diamond software, custom-built for many Lattice products. Depending on the design, LSE can create better resource utilization and faster timing than other synthesis tools. LSE complements the suite of tools available in the Lattice Diamond software and provides complete and comprehensive FPGA/CPLD synthesis solutions.

#### LSE offers the following advantages:

- lt's the built-in Lattice synthesis tool optimized for use with Lattice devices.

- Provides granular control through tool options.

- Supports industry standard Verilog (Verilog 2001 and before) and VHDL (VHDL 2008 and before) including mixed language, along with industry standard attributes and SDC constraints. Enables the user to easily synthesize existing designs using LSE.

#### **Note**

LSE follows the IEEE standards listed below.

- ▶ 1076-1987 IEEE Standard VHDL Language Reference Manual

- ▶ 1076-1993 IEEE Standard VHDL Language Reference Manual

- > 1076-2008 IEEE Standard VHDL Language Reference Manual

- ▶ 1364-1995 IEEE Standard Hardware Description Language Based on the Verilog(R) Hardware

- ▶ 1364-2001 IEEE Standard Verilog Hardware Description Language

- > 1364-2005 IEEE Standard for Verilog Hardware Description Language

Only synthesis constructs described by these standards are supported.

Provides GUI tool support for constraint entry (LDC Editor) and schematic netlist viewing and analysis (Netlist Analyzer), reducing the time required for design entry and analysis.  Offers a choice of optimization goals: Area, Balanced, and Timing enabling the user to highlight which design goals should be emphasized.

This document describes the basic features of LSE. Sections include design flow overviews, preparing HDL source files, setting constraints, inferring block primitives, setting optimization options, analyzing the synthesis report, using Netlist Analyzer, analyzing timing, simulating, designing with modules, and designing with intellectual property (IP).

## **Design Flow Overview: User Interface**

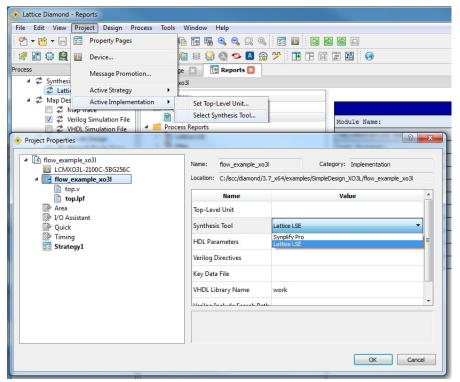

LSE is integrated into the Lattice Diamond software. To specify LSE as the synthesis tool:

Choose Project > Active Implementation > Select Synthesis Tool.

The Project Properties dialog box opens with the active implementation selected, as shown in Figure 1.

Figure 1: Selecting LSE as Synthesis Tool in Lattice Diamond Software

- In the dialog box, double-click the Synthesis Tool row in the Value column.A menu drops down.

- 3. Choose Lattice LSE.

- 4. Click OK.

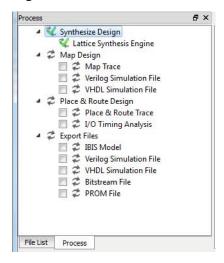

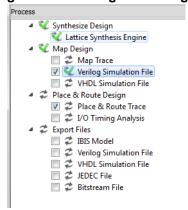

- 5. Start the Synthesize Design process. In the Process View (Figure 2), do one of the following:

- Select Synthesize Design in the Process view, and choose Process

Run.

- Right-click the Synthesize Design process and choose Run.

- Double-click the Synthesize Design process.

Figure 2: Diamond Software Process View

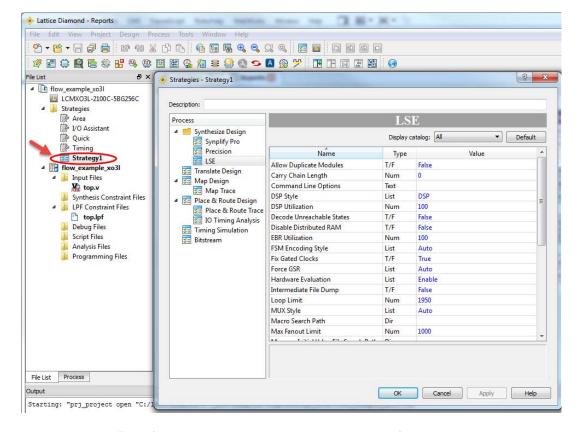

## **LSE Strategy Settings in Diamond**

LSE strategies provide a unified view of all the options related to synthesis. LSE strategy options are listed in the LSE Strategy dialog box. Open the dialog box by double-clicking a strategy name in the File List view, as shown in Figure 3.

Figure 3: Opening the LSE Strategy Dialog Box

For information about an option, select it. A brief description appears at the bottom of the dialog box. Press F1 to open this guide and see the full description in the Diamond online help.

For more information on optimizing a strategy for area or timing, see "Optimizing LSE for Area and Speed" on page 105.

## LSE Strategy Option Settings

Table 1 lists LSE strategy option settings available in the Diamond Strategy Setting dialog box.

**Table 1: Strategy Option Settings**

| Name                    | Туре       | Value                     | Targeted Switch              |

|-------------------------|------------|---------------------------|------------------------------|

| Allow Duplicate Modules | True/False | False(Default)            | -allow_duplicate_modules     |

| Carry Chain Length      | Integer    | 0 (not limited) (Default) | -carry_chain_length          |

| Command line Options    | Text       | Text                      | (flags each preceded by '-') |

| DSP Style               | List       | DSP(Default)              | -use_dsp                     |

| DSP Utilization         | Num        | 100(Default)              | -dsp_utilization             |

**Table 1: Strategy Option Settings (Continued)**

| Name                                     | Туре       | Value                                                          | Targeted Switch            |

|------------------------------------------|------------|----------------------------------------------------------------|----------------------------|

| Decode Unreachable<br>States             | True/False | False (Default)                                                | -decode_unreachable_states |

| Disable Distributed RAM                  | True/False | False (Default)                                                |                            |

| EBR Utilization                          | Float      | 100 (Default, in %)                                            | -bram_utilization          |

| FSM Encoding Style                       | String     | Binary (Default)   One-Hot  <br>Gray                           | -fsm_encoding_style        |

| Fix Gated Clocks                         | True/False | True (Default)                                                 | -fix_gated_clocks          |

| Force GSR                                | String     | Yes   No<br>  Auto (Default)                                   | -force_gsr                 |

| Hardware Evaluation                      | List       | Enable (Default)   Disable                                     | -dt                        |

| Intermediate File Dump                   | True/False | False (Default)                                                | -ifd                       |

| Loop Limit                               | Number     | 1950 (Default)                                                 | -loop_limit                |

| Mux Style                                | String     | Auto (Default)   PFU Mux  <br>L6Mux Single   L6Mux<br>Multiple | -mux_style                 |

| Macro Search Path                        | Text       |                                                                | -p                         |

| Max Fanout Limit                         | Integer    | 1000 (Default)                                                 | -max_fanout                |

| Memory Initial Value File<br>Search Path | Text       |                                                                | -p                         |

| Number of Critical Paths                 | Integer    | 3 (Default)                                                    | -twr_paths                 |

| Optimization Goal                        | String     | Area   Timing   Balanced                                       | -optimization_goal         |

| Use LPF Created from SDC in Project      | True/False | True (Default)   False                                         | -lpf                       |

| Propagate Constants                      | True/False | True (Default)                                                 | -propagate_constants       |

| Ram Style                                | String     | Auto (Default)   Distributed<br>  Block_ RAM   Registers       | -ramstyle                  |

| Rom Style                                | String     | Auto (Default)   ebr   Logic                                   | -romstyle                  |

| Remove Duplicate<br>Registers            | True/False | True (Default)                                                 | - remove_duplicate_regs    |

| Remove LOC properties                    | List       | Off (Default)   On                                             | -r                         |

| Resolve Mixed Drivers                    | True/False | False (Default)                                                | -resolve_mixed_drivers     |

| Resource Sharing                         | True/False | True (Default)                                                 | -resource_sharing          |

| Target Frequency                         | Float      | 200 (Default, in MHz)                                          | -frequency                 |

| Use Carry Chain                          | True/False | True (Default)                                                 | -use_carry_chain           |

| Use IO Insertion                         | True/False | True (Default)                                                 | -use_io_insertion          |

**Table 1: Strategy Option Settings (Continued)**

| Name             | Туре       | Value           | Targeted Switch |

|------------------|------------|-----------------|-----------------|

| Use IO Registers | True/False | True (Default)  | -use_io_reg     |

| VHDL 2008        | True/False | False (Default) | -vh2008         |

The following alphabetical list describes all of the strategy options associated with the LSE synthesis process.

## **Allow Duplicate Modules**

When set to True, allows the design to keep duplicate modules. LSE issues a warning and uses the last definition of the module. Any previous definitions are ignored. The default is False, which causes an error if there are duplicate modules.

This option is equivalent to the "-allow\_duplicate\_modules" option in the SYNTHESIS command.

## **Carry Chain Length**

Specifies the maximum number of carry chain cells (CCUs) that get mapped to a single carry chain. Default is 0, which is interpreted as infinite length.

This option is equivalent to the "-carry\_chain\_length" option in the SYNTHESIS command.

## **Command Line Options**

Enables additional command line options for the LSE Synthesis process.

#### To enter a command line option:

- 1. In the Strategy dialog box, select **LSE** in the Process list.

- 2. Double-click the Value column for the Command line Options option.

- 3. Type in the option and its value (if any) in the text box.

- 4. Click Apply.

For detailed description on LSE command line options, see "Design Flow Overview: Command Line" on page 18.

### **Decode Unreachable States**

When set to True, synthesis infers safe recovery logic from unreachable states in all the state machines of the design.

This option is equivalent to the "-decode\_unreachable\_states" option in the SYNTHESIS command.

### **Disable Distributed RAM**

When set to True, inferred memory will not use the distributed RAM of the PFUs.

## **DSP Style**

Specifies how DSP modules should be implemented: with DSP resources or with Logic (LUTs).

This option is equivalent to the "-use\_dsp" option in the SYNTHESIS command.

### **DSP Utilization**

Specifies the percentage of DSP sites that LSE should try to use.

This option is equivalent to the "-dsp\_utilization" option in the SYNTHESIS command.

### **EBR Utilization**

Specifies EBR utilization target setting in percent of total vacant sites. LSE will honor the setting and do the resource computation accordingly. Default is 100 (in percentage).

This option is equivalent to the "-bram\_utilization" option in the SYNTHESIS command.

### **Fix Gated Clocks**

When set to True, LSE changes standard gated clocks to forms more effective for FPGAs. Clocks are gated with AND or OR gates to conserve power, but in FPGAs such clocks cause skew and prevent global clock resources from being used. The Fix Gated Clocks option is ignored if the Optimization Goal option is set to Area. See "Optimization Goal" on page 13.

The gated clocks must be specified in the .ldc file with create\_clock constraints. For more information about writing the constraints, see the following online help topics in the Diamond software:

User Guides > Applying Design Constraints > Using SDC

Constraints > Applying Lattice Synthesis Engine Constraints > Defining Clocks Using LDC Editor.

Reference Guides > Constraints Reference Guide > Lattice Synthesis Engine (LSE) Constraints > Synopsys Design Constraints (SDC) > create clock.

All inputs of the gating logic must be driven by primary inputs and the gating logic must be decomposable. Instantiated primitives and black boxes are not affected. Converted clocks and the associated registers are reported in the synthesis.log file.

### Force GSR

Enables (True) or disables (False) forced use of the global set/reset routing resources. When the value is Auto, the synthesis tool decides whether to use the global set/reset resources.

This option is equivalent to the "-force\_gsr" option in the SYNTHESIS command.

## **FSM Encoding Style**

Specifies the encoding style to use with the design.

This option is equivalent to the "-fsm\_encoding\_style" option in the SYNTHESIS command. Valid options are auto, one-hot, gray, and binary. The default value is auto, meaning that the tool looks for the best implementation.

#### Note

The encoding type "gray" only works with less than or equal to four machine states. When the number of machine states is large than four, LSE will use other encoding styles and issue the following warning message:

WARNING - Gray encoding is not supported for state machines with more than four states.

#### **Hardware Evaluation**

Enables or disables the ability to temporarily test IP in a device without an IP license. If enabled, a timer is added to the design that allows unlicensed IP to function for about 4 hours in a device. If disabled, you cannot generate a bitstream if there are any unlicensed IP in the design.

You might want to disable this option to refine your design while waiting for the license. You will not be able to generate a bitstream, but you will be able to see how resources are used (without the timer) and close timing. When you get the license, you can then generate the bitstream.

Regardless of how this option is set, if there are any unlicensed IP in the design, some features of Diamond, such as gate level simulation and EPIC, are blocked.

This option is equivalent to the "-dt" option in the SYNTHESIS command.

## **Intermediate File Dump**

If you set this to True, LSE will produce intermediate encrypted Verilog files. If you supply Lattice with these files, they can be decrypted and analyzed for problems. This option is good for analyzing simulation issues.

This option is equivalent to the "-ifd" option in the SYNTHESIS command.

## **Loop Limit**

Specifies the maximum number of iterations of "for" and "while" loops in the source code. The limit is applied when the loop index is a variable, not when it is a constant. The higher the loop\_limit, the longer the run time. The default value is 1950. Setting a higher value may cause stack overflow during some of the optimizations during synthesis. A lower value will be ignored and the default used instead.

This option is equivalent to the "-loop\_limit" option in the SYNTHESIS command.

### Macro Search Path

Allows you to specify a path (or paths) to locate physical macro files used in a given design. The software will add the specified paths to the list of directories to search when resolving file references. The option can also be used for indicating the directories containing include files that are specified in the RTL design files.

You don't need to specify a search path if the necessary .ngo or .nmc file is in the directory containing the top-level .ngo file or if the FILE attribute in the design gives a complete path name for the file (instead of a relative path name).

The software follows the following order to search for .ngo files:

- Current implementation directory

- 2. Project directory

- 3. Directories where the LPC or IPX source files reside

- 4. User-specified macro search paths

To specify a macro search path, double-click the Value box, and directly enter the path or click the ... button to browse for one or more paths.

This option is equivalent to the "-p" option in the SYNTHESIS command.

#### Max Fanout Limit

Specifies the maximum fanout setting. LSE will make sure that any net in the design is not exceeding this limit. Default is 1000 fanouts. Does not apply to clock or reset network.

This option is equivalent to the "-max\_fanout" option in the SYNTHESIS command.

## **Memory Initial Value File Search Path**

Allows you to specify a path (or paths) to locate memory initialization file (.mem) used in a given design. The software will add the specified path(s) to the list of directories to search when resolving file references.

To specify a search path, double-click the Value box, and directly enter the path or click the ... button to browse for one or more paths.

This option is equivalent to the "-p" option in the SYNTHESIS command.

## **MUX Style**

Specifies the MUX style setting, which controls the way the macrogenerator implements the multiplexer macros.

Valid options are:

- Auto (default) LSE looks for the best implementation for each considered macro.

- ► L6Mux Multiple Generates multiplexers allowing for multiple L6Mux resources.

- ▶ L6Mux Single Generates multiplexers allowing for the use of a single L6Mux resource.

- PFU Mux Generates multiplexers using only PFUMux and LUT4 resources.

#### Note

L6Mux resources will only be inferred when driven by four LUT4 and two PFUMux devices.

This option is equivalent to the "-mux\_style" option in the SYNTHESIS command.

### **Number of Critical Paths**

Specifies the number of critical timing paths to be reported in the timing report.

This option is equivalent to the "-twr\_paths" option in the SYNTHESIS command.

## **Optimization Goal**

Enables LSE to optimize the design for area, speed, or balanced.

#### Valid options are:

Area – Optimizes the design for area by reducing the total amount of logic used for design implementation.

When Optimization Goal is set to Area, LSE honors the LDC constraints if there are any. If **Use IO Registers** is set to Auto, LSE packs input and output registers into I/O pad cells. See "Use IO Registers" on page 17..

#### Note

With the Area setting, LSE also ignores all SDC constraints. These constraints are not used by LSE and are not added to an .lpf file for use by the later stages of implementation.

▶ Timing – Optimizes the design for speed by reducing the levels of logic.

When Optimization Goal is set to Timing and a create\_clock constraint is available in an .ldc file, LSE ignores the Target Frequency setting and uses the value from the create\_clock constraint instead.

If there are multiple clocks, and if not all the clocks use create\_clock constraint, then LSE will assign 200 MHz constraint on the remaining clocks in Timing Mode.

If Use IO Registers is set to Auto, LSE does not pack input and output registers into I/O pad cells.

Balanced – Optimizes the design for both area and timing.

When Optimization Goal is set to Balanced, all timing driven optimizations based on static timing analysis will run depending on LDC constraints. If Use IO Registers is set to Auto, LSE does not pack input and output registers into I/O pad cells.

The default setting depends on the device type. Smaller devices, such as MachXO and Platform Manager, default to Balanced. Larger devices—ECP5U, LatticeECP2, LatticeECP3, and LatticeXP2—default to Timing.

For more information, see "Optimizing LSE for Area and Speed" on page 568.

This option is equivalent to the "-optimization\_goal" option in the SYNTHESIS command.

## **Propagate Constants**

When set to True (default), enables constant propagation to reduce area, where possible. LSE will then eliminate the logic used when constant inputs to logic cause their outputs to be constant.

You can turn off the operation by setting this option to False.

This option is equivalent to the "-propagate\_constants" option in the SYNTHESIS command.

## RAM Style

Sets the type of random access memory globally to distributed, embedded block RAM, or registers.

The default is Auto which attempts to determine the best implementation, that is, the synthesis tool will map to technology RAM resources (EBR/Distributed) based on the resource availability.

This option will apply a syn\_ramstyle attribute globally in the source to a module or to a RAM instance. To turn off RAM inference, set its value to Registers.

- Registers Causes an inferred RAM to be mapped to registers (flip-flops and logic) rather than the technology-specific RAM resources.

- Distributed Causes the RAM to be implemented using the distributed RAM or PFU resources.

- Block\_RAM Causes the RAM to be implemented using the dedicated RAM resources. If your RAM resources are limited, for whatever reason, you can map additional RAMs to registers instead of the dedicated or distributed RAM resources using this attribute.

This option is equivalent to the "-ramstyle" option in the SYNTHESIS command.

## **Remove Duplicate Registers**

Specifies the removal of duplicate registers.

When set to True (default), LSE removes a register if it is identical to another register. If two registers generate the same logic, the second one will be deleted and the first one will be made to fan out to the second one's destinations. LSE will not remove duplicate registers if this option is set to False.

This option is equivalent to the "-remove\_duplicate\_regs" option in the SYNTHESIS command.

## Remove LOC Properties

Setting this to On removes LOC properties in the synthesized design before building the Native Generic Database (.ngd) file.

#### **Resolved Mixed Drivers**

If a net is driven by a VCC or GND and active drivers, setting this option to True connects the net to the VCC or GND driver.

## **Resource Sharing**

When this is set to True (default), the synthesis tool uses resource sharing techniques to optimize area.

With resource sharing, synthesis uses the same arithmetic operators for mutually exclusive statements; for example, with the branches of a case statement. Conversely, you can improve timing by disabling resource sharing, but at the expense of increased area.

This option is equivalent to the "-resource\_sharing" option in the SYNTHESIS command.

## **ROM Style**

Allows you to globally implement ROM architectures using dedicated, distributed ROM, or a combination of the two (Auto).

This applies the syn\_romstyle attribute globally to the design by adding the attribute to the module or entity. You can also specify this attribute on a single module or ROM instance.

Specifying a syn\_romstyle attribute globally or on a module or ROM instance with a value of:

- Auto (default) Allows the synthesis tool to choose the best implementation to meet the design requirements for speed, size, and so on.

- Logic Causes the ROM to be implemented using the distributed ROM or PFU resources. Specifically, the logic value will implement ROM to logic (LUT4) or ROM technology primitives (such as ROM16X1, ROM32X1, ROM64X1, and so on).

- ► EBR Causes the ROM to be mapped to dedicated EBR block resources. ROM address or data should be registered to map it to an EBR block. If your ROM resources are limited, for whatever reason, you can map additional ROM to registers instead of the dedicated or distributed RAM resources using this attribute.

Infer ROM architectures using a CASE statement in your code. For the synthesis tool to implement a ROM, at least half of the available addresses in the CASE statement must be assigned a value. For example, consider a ROM with six address bits (64 unique addresses). The CASE statement for this ROM must specify values for at least 32 of the available addresses.

This option is equivalent to the "-romstyle" option in the SYNTHESIS command.

## **Target Frequency**

Specifies the target frequency setting. This frequency applies to all the clocks in the design. If there are some clocks defined in an .ldc file, the remaining clocks will get this frequency setting. When a create\_clock constraint is available in an .ldc file, LSE ignores the Target Frequency setting for that clock and uses the value from the create\_clock constraint instead.

This option is equivalent to the "-frequency" option in the SYNTHESIS command.

## **Use Carry Chain**

Turns on (True) or off (False) carry chain implementation for adders. Default is True.

This option is equivalent to the "-use\_carry\_chain" option in the SYNTHESIS command.

### **Use IO Insertion**

When set to True, LSE uses IO insertion and GSR.

When set to False, LSE will generate an NGO netlist and an NGD file is not created.

This option is equivalent to the "-use\_io\_insertion" option in the SYNTHESIS command.

See "Creating Your Own Black Box Modules" on page 118 for more information.

## **Use IO Registers**

When True, this option forces the synthesis tool to pack all input and output registers into I/O pad cells based on the timing requirements for the target device family. Auto, the default setting, enables this register packing if Optimization Goal is set to Area. If Optimization Goal is Timing or Balanced, Auto disables register packing.

This option is equivalent to the "-use\_io\_reg" option in the SYNTHESIS command.

You can also control packing on individual registers and ports. See "syn\_useioff" on page 77.

## Use LPF Created from SDC in Project

LSE creates a preference (.lpf) file based on the Synopsys Design Constraint (.sdc) file. (When you use LSE, SDC constraints must be in a Lattice Design Constraints (.ldc) file.) When this option is set to True, the synthesis constraints are also applied to the Map Design stage of implementation.

### **VHDL 2008**

When this is set to True, VHDL 2008 is selected as the VHDL standard for the project.

## **Design Flow Overview: Command Line**

LSE can be run from the command line. Table 2 describes the command project options available to run LSE. Examples are provided following the table.

The command is SYNTHESIS. The '-f' option is available to simplify the command line. A project file containing all the user's desired arguments can be constructed as a text file, then passed to LSE using the –f switch. For example:

synthesis -f synth.synproj

For more information about setting up the Diamond command line environment, in the Diamond online help, refer to Reference Manuals > Command Line Reference Guide > Command Line Basics > Setting Up the Environment to Run Command Line.

#### Note

Running LSE from the command line requires an environment variable TEMP be set. Default Cygwin .bashrc unsets this variable, so user must add the following back into their .bashrc:

export TEMP=/temp

**Table 2: LSE Project Options**

| Required Options | Parameter   | Arguments                                              | Description         | Default |

|------------------|-------------|--------------------------------------------------------|---------------------|---------|

| Optional         | -s          | <grade></grade>                                        | Target grade        |         |

| Optional         | -t          | <package></package>                                    | Target Package      |         |

| Optional         | -loop_limit | <value></value>                                        | Iteration limits    |         |

| Optional         | -f          | <argument_filename></argument_filename>                | Argument file       |         |

| Required         | -a          | " <supported_device_family>"</supported_device_family> | Target Architecture | -       |

| Optional         | -d          | <device></device>                                      | Target Device       | -       |

| Optional         | -p          | <searchpath>}</searchpath>                             | Option search path. | \.      |

| Optional         | -top        | <top_module_name></top_module_name>                    | Top-level module    | -       |

**Table 2: LSE Project Options (Continued)**

| Required Options                        | Parameter    | Arguments                                      | Description                                                                                         | Default                                         |

|-----------------------------------------|--------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Required (Only for source of this type) | -ver         | { <verilog_file.v>}</verilog_file.v>           | Name of input Verilog file                                                                          | -                                               |

| (Multiple arguments)                    |              |                                                |                                                                                                     |                                                 |

| Optional                                | -lib         | <li>libname&gt;</li>                           | Include library                                                                                     | -                                               |

| (Multiple arguments)                    |              |                                                |                                                                                                     |                                                 |

| Required                                | -vhd         | { <vhdl_file.vhd>}</vhdl_file.vhd>             | Name of input VHDL                                                                                  | -                                               |

| (Only for<br>source of<br>this type)    |              |                                                | file                                                                                                |                                                 |

| (Multiple arguments)                    |              |                                                |                                                                                                     |                                                 |

| Optional                                | -ngd         | <ngd_file.ngd></ngd_file.ngd>                  | Name of output ngd<br>file, option available<br>only for Diamond<br>devices                         | <top_module_name>.<br/>ngd</top_module_name>    |

| Optional                                | -ngo         | { <ngo_file.ngo>}</ngo_file.ngo>               | Name of output ngo<br>file, option available<br>only for Diamond<br>devices                         | <top_module_name>.<br/>ngo</top_module_name>    |

| Optional                                | -force_gsr   | {auto   yes   no}                              | GSR insertion, option<br>available only for<br>Diamond devices                                      | auto                                            |

| Optional                                | -ramstyle    | { auto   distributed   block_ram   registers } | RAM style                                                                                           | auto                                            |

| Optional                                | -romstyle    | { auto   ebr   logic }                         | ROM style                                                                                           | auto                                            |

| Optional                                | -output_edif | { <filename.edf>}</filename.edf>               | Create EDIF output file                                                                             | <top_module_name>. edf</top_module_name>        |

| Optional                                | -output_hdl  | { <filename>}</filename>                       | Create HDL output file                                                                              | <top_module_name><br/>_prim.v</top_module_name> |

| Optional                                | -sdc         | { <sdc_file.sdc>}</sdc_file.sdc>               | Input SDC file                                                                                      | -                                               |

| Optional                                | -lpf         | {true   false}                                 | Generate output lpf file with name:                                                                 | False                                           |

|                                         |              |                                                | <top_module_name>_l<br/>se.lpf, option available<br/>only for Diamond<br/>devices</top_module_name> |                                                 |

| Optional                                | -logfile     | { <synthesis_logfile>}</synthesis_logfile>     | Name of output log file                                                                             | synthesis.log                                   |

**Table 2: LSE Project Options (Continued)**

| Required<br>Options | Parameter              | Arguments                                                | Description                                             | Default      |

|---------------------|------------------------|----------------------------------------------------------|---------------------------------------------------------|--------------|

| Optional            | -frequency             | {target_frequency }                                      | Target frequency for timing optimization, in MHz        | 200          |

| Optional            | -max_fanout            | {max_fanout }                                            | Maximum driver fanout                                   | 1000         |

| Optional            | -bram_utilization      | {bram_utilization}                                       | Block RAM utilization factor, percent                   | 100          |

| Optional            | -fsm_encoding_style    | {binary   one-hot   gray}                                | Finite State Machine encoding style                     | binary       |

| Optional            | -mux_style             | { auto   pfu_mux  <br>L6Mux_single  <br>L6Mux_multiple } | Mux implementation style                                | auto         |

| Optional            | -use_carry_chain       | {0 1}                                                    | Use carry-chain resources                               | 1 (use)      |

| Optional            | -carry_chain_length    | { chain_length }                                         | Carry chain maximum length                              | 0 (no limit) |

| Optional            | -use_io_insertion      | { 0 1 }                                                  | Insert I/O primitives                                   | 1 (insert)   |

| Optional            | -use_io_reg            | { 0 1 }                                                  | Use I/O registers                                       | 1 (use)      |

| Optional            | -resource_sharing      | { 0 1 }                                                  | Allow resource sharing optimization                     | 1 (allow)    |

| Optional            | -propagate_constants   | { 0 1 }                                                  | Preserve registers with constant inputs                 | 1 (allow)    |

| Optional            | -remove_duplicate_regs | { 0 1 }                                                  | Allow removal of duplicate registers                    | 1 (allow)    |

| Optional            | -ip_dir                | {location of IP installation}                            | Location of IP directory                                | \.           |

| Optional            | -corename              | {name of IP core}                                        | Name of IP core                                         | -            |

| Optional            | -ertl_file             | {name of encrypted RTL file}                             | Name of encrypted file                                  | -            |

| Optional            | -optimization_goal     | { area   timing   balanced }                             | Global optimization strategy                            | area         |

| Optional            | -hdl_param             | { <name value="">}</name>                                | To pass parameters/<br>generics to design top<br>module | -            |

| Optional            | -h                     | -                                                        | Help                                                    | -            |

| Optional            | -twr_paths             | {Num_paths}                                              | Number of TRACE critical paths                          | 3            |

| Optional            | -ifd                   | -                                                        | Dump intermediate files                                 | -            |

| Optional            | -dt                    | -                                                        | Disable h/w timer                                       | -            |

| Optional            | -cbn                   | -                                                        | Consistent Bus<br>Naming                                | -            |

**Table 2: LSE Project Options (Continued)**

| Required Options | Parameter         | Arguments | Description                                  | Default |

|------------------|-------------------|-----------|----------------------------------------------|---------|

| Optional         | -fix_gated_clocks | {0 1}     | Fix Gated Clocks                             | 1       |

| Optional         | -vh2008           | -         | Compile using VHDL<br>2008 libraries         |         |

| Optional         | -key              | (key dat) | Location of the key file used for decryption | =       |

**Examples** Following are a few examples of SYNTHESIS command lines and a description of what each does. Command lines only supports MachXO, MachXO2, MachXO3L, and MachXO3LF devices.

**Example 1** The following command is a simple example with Verilog and VHDL file inputs.

synthesis -a MachXO2 -d LCMXO2-2000HC -t TQFP144 -s 5 -top top\_module\_name -vhd f1.vhd f2.vhd f3.vhd -ver file1.v file2.v -ngd file.ngd

**Example 2** The following example illustrates the usage of a search path -p option for IP .ngo files or include files.

synthesis -a MachXO2 -d LCMXO2-2000HC -p D:/my\_project/tmp -top

top\_module\_name -vhd f1.vhd f2.vhd f3.vhd -ver file1.v file2.v

-ngd file.ngd

**Example 3** The following example shows VHDL library usage with the -lib option.

synthesis -a MachXO2 -d LCMXO2-2000HC -top top -lib work

-vhd top.vhd -lib my\_lib -vhd ff.vhd -ngd file.ngd

**Example 4** The following example illustrates the usage of both the -hdl\_param and -optimization\_goal options.

synthesis -a MachXO2 -d LCMXO2-2000HC -hdl\_param width 7 depth 5 -optimization\_goal timing -ver file1.v file2.v -ngd file.ngd

**Example 5** This is an example of a command line with encrypted RTL for IP designs.

synthesis -a MachXO2 -d LCMXO2-2000HC -corename file\_datapath - ertl\_file source/file\_datapath\_enc.vhd -ip\_dir encryption -ngd file.nqd

**Example 6** This example shows miscellaneous commands for illustrating various syntax structures.

synthesis -vhd source/ora.vhd source/top.vhdl source/

anda\_vhd.vhd

synthesis -ver source/anda.v source/v\_top.v

synthesis -a MachXO2 -d LCMXO2-2000HC -force\_gsr auto -ver

top.v mid.v prim.v -vhd count.vhd

**Example 7** The following example illustrates the usage of a synthesis project file with command -f . The synthesis project file contains strategy setting, Diamond translates strategy options into command line options.

```

synthesis -f D:/my_project/my.synproj

```

Figure 4 shows the contents of the synthesis project synproj.

Figure 4: Example synproj Project

```

File Edit Format View Help

-a "Machxo2"

-d LCMX02-1200HC

-t TQFP144

-s 5

-frequency 200

-optimization_goal Balanced

-bram_utilization 100

-ramstyle Auto

-romstyle auto

-use_carry_chain_length 0

-force_gsr Auto

-resource_sharing 1

-propagate_constants 1

-remove_duplicate_regs 1

-mux_style Auto

-max_fanout 1000

-fsm_encoding_style Auto

-twr_paths 3

-fix_gated_clocks 1

-loop_limit 1950

```

For more information about running Synthesis from the command line, in the Diamond software online help, refer to Reference Guides > Command Line Reference Guide > Command Line Tool Usage > Running SYNTHESIS from the Command Line.

## Preparing the Input

You can create an HDL source file in Diamond Source Editor.

To create an HDL source in Source Editor:

- From the Diamond main window, choose File > New > File. In the New File dialog, choose Verilog Files or VHDL Files from the Source Files list.

- 2. In the New File dialog, fill in the File name and Location, choose the file extension in the Ext. field.

- 3. Check **Add to Implementation** option if you want to add this source to the current project.

- 4. Click New.

In the pop up Source Editor, you can enter the text. When finished editing, click File > Save from the Diamond main window.

#### Note

You can detach Source Editor from the Diamond main window by clicking the Detach Tool icon on the upper right corner of Source Editor. If you want to attach Source Editor back to the main window, click the Attach Window icon on the upper right corner of Source Editor window, or choose Window > Attach Window from Source Editor.

For more information, in the Diamond software online help, refer to **User Guides > Entering the Design > HDL Design Entry**.

## **Constraint Files**

LSE enables you to set Synopsys® Design Constraints (SDC), which are directly interpreted by the synthesis engine. When you use LSE, these SDC constraints are saved to a Lattice Design Constraints file (.ldc). You can create several .ldc files and select one of them to serve as the active synthesis constraint file for an implementation. You can also cause a synthesis preference file to be generated when the design is synthesized. The synthesis preferences can then be merged with the logical preference file (.lpf).

Lattice Design Constraints (LDC) Editor, as well as Source Editor, are available for creating and editing .ldc files. LDC Editor provides a spreadsheet style user interface that enables you to quickly create and edit Synopsys Design Constraints.

For more information, in the Diamond software online help, refer to **User Guides > Applying Design Constraints > Using SDC Constraints**.

## **Specifying Constraints and Attributes**

Constraints on specific design elements are provided to LSE using the SDC constraint language. The constraints reside in the .ldc file, which can be accessed in the Diamond Synthesis Constraint Files folder in the File List pane.

In Diamond, a single constraint file can be active at any one time. The active file is used by synthesis when it is run. There can be multiple .ldc files, but only one can be active.

The .ldc file can be opened in the LDC Editor (GUI), or the text editor.

- To open the LDC Editor, double-click the .ldc file in the File List pane.

- Right-click the .ldc file in the File List pane and in the dropdown choose Open With. The Open With dialog box allows you to choose between the LDC Editor or the Text Editor.

For more information, in the Diamond software online help, refer to **User** Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Synthesis Constraints Using LDC Editor.

The *Timing Closure* section of the *FPGA Design Guide* focuses on timing requirements, explains timing driven FPGA implementation processes, and shows how to tackle timing issues when timing closure becomes problematic. You can access Timing Closure section of the FPGA Design Guide from the Diamond software Start Page. Or, from the Diamond software online help, refer to User Guides > Help for Lattice Diamond, and scroll down to FPGA Design Guide.

## **Defining Synthesis Constraints Using** LDC Editor

The LDC Editor provides a GUI that enables the user to easily choose the type of constraint, and provide all the necessary constraint information (the GUI must make it clear what information is required and what is optional). Key is to provide the user access to actual design element names that will be honored by LSE (e.g. instance, port names). Moreover, it will filter the selection provided to the user based on the legal type. As an example, in a set\_input\_delay constraint, the user will only be given a selection of references for the clock that are considered clocks.

LDC Editor does not perform design rule check (DRC) by default. DRC check can be enabled in the Diamond software by clicking Tools > Options > LDC Editor > General > Run DRC check before saving and Enable realtime DRC check.

When the target of the constraint can not be found, or if the constraint syntax is incorrect, a warning will display and the constraint will not show in the LDC Editor.

For more information, in the Diamond software online help, refer to **User** Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Synthesis Constraints Using LDC Editor.

## **Defining Synthesis Constraints Using Text Editor**

The .ldc file can be edited by Text Editor manually. Do not use TCL features for constraints which are not supported by LSE now. For example:

```

set board_delay 3

set_clock_groups -exclusive \

-group {c0_1} \

-group {c0_0}

```

See the following LSE constraints for syntax examples for each constraint.

## **Defining Clocks**

The create clock constraint creates a clock and defines its characteristics.

#### Note

In LSE timing, interclock domain paths are always blocked for create\_clock. However, the interclock domain path is still valid for constraints such as set\_false\_path and set\_multicycle\_path.

**Syntax** create clock [-name name] -period period value [-waveform {value1 value2}] source object

#### **Arguments** -name name

The name string specifies the name of the clock. If this parameter is not given, the name of the source object is used as the name of the clock. Virtual clocks are currently not supported.

#### -period period value

This value is required and it specifies the clock period in nanoseconds. The value you specify is the minimum time over which the clock waveform repeats. The value specified for the period must be positive as the period of a clock must be greater than zero. The duty cycle of the clock is 50 percent.

#### -waveform {value1 value2}

The values are a list of edge values. Only two edges are supported. Floating values are accepted. Value1 must be less than value2, and the difference must be less than the clock period.

#### source object

The source object is the object on which the clock constraint is defined. The source object can be a port object or a net object in the design. The object is obtained by using one of the get ports or get nets commands. If you specify a clock constraint on a source object that already has a clock, the new clock replaces the existing one. Only one source object is accepted. Wildcards are accepted as long as the resolution shows one port or net object.

**Example** The following example creates two clocks on ports CK1 and CK2 with a period of 6:

```

create_clock -name my_user_clock -period 6 [get_ports CK1]

create_clock -name my_other_user_clock -period 6 [get_ports CK2]

```

**Example** The following example creates a clock on port CK3 with a period of 7.1, and has two edges at 0 and 4.1:

```

create_clock -period 7.1 -waveform {0 4.1} [get_ports CK3]

```

For more information about defining clocks with LDC Editor, For more information, in the Diamond software online help, refer to **User Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Clocks Using LDC Editor.**

## **Defining Generated Clocks**

The create\_generated\_clock creates an internally generated clock and defines its characteristics. This command is used when the clock being created is related to another clock. The generated clock will now be considered a clock when defining constraints such as set\_input\_delay.

**Syntax** create\_generated\_clock -source reference\_object [-master\_clock clock\_object] [-divide\_by factor] [-multiply\_by factor] [-duty\_cycle value] net\_object

Arguments -source reference object

The reference object is an object on which the source clock of the generated clock is defined. The source object can be a net object or a port object. The period of the generated clock is derived from the clock on the reference object using the multiply and divide factors.

-master\_clock clock\_object

If the master is defined, the master clock object becomes the source clock for the generated clock. This is an optional object used to identify a specific clock, if there is more than one clock on the source object.

-divide by factor

This factor is the frequency division factor. The frequency of the generated clock is equal to the frequency of the source clock divided by this factor, if the multiply by factor is not specified. For instance, if this factor is equal to 2, the generated clock period is twice the reference clock period. Default value is 1.

-multiply\_by factor

This factor specifies the frequency multiplication number to be used when finding the generated clock frequency. For instance, if the factor is equal to 2, the generated clock period is half the reference clock period. If both multiply by and divide by factors are used, the frequency is obtained by using both factors. Default value is 1.

#### -duty cycle value

This value specifies the duty cycle in percentage of the clock period. The value can be floating point and ranges from 0 to 100. The default value is 50.

#### net\_object

The net\_object specifies the source of the clock constraint. This is usually an internal -net of the design. If you specify a clock constraint on a net that already has a clock, the new clock replaces the existing clock. Only one source is accepted. Wildcards are accepted as long as the resolution shows one net.

This command creates a generated clock in the current design at a declared net\_object by defining its frequency with respect to the frequency at the reference object. The static timing analysis tool uses this information to compute and propagate the generated clock's waveform across the clock network to the clock pins of all sequential elements driven by this target

**Examples** The following example creates a generated clock on pin pll1/ CLKOP with a period twice as long as the period at the reference port CLK:

```

create_generated_clock -divide_by 2 -source [get_ports CLK]

[get_pins pll1/CLKOP]

```

The following example creates a generated clock at the primary output of myPLL with a period 3/4 of the period at the reference pin clk:

```

create_generated_clock -divide_by 3 -multiply_by 4

[get_ports clk] [get_pins myPLL/CLK1]

```

The following example shows a clock with a duty cycle of 60 percent:

```

create_generated_clock -duty_cycle 60 -source [get_ports clk]

[get_pins myPLL/CLK1]

```

For more information about defining clocks with LDC Editor, in the Diamond software online help, refer to User Guides > Applying Design Constraints >

Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Generated Clocks in LDC Editor.

## **Defining Clock Groups**

The clock\_groups constraint specifies clock groups that are mutually exclusive or asynchronous with each other in a design so that the paths between these clocks are not considered during timing analysis.

**Syntax** set\_clock\_groups -asynchronous | -exclusive -group clock\_objects [-group clock\_objects]

#### **Arguments** -asynchronous

Specifies that the clock groups are asynchronous to each other (meanwhile, Lattice assume all clocks are asynchronous). Two clocks are asynchronous with respect to each other if they have no phase relationship at all.

#### -exclusive

Specifies that clocks are mutually exclusive. Only one clock group will be active at any given time.

#### -group clock\_object

Specifies the clock objects in a group. If you specify only one group, it means that the clocks in that group are exclusive or asynchronous with all other clocks in the design. A default other group is created for this single group. Whenever a new clock is created, it is automatically included in this group.

**Examples** The following example specifies two clock ports (clka and clkb) are asynchronous to each other.

```

create_clock -period 10.000 -name clka_port [get_ports clka]

create_clock -period 10.000 -name clkb_port [get_ports clkb]

# Set clka_port and clkb_port to be mutually exclusive clocks.

set_clock_groups -asynchronous -group [get_clocks clka_port] -

group [get_clocks clkb_port]

# The previous line is equivalent to the following two

commands.

set_false_path -from [get_clocks clka_port] -to [get_clocks

clkb_port]

set_false_path -from [get_clocks clkb_port] -to [get_clocks

clka_port]

```

The following example specifies four clock constraints that won't be active at the same time:

For more information about defining clocks with LDC Editor, in the Diamond software online help, refer to User Guides > Applying Design Constraints >

```

create_clock -period 10.000 -name clka_port [get_ports clka]

create_clock -period 10.000 -name clkb_port [get_ports clkb]

create_clock -period 10.000 -name clkc_port [get_ports clkc]

set_clock_groups -exclusive -group [get_clocks {clka_port

clkb_port}] -group [get_clocks clkc_port]

```

Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Clock Groups in LDC Editor.

## **Setting Input Delays**

The set\_input\_delay constraint defines the arrival time of an input relative to a clock.

**Syntax** set\_input\_delay *delay\_value* [-max |-min] -clock *clock\_object* input\_port\_object

#### Arguments delay\_value

Specifies the arrival time in nanoseconds that represents the amount of time for which the signal is available at the specified input after a clock edge.

-max

Specifies that the delay value is the maximum delay.

-min

Specifies that the delay value is the minimum delay.

-clock clock\_object

Specifies the clock reference to which the specified input delay is related. This is a mandatory argument.

input\_port\_object

Provides one or more input ports in the current design to which delay\_value is assigned. You can also use the keyword "all\_inputs" to include all input ports.

**Example** The following example sets an input delay of 1.2 ns for port data1 relative to the rising edge of CLK1:

```

set_input_delay 1.2 -clock [get_clocks CLK1] [get_ports data1]

```

**Example** The following example sets an input delay of 1.2 ns minimum and 1.5 ns maximum for port data1 relative to the rising edge of CLK1:

```

set_input_delay 1.2 -min -clock [get_clocks CLK1] [get_ports

data1]

set_input_delay 1.5 -max -clock [get_clocks CLK1] [get_ports

data1]

```

For more information about setting input and output delays with LDC Editor, in the Diamond software online help, refer to **User Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Setting Input and Output Delays Using LDC Editor.**

## **Setting Output Delays**

The set\_output\_delay constraint defines the output delay of an output relative to a clock.

**Syntax** set\_output\_delay *delay\_value* [-max |-min] -clock *clock\_object* output\_port\_object

### Arguments delay\_value

Specifies the amount of time from a reference clock to a primary output port.

-max

Specifies that the delay value is the maximum delay.

-min

Specifies that the delay value is the minimum delay.

-clock clock\_object

Specifies the clock reference to which the specified output delay is related. This is a mandatory argument.

output port object

Provides one or more (by wildcard) output ports in the current design to which delay\_value is assigned. You can also use the keyword "all\_outputs" to include all output ports.

**Example** The following example sets an output delay of 1.2 ns for all outputs relative to clki\_c:

```

set_output_delay 1.2 -clock [get_clocks CLK1] [get_ports OUT1]

set_output_delay 1.2 -clock [get_clocks CLK1] [all_outputs]

```

**Example** The following example sets an output delay of 1.2 ns minimum and 1.5 ns maximum for port data1 relative to the rising edge of CLK1:

```

set_output_delay 1.2 -min -clock [get_clocks CLK1] [get_ports

data1]

set_output delay 1.5 -max -clock [get_clocks CLK1] [get_ports

data1]

```

For more information about setting input and output delays with LDC Editor, in the Diamond software online help, refer to **User Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Setting Input and Output Delays Using LDC Editor.**

## **Defining Minimum Delay Paths**

The set\_min\_delay constraint specifies the maximum delay for the timing paths.

**Syntax** set\_max\_delay delay\_value [-from from port\_object or cell\_object] [-to to port\_object or cell\_object]

#### Arguments delay\_value

Specifies a floating point number in nanoseconds that represents the required maximum delay value for specified paths.

If the path ending point is on a sequential device, the tool includes library setup time in the computed delay.

-from from port\_object or cell\_object

Specifies the timing path start point. A valid timing start point is a clock, a primary input, a combinational logic cell, or a sequential cell (clock pin).

-to to port\_object or cell\_object

Specifies the timing path end point. A valid timing end point is a primary output, a combinational logic cell, or a sequential cell (data pin)

**Examples** The following example sets a maximum delay by constraining all paths from ff1a:CLK to ff2e:D with a delay less than or equal to 5 ns:

```

set_max_delay 5 -from [get_cells ff1a] -to [get_cells ff2e]

```

For more information about defining delay paths with LDC Editor, in the Diamond software online help, refer to **User Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Delay Paths Using LDC Editor**.

## **Defining Maximum Delay Paths**

The set\_max\_delay constraint specifies the maximum delay for the timing paths.

**Syntax** set\_max\_delay delay\_value [-from from port\_object or cell\_object] [to to port object or cell object

### Arguments delay value

Specifies a floating point number in nanoseconds that represents the required maximum delay value for specified paths.

If the path ending point is on a sequential device, the tool includes library setup time in the computed delay.

-from from port object or cell object

Specifies the timing path start point. A valid timing start point is a clock, a primary input, a combinational logic cell, or a sequential cell (clock pin).

-to to port object or cell object

Specifies the timing path end point. A valid timing end point is a primary output, a combinational logic cell, or a sequential cell (data pin)

**Examples** The following example sets a maximum delay by constraining all paths from ff1a:CLK to ff2e:D with a delay less than or equal to 5 ns:

```

set_max_delay 5 -from [get_cells ff1a] -to [get_cells ff2e]

```

For more information about defining delay paths with LDC Editor, in the Diamond software online help, refer to **User Guides > Applying Design** Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Delay Paths Using LDC Editor.

## **Defining False Paths**

The set false path constraint identifies paths that are considered false and excluded from timing analysis.

**Syntax** set\_false\_path [-from from port\_object or cell\_object] [-to to port object or cell object

or

set false path [-through through net object]

Arguments -from from port\_object or cell\_object

Specifies the timing path start point. A valid timing starting point is a clock, a primary input, a combinational logic cell, or a sequential cell (clock-pin).

-to to port object or cell object

Specifies the timing path end point. A valid timing end point is a primary output, a combinational logic cell, or a sequential cell (data-pin).

-through through net object

Specifies a net through which the paths should be blocked.

**Examples** The following example specifies all paths from clock pins of the registers in clock domain clk1 to data pins of a specific register in clock domain clk2 as false paths:

```

set_false_path -from [get_ports clk1] -to [get_cells reg_2]

```

The following example specifies all paths through the net UO/sigA as false:

```

set_false_path -through [get_nets UO/sigA]

```

For more information about defining delay paths with LDC Editor, in the Diamond software online help, refer to **User Guides > Applying Design Constraints > Using SDC Constraints > Applying Lattice Synthesis** Engine Constraints > Defining Delay Paths Using LDC Editor.

# **Defining Multicycle Paths**

The set\_multicycle\_path constraint defines a path that takes multiple clock cycles.

**Syntax** set\_multicycle\_path ncycles [-from from net\_object or cell\_object] [to to net object or cell object

#### Arguments ncycles

Specifies a value that represents the number of cycles the data path must have for setup check. The value is relative to the ending point clock and is defined as the delay required for arrival at the ending point.

-from from net\_object or cell\_object

Specifies the timing path start point. A valid timing start point is a sequential cell (clock pin) or a clock net (signal). You can also use the keyword "all registers" to include all registers' clock inputs.

-to to net object or cell object

Specifies the timing path end point. A valid timing end point is a sequential cell (data-pin) or a clock-net (signal). You can also use the keyword "all registers" to include all registers' data inputs.

**Example** The following example sets all paths between reg1 and reg2 to 3 cycles for setup check. Hold check is measured at the previous edge of the clock at reg2.

```

set_multicycle_path 3 -from [get_cells reg1] -to [get_cells

reg2]

```

For more information about defining delay paths with LDC Editor, in the Diamond software online help, refer to **User Guides > Applying Design** Constraints > Using SDC Constraints > Applying Lattice Synthesis Engine Constraints > Defining Delay Paths Using LDC Editor.

# **Setting Up Attributes**

This section describes the Synplify Lattice Attributes that are supported by the Lattice Synthesis Engine (LSE). These attributes are directly interpreted by the engine and influence the optimization or structure of the output netlist. Traditional HDL attributes, such as UGROUP, are also compatible with LSE and are passed into the netlist to direct Map and Place & Route.

All HDL attributes have priority over Strategy settings.

# black\_box\_pad\_pin

This attribute specifies pins on a user-defined black box module. The pins are defined as I/O pads that are visible outside of the black box. If there is more than one port that is an I/O pad, list the ports inside double-quotes ("), separated by commas (,), and without enclosed spaces. This attribute must be used in conjunction with the syn\_black\_box attribute.

**Verilog Syntax** object /\* synthesis syn\_black\_box black\_box\_pad\_pin = "portList" \*/;

where object is a module declaration, and portList is a spaceless, commaseparated list of the black box port names that are I/O pads.

### **Verilog Example**

```

module black_box_pad_pin2(

input[4:0] in1,

input[4:0] in2,

input clk,

output[4:0] q

synthesis

syn_black_box

black_box_pad_pin="in1(4:0),q" */;

reg [4:0] q;

always @(posedge clk)

begin

q <= in1 + in2;

end

endmodule

module black_box_pad_pin_instan(

input[4:0] in1, input[4:0] in2,

input[4:0] in3,

input clk

output[5:0] q_out

wire [4:0] q;

reg [5:0] q_out;

black_box_pad_pin2 test_123(

.in1(in1),

.in2(in2),

.clk(clk),

\cdot q(q)

always @(posedge clk)

begin

q_out <= q + in3;</pre>

end

endmodule

```

**VHDL Syntax** attribute black\_box\_pad\_pin of object : architecture is "portList";

where object is the architecture name of a black box. Data type is string. The portList is a spaceless, comma-separated list of the black box port names that are I/O pads.

## **VHDL Example**

```

entity BBDLHS is

port (D: in std_logic;

E: in std_logic;

GIN : in std_logic_vector(2 downto 0);

Q : out std_logic );

end;

architecture BBDLHS_behav of BBDLHS is

end bl_box_behav;

attribute syn_black_box : boolean;

attribute syn_black_box of BBDLHS_behav : architecture is true;

attribute black_box_pad_pin : string;

attribute black_box_pad_pin of BBDLHS_behav : architecture is

"GIN(2:0),Q";

```

# full\_case

Directive. For Verilog designs only. When used with a case, casex, or casez statement, this directive indicates that all possible values have been given, and that no additional hardware is needed to preserve signal values.

Verilog Syntax object /\* synthesis full\_case \*/

#### **Verilog Example**

```

module full_case1 (q, in1, in2, in3, in4, sel);

output q;

input in1, in2, in3, in4;

input [3:0] sel;

req q;

always @(sel or in1 or in2 or in3 or in4)

begin

casez (sel) /* synthesis full_case */

4'b11??: q = in4;

4'b?1??: q = in3;

4'b???1: q = in1;

4'b??1?: q = in2;

default: q = 'bx;

endcase

end

endmodule

```

## **GSR**

This attribute specifies the use of the global set/reset routing resources. Allows the user to specify which portions of the design are to be altered in the way they respond to the GSR reset signal. Unless specified otherwise, all design elements will respond to the global reset signal if it is present.

#### Available values:

- ► ENABLED This is the default value on most library elements. This value allows the software to determine the final value and will be overridden by the parent hierarchy if the parent has a value of anything other than ENABLED.

- ▶ DISABLED This prevents the hierarchy or element from responding to the GSR value. It cannot be changed by the parent's value.

- ► FORCEENABLE This forces the hierarchy or element to respond to the GSR value. It cannot be changed by the parent's value.

- ▶ IPENABLE This forces the hierarchy or element to respond to the GSR value when IP is being used in evaluation mode. It cannot be changed by the parent's value. This value is only for internal Lattice IP to use. It should never be used within a design itself.

**Verilog Syntax** object /\* synthesis GSR = {ENABLED | DISABLED | FORCEENABLE | IPENABLE} \*/;

### **Verilog Example**

```

`timescale 1 ns / 1 ns

module top (reg_q, rotate_q, a, b, r_l, clk, rst)/* synthesis

GSR = "ENABLED" */;

output [7:0] reg_q, rotate_q;

input [7:0] a, b;

input clk, rst, r_l;

sub1 reg8_1 (.clk(clk), .data(a), .q(reg_q), .rst(rst));

sub2 rotate_1 (rotate_q, b, clk, r_l, rst);

endmodule

```

**VHDL Syntax** attribute gsr of object : objectType is ENABLED | DISABLED | FORCEENABLE | IPENABLE;

#### **VHDL Example**

```

architecture archtest of test is attribute gsr : string; attribute gsr of archtest : architecture is "ENABLED";

```

#### loc

The loc attribute specifies pin locations for Lattice I/Os, instances, and registers, and forward-annotates them to the place-and-route tool. Refer to the Lattice databook for valid pin location values. If the attribute is on a bus, the software writes out bit-blasted constraints for forward-annotation.

**Verilog Syntax** object /\* synthesis loc = "pinLocations" \*/;

In the syntax, pin\_locations is a spaceless, comma-separated list of pin locations.