November 24, 2020 (1.7)

**Application Note AN006**

#### Summary

The Lattice iCEcube2 development software provides a complete FPGA implementation environment for today's FPGA designers. This application note details the basic design and simulation flow using Mentor® ModelSim® simulator.

#### Introduction

The sample design used in this application note is a simple 4-bit binary up-counter with an associated testbench. The counter design, counter.vhd, is presented first:

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity counter is port (

: in

std_logic:

reset : in

std_logic;

count : out std_logic_vector (3 downto 0));

end counter;

architecture behavioral of counter is

signal q : std_logic_vector (3 downto 0);

begin

process(clk, reset)

begin

if(reset = '1') then

q <= (others=>'0');

elsif(clk'event and clk = '1') then

q <= q + 1;

end if;

end process;

count <= q;

end behavioral;

```

The testbench design, count\_tb.vhd, is presented next:

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity count_tb is

end count_tb;

```

```

architecture testbench_arch of count_tb is

component counter

port (

: in std_logic;

c1k

reset : in std_logic;

count : out std_logic_vector (3 downto 0));

end component;

signal clk : std_logic := '0';

signal reset : std_logic := '0';

signal count : std_logic_vector (3 downto 0) := "0000";

constant period : time := 100 ns;

constant duty_cycle : real := 0.5;

constant offset : time := 100 ns;

begin

uut : counter

port map (

clk => clk

reset => reset,

count => count);

process -- clock generation

begin

wait for offset:

clock_loop : loop

clk <= '0';</pre>

wait for (period - (period * duty_cycle));

clk <= '1';</pre>

wait for (period * duty_cycle);

end loop clock_loop;

end process;

process -- reset generation

begin

reset <= '0';

Current Time:

0ns

wait for 100 ns;

reset <= '1';

Current Time:

100ns

wait for 35 ns;

reset <= '0';</pre>

Current Time:

135ns

wait for 1865 ns;

Current Time:

2000ns

end process;

end testbench_arch;

```

This document explains the following scenarios:

- 1. Pre-Synthesis Simulation.

- 2. Post-Synthesis Functional Simulation (Verilog/VHDL).

- 3. Place-and-Route Functional Simulation (Verilog).

- 4. Place-and-Route Timing Simulation (Verilog).

- 5. Place-and-Route Functional Simulation (VHDL).

- 6. Place-and-Route Timing Simulation (VHDL)

#### **Pre-Synthesis Simulation**

This section details the steps required for pre-synthesis simulation.

- 1. Create a new folder and copy the design (counter.vhd) and testbench (count\_tb.vhd).

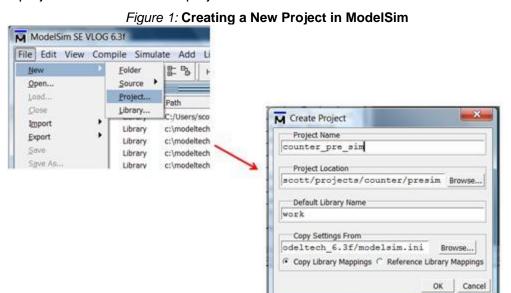

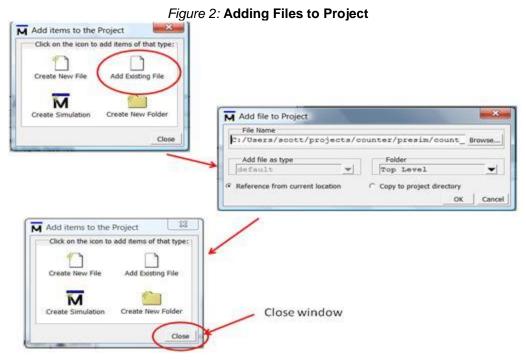

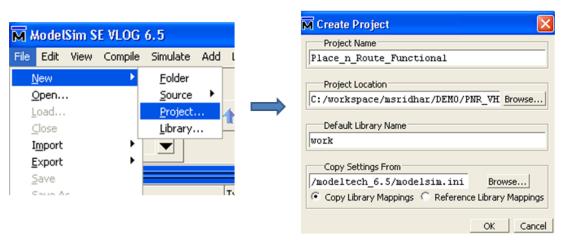

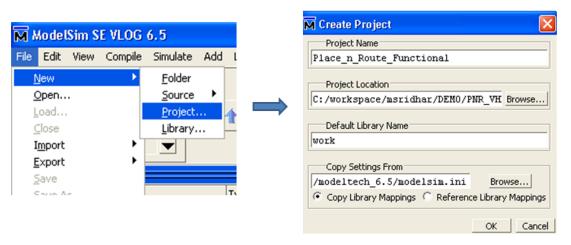

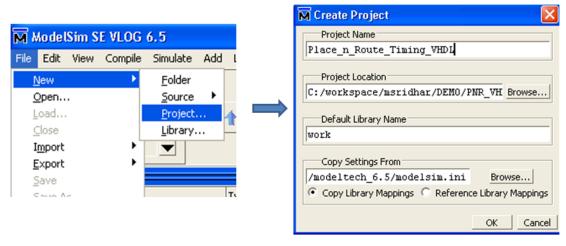

- 2. Start ModelSim and create a new project by choosing File→New→Project. Browse to the newly created project folder and enter a project name. Click "OK".

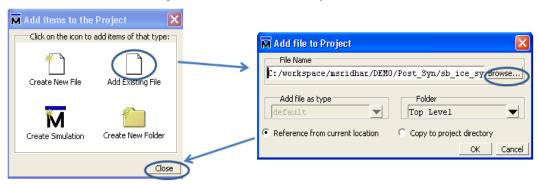

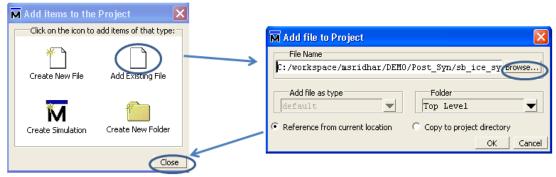

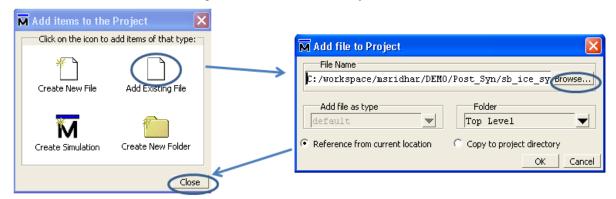

3. Click "Add Existing Files" and add counter.vhd and count\_tb.vhd to the project. Close the "Add items to the Project" window.

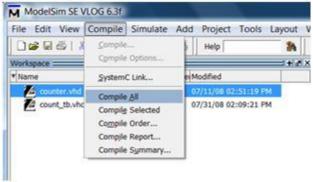

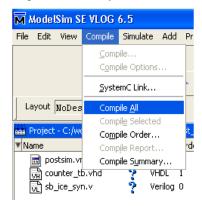

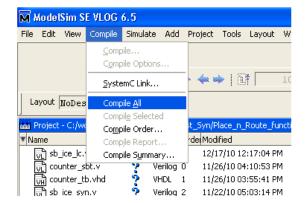

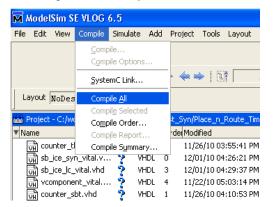

4. Choose Compile → Compile All.

Figure 3: Compiling HDL Files

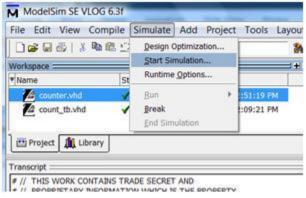

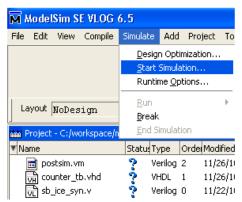

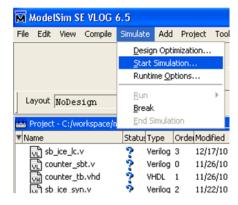

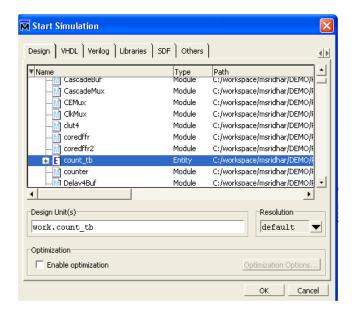

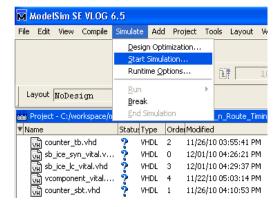

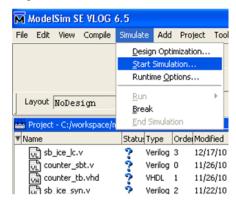

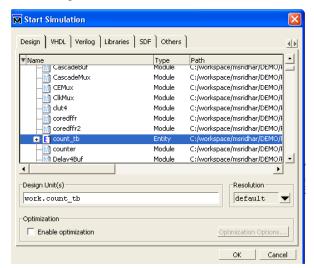

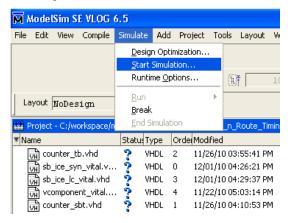

5. Choose Simulate → Start Simulation.

Figure 4: Pre-Synthesis Simulation

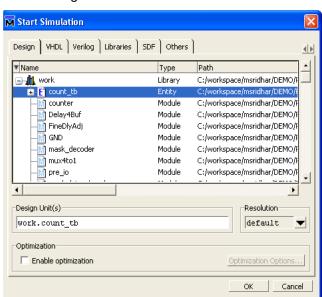

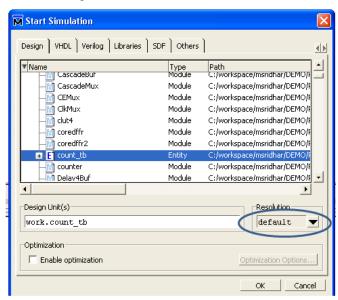

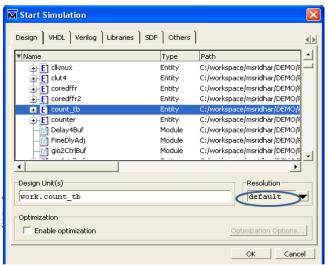

6. Expand the work folder and highlight count\_tb. Clock OK.

M Start Simulation Design VHDL Verilog Libraries SDF Others 4 3 ▼ Name Path Type ■ work Library C:/Users/scott/projects/counter/presim/work count\_tb C:/Users/scott/projects/counter/pre **⊕ E** counter Entity C:/Users/scott/projects/counter/presim/counter.vhd MIA AIM Library c:\modeltech\_6.3f\xilinx\_libs\abel\aim ■ AIM\_VER c:\modeltech\_6.3f\xilinx\_libs\abel\_ver\aim\_ver Library ■ CPLD c:\modeltech\_6.3f\xilinx\_libs\cpld Library CPLD\_VER c:\modeltech\_6.3f\xilinx\_libs\cpld\_ver Library PIS c:\modeltech 6.3f\xilinx libs\abel\nls Library Design Unit(s) Resolution work.count tb default Optimization: Fnable optimization Optimization Options... OK Cancel

Figure 5: Start Simulation Window

- 7. Type the command "view wave" and press the enter key. A new waveform window will show up.

- 8. Type the command "add wave \*" and press the enter key. All I/O signals in the design will show up in the waveform window.

- 9. Type the command "run 2us" and press enter. The 2uS simulation waveform will show up in the waveform window.

- 10. Click the "unlock" button to unlock the waveform window for a better view.

Figure 6: View Waveform Window M ModelSim SE VLOG 6.31 File Edit View Compile Simulate Add Transcript Tools Layout Window Help D# 96 | 1 98 92 | At 8 A 多面积度 🛊 🗢 🗷 100 na 🕽 建建设 产产及 🖀 🖺 Help ▼ | 是是是日 | 下回回| 歌》| 傷 | 我只看我 2 XOX D B tayout Simulate Workspace: ± £ X Objects : wave - default \* Instance Design unit e M uut counter(be... 04 → Ine\_36 count\_tb(te... - 3 line\_47 count\_tb(te... std\_logic\_unsigned std\_logic\_u... std\_logic\_arith std\_logic\_ar... # std\_logic\_1164 std logic ... Now 2000 ns Clickto standard standard 3 4 3 4 ы unlock Project & Library Sim E F6.50 wave window # -- Loading package std\_logic\_unsigned # -- Loading entity counts # Loading work counter(behavioral) VSBM 2> view wave # .main\_pane.mdi.interior.cs.vm.paneset.cli\_0.wf.clip.cs.pw.wf VSBM 3> add wave VSM 4> run 2us Waveform window Enter command

11. Click "count" to expand this bus. Right-click "count" and choose Radix→unsigned to change the bus number radix. Click "Zoom Full" to have a better view.

Figure 7: Waveform Window

#### Generating Files Required for Post-Synthesis and Post-Route Simulations

This section details the steps for generating the files that are required for performing post-synthesis and post-route simulations.

1. Start iCEcube2 and create a new project by clicking Project→New Project. Browse to the project folder, enter a new project name, and select an appropriate part. Click "Next".

SiliconBlue iCEcube2 File View Tool Window Help Open Project Close Project New Project ? X prj\_demo\_sbt.project prj\_sbt.project Project prj\_sbt.project Project Name: postsim prj\_sbt.project prj\_sbt.project Project Directory: C:\workspace\msridhar\DEMO -Device **Browse** Launch Synthesis Tool Device Family: iCE65 P&R Flow Select Implementation Device: L04 Add P&R Files Device Package: CB284 Import P&R Input Files

Run Placer Power Grade: L Run Router

Generate Bitmap Operating Condition -Ambient Temperature (in degrees Celsius) IP Exporter u Best: Range: Typical: Worst: Output Files Reports

Bitmap Simulation Netlist Best: □ Device/Operating Condition Voltage Tolerance Range: Typical: Worst: Device Info +/-5%(datasheet defaul V 1.2 1.14 DeviceFamily Device Device Package Best Typical Worst Power Grade - Operating Condition Core Voltage(V) Start From Synthesis Temperature(C) Start From BackEnd IP Generation Cancel Create a new project

Figure 8: Creating a New Project in iCEcube2

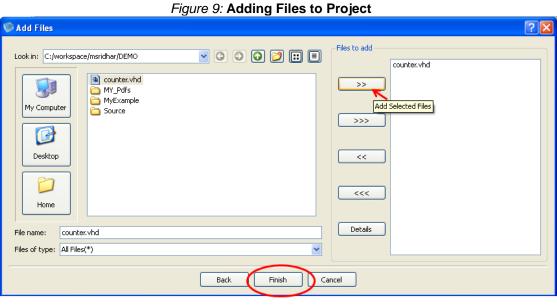

2. Highlight counter.vhd and click ">>" to add counter.vhd to the right panel. Click on "Finish".

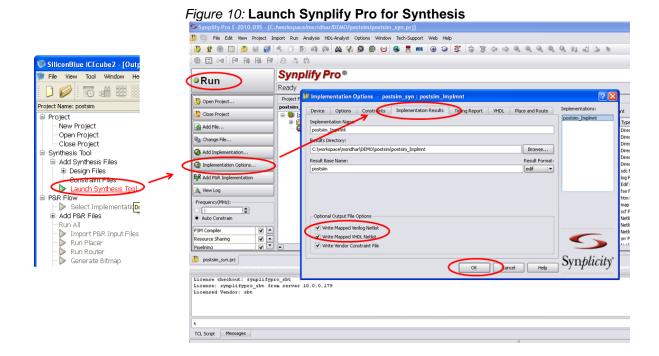

3. Click the "Launch Synthesis Tool" button to launch Synplify Pro® for synthesis. To generate a postsynthesis simulation model in Verilog/VHDL, set the "Write Mapped Verilog Netlist/Write Mapped VHDL Netlist" option in the synthesis tool by going through Implementation Options -> Implementation Results, before doing synthesis. Click RUN in Synplify Pro to synthesize the design.

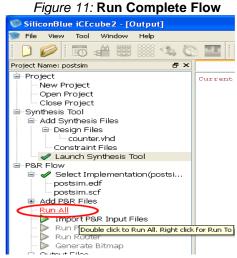

4. Close Synplify Pro after synthesis. This will bring you back to the iCEcube2 tool window. The synthesis outputs "PRJNAME.edf" and "PRJNAME.scf" are automatically added to "Select Implementation" in "P&R Flow" of iCEcube2. Click "Run All" to run placement, routing and Bitmap Generation.

After running the complete flow, the following outputs will be generated.

- PRJNAME.vm, post-synthesis simulation Verilog model

- PRJNAME.vhm, post-synthesis simulation VHDL model

- counter sbt.v, post-route timing simulation Verilog model

- counter sbt.vhd, post-route timing simulation VHDL model

- counter sbt.sdf, for post-route timing Verilog model simulation

- counter\_sbt\_vital.sdf, for post-route timing VHDL model simulation

Post-synthesis simulation models can be found typically in PRJNAME/PRJNAME Implmnt/. These are generated only if you keep the settings mentioned in Step 3 during synthesis.

The post-synthesis simulation VHDL model PRJNAME.vhm needs to be edited to remove the following two lines for ModelSim Lattice Edition.

```

library symplify;

use symplify.components.all;

```

Post-route timing models can be found typically in PRJNAME/PRJNAME\_Implmnt/sbt/outputs/simulation\_netlist

SDF is a standardized representation of timing data commonly used when exchanging timing information between design and simulation tools.

#### Post-Synthesis Functional Simulation (Verilog/VHDL)

- Generate the files that are required for a post-synthesis functional simulation model using the steps described in the section "Generating Files Required for Post-Synthesis and Post-Route Simulations".

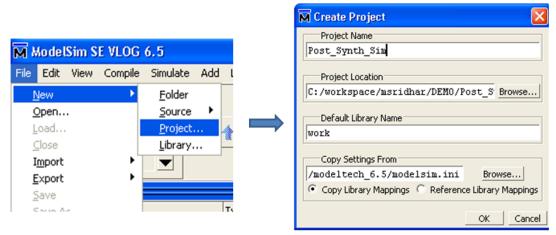

- 2. Open ModelSim. Create new project using File → New → Project. In the New Project window, give a project name and browse to a folder where the project needs to be saved. Click OK.

Figure 12: Create New Project

- 3. Click "Add Existing Files" and add the following files:

- a. PRJNAME.vm, sb\_ice\_syn.v, counter\_tb.vhd for Verilog post-synthesis simulation

- b. PRJNAME.vhm, vcomponent\_vital.vhd, sb\_ice\_lc\_vital.vhd, sb\_ice\_syn\_vital.vhd, counter\_tb.vhd for VHDL post-synthesis simulation

sb\_ice\_syn.v can be found in \$INST\_DIR/verilog and vcomponent\_vital.vhd, sb\_ice\_lc\_vital.vhd, and sb\_ice\_syn\_vital.vhd can be found in \$INST\_DIR/VHDL.

If your design contains **PLL**, add **ABIPTBS8.v** and **ABIWTCZ4.v** in \$INST\_DIR/verilog. To perform post-synthesis simulation on a VHDL design having PLL, you need a mixed-language simulator, since the PLL model (ABIPTBS8.v) is available only in Verilog format. If the design contains **Hardened IP** primitives, add the encrypted Verilog simulation library **sb\_ice\_ipenc\_modelsim.v**, available in \$INST\_DIR/Verilog.

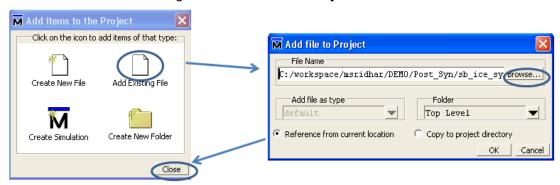

Close the "Add items to project" window once all the files are added.

Figure 13: Add Files to Project

Choose Compile → Compile All.

For VHDL post-synthesis simulation, vcomponent\_vital.vhd should be compiled first, then sb\_ice\_syn\_vital.vhd, sb\_ice\_lc\_vital.vhd, and other files.

Figure 14: Compile All

- 5. Start simulation from Simulate → Start Simulation.

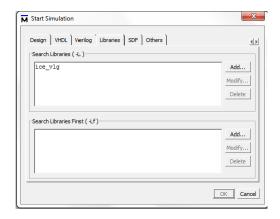

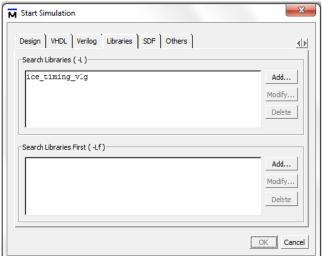

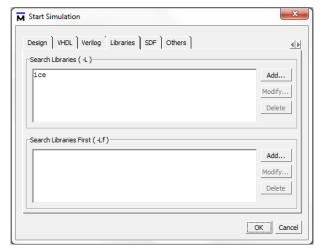

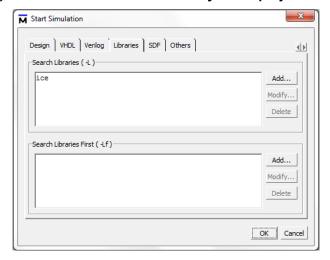

- 6. In the Simulation window, select the Libraries tab and add the **ice\_vlg** resource library for Verilog simulation or **ice** resource library for VHDL simulation in the search libraries path.

Figure 15: Start Simulation

7. Expand the work folder in the "Start Simulation" window and highlight "counter tb". Click OK.

Figure 16: Run Simulation

8. This will open the simulation window. Add the signals wave window and perform simulation as explained in the "Pre-Synthesis Simulation" section from point 7 onwards.

#### Place-and-Route Functional Simulation (Verilog)

- 1. Generate the files that are required for post-route functional simulation model using the steps described in the section "Generating Files Required for Post-Synthesis and Post-Route Simulations."

- 2. Open ModelSim. Create new project using File → New → Project. In the New Project window, give a project name and browse to a folder where the project needs to be saved. Click OK.

Figure 17: Create New Project

- 3. Click "Add Existing Files" and add the following files:

- a. counter sbt.v

- b. counter\_tb.vhd

Add the following Verilog simulation libraries available in \$INST DIR/verilog

- a. sb ice syn.v

- b. sb\_ice\_lc.v

If your design contains PLL, add ABIPTBS8.v & ABIWTCZ4.v in \$INST\_DIR/verilog.

If the design contains **Hardened IP** primitives, add the encrypted simulation library **sb\_ice\_ipenc\_modelsim.v** available in \$INST\_DIR/Verilog.

Close the "Add items to project" window once all the files are added.

Figure 18: Add Files to Project

4. Click on Compile → Compile All.

Figure 6: Compile All

5. Start simulation from Simulate → Start Simulation.

Figure 7: Start Simulation

- 6. In the Simulation window, select the Libraries tab and add the **ice\_vlg** resource library in the search libraries path.

- 7. Expand the work folder in the "Start Simulation" window and highlight "counter tb". Click OK.

Start Simulation

Design | VHDL | Verilog | Libraries | SDF | Others |

Search Libraries (-L.) |

ice\_vlg | Add... |

Modify... |

Delete |

OK | Cancel |

Figure 8: Run Simulation

8. This will open the simulation window. Add the signals wave window and perform simulation as explained in the "Pre-Synthesis Simulation" section from point 7 onwards.

#### Place-and-Route Timing Simulation (Verilog)

- 1. Generate the files that are required for the post-route timing simulation model using the steps described in the section "Generating Files Required for Post-Synthesis and Post-Route Simulations".

- 2. Open ModelSim. Create a new project using File → New → Project. In the New Project window, give a project name and browse to a folder where the project needs to be saved. Click OK.

M Create Project M ModelSim SE VLOG 6.5 Project Name Place\_n\_Route\_Timing\_Verilog File Edit View Compile Simulate Add New Folder Project Location Open... Source C:/workspace/msridhar/DEMO/PNR VH Browse.. Project. Load... Default Library Name Close Library... work Import Export Copy Settings From /modeltech 6.5/modelsim.ini Browse... Save Copy Library Mappings

Reference Library Mappings Cours Ar Cancel

Figure 9: Create New Project

3. Click "Add Existing Files" and add the following files:

counter\_sbt.v, sb\_ice\_syn.v, sb\_ice\_lc.v, counter\_tb.vhd for Verilog post-route timing simulation The sb\_ice\_syn.v, sb\_ice\_lc.v verilog files can be found in \$INST\_DIR/verilog.

If your design contains **PLL**, add **ABIPTBS8.v** in \$INST\_DIR/verilog. If the design contains **Hardened IP** primitives, add the encrypted simulation library **sb\_ice\_ipenc\_modelsim.v** available in \$INST\_DIR/Verilog.

Close the "Add items to Project" window once all the files are added.

Figure 10: Add Files to Project

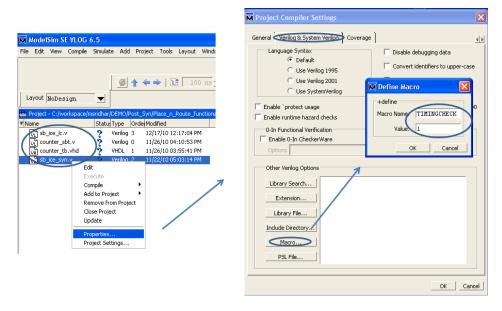

4. In the Project Compiler Settings window, select the "Verilog & System Verilog" tab and click "Macro". In the Define Macro window, set the macro name to "TIMINGCHECK" and set the value to 1. Click OK.

Figure 11: Set TIMINGCHECK Macro

5. Click on Compile → Compile All.

Figure 12: Compile All

6. Start simulation using Simulate → Start Simulation

Figure 13: Start Simulation

7. In the Simulation window, select the "Libraries" tab and add the "ice\_timing\_vlg" resource library in the search libraries path.

Figure 27: Add "ice\_timing\_vlg" resource library to the project

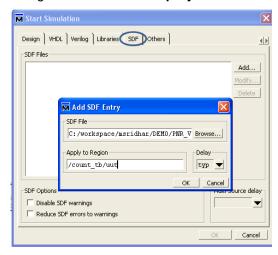

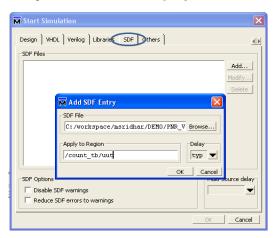

8. In the Simulation window, select the SDF tab. Add the SDF file counter\_sbt.sdf and type "/count tb/uut" in "Apply to Region". Click OK.

Figure 28: Add SDF to project

9. In the Design tab, select "count\_tb" under work. Make sure that the "Time Resolution" was set to PS. Click OK.

Figure 29: Run Simulation

10. This will open the simulation window. Add the signals wave window and perform simulation as explained in the "Pre-Synthesis Simulation" section from point 7 onwards.

#### Place-and-Route Functional Simulation (VHDL)

- 1. Generate the files that are required for post-route functional simulation model using the steps described in the section "Generating Files Required for Post-Synthesis and Post-Route Simulations".

- 2. Create a new project using File → New → Project. In the New Project window, give a project name and browse to a folder where the project needs to be saved. Click OK.

Figure 30: Create New Project

- 3. Click "Add Existing File" and add the following files:

- a. counter\_sbt.vhd

- b. counter tb.vhd

Close the "Add items to the Project" window once all the files are added.

Figure 31: Add Files to Project

4. Click Compile → Compile All.

Figure 32: Compile All

5. Start simulation from Simulate → Start Simulation.

Figure 33: Start Simulation

6. In the simulation window, select the tab "Libraries" and add the "**ice**" resource library in the search libraries path.

Figure 34: Add "ice" resource library to the project

7. Expand the work folder in the "Start Simulation" window and highlight "counter tb". Click OK.

Figure 35: Run Simulation

This will open the simulation window. Add the signals wave window and perform simulation as explained in the "Pre-Synthesis Simulation" section from point 7 onwards.

#### Place-and-Route Timing Simulation (VHDL)

- 1. Generate the files that are required for the post-route timing simulation model using the steps described in the section "Generating Files Required for Post-Synthesis and Post-Route Simulations".

- 2. Create new project using File → New → Project. In the New Project window, give a project name and browse to a folder where the project needs to be saved. Click OK.

Figure 36: Create New Project

- 3. Click "Add Existing Files" and add the following files:

- a. counter sbt.vhd

- b. counter\_tb.vhd

Close the "Add items to the Project" window once all the files are added.

Click on the icon to add items of that type:

Create New File Add Existing File

Create Simulation Create New Folder

Close

Add file to Project

File Name

C: /workspace/msridhar/DEMO/Post\_Syn/sb\_ice\_sy crowse...

Add file as type

Gefault

Folder

Top Level

Reference from current location

Copy to project directory

OK Cancel

Figure 37: Add Files to Project

4. Choose Compile → Compile All.

Figure 38: Compile All

5. Start simulation using Simulate  $\rightarrow$  Start Simulation.

Figure 39: Start Simulation

6. In the Simulation window, select the "Libraries" tab and add the "**ice**" resource library in the search libraries path.

Figure 40: Add "ice" resource library to the project

7. In the Simulation window, select the SDF tab. Add the SDF file counter\_sbt\_vital.sdf and type "/count tb/uut" in "Apply to Region". Click OK.

Figure 41: Add SDF to project

8. In the Design tab, select "count\_tb" under work. Make sure that the "Time Resolution" was set to PS. Click OK.

Figure 42: Run Simulation

9. This will open the simulation window. Add the signals wave window and perform simulation as explained in the "Pre-Synthesis Simulation" section from point 7 onwards.

#### Conclusion

The Lattice iCEcube2 development software provides a complete FPGA implementation environment for today's FPGA designers. For simulation needs, the Mentor ModelSim simulator complements the iCEcube2 development software and is a cost effective, easy to use simulation tool.

#### References

For more information on products, solutions, and applications enabled by Lattice Semiconductor Corporation, take the next step and visit <a href="https://www.latticesemi.com">www.latticesemi.com</a>.

## **Revision History**

| Version | Date        | Description                                                                        |

|---------|-------------|------------------------------------------------------------------------------------|

| 1.7     | 24-Nov-2020 | Updated for ModelSim usage changes.                                                |

| 1.6     | 18-Dec-2013 | Added resource library details for iCE40LM primitives.                             |

| 1.5     | 26-APR-2013 | Added resource library generation details for post route VHDL simulations.         |

| 1.4     | 24-DEC-2010 | Added sections for pre/post synthesis, functional/timing, Verilog/VHDL simulations |

| 1.3     | 23-DEC-2008 | Updated corporate contact information.                                             |

| 1.2     | 20-OCT-2008 | Initial release, updated iCEcube screen shots and timing simulation information.   |

| 1.1     | 06-AUG-2008 | First draft, functional simulation only.                                           |

#### Copyright

Copyright © 2020 Lattice Semiconductor Corporation. All rights reserved. This document may not, in whole or part, be reproduced, modified, distributed, or publicly displayed without prior written consent from Lattice Semiconductor Corporation ("Lattice").

#### **Trademarks**

All Lattice trademarks are as listed at <a href="www.latticesemi.com/legal">www.latticesemi.com/legal</a>. Synopsys and Synplify Pro are trademarks of Synopsys, Inc. Aldec and Active-HDL are trademarks of Aldec, Inc. ModelSim and Questa are trademarks or registered trademarks of Siemens Industry Software Inc. or its subsidiaries in the United States or other countries. All other trademarks are the property of their respective owners.

#### **Disclaimers**

NO WARRANTIES: THE INFORMATION PROVIDED IN THIS DOCUMENT IS "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF ACCURACY, COMPLETENESS, MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL LATTICE OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (WHETHER DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL, INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE INFORMATION PROVIDED IN THIS DOCUMENT, EVEN IF LATTICE HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME JURISDICTIONS PROHIBIT THE EXCLUSION OR LIMITATION OF CERTAIN LIABILITY, SOME OF THE ABOVE LIMITATIONS MAY NOT APPLY TO YOU.

Lattice may make changes to these materials, specifications, or information, or to the products described herein, at any time without notice. Lattice makes no commitment to update this documentation. Lattice reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors contained herein or to advise any user of this document of any correction if such be made. Lattice recommends its customers obtain the latest version of the relevant information to establish that the information being relied upon is current and before ordering any products.

**Lattice Semiconductor Corporation**

5555 N.E. Moore Court,

Hillsboro , Oregon 97124-6421 United States of America

Tel: +1 503 268 8000 Fax: +1 503 268 8347 www.latticesemi.com