# MachXO2 Soft I2C Slave with Clock Stretching

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| 1. Introduction                                               |                |

|---------------------------------------------------------------|----------------|

| 2. Block Diagram                                              |                |

| 3. Port List                                                  |                |

| 4. Deviations from MachXO2 Hard I2C Implementation            | 6              |

| 4.1. Added functionality                                      | 6              |

| 4.2. Reduced functionality                                    |                |

| 5. Registers                                                  | <del>-</del> - |

| 6. Design Migration                                           |                |

| 6.1. EFB Identification and Parameterization                  |                |

| 6.2. Soft Core installation                                   | 15             |

| 6.3. User Design Modifications                                |                |

| 7. Customization                                              |                |

| 7.1. SDA DEL calculation                                      | 17             |

| 7.2. I <sup>2</sup> C Address                                 |                |

| 8. Special Cases                                              |                |

| 8.1. Concurrent EFB use                                       |                |

| 8.2. Multiple I <sup>2</sup> C slaves                         | 18             |

| 8.3. Wishbone Mux                                             |                |

| 9. Resource Utilization – Soft EFB I <sup>2</sup> C           |                |

| References                                                    |                |

| Technical Support Assistance                                  | 21             |

| Revision History                                              |                |

| Figures                                                       |                |

| Figure 2.1. Soft I <sup>2</sup> C Slave                       |                |

| Figure 6.1. IPexpress Instance Example                        |                |

| Figure 6.2. HDL Instance Example                              |                |

| Figure 6.3. IPexpress I <sup>2</sup> C Port Type Example      |                |

| Figure 6.4. IPexpress I <sup>2</sup> C Settings Example       | 14             |

| Figure 6.5. Verilog Port and Address Example                  |                |

| Figure 6.6. VHDL Port and Address Example                     |                |

| Figure 6.7. Primary Files Added to New Implementation Example |                |

| Figure 8.1. WBmux21.v BLOCK DIAGRAM                           | 18             |

| Tables                                                        |                |

| Table 3.1. Port List                                          | 6              |

| Table 6.1 Primary and Secondary File Sets                     | 10             |

## 1. Introduction

The primary purpose of this Reference Design is to provide a form, fit and function equivalent, "drop-in" module to replace the Lattice MachXO2 hard I<sup>2</sup>C core in user designs which require Clock-Stretching support. This reference design has been engineered to require little or no modification to pre-existing WISHBONE bus control logic, and to provide pin-for-pin hook-up. The reference design utilizes 'soft' LUT resources instead of 'hard' logic. As this design consumes additional fabric resources, it can impact timing closure and/or design routability is certain designs. Please refer to Port List, Register Definitions, and Resource Utilization sections for more details.

I<sup>2</sup>C Clock-Stretching is an optional flow-control mechanism in the I2C specification. A slave device can use clockstretching to force a pause in an I<sup>2</sup>C transaction by holding the SCL line low ('0'). The I<sup>2</sup>C Master is prevented from continuing the transaction until the slave releases SCL. The MachXO2 hard I2C block does not operate reliably when clock-stretching is enabled. See References section for additional information on I<sup>2</sup>C bus operation. For details regarding MachXO2 and clock-stretching support, refer to Lattice Product Change Notice PCN #10A-13 at www.latticesemi.com.

As with the original MachXO2 Embedded Function Block (EFB), the WISHBONE control port conforms to the WISHBONE Classic Bus Cycle protocol. Block cycles are not supported. Please refer to the WISHBONE specification or Using User Flash Memory and Hardened Control Functions in MachXO2 Devices Reference Guide (FPGA-TN-02163) for more details (see References section).

Two versions of this Reference design are provided, one containing the Primary WISHBONE registers and I<sup>2</sup>C pin names, the other containing the Secondary WISHBONE registers and I<sup>2</sup>C pin names. As the MachXO2 dedicated primary I<sup>2</sup>C port may be recovered for use as GPIO, the same device pins may be used by the Reference Design as used originally by the hard care. The same is true for the Secondary I<sup>2</sup>C port pins. Thus, no change to an existing Printed Circuit Board (PCB) is necessary.

In the rare case where multiple I<sup>2</sup>C Slaves supporting clock stretching are required, the soft core may be instantiated multiple times, and the WISHBONE ports multiplexed together externally with user circuitry (see Special Cases).

The MachXO2 is a family of ultra-low power, instant-on, non-volatile PLDs with densities from 256 to 6864 LUTs. Each device in the family contains a rich feature set, including Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs) pre-engineered source synchronous I/O support, advanced configuration support including dual-boot capability. Hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter are contained in the Embedded Function Block (EFB). These features allow these devices to be used in low cost, high volume consumer and system applications.

# 2. Block Diagram

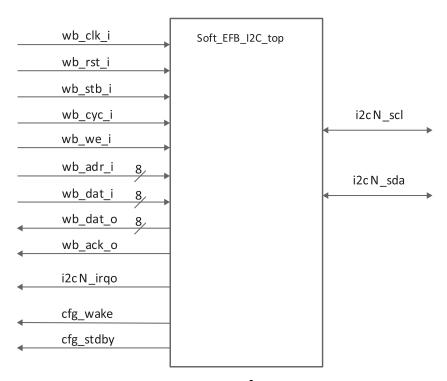

Figure 2.1. Soft I<sup>2</sup>C Slave

## 3. Port List

Table 3.1. Port List

| Port Name | Width | Direction | BUF Type   | Description                                                                                                                                   |

|-----------|-------|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| wb_clk_i  | 1     |           |            | WISHBONE clock. All WISHBONE input signals are evaluated, and output signal updated, on the rising edge of this clock.                        |

| wb_rst_i  | 1     | i         |            | Module asynchronous reset. Asserted high. Both WISHBONE and I2C interfaces are reset.                                                         |

| wb_stb_i  | 1     | i         |            | WISHBONE strobe. Indicates this slave module is selected.                                                                                     |

| wb_cyc_i  | 1     | i         |            | WISHBONE cycle. Provided for port compatibility only. This signal is not connected internally. It may be arbitrarily driven or left floating. |

| wb_we_i   | 1     | i         |            | WISHBONE write enable. Indicates the current cycle is WRITE cycle when asserted logic '1' and is READ cycle when asserted logic '0'.          |

| wb_adr_i  | 8     | i         |            | WISHBONE address. Selects target register                                                                                                     |

| wb_dat_i  | 8     | i         |            | WISHBONE write data. Input data for write cycles.                                                                                             |

| wb_dat_o  | 8     | 0         |            | WISHBONE read data. Output data for read cycles                                                                                               |

| wb_ack_o  | 1     | 0         |            | WISHBONE acknowledge. Input data has been captured, or output data is valid when asserted logic '1'.                                          |

| cfg_wake  | 1     | 0         |            | Signal to wakeup for standy/sleep mode. When enabled, asserted high on I2C Slave Address match or General Call Wakeup command.                |

| cfg_stdby | 1     | 0         |            | Provided for port compatibility only. This signal always drives a logic '0'.                                                                  |

| i2c1_clk  | 1     | i/o       | open drain | Primary instance only: I2C clock                                                                                                              |

| i2c1_sda  | 1     | i/o       | open drain | Primary instance only: I2C data                                                                                                               |

| i2c1_irqo | 1     | 0         |            | Primary instance only: Interrupt, asserted high when enabled                                                                                  |

| i2c2_clk  | 1     | i/o       | open drain | Secondary instance only: I2C clock                                                                                                            |

| i2c2_sda  | 1     | i/o       | open drain | Secondary instance only: I2C data                                                                                                             |

| i2c2_irqo | 1     | 0         |            | Secondary instance only: Interrupt, asserted high when enabled                                                                                |

# 4. Deviations from MachXO2 Hard I2C Implementation

# 4.1. Added functionality

#### SDA DEL

In the Hard IP block, SDA\_DEL is set in time units, and calibrated using an internal high-speed clock reference. In this reference design, the SDA\_DEL is set in WISHBONE clock periods, and calibrated using a new bit field, SDA\_DEL\_FACTOR. SDA\_DEL\_FACTOR is set in BR1 (0x43/0x4D) bits [7:4]. See Customization section for the relationships between SDA\_DEL, SDA\_DEL\_FACTOR, and WISHBONE clock frequency.

#### Programmable I<sup>2</sup>C address

In the MachXO2 Hard IP block, the I2C address is set using IPexpress and is stored in the Feature Row portion of non-volatile RAM. In this reference design, the default Slave I2C address is set in the top level i2c\_config.v file using a 'define. In addition, a new register location (0x4A/0x54) is provided to allow dynamic R/W access to the I<sup>2</sup>C address. Lattice recommends using this feature for development or debugging purposes only.

7

#### 4.2. **Reduced functionality**

#### cfg\_stdby

The ability to receive and interpret the 'Enter Standby' command is reserved for the I2C Configuration block of the EFB. This Reference Design emulates the User block functionality only.

#### wb\_cyc\_i

For WISHBONE Classic bus cycles, wb cyc i and wb stb i are essentially redundant. This Reference Design utilizes only wb\_stb\_i.

#### Registers 5.

#### Notes:

Unless otherwise specified, all Reserved bits in writable registers shall be written '0'.

Differences from the XO2 Hard I 2C Macro are outlined in bold.

|                                  | I <sup>2</sup> C Control (Pri/Sec) |      |        |        |         |                        |       |        |  |  |  |  |  |

|----------------------------------|------------------------------------|------|--------|--------|---------|------------------------|-------|--------|--|--|--|--|--|

| I2C_1_CR / I2C_2_CR              |                                    |      |        |        |         |                        |       |        |  |  |  |  |  |

| Bit                              | 7                                  | 6    | 3      | 2      | 1       | 0                      |       |        |  |  |  |  |  |

| Name                             | I2CEN                              | GCEN | WKUPEN | (Rsrv) | SDA_DEL | _SEL[1:0] <sup>1</sup> | (Rese | erved) |  |  |  |  |  |

| Default                          | 1                                  | 0    | 0      | 0      | 1 0 0   |                        |       |        |  |  |  |  |  |

| Access R/W R/W R/W — R/W R/W — — |                                    |      |        |        |         |                        |       |        |  |  |  |  |  |

Note: The default value is defined by `define SDA DEL INIT in the file "i2c config.v.

I2C System Enable Bit – This bit enables the I2C core functions. If I2CEN is cleared, I2C core is disabled **I2CEN**

> and forced into idle state. 0: I2C function is disabled 1: I2C function is enabled

**GCEN** Enable bit for Generic Call Response – Enables the generic call response in slave mode.

> 0: Disable 1: Enable

**WKUPEN** Wake-up from Standby/Sleep (by Slave Address matching) Enable Bit – When this bit is enabled

> the, I2C core can send a wake-up signal to the on-chip power manager to wake the device up from standby/sleep. The wake-up function is effective when the Slave Address is matched during

standby/sleep mode.

0: Disable 1: Enable

SDA\_DEL\_SEL[1:0] SDA Output Delay (Tdel) Selection

> 00: 4xSDA\_DEL\_FACTOR + 2.5 +/- 0.5 tWB periods 01: 2xSDA\_DEL\_FACTOR + 2.5 +/- 0.5 tWB periods 10: 1xSDA DEL FACTOR + 2.5 +/- 0.5 tWB periods

11: 0.25 +/- 0.25 tWB periods

|            | I <sup>2</sup> C Command (Pri/Sec) |     |     |     |     |        |           |      |  |  |  |  |  |

|------------|------------------------------------|-----|-----|-----|-----|--------|-----------|------|--|--|--|--|--|

| I2C_1_CMDR | / I2C_2_CMDR                       |     |     |     |     |        | 0x41/0x4B |      |  |  |  |  |  |

| Bit        |                                    |     |     |     |     |        |           |      |  |  |  |  |  |

| Name       | STA                                | STO | RD  | WR  | ACK | CKSDIS | (Reser    | ved) |  |  |  |  |  |

| Default    | 0                                  | 0   | 0   | 0   | 0   | 0      | 0         | 0    |  |  |  |  |  |

| Access     | R/W                                | R/W | R/W | R/W | R/W | R/W    | _         | _    |  |  |  |  |  |

© 2014-2019 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

STA Generate START (or Repeated START) condition.

STO Generate STOP condition

RD Indicate Read from slave

WR Indicate Write to slave

ACK Acknowledge Option – when receiving, ACK transmission selection

0: Send ACK 1: Send NACK

CKSDIS Clock Stretching Disable. The I2C cores support "wait state" or clock stretching from slave, meaning

slave can enforce a wait state if it needs time to finish the task. Bit CKSDIS disables the clock

stretching if desired by the user. In that case, the overflow flag must be monitored.

0: Enabled1: Disabled

| i <sup>2</sup> C Clock Prescale 0 (Pri/Sec) |     |            |     |     |     |     |     |     |  |  |  |

|---------------------------------------------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|--|

| I2C_1_BR0 / I2C_2_BR0                       |     |            |     |     |     |     |     |     |  |  |  |

| Bit                                         | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

| Name                                        |     | (Reserved) |     |     |     |     |     |     |  |  |  |

| Default                                     | 0   | 0          | 0   | 0   | 0   | 1   | 1   | 1   |  |  |  |

| Access                                      | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

|               | i <sup>2</sup> C Clock Prescale 1 (Pri/Sec) |            |                        |   |       |           |     |   |  |  |  |  |

|---------------|---------------------------------------------|------------|------------------------|---|-------|-----------|-----|---|--|--|--|--|

| I2C_1_BR1 / I | 2C_2_BR1                                    |            |                        |   |       | 0x43/0x4D |     |   |  |  |  |  |

| Bit           | Bit 7 6 5 4 3 2 1 0                         |            |                        |   |       |           |     |   |  |  |  |  |

| Name          |                                             | SDA_DEL_FA | CTOR[3:0] <sup>1</sup> |   | (Rese | ved)      |     |   |  |  |  |  |

| Default       | 0                                           | 0          | 0                      | 1 | 0     | 0         | 0   | 0 |  |  |  |  |

| Access        | _                                           | _          |                        |   | _     | R/W       | R/W |   |  |  |  |  |

Note: The default value is defined by `define SDA\_DEL\_FACTOR in the file "i2c\_config.v.

I2C\_PRESCALE[9:0] I2C Clock Prescale value.

(For this Slave-only implementation, these bits are undefined and reserved)

SDA DEL FACTOR[3:0] SDA Delay Factor.

This 4-bit value is used in conjunction with SDA\_DEL to set the SCL-to-SDA delay when XO2 is driving SDA.

|                         | I <sup>2</sup> C Transmit Data Register (Pri/Sec) |                 |  |             |             |  |  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------|-----------------|--|-------------|-------------|--|--|--|--|--|--|--|--|

| 12C_1_TXDR / I2C_2_TXDR |                                                   |                 |  |             |             |  |  |  |  |  |  |  |  |

| Bit                     | 7                                                 | 7 6 5 4 3 2 1 0 |  |             |             |  |  |  |  |  |  |  |  |

| Name                    |                                                   |                 |  | I2C_Transmi | t_Data[7:0] |  |  |  |  |  |  |  |  |

| Default                 | 0                                                 | 0 0 0 0 0 0 0   |  |             |             |  |  |  |  |  |  |  |  |

| Access                  | W                                                 | w w w w w w     |  |             |             |  |  |  |  |  |  |  |  |

I2C Transmit Data[7:0] I2C Transmit Data.

This register holds the byte that will be transmitted on the I2C bus during the Write Data phase. Bit 0 is LSB and will be transmitted last. When transmitting the slave address, Bit 0 represents the R/W bit.

© 2014-2019 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

|               | I <sup>2</sup> C Status (Pri/Sec) |      |      |     |      |       |      |           |  |  |  |  |

|---------------|-----------------------------------|------|------|-----|------|-------|------|-----------|--|--|--|--|

| I2C_1_SR / I2 | I2C_1_SR / I2C_2_SR               |      |      |     |      |       |      | 0x45/0x4F |  |  |  |  |

| Bit           | 7                                 | 2    | 1    | 0   |      |       |      |           |  |  |  |  |

| Name          | TIP                               | BUSY | RARC | SRW | ARBL | TRRDY | TROE | HGC       |  |  |  |  |

| Default       | _                                 | _    | _    | _   |      |       |      |           |  |  |  |  |

| Access        | R                                 | R    | R    | R   | R    | R     | R    | R         |  |  |  |  |

#### TIP Transmit In Progress.

The current data byte is being transferred. Note that the TIP flag will suffer one-half SCL cycle latency right after the start condition because of the signal synchronization. Also note that this bit could be high after configuration wake-up and before the first valid I2C transfer start (when BUSY is low), and it is not indicating byte in transfer, but an invalid indicator.

- 1: Byte transfer in progress

- 0: Byte transfer complete

#### BUSY I2C Bus busy.

The I2C bus is involved in transaction. This is set at start condition and cleared at stop. Note only when this bit is set should all other I2C SR bits be treated as valid indicators for a valid transfer.

- 1: I2C bus busy

- 0: I2C bus not busy

#### RARC Received Acknowledge.

An acknowledge response from the addressed slave (during master write) or from receiving master (during master read) was received.

- 1: No acknowledge received

- 0: Acknowledge received

#### SRW Slave R/W.

Indicates transmit or receive mode.

- 1: master receiving / slave transmitting

- 0: master transmitting / slave receiving

#### ARBL Arbitration Lost.

The core has lost arbitration in Master mode. This bit is capable of generating an interrupt.

- 1: Arbitration Lost

- 0: Normal

#### TIP Transmit In Progress.

The current data byte is being transferred. Note that the TIP flag will suffer one-half SCL cycle latency right after the start condition because of the signal synchronization. Also note that this bit could be high after configuration wake-up and before the first valid I2C transfer start (when BUSY is low), and it is not indicating byte in transfer, but an invalid indicator.

#### TRRDY Transmitter or Receiver Ready.

The I2C Transmit Data register is ready to receive transmit data, or the I2C Receive Data Register contains receive data (dependent upon master/slave mode and SRW status). This bit is capable of generating an interrupt.

- 1: Transmitter or Receiver is ready

- 0: Transmitter of Receiver is not ready

TROE Transmitter/Receiver Overrun Error or NACK received.

A transmit or receive overrun error has occurred (dependent upon master/slave mode and SRW status), or a No Acknowledge was received (only when RARC also set). This bit is capable of generating an interrupt.

- 1: Transmitter or Receiver Overrun detected or NACK received

- 0: Normal

HGC Hardware General Call Received.

A hardware general call has been received in slave mode. The corresponding command byte will be available in the General Call Data Register. This bit is capable of generating an interrupt.

- 1: General Call Received in slave mode

- 0: Normal

|            | I <sup>2</sup> C General Call Data Register (Pri/Sec) |                 |  |           |          |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------|-----------------|--|-----------|----------|--|--|--|--|--|--|--|

| I2C_1_GCDR | / I2C_2_GCDR                                          |                 |  | 0x46/0x50 |          |  |  |  |  |  |  |  |

| Bit        | 7                                                     | 7 6 5 4 3 2 1 0 |  |           |          |  |  |  |  |  |  |  |

| Name       |                                                       |                 |  | I2C_GC_D  | ata[7:0] |  |  |  |  |  |  |  |

| Default    | _                                                     |                 |  |           |          |  |  |  |  |  |  |  |

| Access     | R                                                     | R R R R R R     |  |           |          |  |  |  |  |  |  |  |

I2C\_GC\_Data[7:0]

I<sup>2</sup>C General Call Data.

This register holds the second (command) byte of the General Call transaction on the I2C bus.

|            | I <sup>2</sup> C Receive Data Register (Pri/Sec) |                 |  |             |            |  |  |  |  |  |  |  |

|------------|--------------------------------------------------|-----------------|--|-------------|------------|--|--|--|--|--|--|--|

| I2C_1_RXDR | / I2C_2_RXDR                                     |                 |  | 0x47/0x51   |            |  |  |  |  |  |  |  |

| Bit        | 7                                                | 7 6 5 4 3 2 1 0 |  |             |            |  |  |  |  |  |  |  |

| Name       |                                                  |                 |  | I2C_Receive | _Data[7:0] |  |  |  |  |  |  |  |

| Default    | _                                                |                 |  |             |            |  |  |  |  |  |  |  |

| Access     | R                                                | R R R R R R     |  |             |            |  |  |  |  |  |  |  |

I2C Receive Data[7:0]

I2C Receive Data.

This register holds the byte captured from the I2C bus during the Read Data phase. Bit 0 is LSB and was received last.

|               | I <sup>2</sup> C Interrupt Status (Pri/Sec) |                 |      |     |         |          |         |           |  |  |  |  |

|---------------|---------------------------------------------|-----------------|------|-----|---------|----------|---------|-----------|--|--|--|--|

| 12C_1_IRQ / I | I2C_1_IRQ / I2C_2_ IRQ                      |                 |      |     |         |          |         | 0x48/0x52 |  |  |  |  |

| Bit           | 7                                           | 7 6 5 4 3 2 1 0 |      |     |         |          |         |           |  |  |  |  |

| Name          |                                             | (Reser          | ved) |     | IRQARBL | IRQTRRDY | IRQTROE | IRQHGC    |  |  |  |  |

| Default       | _                                           | _               | _    | _   | _       | _        | _       | _         |  |  |  |  |

| Access        | _                                           | _               | _    | R/W | R/W     | R/W      | R/W     |           |  |  |  |  |

**IRQARBL**

Interrupt Status for Arbitration Lost.

When enabled, indicates ARBL was asserted. When INTCLREN='0', write a '1' to this bit to clear the interrupt. When INTCLREN='1', the interrupt is cleared automatically when this register is read.

- 1: Arbitration Lost Interrupt

- 0: No interrupt

**IRQTRRDY**

Interrupt Status for Transmitter or Receiver Ready.

When enabled, indicates TRRDY was asserted. When INTCLREN='0', write a '1' to this bit to clear the interrupt. When INTCLREN='1', the interrupt is cleared automatically when this register is read.

- 1: Transmitter or Receiver Ready Interrupt

- 0: No interrupt

IRQTROE Interrupt Status for Transmitter/Receiver Overrun or NACK received.

When enabled, indicates TROE was asserted. When INTCLREN='0', write a '1' to this bit to clear the interrupt. When INTCLREN='1', the interrupt is cleared automatically when this register is read.

1: Transmitter or Receiver Overrun or NACK received Interrupt

0: No interrupt

IRQHGC Interrupt Status for Hardware General Call Received.

When enabled, indicates HGC was asserted. When INTCLREN='0', write a '1' to this bit to clear the interrupt. When INTCLREN='1', the interrupt is cleared automatically when this register is read.

1: General Call Received in slave mode Interrupt

0: No interrupt

|                            | I <sup>2</sup> C Interrupt Enable (Pri/Sec) |   |            |   |           |            |           |           |  |  |  |  |

|----------------------------|---------------------------------------------|---|------------|---|-----------|------------|-----------|-----------|--|--|--|--|

| I2C_1_ IRQEN / I2C_2_IRQEN |                                             |   |            |   |           |            |           | 0x49/0x53 |  |  |  |  |

| Bit                        | 7                                           | 6 | 5          | 4 | 3         | 2          | 1         | 0         |  |  |  |  |

| Name                       | INTCLREN                                    |   | (Reserved) |   | IRQARBLEN | IRQTRRDYEN | IRQTROEEN | IRQHGCEN  |  |  |  |  |

| Default                    | 0                                           | 0 | 0          | 0 | 0         | 0          | 0         | 0         |  |  |  |  |

| Access                     | _                                           | _ | _          | _ | R/W       | R/W        | R/W       | R/W       |  |  |  |  |

INTCLREN Interrupt Auto Clear Enable:

1: Interrupts are cleared automatically upon a read of the I2C Interrupt Status Register

0: Interrupts are cleared manually by writing to the I2C Interrupt Status Register

IRQARBLEN Interrupt Enable for Arbitration Lost.

1: Interrupt generation enabled0: Interrupt generation disabled

IRQTRRDYEN Interrupt Enable for Transmitter or Receiver Ready

1: Interrupt generation enabled0: Interrupt generation disabled

IRQTROEEN Interrupt Enable for Transmitter/Receiver Overrun or NACK received.

1: Interrupt generation enabled0: Interrupt generation disabled

IRQHGCEN Interrupt Enable for Hardware General Call Received.

1: Interrupt generation enabled0: Interrupt generation disabled

| i <sup>2</sup> C Slave Address MSB (Pri/Sec) |                                         |     |     |     |     |     |     |     |

|----------------------------------------------|-----------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| I2C_1_SADR /                                 | I2C_1_SADR / I2C_2_SADR                 |     |     |     |     |     |     |     |

| Bit                                          | 7                                       | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Name                                         | I2C_Slave_Address_MSB[7:0] <sup>1</sup> |     |     |     |     |     |     |     |

| Default1                                     | 1                                       | 1   | 1   | 1   | 0   | 0   | 0   | 0   |

| Access                                       | R/W                                     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

**Note:** The default value is defined by `define IPex\_I2C\_slave\_addr in the file "i2c\_config.v". The value shown above is used when IPex\_I2C\_slave\_addr =0 (undefined)

i2C\_Slave Address[7:0] I2C Slave Address Most Significant Bits.

I2C\_Slave\_Address[4:0] represent the upper 5 bits of the I2C Slave Address for 7-bit addressing.

The upper bits I2C Slave Address [7:5] are ignored.

I2C\_Slave\_Address[7:0] represent the upper 8 bits of the I2C Slave Address for 10-bit addressing.

The lower 2 LSBs of the I2C Slave Address are fixed by the Reference design: "b01" for the Primary instance and "b10" for the Secondary instance.

Note: Lattice recommends to avoid modifying this register, except for development or debugging purposes.

# 6. Design Migration

#### 6.1. EFB Identification and Parameterization

It is assumed that you are familiar with your FPGA design and that you know the name and location of the EFB instance within this design. The following instructions assume the simple case where the EFB was used to instantiate a single I<sup>2</sup>C Slave core and will be replaced entirely by the Soft I<sup>2</sup>C Slave reference design. For more complicated EFB use, see the Special Cases section.

There are two common instantiations within a design implementation: IPexpress (.ipx), and HDL (.v or .vhd). See Figure 6.1. and Figure 6.2., respectively, for example instantiations (module names are user-defined and the filenames are for example only). Both instantiation types can be examined to verify:

- Primary or Secondary I<sup>2</sup>C port type

- I<sup>2</sup>C Slave address

- General Call Enable

- Wake-up Enable

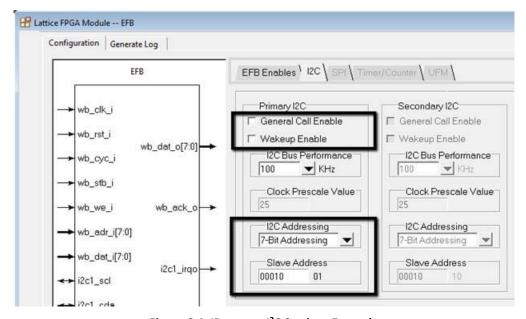

These values will be needed to instantiate and customize the Soft I<sup>2</sup>C Slave reference design. Other settings, such as I<sup>2</sup>C Bus Performance and Clock Prescale Value, are not required for a Slave I<sup>2</sup>C implementation.

Figure 6.1. IPexpress Instance Example

Figure 6.2. HDL Instance Example

The Primary/Secondary port type, Slave I2C address and other settings must be transferred for the Soft Core migration to be successful. These settings can be determined from either instantiation method.

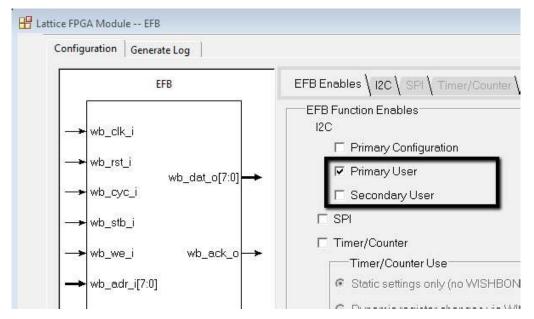

For IPexpress (.ipx) instances, double-click the .ipx filename to open the IPexpress EFB configuration GUI. Primary or Secondary port type can be determined from the EFB Enables tab, while other settings are found on the I2C tab. See Figure 6.3. and Figure 6.4.

Figure 6.3. IPexpress I<sup>2</sup>C Port Type Example

Figure 6.4. IPexpress I<sup>2</sup>C Settings Example

For Verilog (.v) instances, the active I2C port can be determined by inspecting the source file directly. Double-click the Verilog file to open the default editor and view the file. Find the defparam \*.EFB\_I2C1 (Primary) or \*.EFB\_I2C2 (Secondary) lines. In the example in Figure 6.4., the Primary port is Enabled. Also note the corresponding I2C Slave Address, Wakeup and General Call settings.

15

```

derharam minimar o'min nei - ninwammen

defparam EFBInst 0.12C2 WAKEUP = "DISABLED" ;

defparam EFBInst 0.12C2 GEN CALL = "DISABLED" ;

defparam EFBInst_0.I2C2_CLK_DIVIDER = 1 ;

defparam EFBInst 0.I2C2 BUS PERF = "100kHz"

defparam EFBInst_0.I2C2_SLAVE_ADDR = "0b0011001" ;

defparam EFBInst_0.I2C2_ADDRESSING = "7EIT" ;

defparam EFBInst O.EFB I2C2 = "DISABLED"

defparam EFBInst_0.I2C1_WAKEUP = "DISABLED"

defparam EFBInst 0.12C1 GEN CALL = "DISABLED"

0.I2C1 BUS PERF =

defparam EFBInst_0.I2C1_SLAVE_ADDR = "0b0001001

defparam EFBInst_0.I2C1_ADDRESSING = "7EIT" ;

defparam EFBInst_0.EFB_I2C1 = "ENABLED" ;

defparam EFBInst_0.EFB_WB_CLK_FREQ = "10.0

EFB EFBInst_0 (.WBCLKI(wb_clk_i), .WBRSII(wb_rst_i), .WBCYCI(wb_cyc_i),

WRSTRI(wh sth i) WRWFI(wh we i) WRADRI7(wh adr i[7])

```

Figure 6.5. Verilog Port and Address Example

For VHDL (.vhd) instances, the active I2C port can be determined by inspecting the source file directly. Double-click the VHDL file to open the default editor and view the file. Find the generic assignment EFB I2C1 (Primary) or EFB I2C2 (Secondary) lines. In the example in Figure 6.5., the Primary port is Enabled. Also note the corresponding I2C Slave Address, Wakeup and General Call settings.

```

SPI_INIK_IARDI=> LISADLED , SPI_SLAVE_MANUSMARE=> DISADLED ,

SPI_PHASE_ADJ=> "DISABLED", SPI_CLK_INV=> "DISABLED",

SPI LSB FIRST=> "DISABLED", SPI CLK DIVIDER=> 1, SPI MODE=> "MASTER",

EFB_SPI=> "DISABLED", I2C2_WAKEUP=> "DISABLED", I2C2_GEN_CALL=> "DISABLED",

I2C2_CLK_DIVIDER=> 1, I2C2_BUS_PERF=> "100kHz", I2C2_SLAVE_ADDR=> "0b0001001",

I2C2 ADDRESSING=> "7BIT", EFB_I2C2=> "DISABLED",

I2C1_WAKEUP=> "DISABLED",

174

I2C1_GEN_CALL=> "DISABLED"

I2C1 CLK DIVIDER=>

I2C1_BUS_PERF=> "100kHz",

12C1_SLAVE_ADDR=> "0b0001001

I2C1_ADDRESSING=> "7BIT", EFB_I2C1=> "ENABLED", EFB_WB_port map (WBCLKI=>wb_clk_1, WBRSI1=>wb_rst_1, W

LK FREQ=> "50.0")

WBRSII=>Wb_rst_1, WBCYCI=>Wb_cyc_i,

WBSTBI-Sub ath i WBWFI-sub wa i WBNDDI7-sub adr i(7)

```

Figure 6.6. VHDL Port and Address Example

#### 6.2. Soft Core installation

When migrating a design from Hard EFB block to Soft I2C Slave reference design, Lattice recommends taking advantage of the multiple implementation feature available in Lattice Diamond®. Source, Strategy and Preference files can be shared, reducing migration effort and potential errors compared to creating a new design from scratch. Whether modifying an existing implementation or creating a new implementation, the following guidelines should be followed.

- Remove the existing EFB from the implementation. Select the IPexpress (.ipx) or HDL (.v or .vhd) file, right-click and select Remove. The files remains on the hard drive, but are disassociated from the project.

- 2. Add the new design files to the implementation. Different files are required depending upon Primary or Secondary Port replacement. See Table 3.1 The Verilog file may be referenced from an arbitrary installation location, or copied to the Implementation 'source' directory. See Figure 6.6. The NGO file must be located in the active implementation directory.

Table 6.1. Primary and Secondary File Sets

| Component | Primary                | Secondary              |

|-----------|------------------------|------------------------|

| Тор       | Soft_EFB_I2C_top_Pri.v | Soft_EFB_I2C_top_Sec.v |

| Include   | i2c_config.v           | i2c_config.v           |

| Blackbox  | i2c_ip_pri.v           | i2c_ip_sec.v           |

| NGO       | i2c_ip_pri.ngo         | i2c_ip_sec.ngo         |

Figure 6.7. Primary Files Added to New Implementation Example

## 6.3. User Design Modifications

The Soft I<sup>2</sup>C Slave reference design must be modified to match the EFB settings. Additionally, the user Master Wishbone interface design may require modification to ensure new register settings are preserved during operation.

1. Modification to the Soft I2C Slave Reference Design is confined to the i2c\_config.v configuration file. These settings dictate the RESET state of these register bits. Open the i2c\_config.v file and modify the `defines to match the original EFB design:

| `define             | enable                    | disable |  |

|---------------------|---------------------------|---------|--|

| WAKEUP_INIT         | 1'b1                      | 1'b0    |  |

| GEN_CALL_INIT       | 1'b1                      | 1'b0    |  |

| IPex_I2C_slave_addr | See Customization section |         |  |

| SDA_DEL_FACTOR      | See Customization section |         |  |

| SDA_DEL_INIT        | See Customization section |         |  |

- 2. The instantiation of the Soft I2C Slave reference design must be modified so that module names match. In the instantiating code, change the module name to "Soft\_EFB\_I2C\_top". For example:

- Soft\_EFB\_I2C\_top U1 (.wb\_clk\_i (CLK), ... );

- It should not be necessary to modify the instantiation port list.

- 3. It may be necessary to modify the WISHBONE master controller, so that any write to the I2C Control register (I2C\_1\_CR / I2C\_2\_CR) or Clock Prescale 1 register (I2C\_1\_BR1 / I2C\_2\_BR1) reinforce the GCEN, WKUPEN, SDA\_DEL\_SEL[1:0] and SDA\_DEL\_FACTOR[3:0] settings included in i2c\_config.v. It should not be necessary to modify the WISHBONE Master controller further.

© 2014-2019 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 7. Customization

### 7.1. SDA\_DEL calculation

In the Soft Core implementation, the SDA Tdel value is dependent upon the WISHBONE clock period, tWB. This is a change from the hard core. Calculate SDA DEL FACTOR and SDA DEL INIT using the following information:

The initial value of SDA\_DEL can be specified a combination of `define SDA\_DEL\_INIT and `define SDA\_DEL\_FACTOR. SDA\_DEL\_SEL is a 2-bit value with range 0-3 decimal. SDA\_DEL\_SEL set in the I2C Control register. SDA\_DEL\_FACTOR is a 4-bit value with range 0-15 decimal. SDA\_DEL\_ FACTOR set in the I2C Clock Prescale 1 register. These values determine the number of tWB periods after the falling edge of SCL that SDA is updated, based on the table below:

| SDA_DEL                               | tDEL, (tWB periods)                |

|---------------------------------------|------------------------------------|

| 00 4xSDA_DEL_FACTOR + 2.5 +/- 0.5 tWB |                                    |

| 01                                    | 2xSDA_DEL_FACTOR + 2.5 +/- 0.5 tWB |

| 10                                    | 1xSDA_DEL_FACTOR + 2.5 +/- 0.5 tWB |

| 11                                    | 0 +/- 0.5 tWB                      |

| Example 1: | fWB = 25Mhz ( tWB = 40 ns): If SDA_DEL_FACTOR = 5 and SDA_DEL = "10", |

|------------|-----------------------------------------------------------------------|

|            | then tDEL = (1x5+2.5 +/- 0.5) x 40ns = 300ns +/- 20ns                 |

| Example 2: | fWB = 10Mhz (tWB = 100 ns): If SDA_DEL_FACTOR = 1 and SDA_DEL = "10", |

|            | then tDEL = (1x1+2.5 +/- 0.5) x 100ns = 350ns +/- 50ns                |

#### 7.2. I<sup>2</sup>C Address

Setting the I2C Address examples:

| I <sup>2</sup> C Address | IPex_I2C_slave_addr | Comment                         |

|--------------------------|---------------------|---------------------------------|

| 0x41 (7-bit)             | 10'b111_100_0001    | XO2 Hard Primary port default   |

| 0x42 (7-bit)             | 10'b111_100_0010    | XO2 Hard Secondary port default |

| 0x75 (7-bit)             | 10'b111_111_0101    | Primary address example         |

| 0x179 (10-bit)           | 10'b010_111_1001    | Primary address example         |

| 0x2C2 (10-bit)           | 10'b101_100_0010    | Secondary address example       |

# 8. Special Cases

#### 8.1. Concurrent EFB use

Special care is required when instantiating this reference design concurrent with the MachXO2 EFB. This would occur when other aspects of the EFB are used in the design, for example User Flash Memory, User SPI, or even User I<sup>2</sup>C (see note below). First, the WISHBONE port must be multiplexed. Second, I<sup>2</sup>C port pins must be made available.

To multiplex the WISHBONE bus, a simple 2:1 WISHBONE mux (1 Master port, 2 slave ports) is provided with this reference design and may be instantiated as needed.

To free the  $I^2C$  port pins, the EFB module must be generated (or regenerated) using IPexpress to disable the Primary and/or secondary  $I^2C$  port(s) as required. This allows the  $I^2C$  port device pins to be recovered as GPIO and reassigned to the Reference Design  $I^2C$  port(s).

Note: If the Hardened I<sup>2</sup>C port is used, be sure to set CKSDIS = '1' to disable Clock Stretching. This feature is no longer supported by the hardened logic. Due to limitations in the provided WISHBONE multiplexor, the Primary Hardened I<sup>2</sup>C block and the Primary Reference Design cannot be used together as they share the same address space. The same is true for the Secondary.

## 8.2. Multiple I<sup>2</sup>C slaves

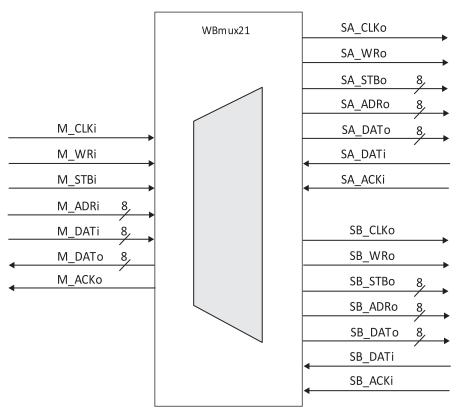

This Reference Design can be instantiated multiple times as required. The WISHBONE ports must be multiplexed. For the simple case instantiating two copies of the Reference Design (a Primary and Secondary), the provided 2:1 WISHBONE mux, WBmux21.v, can be utilized. For three or more instantiations, the user must provide an appropriate multiplexor.

#### 8.3. Wishbone Mux

This Reference Design includes a 2 port WISHBONE multiplexor, WBmux21.v.

Figure 8.1. WBmux21.v BLOCK DIAGRAM

Connect the WISHBONE bus master to the master port, and the 2 slave WISHBONE ports accordingly. The multiplexor passes through the Master output signals to both Slaves. The circuit assumes only one Slave will respond. The Slave ACK signals are OR'd together and passed back to the Master. The DATo port of the ACK'ing slave is routed to the Master DATi port.

19

# 9. Resource Utilization – Soft EFB I<sup>2</sup>C

| Family               | Language                              | Speed Grade | Utilization | fmax (MHz) | I/Os |

|----------------------|---------------------------------------|-------------|-------------|------------|------|

| MachXO2 <sup>1</sup> | NGO-LSE (Lattice<br>Synthesis Engine) | <b>-</b> 5  | 421 LUTs    | >50        | 34   |

|                      | NGO-Syn<br>(Synplify Pro*)            | <b>-</b> 5  | 421 LUTs    | >50        | 34   |

**Note:** Performance and utilization characteristics are generated using LCMXO2-1200HC-5MG132C with Lattice Diamond 3.3 design software.

# References

- UM10204 "I2C-bus specification and user manual" Rev. 4, 13 February 2012, NXP Semiconductor

- "THE I2C-BUS SPECIFICATION", VERSION 2.1 JANUARY 2000, Doc. No. 9398 393 40011, Phillips Semiconductor

- Using User Flash Memory and Hardened Control Functions in MachXO2 Devices Reference Guide (FPGA-TN-02163)

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

# **Revision History**

#### Revision 1.2, November 2019

| Section     | Change Summary                                        |  |

|-------------|-------------------------------------------------------|--|

| All         | Changed document number from RD1186 to FPGA-RD-02092. |  |

|             | Updated document template.                            |  |

| Disclaimers | Added this section.                                   |  |

#### Revision 1.1, November 2014

| Section                         | Change Summary                         |

|---------------------------------|----------------------------------------|

| Resource Utilization – Soft EFB | Added support to Diamond 3.3.          |

| I <sup>2</sup> C                | Added support to Synplify Pro and LSE. |

#### Revision 1.0, September 2013

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

www.latticesemi.com