# I<sup>2</sup>C to SPI Bridge

# **Reference Design**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

#### **Contents**

| 1. Intr   | roduction                                        | 5  |

|-----------|--------------------------------------------------|----|

| 2. Fea    | ıtures                                           | 5  |

| 3. Syst   | tem Block Diagram                                | 5  |

| 4. Sign   | nal Description                                  | 6  |

| 5. Fun    | nctional Description                             |    |

| 5.1.      | Slave Address                                    |    |

| 5.2.      | Write to data buffer                             |    |

| 5.3.      | SPI Read and Write                               |    |

| 5.4.      | Read from Buffer                                 |    |

| 5.5.      | Table for Function IDs                           |    |

| 5.6.      | Configure SPI interface –Function ID F0h         |    |

| 5.7.      | Clear Interrupt-Function ID F1h                  |    |

| 5.8.      | Idle Mode- Function ID F2h                       |    |

| 5.9.      | GPIO Enable –Function ID F6h                     |    |

| 5.10.     | GPIO Configuration –Function ID F7h              |    |

| 5.11.     | GPIO Write-Function ID F4h                       |    |

| 5.12.     | GPIO Read-Function ID F5h                        |    |

| 5.13.     | SPI Interface                                    |    |

| 5.14.     | Initialization Conditions                        |    |

|           | ning Diagram                                     |    |

| 6.1.      | Write Operation                                  |    |

| 6.2.      | Read Operation                                   |    |

|           | nulation Waveforms                               |    |

| -         | eration Sequence and Usage Example               |    |

|           | plementation                                     |    |

|           | Ces                                              |    |

|           | al Support Assistance<br>History                 |    |

| Kevision  | 113COT y                                         |    |

| Figure 3. | <b>ES</b> 1. System Block Diagram                | 5  |

|           | .1. Slave Address                                |    |

| _         | .2. Write to Data Buffer                         |    |

| _         | .3. Function ID                                  |    |

| _         | .4. I <sup>2</sup> C-Bus Message-Write to Buffer |    |

| _         | .5. SPI Message                                  |    |

| _         | .6. Read from Buffer                             |    |

| Figure 5. | .7. Clear Interrupt                              | 9  |

| Figure 5. | .8. Idle Mode                                    | 9  |

| Figure 5. | .9. GPIO Read                                    | 10 |

| Figure 5. | .10. GPIO Write                                  | 11 |

| Figure 5. | .11. GPIO Read                                   | 11 |

# **Tables**

| Table 4.1. Signal Descriptions                     | 6  |

|----------------------------------------------------|----|

| Table 5.1. Function IDs and their Functions        |    |

| Table 5.2. Configure SPI Interface                 |    |

| Table 5.3. Configure SPI Interface Bit Description |    |

| Table 5.4. GPIO Configuration Bit Allocation       |    |

| Table 5.5. GPIO Configuration Bit Description      | 10 |

| Table 9.1. Performance and Resource Utilization    |    |

5

## 1. Introduction

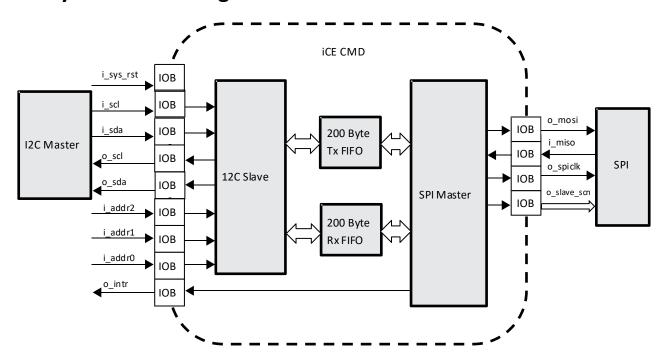

I<sup>2</sup>C and SPI are the two widely used bus protocols in today's embedded systems. The I<sup>2</sup>C bus has a minimum pin count requirement and therefore a smaller footprint on the board. The SPI bus provides a synchronized serial link with performance in MHz range. As embedded systems are required to support an increasing number of protocols and interfaces, bridge designs targeting popular protocols provide solutions to reduce development time and cost. This reference design implements an I<sup>2</sup>C slave to SPI master bridge. It serves as an interface between the standard I<sup>2</sup>C bus of a microcontroller and an SPI bus. This allows the microcontroller to communicate directly with the SPI bus through its I<sup>2</sup>C bus. This bridge extends the available SPI ports for the application processor.

The design is implemented in mixed VHDL and Verilog language. The Lattice iCEcube2™ Place and Route tool, integrated with the Synopsys Synplify Pro® and LSE (Lattice Synthesis Engine) synthesis tools is used for the implementation of the design. The design can be targeted to other iCE40™ FPGA product family devices.

### 2. Features

- I<sup>2</sup>C bus slave interface operating up to 400 kHz

- SPI Master operating up to 1.8 Mbit/s

- 200 byte data buffer

- Up to four slave select outputs

- Up to four programmable I/O pins

- Operating Voltage: 1.8 V to 3.3 V

- Low power mode

- Active low interrupt output

# 3. System Block Diagram

Figure 3.1. System Block Diagram

# 4. Signal Description

**Table 4.1. Signal Descriptions**

| Signal       | Width | Туре   | Description                                                       |

|--------------|-------|--------|-------------------------------------------------------------------|

| i_sys_clk    | 1     | Input  | System Clock                                                      |

| i_sys_rst    | 1     | Input  | Active High Asynchronous reset                                    |

| i_scl        | 1     | Input  | SCL input to I <sup>2</sup> C Slave from I <sup>2</sup> C Master  |

| i_sda        | 1     | Input  | SDA input to I <sup>2</sup> C Slave from I <sup>2</sup> C Master  |

| o_sda        | 1     | Output | SDA output from I <sup>2</sup> C Slave to I <sup>2</sup> C Master |

| o_scl        | 1     | Output | SCL output from I <sup>2</sup> C Slave to I <sup>2</sup> C Master |

| o_scl_tri_en | 1     | Output | Tristate Enable for I <sup>2</sup> C SCL                          |

| o_sda_tri_en | 1     | Output | Tristate Enable for I <sup>2</sup> C SDA                          |

| i_addr2      | 1     | Input  | Address bit for programming I <sup>2</sup> C Slave Address        |

| i_addr1      | 1     | Input  | Address bit for programming I <sup>2</sup> C Slave Address        |

| i_addr0      | 1     | Input  | Address bit for programming I <sup>2</sup> C Slave Address        |

| o_mosi       | 1     | Output | Serial output from SPI Master                                     |

| i_miso       | 1     | Input  | Serial Input to SPI Master                                        |

| o_slave_csn  | 1     | Output | Slave select from SPI Master                                      |

| o_spiclk     | 1     | Output | Serial Clock generated by SPI Master                              |

| o_intr       | 1     | Output | Output Interrupt                                                  |

# 5. Functional Description

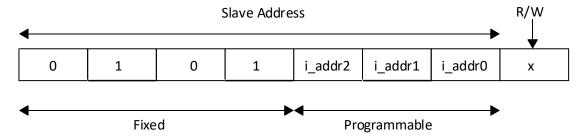

#### 5.1. Slave Address

The first seven bits of the first byte sent after a START condition defines the slave address of the device being accessed on the bus. The eighth bit determines the direction of the message. A '0' in the least significant position of the first byte means that the master will write information to a selected slave. A '1' in this position means that the master will read information from the slave. When an address is sent, each device in a system compares the first seven bits after the START condition with its address. If they match, the device considers itself addressed by the master as a slave-receiver or slave-transmitter, depending on the R/W bit.

A slave address is comprised of a fixed and a programmable part. The programmable part of the slave address enables the maximum possible number of such devices to be connected to the I<sup>2</sup>C-bus. Since this has three programmable address bits (defined by the i\_addr2, i\_addr1, and i\_addr0 pins), it is possible to have eight of these devices on the same bus.

The state of the i\_addr1, i\_addr1, and i\_addr0 pins are latched at reset. Changes made after reset will not alter the address.

Figure 5.1. Slave Address

© 2015-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

7

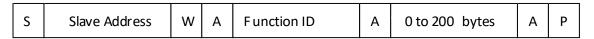

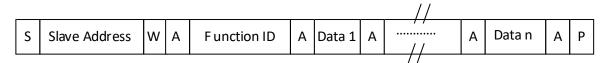

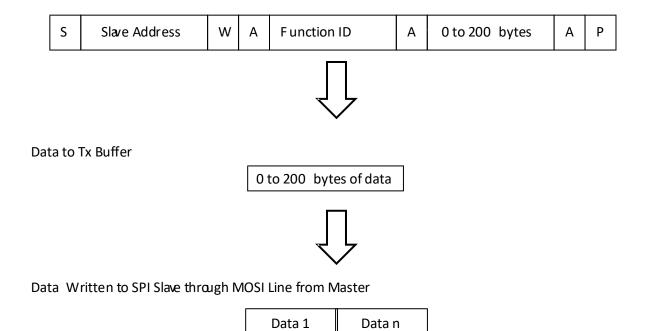

#### 5.2. Write to data buffer

All communications occur through the data buffer. The data buffer is 200 bytes deep. A message begins with the slave address, followed by the Function ID. Depending upon the Function ID, zero to 200 data bytes can follow.

$I^2C$  slave will place the data received into a buffer and continue loading the buffer until a STOP condition is received. After the STOP condition is detected, further communications will not be acknowledged until the function designated by the Function ID has been completed.

Figure 5.2. Write to Data Buffer

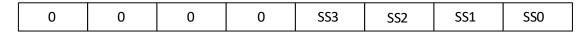

#### 5.3. SPI Read and Write

Data in the buffer will be sent to the SPI port if the Function ID is 01h to 0Fh. The Function ID contains the Slave Select (SS) to be used for the transmission on the SPI port. There are four Slave Selects that can be used, with each SS being selected by one of the bits in the Function ID. There is no restriction on the number or combination of Slave Selects that can be enabled for an SPI message. If more than one SSn pin is enabled at one time, the user should be aware of possible contention on the data outputs of the SPI slave devices.

Figure 5.3. Function ID

The data on the SPI port will contain the same information as the I<sup>2</sup>C-bus data, but without the slave address and Function ID. For example, if the message shown in Figure 5.4 is transmitted on the I<sup>2</sup>C-bus, the SPI bus will send the message shown in Figure 5.5.

Figure 5.4. I<sup>2</sup>C-Bus Message-Write to Buffer

Figure 5.5. SPI Message

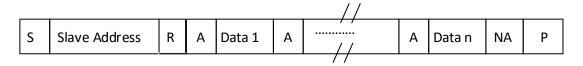

As the data is transmitted from the MOSI pin, SPI Master also read from the MISO pin and saved in the data buffer. Therefore, the old data in the buffer is overwritten. The data in the buffer can then be read back. If the data from the SPI bus needs to be returned to the I<sup>2</sup>C-bus master, the process must be completed by reading the data buffer. I<sup>2</sup>C Master can read back the data.

© 2015-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal

#### 5.4. Read from Buffer

Figure 5.6. Read from Buffer

#### 5.5. Table for Function IDs

Table 5.1. Function IDs and their Functions

| Function ID | Function                                                                               |  |  |  |

|-------------|----------------------------------------------------------------------------------------|--|--|--|

| 01-0Fh      | Write to data buffer (Function ID specifies to which SPI slave data should be written) |  |  |  |

| F0h         | Configure SPI interface                                                                |  |  |  |

| F1h         | Clear the interrupt                                                                    |  |  |  |

| F2h         | Idle mode                                                                              |  |  |  |

| F4h         | GPIO Write                                                                             |  |  |  |

| F5h         | GPIO Read                                                                              |  |  |  |

| F6h         | GPIO Enable                                                                            |  |  |  |

| F7h         | GPIO Configuration                                                                     |  |  |  |

## 5.6. Configure SPI interface -Function ID F0h

The SPI hardware operating mode, data direction, and frequency can be changed by sending a 'Configure SPI Interface' command to the I<sup>2</sup>C-bus. After slave address is transmitted on the bus, the Configure SPI Interface Function ID (F0h) is sent followed by a byte which will define the SPI communications.

Table 5.2 shows Function ID F0h bit allocation. It shows the procedure for configuring SPI interface. Table 5.3 shows Function ID F0h bit description.

**Table 5.2. Configure SPI Interface**

| Bit    | 7 | 6 | 5     | 4 | 3     | 2     | 1  | 0  |

|--------|---|---|-------|---|-------|-------|----|----|

| Symbol | Х | х | Order | х | Mode1 | Mode0 | F1 | F0 |

| Reset  | х | х | 0     | х | 0     | 0     | 0  | 0  |

**Table 5.3. Configure SPI Interface Bit Description**

| Bit | Symbol      | Description              |

|-----|-------------|--------------------------|

| 7:6 | -           | Reserved                 |

| 5   | Order       | 0'-MSB is sent out first |

|     |             | 1'-LSB is sent out first |

| 4   | -           | Reserved                 |

| 3:2 | Mode1:Mode0 | Mode Selection           |

|     |             | 01-CPOL-0,CPHA-1         |

|     |             | 10-CPOL-1,CPHA-0         |

|     |             | 11-CPOL-1,CPHA-1         |

| 1:0 | F1:F0       | SPI clock Rate           |

|     |             | SC18IS602/602B:          |

|     |             | 00-1843 khz              |

|     |             | 01-461 khz               |

|     |             | 10-115 khz               |

|     |             | 11-58 khz                |

|     |             | SC18IS603:               |

|     |             | 00-fosc/4                |

|     |             | 01-fosc/16               |

|     |             | 10-fosc/64               |

|     |             | 11-fosc/128              |

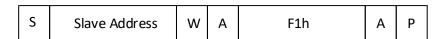

### 5.7. Clear Interrupt-Function ID F1h

An interrupt is generated after completion of every SPI transaction. This interrupt can be cleared (INT pin HIGH) by sending a 'Clear Interrupt' command.

Figure 5.7. Clear Interrupt

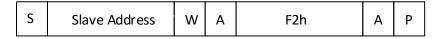

#### 5.8. Idle Mode-Function ID F2h

A low-power mode may be entered by sending the 'Idle Mode' command. The Idle mode will be exited when its I<sup>2</sup>C-bus address is detected.

Figure 5.8. Idle Mode

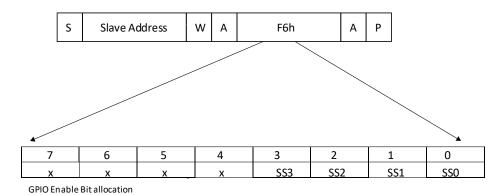

#### 5.9. GPIO Enable –Function ID F6h

At reset, the Slave Select pins (SS0, SS1, SS2 and SS3) are configured to be used as slave select outputs. If these pins are not required for the SPI functions, they can be used as GPIO after they are enabled as GPIO. Any combination of pins may be configured to function as GPIO or Slave Selects. After the GPIO Enable function is sent, the ports defined as GPIO will be configured as quasi-bidirectional. The data byte following the F6h command byte will determine which pins can be used as GPIO. A logic 1 will enable the pin as a GPIO, while a logic 0 will disable GPIO control.

Figure 5.9. GPIO Read

### 5.10. GPIO Configuration – Function ID F7h

The pins defined as GPIO may be configured by software to one of four types on a pin-by-pin basis. These are: quasi-bidirectional, push-pull, open-drain, and input-only. Two bits select the output type for each port pin. The SSn pins defined as GPIO, for example SS0.0 and SS0.1, may be configured by software to one of four types. These are: Bidirectional, Input, Output- pullup, Output- pulldown. Two configuration bits in GPIO Configuration register for each pin select the type for each pin.

**Table 5.4. GPIO Configuration Bit Allocation**

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SS3.1 | SS3.0 | SS2.1 | SS2.0 | SS1.1 | SS1.0 | SS0.1 | SS0.0 |

**Table 5.5. GPIO Configuration Bit Description**

| Bit | Symbol | Description                  |

|-----|--------|------------------------------|

| 7   | SS3.1  | SS3[1:0]-00:Bidirectional    |

| 6   | SS3.0  | SS3[1:0]-01:Input            |

|     |        | SS3[1:0]-10:Output-pullup    |

|     |        | SS3[1:0]-11:Output:pulldown  |

| 5   | SS2.1  | SS2[1:0]-00: Bidirectional   |

| 4   | SS2.0  | SS2[1:0]-01: Input           |

|     |        | SS2[1:0]-10: Output-pullup   |

|     |        | SS2[1:0]-11: Output-pulldown |

| 3   | SS1.1  | SS1[1:0]-00: Bidirectional   |

|     | SS1.0  | SS1[1:0]-01: Input           |

|     |        | SS1[1:0]-10: Output-pullup   |

|     |        | SS1[1:0]-11: Output-pulldown |

| 2   | SS0.1  | SS0[1:0]-00:Bidirectional    |

|     | SS0.0  | SS0[1:0]-01:Input            |

|     |        | SS0[1:0]-10:Output-pullup    |

| 1   |        | SS0[1:0]-11:Output-pulldown  |

© 2015-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

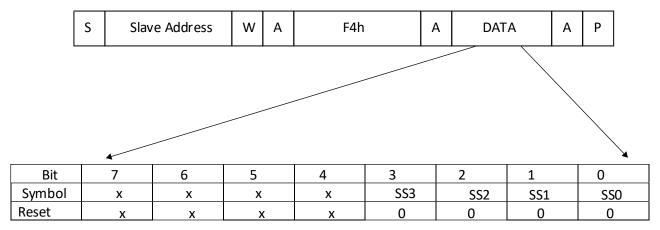

#### 5.11. GPIO Write-Function ID F4h

The state of the pins defined as GPIO may be changed using the Port Write function. The data byte following the F4h command will determine the state of SS3, SS2, SS1, and SS0, if they are configured as GPIO. The Port Enable function will define if these pins are used as SPI Slave Selects or if they are GPIO.

GPIO Write Bit Allocation

Figure 5.10. GPIO Write

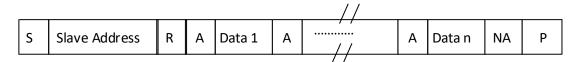

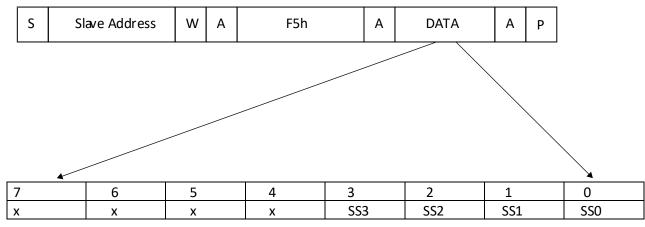

#### 5.12. GPIO Read-Function ID F5h

The state of the pins defined as GPIO may be read into the data buffer using the GPIO Read function. Note that this function does not return the value of the GPIO. To receive the GPIO contents, a one-byte Read Buffer command would be required. The value of the Read Buffer command will return the following byte. Data for pins not defined as GPIO are undefined. A GPIO Read is always performed to update the GPIO data in the buffer. The buffer is undefined after the GPIO data is read back from the buffer. Therefore, reading data from the GPIO always requires a two-message sequence (GPIO Read, followed by Read Buffer).

The data byte following read buffer command is the GPIO read data from read buffer.

GPIO Read bit allocation

Figure 5.11. GPIO Read

### 5.13. SPI Interface

The SPI interface can support Mode 0 through Mode 3 of the SPI specification and can operate up to 1.8 Mbit/s. The SPI interface uses at least four pins: SPICLK, MOSI, MISO, and Slave Select (SSn).

SSn are the slave select pins. In a typical configuration, an SPI master selects one SPI device as the current slave. There are actually four SSn pins (SS0, SS1, SS2 and SS3) to allow the bus to communicate with multiple SPI devices.

The Master generates the SPICLK (SPI clock) signal in order to send and receive data. The SCLK, MOSI, and MISO are typically tied together between two or more SPI devices. Data flows from the master to slave on the MOSI pin and the data flows from slave to master on the MISO pin.

#### 5.14. Initialization Conditions

An asynchronous active high reset signal assertion is necessary to initialize the Controller to proper operating state.

# Timing Diagram

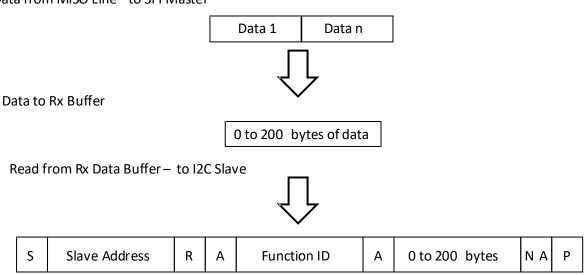

### 6.1. Write Operation

Write to Data Buffer - I2C Slave to Tx Buffer

Figure 6.1. Timing Diagram - Write Operation

© 2015-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 6.2. Read Operation

Data from MISO Line -to SPI Master

Figure 6.2. Timing Diagram - Read Operation

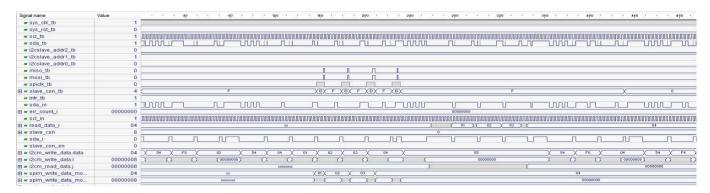

## 7. Simulation Waveforms

Figure 7.1. Simulation Waveforms

# 8. Operation Sequence and Usage Example

The following example describes a typical sequence of events required to read the contents of an SPI-based EEPROM. This example assumes that the Controller is configured to respond to address 50h. A START condition is shown as 'S', while a STOP condition is 'P'. The data is presented in hexadecimal format.

- 1. The first message is used to configure the SPI port for mode and frequency. ST,50,F0,02,SP SPI frequency 115 kHz using Mode 0

- 2. An SPI EEPROM first requires that a Write Enable command be sent before data can be written. ST,50,04,06,SP EEPROM write enable using SS2, assuming the Write Enable is 06h

- 3. Clear the interrupt. This is not required if using a polling method rather than interrupts. ST,50,F1,SP Clear interrupt

- 4. Write the 8 data bytes. The first byte (Function ID) tells which Slave Select output to use. This example uses SS2 (shown as 04h). The first byte sent to the EEPROM is normally 02h for the EEPROM write command. The next one or two bytes represent the sub address in the EEPROM. In this example, a twobyte sub address is used. Bytes 00 and 30 would cause the EEPROM to write to sub address 0030h. The next eight bytes are the eight data bytes that will be written to sub addresses 0030h through 0037h. ST,50,04,02,00,30,01,02,03,04,05,06,07,08,SP Write 8 bytes using SS2

- 5. When an interrupt occurs, do a Clear Interrupt or wait until the slave responds to its I<sup>2</sup>C-bus address. ST,50,F1,SP Clear interrupt

- 6. Read the 8 bytes from the EEPROM. Note that we are writing a command, even though we are going to perform a read from the SPI port. The Function ID is again 04h, indicating that we are going to use SS2. The EEPROM requires that we send a 03h for a read, followed by the sub address you would like to read. We are going to read back the same data previously written, so this means that the sub address should be 0030h. We would like to read back 8 bytes so we can send eight bytes of FFh to tell the Master to send eight more bytes on MOSI. While it is sending these eight data bytes, it is also reading the MISO pin and saving the data in the buffer.

# 9. Implementation

This design is implemented in mixed VHDL and Verilog language. When using this design in a different device, density, speed or grade, performance and utilization may vary.

**Table 9.1. Performance and Resource Utilization**

| Device Family      | Language | Synthesis Tool | Utilization<br>(LUTs) | f <sub>MAX</sub> (MHz) | I/Os | Architecture<br>Resources |

|--------------------|----------|----------------|-----------------------|------------------------|------|---------------------------|

| iCE40 <sup>1</sup> | VHDL and | LSE            | 715                   | >50                    | 25   | (127/160) PLBs            |

|                    | Verilog  | Syn Pro        | 768                   | >50                    | 25   | (122/160) PLBs            |

#### Note:

Performance and utilization characteristics are generated using iCE40LP1K-CM121 with iCEcube2 2014.12 design software and LSE support.

© 2015-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# **References**

• iCE40 LP/HX Family Data Sheet (FPGA-DS-02029)

# **Technical Support Assistance**

Submit a technical support case through www.latticesemi.com/techsupport.

# **Revision History**

### Revision 1.2, February 2020

| Section     | Change Summary                                        |  |  |

|-------------|-------------------------------------------------------|--|--|

| All         | Changed document number from RD1172 to FPGA-RD-02157. |  |  |

|             | Updated document template.                            |  |  |

| Disclaimers | Added this section.                                   |  |  |

#### Revision 1.1, February 2015

| Section                      | Change Summary                                                                     |  |  |  |

|------------------------------|------------------------------------------------------------------------------------|--|--|--|

| Implementation               | Updated Implementation section. Updated Table 9.1, Performance and Resource Utiliz |  |  |  |

|                              | Added LSE support.                                                                 |  |  |  |

| References                   | Updated References section.                                                        |  |  |  |

| Technical Support Assistance | Updated Technical Support Assistance information.                                  |  |  |  |

#### Revision 1.0, April 2013

| Section | Change Summary   |

|---------|------------------|

| All     | Initial release. |

www.latticesemi.com