2013 年 12 月 テクニカルノート TN1206

## はじめに

ソフトエラーは、高エネルギー荷電粒子によって、電子回路内のメモリセルに格納されたチャージが変化して発生することがあります。本現象は最初に DRAM の問題として現出し、高信頼性アプリケーションの大容量メモリシステムではエラー検出と訂正が必要になります。デバイスジオメトリは縮小を続けているため、システムによっては SRAM 内でのメモリエラーの可能性がかなり高くなっています。設計者は様々な手法を使用して、システム動作に与えるメモリエラーの影響を抑えようとしています。

SRAM ベースの PLD は、ロジック・コンフィグレーション・データを SRAM セルに格納します。PLD 内部の SRAM の数と規模が増加しているため、メモリエラーによってプログラムされたシステムの論理動作が変化 する可能性も増しています。この問題は多数の手法で対策されていますが、その多くはユーザが設計のロジック内に実装した IP(Intellectual Property)コアを利用するため、貴重なリソースを使用し、設計の性能に影響を与える可能性があります。 MachXO2TM デバイスはハードウェア実装された SED 回路を持つため、それを SRAM エラーの検出に使用でき、訂正も可能です。

本書では、ラティスセミコンダクターが MachXO2 PLD に採用した、ハードウェアベースの SED 手法について説明します。

# SED の概要

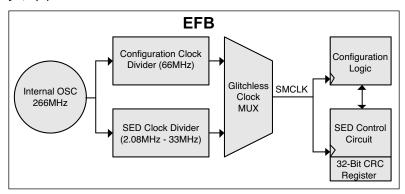

MachXO2 デバイスの SED ハードウェアは、PLD のコンフィグレーション・メモリへのアクセスポイント、制御回路、及び対象ビットストリームの CRC を格納する 32 ビットレジスタで構成されます (図 1-1 参照)。 SED ハードウェアは、PLD のコンフィグレーション・メモリからシリアルデータをリードし、CRC を計算します。そのリードされたデータ、及び計算された CRC には、EBR メモリまたは RAM として使用される PFU が含まれません。その後、計算された CRC は 32 ビットレジスタに格納された CRC の期待値と比較されます。 CRC 値が一致した場合はコンフィグレーション・メモリが破損していないことが示され、値が異なる場合はエラー信号が生成されます。

### 図 1-1. システムブロック図

計算された CRC は、特定の設計に対する特定のコンフィグレーション・メモリの内容に基づいたものになります。その結果、期待される CRC 値は、設計が実装されて配線されるまで指定できません。Lattice Diamond ™または ispLEVER® ビットストリーム生成ソフトウェアは、実装及び配線された設計のコンフィグレーションを解析し、ビットストリーム生成時に 32 ビット SED CRC レジスタの内容を更新します。

以下の項では、MachXO2 SED の実装とフローについて説明します。

## SED の制約

SED を実行できるのは、デバイスのロジックが安定状態に保たれ、誤ったエラー表示が防止される場合に限られます。また、クロック周波数が 33.33MHz を超える場合の SED には対応していません。

SED 回路のクロック (SMCLK) はコンフィグレーション回路と共用されています。そのため、SED モジュールは、EFB 機能の幾つかの動作に対して以下の様な関連性があります。

- ·. SED 回路が動作時に EFB やコンフィグレーション・ロジックがアクセスされると、

- その時点の SED サイクルは強制終了します

- ・SED 回路が強制終了されると、EFB やコンフィグレーション・ロジックがアクセスできるようになるまで SMCLK 2 周期分の遅延があります。これは SMCLK が SED クロックからコンフィグレーション・クロックドメインに切り替えられるために要する期間です。"2 SMCLK" 周期とは低速のSED クロックで定義されます。

- ・SED 回路が強制終了されると、SEDDONE および SEDERR は Low のままに保持され、SEDINPROG は High から Low にリセットされます。

- EFB やコンフィグレーション・ロジックのアクセスで SED 動作に関連性があるのは次の通りです:

- ・JTAG ポートまたは WISHBONE インターフェイスから与えられる以下のコマンド

- LSC\_REFRESH

- ISC\_ENABLE

- ISC ENABLE X

- 全 IEEE 1532 命令

- ISC DISABLE

- プライマリ [2C コンフィグレーション・ロジックのスレーブアドレスが一致

- · SPI コンフィグレーション・ロジックのチップセレクトがアサートされる

- ・. PROGRAMn ピンを検出するロジックは最低 6 SMCLK 周期以上の Low 期間を必要とします。SED 回路 が動作中は 6 SMCLK 周期は SED クロックで定義されます。

# SED の動作モード

MachXO2 デバイスの SED 動作には 2 つのモードがあります。

- ・標準動作モードでは、SEDの実行開始タイミングやエラー検出動作のテストをデザインから制御できます

- ・ワンショット動作モードは、デバイスのコンフィグレーション後に SED を1回実行し、コンフィグレーションが目的のコンフィグレーションと一致していることを確認するために使用されます

どちらの動作でも、EBR 及び RAM メモリを除く、コンフィグレーション SRAM 内の全ビットの CRC がチェックされます。標準モード動作は SEDFA プリミティブを使用して起動されるのに対して、ワンショット動作は SEDFB プリミティブを使用して起動されます。これらのプリミティブについては、次の項で説明します。

SED 動作中にエラーが検出された場合、ユーザは 2 つの訂正アクションのいずれかを選択できます。1 つは ″何もしない ″です。もう 1 つは、PROGRAMN ピンを Low にすることで、オンデマンドのユーザ再コンフィグレーションを開始します。これは別のデバイスから、または図 16-4 に示す MachXO2 デバイスの出力から 行います。

PROGRAMn ピンを検出するロジックは最低 6 SMCLK 周期以上の Low 期間を必要とします。SED 回路が動作中は 6 SMCLK 周期は SED クロックで定義されます。エラー検出がアクティブにされると、PROGRAMn の Low 期間は SEDCLK で 6 周期の定義になります。これはアクティブは SMCLK は SEDCLK に切り替えられる

ためです。これは SMCLK が最速で動作している通常動作時とは異なる振る舞いです。デバイス起動後、SED 機能ブロックは新規コンフィグレーション設定に基づいて動作します。

#### 標準 SED

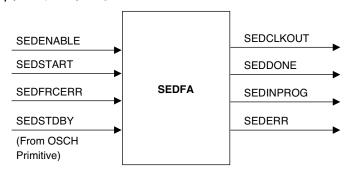

標準 SED 動作は、図 1-2 に示す SEDFA プリミティブを実現することで使用できます。プリミティブのポート定義を表 1-1 に示します。各ポートの詳細については、本書の「ポート説明」の項を参照してください。(日本語注<sup>1</sup>)

## 図 1-2. SEDFA プリミティブ・シンボル1

### ワンショット SED

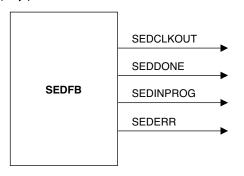

ワンショット SED 動作は、図 1-3 に示す SEDFB プリミティブを実現することで使用できます。SEDFB プリミティブのポート定義を表 1-1 に示します。各ポートの詳細については、本書の「ポート説明」の項を参照してください。(日本語注<sup>2</sup>)

## 図 1-3. SEDFB プリミティブ・シンボル

1-3 TN1206J 01.9

<sup>1.</sup> 日本語注:英語版オリジナルにある R1 デバイスの記述は省略

<sup>2.</sup> 日本語注:英語版オリジナルにある R1 デバイスの記述は省略

# 信号説明

## 表 1-1. SEDFA プリミティブのポート定義

| 信号名       | 方向 | アクティブ    | 記述                          |

|-----------|----|----------|-----------------------------|

| SEDENABLE | 入力 | High     | SRAM CRC イネーブル              |

| SEDSTART  | 入力 | 立ち上がりエッジ | SRAM CRC サイクルを開始            |

| SEDFRCERR | 入力 | 立ち上がりエッジ | SRAM CRC エラーフラグを強制的にアサート    |

| SEDSTDBY  | 入力 | High     | スタンバイモード時に SRAM CRC をディセーブル |

| SEDCLKOUT | 出力 | N/A      | 出力クロック                      |

| SEDDONE   | 出力 | High     | SRAM CRC サイクル完了             |

| SEDINPROG | 出力 | High     | SRAM CRC サイクル実行中            |

| SEDERR    | 出力 | High     | SRAM CRC エラーフラグ             |

# SED のクロックドライバ

SEDFA または SEDFB プリミティブ使用時、SED 回路は MachXO2 内部オシレータでドライブされます。対応 する最高周波数は 33.25MHz です。

MachXO2 内部オシレータは、コンフィグレーション、SED、内部ユーザクロックなど、デバイス内のいくつかの機能で使用できます。オシレータ出力の周波数は、こうした用途ごとに異なる設定にできます。SED クロックで使用可能な設定を、次の表に示します。SED 使用時、内部オシレータ周波数は SED\_CLK\_FREQ パラメータで指定されます。

表 1-2. SED に内部オシレータが対応する周波数設定

| 2.08 | 4.16       | 8.31  | 16.63 |  |

|------|------------|-------|-------|--|

| 2.15 | 4.29       | 8.58  | 17.73 |  |

| 2.22 | 4.43       | 8.87  | 19.00 |  |

| 2.29 | 4.59       | 9.17  | 20.46 |  |

| 2.38 | 4.75       | 9.50  | 22.17 |  |

| 2.46 | 4.93       | 9.85  | 24.18 |  |

| 2.56 | 5.12       | 10.23 | 26.60 |  |

| 2.66 | 5.32       | 10.64 | 29.56 |  |

| 2.77 | 5.54       | 11.08 | 33.25 |  |

| 2.89 | 5.78       | 11.57 |       |  |

| 3.02 | 6.05       | 12.09 |       |  |

| 3.17 | 6.33       | 12.67 |       |  |

| 3.33 | 6.65 13.30 |       |       |  |

| 3.50 | 7.00       | 14.00 |       |  |

| 3.69 | 7.39       | 14.78 |       |  |

| 3.91 | 7.82       | 15.65 |       |  |

# SED の属性

SED プリミティブに使用可能な属性が 3 つあり、それらを表 1-3 に示します。これら属性の使用例は、本書の「記述例」の項にあります。現在のところ、SEDFB プリミティブはここに示す 3 つの属性に対応していません。

### 表 1-3. SED の属性

| 属性名          | 属性タイプ  | 記 述                           |

|--------------|--------|-------------------------------|

| SED_CLK_FREQ | String | SEDFA プリミティブで使用時のクロック周波数を指定する |

| DEV_DENSITY  | String | シミュレーションモデルで使用するデバイス規模を指定する   |

| CHECKALWAYS  | String | (予約)                          |

SED\_CLK\_FREQ 属性はクロック周波数の指定に使用されます。SEDFA プリミティブは、クロック源として MachXO2 内部オシレータを使用します。表 1-3 に使用可能な設定を示します。この表に示した以外の値を使用した場合、ソフトウェアはエラーメッセージを表示し、MAP プロセスを終了します。

DEV\_DENSITY 属性は MachXO2 シミュレーションモデルのデバイス規模の指定に使用されます。 DEV\_DENSITY 属性を指定しなかった場合は、デフォルト値の 1200L が使用されます。DEV\_DENSITY 属性に 指定可能な値は次のとおりです。

256L, 640L, 1200L, 2000L, 4000L, 7000L, 640U, 1200U, または 2000U

現時点で CHECKALWAYS 属性には対応していません。

# ポート説明

### **SEDENABLE**

SEDENABLE はレベルセンシティブ信号で、High のときは SED がイネーブルになります。この信号が Low になると、SEDハードウェアがディセーブルされます。必要であれば、設計内でHighに固定することもできます。

#### **SEDSTART**

SEDSTART は SED プロセスを開始する信号です。SEDENABLE が High の場合、SEDSTART 信号の立ち上が りエッジで SED サイクルが開始されます。SEDSTART 信号は、SED プロセスが完了するまで High になって いる必要があります。SED サイクル中に SEDSTART が Low になると、SEDDONE または SEDERR をアサート することなくプロセスが終了します。

#### SEDFRCERR

SEDFRCERR は SEDERR 信号でエラー表示を返すよう、SED プロセスを強制設定するために使用されます。通常は、SEDERR 出力に関連するロジックのテストに使用されます。SEDFRCERR 信号の立ち上がりエッジは、SED ハードウェアで検出され、SED クロックドライバ信号の立ち上がりエッジでラッチされます。エラー表示を返すためには、SED がアクティブの間、SEDFRCERR が High にラッチされている必要があります。推奨する使用法は、SEDINPROG 信号の立ち上がりエッジが検出されたときに、セットアップ・ホールド時間要件を満たしながら図 1-5 に示すようにユーザロジックで SEDFRCERR 信号を Low から High にドライブすることです。

## **SEDSTDBY**

SEDSTDBY ポートは SEDFA プリミティブのみにあり、OSCH コンポーネントの SEDSTDBY 出力ポートに接続されている必要があります。この信号は STDBY 機能のシミュレーションサポート用に用意され、内部オシレータをオフするために使用されます。STDBY 機能によって内部オシレータがオフされると、クロック源がオフされるため、SEDFA ブロックは動作しなくなります。ユーザが SEDFA のこの信号を接続しなかった場合でも、SED はハードウェア的に同じ動作となりますが、STDBY を使用した場合とはシミュレーション結果が一致しないことがあります。

#### **SEDCLKOUT**

SEDCLKOUT は SED ブロックへの SED クロックドライバ信号の、ゲート付きバージョンです。SEDCLKOUT は SEDENABLE でゲート処理されます。この信号は、SED ブロックへの入力、または SED ブロックからの出力の同期に使用されます。

#### **SEDDONE**

SEDDONE は SED チェックのサイクル完了を示す出力です。この信号は SED ハードウェアのアクティブ High 出力であり、SEDCLKOUT の立ち上がりエッジでクロックされます。SEDDONE は SEDSTART 信号が Low になるとリセットされます。

#### **SEDINPROG**

SEDINPROG は SED チェックの実行中を示す出力です。この信号は SED ハードウェアのアクティブ High 出力であり、SEDCLKOUT の立ち上がりエッジでクロックされます。SEDINPROG は SEDSTART が High になると、図 1-5 に示す遅延後に High になります。

#### **SEDERR**

SEDERR は SED チェックのサイクルが完了し、エラーがあったことを示す出力です。この信号は SED ハードウェアのアクティブ High 出力であり、SEDCLKOUT の立ち上がりエッジでクロックされます。 SEDERR は SEDSTART 信号が Low になると、図 1-5 に示す遅延後にリセットされます。

## SED フロー

一般的な SED フローは、次のようになります。

- 1. ユーザロジックが SEDENABLE を High にする。必要に応じてこの信号は High に固定される

- 2. ユーザロジックが SEDSTART を High にし、SED サイクルの実行中 High に保つ。SEDINPROG が High になる。SEDDONE または SEDERR が既に High になっていた場合は Low にドライブされる

- 3. SED が、コンフィグレーション SRAM からのデータリードを開始する

- 4. SED がチェックを終了する。SEDERR が更新され、SEDINPROG が Low になり、SEDDONE が High になる。別の SED サイクルが開始されると、SEDERR 信号がリセットされる

- 5. SEDERR が High にドライブされている場合は、PLD を再コンフィグレーションするとリセットでき

- 6. ユーザの指定に応じて SEDENABLE が Low になり、SED が使用されなくなる

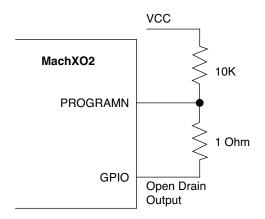

エラー検出時の望ましい動作は、PLD を再コンフィグレーションすることです(日本語注 $^1$ )。再コンフィグレーションは、PROGRAMN ピンを Low にドライブすると行われます。これは、外部的に GPIO ピンを PROGRAMN に接続すると実現できます。

<sup>1.</sup> 日本語注:自動的に無条件で再コンフィグレーションすることは推奨しない。図 16-4 はあくまで一例として示す意図である。望ましい動作はシステム要件・システム設計に依存する。

図 1-4. 回路例

Note: The 1 Ohm resistor shown allows a user to recover from a bad program which always pulls the GPIO pin low in the MachXO2 device. If this type of pattern is loaded into the MachXO2, the device will always be held in the re-configuration state and is not able to communicate or be erased to clear the error condition. To recover from this condition, remove the resistor and reprogram the device, then replace resistor.

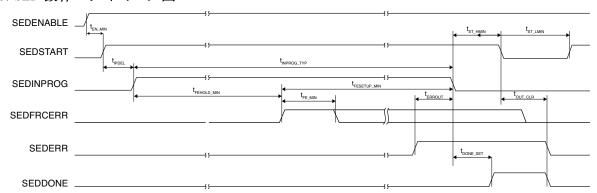

# SED 動作のタイミング図

# 図 1-5. SED 動作のタイミング図

ここで、図中のパラメータは以下の通りです。

| パラメータ                    | 値  | 単位     |

|--------------------------|----|--------|

| t <sub>EN_MIN</sub>      | 0  | SEDCLK |

| t <sub>IPDEL</sub>       | 2  | SEDCLK |

| t <sub>FEHOLD_MIN</sub>  | 92 | SEDCLK |

| t <sub>FESETUP_MIN</sub> | 5  | SEDCLK |

| t <sub>FE_MIN</sub>      | 2  | SEDCLK |

| t <sub>ERROUT</sub>      | 1  | SEDCLK |

| t <sub>ST_HMIN</sub>     | 0  | SEDCLK |

| t <sub>ST_LMIN</sub>     | 1  | SEDCLK |

| t <sub>OUT_CLR</sub>     | 2  | SEDCLK |

| t <sub>DONE_SET</sub>    | 0  | SEDCLK |

## SED の実行時間

SED チェックの実行に必要な時間は、デバイスの規模と、SED クロックドライバ信号の周波数によって異なります。また、計算のためのオーバーヘッド時間もある程度かかりますが、相対的には非常に短時間です。必要な時間は、次の式を使用して概算できます。

(最大ビット数 / 8) / SED クロックドライバ周波数 = 時間 (ms)

最大ビット数は Kbits 単位で表し、PLD の規模によって異なります (表 1-4 参照)。SED クロックドライバ信 号周波数は MHz 単位で表します。時間はミリ秒単位です。MachXO2 デバイスの SED チェックでは、SED サイクルごとに 8 ビット(1 バイト)がリードされます。

たとえば、4,000 LUT の MachXO2 を使用した設計で、SED クロックドライバ周波数が 7MHz の場合は、次のようになります。

(972 KBits / 8) / 7.0 MHz = 17.4 ms

この例では、SED チェックに約 17.4ms 要します。

SED クロックドライバ信号の生成には内部オシレータが使用されますが、その周波数は ±5.5% の変動があることに注意してください。

### 表 1-4. SED の実行時間

|          | XO2-<br>256 | XO2-<br>640 | XO2-640U | XO2-<br>1200 | XO2-<br>1200U | XO2-<br>2000 | XO2-<br>2000U | XO2-<br>4000 | XO2-<br>7000 |    |

|----------|-------------|-------------|----------|--------------|---------------|--------------|---------------|--------------|--------------|----|

| 規模¹      | 94K         | 191K        | 360K     | 360K         | 535K          | 535K         | 972K          | 972K         | 1534K        | 単位 |

| 33.3 MHz | 0.35        | 0.72        | 1.35     | 1.35         | 2.00          | 2.00         | 3.64          | 3.64         | 5.75         | ms |

| 3.05 MHz | 3.84        | 7.82        | 14.8     | 14.8         | 21.9          | 21.9         | 39.9          | 39.9         | 62.9         | ms |

<sup>1.</sup> 規模とはデバイス内のコンフィグレーション用ビット数を示す

# 記述例

次の簡単な RTL 記述例は、SED プリミティブの初期化方法を示しています。この例では、SRAM CRC 検出が常にイネーブルとなり、"sed\_start" 信号が High にドライブされると実行されます。SED ハードウェアの出力は、PLD 出力ピンに送出でき、別のモジュールで使用することもできます。SADFA プリミティブは、ispLEVER 8.1 SP1 以降及び Diamond 1.1 以降に含まれています。

# SEDVHDL 記述例

#### VHDL SEDFA

COMPONENT SEDFA

GENERIC(

SED\_CLK\_FREQ : string := "3.5";

CHECKALWAYS : string := "DISABLED";

DEV DENSITY : string := "1200L");

--"256L","640L","1200L","2000L","4000L","7000L", "640U", "1200U", "2000U"

PORT(

SEDENABLE : in STD\_LOGIC; SEDSTART : in STD\_LOGIC; SEDFRCERR : in STD\_LOGIC; SEDSTDBY : in STD\_LOGIC;

```

:

STD LOGIC;

SEDERR

out

SEDDONE

:

out

STD LOGIC;

SEDINPROG

:

out

STD LOGIC;

SEDCLKOUT

out

STD_LOGIC);

END COMPONENT;

attribute SED_CLK_FREQ : string ;

attribute SED_CLK_FREQ of SEDinst0 : label is "13.30";

attribute CHECKALWAYS : string ;

attribute CHECKALWAYS of SEDinst0 : label is "DISABLED" ;

attribute DEV_DENSITY : string ;

attribute DEV_DENSITY of SEDinst0 : label is "1200L" ;

SEDinst0: SEDFA

-- synthesis translate off

GENERIC MAP ( SED_CLK_FREQ => "13.30";

CHECKALWAYS => "DISABLED" ;

DEV_DENSITY => "1200L" )

-- synthesis translate on

PORT MAP (SEDENABLE => '1',

SEDSTART => sed_start,

SEDFRCERR => '0',

SEDSTDBY => sed_stdby,

SEDERR => sed err,

SEDDONE => sed done,

SEDINPROG => sed active,

SEDCLKOUT => sed_clkout);

SED Verilog 記述例

Verilog SEDFA

module SEDFA (SEDENABLE, SEDSTART, SEDFRCERR, SEDSTDBY, SEDERR, SEDDONE, SEDINPROG,

SEDCLKOUT);

input

SEDENABLE, SEDSTART, SEDFRCERR, SEDSTDBY;

SEDERR, SEDDONE, SEDINPROG, SEDCLKOUT;

parameter SED_CLK_FREQ = "3.5";

parameter CHECKALWAYS = "DISABLED";

parameter DEV_DENSITY = "1200L";

//"256L", "640L", "1200L", "2000L", "4000L", "7000L", "640U", "1200U", and "2000U"

endmodule

Verilog SEDFA プリミティブ・インスタンス

// instantiate SEDFA primitive module with parameter passing to SEDFA module

SEDFA # (.SED_CLK_FREQ("4.75"), .DEV_DENSITY("1200L"))

```

sedfa\_tst (.SEDENABLE(1'b1), .SEDSTART(sed\_start), .SEDFRCERR(1'b0), .SEDSTDBY(),

.SEDERR(sed\_err), .SEDDONE(sed\_done), .SEDINPROG(sed\_active), .SEDCLK-OUT(sed\_clkout));

# テクニカルサポート支援

ホットライン:1-800-LATTICE(北米)

+1-503-268-8001(北米以外)

e-mail: techsupport@latticesemi.com インターネット:www.latticesemi.com

# 日本語版変更履歴

| 日付       | パージョン | 新ページ | 変更内容                                  |

|----------|-------|------|---------------------------------------|

| 2011年8月  | 01.4  | -    | 初版                                    |

| 2012年8月  | 01.6  | _    | ロゴ更新                                  |

|          |       | 2, 3 | 検出制限の節と動作モードの節を追記更新                   |

| 2013年2月  | 01.8  | _    | "SRAM CRC エラー検出"> "SED" に更新。章番号を 16>1 |

|          |       | 1    | 図 1-1 差し替え                            |

|          |       | 2    | "SED の制約"節、および"SED 動作モード"節、それぞれ更新     |

|          |       | 5    | SEDSTART 項、記述一部削除                     |

|          |       | 6    | "SED フロー"節、項番2削除                      |

|          |       | 7    | "SED 動作タイミング"節と図 1-5 タイミング、および表追加     |

| 2013年12月 | 1.9   | 5    | SEDFRCERR 信号記述一部更新                    |

|          |       | 6    | SEDINPROG、SEDERR 信号記述一部更新             |

|          |       |      |                                       |