# MachXO2 sysIO 使用ガイド

**2015 年 5 月** テクニカルノート TN1202

# はじめに

MachXO2™ PLD ファミリの sysIO™バッファは、現代の速いペースの設計で求められる、柔軟に I/O 規格に対応するというニーズを満たす設計になっています。対応可能な I/O 規格は、ユーザが各自の設計を標準バス、メモリデバイス、ビデオアプリケーション及び新しい標準と簡単に連携させられるように、シングルエンド I/O から差動 I/O まで様々です。このテクニカルノートでは、対応する I/O 規格及び MachXO2 PLD ファミリのバンク方式について説明します。 I/O 機能及び配置規則のより一層の理解が得られるように、sysIOアーキテクチャ及びソフトウェアの使用法についても説明します。

# sysIO バッファの概要

MachXO2 sysIO を構成する基本要素は、PIC(Programmable I/O Cell、プログラマブル I/O セル)ブロックです。MachXO2 デバイスアーキテクチャには、4 タイプの PIC ブロックがあり、それらは基本 PIC ブロック、DDR 対応用のメモリ PIC ブロック、ギアリング (=DeMux) 付き受信側 PIC ブロック、及びギアリング (=Mux) 付き送信側 PIC ブロックです。ギアリング付き PIC ブロックは、ビデオ及び高速アプリケーションに使用され、ワードアライメント用の制御モジュールが組み込まれています。メモリ PIC ブロックには、DQS ストローブ信号及びクロック位相シフト管理用の付加的ロジックがあります。メモリ PIC ブロック及びギアリング PIC ブロックの詳細については、"TN1203、MachXO2 High-Speed Source Synchronous and Memory Interfaces (高速ソースシンクロナスとメモリインターフェイス) "を参照してください。

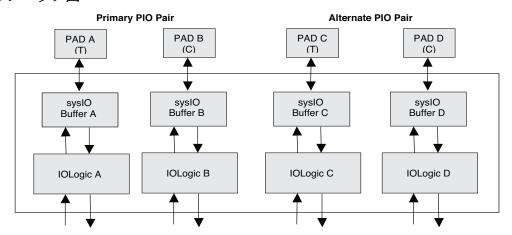

4タイプ全ての PIC ブロックに共通する特徴は、各 PIC ブロックが 4 つの PIO (Programmable I/O、プログラマブル I/O) で構成されている点です。PIO は、それぞれが 1 つの sysIO バッファと 1 つの I/O 論理ブロックを含みます。簡略化した sysIO ブロック図を図 10-1 に示します。I/O 論理ブロックは、入力ブロック及び出力ブロック及びトライステートブロックで構成されています。これらのブロックには、レジスタ、入力遅延セル、及び各種の動作モードの実現に必要な制御ロジックがあります。sysIO バッファは、対応する I/O 規格への準拠を判断します。また、共通の設計ニーズを満たすためにヒステリシスなどの機能も実現します。I/O 論理ブロック及び sysIO バッファは、チップ面積の使用が最小になるように設計されているため、容易なバスインターフェイス及び効率的なピン配置ができます。

隣接する 2 つの PIO は、コンプリメンタリ出力ドライバペアを形成できます。ここでは、PIC ブロックの PIOA 及び PIOB がバッファのプライマリペアを形成し、一方 PIOC 及び PIOD バッファはセカンダリ (代替) ペアを構成します。プライマリペアは、セカンダリペアにはない付加的な機能を持ちます。PIC ブロックの sysIO バッファは、シングルエンド I/O 規格として実装された場合には等価です。

# 対応する sysIO 規格

Lattice MachXO2 sysIO バッファは、シングルエンド規格及び差動規格の両方に対応します。さらにシングルエンド規格は、LVCMOS のような内部レシオ規格、及び SSTL のような外部基準電圧を参照する規格に分類できます。内部レシオ規格は、個別にコンフィグレーション可能なドライブ強度及びバスメンテナンス回路(弱いプルアップ、弱いプルダウン、またはバスキーパ)を実現します。

## 図 10-1. PIC ブロック図

2 タイプのレシオ型入力バッファがあり、一方は  $V_{CCIO}$  に接続され、他方は  $V_{CC}$  (1.2V) に接続されます。各 sysIO バッファは両方のバッファに同時に対応します。そのため、 $V_{CCIO}$  電圧に関係なく、任意の入力バッファを 1.2V レシオ型入力バッファにプログラムするオプションが用意されています。

MachXO2 デバイスの全てのバンクが、外部レジスタ及びコンプリメンタリ LVCMOS 出力を使用して、真の 差動入力及びエミュレート差動出力を実現できます。真の LVDS 差動出力及び LVDS 入力終端は、本書の "sysIO のバンク方式"に記述がある特定のバンクで実現します。

## 表 10-1. 対応する入力規格

| 入力規格               | V <sub>REF</sub> (公称) | V <sub>CCIO</sub> ¹(公称) |  |  |  |

|--------------------|-----------------------|-------------------------|--|--|--|

| シングルエンド・インターフェイス   |                       |                         |  |  |  |

| LVTTL33            | _                     | _                       |  |  |  |

| LVCMOS33           | _                     | _                       |  |  |  |

| LVCMOS25           | _                     | _                       |  |  |  |

| LVCMOS18           | _                     | _                       |  |  |  |

| LVCMOS15           | _                     | _                       |  |  |  |

| LVCMOS12           | _                     | _                       |  |  |  |

| SSTL25 Class I, II | 1.25                  | _                       |  |  |  |

| SSTL18 Class I, II | 0.9                   | _                       |  |  |  |

| HSTL18 Class I, II | 0.9                   | _                       |  |  |  |

| PCI33              | -                     | 3.3                     |  |  |  |

| 差動インターフェイス         |                       |                         |  |  |  |

| LVDS25             | _                     | _                       |  |  |  |

| LVPECL33           | _                     | _                       |  |  |  |

| MLVDS25            | _                     | _                       |  |  |  |

| BLVDS25            | _                     | _                       |  |  |  |

| RSDS25             | _                     | _                       |  |  |  |

| SSTL25 差動          | _                     | _                       |  |  |  |

| SSTL18D 差動         | _                     |                         |  |  |  |

| HSTL18D 差動         | _                     | _                       |  |  |  |

| LVTTL / LVCMOS 差動  |                       | _                       |  |  |  |

| MIPI <sup>2</sup>  | _                     | _                       |  |  |  |

- 1. 規定がない場合は、、VCCIO 要件セクションの電圧混在サポートを参照

- 2. 外付け抵抗でエミュレートする

## 表 10-2. 対応する出力規格

| 出力規格                  | ドライブ (mA)           | V <sub>CCIO</sub> (公称) |

|-----------------------|---------------------|------------------------|

| シングルエンド・インターフェ        | -イス                 |                        |

| LVTTL33               | 4, 8, 12, 16, 24    | 3.3                    |

| LVCMOS33              | 4, 8, 12, 16, 24    | 3.3                    |

| LVCMOS25              | 4, 8, 12, 16        | 2.5                    |

| LVCMOS18              | 4, 8, 12            | 1.8                    |

| LVCMOS15              | 4, 8                | 1.5                    |

| LVCMOS12              | 2, 6                | 1.2                    |

| SSTL25 Class I        | 8                   | 2.5                    |

| SSTL18 Class I        | 8                   | 1.8                    |

| HSTL18 Class I        | 8                   | 1.8                    |

| PCI33                 | 24                  | 3.3                    |

| 差動インターフェイス            |                     |                        |

| LVDS25                | 3.5, 2.5, 2.0, 1.25 | 2.5, 3,3               |

| LVPECL33              | 16                  | 3.3                    |

| MLVDS25               | 16                  | 2.5                    |

| BLVDS25               | 16                  | 2.5                    |

| RSDS25                | 8                   | 2.5                    |

| SSTL25 Differential   | 8                   | 2.5                    |

| SSTL18D Differential  | 8                   | 1.8                    |

| HSTL18D Differential  | 8                   | 1.8                    |

| LVTTL33 Differential  | 4, 8, 12, 16, 24    | 3.3                    |

| LVCMOS33 Differential | 4, 8, 12, 16, 24    | 3.3                    |

| LVCMOS25 Differential | 4, 8, 12, 16        | 2.5                    |

| LVCMOS18 Differential | 4, 8, 12            | 1.8                    |

| LVCMOS15 Differential | 4, 8                | 1.5                    |

| LVCMOS12 Differential | 2, 6                | 1.2                    |

| MIPI <sup>1</sup>     | 2                   | 2.5                    |

# sysIO バンク構成

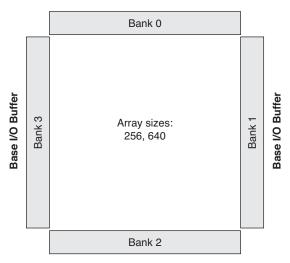

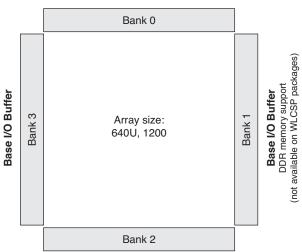

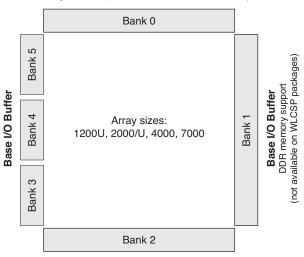

MachXO2 ファミリは非対称な I/O バンク構造を持ちます。MachXO2-256 と MachXO2-640/U 及び MachXO2-1200 は、各辺に 1 つの I/O バンクで計 4 つの I/O バンクを持ちます。MachXO2-1200U と MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスは、上下辺及び右辺それぞれに 1 つの I/O バンクと、左辺に 3 つのバンクで計 6 つの I/O バンクを持ちます。

規模が MachXO-640U と MachXO-1200/U 以上のデバイスは、上辺バンク(バンク 0)のプライマリペアで真の LVDS 差動出力を実現し、下辺 I/O バンクの各 I/O ペアで  $100\,\Omega$  の差動入力終端を実現します。これらのデバイスでは、下辺 I/O バンクでプログラマブル PCI クランプも使用可能です。 $^{12}$

MachXO2-256 及び MachXO2-640 は、真の LVDS 差動出力、差動入力終端、及び PCI クランプをいずれのバンクにおいても実現しません(MachXO2-640U I/O のアーキテクチャは大規模デバイスに類似し、後述する機能を実現します)。全ての MachXO2 PLD の各 I/O ピンに、ディセーブルまたはイネーブル可能なクランプ機能があります。このクランプは PCI クランプに似ていますが、規模が MachXO2-640U と MachXO2-1200/U 以上のデバイスにおける下辺バンクでの場合を除いて、PCI に準拠していません。I/O バンクの配置を図 10-

1. 英語オリジナル版では 1200-R1 に関する記述がありますが、日本語版では省略しています。

2 と 10-3、及び 10-4 に示します。WLCSP (Wafer Level Chip Scale Package) デバイスでは、バンク 1 での DDR メモリに対応していません。

## 図 10-2. MachXO2-256 及び MachXO2-640 の I/O バンク配置

#### Base I/O Buffer

Base I/O Buffer

# 図 10-3. MachXO2-640U及び MachXO2-1200 の I/O バンク配置

#### Base I/O Buffer

Plus: 1 pair of LVDS differential outputs for every four PIO (3.5 mA, 2.5 mA, 2.0 mA, 1.25 mA)

#### Base I/O Buffer

Plus: 100 ohm differential input termination on every pair plus PCI clamp

図 10-4. MachXO2-1200U と MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 の I/O バンク配置

#### Base I/O Buffer

Plus: 1 pair of LVDS differential outputs for every four PIO (3.5 mA, 2.5 mA, 2.0 mA, 1.25 mA)

#### Base I/O Buffer

Plus: 100 ohm differential input termination on every pair plus PCI clamp

# I/O バンクで対応する sysIO 規格

全バンクが上述の VCCIO 規則に従複数の I/O 規格に対応可能です。表 10-3 及び 10-4 に、MachXO2 デバイスの各辺が対応する I/O 規格の概略を示します。

表 10-3. 各辺で対応するシングルエンド I/O 規格

| 規格                  | 上辺  | 下辺               | 左辺  | 右辺  |

|---------------------|-----|------------------|-----|-----|

| PCI33               | _   | Yes <sup>1</sup> | _   | _   |

| LVTTL33             | Yes | Yes              | Yes | Yes |

| LVCMOS33            | Yes | Yes              | Yes | Yes |

| LVCMOS25            | Yes | Yes              | Yes | Yes |

| LVCMOS18            | Yes | Yes              | Yes | Yes |

| LVCMOS15            | Yes | Yes              | Yes | Yes |

| LVCMOS12            | Yes | Yes              | Yes | Yes |

| SSTL25 <sup>2</sup> | Yes | Yes              | Yes | Yes |

| SSTL18 <sup>2</sup> | Yes | Yes              | Yes | Yes |

| HSTL18 <sup>2</sup> | Yes | Yes              | Yes | Yes |

<sup>1.</sup> PCI33 は MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、および MachXO2-7000 デバイスの底辺バンクで対応する

<sup>2.</sup> SSTL Class II と HSTL Class II は入力にのみ対応する

## 表 10-4. 各辺で対応する差動 I/O 規格

| 規格                     | 上辺               | 下辺  | 左辺  | 右辺  |

|------------------------|------------------|-----|-----|-----|

| LVDS 出力                | Yes <sup>1</sup> | _   | _   | _   |

| LVPECL33E <sup>2</sup> | Yes              | Yes | Yes | Yes |

| MLVDS25E <sup>2</sup>  | Yes              | Yes | Yes | Yes |

| BLVDS25E <sup>2</sup>  | Yes              | Yes | Yes | Yes |

| RSDS25E <sup>2</sup>   | Yes              | Yes | Yes | Yes |

| LVDS25E <sup>2</sup>   | Yes              | Yes | Yes | Yes |

| SSTL25D 出力             | Yes              | Yes | Yes | Yes |

| SSTL18D 出力             | Yes              | Yes | Yes | Yes |

| HSTL18D 出力             | Yes              | Yes | Yes | Yes |

| LVTTL33D 出力            | Yes              | Yes | Yes | Yes |

| LVCMOS33D 出力           | Yes              | Yes | Yes | Yes |

| LVCMOS25D 出力           | Yes              | Yes | Yes | Yes |

| LVCMOS18D 出力           | Yes              | Yes | Yes | Yes |

| LVCMOS15D 出力           | Yes              | Yes | Yes | Yes |

| LVCMOS12D 出力           | Yes              | Yes | Yes | Yes |

| LVDS 入力                | Yes              | Yes | Yes | Yes |

| LVPECL33 入力            | Yes              | Yes | Yes | Yes |

| MLVDS25 入力             | Yes              | Yes | Yes | Yes |

| BLVDS25 入力             | Yes              | Yes | Yes | Yes |

| RSDS25 入力              | Yes              | Yes | Yes | Yes |

| SSTL25D 入力             | Yes              | Yes | Yes | Yes |

| SSTL18D 入力             | Yes              | Yes | Yes | Yes |

| HSTL18D 入力             | Yes              | Yes | Yes | Yes |

| LVTTL33D 入力            | Yes              | Yes | Yes | Yes |

| LVCMOS33D 入力           | Yes              | Yes | Yes | Yes |

| LVCMOS25D 入力           | Yes              | Yes | Yes | Yes |

| LVCMOS18D 入力           | Yes              | Yes | Yes | Yes |

| LVCMOS15D 入力           | Yes              | Yes | Yes | Yes |

| LVCMOS12D 入力           | Yes              | Yes | Yes | Yes |

| MIPI                   | Yes              | Yes | Yes | Yes |

<sup>1.</sup> 真の LVDS 出力は MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、および MachXO2-7000 デバイスの上辺バンクで対応する

# 供給電源要件

MachXO2 デバイスファミリの電源系統は sysIO バッファ用に簡略化されていて、コア電源  $V_{CC}$  及びバンク電源  $V_{CCIO}$  が 2 つのメイン電源です。 $V_{CC}$  及び  $V_{CCIO}$  を公称 1.2V に接続することにより、MachXO2 デバイスは、単一電源の供給と動作が可能です。JTAG プログラミングピンは、JTAG ピンがあるバンクの  $V_{CCIO}$  による電源供給が可能です。全てのユーザ sysIO で、電源起動後とデバイスコンフィグレーションの完了前に弱いプルダウン状態になります。

<sup>2.</sup> エミュレート出力規格は規格名の後ろに "E" を付加する

# I/O 規格の V<sub>CCIO</sub> 要件

MachXO2 デバイスの各 I/O バンクに別個の  $V_{CCIO}$  電源ピン(1.2V/1.5V/1.8V/2.5V/3.3V に接続可能)があり、この電圧は出力 I/O 規格の電源、及び出力のドライブ強度のソースとして使用されます。これに加えて  $V_{CCIO}$  は、LVTTL や LVCMOS 及び PCI などのレシオ型入力バッファの電源供給も行います。これにより  $V_{CCIO}$  電圧レベルに追随する入力バッファの閾値が確保されます。

LVCMOS I/O タイプでは、入力または I/O 規格の  $V_{CCIO}$  要件が同じである限り、あるいはバンクでの全入力が、表 10-5 及び 10-6 に規定されているオーバードライブまたはアンダードライブの範囲内にある場合に、各 I/O バンクで入力電圧の混在に対応可能です。他にも、入力レシーバの柔軟性をより一層高める 2 つのオプションが存在します。1 つは、バンク  $V_{CCIO}$  電圧に関係なく I/O が 1.2V レシオ型入力バッファになるようにコンフィグレーションすることです。これが可能なのは、MachXO2 sysIO バッファに  $V_{CCIO}$  及び  $V_{CCIO}$  に同時に接続された 2 つのレシオ型入力バッファがあるためです。もう 1 つは、入力基準電圧ピンを使用して、バンクの  $V_{CCIO}$  が扱わない LVCMOS 規格の入力閾値を設定することです。

## 表 10-5. LVCMOS / LVTTL I/O が同じバンクの V<sub>CCIO</sub> 要件 <sup>1</sup>

| I/O タイプ                     | バンクの制限                                                                                     |

|-----------------------------|--------------------------------------------------------------------------------------------|

| LVCMOS12                    | 出力は $V_{\rm CCIO}$ = 1.2V が必要<br>入力は全 $V_{\rm CCIO}$ レベルに対応                                |

| LVCMOS15                    | 出力は $V_{\rm CCIO}$ = 1.5V が必要<br>入力は全 $V_{\rm CCIO}$ レベルに対応                                |

| LVCMOS15R33 <sup>2, 3</sup> | 入力のみ。V <sub>CCIO</sub> = 3.3V と V <sub>REF</sub> = 0.75V が必要                               |

| LVCMOS15R25 <sup>2, 3</sup> | 入力のみ。V <sub>CCIO</sub> = 2.5V and V <sub>REF</sub> = 0.75V が必要                             |

| LVCMOS18                    | 出力は V <sub>CCIO</sub> = 1.8V が必要<br>入力は V <sub>CCIO</sub> = 1.5V, 1.8V, 2.5V, or 3.3V が必要  |

| LVCMOS18R33 <sup>2, 3</sup> | 入力のみ。V <sub>CCIO</sub> = 3.3V and V <sub>REF</sub> = 0.9V が必要                              |

| LVCMOS18R25 <sup>2, 3</sup> | 入力のみ。V <sub>CCIO</sub> = 2.5V and V <sub>REF</sub> = 0.9V が必要                              |

| LVCMOS25                    | 出力は V <sub>CCIO</sub> = 2.5V が必要<br>入力は V <sub>CCIO</sub> = 1.5V, 1.8V, 2.5V, or 3.3V. が必要 |

| LVCMOS25R33 <sup>2, 3</sup> | 入力のみ。V <sub>CCIO</sub> = 3.3V and V <sub>REF</sub> = 1.25V が必要                             |

| LVCMOS33                    | 出力は V <sub>CCIO</sub> = 3.3V が必要<br>入力は V <sub>CCIO</sub> = 1.5V, 1.8V, 2.5V, or 3.3V が必要  |

| LVTTL33                     | 出力は V <sub>CCIO</sub> = 3.3V が必要<br>入力は V <sub>CCIO</sub> = 1.5V, 1.8V, 2.5V, or 3.3V が必要  |

| PCI33                       | 入力と出力が共に V <sub>CCIO</sub> = 3.3V が必要                                                      |

- 1. 特定の I/O タイプとバンク VCCIO の組み合わせは、より大きい直流電流を引き起こすかもしれない。その他の詳細については表 10-6 を参照。I/O タイプの電力見積もりにはパワーカリキュレータを用いる

- 2. オプションと BUS KEEPER オプションはこれらの I/O タイプでは利用できない

- 3. 各 I/O バンクで 1 つの VREF 信号に対応できるため、各 I/O バンクではこれらの I/O 規格の 1 つを用いることができる

### 表 10-6. LVCMOS 及び LVTTL I/O タイプの電圧混在への対応

|                   | 入力               |                        |                        | 入力                     |                  |      |      | 出力   |      |      |

|-------------------|------------------|------------------------|------------------------|------------------------|------------------|------|------|------|------|------|

| V <sub>CCIO</sub> | 1.2V             | 1.5V                   | 1.8V                   | 2.5V                   | 3.3V             | 1.2V | 1.5V | 1.8V | 2.5V | 3.3V |

| 1.2V              | YES              | YES <sup>6</sup>       |                        |                        |                  | YES  |      |      |      |      |

| 1.5V              | YES <sup>1</sup> | YES                    | YES <sup>6</sup>       | YES <sup>6</sup>       | YES <sup>6</sup> |      | YES  |      |      |      |

| 1.8V              | YES <sup>1</sup> | YES <sup>5</sup>       | YES                    | YES <sup>6</sup>       | YES <sup>6</sup> |      |      | YES  |      |      |

| 2.5V              | YES <sup>1</sup> | YES <sup>2, 5, 7</sup> | YES <sup>3, 5, 7</sup> | YES                    | YES <sup>6</sup> |      |      |      | YES  |      |

| 3.3V              | YES <sup>1</sup> | YES <sup>2, 5, 7</sup> | YES <sup>3, 5, 7</sup> | YES <sup>4, 5, 7</sup> | YES              |      |      |      |      | YES  |

- 1. バスホールドや弱いプルアップがオンされると、リークが起きる

- 2. レシオ入力バッファをアンダードライブ条件で用いるか、または参照型入力バッファの I/O タイプ LVCMOS15R25 か LVCMOS15R33 を用いることで、本入力規格に対応できる

- 3. レシオ入力バッファをアンダードライブ条件で用いるか、または参照型入力バッファの I/O タイプ LVCMOS18R25 か LVCMOS18R33 を用いることで、本入力規格に対応できる

- 4. レシオ入力バッファをアンダードライブ条件で用いるか、または参照型入力バッファの I/O タイプ LVCMOS25R33 を用いることで、本入力規格に対応できる

- 5. レシオ入力バッファを使用し、入力電圧が VCCIO 以下の場合のアンダードライブ条件

- a. IO が High レベルにあるときのアンダードライブは、より大きめの DC 電流を引き起こす。そのような条件下では、電力見積もりにパワーカリキュレータを用いることを推奨

- b. ヒステリシスは対応しないので、Diamond にて HYSTERESIS を NA にセットする必要がある

- c. クランプは対応しないので、Diamond にて CLAMP は OFF にする必要がある

- d. IO 終端は対応しないので、Diamond にて PULLMODE は NONE にする必要がある

- 6. レシオ入力バッファを使用し、入力電圧が VCCIO 以上の場合ののオーバードライブ条件

- a. ヒステリシスは対応しないので、Diamond にて HYSTERESIS を NA にセットする必要がある

- c. クランプは対応しないので、Diamond にて CLAMP は OFF にする必要がある

- d. IO 終端は対応しないので、Diamond にて PULLMODE は NONE にする必要がある

- 7. アンダードライブ条件では、一般的な低消費電力要件の観点から参照型入力バッファよりもレシオ入力バッファを用いることが望ましい

- 8. レシオ入力バッファをアンダードライブかオーバードライブ条件で用いるとき、HYSTERESIS 設定は NA にし、CLAMP 設定は OFF にするべきで、かつ UP と KEEPER PULLMODE 設定には対応しない

差動入力規格では、表 10-7 に示すようなアーキテクチャによって、一定の電圧混在が可能になっています。

### 表 10-7. 差動入力規格の電圧混在への対応

|                   |                                                      | 差動入力    |                     |                        |                                       |           |

|-------------------|------------------------------------------------------|---------|---------------------|------------------------|---------------------------------------|-----------|

| V <sub>CCIO</sub> | LVDS,<br>LVPECL33,<br>MLVDS25,<br>BLVDS25,<br>RSDS25 | SSTL25D | SSTD18D,<br>HSTL18D | LVTTL33D,<br>LVCMOS33D | LVCMOS25D,<br>LVCMOS15D,<br>LVCMOS12D | LVCMOS18D |

| 1.2V              |                                                      |         |                     |                        |                                       |           |

| 1.5V              |                                                      |         |                     |                        |                                       |           |

| 1.8V              |                                                      |         | YES                 |                        |                                       | YES       |

| 2.5V              | YES                                                  | YES     | YES                 |                        | YES                                   | YES       |

| 3.3V              | YES                                                  | YES     | YES                 | YES                    | YES                                   | YES       |

## 入力基準 (参照) 電圧

各 I/O バンクは 1 つの基準電圧( $V_{REF}$ )に対応します。バンクの任意の I/O を入力基準電圧ピンとしてコンフィグレーションできます。このピンは、基準電圧入力として使用されていなければ通常の I/O です。SSTL

及び HSTL 入力に対応するために、基準電圧は  $V_{\rm CCIO}$  レベルの 1/2 に設定されます。入力基準電圧は、 $V_{\rm REF}$  ジェネレータから内部的に生成することもできます。その場合も同様に、バンクごとに 1 つの  $V_{\rm REF}$  ジェネレータがあり、そのプログラマブル設定は OFF、 $V_{\rm CCIO}$  の 45%、 $V_{\rm CCIO}$  の 50%、及び  $V_{\rm CCIO}$  の 55% です。バンクごとに 1 つの  $V_{\rm REF}$  しか存在しないため、内部 VREF ジェネレータ及び外部 VREF ピンのプログラミングは、特定のバンクについて同時に設定することはできません。

# sysIO バッファのコンフィグレーション

様々なシングルエンド規格及び差動規格に対応するために、MachXO2 デバイスは、3 タイプの汎用 sysIO バッファペアを備えていて、各バッファペアは、2 つの PIO バッファからなります。 PIO A 及び B パッドはプライマリペアを形成し、PIO C 及び D パッドはセカンダリペアを形成します。ペアのパッド A 及び C は "true" パッドと見なされ、一方、パッド B 及び D は "comp" パッドと見なされます。 "true" パッドは差動信号の非反転側に関連付けられ、一方、"comp" パッドは差動信号の反転側に関連付けられます。

弱いプルアップ、または弱いプルダウン、あるいは弱いバスキーパを可能とするため、全ての PIO がプログラマブルクランプ及びメンテナンス回路に対応しています。基本 sysIO バッファペアは小規模デバイスの全ての辺と、MachXO2-640U や MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスの左辺及び右辺で使用されます。LVDS sysIO バッファペアは、プライマリ PIO ペアに LVDS 出力ドライバが付加されています。それらは MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスの上辺バンクで使用できます。下辺の sysIO バッファペアには、 $100\Omega$  終端抵抗が "true" 及び "comp" パッド間にあります。下辺の sysIO バッファペアは PCI クランプも実現します。それらには MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスの下辺 I/O バンクが対応しています。

## LVCMOS バッファのコンフィグレーション

LVCMOS バッファは基本 sysIO バッファペアに組み込まれていて、これらは共通の回路設計ニーズに対応するために様々なモードでコンフィグレーションできます。

#### バスメンテナンス回路

各パッドは弱いプルアップと弱いプルダウン、及び弱いバスキーパ機能を備えていて、、ON 及び OFF のプログラマビリティで選択されます。プルダウン及びプルアップの設定はワイヤード OR などのワイヤードロジックの構成時に役立ちます。バスキーパ・オプションは、最後のドライブ状態で信号をラッチして、最小の電力消費で有効レベルに保持します。入力リークは、バスメンテナンス回路をオフにすることによって最小に抑えることができます。ただし、入力バッファでの不要な電力消費を避けるために、既知の状態に入力がドライブされるようにすることが重要です。バスメンテナンス回路はシングルエンドのレシオ I/O 規格に使用可能です。

### プログラマブル・ドライブ強度

全てのシングルエンド・ドライバがプログラマブルなドライブ強度を持ち、I/O ごとに個別に設定できます。各 I/O 規格に使用可能なドライブ強度については、表 10-9 を参照してください。MachXO2 プログラマブル・ドライブのアーキテクチャは、各ドライブ設定に対して最小ドライブ強度で保証されています。データシートの V/I 曲線は、出力ドライブ機能と出力負荷の詳細を示します。ドライブ強度を選択する場合は、この情報をバンクごとの電流及びパッケージ熱限界電流と共に考慮する必要があります。

## 入力ヒステリシス

LVCMOS12 を除く全てのレシオ型入力レシーバが入力ヒステリシスに対応します。LVCMOS33 とLVCMOS25、LVCMOS18 及びLVCMOS15 の入力ヒステリシスは、柔軟性のために 2 つの設定を備えています。表 10-5 及び 10-6 に示したようなアンダードライブまたはオーバードライブの入力状態で動作する場合、レシオ型入力レシーバは入力ヒステリシスを持ちません。

## プログラマブル・スルーレート

各デバイス I/O ピンのシングルエンド出力バッファは、低ノイズ (SLEWRATE=SLOW) または高速 (SLEWRATE=FAST) のいずれかの性能にコンフィグレーション可能なプログラマブル出力スルーレート制御

を持ちます。各 I/O ピンは、個別のスルーレート制御を持ちます。このスルーレート制御は、立ち上がりエッジ及び立ち下がりエッジの両方に影響します。各 I/O 規格の立ち上がり / 立ち下がりランプレートについては、該当する I/O 設定に対する IBIS ファイルにモデル化されています。

## トライステート制御及びオープンドレイン制御

各シングルエンド出力ドライバは、デバイスとしてのグローバル・トライステート制御の他に別個のトライステート制御を持ちます。シングルエンド出力ドライバは、各 I/O でのオープンドレイン動作にも別個に対応します。オープンドレイン出力は一般に、外部でプルアップされ、シンク電流仕様のみが維持されます。

## PCI クランプでの PCI 対応

下辺の sysIO バッファペアは、個別にプログラム可能なオプションの PCI クランプ・ダイオードに対応しています。

これは MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスの下辺のみが対応します。PCI クランプは、デバイスの他の全辺で使用可能なプログラマブル・クランプよりも大きいクランプ電流に対応できます。

## コンプリメンタリ出力

各 sysIO バッファペアには、"true" パッドに関連付けられたシングルエンド・ドライバをドライブするデータを、オプションでドライブが可能なコンプリメンタリ回路が組み込まれています。このためシングルエンド・ドライバのペアを使用して、信号間で最も低スキューを持つコンプリメンタリ出力をドライブできます。

## 差動バッファのコンフィグレーション

基本 sysIO バッファペアは差動入力規格に対応し、そのコンプリメンタリ出力は SSTL 及び HSTL の差動出力規格に対応します。規模が MachXO2-640U と MachXO2-1200/U 及びそれ以上のデバイスでは、上下辺は基本 sysIO バッファペアが対応する機能に対して付加的な機能もいくつか実現します。

#### 差動レシーバ

全ての sysIO バッファペアがデバイス全辺で差動入力に対応します。sysIO バッファペアが差動レシーバとしてコンフィグレーションされた場合、入力ヒステリシス及びバスメンテナンス機能はディセーブされます。

#### オンチップ入力終端

MachXO2デバイスはオンチップ  $100\,\Omega$  (公称) 入力差動終端を MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスの下辺で実現します。終端は下辺の全入力 PIO ペアで使用でき、プログラマブルです。

#### エミュレート差動規格

全ての sysIO バッファペアが、上述したコンプリメンタリ出力に対応しています。この機能を使用すると、 差動 SSTL 及び HSTL 規格に必要なコンプリメンタリ SSTL または HSTL 信号をドライブできます。またオンチップ抵抗ネットワークと組み合わせて使用すると、LVPECL や MLVDS、BLVDS、及び差動 RSDS などの差動出力規格をエミュレートすることもできます。sysIO バッファペアを差動トランスミッタとしてコンフィグレーションした場合、バスメンテナンス及びオープンドレイン機能はディセーブルされます。MachXO2ファミリの全シングルエンド sysIO バッファペアが、エミュレート差動出力規格に対応します。

### 真の差動出力及び出力ドライブ

MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスは、真の差動出力ドライバを上辺で対応しますが、これらはプライマリ PIO ペアでのみ使用可能です。出力ドライバは固定の 1.2V コモンモードで、1.25 mA と 2.5 mA、2.0mA または 3.5mA のプログラマブル・ドライブ電流を持ちます。一度に使用可能な真の LVDS 差動ドライブ設定は 1 つのみ、上辺のドライバが全て同一ドライブ強度を持つようにプログラムする必要があります。真の差動出力のバンク VCCIO は 2.5V または 3.3V にできます。

# ソフトウェアの sysIO 属性

sysIO バッファの機能及び性能を制御するために、sysIO 属性またはプリミティブをラティス開発ソフトウェアで使用する必要があります。これらの指定は HDL ソースコードや Lattice Diamond ™の Spreadsheet View(スプレッドシート・ビュー) GUI によって、又は ASCII 制約ファイル (.lpf ファイル) で直接行います。付録 A、B 及び C に、このような属性を様々な環境で使用した例をリストしてあります。このセクションでは、これらの各属性について詳細に説明します。

## HDL 属性

HDL ソースコードでは、このセクションで説明する属性の 2 つを除いて全てを使用して、sysIO バッファ機能を指定できます。

#### IO TYPE

この属性は I/O の sysIO 規格を設定するために使用されます。これらの I/O 規格を設定するために必要な VCCIO は属性名に組み込まれています。BANK VCCIO 属性は、各 I/O タイプに許容される VCCIO の組み合わせを指定するために使用されます。MachXO2 ファミリの有効な I/O タイプを表 10-8 に示します。

# 表 10-8. 対応する I/O タイプ

| sysIO シグナリング規格                           | IO_TYPE     |

|------------------------------------------|-------------|

| LVDS 2.5V                                | LVDS25      |

| エミュレート LVDS 2.5V¹                        | LVDS25E     |

| RSDS                                     | RSDS25      |

| エミュレート RSDS¹                             | RSDS25E     |

| Bus LVDS 2.5V                            | BLVDS25     |

| エミュレート Bus LVDS 2.5V¹                    | BLVDS25E    |

| MLVDS 2.5V                               | MLVDS25     |

| エミュレート MLVDS 2.5V <sup>1</sup>           | MLVDS25E    |

| LVPECL 3.3V                              | LVPECL33    |

| エミュレート LVPECL 3.3V¹                      | LVPECL33E   |

| SSTL 25 Class I                          | SSTL25_I    |

| SSTL 25 Class II <sup>2</sup>            | SSTL25_II   |

| SSTL 25 Class I 差動                       | SSTL25D_I   |

| SSTL 25 Class II 差動 <sup>2,3</sup>       | SSTL25D_II  |

| SSTL 18 Class I                          | SSTL18_I    |

| SSTL 18 Class II <sup>2</sup>            | SSTL18_II   |

| SSTL 18 Class I 差動 <sup>3</sup>          | SSTL18D_I   |

| SSTL 18 Class II 差動 <sup>2, 3</sup>      | SSTL18D_II  |

| HSTL 18 Class I                          | HSTL18_I    |

| HSTL 18 Class II <sup>2</sup>            | HSTL18_II   |

| HSTL 18 Class I 差動 <sup>3</sup>          | HSTL18D_I   |

| HSTL 18 Class II 差動 <sup>2,3</sup>       | HSTL18D_II  |

| PCI 3.3V                                 | PCI33       |

| LVTTL 3.3V                               | LVTTL33     |

| LVTTL 3.3V 差動 <sup>3</sup>               | LVTTL33D    |

| LVCMOS 3.3V                              | LVCMOS33    |

| LVCMOS 3.3V 差動 <sup>3</sup>              | LVCMOS33D   |

| LVCMOS 2.5V (デフォルト)                      | LVCMOS25    |

| LVCMOS 2.5V 差動 <sup>3</sup>              | LVCMOS25D   |

| LVCMOS 2.5V、3.3V VCCIO バンク内 <sup>4</sup> | LVCMOS25R33 |

| LVCMOS 1.8V                              | LVCMOS18    |

| LVCMOS 1.8V 差動 <sup>3</sup>              | LVCMOS18D   |

| LVCMOS 1.8V、3.3V VCCIO バンク内 <sup>4</sup> | LVCMOS18R33 |

| LVCMOS 1.8V、2.5V VCCIO バンク内 <sup>4</sup> | LVCMOS18R25 |

| LVCMOS 1.5V                              | LVCMOS15    |

| LVCMOS 1.5V 差動 <sup>3</sup>              | LVCMOS15D   |

| LVCMOS 1.5V、3.3V VCCIO バンク内 <sup>4</sup> | LVCMOS15R33 |

| LVCMOS 1.5V、2.5V VCCIO バンク内 4            | LVCMOS15R25 |

| LVCMOS 1.2V                              | LVCMOS12    |

| LVCMOS 1.2V 差動 <sup>3</sup>              | LVCMOS12D   |

| MIPI                                     | MIPI        |

<sup>1.</sup> これらの差動出力規格は、外付け抵抗パックと共にコンプリメンタリな LVCMOS ドライバペアを用いることによって、エミュレートされる

<sup>2.</sup> 入力モードにのみ対応する。これらの I/O タイプでは出力や双方向モードには対応しない

<sup>3.</sup> これらの差動規格は、コンプリメンタリ LVCMOS ドライバペアを用いることによって実装される

<sup>4.</sup> これらは入力のみであり、I/O タイプを用いることができるように VREF を規定の特定値に設定する必要がある

#### **DRIVE**

DRIVE 強度属性は出力規格及び双方向 I/O 規格に使用可能です。デフォルトのドライブ値は、使用される I/O 規格によって決まります。表 10-9 に、指定された  $V_{CCIO}$  条件下でのシングルエンド I/O タイプの対応 するドライブ強度を示します。

### 表 10-9. レシオ sysIO 規格の出力ドライブ機能

| ドライブ強度 |          |          | I/O 3    | タイプ      |          |         |

|--------|----------|----------|----------|----------|----------|---------|

| (mA)   | LVCMOS12 | LVCMOS15 | LVCMOS18 | LVCMOS25 | LVCMOS33 | LVTTL33 |

| 2      | YES      |          |          |          |          |         |

| 4      |          | YES      | YES      | YES      | YES      | YES     |

| 6      | YES      |          |          |          |          |         |

| 8      |          | YES      | YES      | YES      | YES      | YES     |

| 12     |          |          | YES      | YES      | YES      | YES     |

| 16     |          |          |          | YES      | YES      | YES     |

| 24     |          |          |          |          | YES      | YES     |

<sup>1.</sup> ハードウェアのデフォルト (ブランク状態) の設定

#### DIFFDRIVE

DIFFDRIVE 強度属性は真の LVDS 出力規格に使用可能です。上辺の真の LVDS 差動ドライバが全て同一ドライブ強度を持つようにプログラムする必要があります。LVDS25 出力にのみ有効であるため、DIFFDRIVE 値は、Design Planner の DRIVE 列にリストされます。

Values: 1.25, 2.0, 2.5, 3.5, NA

Software Default: 3.5

Hardware Default (Erased): NA

### **PULLMODE**

PULLMODE オプションは、各 I/O ごとに別個にイネーブルまたはディセーブルにすることができます。ユーザが OPENDRAIN=ON を選択した場合、出力規格の PULLMODE はデフォルトでは NONE になります。 LVCMOS I/O タイプをアンダードライブまたはオーバードライブモードで使用した場合、UP 及び KEEPER 設定はできません。 FAILSAFE オプションは MLVDS25E 双方向モードでのみ使用可能です。

Values: UP, DOWN, NONE, KEEPER, FAILSAFE

Software Default: DOWN for LVTTL, LVCMOS, and PCI; all others NONE

Hardware Default (Erased): Down

#### **CLAMP**

CLAMPオプションは、各I/Oごとに別個にイネーブルまたはディセーブルにすることができます。MachXO2-640Uと MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスの下辺で使用可能な設定はPCIまたはOFFです。その他のI/Oは全てが、この属性に対してONまたはOFFの設定を持ちます。

Values: OFF, ON, PCI Software Default: OFF

Hardware Default (Erased): OFF

#### **HYSTERESIS**

レシオ型入力バッファは、2 つの入力ヒステリシス設定を持ちます。HYSTERESIS オプションは、LVCMOS12 入力を除いた LVTTL 及び LVCMOS 入力規格と双方向 I/O 規格のヒステリシス量を変更するために使用できます。LVCMOS12 入力は HYSTERESIS に対応しません。

LVCMOS25R33 と LVCMOS18R25、LVCMOS18R33, LVCMOS15R25、及び LVCMOS15R33 入力タイプは HYSTERESIS に対応しません。入力ピンそれぞれの HYSTERESIS オプションは、I/O タイプに対応している 場合には個別に設定できます。

Values: SMALL, LARGE, NA Software Default: SMALL

Hardware Default (Erased): With very small hysteresis (0~60 mV)

#### **VREF**

VREF オプションは、シングルエンド SSTL 及び HSTL 入力と参照型 LVMCOS 入力バッファの場合にイネーブルにされます。参照型 LVMCOS 入力バッファは、I/O タイプを LVCMOS25R33 や LVCMOS18R25、LVCMOS18R33、LVCMOS15R25、または LVCMOS15R33 と選択することによって指定されます。VREF 信号を使用しない全ての I/O タイプには、デフォルト値 NA が適用されます。

VREF はデフォルトではシングルエンド SSTL/HSTL 入力と LVCMOS25R33、LVCMOS18R25、LVCMOS18R33、LVCMOS15R25、または LVCMOS15R33 入力の外部 VREF ピンになります。ユーザは、Diamond ソフトウェアの Spreadsheet View にある "VREF Location(s) (VREF 位置)" ポップアップ・ウィンドウで VREF\_NAME 値を入力できます。こうすることで、Diamond Spreadsheet View の Port Assignments (ポート割り当て) タブの VREF 列に、I45、I50 及び I55 値に加えて、VREF\_NAME が使用可能な値として提供されます。VREF\_NAME 値によって指定されるピン位置は、その I/O バンクの VREF ドライバとして使用されます。VREF\_NAME は、ユーザが外部 VREF ピンとしてピンを使用したい場合にのみ必要です。そうでなければ、ソフトウェアによって自動的にピンが VREF 信号に割り当てられます。

I/O バンクごとに VREF ピンまたは内部 VREF ドライバは 1 つのみです。それぞれの I/O バンクに使用できるのは、I45、I50、I55 または VREF1\_LOAD から選択した 1 つの VREF ドライバ設定のみです。この属性は、ソフトウェアの GUI で、または ASCII 制約ファイルで設定できます。

Values: OFF, I45, I50, I55, VREF NAME

Software Default: NA

Hardware Default (Erased): OFF

#### **OPENDRAIN**

OPENDRAIN オプションは、全ての LVTTL 及び LVCMOS 出力規格と双方向 I/O 規格に使用可能です。各 sysIO は別個にオープンドレインになるように割り当てることができます。OPENDRAIN 属性を使用した場合、PULLMODE は NONE、CLAMP は OFF にする必要があります。

Values: OFF, ON Software Default: OFF

Hardware Default (Erased): OFF

#### **SLEWRATE**

各 I/O ピンは出力及び双方向 I/O ピンごとにスルーレート制御を指定できます。これは入力または真の差動出力には無効な属性です。

Values: FAST, SLOW, NA Software Default: SLOW

Hardware Default (Erased): SLOW

## **DIFFRESISTOR**

下辺の I/O ピンは MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 デバイスで、オンチップ差動入力終端抵抗に対応します。終端レジスタは、sysIO のプライマリペア及びセカンダリペアの両方に使用可能です。対応する値はゼロ(OFF)または  $100\,\Omega$  です。

Values: OFF, 100 Software Default: OFF

Hardware Default (Erased): OFF

#### DIN/DOUT

DIN/DOUT オプションは各 I/O に使用可能で、別個にコンフィグレーションできます。入力レジスタは、DIN 属性が割り当てられたときに入力に使用されます。同様に、DOUT 属性が指定されると出力レジスタが割り当てられます。デフォルトでは、可能であれば DIN または DOUT が、入力レジスタまたは出力レジスタに自動的に割り当てられます。

#### LOC

この属性は、マッピングプロセス後にコンポーネントのサイト位置を指定します。複数のコンポーネントに付加される場合は、これらのブロックが指定のサイトに一緒にマップされることを示します。パッドに割り当てられる場合は PIC サイトを指定します。LOC 属性は I/O セルとクロック、及び内部フリップフロップになるコンポーネントに付加できますが、論理セルに割り当てられる組み合わせ論理に与えてはいけません。そのような付加を行うと、位置指定制約の生成に失敗する可能性があります。LOC 属性はレジスタ順序付け(register ordering)をオーバーライドします。

#### バンク VCCIO

この属性はバンクの有効な I/O タイプを検証するため、またいずれの入力バッファを使用するかを決定するため、そして I/O タイプに適用可能な正しいドライブ強度を設定するために必要です。I/O バンク情報は HDL レベルでは不要なため、この属性は Diamond ソフトウェアの Spreadsheet View、または ASCII 制約ファイルで使用できます。

Values: AUTO, 3.3, 2.5, 1.8, 1.5, 1.2.

Software Default: AUTO. Hardware Default (Erased): NA

# sysIO プリミティブ

ソフトウェア・ライブラリには多数の sysIO プリミティブがあります。一部の sysIO 機能が利用できるのは HDL ソースコードでプリミティブをインスタンス化した場合に限られるため、このセクションでは少しだけ 取り上げて説明します。

## TSALL (Tri-State All、全てトライステート)

MachXO2 デバイスは、全出力バッファに対するトライステート制御をイネーブルまたはディセーブルにするために使用される TSALL 機能に対応します。TSALL 専用ピンはないため、TSALL 機能を制御する用途に任意の汎用 I/O ピンを選択できます。TSALL 機能をイネーブルにするためには、TSALL プリミティブをソースコードにおいてインスタンス化する必要があります。本プリミティブの入力は、入力ピンまたは内部信号を割り当てることができます。

値 TSALL=1 では全ての出力がトライステートになりますが、TSALL=0 時には出力は OE で個別に制御されます。

### 図 10-5. TSALL プリミティブ

### DELAYE(固定データ遅延)

本プリミティブは、MachXO2 デバイスの全バンク全 sysIO バッファに対して、最長 32 ステップのスタティック (固定) 遅延に対応します。遅延ステップ値については、"MachXO2 Family Data Sheet" を参照してください。入力遅延を設定するために USER DEFINED モードを選択できますが、このプリミティブは、"TN1203,

MachXO2 High-Speed Source Synchronous and Memory Interfaces (高速ソースシンクロナスとメモリインターフェイス) "で説明されている定義済みソースシンクロナス・インターフェイスによって主に使用されます。

## 図 10-6. DELAYE プリミティブと関連属性

| アトリビュート   | 記述            | 値                                                                                | ソフトウェア・デフォルト |

|-----------|---------------|----------------------------------------------------------------------------------|--------------|

| DEL_MODE  | インダーフェイスに収存する | SCLK_ZEROHOLD ECLK_ALIGNED ECLK_CENTERED SCLK_ALIGNED SCLK_CENTERED USER_DEFINED | USER_DEFINED |

| DEL_VALUE | ユーザ定義の遅延値     | DELAY0DELAY31                                                                    | DELAY0       |

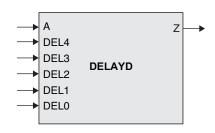

### DELAYD(ダイナミックデータ遅延)

本プリミティブでは、規模が MachXO2-640U と MachXO2-1200/U 以上のデバイスにおいて、下辺バンク (バンク 2) の sysIO バッファに対してダイナミックデータ遅延が可能です。5 ビット入力は、デバイス動作中の遅延を修正するために、ユーザ論理によって制御できます。

## 図 10-7. DELAYD プリミティブ

# 設計上の注意点及び使用法

このセクションでは、前セクションで詳述した MachXO2 設計の規則及び注意点の概略を示します。表 10-6に MachXO2 デバイスの各辺におけるその他の I/O 機能のリストを示してあります。

## 全ての MachXO2 デバイスに共通の sysIO バッファ機能

- 1. 全てのバンクが真の差動入力に対応します.

- 2. A全てのバンクが外部抵抗とコンプリメンタリ LVCMOS 出力を用いて、エミュレート差動出力に対応できます。エミュレート差動出力バッファは、プライマリペアとセカンダリペアの両方で対応可能です。

- 3. 3. 全てのバンクがプログラマブル I/O クランプを持ちますが、それらは PCI 準拠のクランプではありません。

- 4. 4. 全てのバンクが弱いプルアップ、プルダウン、及びバスキーパ (バスホールドラッチ) 設定を各 I/O で別個に対応できます。

- 5. 5. VCCIO 電圧レベルと、選択した I/O タイプとによって、プルモード、ヒステリシス、クランプ動作、及びドライブ強度など、バンクが対応可能な I/O の特性が決定されます。アンダードライブまたはオーバードライブ条件下のバンクにおいて、複数の入力規格に対応できます。バンクの VREF 設定に対応できるのは 1 つのセカンダリ入力規格のみです(例えば、LVCMOS25R33 では 3.3V の VCCIO バンクにおいて VREF は 1.25V の必要があります)。各バンクは、バンクの VCCIO 設定に関係なく 1.2V 入力に対応します。

- 6. 6. 各バンクは1つの V<sub>CCIO</sub> 信号に対応します。

- 7.7. 各バンクは、外部ピンか内部 V<sub>REF</sub> ジェネレータかに関わらず、1 つの VREF 信号に対応します。

# MachXO2-256 及び MachXO2-640 に固有の sysIO バッファ規則

- 1. 真の差動出力バッファに対応しません。

- 2. 内部 100 Ω 差動入力終端抵抗はありません。

- 3. PCI クランプに対応しません。

# MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、及び MachXO2-7000 に固有の sysIO バッファ規則

- 1. バンク 0 (上辺) のみが、プログラマブル・ドライブ強度を持つ真の差動出力バッファを持ちます。プラ イマリペアのみが真の差動出力バッファに対応します。

- 2. 2. バンク 2 (下辺) のみに内部  $100\Omega$  差動入力終端抵抗があります。

- 3. バンク2(下辺)のみが PCI 準拠のクランプに対応します。

## 表 10-10. デバイスの各辺におけるその他の I/O 機能

| 機能                    | 上辺  | 下辺               | 左辺  | 右辺  |

|-----------------------|-----|------------------|-----|-----|

| 100 Ω 差動抵抗            | _   | Yes <sup>1</sup> | _   | _   |

| 活線挿抜                  | Yes | Yes              | Yes | Yes |

| クランプ <sup>3</sup>     | Yes | Yes              | Yes | Yes |

| PCI 互換クランプ            | _   | Yes <sup>1</sup> | _   | _   |

| 弱いプルアップ <sup>3</sup>  | Yes | Yes              | Yes | Yes |

| 弱いプルダウン <sup>2</sup>  | Yes | Yes              | Yes | Yes |

| バスキーパ3                | Yes | Yes              | Yes | Yes |

| 入力ヒステリシス <sup>3</sup> | Yes | Yes              | Yes | Yes |

| スルーレート制御              | Yes | Yes              | Yes | Yes |

| オープンドレイン              | Yes | Yes              | Yes | Yes |

- 1. MachXO2-640U と MachXO2-1200/U、MachXO2-2000/U、MachXO2-4000、および MachXO2-7000 デ バイスで対応する

- 2. ソフトウェアのデフォルト設定

- 3. 特定条件下での I/O 特性

a.LVCMOS12 には HYSTERESIS オプションはない

b.HYSTERESIS オプションと BUS KEEPER オプションは参照型入力規格では利用できない c.レシオ入力バッファをアンダードライブかオーバードライブ条件で用いるとき、HYSTERESIS 設

定は NA になり、CLAMP 設定は OFF に、そして UP と KEEPER PULLMODE 設定は対応しない

d.差動レシーバでは HYSTERESIS とバスキーパ機能は無効

# テクニカルサポート支援

e-mail: techsupport@latticesemi.com インターネット:www.latticesemi.com

# 日本語版更新履歴

| 日付       | バージョン    | 新該当ページ                  | 更新概要                                              |

|----------|----------|-------------------------|---------------------------------------------------|

| 2010年11月 | 01.0     |                         | 初版                                                |

| 2011年1月  | 01.1     |                         | 超多ピン ("U") デバイスに関する記述全面                           |

| 2011年4月  | 01.2     |                         | Lattice Diamond ツールに関する更新                         |

| 2011年7月  | 01.3     |                         | 日本語版初版。英語オリジナルでは 1200-R1 に関する注記が追加されているが、日本語版では省略 |

| 2012年2月  | 01.4     |                         | ロゴ更新、ドキュメント・ステータスを Preliminary から正規               |

| 2013年3月  | 01.5     | 10-8                    | 表 10-6 脚注記述を更新                                    |

|          |          | 10-9                    | プログラマブル・スルーレート節に追記                                |

| 2013年10月 | 1.7      | 10-8                    | 表 10-6 1.2V 入力対応セルを更新                             |

|          |          | 10-11,12,18 -<br>20, 22 | I/O_TYPE を IO_TYPE に変更                            |

| 2014年12月 | 1.8, 1.9 | 10-8                    | 表 10-6、1.2V 列の入力、1.2V / 1.5V 以外の YES を削除          |

|          |          | 10-13                   | 表 10-9、脚注追加                                       |

|          |          | $10-13 \sim 10-15$      | 各パラメータのデフォルト値、変更・追加                               |

| 2015年5月  | 2.0      | 2, 3                    | 表 10-1、10-2 に MIPI を追加                            |

|          |          | 6                       | 表 10-4 に MIPI を追加                                 |

|          |          | 12                      | 表 10-8 に MIPI を追加                                 |

# 付録 A. sysIO HDL 属性

sysIOsysIO 属性は HDL ソースコードで直接使用できます。本セクションでは MachXO2 PLD ファミリが対応可能な sysIO 属性のリストを示します。ここで示した Synplify® 論理合成ツールの正しい構文及び例は参照用です。

## VHDL 言語での属性

## 構文

## 表 10-11. VHDL 属性の構文

| 属性           | 構文                                                                                                 |

|--------------|----------------------------------------------------------------------------------------------------|

| IO_TYPE      | attribute IO_TYPE: string; attribute IO_TYPE of Pinname: signal is "IO_TYPE Value";                |

| DRIVE        | attribute DRIVE: string; attribute DRIVE of Pinname: signal is "Drive Value";                      |

| DIFFDRIVE    | attribute DRIVE: string; attribute DRIVE of Pinname: signal is "Diffdrive Value";                  |

| DIFFRESISTOR | attribute DIFFRESISTOR: string; attribute DIFFRESISTOR of Pinname: signal is "DIFFRESISTOR Value"; |

| CLAMP        | attribute CLAMP: string; attribute CLAMP of Pinname: signal is "Clamp Value";                      |

| HYSTERESIS   | attribute HYSTERESIS: string;<br>attribute HYSTERESIS OF Pinname: signal is "Hysteresis Value";    |

| VREF         | NA                                                                                                 |

| PULLMODE     | attribute PULLMODE: string;<br>attribute PULLMODE of Pinname: signal is "Pullmode Value";          |

| OPENDRAIN    | attribute OPENDRAIN: string; attribute OPENDRAIN of Pinname: signal is "OpenDrain Value";          |

| SLOWSLEW     | attribute PULLMODE: string; attribute PULLMODE of Pinname: signal is "Slewrate Value";             |

| DIN          | attribute DIN: string;<br>attribute DIN of Pinname: signal is "value";                             |

| DOUT         | attribute DOUT: string;<br>attribute DOUT of Pinname: signal is "value";                           |

| LOC          | attribute LOC: string; attribute LOC of Pinname: signal is "Pin locations";                        |

| BANK VCCIO   | NA                                                                                                 |

## 例

# IO\_TYPE

```

--**Attribute Declaration***

ATTRIBUTE IO_TYPE: string;

--***IO_TYPE assignment for I/O Pin***

ATTRIBUTE IO_TYPE OF portA: SIGNAL IS "PCI33";

ATTRIBUTE IO_TYPE OF portB: SIGNAL IS "LVCMOS33";

ATTRIBUTE IO_TYPE OF portC: SIGNAL IS "SSTL18_I";

ATTRIBUTE IO_TYPE OF portD: SIGNAL IS "LVDS25";

```

#### **DRIVE**

```

--***Attribute Declaration***

ATTRIBUTE DRIVE: string;

--***DRIVE assignment for I/O Pin***

ATTRIBUTE DRIVE OF portB: SIGNAL IS "8";

```

## **DIFFDRIVE**

```

--***Attribute Declaration***

ATTRIBUTE DIFFDRIVE: string;

--*** DIFFDRIVE assignment for I/O Pin***

ATTRIBUTE DIFFDRIVE OF portD: SIGNAL IS "2.0";

```

#### **DIFFRESISTOR**

```

--***Attribute Declaration***

ATTRIBUTE DIFFRESISTOR: string;

--*** DIFFRESISTOR assignment for I/O Pin***

ATTRIBUTE DIFFRESISTOR OF portD: SIGNAL IS "100";

```

#### CLAMP

```

--***Attribute Declaration***

ATTRIBUTE CLAMP: string;

--*** CLAMP assignment for I/O Pin***

ATTRIBUTE CLAMP OF portA: SIGNAL IS "PCI33";

```

### **HYSTERESIS**

```

--**Attribute Declaration***

ATTRIBUTE HYSTERESIS: string;

--*** HYSTERESIS assignment for Input Pin***

ATTRIBUTE HYSTERESIS OF portA: SIGNAL IS " LARGE ";

```

## **PULLMODE**

```

--**Attribute Declaration***

ATTRIBUTE PULLMODE : string;

--**PULLMODE assignment for I/O Pin***

ATTRIBUTE PULLMODE OF portA: SIGNAL IS "DOWN";

ATTRIBUTE PULLMODE OF portB: SIGNAL IS "UP";

```

## **OPENDRAIN**

```

--***Attribute Declaration***

ATTRIBUTE OPENDRAIN: string;

--***Open Drain assignment for I/O Pin***

ATTRIBUTE OPENDRAIN OF portB: SIGNAL IS "ON";

```

#### **SLEWRATE**

```

--***Attribute Declaration***

ATTRIBUTE SLEWRATE : string;

--*** SLEWRATE assignment for I/O Pin***

ATTRIBUTE SLEWRATE OF portB: SIGNAL IS "FAST";

```

## DIN/DOUT

```

--**Attribute Declaration***

ATTRIBUTE din : string; ATTRIBUTE dout : string;

--** din/dout assignment for I/O Pin***

ATTRIBUTE din OF input_vector: SIGNAL IS "TRUE ";

ATTRIBUTE dout OF output vector: SIGNAL IS "TRUE ";

```

#### LOC

```

--***Attribute Declaration***

ATTRIBUTE LOC: string;

--*** LOC assignment for I/O Pin***

ATTRIBUTE LOC OF input vector: SIGNAL IS "E3,B3,C3";

```

# Verilog 言語での属性

## 構文

# 表 10-12. Verilog 属性の構文

| 属性           | 構文                                                                  |

|--------------|---------------------------------------------------------------------|

| IO_TYPE      | PinType PinName /* synthesis IO_TYPE="IO_Type Value"*/;             |

| DRIVE        | PinType PinName /* synthesis DRIVE="Drive Value"*/;                 |

| DIFFDRIVE    | PinType PinName /* synthesis DIFFDRIVE =" DIFFDRIVE Value"*/;       |

| DIFFRESISTOR | PinType PinName /* synthesis DIFFRESISTOR =" DIFFRESISTOR Value"*/; |

| CLAMP        | PinType PinName /* synthesis CLAMP =" Clamp Value"*/;               |

| HYSTERESIS   | PinType PinName /*synthesis HYSTERESIS = "Hysteresis Value" */;     |

| VREF         | N/A                                                                 |

| PULLMODE     | PinType PinName /* synthesis PULLMODE="Pullmode Value"*/;           |

| OPENDRAIN    | PinType PinName /* synthesis OPENDRAIN ="OpenDrain Value"*/;        |

| SLOWSLEW     | PinType PinName /* synthesis SLEWRATE="Slewrate Value"*/;           |

| DIN          | PinType PinName /* synthesis DIN= "value" */;                       |

| DOUT         | PinType PinName /* synthesis DOUT= "value" */;                      |

| LOC          | PinType PinName /* synthesis LOC="pin_locations "*/;                |

| Bank VCCIO   | N/A                                                                 |

## 例

```

//IO_TYPE, PULLMODE, SLEWRATE and DRIVE assignment

output portB /*synthesis IO_TYPE="LVCMOS33"

PULLMODE ="UP" SLEWRATE ="FAST" DRIVE ="20"*/;

output portC /*synthesis IO_TYPE="LVDS25" */;

//DIFFDRIVE

output portD /* synthesis IO_TYPE="LVDS25" DIFFDRIVE="2.0"*/;

//DIFFRESISTOR

output [4:0] portA /* synthesis IO_TYPE="LVDS25" DIFFRESISTOR ="100"*/;

//CLAMP

output portA /*synthesis IO_TYPE="PCI33" CLAMP ="PCI" */;

//HYSTERESIS

input mypin /* synthesis HYSTERESIS = "LARGE" */;

//OPENDRAIN

output portA /*synthesis OPENDRAIN ="ON"*/;

// DIN Place the flip-flops near the load input

input load /* synthesis din="" TRUE */;

```

# // DOUT Place the flip-flops near the outload output

output outload /\* synthesis dout="TRUE" \*/;

## //LOC pin location

input [3:0] DATA0 /\* synthesis loc="E3,B1,F3"\*/;

## //LOC Register pin location

reg data\_in\_ch1\_buf\_reg3 /\* synthesis loc="R10C16" \*/;

## //LOC Vectored internal bus

reg [3:0] data\_in\_ch1\_reg /\*synthesis loc ="R10C16,R10C15,R10C14,R10C9" \*/;

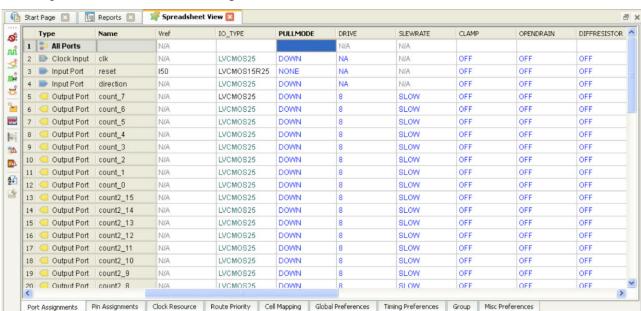

# 付録 B. Spreadsheet View を使用した sysIO 属性

sysIO バッファ属性は、Diamond 設計ツールで利用可能な Spreadsheet View を使用して割り当てることができます。VREF 及びバンク VCCIO など、HDL 属性にない属性は Spreadsheet View)の GUI にあります。

Port Assignment(ポート割り当て)タブには、設計の全てのポート及び設計制約として使用可能な全ての sysIO 属性がリストされます。これらセルのそれぞれをクリックすると、そのポートに有効な全 I/O 制約の リストが示されます。各列はその次の列よりも優先されます。したがって、特定の IO\_TYPE が選択された場合、DRIVE、PULL-MODE、SLEW-RATE 及びその他の属性には、その IO\_TYPE に有効な組み合わせがリストされます。ピン位置は Port Assignment タブの Pin 列を使用してロックできます。セルを右クリックすると、使用可能な全てのピン位置がリストされます。Spreadsheet View は DRC チェックを実行して、正しくない sysIO 属性割り当ての有無を調べることができます。

Spreadsheet View を使用して割り当てられた全ての設計制約は論理制約ファイル (.lpf) に書き出されます。

図 10-8. Spreadsheet View の Port Assignment タブ

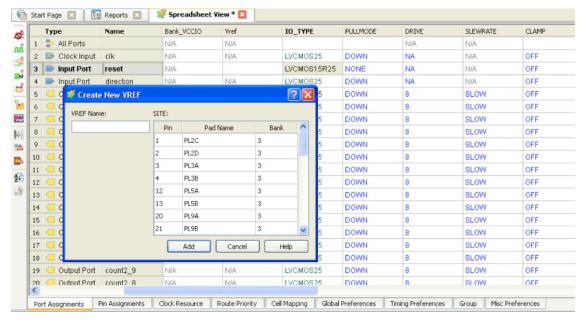

図 10-9. Spreadsheet View の VREF 名と位置のポップアップ・ウィンドウ

# Spreadsheet View における V<sub>REF</sub> 割り当て

VREF 属性は、Spreadsheet View で左側の Vref Locations(s) (VREF 位置) ボタンをクリックすることで割り当てられます。このボタンを使用する必要があるのは、VREF ドライバを特定の位置にする場合のみです。それ以外の場合、VREFドライバ信号はソフトウェアによって、sysIO バンク規則に違反しない任意の位置に割り当てられます。

VREF\_NAME が特定のピンに割り当てられた場合、その VREF\_NAME は Port Assignments タブの VREF 列にリストされます。VREF\_NAME及びピン位置の両方が Pin Attribute (ピン属性) シートの VREF 列に反映されます。

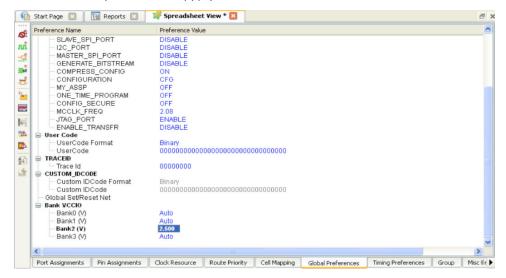

# Spreadsheet View におけるバンク V<sub>CCIO</sub> 設定

バンク VCCIO は、Spreadsheet View の Global (グローバル) タブで使用できます。バンク VCCIO の値は、特定のバンクの VCCIO 値を決定するためにユーザが選択できます。

図 10-10. Global Preference (グローバル制約) タブのバンク VCCIO

# 付録 C. 制約ファイル (ASCII ファイル) を使用した sysIO 属性

sysIO 属性を sysIO バッファ制約として制約ファイル (.lpf) に直接入力できます。LPF ファイルは、Spreadsheet Vie または直接テキストエディタで作成または修正された論理制約を格納する、論理合成後の FPGA 設計制約ファイルです。また HDL ソースからの論理制約も含んでいます。Diamond ソフトウェアで Spreadsheet View を修正すると、自動的に LPF ファイルの内容が更新され、また逆の更新も同様に行われます。 Spreadsheet View の設定は、保存されると制約ファイルに反映されます。対応可能な設計制約及び各構文の詳細については、Diamond のヘルプを参照してください。